# Low power FIR filter design using Graph Based Algorithm

R. Ramathilagam<sup>1</sup>, B. Karthiga<sup>2</sup>

<sup>1</sup>PG Student, Srinivasan Engineering College, Perambalur, TamilNadu, India.

Email : thilaga.santhi10@gmail.com Contact No :09597670430

<sup>2</sup>Associate Professor, Department of ECE, Srinivasan Engineering College, Perambalur, TamilNadu, India.

Email : karthiga.jaya@yahoo.com Contact No : 09443412750

*Abstract:*-Digital filters are a very important part of DSP. In fact, their efficient performance is one of the key reasons that DSP has become so popular. In this paper, we designed an FIR filter using graph based algorithm. Common Sub expression Elimination (CSE) algorithm has a drawback that, it defines the constant in number representation such as CSD (or) MSD, binary. But, when implementing Graph Based (GB) algorithm, it is not restricted to any number of representation of constant. By reducing the height of the tree structure, the numbers of adders are reduced. It reduces the area and power than existing one. The implementation of GB Algorithm is done by Verilog.

Keywords: Finite Impulse Response (FIR) filtering, Common Sub expression Elimination (CSE) algorithm, Graph Based (GB) algorithm. \*\*\*\*\*

### I. Introduction

Digital filter is the filter which arises due to its operation on discrete time signals. The term finite impulse response arises because the filter output is computed as a weighted, finite term sum, of past, present, and perhaps future values of the filter input, i.e.,

$y[n] = \sum_{k=0}^{N} h[k] x[n-k]$ -----(1)

The implementation of FIR filter requires three basic building blocks-multiplication, addition and signal delay. We also need to be able to store filter coefficients in memory. In DSP system, multiplier must be fast and must have sufficient precision to support the desired application. If the multiplier is not fast, throughput gets affected. In an FIR filter additions are required in combinations with multiplications, hence DSP feature multiply accumulate microprocessors (MAC)units. Adders generally operate with just two input at a time. The unit delay provides a one sample signal delay. A sample value is stored in a memory slot for one sample clock cycle and then made available as an input to the next processing stage. An M-unit delay requires M-memory cells

An FIR filter of order N is characterized by N+1 coefficients and, in general, require N+1 multipliers and N two-input adders. Structures in which the multiplier coefficients are precisely the coefficients of the transfer function are called direct form structures.

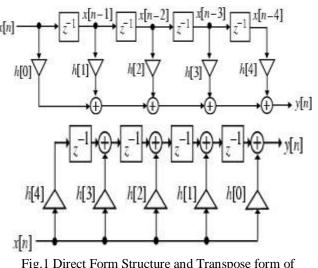

Fig.1 Direct Form Structure and Transpose form of direct structure

The transpose of the direct form structure shown earlier is indicated above. Both direct form structures are canonic with respect to delays.

The core of FIR filter design is the multiplication of a variable by a set of constants. The optimization of these multiplications can lead to improvements in various design parameters like area or power consumption. This problem is known as a multiple constant multiplication problem (MCM).

Graph based algorithms and common subexpression elimination (CSE) technique are two methods to tackle the MCM problem. Multiplier free design of MCM is achieved with the help of shift and adds operation which shares the common sub operations using canonical signed digit (CSD) coding and common sub expression elimination (CSE) to minimize the adder count of MCM. As a simple example, consider the constant multiplication 30914x.their decomposition in binary are listed as follows:

30914x=(111100011000010)binx=x<<14+x<<13+x<<7 +x<<11+x<<12+x<<6+x<<1.

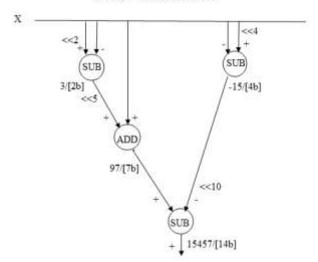

## II. COMMON SUB-EXPRESSION ELIMINATION (CSE)

C=30914="111100011000010

Fig.2 Common Sub-expression Elimination (CSE)

An algorithm for efficient solution for the multiple constant multiplication problems.

The idea of CSE can be demonstrated on a FIR filter design. The optimization procedure targets the minimization of the multiplier block area. After expressing the coefficients in a canonical signed digit (CSD) format in order to reduce the total number of nonzero bits(thus also the addition/subtractions necessary), an add shift expansion is performed. The goal of CSE is identify the bit patterns that are present in the coefficient set more than once. Since it is sufficient to implement the calculation of the multiple identical expressions only once, the resources necessary for these operations can be shared.

The CSE algorithm consists of four steps. First, all possible implementations of constants are extracted from the nonzero digits of the constants defined under a number representation: binary, CSD, or MSD. Then, the implementations of constants are represented in terms of a Boolean network. Third, the bit-level area optimization problem is formalized as a 0-1 ILP problem with a cost function to be minimized and a set of constraints to be satisfied. Finally, a set of operations that yields the minimum area solution is obtained using a generic 0-1 ILP solver.

#### III. GRAPH BASED (GB) ALGORITHM

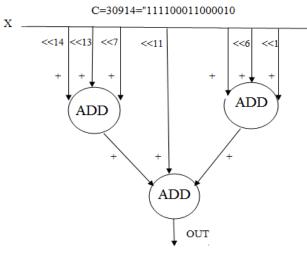

Fig .3.Graph Based Algorithm

The graph based algorithm which is introduced to reduce the addition in shift adds implementations of constant multiplications. These methods are not limited to any particular number representation and consider a large number of alternative implementations of a constant yielding better solution than the shift add implementation of constant multiplication.

### IV. SIMULATION AND SYNTHESIS REPORT

We performed the simulation and synthesis of Common Sub expression Elimination (CSE) and Graph Based (GB) algorithm.

|                                               | Device Utilization Summary |           |            |

|-----------------------------------------------|----------------------------|-----------|------------|

| Logic Utilization                             | Used                       | Available | Ublization |

| Number of Silve Rip Flaps                     | 124                        | 26.624    | 13,        |

| Number of 4 input LUTs                        | 320                        | 26,524    | 11         |

| Logic Distribution                            |                            |           |            |

| Number of occupied Silces                     | 182                        | 13.212    | .81        |

| Number of Slose containing only related logic | 182                        | 182       | 1001       |

| Number of Slices containing unrelated logic   | 0                          | 182       | 01         |

| Total Number of 4 input LUTs                  | 354                        | 26,624    | 15         |

| Number used an logic                          | 320                        |           |            |

| Number used as a route-thru                   | 34                         |           |            |

| Number of bonded (CE)                         | 116                        | 457       | 231        |

| KOB Rip Rops                                  | 2                          |           |            |

| Number of GCLKs                               | 1                          | 8         | 125        |

| Total equivalent gate count for design        | 4,401                      |           |            |

| Addeonal JTAG gate count for IOBs             | 5,568                      |           |            |

(b)

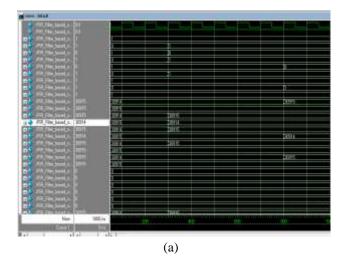

Fig.4. Common Sub expression Elimination (CSE) algorithm. (a) FIR filter based on adder tree by CSE output waveform. (b) Synthesis result for area.

| g vae-tilali                   |       |             |         |

|--------------------------------|-------|-------------|---------|

| 🕴 (FR_File_based_or_) St       |       |             |         |

| 👌 (FR_File_based_n.) St        |       |             |         |

| 😝 /FR_Filer_baset_c.   0000011 | 00000 |             | 1000011 |

| ⊕👌 /RR_Rier_beset_n.   92%2    | 3314  | \$163       | 300     |

| 😝 / FR_Filer_baset_o.   \$2742 | 33314 | <b>3163</b> | 300     |

| 😝 /FR_Filer_baset_o., 52742    | 33314 | 51638       | 370     |

| 😝 /FR_Filer_based_o.   \$2742  | 33314 | <b>5163</b> | 300     |

| 😝 /FR_Filer_baset_c.   \$2742  | 33314 | 51638       | 370     |

| 😝 /FR_Fler_baset_c.   C        |       |             |         |

| 😝 /FR_Fler_baset_c.   C        |       |             |         |

| 😝 /FR_Fler_baset_r D           |       |             |         |

| 😝 /FR_Filer_baset_o.   \$2742  | 33314 | <b>5163</b> | 300     |

| 😝 /FR_Flei_baet_c. (2012       | 33314 | 5163        | 300     |

|                                |       |             |         |

(a)

|                                               | Device Utiliza |           |             |

|-----------------------------------------------|----------------|-----------|-------------|

| Logic Utilization                             | Used           | Available | Utilization |

| Number of Slice Rip Raps                      | 55             | 7,168     | 15          |

| Number of 4 input LUTs                        | 107            | 7,168     | 13          |

| Logic Distribution                            |                |           |             |

| Number of occupied Sices                      | 58             | 3,584     | 15          |

| Number of Sices containing only related logic | 58             | 58        | 100%        |

| Number of Sices containing unrelated logic    | 0              | 58        | 偽           |

| Total Number of 4 input LUTs                  | 114            | 7,168     | 14          |

| Number used as logic                          | 107            |           |             |

| Number used as a route-timu                   | 7              |           |             |

| Number of bonded 1 <u>08s</u>                 | 31             | 141       | 21%         |

| ICB Rip Rops                                  | 5              |           |             |

| Number of GCLKe                               | 1              | 8         | 12%         |

| Total equivalent gate count for design        | 1,636          |           |             |

| Additional JTAG gate count for IOBs           | 1,488          |           |             |

(b)

Fig 5.Graph Based (GB) algorithm. (a) FIR filter based on adder tree by GB output waveform. (b) Synthesis result for area.

### TABLE

Comparison between area and power using Common Sub expression Elimination (CSE) and Graph Based (GB) algorithm.

| Parameters       | CSE      | GB       |

|------------------|----------|----------|

| Delay            | 20.360ns | 19.849ns |

| Number of slices | 124      | 55       |

### V. CONCLUSION

Graph based algorithm provides a significant changes in the method of shift and add operation, thereby height of tree structure is reduced. Thus in our paper, by the implementation of graph based algorithm, the area is maximum reduced, and the power is also reduced.

#### REFERENCE

- [1] 1] David W.Redmill and David, R.Bull, 1991, 'Design of primitive operator digital filter using genetic algorithm'

- [2] 2] DeepshikhaBharti,K.Anusudha,2011, 'High speed FIR filter based on truncated multiplier and parallel adder'. International Journal of Engineering Trends and Technology (IJETT) – Volume 5.

- [3] 3] Donald A. Lobo and Barry M.Pangrle,1991,'Redundant operator creation: A scheduling optimization technolog'.

- [4] 4] In-Cheol Park and Hyeong-Ju Kang,2001, 'Digital filter synthesis based on an algorithm to generate all minimal signed digit representations'.IEEE transactions on computer-aided design of integrated circuits and systems, vol. 21, no. 12, December.

- [5] 5] Levent Aksov, Member, IEEE, Cristiano Lazzari, Member, IEEE, 2013, 'Design of Digit FIRFilters: Algorithms, Architectures, and a CAD Tool', IEEE Transaction on VLSI systems, vol.21, no.3.

- [6] Mahesh Mehendale, S.D. Sherlekar,G.Venkatesh,june1995,'Synthesis of multiplier less FIR filter with minimum number of adder'.

- [7] A.P.Vinod, and Edmund M-K.Lai,Senior 2004,'An Efficient Coefficient-Partitioning Algorithm for Realizing Low Complexity digital filter'.Paper No. 2032

- [8] Y.Voronenko and M.Piicshel 2007, 'Multiplier less Multiple Constant Multiplication.