Mr. Gaurav M. Kathalkar Department of Elect. & Tele Engg. G. H. Raisoni College Of Engg. And Management Pune,India gauravkathalkar9090@gmail.com Prof. Vaishali Raut Department of Elect. & Tele Engg G. H. Raisoni College Of Engg. And Management Pune,India

*Abstract*— Design of binary circuit is restricted by the necessity of the interconnection. A conceivable arrangement could be touched base at by utilizing a bigger arrangement of signs over the same chip region. Quaternary outlines are picking up significance from that point of view. In this paper we design two types of full adder based on quaternary logic is proposed which will reduced the parameter such as area, power, and delay. The feature of this full adder is based on one hot encoding technique and binary encoding technique. All the design is using 180nm CMOS techniques. Sum and carry blocks are handled in two separate square controlled by the code generator unit. Plan check will be done by tanner tools.

#### I. INTRODUCTION

In binary digital circuit static power is directly related to the leakage power. In binary circuit number of interconnection is available to reduce that interconnection we can used quaternary adder. Quaternary circuit shows improvement in area, power and delay.[5]

Interconnection of area is determined by the number of interconnection and their length. Interconnection length is also determined by the complexity of interconnection.

The decimal number 255 in binary it will be 11111111 and in quaternary it is represented as 3333[1]. To reduce the area, interconnection, power, transistor by using quaternary logic. There are four quaternary states 0, 1, 2 and 3 for which we can take parallel comparable as 00, 01, 10 and 11 [5]. They are called as total low, medium low, medium high and supreme high. In the event that the bits of paired representation trade their position and quaternary state stay unaffected then it is called as twofold symmetry if not called as halter kilter.[3] This paper is organized as, section II full adder using one hot encoding. Section III Full adder using binary encoding, section IV Future scope and conclusion is in section V.

#### II. FULL ADDER USING ONE HOT ENCODING

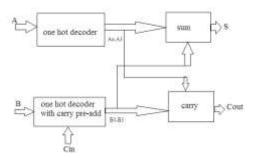

The propose quaternary full Adder designed with one hot encoding technique. It consists of one hot decoder block, one hot decoder with carry block, sum and carry block. In one hot decoder at a time only one bit active. A and B are the two input of full adder circuit. Barrel Shifter is controlled by two inputs A and B. In quaternary input logic level of 0, 1, 2, and are represented by 0V, 1V, 2V and 3V.

Figure 1: Block Diagram Of Quaternary Full Adder

#### One-Hot Encoder Block:-

In one hot encoding only one bit of the state vector is assert for any given state given state. All other state bits are zero. Thus if there are n state then n state flip-flops are required. As only one bit remains logic high and rest are logic low, it is called as one-hot encoding. And the input will generate A0-A3 four hot codes. Since there is a two inputs A and B.

# Encoding For The Input B With Carry Pre-Addition:-

It depends on the one contribution of the yield lines will be high and all others will be low. The point by point hardware incorporates down strict circuits, twofold XOR doors alongside double inverters to get fitting one hot yield. Thus the snake to be composed is a full viper we ought to likewise deal with the convey info. Thus because of this convey pre expansion is done to the information B before the yield is shared amongst Sum and Carry generators.

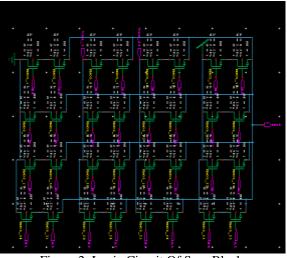

# Summer Block:-

Subsequently it is clear that from the table of a full adder the entirety part of the adder is only a movement of one info relying upon the other. To minimized the circuitry barrel shifter is used where 0V, 1V, 2V and 3V is the quaternary voltage level. In circuit diagram A0-A3, B0-B3 is the output of one hot encoding and sum block show in the circuit.

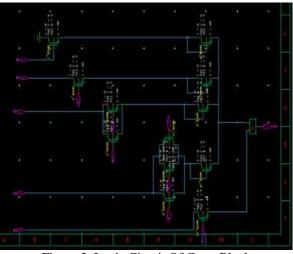

## Carry Block:-

The carry generator block utilized is only a blend of inputs where one info line goes about as select line and chooses or rejects a different line taking into account whether the blend of info is meeting the prerequisites of producing convey yield. The convey pre-expansion activity which happens in the main part of the snake, dispenses with the convey part if data B is 3V and convey in is high thus an OR entryway is utilized to spare that convey what's more, drive it to complete in the carry block circuit.

Figure 2: Logic Circuit Of Sum Block

Figure 3: Logic Circuit Of Carry Block

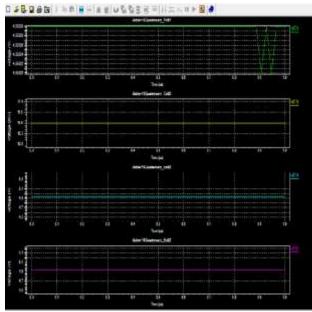

Figure 5: Output Of Quaternary 16-Bit Adder

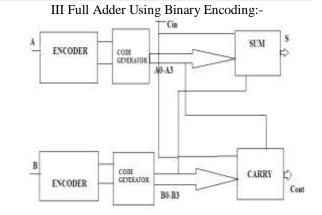

#### Encoder Block:-

In full adder using binary encoding there is a Encoder block the encoder block having input A and B yield is sustained to the code generator unit. Furthermore, this code generator unit produces codes which are used for the entirety and convey square to produce last estimation of entirety and convey. Code generator having output A0-A3 and B0-B3 and it is given to sum and carry block.

# Code Generator:-

Code generation is the process by which a compiler's code generator converts some intermediate representation of source code into a form (e.g., machine code) that can be readily executed by a machine. Code generator block generate the output A0-A3 and B0-B3. And it is given to sum and carry.

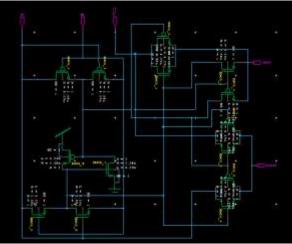

# Sum & Carry Block:-

In the full adder using unique encoding diagram the Sum and carry blocks are built with pass transistors. And this Pass transistor can be replaced by the transmission gates for proper logic levels. According to the levels of the input the quaternary voltage levels are switched towards output. The Codes A0, A1, A2, A3, B0, B1, B2 and B3 are generated by the code generator block which is used to control these pass transistors

Figure 6: Logic Circuit Of Carry Block

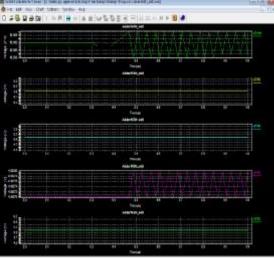

Figure 7: Output Of Quaternary Binary Adder

| Author                            | Technology | Del<br>ay  | Transisto<br>r Count | Average<br>Power |

|-----------------------------------|------------|------------|----------------------|------------------|

| Mr. t. R.<br>Pardhi[1]<br>2014    | 180nm      | 1.4<br>ns  | 120                  | 394uw            |

| Hirokatsu<br>Shirahama<br>[4]2008 | 180nm      | 1.4<br>ns  | 194                  | 194uw            |

| Ricardo<br>Cunha[7]2<br>006       | 180nm      | 2.2<br>4ns | 332                  | 181uw            |

| Proposed<br>work                  | 180nm      | 2.0<br>2ns | 200                  | 210uw            |

# Table I: COMPARISON

#### **IV. FUTURE SCOPE**

1) System will help to save the area because in quaternary it will design on a single chip that why area will be reduce.

2) It also used to reduce the transistor for design the circuit.

3) Circuit will also help to reduce the delay, Power consumption.

#### V. CONCLUSION

From latest research after studied various papers it is observed that work done on quaternary adder is very less. From literature review it is observed that they design and verify the single bit quaternary adder. In this paper, designing a 16-bit quaternary adder using various encoding techniques. In type I quaternary adder is required 200 transistors and 2.10 watt dissipates at 50nHz. In type II full adder circuit required 224 transistor and 2.91 watt dissipate at 50nHz. Simulation of the proposed circuit is carry out targeted for 180ns technology using tanner tool.

# REFERENCES

- [1]. Mr. t. R. Pardhi "Design of Quaternary Adder Using Various Encoding Techniques: A Review"Discovery , Volume 19,Number 56, May 12, 2014.

- [2]. Thoidis D.Soudris, I. Karafyllidis, S. Christofoidis, A Thanailaki, "Quaternary Voltage Mode Cmos Circuit For Multiple-Voltage" IEE Proc-Circuit Device Syst. Vol.145 No.2 April 1998.

- [3]. Amanda Das, Ifat Jahangir, Masud Hasan, Shafera Hossain "On Design and Anaiysis of Quaternary serial and parallel Adder" 978-1-4244-6890-4/10/\$26.00/2010 IEEE.

- [4]. Diogo Brito, Jorge R. Fernandes, José Monteiro "Quaternary Logic Lookup Table In Standard CMOS" Ieee Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 23, No. 2, February 2015.

- [5]. WU Haixia, ZHONG Shunan, QU Xiaonan, XIA Qianbin, CHENG Yueyang "Design of a Conditional Sum Adder Based on Multiple-Valued Logic" 978-1-4577-0321-8/11/\$26.00 ©2011 IEEE

- [6]. Kanchan G. Survawanshi, Dr. A. Y. Deshmukh "Power Optimization of Combinational Quaternary Logic Circuit" International Journal on Recent and Innovation Trends in Computing and communication" Volume:3 Issue 2,Feb2015.

- [7]. Hirokatsu Shirahama and Takahiro Hanyu, "Design of High- Performance Quaternary Adders Based on Output-Generator Sharing", Proceedings of the IEEE, 38th International Symposium on Multiple Valued Logic, pp.8-13, 2008.

- [8]. Neha W.Umredkar, M. A. Gaikwad, D. R. Dandekar "Review Of Quaternary Adder In Voltage Mode Multi-Valued Logic" International Journal Of Computer Application Recent Trends In Engineering Technology 2013.

- [9]. Prashant Y. Shende, Dr. R. V. Kshirsagar "Quaternary Adder Design using VHDL" International journal of Engineering research and application. Vol. 3 Issue 3, May 2013.

- [10]. Ricardo Cunha G. da Silva, "A novel voltage mode CMOS quaternary logic design", IEEE Transactions on Electron devices, vol.53, no 6, June 2006.

- [11]. Vasundara Patel K S, K. S. Gurumurthy "Design of high performance Quaternary adders" 2011 41st IEEE International Symposium on Multiple-valued logic.

- [12]. Uma Nirmal, Geetanjali Sharma, Yogesh Mishra "A LowPower High Speed Adders Using MTCMOS Technique"IJCEM International Journal of Computational Engineering & Manegment, Vol 13, July 2011.