# Design of Reversible Even and Odd Parity Generator and Checker Using Multifunctional Reversible Logic Gate (MRLG)

Vinay Kumar Department of ECE PEC University Of Technology . Chandigarh, India Vinaykdz@gmail.com Divya Dhawan Asst. Professor Department of ECE PEC University Of Technology. Chandigarh, India divyadhawan@pec.ac.in

*Abstract*— Digital data transmission made more efficient of communication. For error free transmission in the digital communication at the source end used parity generator and at destination used parity checker. This paper proposed design of 3 bit reversible Even and Odd parity generator and checker using the multifunctional reversible logic gate (MRLG). The proposed design is designed and simulated using cadence software.

Keywords- reversible logic, Parity generator, Parity checker, MRLG.

\*\*\*\*\*

#### I. INTRODUCTION

Moore's law, that has only outperformed itself in the past, states that, the number of the transistor fabricated in an IC doubles in a period of a year and a half, so does the heat generation arising from the increasing chip density. Hence In the past years the incentives of Reversible logic have become increasingly motivating. During the operation conventional gates dissipate heat on losing a bit. In 1973 C.H Bennett [1], a physicist, demonstrated that when a circuit is designed with reversible logic no energy dissipation takes place. A circuit is reversible if one can recover input data from the output data which means the circuit information is lossless. The general considerations of bijectivity is imposed on the design of reversible logic, which means that the circuit design should have equal number of output and input and one to one mapping. This eliminates the loss of information that is main reason for power dissipation. The unused outputs of reversible gate are called Garbage output similarly Redundant Inputs to reversible gate are called Garbage inputs. Complexity and Performance of reversible circuits/ gate are defined by the following parameters

- Number of logic gates

- Number of garbage and constant inputs

- Number of Garbage outputs.

- Fan-out is restricted in reversible logic gate. The fanout of each gate is equal to one. If more fan out are required then use a copying gate.

In the end of this paper we get a new reversible logic gate so as to produce minimum no. of garbage output, lower quantum cost and minimum delay. In Section II we have outlined the related work in terms of gate size, functionality, number of inputs and outputs and logic description. In Section III we have described the proposed New Multifunctional Reversible Logic Gate (MRLG) with CMOS logic structures. In Section IV and V give the basic idea of the reversible parity generator and checker. In Section VI we have design the circuits of proposed parity generator and checker. The proposed design and MRLG gate has been developed to operate in the voltage range of 1.5 V to 5V with length 180nM and width  $2\mu$ M transistor with gpdk 180 process. Section VII presents the simulation result and Input output waveform. Conclusion is presented in section VIII.

## II. RELATED WORK

Various similar implementation of logic gates have been addressed in [1-14], the classification is defined in terms of its size and functionality. The 1x1 reversible gate is NOT. The 2x2 reversible gate is Feynman. The 3x3 reversible gates are Fredkin, Toffoli, Peres, TR gate, new gate, PRT-1 and PRT-2 and the 4x4 gate includes MKG, TSG and DKG. In Table 1 we have described the logic functionality and a brief description of various gates.

| D 11       | <u> </u> |                                                |                        |

|------------|----------|------------------------------------------------|------------------------|

| Reversibl  | Gate     |                                                |                        |

| e Gate     | Size     | Input and output                               | Logic Description      |

| (Existing) |          |                                                |                        |

| Feynman    |          | Input A, B                                     | Output $Q = A'$ ,      |

| 1985 [ 5]  | 2x2      | Output $P = A$ and                             | when input A=1         |

|            |          | $\mathbf{Q} = \mathbf{A} \bigoplus \mathbf{B}$ | Q = Buffer,            |

|            |          |                                                | otherwise              |

|            |          | Input A, B, C                                  | Output $Q = C$ and $R$ |

| Fredkin    |          | Output P=A,                                    | = B when input A $=$   |

| 1982 [6]   | 3x3      | Q=A'B⊕AC and                                   | 1. Otherwise $Q = B$   |

|            |          | R=A'C'⊕ AB)                                    | and $R = C'$ .         |

|            |          | Input A, B, C                                  | R = C', When $A = 1$   |

| Toffoli    | 3x3      | Output P=A,                                    | and $\mathbf{B} = 1$   |

| 1980 [ 16] |          | Q=B and                                        | R = Buffer,            |

|            |          | R=AB⊕ C                                        | otherwise              |

| Peres      |          | Input A, B, C                                  | Q = B', When A=1       |

| 1985[14]   | 3x3      | Output P=A, Q=                                 | R=C', When $A=1$       |

|            |          | $A \oplus B$ and                               | and B=1.               |

|            |          | R=A⊕ BC                                        |                        |

|            |          | Input A, B, C                                  | R = A NAND B,          |

| TR 2011    | 3x3      | Output P=AQ=                                   | when B = inverted      |

| [7]        |          | A⊕ B, R=AB'⊕                                   | input                  |

|            |          | C                                              | -                      |

|            |          | Input A, B, C                                  | R = A' Ex-OR B',       |

| New 2002   | 3x3      | Output P=A, Q=                                 | When C=0               |

| [2]        |          | AB⊕ C,                                         | Else Q= A AND B        |

|            |          | R=A'C'⊕ B'                                     |                        |

|            | 1   |                                |                       |

|------------|-----|--------------------------------|-----------------------|

|            |     | Input A, B, C                  | Q = B Ex - NOR C,     |

|            |     | Output                         | and $R = B OR C$      |

| PRT-I      | 3x3 | P=AB⊕B'C,Q=                    | When A=1.             |

| 2011[15]   |     | $A \oplus B \oplus C$ and      | and $Q = A Ex-OR B$ , |

|            |     | $R=AB' \oplus BC$              | and $R = A AND B$ ,   |

|            |     |                                | When C=0              |

|            |     | Input A, B, C                  | P = B OR C, When      |

| PRT-II     | 3x3 | Output                         | A=1, and              |

| 2011 [ 15] |     | P=BC⊕AC',                      | Q= A Ex-NOR C,        |

|            |     | Q=A'(B⊕C)+A                    | When $C=1$            |

|            |     | B and R=C                      |                       |

|            |     | Input A, B, C, D               |                       |

| TSG 2005   | 4X4 | Output $P = A, Q$              | S = A AND B, When     |

| [8]        |     | $= A' C' \oplus B', R$         | C=0 & D= 0            |

|            |     | $= (A'C' \oplus B') \oplus$    |                       |

|            |     | A and                          |                       |

|            |     | S=(A'C'⊕B')                    |                       |

|            |     | $D \oplus (AB \oplus C)$       |                       |

|            |     | Input A, B, C, D               | R = B Ex-OR C, and    |

| MKG        |     | Output $P = A, Q =$            | S= B AND C When       |

| 2007       | 4X4 | $C, R = (A'D' \oplus$          | A=0 & D=0             |

| [11]       |     | B') $\oplus$ C and S =         | R = B Ex-NOR C,       |

|            |     | (A'D'⊕ B')C ⊕                  | When $A=1 \& D=0$     |

|            |     | (AB⊕D))                        |                       |

|            |     | Input A, B, C, D               |                       |

| DKG        | 4X4 | Output $P = B, Q$              | Ex-OR when A=0        |

| 2011       |     | = A'C + AD',                   |                       |

| [10]       |     | $R = (A \oplus B)(C \oplus D)$ |                       |

|            |     | ) $\oplus$ CD and S =          |                       |

|            |     | $B \oplus C \oplus D)$         |                       |

| L          |     |                                | 1                     |

# III. PROPOSED MULTIFUNCTIONAL REVERSIBLE LOGIC GATE (MRLG)

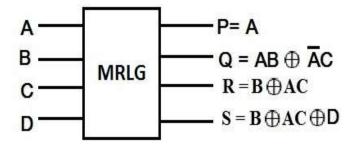

The basic proposed of this Multifunctional Reversible Logic Gate is a reversible logic gate. MRLG have a low power and small delay in design. Fig.1 was the basic approach of this proposed 4X4 reversible MRLG gate. Table 2 shows the MRLG gate truth table. In the truth table of the MRLG input pattern corresponding to a specific output pattern is determined uniquely and to maintain the one-to-one correspondence mapping between the input vector and the output vector.

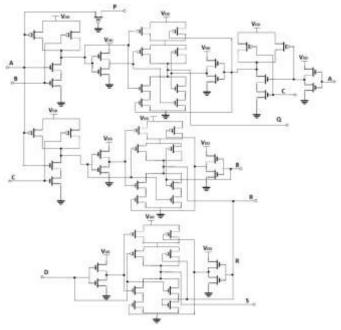

The MRLG input vector is  $I_v = (A, B, C, D)$  and there output vector is  $O_v = (P = A, Q = AB \bigoplus A^{\circ}C, R = B \bigoplus AC, S = B \bigoplus AC \bigoplus D)$ . Its CMOS realization is shown in fig. 1.

Fig. 1. Proposed MRLG reversible gate.

| Table 2: | : Proposed | MRLG | gate | truth ta | ble |

|----------|------------|------|------|----------|-----|

|----------|------------|------|------|----------|-----|

| Input | ts |   |   | Outp | nuts |   |   |

|-------|----|---|---|------|------|---|---|

| A     | B  | С | D | P    | Q    | R | S |

| 0     | 0  | 0 | 0 | 0    | 0    | 0 | 0 |

| 0     | 0  | 0 | 1 | 0    | 0    | 0 | 1 |

| 0     | 0  | 1 | 0 | 0    | 1    | 0 | 0 |

| 0     | 0  | 1 | 1 | 0    | 1    | 0 | 1 |

| 0     | 1  | 0 | 0 | 0    | 0    | 1 | 1 |

| 0     | 1  | 0 | 1 | 0    | 0    | 1 | 0 |

| 0     | 1  | 1 | 0 | 0    | 1    | 1 | 1 |

| 0     | 1  | 1 | 1 | 0    | 1    | 1 | 0 |

| 1     | 0  | 0 | 0 | 1    | 0    | 0 | 0 |

| 1     | 0  | 0 | 1 | 1    | 0    | 0 | 1 |

| 1     | 0  | 1 | 0 | 1    | 0    | 1 | 1 |

| 1     | 0  | 1 | 1 | 1    | 0    | 1 | 0 |

| 1     | 1  | 0 | 0 | 1    | 1    | 1 | 1 |

| 1     | 1  | 0 | 1 | 1    | 1    | 1 | 0 |

| 1     | 1  | 1 | 0 | 1    | 1    | 0 | 0 |

| 1     | 1  | 1 | 1 | 1    | 1    | 0 | 1 |

Fig. 2. CMOS realization of MRLG gate

#### IV. PARITY GENERATOR

Parity bit is an extra bit included with the binary information to detect errors during the transmission of binary information. In digital communication, an extra bit is added in binary message such that the total number of 1s in the message can be either odd or even according to the type of parity used. The parity generator is a combinational logic circuit that generates the parity bit(s). There are two types of parity generators.

- 1. Even parity generator

- 2. Odd parity generator

- 1. Even parity generator: The even parity generator is a combinational logic circuit that generates the parity bit such that the number of 1s in the message becomes even. The parity generator checks the

0

0

1

input's binary information and generators the parity bit 0/1 such that after the addition of parity bit, the total number of 1s in the message become even. Table 3 shows the 3-bit information with even parity.

| А | В | С | Output (P) |

|---|---|---|------------|

| 0 | 0 | 0 | 0          |

| 0 | 0 | 1 | 1          |

| 0 | 1 | 0 | 1          |

| 0 | 1 | 1 | 0          |

| 1 | 0 | 0 | 1          |

|   |   |   |            |

0

1

0

1

1

Table 3. 3-bit information with even parity

2. Odd parity generator: The odd parity generator is a combinational logic circuit that generates the parity bit such that the number of 1s in the message becomes odd. The parity generator checks the input's binary information and generators the parity bit o/1 such that after the addition of parity bit, the total number of 1s in the message become odd. Table 4 shows the 3-bit information with odd parity.

Table 4. 3-bit information with odd parity

| А | В | С | Output (P) |

|---|---|---|------------|

| 0 | 0 | 0 | 1          |

| 0 | 0 | 1 | 0          |

| 0 | 1 | 0 | 0          |

| 0 | 1 | 1 | 1          |

| 1 | 0 | 0 | 0          |

| 1 | 0 | 1 | 1          |

| 1 | 1 | 0 | 1          |

| 1 | 1 | 1 | 0          |

### V. PARITY CHECKER

At the receiving end, a combinational logical circuit is used to check the parity of the received information. It determines whether the error is included in the message or not. The combinational logic circuit used at the receiver to check the parity of received information is known as the parity checker. There are two types of parity checkers:

- 1. Even parity checker

- 2. Odd parity checker

- 1. Even parity checker: The even parity checker is a combinational logical circuit. It has n-bit inputs message and a parity error as the output. The circuit checks the parity of inputs and provides the output 0/1. For an even parity checker, if the parity of input massage is even, then the output is zero. Otherwise the output is 1. When the output is 1, it shows there is error in the message. The truth table of a 4-bit even parity checker is given in Table 5.

Table.5 even parity checker

| А    | В | С | Pin | Output<br>(P) |

|------|---|---|-----|---------------|

| <br> |   | - |     |               |

| 0    | 0 | 0 | 0   | 0             |

| 0    | 0 | 0 | 1   | 1             |

| 0    | 0 | 1 | 0   | 1             |

| 0    | 0 | 1 | 1   | 0             |

| 0    | 1 | 0 | 0   | 1             |

| 0    | 1 | 0 | 1   | 0             |

| 0    | 1 | 1 | 0   | 0             |

| 0    | 1 | 1 | 1   | 1             |

| 1    | 0 | 0 | 0   | 1             |

| 1    | 0 | 0 | 1   | 0             |

| 1    | 0 | 1 | 0   | 0             |

| 1    | 0 | 1 | 1   | 1             |

| 1    | 1 | 0 | 0   | 0             |

| 1    | 1 | 0 | 1   | 1             |

| 1    | 1 | 1 | 0   | 1             |

| 1    | 1 | 1 | 1   | 0             |

2. Odd parity checker: The odd parity checker is a combinational logical circuit. It has n-bit inputs message and a parity error as the output. The circuit checks the parity of inputs and provides the output 0/1. For an odd parity checker, if the parity of input massage is odd, then the output is zero. Otherwise the output is 1. When the output is 1, it shows there is error in the message. The truth table of a 4-bit odd parity checker is given in Table 6.

| ruble of even pullty enceker | Table 6. | even | parity | checker |

|------------------------------|----------|------|--------|---------|

|------------------------------|----------|------|--------|---------|

| А | В | С | Pin | Output<br>(P) |

|---|---|---|-----|---------------|

| 0 | 0 | 0 | 0   | 1             |

| 0 | 0 | 0 | 1   | 0             |

| 0 | 0 | 1 | 0   | 0             |

| 0 | 0 | 1 | 1   | 1             |

| 0 | 1 | 0 | 0   | 0             |

| 0 | 1 | 0 | 1   | 1             |

| 0 | 1 | 1 | 0   | 1             |

| 0 | 1 | 1 | 1   | 0             |

| 1 | 0 | 0 | 0   | 0             |

| 1 | 0 | 0 | 1   | 1             |

| 1 | 0 | 1 | 0   | 1             |

| 1 | 0 | 1 | 1   | 0             |

| 1 | 1 | 0 | 0   | 1             |

| 1 | 1 | 0 | 1   | 0             |

| 1 | 1 | 1 | 0   | 0             |

| 1 | 1 | 1 | 1   | 1             |

# VI. PROPOSED DESIGN

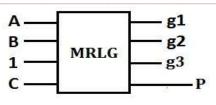

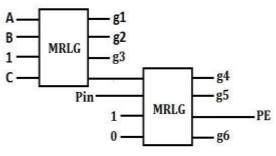

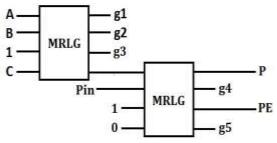

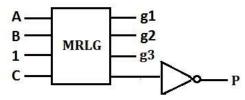

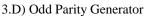

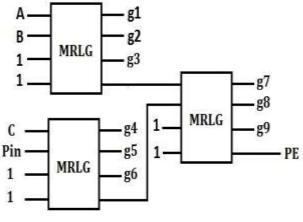

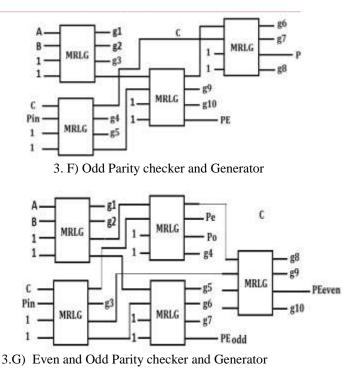

In Fig.3 shows the Design of Even and odd Parity Generator/Checker/ Parity Generator and Checker using MFRG Gate.

3.A) Even Parity Generator

3.B) Even Parity checker

3.C) Even Parity generator and checker

3.E) Odd Parity checker

Fig.3 Design of Even and odd Parity Generator/Checker/ Parity Generator and Checker using MFRG Gate

#### VII. RESULTS AND DISCUSSION

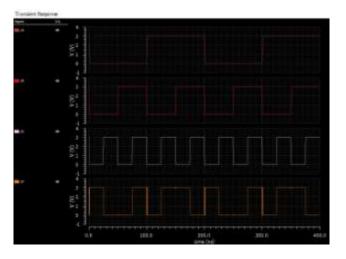

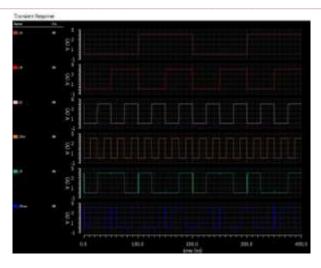

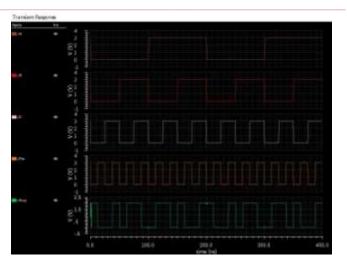

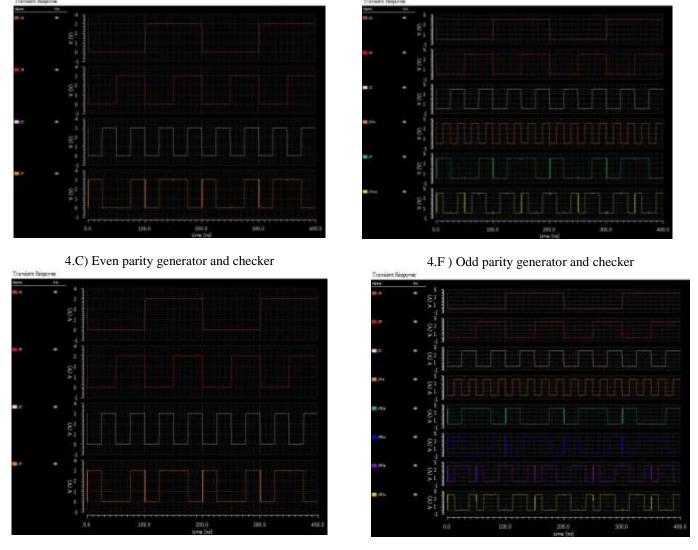

The proposed design is simulated using Cadence software. Input and Output waveform of Even and odd Parity Generator/Checker/ Parity Generator and Checker shown in fig.4. In Table 4. Shows the average power dissipation calculated for the entire input bit pattern. In comparison of different techniques, the advantage of this design is not only depends on transistor count, delay, and power but also on delay product) and PDP (power and delay product) values. The comparisons of transistors count, Power dissipation, Delay, and PDP are shown in Table 4.

4.A) Even parity generator

International Journal on Recent and Innovation Trends in Computing and Communication Volume: 4 Issue: 6

4.B) Even parity checker

4.E) Odd parity checker

4. D) Odd parity generator

4. G) Even and odd parity generator and checker

Fig.4. Input and Output waveform of Even and odd Parity Generator/Checker/ Parity Generator and Checker.

Table4. Synthesis results of Even and odd Parity Generator/Checker/ Parity Generator and Checker

|                      | MRLG gate | Garbage | Applied | Average power    | Delay (ns) | Power delay |

|----------------------|-----------|---------|---------|------------------|------------|-------------|

|                      | count     | output  | voltage | dissipation (µW) | (average)  | product     |

| Even                 |           |         | 1.5 V   | 12.74            | 0.1757     | 2.2384      |

| Parity Generator     | 1         | 3       | 2 V     | 33.67            | 0.2753     | 9.2693      |

|                      |           |         | 3 V     | 144.1            | 0.4641     | 66.876      |

|                      |           |         | 4 V     | 395.1            | 0.4368     | 172.57      |

| Even                 |           |         | 1.5 V   | 6.6              | 0.1250     | 8.325       |

| Parity Checker       | 2         | 6       | 2 V     | 136.8            | 0.4166     | 56.990      |

|                      |           |         | 3 V     | 438.5            | 0.5392     | 236.43      |

|                      |           |         | 4 V     | 1046             | 0.6122     | 640.36      |

| Even                 |           |         | 1.5 V   | 66.64            | 0.1239     | 8.256       |

| Parity Generator and | 2         | 5       | 2 V     | 139.8            | 0.3048     | 42.611      |

| Checker              |           |         | 3 V     | 438.5            | 0.3924     | 172.06      |

|                      |           |         | 4 V     | 1046             | 0.4578     | 478.06      |

| Odd                  |           |         | 1.5 V   | 13.95            | 0.2924     | 4.0789      |

| Parity Generator     | 2         | 3       | 2 V     | 36.02            | 0.3792     | 13.658      |

|                      |           |         | 3 V     | 150.8            | 0.5011     | 75.565      |

|                      |           |         | 4 V     | 411.9            | 0.6526     | 268.80      |

| Odd                  |           |         | 1.5 V   | 86.68            | 1.0711     | 92.842      |

| Parity Checker       | 3         | 9       | 2 V     | 195.3            | 0.6732     | 131.47      |

|                      |           |         | 3 V     | 611.7            | 0.4313     | 263.82      |

|                      |           |         | 4 V     | 1449             | 0.2387     | 345.87      |

| Odd                  |           |         | 1.5 V   | 111.9            | 0.7373     | 82.503      |

| Parity Generator and | 4         | 10      | 2 V     | 250.5            | 0.5472     | 137.07      |

| Checker              |           |         | 3 V     | 792.7            | 0.4612     | 365.59      |

|                      |           |         | 4 V     | 1885             | 0.4161     | 784.34      |

| Even and Odd         |           |         | 1.5 V   | 143.2            | 0.7744     | 110.80      |

| Parity Generator and | 5         | 10      | 2 V     | 333.9            | 0.4876     | 162.80      |

| Checker              |           |         | 3 V     | 1100             | 0.5951     | 654.61      |

|                      |           |         | 4 V     | 2601             | 0.4922     | 1280.2      |

#### VIII. CONCLUSION

For error free transmission in the digital communication at the source end used parity generator and at destination used parity checker. The Even and Odd Parity Generator and Checker designed using reversible logic with CMOS and pass transistor switch enables the circuit in providing better performance with low power consumption and minimum delay time with supply voltage 1.5 V to 4 V. The use of MFRL gate for parity generator and the parity checker with reduced power dissipation. The retival of the input data from the output therefore generated is created highly possible by the use of the garbage values. Hence efficient data transmission, reversible logic gates are effective than the conventional methods. The data transmission in the digital form using the reversible logic gates the loss of information is zero. The simulation is done on cadence software with transistor length 180nM and width 2µM transistor with gpdk 180 process.

#### REFERENCES

- [1] Bennett, C.H., "Logical Reversibility of Computation", IBM Journal Research and Development, 525-532. 1973.

- [2] Azad Khan, M.H, "Design of Full-Adder with Reversible Gates", International Conference on Computer and Information Technology, Dhaka, Bangladesh, pp: 515-519. 2002.

- [3] Bisdounis, L., D. Gouvetas and O. Koufopavlou, "A comparative study of CMOS circuit design styles for low-

power high-speed VLSI circuits". International Journal of Electronics, 599-613. 1998.

- [4] Chatzigeorgiou, A. and S. Nikolaidis, "Modeling the operation of pass transistor and CPL gates", International Journal Electronics, 977-1000, 2001.

- [5] Feynman, R., "Quantum Mechanical Computers", Optic News, 11-20, 1985.

- [6] Fredkin, E. and T. Toffoli, "Conservative Logic", International Journal of Theoretical Physics. 219-253. 1982.

- [7] Himanshu Thapliyal and Nagarajan Ranganathan, "A New Design of the Reversible Subtractor circuit", 11<sup>th</sup> IEEE international Conference Nanotechnology, 2011.

- [8] Himanshu Thapliyal and M.B. Srinvas, "Novel Reversible TSG gate and Its Application for Designing Components of Primitive Reversible/ Quantum ALU", ICICS 2005.

- [9] Krishnaveni, D. and M. Geetha Priya, "Design of Reversible Serial and Parallel Novel Adder/Subtractor", International Journal of Engineering Science and Technology; (IJEST) march. 2011.

- [10] Landauer, R., "Irreversibility and Heat Generation in the Computing Process", IBM Journal Research and Development, 183-191, 1961.

- [11] Majid haghparast and Keivan Navi, "A Novel Reversible Full Adder Circuit for Nanotechnology Based Systems", Journal of Applied Sciences, 3995-4000, 2007.

- [12] Maslov, D., D.M. Miller and. G.W. Dueck, "Techniques for the Synthesis of Reversible Toffoli Networks", ACM Transaction Design Automated Electronic System, 2007.

- [13] Morgenshtein, A, A. Fish and I.A. Wagner, "Gate-diffusion input (GDI): A power-efficient method for digital combinatorial circuits", IEEE Transaction on VLSI, 566-581, 2002.

- [14] Peres, A., "Reversible Logic and Quantum Computers", Physical Review, 3266-3276. 1985.

- [15] R. Landauer, —Irreversibility and heat generation in the computing process, IBM J. Res. Develop., vol. 3, pp. 183– 191, 1961.

- [16] V. V. Zhirnov, R. K. Cavin, J. A. Hutchby, and G. I. Bourianoff, —Limits to binary logic switch scaling—A Gedanken model, Proc.IEEE, vol. 91, no, 11, pp. 1934– 1939, Nov. 2003.

- [17] C. Bennett, —Logical reversibility of computations, IBM J. Res.Develop., vol. 17, no. 6, pp. 525–532, 1973.

- [18] T. Ogriro, A. Alhazov, T. Tanizawa, and K. Morita, —Universality of 2-state 3-symbol reversible logic elements—A direct simulation method of a rotary element, in Int. Workshop Natural Comput. (IWNC2009), Proc. Inform. Commun. Technol. (PICT), 2010, vol. 2, pp. 252– 250.

- [19] T. Sasao and K. Nimoshita, —Conservative logic elements and their universality, IEEE Trans. Comput., vol. C-28, no. 9, pp. 682–685, Sep.1979.

- [20] M. A. Karim and A. A. S. Awal, Optical Computing: An Introduction. New York: Wiley, 1992, chs. 7 and 9.

- [21] J. E. Rice, —Project in reversible logic, Dept. Math. Comput. Sci., Univ.Lethbridge, Lethbridge, AB, Canada, Tech. Rep. TR-CSJR1-2005, Jul.2005.

- [22] H. M. H. Babu and A. R. Chowdhury, —Design of a compact reversible binary coded decimal adder circuit, J. Syst. Archit., vol. 52, pp. 272–282,2006.

- [23] H. R. Bhagyalakshmi and M. K. Venkatesha, —Optimized reversible BCD adder using new reversible logic gates, J. Comput., vol. 2, no. 2, pp. 28–32, 2010.

- [24] D. P. Vasudevan, P. K. Lala, J. Di, and J. P. Parkerson, —Reversable-logic design with online testability, IEEE Trans. Instrum.Meas., vol. 55, no. 2, pp. 406–414, Apr. 2006.

- [25] Vinay Kumar, Divya Dhawan "An approach To Design of Reversible Synchronous Counters Using Pseudo Reed – Muller Expression", IRJETERM, vol.1 issue 8, pp. 37-48, 2015.

- [26] S.S.Gayathri, A.V.Ananthalakshmi, "Design And Implementation Of Efficient Reversible Even Parity Checker And Generator", International Conference on Science, Engineering and Management Research (ICSEMR), 2014.

- [27] Vinay Kumar, Divya Dhawan, "An Approach to Design a New Multifunctional Reversible Logic Gate (MRLG)", International Journal of Innovative Research in Computer and Communication Engineering, vol.4 issue 5 pp. 9249-9256, 2016.