# Performance Analysis of Full Adder Circuits Using CMOS 90nm Technology

Aastha Gupta B.Tech. Student M.I.T, Moradabad Moradabad, India *e-mail: 12.aastha.gupta@gmail.com*  Akshay Goyal B.Tech. Student M.I.T, Moradabad Moradabad, India *e-mail: me.akshaygoyal@gmail.com*  Pragati Gupta Assistant Professor M.I.T, Moradabad Moradabad, India email: guptapragati30@gmail.com

*Abstract*: This paper represents designing of full adder circuit using CMOS 90nm technology. In this paper three full adder circuits have been proposed using 28 and 36 transistors and comparison analysis is done between 28T(a),28T(b) and 36T on the basis of area, power and number of transistors. By comparison it shows that proposed 28T(b) full adder circuit is better than 28T(a) and 36T full adder circuits as it required power less than other two circuits.

Keywords: CMOS, Full Adder, VLSI, Transistor

\*\*\*\*

# I. INTRODUCTION

The number of components are increasing day by day in integrated circuits due to which the circuits are becoming more complex and due to the same reason the power consumption also increases with a rapid rate. Due to the increase in power consumption temperature of the circuit increases which affects the reliability of the circuit. With the increase in the power consumption the packaging and cooling cost goes up. Three major sources of power consumption in complementary metal oxide semiconductor (CMOS) circuits are:

- 1. Switching power due to output transistor.

- 2. Short circuit power due to current between  $V_{DD}$  and ground during switching.

- 3. Static power due to leakage and static currents. Static power consumption varies with the process technology.

The dynamic power of the circuit depends upon the charging and discharging of load capacitance which is given by Dynamic power =  $\alpha (V_{DD})^2 f C_1$  -----(1)

Where  $\alpha$  is the switching activity,  $V_{DD}$  is the supply voltage, f is the switching capacity and  $C_1$  is the load capacitance. As the equation suggest power consumption mainly depends upon  $V_{DD}$ . So by decreasing  $V_{DD}$  power consumption also decreases

As the need of portable device is increasing day by day ,so it is required to optimize power consumption of very large scale integration (VLSI) circuits. Power optimization is the basic constraint which is to be kept in mind designing the VLSI circuits.

An adder is a basic building block of various VLSI circuits like comparators, parity checkers, compressors etc. The performance of an adder circuit highly affects the overall capability of the circuit. Thus any improvement in an adder circuit will improve the capability of the whole system.

# II. ADDERS

Basically an adder is of two types – half adder and full adder.

A basic full adder takes three inputs and computes two outputs that are denoted as sum and carry. A full can be easily assembled with the help logic gates, transistors, CMOS technology etc.

| Table  | 1 Tr  | uth Ta | ble of a | Full   | Adder |

|--------|-------|--------|----------|--------|-------|

| 1 auto | 1. 11 | um ra  |          | i i un | ruuuu |

| Α | В | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

Adder is one of the most important component of a processor. It is used in arithmetic logic unit (ALU) and in other parts of processor. Its use is increasing in mobile electronics devices such as cellular phones, laptops etc.

The basic operation performed in most of the components is the binary addition. So it need to be performed using low power, less area and at greater speed. There is no ideal full adder cell that can satisfy the requirements of all applications, so various architectures are proposed which have their own set of advantages and disadvantages.

#### III. SIMULATION

We have designed three full adder circuits with 28 transistors, 32 transistors and 36 transistors using CMOS technology.

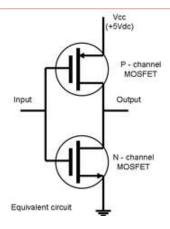

Complementary metal oxide semiconductor (CMOS) consists of p-type metal oxide semiconductor (PMOS) and n-type metal oxide semiconductor (NMOS) transistors, in which source of PMOS transistor is connected to the drain of the NMOS transistor and there base is connected together. The input to the CMOS is applied to the base of the transistors and output is taken at the junction of the drain and source. When logic 1 is applied at the input the PMOS transistor behave as open circuited and the NMOS transistor behaves as short circuited due to which the output line connected to ground through the NMOS transistor and the output switches to 0 and when logic 0 is applied PMOS is short circuited and NMOS is open circuited thus the output line is connected to the supply and switches the output to logic 1. A CMOS circuit is shown in fig. 1

Fig. 1 CMOS circuit

The same concept is used for building the adder circuits using CMOS technology.

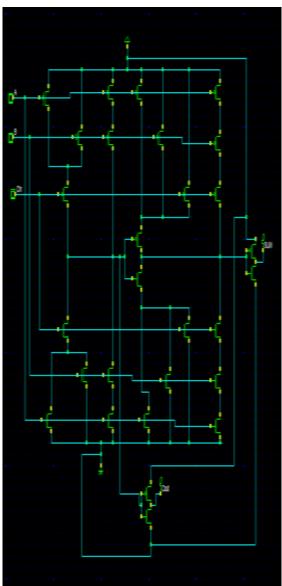

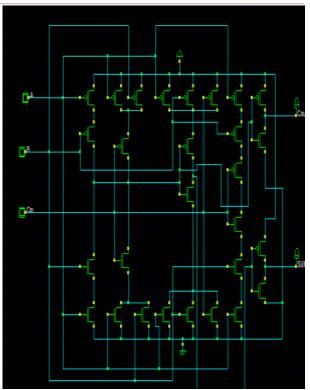

The schematic of 28T, 32T and 36T full adder circuits is shown in fig. 2, 3, 4 respectively.

Fig. 2 Schematic of 28T full adder

Fig. 3 schematic of 28T full Adder

Fig.4 Schematic of 36T Full Adder

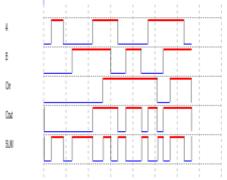

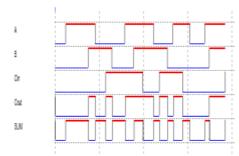

### Timing diagram of schematics are shown in figures 5,6,7.

Fig. 5 timing diagram of schematic shown in fig. 2

Fig.6 timing diagram of schematic shown in fig. 3

Fig. 7 timing diagram of schematic shown in fig. 4

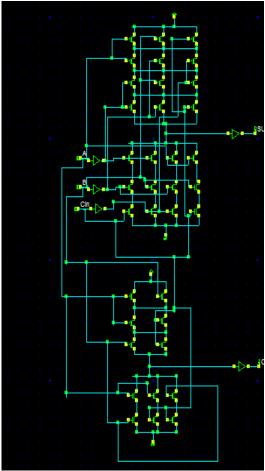

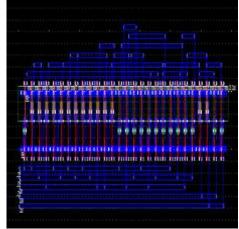

Layout of schematics of full adder circuits is shown in fig. 8, 9, 10.

Fig. 8 layout of full adder circuit shown in fig. 2

Fig. 9 layout of full adder circuit shown in fig. 3

Fig. 10 layout of full adder circuit shown in fig.4

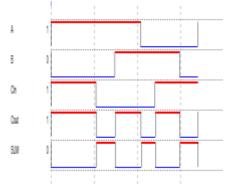

# Timing diagram of layouts are shown in fig. 11, 12

Fig. 11 timing diagram of layout of full adder shown in fig.8

Fig. 12 timing diagram of full adder layout shown in fig. 9

Fig. 13 timing diagram of full adder layout shown in fig. 1

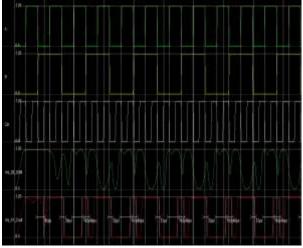

IV. COMPARISION OF RESULT

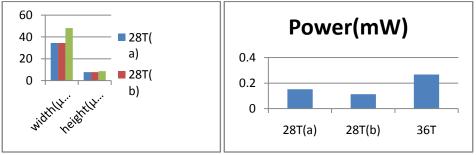

Comparison is made between three proposed full adder circuits with respect to the height, width, area and power requirement.

The height, width and area of 28T(a) and 28T(b) full adder circuit are same as the number of transistors are equal(height= $7.8\mu$ m,width= $34.5\mu$ m and area= $269.1 \ \mu$ m<sup>2</sup>) whereas the height, width and area of the 36T full adder circuit is greater than that of  $28T(height=8.6\mu$ m,width= $48.1\mu$ m and area= $413.66\mu$ m<sup>2</sup>), as shown fig. 14.

In 36T full adder circuit the power requirement is more as the number of transistor is greater than the number of transistors used in other two circuits. The power of 36T full adder circuit is 0.267 mW, for 28T(a) full adder circuit it is 0.152 mW and that of 28T(b) full adder circuit is 0.113 mW. The power requirement of 28T(a) full adder circuit is greater than that of 28T(b) full adder circuit though there are same number of transistors because the data path for both the circuits is different.

Fig. 14 Comparison of width and height,

#### V. CONCLUSION

In this paper we have presented 3 full adder circuits using CMOS 90nm technology. Simulated results has shown that the power dissipated from different full adder circuit is dependent on number of transistors used and the data path. As 28T(a) and 28T(b) has same number of transistors but the power dissipated by both of them is different. Power dissipated by 28T(a) circuit is 1.34 times greater than the 28T(b) circuit and the power dissipated by the 36T circuit is 2.36 times greater than 28T(b) circuit.

Area required by the circuit mainly depends upon the number and type of components used as the area required by the 28T(a) and 28T(b) circuit is same and the area required by 36T circuit is 1.53 times greater than the area required by the other two circuits.

#### VI. REFRENCES

- M.B. Damle, Dr. S. S Limaye and M.G Sonwani, "Comparitive Analysis of Different Types of Full Adder Circuits", IOSR Journal of Computer Engineering(IOSR-JCE), e-ISSN: 2278-0661, p- ISSN: 2278-8727 Volume 11 issue 3(May-June,2013), PP 01-09.

- [2] Manoj Kumar, Sandeep K. Arya, Sujata Pandey,"Low Power C-MOS Full Adder Design With 12 Transistors", ICITCS Volume 2, no. 6, December 2012.

- [3] R.P. Meenaakshi Sundari, Dr. R.Anita, M.K. Anand Kumar," Implementation of Low Power C-MOS Full Adders Using

Fig. 12 Comparison of power

Pass Transistors Logic", IOSR-JVSP Volume 2,Issue 5(mayjun. 2013), PP 38-43 e-ISSM: 2391-4200, ISSN no.: 2319-4197.

- [4] Ms. Namrata V. Bhadade and prof. Amol K. Boke," Design And Analyze High Speed, Power Efficient Full Adder using digital Logic Technique", ISSN 2348-9928 Doi: 01.0401/ijaict.2014.07.11 Published on 05 (12) 2014.

- [5] Umesha H.S and Dr. A.R. Aswatha," Novel Shannon Based Full Adder Architecture Low Power Neural Network Applications", ISSN:0975-9646, Umesha H.S et al,/ (IJCSIT) International Journal of Computer Science and Information technology, vol.4 (3), 2013, 423-425.

- [6] T. Divya Bharti and B.N. Shrinivasa Rao," Design and Implementation of Low-Power High-Speed Full Adder Cell Using GDI Technique", ISSN 2319-5967 ISO 9001:2008 Certified, International journal of Engineering Science and Innovative Technology (IJESIT) Volume 2, Issue 2, march 2013.

- [7] Poonam Yadav and Pankaj Kumar," Perfomance Analysis of GDI Based 1-Bit Full Adder Circuit For Low power And High Speed Applications", International Journal of VLSI and Embedded Systems-IJVES, ISSN: 2249-6556, Volume 4, Issue 3; May-June 2013.