# Review on Design of OTA Using Non-Conventional Analog Techniques

Jasbir Kaur Department of E&CE (Asst. Prof.) PEC University of Technology Chandigarh, India jasbirkaur@pec.ac.in

Deepak Goel Department of E&CE (P.G. Scholar) PEC University of Technology Chandigarh, India deepakgoelmevlsi14@pec.edu.in

Abstract — The OTA is an amplifier whose differential input voltage produces an output current. Thus, it is a voltage controlled current source. Operational transconductance amplifier is one of the most significant building-blocks in integrated continuous-time filters. A review of various non-conventional analog design techniques has been done in this paper. Several previous works have been studied and their comparison on various performance parameters is shown. This paper starts with the introduction of OTA, followed by the discussion on various OTA design techniques along with their block diagram in addition to advantages and disadvantages of these techniques. Two comparative tables are shown at the end.

Keywords—OTA, Bulk-driven MOST, Floating gate MOST, Quasi FG-MOST, LP, LV, Gain and Transconductance.

\*\*\*\*

## I. INTRODUCTION

Today operational amplifiers (OPAMPs) are widely used as basic building blocks in implementing a variety of analog applications from amplifiers, summers, integrators, and differentiators to more complicated applications such as filters and oscillators. Using OPAMPs greatly simplifies design, analysis, and implementation for analog applications.

The Operational Transconductance Amplifier (OTA) is an amplifier whose differential input voltage produces an output current. Thus, it is a voltage controlled current source. There is usually an additional input for a current to control the amplifier's transconductance. An OTA is similar to a standard operational amplifier in that it has a high impendence differential input stage and that it may be used with negative feedback. Portable electronics with low-voltage operation finds big markets. However, the threshold voltage is not reduced proportionally with the supply voltage. Thus, the threshold voltage is becoming a restraint for many analog circuits. Some special techniques are used to overcome the size of the threshold voltage, e.g. floating gate transistors, bulk-driven transistors, continuous-time filters and low threshold transistors. They suffer from several drawbacks or need special fabrication steps, which increases the cost. It is preferred to implement low-voltage circuits using a standard CMOS technology.

OTA is the most important building block in analog circuits, the amplifier faces another difficulty in the low-voltage design, providing high gain and high output swing with low power consumption. The usual way to boost the gain, cascading of transistors, is not possible in low-voltage design due to its output swing limitation.

This paper is organized as follows. In Section 2, the nonconventional techniques based on bulk CMOS technology are presented, including principle of operation and main advantages and disadvantages of each technique. Section 3 presents OTA design based on these techniques and comparison specification of various parameters related to OTA are also included. Finally, Section 4 concludes the paper.

II. NON-CONVENTIONAL TECHNIQUES BASED ON BULK CMOS TECHNOLOGY

## A. Bulk-driven MOST (BD-MOST)

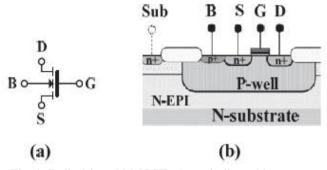

The MOS transistor is actually a four terminal device. The bulk-terminal is usually ignored and simply connected to VDD or VSS, or tied to the source terminal. However, the bulk-terminal could be used as a signal input to remove the threshold voltage requirement from the signal path, and the device which is similar to JFET transistor with depletion characteristics is obtained. The principle of the bulk-driven technique was firstly presented in [10].

Fig. 1. Bulk-driven N-MOST: a) symbolic and b) crosssection.

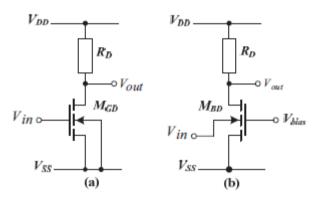

The operation of the Bulk-driven MOST is conformable to a JFET. To enable bulk driving, one must first bias the gate to form a conduction channel inversion layer by connecting the gate terminal to a fixed voltage that is sufficient to form an inversion layer (e.g.,  $V_{\text{bias}} > V_T$  for the NMOS). By applying a

potential difference between the drain and source, this inversion layer will act very much like a conduction channel of JFET (see Fig. 2). Since the bulk voltage affects the thickness of the depletion region associated with the inversion layer (conduction channel), the drain current can be modulated by varying the bulk voltage through the body effect of the MOST.

Fig. 2. Common source amplifier based on a) gate-driven NMOST and b) bulk-driven NMOST.

Many advantages can be obtained by using the BDMOST in analog circuit design:

- The threshold voltage requirements are removed.

- A wider input common mode range under negative, zero and slightly positive input voltage (BDNMOST). Suitable for rail-to-rail applications.

- Can be modeled using the conventional MOS transistor.

- Can process DC and AC over the FG-MOST and QFG-MOST which process AC only, as it is discussed below.

In the other hand some drawbacks come with the BDMOST technique:

- Smaller transconductance and transition frequency in comparison with GD-MOST.

- Higher input referred noise than conventional GDMOST.

- In the applications where both PMOS and NMOS are needed to use as bulk-driven transistors, twin well process is needed, that can be achieved at the expense of higher cost process and larger chip area.

- Analog circuits with tight matching between BDMOSTs are difficult to be fabricated, since BDMOSTs are fabricated in differential wells to have isolated bulk.

- Latch-up maybe occurs.

#### B. Floating-gate MOST (FG-MOST)

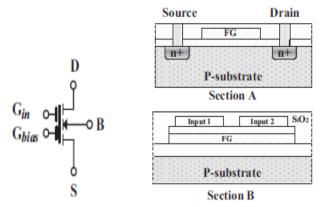

The first well-known application of the FG-MOST was to store data in digital EEPROMs, EPROMs and flash memories [3]. The symbol of the FG-MOST with two control gates is shown in Fig. 3(a) and the cross-sectional views in (b). The gate is fabricated using the poly1 layer in FG-MOST and is left floating, since it is surrounded by insulator layers (SiO2). Two or more control gates ( $G_{in}$ ,  $G_{bias}$ ) are formed using the second poly layer and capacitively coupled to the floating gate.

Fig.3. Two-input floating gate NMOST: a) symbolic, b) crosssectional views.

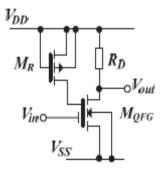

To demonstrate the operation principle of the FGMOST, a common source amplifier based on the FGNMOST with two control gates is shown in Fig. 4. As it is clarified in Fig. 4, a proper bias voltage  $V_{\text{bias}}$  is applied at one of the control gates  $G_{\text{bias}}$  through large value capacitance, which is able to shift the threshold voltage. The input signal is applied at the second control gate  $G_{\text{in}}$  and modulates the inversion layer, thus controls the drain current.

Fig. 4. Floating-gate MOST: common source amplifier

Many advantages can be obtained using FG-MOST technique, such as:

- Possibility of multi-input terminals.

- Threshold voltage can be shifted according to the application's requirements.

- Can be used in ultra-low power ultra-low voltage applications.

- Can be fabricated in any MOS technology, although for better performance double poly technology is recommended.

There are some disadvantages coming with this technique:

- Larger area is occupied on the chip over the conventional GD-MOST, since the bias and input capacitances have relatively high values [18, 9].

- Uncertain amount of cumulative initial charge in the floating gate.

- Reduction of the effective transconductance and output impedance in comparison with the conventional GD-MOST.

- Smaller transition frequency, hence smaller bandwidth than the GD-MOST.

- Shortage of simulation models, as well the simulators don't accept the floating node.

## C. Quasi-Floating-gate MOST (QFG-MOST)

Many recent publications describe interesting and important implementations of the QFG-MOST in LV LP applications. The QFGMOST appears as a developed version of the FG-MOST to overcome some of its drawbacks. It has been discussed previously that the relatively high bias capacitance value of the FG-MOST leads to an increase in the silicon area and a reduction of the effective transconductance and GBW. Besides, FG-MOST has uncertain residual charge trapped at the floating gate. Using the QFG-MOST, the occupied chip area is minimized and the initial charge is no longer an issue [12]. Fig. 5 shows the symbolic of the QFG-MOST. QFG-MOST may have a multiple input terminals like the FG-MOST. Besides, it can be fabricated in any MOS technology, nevertheless, the double poly technology is recommended to obtain better results.

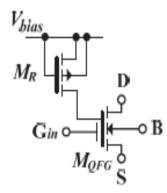

Fig. 5. One-input Quasi-Floating gate NMOST

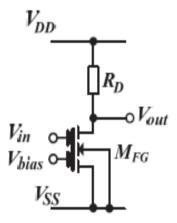

Fig. 6 shows the common source amplifier based on QFG-MOST. The operation principle of the QFG-MOST is similar to the FG-MOST.

The QFG-MOST has almost the same advantages as the FG-MOST, besides:

- There is no initial charge trapped at the floating gate.

- Smaller occupied chip area than FG-MOST.

• The effective transconductance and transition frequency are relatively higher than the effective transconductance and transition frequency of FG-MOST, but they are still smaller than the transconductance and transition frequency of the conventional GDMOST.

Fig. 6. Quasi-Floating gate MOST: common source amplifier with single input terminal

Some drawbacks come with QFG-MOST techniques, such as:

- Greater effective output conductance than the effective output conductance of FG-MOST and the output conductance of GD-MOST.

- Floating gate voltage must not exceed the cut-in voltage of the p-n junction of the diode connected transistor M<sub>R</sub>.

#### III. OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA)

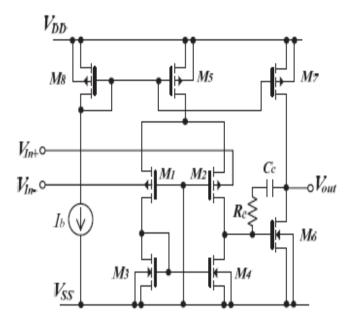

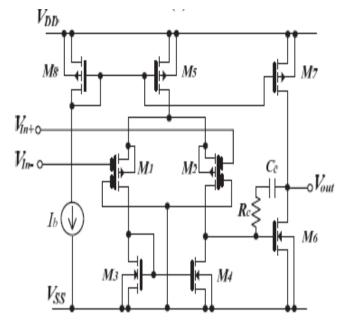

To illustrate the implementation principle of non-conventional techniques in analog circuit design, these techniques are used in this section to build three LV LP Miller OTAs with the same voltage supply, power consumption and transistors aspect ratios. However, the differential pair transistors are different i.e. BD-PMOST, FG-PMOST and QFG-PMOST to clarify the performances of each technique. A comparison study between the most important characteristics of the three OTAs is presented as well [20].

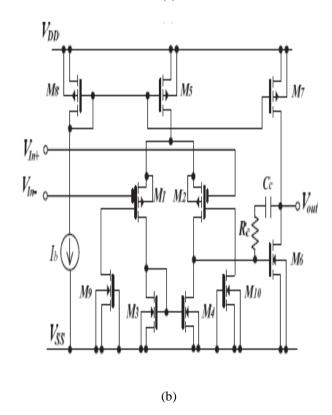

Since operational transconductance amplifier is an important block used in many applications and structures. Actually, Miller OTA composite of cascade of two stages, first stage is a differential amplifier with PMOS input transistors (M1, M2), see Fig. 7, and the current mirror (M3, M4) acting as an active load. The second stage is a simple common source amplifier with transistor M6 acting as driver and M7 as an active load, its output connected to its input through the compensation capacitor Cc and resistor Rc, this capacitor acting as Miller capacitance, without it the circuit is not stable [5]. The bias current  $I_b$  and transistors M8, M5, M7 provide the bias currents needed for the first and second stage of OTAs. Utilizing the non-conventional techniques as input devices of the differential amplifier at the first stage, LV LP OTAs can be achieved.

Three Miller OTAs based on non-conventional techniques are depicted in Fig. 7, bulk-driven OTA in (a), floating-gate OTA 246

in (b) and quasi-floating-gate OTA in (c). In the bulk-driven OTA, the gate terminals of BD-PMOSTs (M1, M2) are tied to designed by implementation of two FG-PMOSTs (M1, M2) with two control gates. The bias voltage Vss is applied at one of control gates of each transistor. The input signals are applied at the second control gate as it is shown in Fig. 7(b). The third OTA has two QFG-PMOSTs with single input

Vss to provide sufficient bias voltage, the input signals are applied at bulk terminals Fig. 7(a). Floating-gate OTA is terminal as input devices; the floating gates of the QFG-PMOSTs are tied through reversed-biased diode connected transistors (M9 and M10) to Vss, while input signals applied to the input terminals as shown in Fig. 7(c).

(c) Fig. 7. LV LP Miller OTA based on: a) BD-MOST, b) FGMOST and c) QFG-MOST.

#### IV. CONCLUSION

In this review, the principle of non-conventional techniques for LV LP analog circuit design has been discussed. Furthermore, their advantages are listed, thus one can use appropriate technique for intended analog circuit design. In spite of that the non-conventional techniques offer design simplicity with high performance, low voltage and low power operation, some drawbacks come with these techniques, mainly, the reduction of the gain, bandwidth and transconductance (in FG-MOST and QFG-MOST case).

Finally various types of OTA design using non-conventional techniques are focused upon. Table 1 shows performance comparison between various parameters related to OTA. Some authors have worked on reducing the supply voltage and improving gain of OTA [21],[15],[6],[2]. It is observed that the highest gain is achieved by BD MOST design. The work of some authors is directed towards improving linearity and power dissipation of OTA [4],[13],[6],[15]. From the table 2, it is observed that the highest gain is achieved by Quasi FG-MOST design under certain measurement condition [20]. Thus the non-conventional techniques are utilized successfully in LV LP applications.

(a)

| Parameters             | Bulk-driven OTA |      |      |      |      |        |      | Gate-<br>driven | Quasi-<br>floating gate |

|------------------------|-----------------|------|------|------|------|--------|------|-----------------|-------------------------|

| rarameters             | [11]            | [13] | [14] | [15] | [21] | [6]    | [2]  | OTA [2]         | OTA[4]                  |

| Supply voltage         | 1               | 1    | 0.8  | 0.9  | 1.3  | 0.6    | 0.5  | 0.5             | <u>+</u> 0.3            |

| Power dissipation (uW) | 300             | 5    | -    | 0.5  | 460  | .55    | 100  | 100             | 57                      |

| Open loop DC gain (dB) | 49              | 70   | 53   | 70   | 84   | 73.5   | 48   | 72              | 40                      |

| Unity-gain BW (MHz)    | 1.3             | 0.2  | 1.3  | 6KHz | 1.3  | 0.013  | 2.4  | 15              | 1.2                     |

| Load capacitance (pf)  | 22              | 7    | 20   | 12   | -    | 15     | 20   | 20              | 10                      |

| Phase margin (deg.)    | -               | -    | -    | -    | -    | 54.1   | 45   | 60              | 77                      |

| Slew Rate (V/us)       | -               | -    | -    | -    | -    | 0.0147 | 2.92 | 2.7             | 0.8                     |

| Technology (um)        | 2               | 0.35 | 0.5  | 2.5  | 0.7  | 0.35   | 0.18 | 0.18            | 0.18                    |

## Table 1. Comparison of main specifications of the OTA work

**Table 2.** Comparison of main specifications of three LV LP Miller OTAs.

| Characteristics                                                                                                 | Bulk-driven OTA [20] | Floating-gate OTA [20] | Quasi-floating-gate OTA [20] |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------|------------------------|------------------------------|--|--|--|--|

| Power consumption [uW]                                                                                          | 23.5                 | 23.5                   | 23.5                         |  |  |  |  |

| Phase margin [deg]                                                                                              | 93                   | 87                     | 84                           |  |  |  |  |

| Offset voltage [mV]                                                                                             | 0.7                  | 0.44                   | 0.92                         |  |  |  |  |

| Dynamic range [mV]                                                                                              | -100 to 400          | -300 to 395            | -237 to 400                  |  |  |  |  |

| CMRR [dB]                                                                                                       | 42.4                 | 50.29                  | 49.8                         |  |  |  |  |

| GBW [MHz]                                                                                                       | 1.5                  | 3.84                   | 7.47                         |  |  |  |  |

| Gain [dB]                                                                                                       | 24                   | 35.94                  | 41.50                        |  |  |  |  |

| Slew rate [V/us]                                                                                                | 0.28                 | 0.54                   | 0.76                         |  |  |  |  |

| Measurement conditions: $V_{dd}$ = 0.4V, $V_{ss}$ =-0.4V, $Cc = C_L$ =1pF, $C_{in} = C_{bias}$ =1pF, $I_b$ =6uA |                      |                        |                              |  |  |  |  |

#### REFERENCES

- [1] The International Technology Roadmap for Semiconductors (2004 Edition) [Online]. Available: http://public.itrs.net

- [2] S. Chatterjee, Y. Tsividis, and P. Kinget, "A 0.5-V bulk-input fully differential operational transconductance amplifier," Proc. 30th ESSCIRC, pp. 147–150, Sep. 2004.

- [3] F. Khateb, N. Khatib, D. Kubánek, Novel ultralowpower class AB CCII+ based on floating-gate folded cascade OTA. Circuits, Systems, and Signal Processing Journal, 2012, vol. 31, no. 2, p. 447 - 464.

- [4] Farzan Rezaei, Seyed Javad Azhari, Ultra low-voltage, rail-to-rail input/output stage Operational Transconductance Amplifier (OTA) with high linearity and its application in a Gm-C filter, in: Proceedings of the 11th IEEE International symposium on Quality Electronic Design (ISQED), March 2010, pp. 231–236.

- [5] F. Maloberti, "Analog Design for CMOS VLSI Systems", Dordrecht: Kluwer Academic Publishers, 2001.

- [6] Lui's H.C.Ferreira, Tales Cleber Pimenta, Robson L.Moreno, Anultra-low- voltage ultra-low-power CMOS miller OTA with rail-to-rail input/output swing, IEEE Transactions on Circuits and Systems II 54(10) (2007) 843–847.

- [7] S. Narendra, J. Tschanz, J. Hofsheier, B. Bloechel, S. Vangal, Y. Hoskote, S. Tang, D. Somasekhar, A. Keshavarzi, V. Erraguntla, G. Dermer, N. Borkar, S. Borkar, and V. De, "Ultra-low voltage circuits and processor in 180 nm to 90 nm technologies with a swapped-body biasing technique," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, Feb. 2004, pp. 156–157.

- [8] J. W. Tschanz, J. T. Kao, S. Narendra, R. Nair, D. Antoniadis, and A. P. Chandrakasan, "Adaptive body bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1396–1402, Nov. 2002.

- [9] F. Khateb, N. Khatib, D. Kubánek, "Low-voltage ultra low- power current conveyor based on quasi-floating gate transistors", Radioengineering, 2012, vol. 21, no. 2, p. 725 - 735.

- [10] A. Guzinski, M. Bialko, and J. Matheau, "Body driven differential amplifier for application in continuous-time active-C filter," in Proc. ECCD, 1987, pp. 315–319.

- [11] B. Blalock, P. Allen, and G. Rincon-Mora, "Designing 1-V op-amps using standard digital CMOS technology," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 45, no. 7, pp. 769–780, Jul. 1998.

- [12] RODRIGUEZ-VILLEGAS, E. Low Power and Low Voltage Circuit Design with the FGMOS Transistor. London: Institution of Engineering and Technology, 2006.

- [13] K. Lasanen, E. Raisanen-Ruotsalainen, and J. Kostamovaara, "A 1-V 5 W CMOS-opamp with bulkdriven input transistors," in 43rd IEEE Midwest Symp. Circuits and Systems, 2000, pp. 1038–1041.

- T. Lehmann and M. Cassia, "1-V power supply CMOS cascode amplifier," IEEE J. Solid-State Circuits, vol. 36, no. 7, pp. 1082–1086, Jul. 2001.

- [15] T. Stockstad and H. Yoshizawa, "A 0.9-V 0.5- A railto-rail CMOS operational amplifier," IEEE J. Solid-State Circuits, vol. 37, pp. 286–292, 2002.

- [16] S. Karthikeyan, S. Mortezapour, A. Tammineedi, and E. Lee, "Lowvoltage analog circuit design based on biased inverting opamp configuration," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 47, no. 3, pp. 176–184, Mar. 2000.

- [17] K. Bult, "Analog design in deep sub-micron CMOS," in Proc. ESSCIRC, Sep. 2000, pp. 11–17.

- [18] ALGUETA MIGUEL, J. M., DE LA CRUZ BLAS, C.A., LOPEZMARTN, A. J. CMOS triode transconductor based on quasifloating- gate transistors. Electronics Letters, 2010, vol. 46, no. 17, pp. 1190 -1191.

- [19] A. Baschirotto, F. Rezzi, and R. Castello, "Low-voltage balanced transconductor with high input common-mode rejection," Electron. Lett., vol. 30, no. 20, pp. 1669– 1671, Sep. 1994.

- [20] Fabian KHATEB, Salma BAY ABO DABBOUS, Spyridon VLASSIS, "A Survey of Non-conventional Techniques for Low-voltage Low-power Analog Circuit Design" RADIOENGINEERING, VOL. 22, NO. 2, JUNE 2013,pp. 415-427.

- [21] T. Kobayashi and T. Sakurai, "Self-adjusting thresholdvoltage scheme (SATS) for low-voltage high-speed operation," in Proc. IEEE Custom Integrated Circuits Conf., May 1994, pp. 271–274.

- [22] J. T. Kao, M. Miyazaki, and A. P. Chandrakasan, "A 175-mV multiply- accumulate unit using an adaptive supply voltage and body bias architecture," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1545–1554, Nov. 2002.

- [23] G. Ferri and W. Sansen, "A 1.3V op/amp in standard 0.7 um CMOS with constant g and rail-to-rail input and output stages," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, vol. 478, 1996, pp. 382–383.