# Simulation of a High Voltage Gain dc-dc Converter Integrating with Coupled Inductor and Two Voltage Multiplier Cells

P Madhuri<sup>1</sup>, K.Venkata Reddy<sup>2</sup>, A.Srinivasa Reddy<sup>3</sup> madhuripasupuleti4@gmail.com kattavenkatareddy@hotmail.com srinu525@live.com

*Abstract:* In this paper, a high voltage gain dc-dc converter is presented for renewable energy applications. This paper develops step up converter which consists of two voltage multiplier cells with coupled inductor in order to achieve the multiple voltage requirements with high voltage gain. And also two capacitances are provided for charging when the device is under turned-off condition, by utilizing the stored energy levels in the coupled inductor which can enhances the voltage transfer capability levels of the system The voltage imbalance levels are compensated at main power switch. The implemented model operates with low resistance  $R_{DS(ON)}$  at main power switch which can reduce the switching losses. The developed simulink models are tested and verified within the MATLAB/SIMULINK with multiple output functions with high voltage gains.

Keywords: - dc/dc converters, Coupled inductor, voltage multiplier.

## I. INTRODUCTION

\*\*\*\*

The non-conventional sources are available free of cost, are pollution-free and inexhaustible Man has used these sources for many centuries in propelling ships, driving windmills for grinding corn and pumping water, etc. Because of the poor technologies then existing, the cost of harnessing energy from these sources was quite high. Also because of uncertainty of period of availability and the difficulty of transporting this form of energy, to the place of its use are some of the factors which came in the way of its adoption or development. The use of fossil fuels replaced totally the non-conventional methods because of inherent advantages of transportation and certainty of availability; however these have polluted the atmosphere to a great extent.

People began to realize that the fossil fuels are not going to last longer. But unfortunately, coal energy pose serious environmental problems. The combustion of coal may upset the planet's heat balance. As a result of these problems, it was decided by almost all the countries to develop and harness the non-conventional sources of energy, even though they are relatively costlier as compared to fossil-fuel sources. It is hoped that with advancement in technology and more research in the field of development of non-conventional sources of energy, these sources prove to be cost-effective as well. The future of wind, solar, tidal and other energy sources is bright and these will play an important role in the world energy scenario.

Nowadays, photovoltaic (PV) [1] energy appears quite attractive for electricity generation because of its noiseless, pollution-free, scale flexibility, and little maintenance. Due to cost reduction of PV modules and government incentives, grid-connected photovoltaic power systems are getting more and more attention in the last decade. However, the output voltage of PV arrays is relatively low. The generated power of the PV arrays is decreased greatly because of the PV power generation dependence on sun irradiation level, ambient temperature, and unpredictable shadows.

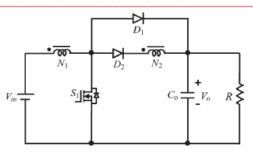

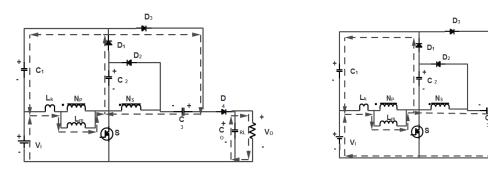

Fig.1 Conventional high step up dc-dc converter

Conventionally, the PV arrays are series connected [2-3] to provide high voltage for grid inverters. The generated power of the PV arrays is decreased greatly because of partial shield Based on this reason; the parallel-connected PV arrays are more efficient than series connected. However, the output voltage in the parallel connected PV arrays is low. The converters need to raise low DC voltage (12V) to high DC voltage (380V) [4] for the PV inverter. Thus, the research on the high step-up DC–DC converters was developed. Theoretically, conventional boost converters can achieve high-voltage gain with an extremely high duty ratio. However, the performance of the system will be deteriorated with a high duty cycle due to several problems.

A conventional high step-up dc–dc converter with a coupled inductor technique [5] is shown in Fig.1. The structure of this converter is very simple, and the leakage inductor energy of the coupled inductor can be recycled to the output. Coupled-inductor based converters can achieve high step-up voltage gain. However, the voltage stresses on switch  $S_1$  and diode  $D_1$ , which are equal to the output voltage, are high and deteriorates the efficiency. To overcome this, coupled inductor based converter with an active clamp circuit are introduced. Some transformer-based [6] converters like push–pull, or flyback converters can achieve high step-up voltage gain by adjusting the turn ratio of the transformer However; the leakage inductor of the transformer will cause serious problems. Transformer less [7] dc–dc high step-up converter eliminates the drawbacks of transformer based converters.

Some literatures like transformer less with coupled inductor, switched capacitors [8-10], voltage double techniques [11-13] have been widely used. However these techniques have some drawbacks as high charging currents and conduction losses. High step-up converters with two switches, single switch are introduced in some literatures.

This paper presents a high voltage gain dc-dc converter for renewable energy applications. The suggested structure consists of two voltage multiplier cells with coupled inductors in order to achieve the multiple voltage requirements with high voltage gain. And also two capacitances are provided for charging when the device is under turned-off condition; by utilizing the stored energy level in the coupled inductor which can enhances the voltage transfer capability levels of the system. The voltage imbalance levels are compensated at main power switch. The implemented model operated with low resistance  $R_{DS(ON)}$  at main power switch which can reduce the switching losses. This developed step-up converter step up the low voltage (40V) to high voltage (600V) with high voltage gain.

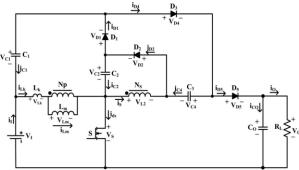

Fig 2Circuit configuration of the high-step-up converter

# II. OPERATING PRINCIPLE OF THE CONVERTER

The system design of the proposed framework is appeared in Fig. 2. The proposed system connection has a dc voltage (VI), dynamic force switch (S), coupled inductor, four diodes, then four capacitors Then Capacitor C1 then diode D1 is filling in as braces system exclusively.

The capacitor C3 is included as the capacitor of the long voltage multiplier cell. So that capacitor C2 then diode D2 is the circuit components of the voltage multiplier which upsurge the voltage of clipping capacitor C1. The coupled inductor is open as a perfect transformer with a turn proportion N (NP/NS), a polarizing inductor Lm and spillage inductor Lk.

Keeping in mind the end goal to diminish the circuit investigation of the converter, some preparing are watchful as takes after:

1) All Capacitors are suitably expansive; in this way VC1, VC2, VC3 then VO are reserved to be steady finished one exchanging period;

2) All instruments are perfect however the spillage inductance of the coupled inductor is unhurried. Providing for the previously stated presumptions, the constant conduction mode (CCM) operation of the proposed converter incorporates five interims in one exchanging period.

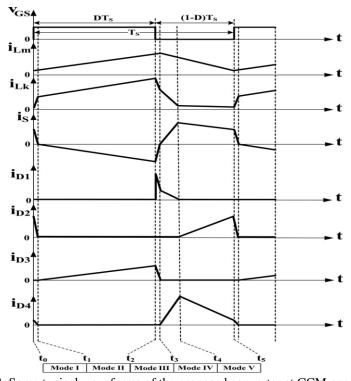

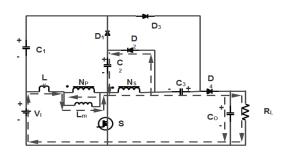

According to the aforementioned assumptions, the continuous conduction mode (CCM) operation of the proposed converter includes five intervals in one switching period. Some typical waveforms under CCM operation are illustrated in Fig. 3 and the current-flow path of the proposed converter for each stage is depicted in Fig. 4

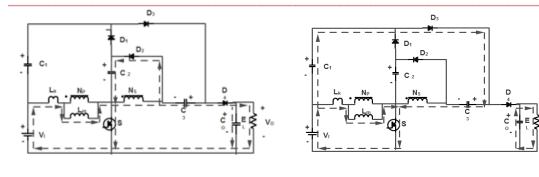

The operating stages are explained as follows:

1) Stage I [t0 < t < t1 see Fig. 4(a)]: In this stage, switch S is turned ON. In like manner, diodes D2 and D4 are turned ON and diodes D1 and D3 are killed. The dc source (VI) polarizes Lm through S.

2) Stage II [t1 < t < t2 see Fig. 4(b)]: In this stage, switch S and diode D3 are turned ON and diodes D1, D2, and D4 are killed. The dc source VI polarizes Lm through switch S. In this way, the current of the spillage inductor Lk and charging inductor Lm increment straightly

Fig. 3: Some typical waveforms of the proposed converter at CCM operation

International Journal on Recent and Innovation Trends in Computing and Communication Volume: 4 Issue: 3

(b)

(e)

Fig 4:.Current path of operating modes during one switching period at CCM operation. (a) *Stage* I. (b) *Stage* II. (c) *Stage* III. (d) *Stage* IV. (e) *Stage* V.

3) Stage III [ $t^2 < t < t^3$  see Fig. 4(c)]: In this stage, switch S is killed. Diodes D1 and D3 are turned ON and diodes D2 and D4 are killed. The clasp capacitor C1 is charged by the put away vitality in capacitor C2 and the energies of spillage inductor Lk and polarizing inductor Lm.

4) Stage IV [t3 < t < t4 see Fig. 4(d)]: In this stage, S is killed. Diodes D1 and D4 are turned ON and diodes D2 and D3 are killed.

5) Stage V [t4 < t < t5 see Fig. 4(e)]: In this stage, S is killed. Diodes D2 and D4 are turned ON and diodes D1 and D3 are killed. The streams of the spillage inductor Lk and charging inductor Lm lessening directly.

# III.STEADY-STATE ANALYSIS OF THE PROPOSED CONVERTER

### A. CCM Operation

To simplify the steady-state analysis, only stages II, IV, and V are considered since these stages are sufficiently large in comparison with stages I and III.

During stage II,  $L_k$  and  $L_m$  are charged by dc source  $V_I$ . Therefore, the following equation can be written according to Fig. 4(b).

$$V_{I} = kV \tag{1}$$

Where k is the coupling coefficient of coupled inductor, which equals to  $L_m/(L_m + L_k)$ . Capacitor  $C_3$  is charged by clamp capacitor  $C_1$ , dc source( $V_I$ ), and the secondary-side of the coupled inductor. The voltage across the capacitor  $C_3$  can be expressed by

$$V_{C3} = V_{C1} + (kn+1)V$$

(2)

Where *n* is the turn ratio of coupled inductor, n=Ns/Np. As shown in Fig. 2(d), during stage IV, *Lk* and *Lm* demagnetize to the clamp capacitor *C*1 with the help of capacitor *C*2. Hence, the voltage across *Lm* can be written as

$$V_{L_m} = k \left( V_{C2} - V_{C1} \right)$$

(3)

Also, the output voltage can be formulated based on Fig. 2(d)

$$V_{o} = V_{1} + V_{C3} + (kn+1)(V_{C1} - V_{C2})$$

(4)

According to Fig. 2(e), in the time interval of stage V, the voltage across L<sub>m</sub> can be expressed by

$$V_{L_m} = -\frac{V_{C2}}{n} \tag{5}$$

Moreover, the output voltage is derived as

$$V_{O} = V_{1} + V_{C3} + \left(\frac{1}{kn} + 1\right) V_{C2}$$

(6)

According to aforementioned assumption, the output capacitor voltage is constant during one switching period. Therefore, by equalization of (4) and (6), the following equation is derived as:

$$V_{C1} = \frac{(kn+1)}{kn} V_{C2}$$

(7)

Using the volt-second balance principle on  $L_m$  and equations (1), (3), (5) and (7), the voltages across capacitors  $C_1$  and  $C_2$  is obtained as

$$V_{C1} = \frac{(kn+1)D}{(1-D)}V_1$$

(8)

$$V_{C2} = \frac{knD}{1-D}V_1 \tag{9}$$

Substituting (8) into (2), yields

$$V_{C3} = \frac{kn+1}{1-D}V_1$$

(10)

Substituting (9) and (10) into (6), the voltage gain is achieved as

$$M_{CCM} = \frac{2 + kn + knD}{1 - D} V_1 \tag{11}$$

When k equals 1, the ideal voltage gain is obtained as

$$M_{CCM} = \frac{2+n+nD}{1-D}V_1 \tag{12}$$

Based on the description of the operating modes, the voltage Stresses on the active switch S and diodes  $D_1$ ,  $D_2$ ,  $D_3$ , and  $D_4$  are expressed as

$$V_{DS} = V_{D1} = \frac{1}{1 - D} V_1 = \frac{1}{2 + 2n} (V_0 + nV_1)$$

(13)

$$V_{D3} = V_{D4} = \frac{1+n}{1-D}V_1 = \frac{1}{2}(V_O + nV_1)$$

(14)

$$V_{D2} = \frac{n}{1 - D} V_1 = \frac{n}{2 + 2n} \left( V_0 + n V_1 \right)$$

(15)

According to Fig. 4, the average value of input current can be achieved as follows when switch is turned on/off:

$$I_{in(on)} = (n+1)I_{D3} + I_{L_m}$$

(16)

$$I_{in(off)} = I_O \tag{17}$$

From (16) and (17), the average current value of magnetizing inductor can be obtained as follows:

$$I_{L_m} = \frac{\left(M_{CCM} - 2 - n\right)I_O}{D} = \frac{2(n+1)}{1 - D}I_O$$

(18)

The integral form of the current equation of magnetizing inductor can be written as

$$i_{L_m}(t) = i_{L_m}(t_o) + \frac{1}{L_m} \int_{i0}^{t} v_{L_m}(\tau) d\tau$$

(19)

Substituting (16) into (19), and for k = 1, t = DT, and  $t_0 = 0$ , yields

....

$$\Delta i_{L_m} = \frac{DV_{in}}{L_m f_s} \tag{20}$$

According to Fig. 3 and applying the ampere–second balance principle on capacitors, the average current values of diodes are equal to  $I_0$ . Therefore, the peak values of diodes  $D_3$  and  $D_4$  can be obtained as

$$i_{D3(peak)} = \frac{2I_o}{D} \tag{21}$$

$$i_{D4(peak)} = \frac{2I_o}{1-D} \tag{22}$$

$$i_{s(peak)} = i_{D1(peak)} = \left(\frac{2+n+nD}{D(1-D)}\right) I_O + \frac{DV_{in}}{L_m f_s}$$

(23)

Neglecting modes I and III, the time interval of modes IV and V are given as

$$d_4 = \frac{2I_o}{i_{D1(peak)}} = \frac{1-D}{n+1}$$

(24)

$$1 - D - d_1 = d_5 \tag{25}$$

From equation (25), the peak value of diode  $D_2$  is obtained as

$$i_{D2(peak)} = \frac{2(n+1)I_o}{n(1-D)}$$

(26)

### CAPACITORS AND INDUCTANCE CALCULATION:

The minimum value of the magnetizing inductance can be calculated as follows:

$$L_{m\min} = \frac{D(1-D)^2 R_L}{8f_s \left[ n^2 (1+D) + n(3+D) + 1 \right]}$$

(27)

According to, the magnetizing inductance should be more than 148  $\mu$ H. A coupled inductor with the magnetizing inductance of the 300  $\mu$ H is employed to guarantee the CCM operation of the implemented converter.

In order to design the size of the capacitors, it should be followed four conditions regarding the ripple in the output voltage. The conditions are ripple of the capacitor current, ripple due to the equivalent series resistance (ESR) of the capacitor, ripple due to the equivalent series inductance (ESL) of the capacitor, and the hold-up time requirement for load step response which the last condition is for the output capacitor. First, the design is started by considering only the first condition which ESRs and ESLs are not known before selecting the capacitor. Then, ESRs and ESLs are obtained from the capacitors' datasheets. The total output voltage ripple is checked to make sure that it is below the admissible value by considering ESRs and ESLs. In addition, the ripple of the capacitor currents are calculated and compared to the value mentioned in datasheet to make sure that the selected capacitors are in consistent with the practical conditions. In order to calculate the voltage ripple of a capacitor ESR and ESL, the following equation is used:

$$V_C(t) = V_C(t_0) + \frac{1}{C} \int_{t_0}^t i(t) dt$$

<sup>(28)</sup>

Since the average currents through capacitors  $C_1$ ,  $C_2$ ,  $C_3$  and  $C_0$  are zero under steady state, the average current values of diodes are equal to  $I_0$ . Therefore, according to the CCM operation modes shown in Fig. 3 and (31), the voltage ripple of all capacitors can be given as follows:

$$\Delta V_{C1,2,3} = \frac{V_O}{R_L C}, \Delta V_{CO} = \frac{DV_O}{R_L C_O f_s}$$

(29)

The peak-to-peak voltage across ESR of a capacitor can also be considered as follows:

$$\Delta V_C^{ESR} = r_C \Delta I_C \tag{30}$$

According to equations (21)–(23), (26) and (30), the peak-to peak voltages across the capacitors ESR are expressed below

$$\Delta V_{C1}^{ESR} = r_{C1} \left[ \left( \frac{4 + n + (n - 2)D}{D(1 - D)} \right) I_o + \frac{DV_{in}}{L_m f_s} \right] \\ \Delta V_{C2}^{ESR} = r_{C2} \left[ \left( \frac{2 + n + nD + \frac{2D(n + 1)}{n}}{D(1 - D)} \right) I_o + \frac{DV_{in}}{L_m f_s} \right] \\ \Delta V_{C3}^{ESR} = r_{C3} \frac{2I_o}{D(1 - D)} \\ \Delta V_{C0}^{ESR} = r_{C0} \frac{2I_o}{1 - D}$$

(31)

The peak-to-peak voltage across ESL of a capacitor can also be considered as follows:

$$\Delta V_C^{ESL} = L_C \frac{di_C}{dt} \tag{32}$$

According to equations (21)-(23), (26) and (32), the peak-to peak voltages across ESL of the capacitors are expressed below

IJRITCC | March 2016, Available @ http://www.ijritcc.org

$$\Delta V_{C1}^{ESL} = L_{C1} \left[ \frac{(n+1) \left[ \left( \frac{2+n+nD}{D(1-D)} \right) I_o + \frac{DV_{in}}{L_m f_s} \right]}{(1-D) T_s} + \frac{2I_o}{D^2 T_s} \right] \\ \Delta V_{C_2}^{ESL} = L_{C_2} \left[ \frac{\left( n+1 \right) \left[ \left( \frac{2+n+nD}{D(1-D)} \right) I_o + \frac{DV_{in}}{L_m f_s} \right]}{(1-D) T_s} + \frac{2(n+1)^2 I_o}{n^2 (1-D)^2 T_s} \right] \\ \Delta V_{C3}^{ESL} = L_{C3} \left( \frac{2I_o}{(1-D)^2 T_s} + \frac{2I_o}{D^2 T_s} \right) \\ \Delta V_{C0}^{ESL} = L_{C0} \left( \frac{2I_o}{(1-D)^2 T_s} \right)$$

(33)

By imposing a certain ripple value, the sizes of the capacitors are calculated using equation (29). Then, by knowing ESRs and ESLs of the chosen capacitors, the total voltage ripple,  $\Delta V_C + \Delta V_C \stackrel{\text{ESR}}{} + \Delta V_C \stackrel{\text{ESL}}{}$ , have to be checked to be less than the desired proportion of capacitor voltages. An important condition in the design of the output capacitor in any converter is the hold-up time requirement for step-load response. A load variation,  $\Delta I_{out}$ , in the load current causes a load voltage change,  $\Delta V_{CO}$ . It takes a short non zero time,  $\tau$ , until the feedback loop responds to bring back the load voltage to its steady-state value. According, this duration is usually approximated as  $1/(0.1f_S)$ . During the time  $\tau$ , the capacitor must hold the load voltage, such that  $\Delta V_{CO}$  remains under the acceptable ripple value, usually 1% of  $V_{out}$ . This means that the capacitor value has to be at least

$$C_{O\min} = \frac{\Delta I_{out}}{0.01 V_{out}} \tau \tag{34}$$

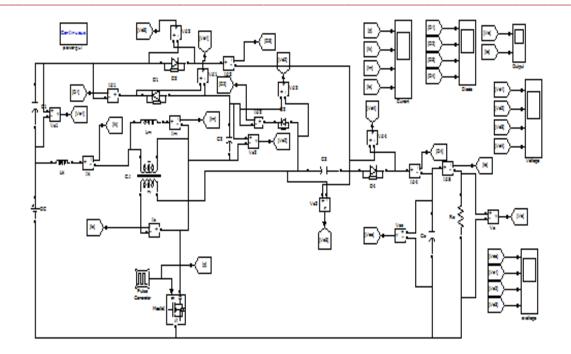

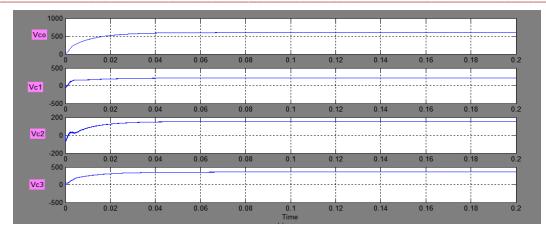

#### **IV SIMULATION RESULTS:**

The performance of the presented converter is assessed using these specifications given in Table

| Specifications                                                           | Values                       |

|--------------------------------------------------------------------------|------------------------------|

| Input dc voltage                                                         | 40V                          |

| Output dc voltage                                                        | 600V                         |

| Coupled Inductor                                                         | L <sub>K</sub> :1µH,Lm:300µH |

| CapacitorsC <sub>1</sub> ,C <sub>2</sub> ,C <sub>3</sub> .C <sub>0</sub> | (47,47,100,220)µF            |

| Switching Frequency                                                      | 60KH <sub>Z</sub>            |

#### Table 1: SIMULATION PARAMTERS

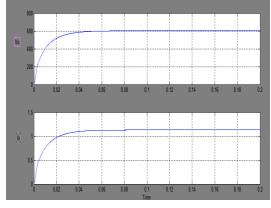

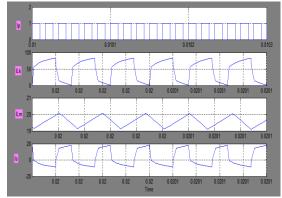

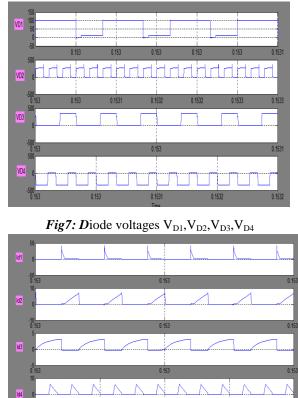

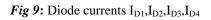

The results verify the analysis of the steady state operation. The voltage on the switch ( $V_{DS}$ ) during the turn-off state is clamped. Therefore, a low-voltage-rated switch can be used to improve the efficiency of the converter. Fig. 5 shows the simulation circuit of the converter Fig.6 shows the output of the converter, Fig. 7 depicts the voltage stresses on the diodes, fig 8 shows that the energy stored in the leakage inductance is recycled to capacitor C1 through diode  $D_{1}$ , and magnetizing inductor current. Fig 9 shows diode currents.Fig.10 shows capacitors voltages.

Fig5 : Simulation circuit for proposed system

Fig6: Output voltage and current

*Fig 8:* Pulse,Leakage inductor ,Magnetizing inductor, Secondary currents

The current waveforms of the diodes and the coupled inductor  $(i_{LK})$  shown in validate the analysis and the feasibility of the proposed converter. The input current ripple is as much as other proposed high-step-up converters. However, a low-pass filter can be used to reduce the input current ripple. The results show the high conversion efficiency of the presented converter

### **V. CONCLUSION**

This paper concentrated on the high step up dc-dc converter for non-conventional energy sources. The converter is flexible for distributed generations based on the non-conventional energy resources, which has to be performing with high voltage gain transfer functions. The energy stored under the leakage inductance is given back to multiplier module which wills leads to enhance the system performance. The voltage imbalances in the main power switch related losses were minimized by the presence of low resistance utilization. The implemented model has produced less steady state error which improves the behaviour of the system. The capacitances are utilized to charge under turned off conditions. The designed simulink models are tested and verified within the simulation.

#### REFERENCES

- [1] Y. Zhao, X. Xiang, C. Li, Y. Gu, W. Li, and X. He, "Single-phase high step-up converter with improved multiplier cell suitable for halfbridge based PV inverter system," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2807–2816, Jun. 2014.

- [2] H. Lee, T. J. Liang, and J. F. Chen, "Isolated coupled-inductor-integrated DC–DC converter with non-dissipative snubber for solar energy applications," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3337–3348, Jul. 2014.

- [3] C. W. Chen, K. H. Chen, and Y. M. Chen, "Modeling and controller design of an autonomous PV module for DMPPT PV systems," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp.4723–4732, Sep. 2014.

- [4] Y. P. Hsieh, J. F. Chen, T. J. Liang, and L. S. Yang, "Analysis and implementation of a novel single-switch high step-up DC-DC converter," *IET Power Electron.*, vol. 5, no. 1, pp. 11–21, Jan. 2012.

- [5] L. S. Yang, T. J. Liang, H. C. Lee, and J. F. Chen, "Novel high step-up DC–DC converter with coupled-inductor and voltage-doubler circuits," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 4196–4206, Sep. 2011.

- [6] J. A. Carr, D. Hotz, J. C. Balda, H. A. Mantooth, A. Ong, and A. Agarwal, "Assessing the impact of SiC MOSFETs on converter interfaces for distributed energy resources," *IEEE Trans. Power Electron.*, vol. 24, no.1, pp. 260–270, Jan. 2009.

- [7] L. S.Yang, T. J. Liang, and J. F.Chen, "Transformer-less DC-DC converter with high voltage gain," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp.3144–3152, Aug. 2009.

- [8] C. L. Wei and M. H. Shih, "Design of a switched-capacitor DC-DC converter with a wide input voltage range," *IEEE Trans. Circuits Syst.*, vol.60, no. 6, pp. 1648–1656, Jun. 2013.

- [9] W. Qian, D. Cao, J. G. C. Rivera, M. Gebben, D.Wey, and F. Z. Peng, "A switched-capacitor DC–DC converter with high voltage gain and reduced component rating and count," *IEEE Trans. Ind. Electron.*, vol. 48, no. 4,mpp. 1397–1406, Jul. 2012.

- [10] Y. P. Hsieh, J. F. Chen, T. J. Liang, and L. S. Yang, "Novel high step-up DC–DC converter with coupled-inductor and switchedcapacitor techniques," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 998–1007, Feb. 2012.

- [11] T. J. Liang, J. H. Lee, S. M. Chen, J. F. Chen, and L. S. Yang, "Novel isolated high-step-up DC–DC converter with voltage lift," *IEEE Trans.Ind. Electron.*, vol. 60, no. 4, pp. 1483–1491, Apr. 2013.

- [12] [12] F. L. Luo and H. Ye, "Hybrid split capacitors and split inductors applied in positive output super-lift Luo-converters," *IET Power Electron.*, vol. 6, no. 9, pp. 1759–1768, Jun. 2013.

- [13] [13] T. J. Liang, J. H. Lee, S. M. Chen, J. F. Chen, and L. S. Yang, "Novel isolated high-step-up DC–DC converter with voltage lift," *IEEE Trans.Ind. Electron.*, vol. 60, no. 4, pp. 1483–1491, Apr. 2013.