# Approximate Compressors for Multiplication

Pooja Rathee M.Tech. student in ECE (VLSI-Design), Deenbandhu Chhotu Ram University of Science and Technology, Sonepat, India *poojarathee9@gmail.com*  Rekha Yadav Assistant Professor of Electronics And Communication Department, Deenbandhu Chhotu Ram University of Science and Technology, Sonepat, India *rekha\_7r@yahoo.co.in*

*Abstract:* At nanometric scales, approximate computing is an attractive prototype used for digital processing. Despite providing less accurate results, approximate computing is preferred over exact computing as it provides a fast & significant output along with low power consumption. Designing of an efficient multiplier has always been a challenge for VLSI designers as multipliers have a large area, long latency consumes considerable power. For this inconvenience compressor with low latency, low power consumption and reduced stages of the product are designed. This paper proposes two methods to design high order compressors (8:4 & 9:4) (i) Using adders (half & full) (ii) Using multiplexers in Cadence VIRTUOSO tool using 45nm technology. Extensive simulation results show that the proposed designs achieve significant accuracy improvement along with power, area, and delay reductions compared to previous compressor designs.

Keywords: approximate computing; multipliers; high order compressors; latency; power consumption.

# I. INTRODUCTION

Multiplication operation serves as the backbone of all signal processing applications like in DSP & Embedded systems. The speed of multiplier decides the speed of the processor. Speed attribute of any processor which involves multipliers depends on efficiency obtained in the multiplication process.

Multiplication process can be stated as repeated sum of partial products. The final product is obtained by repeatedly adding the multiplicand to itself number of times specified by another multiplier. The hardware requirements of multipliers are very high which results in low precision, increase in chip area & hardware complexity along with increased latency. To carry out time efficient multiplication, high-speed multipliers are being used that electronically computes the result by following certain logics. Due to the vast application area of multipliers, it is imperious to design a multiplier that offers low latency, consumes low power along with physically compact design.

Multiplication is intrinsically a three step process

- partial product generation

- partial product reduction

- final result computation.

As the number of bits (to be multiplied) increases the number of partial products generated also increases. However, the problem comes while multiplying high order bits as the partial products reduction have long vertical paths which leads to high latency. The most common technique used by the designers to reduce these vertical paths was by using adders. More number of stages were introduced to reduce the partial products which eventually create problems such as signal discontinuities. So the designers come up with the idea of using compressors in multipliers. Compressors serve as a critical component of a multiplier & are used in large numbers to perform the reduction process. These are combinatorial devices that provide effective partial product reduction by reducing the latency of this step by following certain logics. The performance of the multiplier can be enhanced by improving the compressor designs by lowering the transistors count that ultimately reduces the delay.

A compressor takes equally weighted inputs & produces binary outputs. More specifically an m:n compressor counts the number of ones at the inputs & provides with the binary count at the output (here m represents input bits & n represents output bits). The weight of the LSB of the compressor output is the same as the weight of each of the inputs, and the remaining bits have increasingly higher weights.

Depending on the bits converted, compressors are classified into two classes low order compressors (such as 3-2, 4-2, 5-2) [3] & high order compressors (such as 5-3, 6-3, 7-3, 8-4, 9-4). In this paper, two designs of high order compressor (8-4 & 9-4) one using half & full adders & other using multiplexers are being designed & analyzed & their performance matrices such as power, delay & area are compared with the present technical designs.

# II. PROPOSED DESIGN OF COMPRESSOR

In this section, two designs are presented to design 8-4 & 9-4 compressors in 45nm technology using Cadence tool. The first design is by using adders & another design is by using multiplexers. Both the high order compressor's designs show

<sup>\*\*\*\*</sup>

much better results regarding delay, area & power as compared to the traditional designs[1].

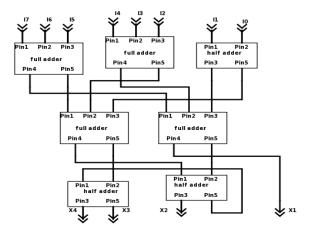

#### A. Design 1: 8-4 & 9-4 compressors using adders

Figure 1 shows the schematic of 8-4 compressor designed using half adders & full adders. An 8-4 compressor has eight inputs (i0-i7) & produces four outputs (X1-X4) i.e. it compresses eight partial products into four. If all the input bits are one (i.e. 11111111), then the output will be 1000. It demonstrates that output is the binary equivalent of the inputs. It uses three stages of half & full adders to compress the inputs by applying all sum **o**utputs of the first stage to one adder of the second stage & all carry outputs to another adder. The set of equations (1-4) shown below governs the process.

$$X1 = a \oplus c \oplus e \tag{1}$$

$$X2 = ((ac)|(ae)|(ce)) \oplus (b \oplus d \oplus f)$$

(2)

$$X3 = \left( \left( (ac) | (ae) | (ce) \right) \cdot (b \oplus d \oplus f) \right)$$

$$\oplus \left( (bd) | (bf) | (df) \right) \tag{3}$$

$$X4 = \left( \left( (ac)|(ae)|(ce) \right) \cdot (b \oplus d \oplus f) \right) \cdot \\ \left( (bd)|(bf)|(df) \right)$$

(4)

where :

$$a = I0 \oplus I1; B = I0 \cdot I1;$$

$$c = I2 \oplus I3 \oplus I4$$

$$d = ((I2 \cdot I3)|I2 \cdot I4|(I3 \cdot I4));$$

$$e = I5 \oplus I6 \oplus I7$$

$$f = ((I5 \cdot I6)|(I5 \cdot I7)|(I6 \cdot I7))$$

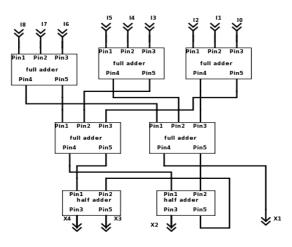

Figure 2 shows the schematic of the 9-4 compressor using three stages of adders. It takes nine inputs (I0-I8) & compresses to 4 outputs (X1-X4) following a set of equations (5-8). In 9-4 compressors, if all the inputs are high i.e. I0-I8 are high (1111111) then maximum output (X1-X4) will be 1001. The proposed 9-4 compressor uses a combination of 5 full adders & half adders. The total number of adders used in the proposed design are much less as compared to the number of adders used in low order compressors as in low order, the number of components increases progressively with the input bits to be compressed. So the number of stages decides the performance characteristics such as delay, area, power consumption.

$$X1 = a \oplus c \oplus e$$

(5)

$$X2 = ((ac)|(ae)|(ce)) \oplus (b \oplus d \oplus f)$$

(6)

$$X3 = (((ac)|(ae)|(ce)) \cdot (b \oplus d \oplus f)) \oplus ((bd)|(bf)|(df))$$

(7)

$$X4 = (((ac)|(ae)|(ce)) \cdot (b \oplus d \oplus f)) \cdot ((bd)|(bf)|(df))$$

(8)

where :

$a = I0 \bigoplus I1 \bigoplus I2;$  $b = ((I0 \cdot I1))((I0 \cdot I2))((I1 \cdot I2);$

$$d = ((I3 \cdot I4)|I3 \cdot I5|(I4 \cdot I5));$$

$$e = I6 \oplus I7 \oplus I8;$$

$$f = ((I6 \cdot I7)|(I6 \cdot I8)|(I7 \cdot I8))$$

$c = I3 \oplus I4 \oplus I5;$

Figure 1. Schematic of 8-4 compressor using adders

Figure 2. Schematic of 9-4 compressor using adders

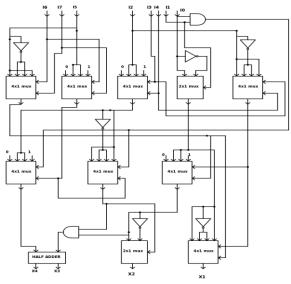

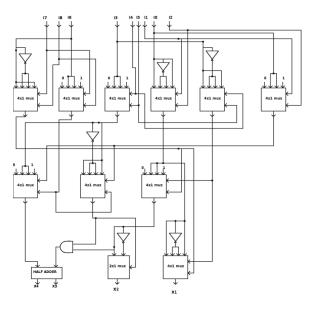

# B. Design II: 8-4 & 9-4 Compressors using multiplexers

Although compressors built using adders shows much improvement over conventional ones, the performance can be further enhanced using multiplexers instead of adders. Figure 3 & 4 shows the schematic of 8-4 & 9-4 compressors designed using multiplexers respectively. As the select lines control multiplexer's operations, so the required part of the structure can be made active & rest can be set in ideal mode. This feature serves as a significant advantage in reducing the power consumption of the circuit along with critical path delay reduction.

Figure 3. Schematic diagram of 8-4 compressor using multiplexers

Figure 4 Schematic of 9-4 compressor using multiplexer

#### **III. SIMULATION & RESULTS**

In this section, the proposed 8-4 & 9-4 compressors designs depicted in section II are analyzed & compared with the traditional designs. For analyzing power, delay & area, the designs are implemented in 45 nm CMOS technology using Cadence Virtuoso tool. The simulation results obtained are discussed using tabular comparison.

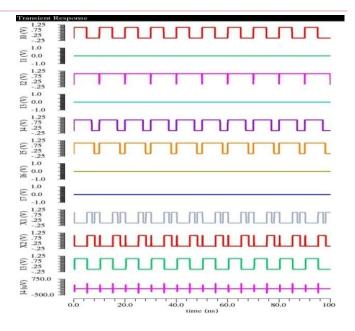

Figure 5 shows the simulation results of the 8-4 compressor with inputs from I0-I7 & output from X1-X4.

Figure 5. Output waveform of 8-4 compressor using adders

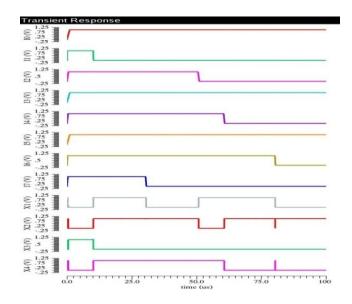

Figure 6 shows the simulated waveform of 9-4 compressor designed using adders with inputs from I0-I8 & output from X1-X4.

Figure 6. Output waveform of 9-4 compressor using adders

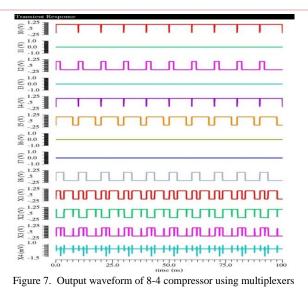

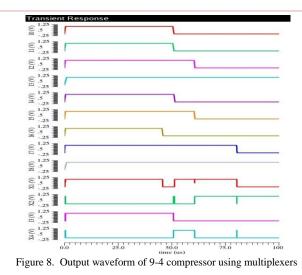

Figure 7 shows the output waveform of the 8-4 compressor using multiplexers with inputs from IO-I7 & output from X1-X4.

Figure 8 shows the output waveform of the 9-4 compressor using multiplexers with inputs from IO-I8 & output from X1-X4.

Table 1 describes the performance comparison of the proposed 8-4 & 9-4 compressors with the previous results where it depicts the superiority of the proposed work over the

traditional design in terms of power, delay & area.

TABLE I.

Performance Comparision Of 8-4 & 9-4 Compressors

| 8-4 compressor         |                          |                            |                         |                            | 9-4 compressor           |                            |                         |                            |

|------------------------|--------------------------|----------------------------|-------------------------|----------------------------|--------------------------|----------------------------|-------------------------|----------------------------|

|                        | Using half & full adders |                            | Using multiplexers      |                            | Using half & full adders |                            | Using multiplexers      |                            |

| PARAMETERS             | Previous<br>results [1]  | Proposed<br>design results | Previous<br>results [1] | Proposed<br>design results | Previous<br>results [1]  | Proposed<br>design results | Previous<br>results [1] | Proposed<br>design results |

| POWER(nW)              | 18276.250                | 1037                       | 15263.603               | 2628                       | 21848.218                | 837.4                      | 15459.456               | 3018                       |

| AREA(um <sup>2</sup> ) | 93.139                   | 21.60                      | 110.779                 | 91.91                      | 102.1900                 | 36.00                      | 112.190                 | 107.72                     |

| DELAY(ps)              | 1028                     | 5.167                      | 1071                    | 5.239                      | 1082                     | 5.180                      | 1077                    | 5.166                      |

# IV. CONCLUSION

To speed up multipliers such as Dadda[5], Wallace tree, Booth, compressors are the key in partial product reduction. The use of compressors in the multipliers not only reduces the vertical critical path but also reduce the stage operations simultaneously. To show better improvement, two different designing process has been explored (one using adders & other using multiplexers in the circuitry) in 45 nm technology using Cadence Virtuoso tool. The simulation results demonstrate considerable improvement regarding delay, area & power over conventional 8-4 & 9-4 compressor designs.

#### REFERENCES

Marimuthu, R., Dhruv Bansal, S. Balamurugan & P.S. Mallick "Compressors For High-Speed Multiplication" in American Journal of Applied Sciences 10 (8): 893-900, 2013.

- [2]. N. Maheshwari, Z. Yang, J. Han, F. Lombardi, "A design approach for compressor based approximate Multipliers," Proc. 28th Int. Conf. VLSI Design (VLSID), pp. 209-214, Jan. 2015.

- [3]. Baran, D., M. Aktan and V.G. Oklobdzija "Energy Efficient implementation of parallel CMOS multipliers with improved compressors," Proceedings of the International Symposium on Low Power Electronics and Design, Aug. 18-20, IEEE Xplore Press, Austin, TX, USA., pp: 147-152.

- [4]. K. Prasad and K. K. Parhi, "Low-power 4-2 and 5-2 compressors," in Proceedings of 35th Asilomar Conference On Signals, Systems, and Computers, vol. 1, pp. 129-133, 2001.

- [5]. A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication," IEEE Trans. Comput., vol. 64, no. 4, pp. 984–994, Apr. 2015.

- [6]. J. Liang, J. Han, and F. Lombardi, "New metrics for the reliability of approximate and probabilistic adders," IEEE Trans. Comput., vol. 62, no. 9, pp. 1760–1771, Sep. 2013

- [7]. Z. Wang, G. A. Jullien, and W. Miller, "A new design technique for column compression multipliers," in IEEE Trans. Comput., vol. 44, pp. 962–970 Aug. 1995.

- [8]. J. Gu, C. H. Chang, "Ultra Low-voltage, a low-power 4-2 compressor for high-speed multiplications," in Proc. 36th IEEE Int. Symp. Circuits Systems, Bangkok, Thailand, May 2003.

- [9]. C. Chang, J. Gu, M., "Ultra Low-Voltage Low- Power CMOS 4-2 and 5-2 Compressors for Fast Arithmetic Circuits," IEEE Transactions on Circuits & Systems, Vol. 51, No. 10, Oct. 2004.

- [10].J. Ma, K. Man, T. Krilavicius, S. Guan, and T. Jeong, "Implementation of High-Performance Multipliers Based on Approximate Compressor Design" in International Conference on Electrical and Control Technologies (ECT), 2011.

- [11].C. Liu, J. Han and F. Lombardi, "A Low-Power, High-Performance Approximate Multiplier with Configurable Partial Error Recovery," DATE 2014, Dresten, Germany, 2014.

- [12]. Amir Naja, Ardalan Naja, and Sattar Mirzakuchaki," Lowpower and high performance 5:2 compressors", 22nd Iranian Conference on Electrical Engineering, 2014 May 20-22.

- [13]. Ming-Bo Lin, "Introduction to VLSI Systems," CRC Press. November; 2011;pp .256-300.

- [14].S. Veeramachaneni, K. M. Krishna, L. Avinash, S. R. Puppala, M. B. Srinivas, "Novel architectures for highspeed and low-power 3-2 4-2 and 5-2 compressors", Proc. Int. Conf. VLSI Design (VLSID), pp. 324-329, Jan. 2007.

- [15].A. Pishvaie, G. Jaberipur, A. Jahanian, "High-performance CMOS (4:2) compressors", Int. J. Electron., vol. 101, no. 11, pp. 1511-1525, Jan. 2014.

- [16].H. Jiang, J. Han, F. Lombardi, "A comparative review and evaluation of approximate adders," Proc. ACM Great Lakes Symp. VLSI (GLSVLSI), pp. 343-348, May 2015.

- [17].Jaymin Mody, Rutuja Lawand, Priyanka R,Sivananthan S\*, Sivasankaran K, "Study of Approximate Compressors for Multiplication Using FPGA", International Conference on Green Engineering and Technologies (IC-GET 2015)

- [18].Shima Mehrabi, Keivan Navi, and Omid Hashemipour, "Performance Comparison of High-Speed High-Order (n:2) and (n:3) CNFET-Based Compressors", International Journal of Modelling and Optimization, Vol. 3, No. 5, October 2013.

- [19].Sana Raffath, "Adaptive Design and Analysis of Approximate Compressor for Multiplication with Low Power Consumption", Aurora's International Journal of Computing | 2015 | Vol. 2. Issue 2 | July-December 2015.

- [20]. Ravi Nirlakalla, Thota Subba Rao, Talari Jayachandra Prasad," Performance Evaluation of High-Speed Compressors for High-Speed Multipliers", Serbian journal of electrical engineering vol. 8, no. 3, November 2011.