# Analysis of Drop Out and Load Current for on Chip Voltage Regulators

Dr S. K Bishnoi<sup>1</sup>, Vijendra K Maurya<sup>2</sup>, Mohammad sabir<sup>3</sup>

<sup>1</sup>Asso. Prof. ECE Dept. Govt. Engg College, Bikaner, bishnoi\_sk@yahoo.com <sup>2</sup>Asso. Prof. ECE Dept. GITS, Udaipur, maurya.vijendra@gmail.com <sup>3</sup> Asst. Prof. ECE Dept. GITS, Udaipur, sabii.sankhla@gmail.com

Abstract. LDO (Low Drop-Out) Voltage regulators are commonly used in electronics power supply circuit. DC linear voltage regulator is a LDO regulator that can regulate the output voltage even when the power supply voltage is very near to the output voltage. This paper present a comparison between two of the most admired voltage regulator structures such as feed forward ripple cancellation technique and MOS capacitor compensation technique. The comparison has been carried out considering the output voltage, power consumption, drop-out voltage, load current, quiescent current, line regulation and load regulation. The discussion is supported by practical analysis of both the voltage regulator. The two LDO voltage regulators are taken with power supply voltage, reference voltage, error amplifier, pass transistor. The object of this paper is to compare the all the parameter of the voltage regulator to found best LDO voltage regulator structure. The comparison showed that the voltage regulator circuit with MOS capacitor compensation technique (MCC) is best rather than feed forward ripple cancellation technique (FFRC). All simulation and result of LDO voltage regulator is done at tanner tool 14.1.

Keywords: Low Drop-out(LDO), MOS capacitor, Pass transistor, Error amplifier, summing amplifier and ,feed-forward amplifier.

\*\*\*\*

#### **1 INTRODUCTION**

LDO voltage regulators are necessary building blocks in power-management systems. Power management systems for microprocessors and portable devices often use multiple LDO regulators to offer a regulated supply voltage with minimum

ripple to supply-noise-sensitive blocks [1]. To raise batterylife and to achieve better power efficiency, low-dropout regulators are essential. LDO consists of a pass transistor, an error amplifier EA, a feedback network (RF1 and RF2) and a immense off chip capacitor . Various electronic equipments contains circuit which convert AC supply voltage into DC voltage at the preferred level. The DC voltage attained from such circuits must be stable. The DC voltage regulated power supplies are used to acquire the stable DC voltage yet there are variations in load current, temperature and AC line voltage. This power supply attenuates the ripple in the input voltage. The essential function of a voltage regulator is voltage regulation, provides clean, constant, accurate voltage to a circuit.

Regulator benefits:-

- 1. Accurate supply voltage

- 2. Active noise filtering

- 3. Protection from over current faults

- 4. Generation of multiple output voltages from single source

- 5. Inter-stage isolation

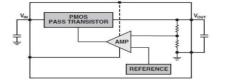

Fig 1: Block diagram of LDO Voltage Regulator [1]

LDO Architecture: - The architecture consists of following four parts:

- 1. Voltage Reference

- 2. Error Amplifier

- 3. Pass Transistor

- 4. Feedback Resistor

LDO be made of a voltage reference, an error amplifier, a feedback voltage divider and a pass transistor and load circuit. In this circuit, Output current is delivered through the pass device. Its gate voltage is restricted by the error amplifier which compares the reference voltage with the feedback voltage and also amplifying the differences so that reduce the error voltage.

#### **2** IMPLEMENTATION OF LOW DROP-OUT **VOLTAGE REGULATOR**

#### 2.1 FEED-FORWARD RIPPLE CANCELLATION TECHNIQUE[FFRC]

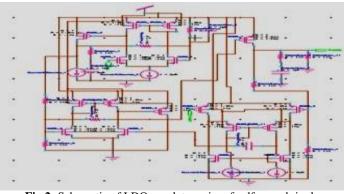

The Schematic of LDO structure is shown in fig 2. PMOS 1, PMOS 2, PMOS 3, NMOS 1 and NMOS 2 form first stage amplifier i.e. Feed-Forward Amplifier. PMOS\_4, PMOS\_5, PMOS\_6, NMOS\_3 and NMOS\_4 form second stage amplifier called Summing Amplifier. At the third stage, PMOS\_7, PMOS\_8, PMOS\_9, PMOS\_10, NMOS\_6 and NMOS\_5 form Error Amplifier. PMOS\_11 is the Power PMOSFET forming fourth stage. Diode connected transistor PMOS\_12 and PMOS\_13 form feedback resistive network. Resistor\_9, Resistor\_10 and Capacitor\_4 resistance are the load and capacitance.Capacitor\_1,Capacitor\_2 and Capacitor\_3 are required on-chip active MOS capacitances of LDO structure.

To eliminate input ripples from appearing at the output, a zero transfer gain is necessary from the input to the output. Hence, the gate-overdrive voltage is independent of input ripples, and as a result no ripple appears across the load. Supply ripples, appearing at the source of pass transistor Mp

, are reproduced at the gate of using Mp the feed-forward path.

Fig 2: Schematic of LDO regulator using feedforward ripple cancellation technique

# 2.2 MOS CAPACITOR COMPENSATION TECHNIQUE [MCC]

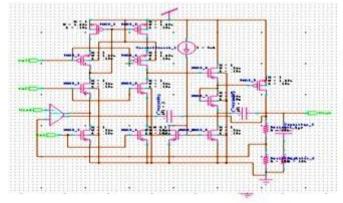

The solution to control the damping factor and reduce the area of the compensation capacitor on chip, is the NMC technique with active capacitor and resistor; it is called an NMCACR LDO. In this technique, a capacitor is connected between the input differential stage and the output stage.

This LDO is composed of two gain stages, a power PMOS transistor and the feedback resistor network. First stage is the error amplifier (EA), second is a high gain stage. Capacitor\_1, Capacitor\_2 are the on-chip Active MOS capacitances. Resistor\_1 and Resistor\_3 construct the feedback resistive network. Resistor\_2 and Capacitor\_3 the equivalent load resistance and load capacitance at the power PMOS transistor.

Fig3: Schematic of LDO regulator using MOS capacitor compensation technique

## 3 ANALYSIS AND COMPARISION OF LDO VOLTAGE

#### REGULATOR

#### 3.1 Feed-Forward Ripple Cancellation Technique

In LDO voltage regulator different types of parameters are consider :-

**Load Regulation** is the amount that the output voltage changes for a given change in load current. It can be improved by increasing the loop gain of LDO regulator which is constructed by gain of error amplifier and tranconductance of series pass transistor. Line Regulation means the resistance of LDO against the variation of supply vol tage.

#### Line Regulation = $\Delta Vout/\Delta Vin$

**Quiescent current** that a part draws from the source when idling (either shut down or not delivering significant amounts of load current) can be of critical importance in battery-powered applications.

**Load Current** is maximum current required in an application must be considered when selecting an IC regulator. The load current specification for an IC regulator be defined as either a single value or a value that is dependent on inputoutput voltage differential.

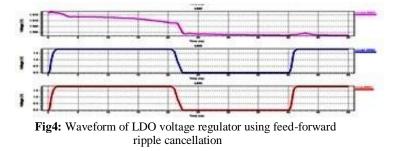

In Feed-Forward Ripple Cancellation Technique Voltage regulator at input 1.8V, the output is 1.7V. Therefore the Drop-out voltage is 0.1V which is shown in fig.4.

Different types of parameters are calculated and listed below in table 1 & table 2.

TABLE 1.POWER, LOAD CURRENT AND QUIESCENT CURRENT AT DIFFERENT  $V_{\text{DD}}$

| S<br>No. | I<br>npu<br>t(V) | Power<br>Consump-<br>tion(mw) | Load<br>Cur-<br>rent(µA) | Quie<br>scent<br>cur-<br>rent(µA<br>) |

|----------|------------------|-------------------------------|--------------------------|---------------------------------------|

| 1.       | 1.5              | 0.486                         | 52                       | 46                                    |

| 2.       | 1.8              | 0.623                         | 72                       | 78                                    |

| 3.       | 2                | 0.954                         | 88                       | 92                                    |

TABLE 2. OUTPUT, DROP-OUT VOLTAGE AND LOAD

REGULATION AT DIFFERENT VDD

| S<br>No. | Input(V) | Output(V) | Drop-out<br>Voltage(V) | Load<br>Regulation<br>(V/mA) |

|----------|----------|-----------|------------------------|------------------------------|

| 1.       | 1.5      | 1.23      | 0.27                   | 8.01                         |

| 2.       | 1.8      | 1.52      | 0.28                   | 7.00                         |

| 3.       | 2        | 1.7       | 0.3                    | 6.34                         |

#### 3.2 Mos Capacitor Compensation Technique

A full on-chip and area efficient low-dropout voltage regulator, which utilize the technique nested miller compensation with active capacitor (NMCAC) to eliminate the external capacitor without compromising the stability of the system in the full output current range.

Fig5: waveform of LDO Voltage regulator using MOS Capacitor Compensation Technique

Its different parameters such as Power ,Load current, Quiescent current, Load regulation and Dropout voltage are calculated as listed below in table 3 & table 4.

TABLE 3. POWER, LOAD CURRENT AND QUIESCENT

CURRENT AT DIFFERENT VDD

| S.<br>No. | Input<br>(V) | Power<br>Con-<br>sump-<br>tion<br>(mw) | Load<br>Cur-<br>rent(µA) | Quiescent<br>Cur-<br>rent(µA) |

|-----------|--------------|----------------------------------------|--------------------------|-------------------------------|

| 1.        | 1.5          | 0.439                                  | -47                      | 127                           |

| 2.        | 1.8          | 0.615                                  | 10                       | 100                           |

| 3.        | 2            | 0.928                                  | 20                       | 95                            |

**TABLE 4.** OUTPUT, DROP-OUT VOLTAGE AND LOAD

REGULATION AT DIFFERENT VDD

| S.<br>No. | Input(V) | Output(V) | Drop-out<br>Voltage(V) | Load Regula-<br>tion (V/mA) |

|-----------|----------|-----------|------------------------|-----------------------------|

| 1.        | 1.5      | 1.45      | 0.05                   | 3.68                        |

| 2.        | 1.8      | 1.75      | 0.05                   | 2.93                        |

| 3.        | 2        | 1.95      | 0.05                   | 1.56                        |

### 4. COMPARISION OF LDO VOLTAGE REGULATOR USING DIFFERENT TECHNIQUE

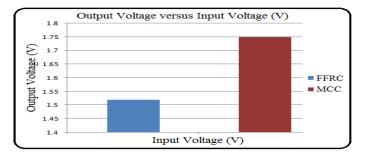

Fig6: Comparision of Output Voltage between FFRC & MCC

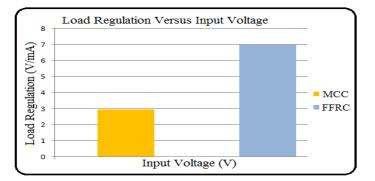

Fig7:Comparision of Load Regulation between FFRC&MCC

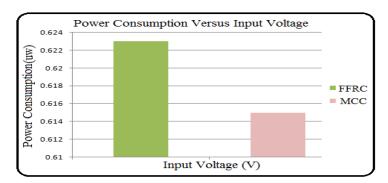

Fig8: Comparision of Power Consumption of FFRC&MCC.

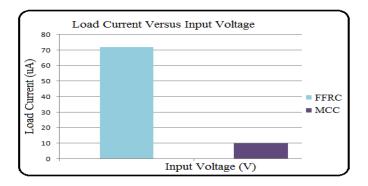

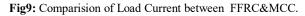

Fig.10: Comparision of Drop-Out Voltage between FFRC&MCC

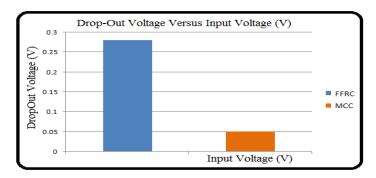

Fig11: Comparision of Line Regulation of FFRC&MCC

The performance comparison of voltage regulator table is shown below

TABLE 5. COMPARISON OF VOLTAGE REGULATOR WITH CONSTANT  $V_{\rm IN}(1.8V)$

|        | Parameters                   | <b>Technique of Regulator</b> |       |  |

|--------|------------------------------|-------------------------------|-------|--|

| S. No. |                              | FFRC                          | МСС   |  |

| 1.     | Output<br>Voltage(V)         | 1.52                          | 1.75  |  |

| 2.     | Power<br>consumption(µ<br>w) | 0.623                         | 0.615 |  |

| 3.     | Load<br>Current(uA)          | 72                            | 10    |  |

| 4.     | DropOut<br>Voltage(V)        | 0.28                          | 0.05  |  |

| 5.     | Line<br>Regulation(V)        | 2.5                           | 1.8   |  |

| 6.     | Load<br>Regulation(V/<br>mA) | 7                             | 2.93  |  |

#### **5.** CONCLUSION

In this work, experimental comparison between two of the low power, low drop-out voltage regulator structures was presented. The analytical description showed that the MOS Capacitor Compensation technique has an output voltage higher than the Feed-Forward Ripple Cancellation technique with power supply voltage 1.8V. The comparison result shows that the LDO voltage regulator with MCC technique provides improvements in terms of output voltage, drop-out voltage, power consumption, quiescent current, line regulation. Therefore we found that performance of LDO voltage regulator with MCC technique is best which provides clean, constant, accurate voltage to a circuit.

#### ACKNOWLEDGMENT

The authors would like to thank Kumkum Verma, Sanjay Jaiswal, Harshita

Dadhich.

#### References

- [1]. Joselyn torres, mohamed El-nozahi, ahmed amer, seenu gopalraju, reza abdullah, Kamran Entesari, and Edgar sánchez-sinencio, "Low Drop-Out Voltage Regulators : Capacitor-less Architecture Comparison,"IEEE CIRCUITS AND SYSTEMS MAGAZINE,20 May 2014.

- [2]. C. Zhan and W. H. Ki, "An output-capacitor-free adaptively biased low-dropout regulator with subthreshold undershoot-reduction for SoC," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 5, pp. 1119– 1131, May 2012.

- [3]. C.Shi,B.C.Walker,E.Zeise,B.Hu,andG.H.McAllister," Ahighly integrated power management IC for advanced mobile applications,"IEEEJ.Solid-StateCircuits,vol.42,no.8,pp.1723–1731,Aug.2007.

- [4]. K. N. Leung and P. K. T. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factorcontrol frequency," IEEE J. Solid-State Circuits, vol. 37, no. 10, pp. 1691–1701, Oct. 2003.

- [5]. R. J. Milliken, J. Silva-Martinez, and E. Sánchez-Sinencio, "Full on-chip CMOS low-dropout voltage regulator," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 9, pp. 1879–1890, Sep. 2007.

- [6]. Zared Kamal, Zouak Mouhcine and Qjidaa Hassan, "Full On-Chip CMOS Low Dropout Voltage Regulator Using MOS Capacitor Compensation", IEEE PUBLICATION, 2012.

- [7]. Vijendra K Maurya, Navneet Agrawal, Ashik Hussan ," Design & Analysis of on Chip Voltage Regulator Circuits for Low Power VLSI Applications" Journal of Scientific and Engineering Research, 2017, 4(6):65-70, ISSN: 2394-2630.

- [8]. Jesus Lopez-Arredondo, Esteban Tlelo-Cuautle, Rodolfo Trejo-Guerra, "Optimizing an LDO voltage regulator by evolutionary algorithms considering tolerances of the circuit elements", 2015 16th Latin-American Test Symposium (LATS), vol. 00, no. , pp. 1-5, 2015,

doi:10.1109/LATW.2015.7102506