# An Effective Low Power Ring Oscillator Based All Digital Phase Locked Loop

J. Jeslin Jijo Student, VLSI Design Marthandam College of Engineering and Technology, Kuttakuzhi *e-mail: pjsjeslin@gmail.com*  Mr. R. Dinesh Asso.prof/ECE Marthandam College of Engineering and Technology, Kuttakuzhi *e-mail: dinaofc@yahoo.co.in*

*Abstract* — The All digital phase-locked loops (ADPLL) widely employed in the data communication systems including, but not limited to, the implementation of the frequency multiplication and clock synchronization circuits. A phase-interpolator is utilized for power consumption reduction by using TDC in a ring-oscillator in a fractional-N phase-locked loop. A predicted-phase-interpolation method is used to calculate the integer and fractional parts of the frequency-division-ratio and to find two interpolation clocks. The prediction method gives a significant power reduction in the proposed PIFC by enabling the use of low-frequency clocks for phase interpolation

**Keywords** - Time to Digital Convertor (TDC), All Digital Phase Locked Loop (ADPLL), Phase –Interpolator based Fractional counter (PIFC), Predicted-Phase- interpolation.

## I. INTRODUCTION

Phase-locked loops are widely used in advance electronic circuits, Data communication systems as a clock and data recovery, modulation and frequency synthesis, etc... The conventional PLLs consist of analog phase and frequency detector, charge pumps, analog loop filters (LFs) and voltage controlled oscillators (VCOs). Even though, Analog PLLs is giving good locking range and wide operating frequency still it gives problems like PVT variations, redesign problem, more area utilization etc. Due to the technical improvement and new innovation ideas now we have All digital PLL(ADPLL). ADPLL consist of full digital components and it solved the problems occur in DPLL and Analog PLL. The advantages of a digital implementation are the inherent noise immunity of digital circuits, good scalability and easy redesign. Nowadays the designer avoiding the percentage of analog circuitry so that redesign time is improving.

A phase-lock loop is essentially a negative feedback loop in which the phase of the frequency controlled oscillator should lock with that of the incoming signal. Phase error will be created in the Unlock state.

ADPLL have become more attractive because of its wide frequency range, low power consumption, good testability, stability, and portability over difference process. Bang bang phase detector gives good robustness and low power consumption [13]. Frequency locking time is time between initialization of ADPLL and the frequency locking [14].There are two major issues needed to be considered. 1. Design a Digitally-Controlled Oscillator with wide tuning range and high resolution. 2. Design with less lock in time.

The paper is organised as follows Section II covers proposed method of ADPLL and section III covers result analysis and in section IV conclusion is presented.

#### II. PROPOSED SYSTEM

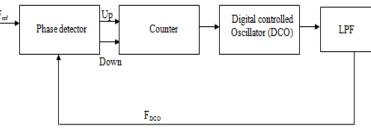

The proposed ADPLL consist of D-flip flop based phase detector, counter, digital lop filter and Ring based digital oscillator.  $F_{\text{REF}}$  represents frequency of reference signal and  $F_{\text{OUT}}$  represents the frequency of ring oscillator frequency.

Figure 1. Proposed Block Diagram

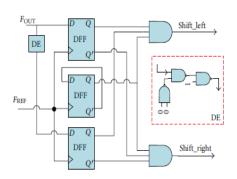

Phase detector generates shift right or shift left without considering of the frequency difference between  $F_{\text{REF}}$  and  $F_{\text{OUT}}$ . As a result, a frequency divider block is not needed in this ADPLL. The delay element of the detector governs the final phase difference.. Generating shift left or shift right once every two cycles of the reference clock provides stability.

Figure 2. Phase Detector

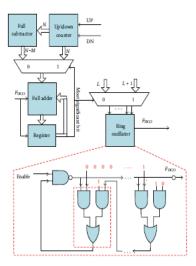

Figure 3. Digitally Controlled Oscillator (DCO)

Digitally Controlled Oscillator (DCO) is the frequency generating block in ADPLL. The frequency of DCO is adjusted for achieving frequency and phase locking. It is used to generate multiples of the frequency. It consists of ring oscillator and fractional divider. The ring oscillator consists of one NAND gate for enabling/disabling the oscillation and a combination of AND OR delay elements. The ring oscillator produces a clock signal (FOSC) whose frequency is proportional to the number of the delay elements in the ring. The FOSC signal must go through each of the delay elements twice to provide one period of oscillation. The number of delay elements and ring oscillator are inversely proportional.

The fractional divider consists of an adder accumulator. The MSB of the accumulator signed register is used to switch the input of the adder between signed integer number N and its two's complement N-M. It is also used to switch between two adjacent ring oscillator chain lengths, (L1) and (L2). The  $F_{\text{OSC}}$  is given by Fosc= 1/2L tde -----2/1

where  $t_{de}$  is the time delay for each delay element and *L* is the chain length that is defined by a one-hot coded control word.

Accordingly, switching between two adjacent chain lengths L1 and L2 provides on average fine frequency resolution.

Frequency stability is normally achieved by designing a stable and fast controller based DCO, whereas a high frequency resolution is achieved by increasing the number of bits of the accumulator signed register.

### III. RESULTS AND DISCUSSIONS

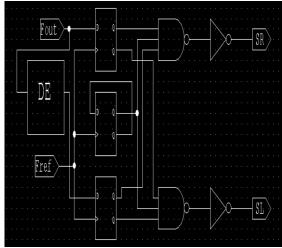

(a) Schematic Results for Phase Detector

Figure 3.1 Schematic Results for Phase Detector

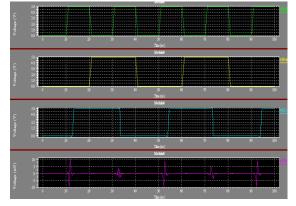

(b) Simulation Results for Phase Detector

Figure 3.2 Simulation Results for Phase Detector

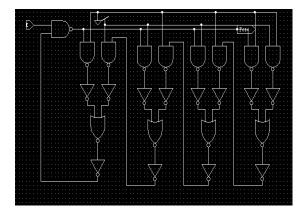

(c) Schematic Results for Ring Oscillator

Figure 3.3 Schematic Results for Ring Oscillator

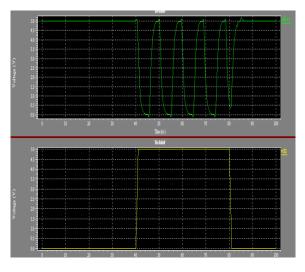

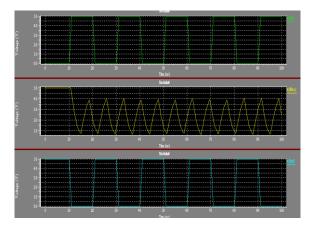

(D) Simulation Results for Ring Oscillator

Figure 3.4 Simulation Results for Ring Oscillator

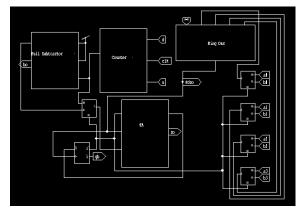

(E) Schematic Results for ADPLL

Figure 3.5 Schematic Results for ADPLL

(F) Simulation Result for ADPLL

Figure 3.6 Schematic Results for ADPLL

The ADPLL power consumption is 0.31 mW and the frequency is 142 MHz

## IV. CONCLUSIONS

Thus, the ADPLL designed with D flip flop based phase detector, digital loop filter and ring based DCO. D flipflop based phase detector utilize low power consumption and utilize low area. The ring oscillator is preferred because of its low power consumption and its ability of delay stages extension. Frequency divider is not required in the block The ADPLL is designed with low power utilization, low chip area and the system gives good locking range and frequency resolution.

### REFERENCES

- B. Markovic, S. Tisa, F. A. Villa, A. Tosi, and F. Zappa, "A high-linearity, 17 ps precision time-to-digital converter based on a single-stage Vernier delay loop fine interpolation," *IEEE Trans. Circuits Syst. 1, Reg. Papers*, vol. 60, no. 3, pp. 557–569, Mar. 2013.

- [2]. C. Venerus and I. Galton, "Delta-sigma FDC based fractional-N PLLs," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 5, pp. 1274–1285, May. 2013.

- [3]. C. Weltin-Wu, E. Temporiti, M. Cusmai, D. Baldi, and F. Svelto, "Insights into wideband fractional ADPLLs: Modeling and calibration of nonlinearity induced fractional spurs," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 9, pp. 2259–2268, Sep. 2010.

- [4]. J. Liu et al., "A 0.012 mm2 3.1 mW bang-bang digital fractional-N PLL with a power supply noise cancellation technique and a walking-one phase-selection fractional frequency divider," in Proc. IEEE ISSCC Dig. Tech. Papers, Feb. 2014, pp. 268–270.

- [5]. J. Shin, J. Kim, S. Kim, and H. Shin, "A delta–sigma fractional-N frequency synthesizer for quad-band multistandard mobile broadcasting tuners in 0.18μmCMOS,"IEIE J. Semicond. Technol. Sci.,vol.7, no. 4, pp. 267–273, Dec. 2007.

- [6]. L. Xu, K. Stadius, and J. Ryynanen, "An all-digital PLL frequency synthesizer with an improved phase digitization approach and an optimized frequency calibration technique," IEEETrans.CircuitsSyst.I,Reg. Papers, vol. 59, J.JESLIN JIJO obtained her B.E (ECE) from Anna University Chennai. Currently she is doing M.E (VLSI DESIGN) in Marthandam College of Engineering & Technology, (Anna University, Chennai.) Her area of interest includes digital design, VLSI design, etcno. 11, pp. 2481–2494, Nov. 2012.

- [7]. L. Yang and J. Yuan, "An arbitrarily skewable multiphase clock generator combining direct interpolation with phase error average," in Proc. IEEE Int. Symp. Circuit Syst., May 2003, vol. 1, pp. 25–28.

- [8]. M. S.-W. Chen, D. Su, and S. Mehta, "A calibration-free 800 MHz fractional-N digital PLL with embedded TDC," IEEE J. Solid-State Circuits, vol. 45, no. 12, pp. 2819– 2827, Dec. 2010.

- [9]. P. E. Su and S. Pamariti, "Fractional-N phase-locked-loopbased frequency synthesis: A tutorial," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 56, no. 12, pp. 881–885, Dec. 2009.

- [10]. R. B. Staszewski and P. T. Balsara, "All-digital PLL with ultra fast settling," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 2, pp. 181–185, Feb. 2007.

- [11]. R. Nonis, W. Grollitsch, T. Santa, D. Cherniak, and N. Da Dalt, "digPLL-Lite: A low-complexity, low-jitter fractional-N digital PLL architecture," IEEE J. Solid-State Circuits, vol. 48, no. 12, pp. 3134–3145, Dec. 2013.

- [12]. S. E. Meninger and M. H. Perrott, "A fractional-N frequency synthesizer architecture utilizing a mismatch compensated PFD/DAC structure for reduced quantizationinduced phase noise," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 50, no. 11, pp. 839–849, Nov. 2003.

- [13]. R.Dinesh, Dr.Ramalatha marimuthu," A Survey on ADPLL Components and their effects upon Power, Frequency and Resolution" in International Journal of Applied Engineering Research, Volume 11, Number 3 (2016) pp 1569-1574.

- [14]. R.Dinesh, Dr.Ramalatha marimuthu," A low power and fast locking ADPLL to enhance healthcare monitoring systems for elderly people", ARPN Journal of Engineering and Applied Sciences, Vol. 13, no. 6, march 2018.

**J.JESLIN JIJO** obtained her B.E (ECE) from Anna University Chennai. Currently she is doing M.E (VLSI DESIGN) in Marthandam College of Engineering & Technology, (Anna University, Chennai.) Her area of interest includes digital design, VLSI design, etc.

**Mr..R.Dinesh** has been in teaching for 14 years and currently working as Associate Professor in ECE in Marthandam College of Engineering &Technology, India. He has received the B.E degree in Electronics and communication from Bharathidasan University, India, M.E degree in Optical Communication from Anna

University, India and M.B.A degree from Madurai Kamaraj University, India. Currently he is doing PhD in VLSI. He has published 15 technical papers in International conferences and journal in the areas of optical communication, VLSI and signal processing. He is a life time member of ISTE. His research area of interest include, Low power VLSI, Clock Synchronization, ADPLL etc.