# **Digital Signal Processing**

The Impact of Convergence on Hardware Design Flow

# Kofi Appiah, Department of Computing and Informatics, United Kingdom Andrew Hunter

Abstract: Design and development of real-time, memory and processor hungry digital signal processing systems have for decades been accomplished on general-purpose microprocessors. Various attempts to improve the performance of these systems resulted in the use of dedicated digital signal processing devices like DSP processors and the former heavyweight champion of electronics design — Application Specific Integrated Circuits. The advent of RAM-based Field Programmable Gate Arrays has changed the DSP design flow. Software algorithmic designers can now take their DSP algorithms right from inception to hardware implementation, thanks to the increasing number of C/C++ hardware design flow. This has led to a demand in the industry for graduates with good skills in both electrical engineering and computer science. This paper evaluates the impact of technology on DSP-based designs, hardware design languages, and how graduate/undergraduate courses have changed to suit this transition.

Keywords: Digital Signal Processing, Application Specific Integrated Circuits, Field Programmable Gate Array, Augmented C/C++ design-flow

# Introduction

AST CHANGING STATE-OF-THE-ART technologies have had a great impact on electronic system design issues. The 1970s was the decade of semiconductors, which enabled the digital generation. This was followed by dynamic memory (DRAM) in the 1980s and then the microprocessor era in the 1990s, which made the word "Megahertz (MHz)" a common term in our everyday language [3]. The new millennium has made Digital Signal Processing the technology of focus with an expected exponential growth. Digital Signal Processing (otherwise referred to as DSP) is the branch of electronics that involves the representation, processing and manipulation of real-world signals in digital form [26]. DSP as a technology has been available to engineers for over two decades and was initially used in application areas where cost and performance were the ultimate goals [21]. This special technology can be found in almost all aspects of our daily lives; including but not limited to security systems (home or industrial), medical systems, telecommunications, consumer electronics, defence and aerospace.

DSP systems for the past decade have been implemented using the ubiquitous general-purpose microprocessors. The increasing demand by consumers of such systems for high-speed, resulted in the use of dedicated Digital Signal Processors also referred to as DSPs; a special type of general-purpose processor optimised for signal processing algorithms. The processing power of general-purpose processors has increased over the past years while their price decreases; thanks to Moore's law. This trend of increasing the clock-rate of the processor has two major drawbacks:

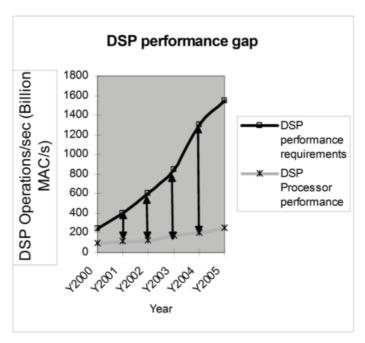

- Inability to meet the performance demand of today's electronic systems, as depicted in Figure 1.

- 2. High power consumption, unsuitable for battery-powered systems.

As the clock-rate of general purpose processor increases the processing requirement of DSP systems increase as well. This trend has overstretched the performance of DSPs to a point that they can no longer support the demand of today's systems – Hook's law applied to DSP. Power dissipation is important in almost all DSP-based consumer electronic devices; hence the high-speed, power-hungry DSPs become unattractive. For hardware acceleration and low power consumption, DSP designers had no option, other than the then heavyweight champion of electronic design [7], ASIC, sacrificing flexibility for performance.

$\bigcirc$

INTERNATIONAL JOURNAL OF TECHNOLOGY, KNOWLEDGE AND SOCIETY, VOLUME 1, 2005/2006 http://www.Technology-Journal.com, ISSN 1832-3669

© Common Ground, Kofi Appiah, Andrew Hunter, All Rights Reserved, Permissions: cg-support@commongroundpublishing.com

Figure 1: DSP Performance Requirements vs. General-Purpose DSP Processor Performance. Top-Down DSP Design Flow to Silicon Implementation [3].

Dedicated Digital Signal Processors and Application Specific Integrated Circuits have high disparities in term of flexibility and performance. Algorithmic designers in the DSP world have long been software engineers with little or no knowledge in hardware design, but rather software programming and mostly high-level mathematics needed for DSP. The only way software engineers could have their design implemented in hardware, for increased performance, was to pass their algorithms and specifications over to their hardware colleagues. These hardware engineers are much interested in the "how" of a technological phenomenon rather than the "why" and hence do not have the deep understanding of high-level mathematics needed in DSP [16]. This makes the hardware implementation from algorithmic level, through the register transfer level (RTL) to its final or silicon implementation error prone.

A hybrid reconfigurable computing architecture like Field Programmable Gate Array (FPGA) offers the necessary computing resources needed for today's DSP. There is an increasing need for DSPs to become more reconfigurable to meet future needs [8]. "The responses also make us believe that programmable logic is likely to dominate the digital design domain over the next decade" Kevin Morris [1] in a survey conducted by Xilinx in September 2004. The latest Dataquest reports show that 40% of ASIC designs in 2003 had less than 1 million gates, running at 500 MHz or less [11]. Current FPGAs from key players like Xilinx and Altera have as many as 8 million gates, running at 500MHz or more. Unless power usage is very critical or production volumes are extraordinary, it is becoming increasingly hard to justify the use of ASIC over FPGA.

Technological advancements in Field Programmable Gate Arrays (FPGAs) over the past decade, open new paths for DSP design engineers. FPGAs maintain the advantages of the high specificity of the ASIC while avoiding the high development costs and inability to make design modifications after production. They also add design flexibility and adaptability with optimal device utilization conserving both board space and system power, which is often not the case with DSP chips. When the design demands more than 100 MIPS, time-to-market is critical or design adaptability is crucial, the use of reconfigurable architecture becomes inevitable.

New implementation platforms call for new design processes for efficiency and accuracy. As the timeto-market has become very critical in the design and implementation of DSPs, the conventional method of implementing DSP designs on ASICs is highly unacceptable. Designing with multimillion-gate FP-GA for time constraint systems, therefore require a new breed of engineers with unique DSP skills. This is in line with the optimistic view on the impact of new technologies on society and employment pattern. To the optimists, new technologies come with new jobs that replace existing ones and new skill requirements - "reskilling" [36].

# **DSP Design Options**

Digital Signal Processing can be implemented on four major platforms: the use of conventional microprocessor, dedicated DSP chip, reconfigurable Field Programmable Gate Array and dedicated Application Specific Integrated Circuit. Clock speed or instruction cycle time is not the only contributing factor for the evaluation of the total performance of a particular DSP platform [25]. Rather the bus architecture, input/output (IO) hardware and the software algorithm upon which the implementation is based must be considered. Table 1 gives a comparison between these platforms in terms of flexibility and performance.

DSP design typically starts with the system specification or algorithmic design, which is followed by a decision on a platform and finally the actual implementation. Each platform requires a specific design route. Knowledge of the final implementation architecture is required for a successful and highly optimised DSP design.

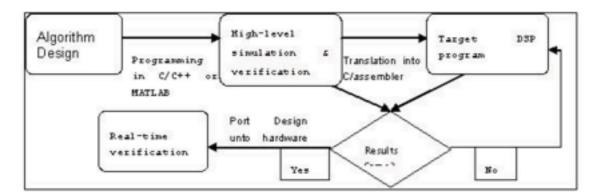

Designing DSP-based systems with a microprocessor or dedicated DSP chip is cheaper and much easier than the other methods, see figure 2. This starts with the design of the actual algorithm followed by simulation and verification of the algorithm with a high-level programming language. It is then followed by a translation of the algorithm into code acceptable to the final DSP platform, usually C or assembler. The functionality of the DSP code is verified with the high-level program as reference. The design is then ported to the final hardware for final debugging and verification.

|                   | Flexibility     |                   | Performance           |                        |                          |

|-------------------|-----------------|-------------------|-----------------------|------------------------|--------------------------|

|                   | Programmability | Reconfigurability | Area Utiliza-<br>tion | Power Consump-<br>tion | Computational throughput |

| ASIC <sup>1</sup> | Low             | Low               | Low                   | Low                    | High                     |

| DSP               | Medium          | Medium            | High                  | High                   | Low                      |

| MicroP<br>(P)     | Medium          | High              | High                  | High                   | Low                      |

| FPGA              | Medium          | High              | Low                   | Medium                 | Medium                   |

Table 1: Signal Processing Implementation Platform Comparison.

<sup>1</sup> Source : Jing Ma, Signal and Image Processing Via Reconfigurable Computing, (University of New Orleans: Workshop on Information and Systems Technology - May 2003)

Figure 2 : Microprocessor/DSP Chip Based DSP-Design Flow. Digital Signal Processing and Applications [25].

This design flow is very short and prone to fewer errors, as the same person who designs the algorithm does the hardware implementation. The performance of the resulting system in term of speed makes them unattractive.

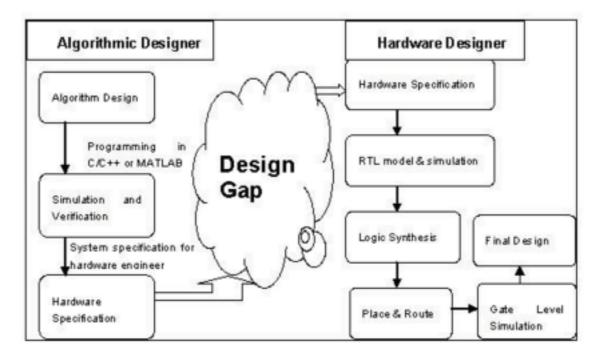

Designing for Application Specific Integrated Circuits (ASIC) comes in two disjoint levels, see figure 3. A system or algorithmic designer handles the first level while a hardware engineer handles the second level. The algorithmic designer describes and simulates the implementation in a high-level programming language like C/C++ or MATLAB. This design is then sent to a hardware designer who will then convert the specification into Register Transfer logic (RTL) model, by converting all floating-point operation into fixed-point. The model is then simulated for similarity with the high-level design. This design flow is not only error prone but time consuming as well.

Figure 3 : A Typical Application Specific Integrated Circuit (ASIC) Design Flow.

Many hardware designers have taken to FPGA computing for their DSP-based designs for the following important reasons [10], [Xilinx]:

- 1. Fast time-to-market

- 2. Non-recurring engineering cost

- 3. Efficient use of time and

- 4. Satisfying human wants.

The low price/performance ratio of today's high-end FPGAs [9] makes them very attractive for the development of DSP systems. Until recently, the FPGA design solutions have been unavailable to software or algorithmic designers with little or no skills in computer hardware.

Many design tools have floored the EDA market, taking advantage of the short FPGA design flow. Tools based on high-level languages like C/C++ and MATLAB very common to DSP designers, have been available on the market recently. This has helped DSP algorithmic designers to take full advantage of FPGA solutions without a steep learning curve [10]. The C programming language has been the language of choice for most DSP applications, for its portability and compactness [4]. C as a typical language for general-purpose computers lacks the specialised features like parallelism, wires, clocking and delays, required in hardware design [24]. To extend the capabilities of C/C++ for hardware designs, many tool developers have turned to augmented C/C++ [26]; tools which extend the capabilities of C for hardware purposes. Typical examples are SystemC, SystemVerilog, Impulse-C, Handel-C and AccelChip (based on MATLAB).

Impulse-C is designed to simplify the development of highly parallel, processing-intensive applications, including applications that require a mix of hardware and software processing resources, or applications in which specific processes must be interfaced to other hardware and/or software components to form a complete system. The benefit of using Impulse-C is that it gives you more opportunities to experiment with alternative algorithmic approaches, a faster path to a working prototype and greater opportunities to improve system-level performance through iterative design methods [30].

Another big player in the C/C++ augmentation for ASIC and FPGA design capture, simulation and synthesis is Celoxica [31]. Celoxica's Handel-C has special statements to support concepts like clocks, pins, parallelism, interfaces, RAM and ROM. The numerous libraries that come with the language makes it much easier to interact with their RC-series FPGA boards. Designing code with Handel-C is fairly straightforward to any conventional C programmer. This makes it easier for any software engineer, adopt and use Handel-C for hardware development. Handel-C is seen as a programming language rather than a hardware description language like VHDL and Verilog.

AccelChip DSP synthesis tool, which is based on MATLAB design flow, has made significant impact in the FPGA-DSP design environment. The Accel-Chip DSP synthesis tool directly reads in MATLAB (a popular DSP algorithm design tool from The MathsWorks Inc.) models and automatically outputs synthesizable RTL models and simulation testbenches in VHDL or Verilog. This provides DSP designers with a significant reduction in design labour and time, elimination of misinterpretations and costly design rework, automatic verification of the hardware implementation, and the ability of systems engineers and algorithmic developers to perform architectural exploration in the early phases of their development cycle [3].

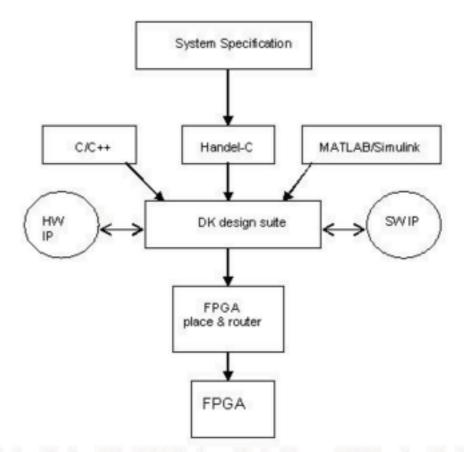

The simple and short design flow exhibited by Impulse-C and Handel-C is shown in figure 4. The entire design is described in C; taking advantage of the added hardware support feature as well as the libraries supplied with the EDA tool. A typical example is the PAL library that comes with Celoxica's DK suite for interacting with devices, external to the Field Programmable Gate Array. The design is then compiled into a Hardware Descriptive Language (HDL) or an Electronic Design Interchange Format (EDIF) suitable for a particular vendor's place and route tool.

Pessimists of new technologies describe the emerging short-hardware-design flow for DSP applications as detrimental. They argue that there will be an overall decline in job opportunities and thus, leading to large-scale and possibly permanent unemployment. This is the case, when a single engineer with the aid of automated design tools is able to accomplish the task of two engineers; in this case the algorithmic designer and the hardware designer. The use of EDA tools also results in deskilling, as technology downgrade hardware design engineers.

Figure 4 : Impulse-C and Handel-C Hardware Design Flows. WWW.Impulsec.Com[30] and WWW.Celoxica.Com[31]

#### **FPGA-Based Design Requirements**

Designing FPGA-based systems, using Hardware Descriptive Languages (HDLs) like VHDL and Verilog is very similar to building hardware or arrays of gates as compared to programming in software. Thus the designer or developer is expected to focus on using hardware components rather than software constructs, to avoid using too many gates and highly inefficient chip and logic layouts. It is becoming increasingly hard to justify an inefficient hardware implementation of an algorithm over the same algorithm written in C and running on today's highspeed microprocessors. Thus simply implementing an algorithm in hardware does not necessary make them faster than their software implementation.

Finding a way to help FPGA designers skip the long and time consuming HDL-based design without missing a beat in productivity is a key to gaining acceptance [6]. Even though many high-level languages have been proposed as system design languages (C/C++, Java, and MATLAB) [22], most of these languages would produce very large logic designs, if the designer has very little knowledge of the hardware architecture. Most of these soft-

ware/hardware tool developers argue that in this era where chips are very cheap, hardware efficiency is no longer important. Unfortunately, this is not always true, as most FPGA designs would have to meet timing, power and architectural constraints. Therefore, a uniquely skilled DSP/logic designer is generally required to construct an FPGA design.

Design and implementation of high-speed and low-powered DSPs to meet the short time-to-market requirements of today's increasing consumer electronics require a broad knowledge in areas traditionally not covered in a single discipline. These areas include Computer Science, Electrical and Electronic Engineering, Business, Social Science, Mathematics and others. This has made it very difficult over the past years to train students in a single discipline to effectively design and implement high-speed Digital Signal Processing systems.

Attempts by various academic institutions in training students for the always-changing DSP industry resulted in a number of disciplines with no clear bounds between them. This means students involved in such disciplines had much more workload. Computer Science is concerned with the theoretical and algorithmic aspects of computing. Electrical Engineering is concerned with the physical aspect of electronics whiles Software Engineering is an engineering discipline that is concerned with all aspects of software production from early stages of system specification to maintaining the system after it has gone into use [35]. Thus Digital Signal Processing designs, call for a cross-pollinated engineer with a multidisciplinary design skills. Such an engineering discipline will embody the science and technology of design, construction, implementation, and maintenance of software and hardware components of modern computing systems and computer-controlled equipments.

The Computer Society of the Institute for Electrical and Electronic Engineers (IEEE-CS) and the Association for Computing Machinery (ACM) by means of drawing a clear boundary between the related disciplines (Computer Science and Electrical Engineering) established a Joint Task Force on Computing Curricula to undertake a major review of the curriculum guidelines for undergraduate programs in computing [32]. The three-year degree program that resulted from this Task Force's report (Computing Curricula for Computer Engineering -CCCE) is computer engineering, which lies between computer science and electrical engineering.

Computer engineering is solidly grounded in the theories and principles of computing, mathematics, science, and engineering and it applies these theories and principles to solve technical problems through the design of computing hardware, software, network, and processes [33]. The CCCE report published in 2004(CCCE-04), requires all computer engineers to exhibit the following characteristics:

- Professionalism as the public has entrusted in engineers a level of responsibility based on the systems they design, engineers have to exercise the utmost conscientiousness when designing.

- Ability to design to seek and exploit new and improved products.

- Breadth of Knowledge that enables the engineer to span the entire fields of study.

Engineers in other fields like electrical and electronic engineering are also expected to possess the same characteristics, with the exception of the breadth of knowledge require by a computer engineer.

To clarify the similarity in workload of a computer-engineering student and an electronic engineering student, we evaluate on a common computer-related course like computer organization and architecture. Typically electrical engineers spend time in resolving complex communication and synchronisation issues when dealing with concepts of parallelism using array of processors. A computer engineer resolving a similar issue for the purpose of DSP will use the widespread Field Programmable Gate Array (FPGA) without having to worry about complex communication and synchronisation issues. FPGAs, which were originally used primarily for glue logic, now have distributed memory and multiplication resources that are capable of handling computational tasks directly [34]. An electrical engineer will typically program in Hardware Descriptive Language (HDL) like VHDL (Very high-speed integrated circuit Hardware Descriptive Language), which is much harder as compared to a computer engineer who will program in a high-level system design language like Handel-C. Details of common courses and their content, taken by computer engineer, computer scientist and electrical engineer showing their difference have been given in [33].

Unlike professions such as law and medicine, engineering generally does not require an advanced degree for employment in the field. As a means to allow engineers and scientists from fields other than computer engineering to take full advantage of new technologies and their design requirements, several universities have started graduate degree course in System-on-Chip (SoC) Design.

The Institute for System Level Integration (ISLI) started the first postgraduate program in system-onchip aimed specifically at system level integration. The emergence of new generation of design technologies and methodologies, like development of Electronic Design Automation (EDA) tools, systems partitioning between software and hardware and design verification have made this postgraduate course very popular.

The SOCWARE design cluster including the Royal Institute of Technology (KTH), Linkoping University and the Lund University all in Sweden have for the past four years been running masters programs in System-on-Chip Design. The key aspects of these courses have been the design methods, architectures and circuit design towards system level integration (SLI). The content of the program is been driven by:

- Interdisciplinary approach ranging from deep submicron and digital noise issues to formal techniques and system modelling.

- Practical competence in the form of small projects undertaken in worlds-leading high-tech companies and hands-on laboratory sessions for industrial practice and academic expertise.

Similarly, the Graz University of Technology, Austria in 2002 started a postgraduate programme in SoC Design. Students of this program take courses in concurrent systems, hardware/software co-design and how to model hardware-software systems. Their modules also emphasize on the use of IP cores as well as software libraries, as today's systems-onsilicon contain more and more software. The post-

graduate course in Embedded Systems Design at the Advanced Learning and Research Institute, Lugano in Switzerland and the newly designed master's programme in SoC Design at the faculty of engineering, University of Sheffield in England are no different from the above programmes. We are beginning an era where the system designer is the Integrated Circuit (IC) designer, the digital designer, the analogue designer and the system integrator [28]; this therefore calls for graduates who are well prepared for career challenges ahead of them and hence has spark the design of new undergraduate/graduate programmes. Stewart et al [27] also pointed out the importance of integrating electrical engineering and computer science courses to aid advanced DSP designs in both industrial and educational institutions.

## Conclusion

Digital Signal Processing is widely used in almost all aspects of our daily life, yesterday's wants have become today's needs and this trend in expected to continue throughout this millennium [37]. The increasing need to meet human satisfaction coupled with the high competition amongst electronic design companies has triggered the use of FPGAs in the DSP industry. The use of sophisticated EDA tools for FPGA designs give pessimists the impression that new technologies results in deskilling as well as unemployment. Optimists have the view that these technologies create new jobs, which in effect replaces old ones and hence the employment rate remains unchanged. Concerning skill requirement, optimists are of the view that new graduates as well as skilled engineers are required to effectively utilise the capabilities of these technologies and thus causing "reskilling". A third group with mixed views on new technologies has emerged as a result of convergence between the optimists and the pessimist. Long-term optimists or the short-term pessimists believe that new technologies will cause considerable displacement in certain sectors; they maintain it should be for short term.

Programming FPGA with high-level languages like C, Java and MATLAB have changed the DSP design flow and also added to the skill requirements of today's DSP development. We have explained in this paper the requirements in today's DSP industry and how several universities have restructured their curriculum to teach courses in DSP designs and hardware architectures, to prepare graduates for the always-changing industries. A typical example is the new curriculum, computer engineering which has emerged as a convergence between computer science and electronic engineering. The software/hardware designs or the software-hardware co-designs have significantly shortened the DSP design flow.

#### References

Associated Compiler Expert (ACE), "Programming DSPs in High-Lebel Languages", *TechOnLine*, November 2002. Bouldin, Don, Warren Snapp, Paul Haug, David Sunderland, Roger Brees, Carl Sechen, and Wayne Dai. "ASIC by Design",

IEEE Circuit & Devices magazine August 2004.

- Bursky, Dave, and Ashok Bindra. "Digital ICs: DSP", ED Online January 2002.

- Caporossi, Dino. "FPGA Designers Are Heavyweights Too", ED Online, August 2003.

- Christopher Rowe and Jane Thompson, "People and Chips: the human implication of Information Technology", *McGraw-Hill* 1996.

- "Computing Curricula Computer Engineering, Final Report", Report of the IEEE-CS/ASM Joint Task Force on Computer Engineering, 2004.

- Dick, Chris. "FPGAs: The high-end alternative for DSP applications", DSP Engineering Spring 2000.

- ED Online. "FPGA High-Level Design Methodology Comes Into its Own", June 1999.

- Edwards, John. "DSP Technology gains importance in all major market segments", Boards and Solutions March 2003.

- Frantz, Gene A. "Preparing EE's for the 21 st Century with a 20th Century Education", *Signal Processing Education Workshop* – 2000.

- Feist, Tom. "What's the right language for DSP system-level Design?" *FPGA and Programmable Logic Journal*, November 2003.

- Ganousis, Dan. (AccelChip, Inc.), "Top-Down DSP design flow to Silicon Implementation", System Design Frontier July 2004.

- Habibi, Ali, and Sofiene Tahr. "A Survey on System-On-a-Chip Design Languages", *IEEE workshop on SOC for Real-Time Applications* 2003.

- Kinast, Allen. "Designing Digital Signal Processing with FPGA", White Paper Mentor Graphics February 2003.

- Kairus, Jaakko, Juha Forsten, Matti Tommiska and Jorma Skytta. "Bridging the GAP between future software and hardware Engineers: A case study using the NIOS softcore processor", *ASEE/IEEE Frontiers in Education Conference* November 2003.

- Kaplan, Ian. "C as a Hardware Design Language", January 2002.

- Konsbruck Robert Lee, "Impact of Information Technology on Society in the new Century", 2002.

- Leibson, Steven. "Tailored Processors hit closer to performance aims", COTS Journal June 2003.

Maliniak, David. "An Easier Path to RTL for DSP Algorithms", ED Online May 2004.

Maliniak, David. "DSP development flow Evolves to next level", ED Online October 2004.

Maki, Larry. "Programming FPGA Systems Doesn't Have to be difficult", ED Online June 2004.

- Ma, Jing. "Signal and Image Processing Via Reconfigurable Computing", 2003 http://www.impulsec.com/ http://www.celox-ica.com/

- Maxfield, Clive. "The Design Warrior's guide to FPGAs: Devices, Tools and Flows", Newnes Publication 2004.

- Morris, Kevin. "Engineers Speak Out-The voice of the FPGA Design Community", FPGA Programmable Logic Journal-October 2004.

- Moussavi, Massoud. "Digital Signal Processing in Electrical Engineering Technology programs"

- Ohr, Stephan. "DSP design tools shift to SystemC", EE Times march 2002.

- Pentek Inc. "C-Language Programming for DSP", 2003

Raje, Salil. "Catching the FPGA productivity wave", ED Online October 2004.

- Spivey, Gary, Shuvra Bhattacharyya, and Kazuo Nakajima. "Logic Foundry: Rapid Prototyping on FPGA-based DSP systems", January 2003.

- Stranneby, Dag, and William Walker. "Digital Signal Processing and Applications", Newnes Publication- 2004.

- Stewarts, R. W, J. D. Quayle, D. Garcia-Alis and S. Weiss. "Digital Signal Processing Education: Technology and Tradition", Signal Processing Education Workshop - 2000.

- Soldan, David L, Victor P. Nelson, Andrew McGettrick, John Impagliazzo, Pradip Srimani, Mitchell D. Theys and Joseph L. A. Hughes. "Development of The Model Curriculum for Computer Engineering", ASEE/IEEE Frontiers in Education Conference – October 2004.

Sommerville, Ian "Software Engineering", Pearson Education Limited 2004.

- Trevor Jones, "Microelectronics and Society", The Open University Press 1980.

- Wood, Sally L. and Chris Dick. "Concepts of Parallelism in an Introductory Computer Architecture Course with FPGA Laboratories", *ASEE/IEEE Frontiers in Education Conference* October 2004.

- Young, Duncan. "FPGAs' impact on next generation sensor digital signal processing", *Military Technology Insider* June 2004.

## About the Authors

Mr Kofi Appiah

Department of Computing and InformaticsUnited Kingdom

Andrew Hunter

Head of Department, Dept. Computing and Informatics, University of Lincoln, Brayford Pool, Lincoln, LN6 7TS.