#### Technische Universität Dresden

#### Fabrication and Characterization of AlGaN/GaN Metal-Insulator-Semiconductor High Electron Mobility Transistors for High Power Applications

M. Sc.

#### **Anthony Calzolaro**

der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades

#### Doktoringenieur

(Dr.-Ing.)

genehmigte Dissertation

Vorsitzender: Prof Dr.-Ing. Steffen Bernet Gutachter: Prof. Dr.-Ing. Thomas Mikolajick

Gutachter: apl. Prof. Armin Dadgar

Tag der Einreichung: 14.09.2021 Tag der Verteidigung: 3.02.2022

A Tata e Mathieu Per la tenacia e la purezza

#### **Abstract**

AlGaN/GaN metal-insulator-semiconductor high electron mobility transistors (MIS-HEMTs) are promising candidates for next generation high-efficiency and high-voltage power applications. The excellent physical properties of GaN-based materials, featuring high critical electric field and large carrier saturation velocity, combined to the high carrier density and large mobility of the two-dimensional electron gas confined at the AlGaN/GaN interface, enable higher power density minimizing power losses and self-heating of the device. However, the advent of the GaN-based MIS-HEMT to the industrial production is still hindered by technological challenges that are being faced in parallel. Among them, one of the biggest challenge is represented by the insertion of a gate dielectric in MIS-HEMTs compared to Schottky-gate HEMTs, which causes operational instability due to the presence of high-density trap states located at the dielectric/III-nitride interface or within the dielectric. The development of a gold-free ohmic contact technology is another important concern since the high-volume and cost-effective production of GaN-based transistors also depends on the cooperative manufacturing of GaN-based devices in Si production facilities, where gold represents an undesidered source of contamination. In fact, even though over the past years there have been multiple attemps to develop gold-free ohmic contacts, there is still no full understanding of the contact formation and current transport mechanism.

The first objective of this work was the investigation of a gold-free and low-resistive ohmic contact technology to AlGaN/GaN based on sputtered Ta/Al-based metal stacks annealed at low temperatures. A low contact resistance below 1  $\Omega$  mm was obtained using Ta/Al-based metal stacks annealed at temperatures below 600 °C. The ohmic behavior and the contact properties of contact resistance, optimum annealing temperature and thermal stability of Ta/Al-based contacts were studied. The nature of the current transport was also investigated indicating a contact mechanism governed by thermionic field emission tunneling through the AlGaN barrier. Finally, gold-free Ta/Al-based ohmic contacts were integrated in MIS-HEMTs fabricated on a 150 mm GaN-on-Si substrate, demonstrating to be a promising contact technology for AlGaN/GaN devices and revealing to be beneficial for devices operating at high temperatures.

The optimization of the MIS-gate structure in terms of trap states at the dielectric/III-nitride interface and inside the dielectric in MIS-HEMTs using atomic layer deposited (ALD)  $Al_2O_3$  as gate insulator was the second focus of this work. First, the MIS-gate structure was improved by an  $O_2$  plasma surface preconditioning applied before the  $Al_2O_3$  deposition and by an  $N_2$  postmetallization anneal applied after gate metallization, which significantly reduced trap states at the  $Al_2O_3$ /GaN interface and within the dielectric. Afterwards, the effectiveness of these treatments was demonstrated in  $Al_2O_3$ -AlGaN/GaN MIS-HEMTs by pulsed current–voltage measurements revealing improved threshold voltage stability. Lastly, it was shown that also the lower annealing temperatures used for the formation of Ta/Al-based ohmic contacts, processed before gate dielectric deposition, are beneficial in terms of trap states at the ALD-Al $_2O_3$ /GaN interface, representing a new aspect to be considered when using an ohmic first fabrication approach.

## **Contents**

| 1 | Intr                     | oducti         | on                                                                                                    | 1  |

|---|--------------------------|----------------|-------------------------------------------------------------------------------------------------------|----|

| 2 | Fun<br>2.1<br>2.2<br>2.3 | Group<br>AlGal | ntals of heterostructure field-effect transistors  O III-Nitrides                                     | 5  |

| 3 | Pro                      | perties        | of epitaxial material and process modules for high device performance                                 | 13 |

|   | 3.1                      | AlGal          | N/GaN epitaxial layers on Si                                                                          | 13 |

|   | 3.2                      | MIS-g          | ate HEMTs                                                                                             | 15 |

|   |                          | 3.2.1          | Gate dielectrics                                                                                      | 16 |

|   |                          | 3.2.2          | Dielectric trapping effects                                                                           | 18 |

|   | 3.3                      | Ohmi           | c contacts to 2DEG                                                                                    | 19 |

|   |                          | 3.3.1          | Basic physics of ohmic contacts                                                                       | 19 |

|   |                          | 3.3.2          | Formation of ohmic contacts to AlGaN/GaN                                                              | 22 |

|   |                          | 3.3.3          | Au-free ohmic contacts to AlGaN/GaN                                                                   | 23 |

| 4 | Exp                      | erimer         | ntal methods                                                                                          | 25 |

|   | 4.1                      | Proces         | ssing technology                                                                                      | 25 |

|   |                          | 4.1.1          | Mesa etching                                                                                          | 25 |

|   |                          | 4.1.2          | Surface preconditioning                                                                               | 26 |

|   |                          | 4.1.3          | Physical vapor deposition                                                                             | 26 |

|   |                          | 4.1.4          | Atomic layer deposition                                                                               | 28 |

|   |                          | 4.1.5          | Thermal annealing                                                                                     | 28 |

|   | 4.2                      | Fabric         | eation of test structures                                                                             | 29 |

|   |                          | 4.2.1          | Ohmic contacts                                                                                        | 30 |

|   |                          | 4.2.2          | MISH capacitor                                                                                        | 31 |

|   |                          | 4.2.3          | MIS-HEMT                                                                                              |    |

|   | 4.3                      | Electri        | ical characterization                                                                                 |    |

|   |                          | 4.3.1          | Transfer length method                                                                                |    |

|   |                          | 4.3.2          | Frequency-dependent capacitance-voltage method                                                        |    |

|   |                          | 4.3.3          | Pulsed measurements of $V_{\text{th}}$ instability under forward gate bias stress $\ \ldots \ \ldots$ | 39 |

| 5 | Lov                      | v-temp         | perature Au-free Ta/Al-based ohmic contacts                                                           | 42 |

|   | 5.1                      | Ta/Al          | -based ohmic contacts                                                                                 | 42 |

|   |                          | 5.1.1          | AlN spacer layer                                                                                      | 44 |

|   |                          | 5.1.2          | Capping metal layer                                                                                   | 46 |

|   |                          | 5.1.3          | Nature of current transport                                                                           | 51 |

|     |        | 5.1.4 Impact of Ta/Al thickness ratio                                              | . 55 |

|-----|--------|------------------------------------------------------------------------------------|------|

|     | 5.2    | Comparison to high-temperature and Au-containing Ti/Al-based ohmic contacts        | . 57 |

|     |        | 5.2.1 Contact resistance homogeneity                                               | . 58 |

|     |        | 5.2.2 Surface morphology and edge acuity                                           | . 59 |

|     |        | 5.2.3 Thermal stability of sheet resistance                                        | . 60 |

|     |        | 5.2.4 Mechanism of current transport                                               | . 63 |

|     | 5.3    | Summary                                                                            | . 65 |

| 6   | Eng    | ineering and optimization of MIS-gate module                                       | 67   |

|     | 6.1    | Surface preconditioning                                                            |      |

|     |        | 6.1.1 GaN surface morphology                                                       | . 68 |

|     |        | 6.1.2 Influence on ALD-Al <sub>2</sub> O <sub>3</sub> /III-nitride interface       | . 69 |

|     | 6.2    | Postmetallization annealing                                                        | . 72 |

|     |        | 6.2.1 Effects on ALD-Al <sub>2</sub> O <sub>3</sub> /III-nitride interface         |      |

|     |        | 6.2.2 Impact of annealing temperature                                              | . 74 |

|     | 6.3    | Influence of ohmic contacts annealing                                              | . 78 |

|     | 6.4    | Summary                                                                            | . 81 |

| 7   | Perf   | formance of AlGaN/GaN MIS-HEMTs                                                    | 82   |

|     | 7.1    | Au-free Ta/Al-based ohmic contacts in MIS-HEMTs                                    | . 82 |

|     |        | 7.1.1 DC characteristics                                                           | . 83 |

|     |        | 7.1.2 Influence of ohmic contacts at high-temperature operation                    | . 86 |

|     | 7.2    | MIS-HEMTs with optimized ALD-Al <sub>2</sub> O <sub>3</sub> /III-nitride interface |      |

|     | 7.3    | Summary                                                                            | . 90 |

| 8   | Con    | nclusions                                                                          | 92   |

| Bi  | bliog  | graphy                                                                             | 96   |

| Li  | st of  | symbols                                                                            | 109  |

| Li  | st of  | abbreviations                                                                      | 113  |

| A   | ckno   | wledgments                                                                         | 115  |

| Cı  | arrici | ulum vitae                                                                         | 116  |

| Li  | st of  | publications                                                                       | 117  |

|     |        | ation of Authorship                                                                | 118  |

| _ • | LIMI   |                                                                                    | -10  |

# **List of Figures**

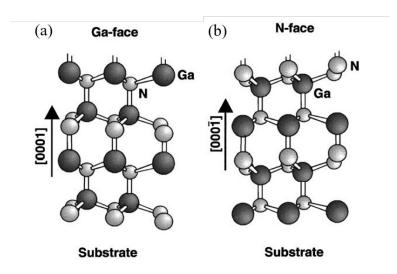

| 2.1 | Crystal structure of wurtzite (a) Ga-face and (b) N-face GaN, taken from [21]                           | 4  |

|-----|---------------------------------------------------------------------------------------------------------|----|

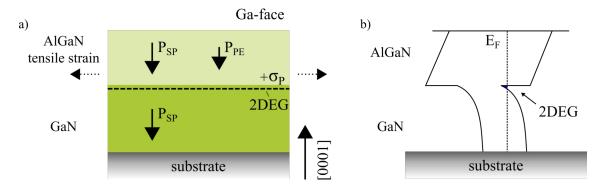

| 2.2 | (a) Spontaneous polarization and piezoelectric polarization and induced interface                       |    |

|     | charges and 2DEG in Ga-face tensile strained AlGaN/GaN heterostructure. $P_{SP}$                        |    |

|     | denotes the spontaneous polarization and P <sub>PE</sub> the piezoelectric polarization. (b)            |    |

|     | Schematic band diagram of AlGaN/GaN heterostructure illustrating the electron                           |    |

|     | accumulation and formation of 2DEG located in the GaN at the AlGaN/GaN interface.                       | 6  |

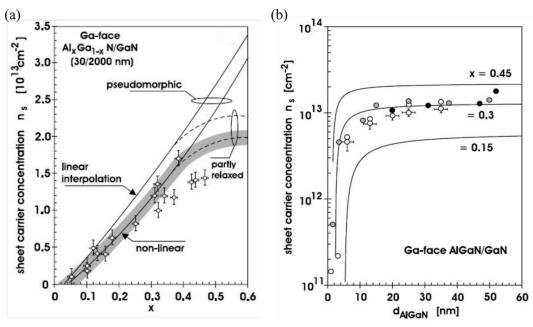

| 2.3 | Dependence of the 2DEG sheet carrier concentration $n_s$ on (a) the Al content $x$ and                  |    |

|     | (b) the thickness of the $Al_xGa_{1-x}N$ barrier layer $d_{AlGaN}$ , taken from [21]. In (a), the       |    |

|     | theoretical predictions (solid lines) are compared to experimental data (symbols).                      |    |

|     | The sheet carrier concentration is calculated using a linear interpolation of the                       |    |

|     | physical properties of the binary compounds (upper solid curve) and considering                         |    |

|     | the nonlinear behaviour of piezoelectric and spontaneous polarization (lower solid                      |    |

|     | curve). The grey area represents the uncertainty of the calculated values of $n_s$ . The                |    |

|     | dashed lines depicts the dependence of $n_s$ on the alloy composition taking into                       |    |

|     | account the relaxation of the $Al_xGa_{1-x}N$ barrier with increasing $Al$ content                      | 7  |

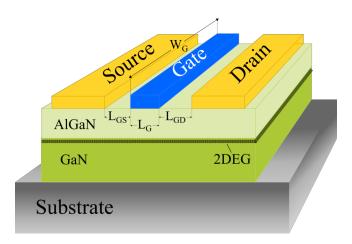

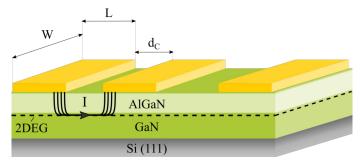

| 2.4 | Schematic of AlGaN/GaN HEMT device. W <sub>G</sub> indicates the gate width of the device.              |    |

|     | $L_{GS}$ is the gate-to-source distance, $L_{G}$ is the gate length and $L_{GD}$ is the gate-to-drain   |    |

|     | distance                                                                                                | 8  |

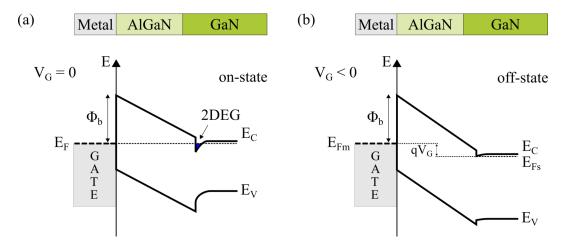

| 2.5 | Schematic of band energy diagrams (a) under zero gate voltage and (b) under                             |    |

|     | negative gate bias. In (a) the 2DEG conductive channel is formed at the AlGaN/GaN                       |    |

|     | interface. $E_{C}$ is the conduction band minimum, $E_{V}$ the valence band maximum,                    |    |

|     | $E_{Fm}$ the Fermi level in the metal, $E_{Fs}$ the Fermi level in the semiconductor, $\Phi_b$ the      |    |

|     | Schottky barrier height and $V_G$ the gate voltage                                                      | 9  |

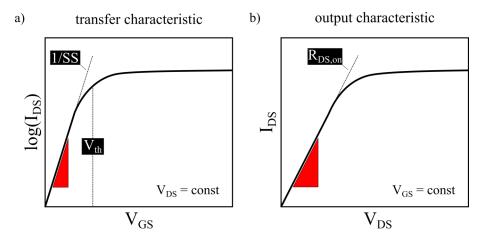

| 2.6 | Schematic of HEMT (a) transfer and (b) output characteristics. The device parameters                    |    |

|     | threshold voltage V <sub>th</sub> , subthreshold slope SS and on-state drain-to-source resistance       |    |

|     | 20/01.                                                                                                  | 11 |

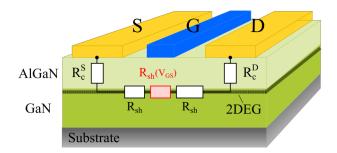

| 2.7 | Schematic of the resistive elements contributing to the R <sub>DS,on</sub> of an AlGaN/GaN              |    |

|     | HEMT device                                                                                             | 12 |

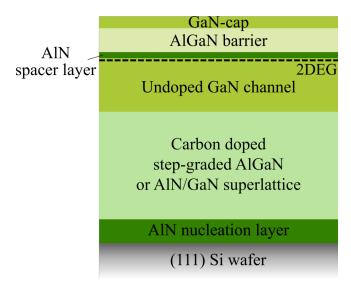

| 3.1 | Schematic cross-section of the typical epitaxial layer structure used for the manufac-                  |    |

|     |                                                                                                         | 14 |

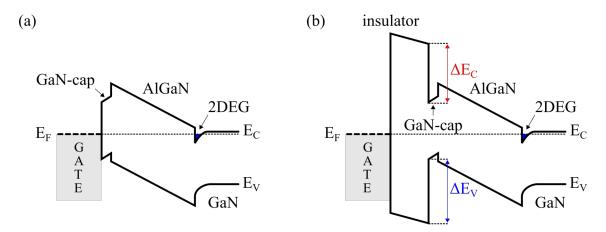

| 3.2 | Comparison of band diagrams of (a) Schottky-gate and (b) MIS-gate without gate                          |    |

|     | voltage applied. E <sub>C</sub> and E <sub>V</sub> are the conduction and valence bands of GaN, respec- |    |

|     | tively. $\Delta E_C$ and $\Delta E_V$ are the conduction and valence band offsets of GaN with respect   |    |

|     | to the insulator. $E_F$ denotes the Fermi energy                                                        | 15 |

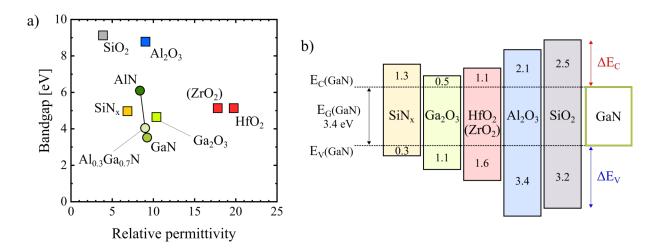

| 3.3  | (a) Energy bandgap versus permittivity for various insulators and GaN compounds. (b) Conduction and valence band offsets, $\Delta E_{C}$ and $\Delta E_{V}$ respectively, of various dielectric materials with respect to GaN, calculated by Robertson and Falabretti.[56] The conduction band $E_{C}$ and valence band $E_{V}$ of GaN are marked as dashed lines.                                                                                   |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |

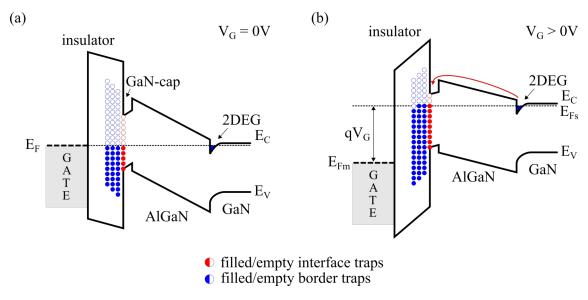

| 3.4  | Schematic band diagrams of the GaN-capped AlGaN/GaN heterostructure with insulator as gate dielectric at (a) zero bias ( $V_G = 0 \text{ V}$ ) and (b) under forward bias ( $V_G > 0 \text{ V}$ ). Electrons can overcome the AlGaN barrier from the 2DEG channel and be trapped in the states located at the insulator/GaN interface or within the insulator. $E_F$ denotes the Fermi energy at 0 V gate voltage, while with a gate voltage applied |    |

|      | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18 |

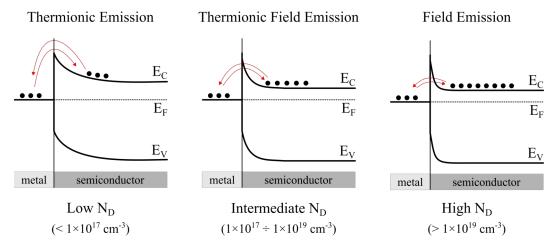

| 3.5  | Schematic illustration of the different carrier transport mechanisms through a metal/n-type semiconductor barrier for different doping level $N_D$                                                                                                                                                                                                                                                                                                   | 20 |

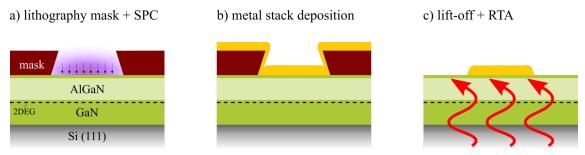

| 4.1  | Schematic fabrication process for ohmic contacts used in this thesis                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

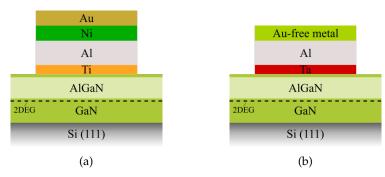

| 4.2  | Schematic of the multilayer metal stacks used in this work to fabricate ohmic contacts to AlGaN/GaN heterostructures: (a) conventional Ti/Al/Ni/Au contact, (b)                                                                                                                                                                                                                                                                                      |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

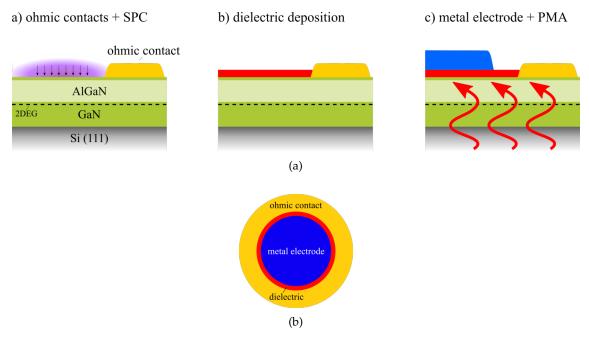

| 4.3  | (a) Schematic fabrication process and (b) top view of circular MISH capacitors used                                                                                                                                                                                                                                                                                                                                                                  |    |

| 4.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

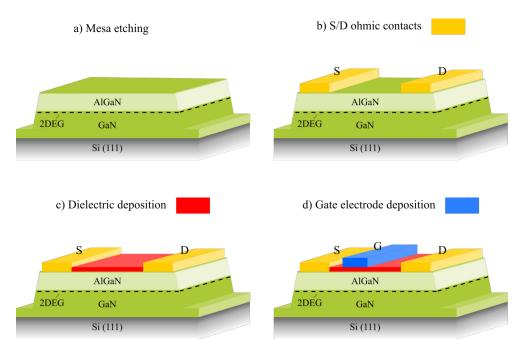

| 4.4  | Schematic fabrication process flow for MIS-HEMTs used in this thesis. The letters G,                                                                                                                                                                                                                                                                                                                                                                 | 32 |

| 4.5  | S and D represent the gate, source and drain electrodes, respectively Schematic of a TLM test structure with the current flowing between two adjacent                                                                                                                                                                                                                                                                                                | 32 |

| 1.0  | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

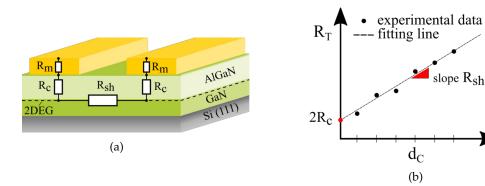

| 4.6  | (a) Schematic of the different resistive contributions of Equation 4.1. $R_m$ represents                                                                                                                                                                                                                                                                                                                                                             | -  |

|      | the metal pad resistance which is not taken into account because it is usually much smaller than other contributions. (b) Method to extract the contact resistance and                                                                                                                                                                                                                                                                               |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

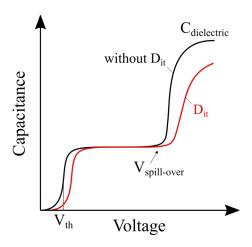

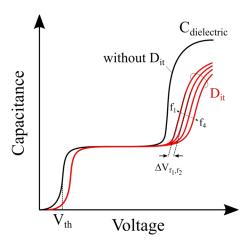

| 4.7  | Schematic C–V characteristics of a dielectric/GaN/AlGaN/GaN capacitor without                                                                                                                                                                                                                                                                                                                                                                        | 26 |

| 4.0  | (ideal case) and with trap states of density D <sub>it</sub> located at the dielectric/GaN interface.                                                                                                                                                                                                                                                                                                                                                |    |

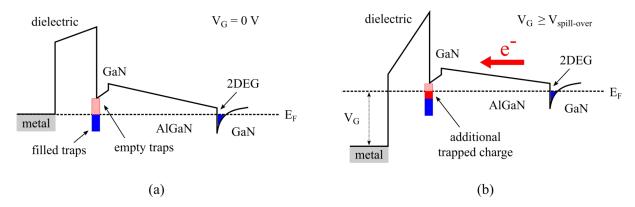

| 4.8  | Schematic conduction band diagram (not to scale) of a dielectric/GaN-cap/AlGaN/GaN structure at a) zero bias ( $V_G = 0$ V) and b) under forward bias in the the spill-over regime ( $V_G \ge V_{\text{spill-over}}$ ). Electrons can overcome the AlGaN barrier from the 2DEG channel and be trapped in the states located at the dielectric/GaN interface. $E_F$ denotes the Fermi energy at 0 V gate voltage                                      |    |

| 4.9  | Schematic C–V characteristics of a dielectric/GaN/AlGaN/GaN capacitor without (ideal case) and with trap states located at the dielectric/GaN interface for different frequencies. A certain frequency dispersion is obtained due to the presence of                                                                                                                                                                                                 | JI |

|      | 1 1/1/2 1                                                                                                                                                                                                                                                                                                                                                                                                                                            | 38 |

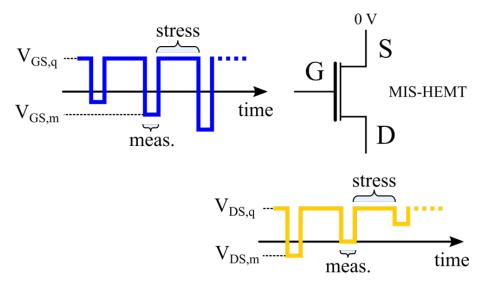

| 4.10 | Principle of pulsed I-V measurement.                                                                                                                                                                                                                                                                                                                                                                                                                 | 40 |

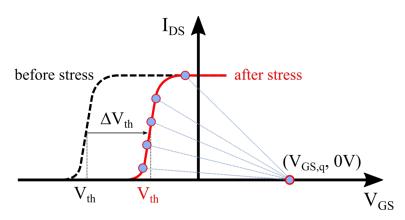

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 4.11 | Schematic of a pulsed $I_{DS}$ - $V_{GS}$ measurement showing the $I_{DS}$ - $V_{GS}$ characteristics before (dashed curve) and after (solid curve) the application of a forward gate bias stress. After stress, the $V_{th}$ shifts due to trapping at the dielectric/III-N interface or within the gate dielectric                                                                                                     | 40       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

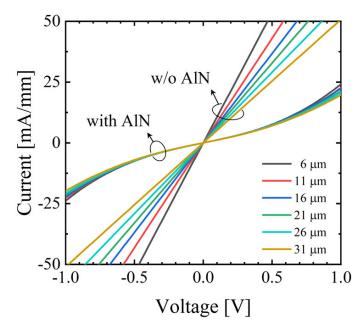

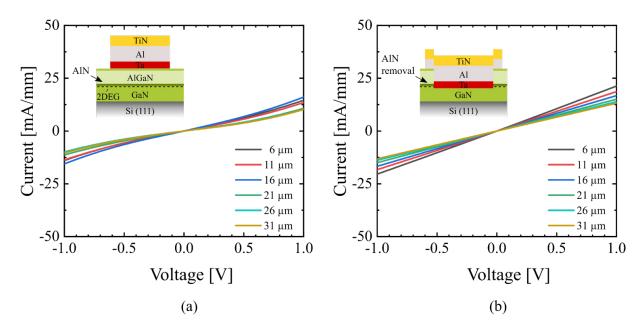

| 5.1  | I-V characteristics of TLM structures of Ta/Al/Ta metal contacts fabricated on epitaxial material with (Sample A.I) and without (Sample A.II) AlN spacer and annealed at 500 °C. For Sample A.II, TLM analysis revealed $R_c$ = 2.7 $\Omega$ mm and $R_{sh}$                                                                                                                                                             |          |

| 5.2  | = $500~\Omega~sq^{-1}$                                                                                                                                                                                                                                                                                                                                                                                                   | 44       |

| 5.3  | analysis revealed a large $R_c$ of about 20 $\Omega$ mm                                                                                                                                                                                                                                                                                                                                                                  | 45       |

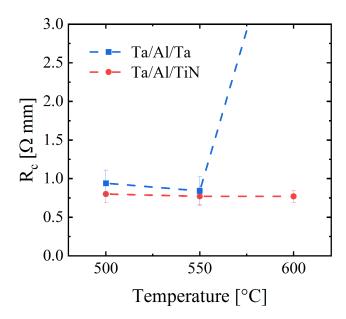

| 5.4  | highly resistive behavior after annealing at 600 °C                                                                                                                                                                                                                                                                                                                                                                      | 47       |

| 5.5  | nealed at 600 °C resulted to be almost completely lost                                                                                                                                                                                                                                                                                                                                                                   | 47       |

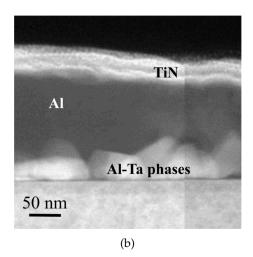

| 5.6  | as shown from the EDX analysis of Figure 5.6                                                                                                                                                                                                                                                                                                                                                                             | 48<br>48 |

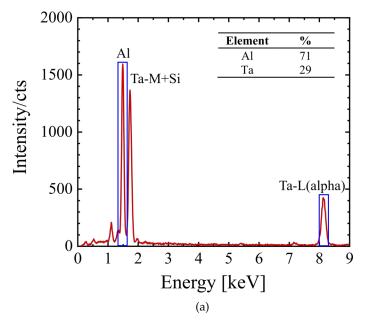

| 5.7  | (a) I-V measurements of the TLM structure of the Ta/Al/TiN metal stack (Sample C.II) annealed at 600 °C. In (b) the corresponding TLM curve from which $R_{\rm c}$ is                                                                                                                                                                                                                                                    |          |

| 5.8  | (a) $R_{sh}$ and (b) $R_c$ as a function of the temperature for the Ta/Al/TiN metal stack (Sample C.II) annealed at 500 °C. The solid line in (a) shows the fit of the experimental data with the temperature dependence $T^{-0.5} \times [\exp(T_0/T)-1]^{-1}$ in accordance with the mobility reduction due to increased phonon scattering with higher temperatures. The dashed line in (b) is only a guide to the eye |          |

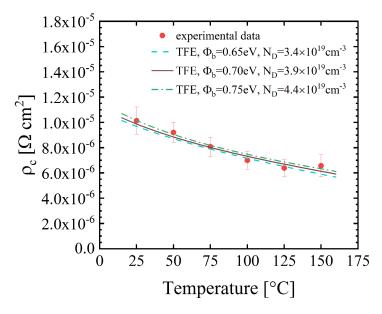

| 5.9  | Temperature dependence of specific contact resistivity $\rho_c$ for the Ta/Al/TiN metal stack (Sample C.II) annealed at 500 °C for a measurement temperature ranging from 25 °C to 150 °C. The lines represent the fits obtained using the TFE model with $\Phi_b = 0.70 \pm 0.05$ eV and $N_D = 3.9 \times 10^{19} \pm 0.5 \times 10^{19}$ cm <sup>-3</sup>                                                             |          |

|      | 0.0 ± 0.00 €7 title 110 ± 0.0 ∧ 10 €tit                                                                                                                                                                                                                                                                                                                                                                                  | <u>ر</u> |

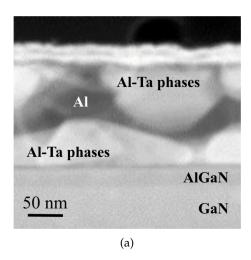

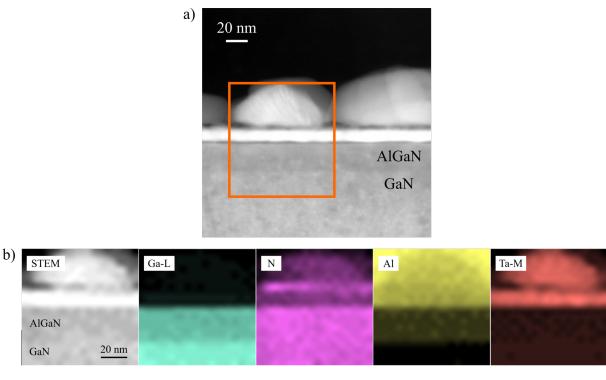

| 5.10 | (a) STEM darkfield image of cross-section of the Ta/Al/TiN metal stack after an-                |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | nealing at 550 °C. The marked area indicates the area of the contact analyzed in (b)            |    |

|      | by EELS. While no Ga is detected in the metal stack, presence of nitrogen is revealed           |    |

|      | into the crystal grains of Ta-Al intermetallic phases formed at the bottom of the metal         |    |

|      | stack. This indicates that nitrogen out-diffused from the AlGaN and GaN layers                  |    |

|      | beneath the metal contact. The Ta bottom layer is also still present at the interface           | 53 |

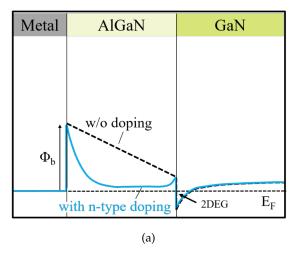

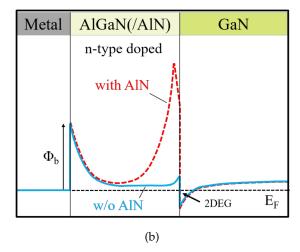

| 5.11 | Schematic conduction band diagrams of the AlGaN/GaN heterostructure under                       |    |

|      | the contact (a) without (dashed line) and with (solid line) an n-type region in the             |    |

|      | AlGaN barrier and (b) with the n-type region in the cases without (solid line) and              |    |

|      | with (dashed line) an AlN spacer layer. The n-type region is supposed to be initiated           |    |

|      | by the ohmic contacts annealing. $E_F$ and $\Phi_b$ denote the Fermi energy and Schottky        |    |

|      | barrier height, respectively.                                                                   | 54 |

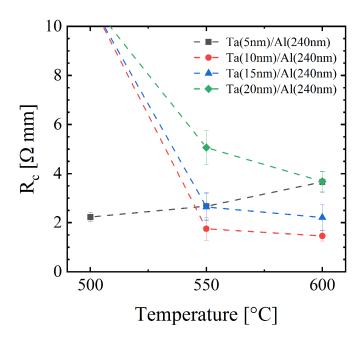

| 5.12 | $R_{c}$ of Ta/Al/TiN metal stacks with various Ta thickness (Samples D.I - D.IV) annealed       |    |

|      | at the temperatures of 500 °C, 550 °C and 600 °C. Error bars indicate the variation of          |    |

|      | different TLM structures. The metal stack with 5 nm of Ta (Sample D.I) showed an                |    |

|      | ohmic behavior already at 500 °C with an increasing $R_{c}$ with increasing annealing           |    |

|      | temperature. On the contrary, the other metal stacks (Samples D.II - D.IV) with a               |    |

|      | thicker Ta layer from 10 nm to 20 nm showed the transition to ohmic behavior only               |    |

|      | at 550 °C and decreasing $R_{c}$ for higher annealing temperatures. The dashed lines are        |    |

|      | only guides to the eye.                                                                         | 56 |

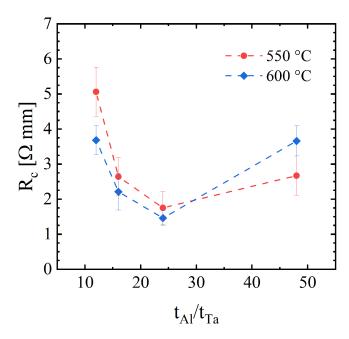

| 5.13 | $R_c$ as a function of the Al/Ta thickness ratio $t_{Al}/t_{Ta}$ for Ta/Al/TiN metal stacks     |    |

|      | (Samples D.I - D.IV) annealed at the temperatures of 550 °C and 600 °C. Error bars              |    |

|      | indicate the variation of different TLM structures. At both annealing temperatures              |    |

|      | the contact resistance decreases towards a minimum value reached at a $t_{\rm Al}/t_{Ta}$ ratio |    |

|      | , ,                                                                                             | 57 |

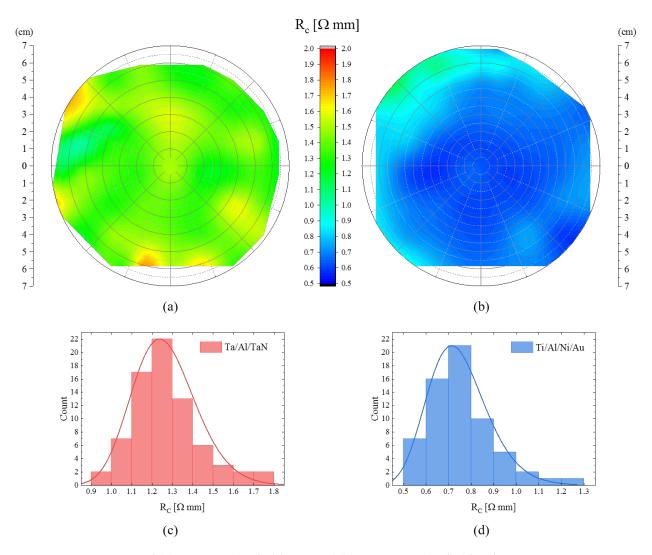

| 5.14 | R <sub>c</sub> maps of (a) sputtered Ta/Al/TaN and (b) evaporated Ti/Al/Ni/Au contacts on       |    |

|      | 150 mm GaN-on-Si wafers annealed in N <sub>2</sub> at 550 °C for 3 minutes and at 850 °C for    |    |

|      | 30 seconds, respectively. (c) and (d) $R_c$ distributions extrapolated from the $R_c$ maps      |    |

|      | in (a) and (b), respectively. Excellent homogeneity with $R_{c}$ mean values of $1.2\pm0.1$     |    |

|      | $\Omega$ mm and $0.7\pm0.1~\Omega$ mm are obtained over the entire substrates for Ta/Al/TaN     |    |

|      | and Ti/Al/Ni/Au contacts, respectively. White regions in (a) and (b) represent areas            |    |

|      | O                                                                                               | 59 |

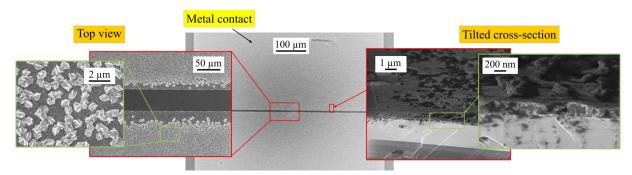

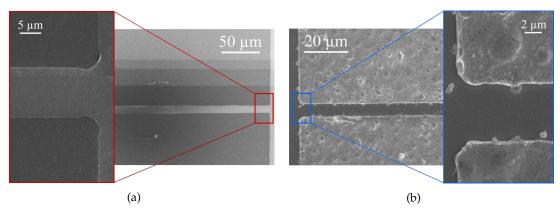

| 5.15 | SEM top views of (a) Ta/Al/TaN contacts annealed at 550 °C for 3 minutes and (b)                |    |

|      | Ti/Al/Ni/Au contacts annealed at 850 °C for 30 seconds. The Ta/Al/TaN metal                     |    |

|      | pads show a smoother surface morphology corresponding to a better edge acuity                   |    |

|      | after annealing.                                                                                | 60 |

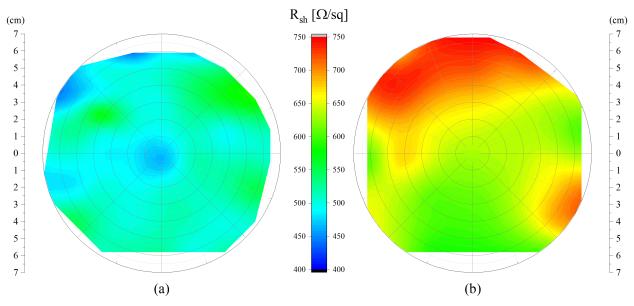

| 5.16 | $R_{sh}$ maps obtained after annealing of (a) Ta/Al/TaN contacts at 550 °C for 3 minutes and (b) Ti/Al/Ni/Au contacts at 850 °C for 30 seconds. $R_{sh}$ mean values are (a) 500 |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $\pm$ 25 $\Omega/sq$ and (b) 660 $\pm$ 40 $\Omega/sq$ , respectively. A larger $R_{sh}$ degradation is clearly                                                                   |    |

|      | visible after the high temperature anneal of the Ti/Al/Ni/Au contacts compared to                                                                                                |    |

|      | the as-grown $R_{\text{sh}}$ of about 420 $\Omega/\text{sq}$ . White regions represent areas at the edge of                                                                      |    |

|      | the wafers that were not measured                                                                                                                                                | 61 |

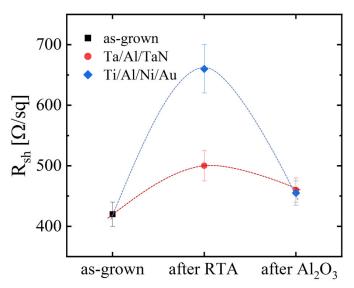

| 5.17 | $R_{sh}$ change of Ta/Al/TaN and Ti/Al/Ni/Au contacts after RTA (mean values taken                                                                                               |    |

|      | from Figure 5.16) and after ALD-Al $_2$ O $_3$ passivation. The as-grown $R_{sh}$ value is about                                                                                 |    |

|      | $420\ \Omega/sq$ for both epitaxial materials used. A recovery of $R_{sh}$ towards the as-grown                                                                                  |    |

|      | value can be seen in both cases. The dashed lines are only guides to the eye                                                                                                     | 62 |

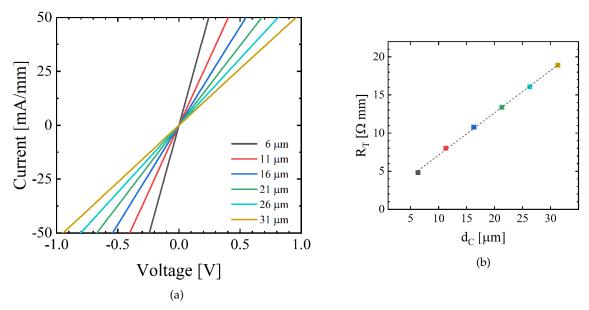

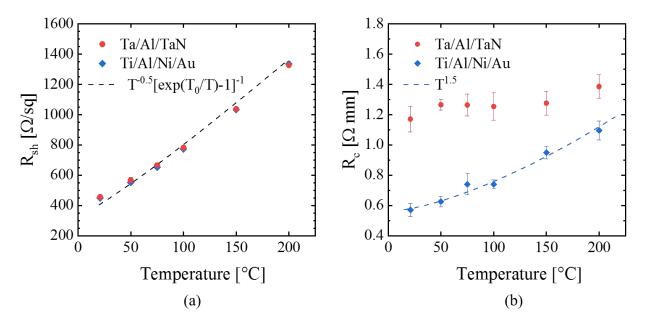

| 5.18 | (a) $R_{sh}$ and (b) $R_c$ as a function of the temperature for Ta/Al/TaN and Ti/Al/Ni/Au                                                                                        |    |

|      | metal stacks annealed at 550 °C for 3 minutes and 850 °C for 30 seconds, respectively,                                                                                           |    |

|      | and subsequently passivated with 20 nm of ALD-Al $_2$ O $_3$ . The dashed line in (a) shows                                                                                      |    |

|      | the fit of the experimental data with the temperature dependence $T^{-0.5} \times [exp(T_0/T)-$                                                                                  |    |

|      | 1] <sup>-1</sup> in accordance with the mobility reduction due to phonon scattering, while the                                                                                   |    |

|      | line in (b) shows the fit of the experimental data with the temperature dependence                                                                                               |    |

|      | $T^{\alpha}$ with $\alpha = 1.5$ only for Ti/Al/Ni/Au ohmic contacts                                                                                                             | 63 |

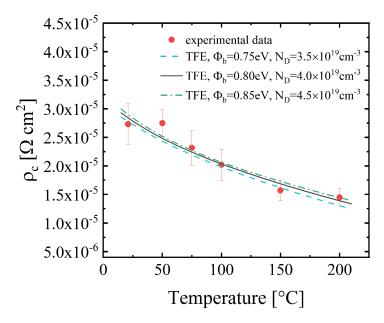

| 5.19 | Temperature dependence of specific contact resistivity $ ho_c$ for the Ta/Al/TaN metal                                                                                           |    |

|      | stack annealed at 550 °C for a measurement temperature ranging from RT to 200 °C.                                                                                                |    |

|      | The lines represent the fits obtained using the TFE model with $\Phi_b$ = 0.80 $\pm$ 0.05 eV                                                                                     |    |

|      | and $N_D$ = $4.0 \times 10^{19} \pm 0.5 \times 10^{19} \ cm^{-3}$                                                                                                                | 64 |

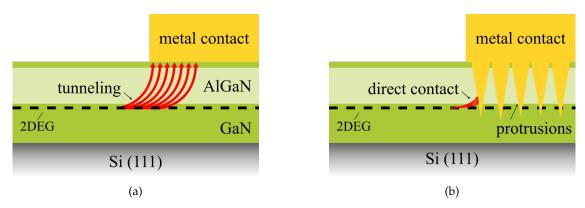

| 5.20 | Schematic illustration of physical models of (a) a 2DEG-semiconductor-metal con-                                                                                                 |    |

|      | nection governed by tunneling in line with the TLM model and (b) a direct sideway                                                                                                |    |

|      | 2DEG-metal connection due to metal protrusions into the AlGaN barrier                                                                                                            | 65 |

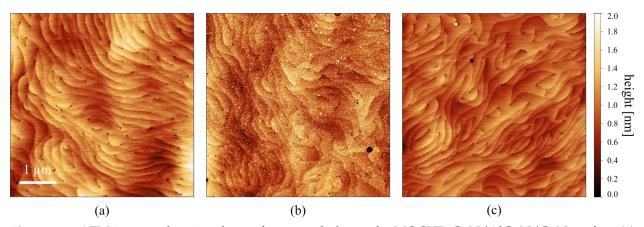

| 6.1  | AFM images showing the surface morphology of a MOCVD GaN/AlGaN/GaN                                                                                                               |    |

|      | surface (a) as-grown, (b) before SPC and (c) after SPC. The SPC treatment is effective                                                                                           |    |

|      | in removing contaminants and restoring the surface morphology resulting in a flat                                                                                                |    |

|      | step-like terrace structure similarly to the as-grown GaN surface                                                                                                                | 69 |

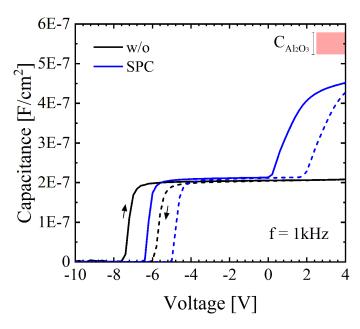

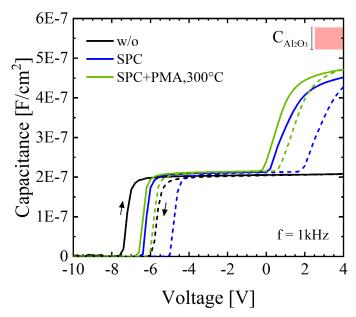

| 6.2  | C-V characteristics of Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN capacitors having 16 nm thick                                                                               |    |

|      | Al <sub>2</sub> O <sub>3</sub> without (Sample E.I) and with (Sample E.II) SPC treatment applied. The                                                                            |    |

|      | DC voltage sweep starts at -10 V. The AC signal frequency is 1 kHz with 30 mV                                                                                                    |    |

|      | amplitude. Down-sweep curves are indicated by dashed lines in both cases. The                                                                                                    |    |

|      | ideal range of values of $C_{\mathrm{Al_2O_3}}$ calculated from 16 nm thick $\mathrm{Al_2O_3}$ considering a                                                                     |    |

|      | deviation from the nominal value of 0.5 nm is also indicated, in accordance with the                                                                                             |    |

|      | series capacitance model                                                                                                                                                         | 70 |

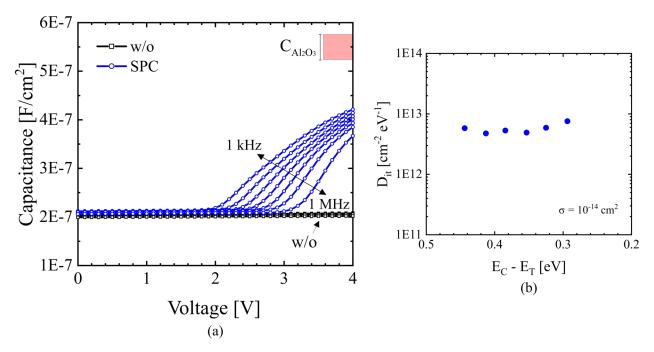

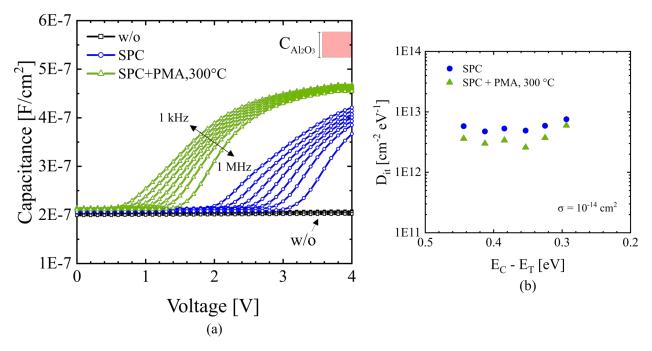

| 6.3 | (a) Frequency dispersion in forward bias region of the C–V characteristics of Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN capacitors having 16 nm-thick Al <sub>2</sub> O <sub>3</sub> without treatment applied (Sam- |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | ple E.I in black rectangles) and after SPC (Sample E.II in blue circles). The frequency                                                                                                                                  |

|     | ranges from 1 kHz to 1 MHz, e.g. [1, 3, 10, 30, 100, 300, 1000 kHz]. The ideal range                                                                                                                                     |

|     | of values of $C_{Al_2O_3}$ is indicated. In (b) the corresponding $D_{it}$ - $E_T$ mapping for the                                                                                                                       |

|     | Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN capacitor after SPC treatment                                                                                                                                              |

| 6.4 | C–V characteristics of 16 nm Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN capacitors fabricated with-                                                                                                                   |

| 0.1 | out (Sample E.I) and with (Sample E.II) SPC treatment and with SPC treatment                                                                                                                                             |

|     | combined with the PMA process at 300 °C for 10 minutes in $N_2$ ambient (Sample                                                                                                                                          |

|     | 1                                                                                                                                                                                                                        |

|     | E.III). The DC voltage sweep starts at -10 V. The AC signal frequency is 1 kHz with                                                                                                                                      |

|     | 30 mV amplitude. Down-sweep curves are indicated by dashed lines in all cases.                                                                                                                                           |

|     | The ideal range of values of $C_{\mathrm{Al_2O_3}}$ is also indicated, in accordance with the series                                                                                                                     |

|     | capacitance model                                                                                                                                                                                                        |

| 6.5 | (a) Frequency dispersion in forward bias region of the C–V characteristics of Al <sub>2</sub> O <sub>3</sub> /GaN/                                                                                                       |

|     | AlGaN/GaN capacitors without treatment applied (Sample E.I in black rectangles),                                                                                                                                         |

|     | after SPC (Sample E.II in blue circles) and SPC combined with PMA at 300 °C for 10                                                                                                                                       |

|     | minutes in N <sub>2</sub> (Sample E.III in green triangles). The frequency ranges from 1 kHz                                                                                                                             |

|     | to 1 MHz, e.g. [1, 3, 10, 30, 100, 300, 1000 kHz]. The ideal range of values of $C_{\rm Al_2O_3}$                                                                                                                        |

|     | is indicated. In (b) the corresponding $D_{it}$ - $E_T$ maps extracted from the frequency                                                                                                                                |

|     | dispersion only in the cases of capacitors treated with SPC and SPC combined with                                                                                                                                        |

|     | PMA                                                                                                                                                                                                                      |

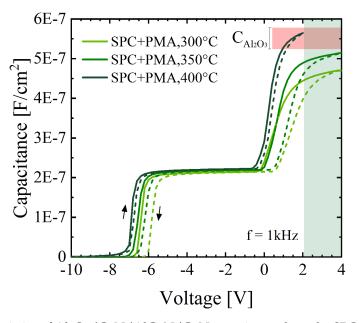

| 6.6 | C–V characteristics of Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN capacitors where the SPC treatment                                                                                                                  |

|     | is combined with the PMA treatment performed at the annealing temperatures of 300                                                                                                                                        |

|     | $^{\circ}$ C, 350 $^{\circ}$ C and 400 $^{\circ}$ C for 10 minutes in N <sub>2</sub> ambient (Samples E.III). The DC voltage                                                                                             |

|     | sweep starts at -10 V and the AC signal frequency is 1 kHz with 30 mV amplitude.                                                                                                                                         |

|     | Down-sweep curves are illustrated by dashed lines and the ideal range of values of                                                                                                                                       |

|     | $C_{\mathrm{Al}_2\mathrm{O}_3}$ is indicated. The green shadow area indicates the voltage measurement limit                                                                                                              |

|     | for the sample treated by PMA at 400 °C due to leakage currents preventing the C-V                                                                                                                                       |

|     | measurement beyond 2 V                                                                                                                                                                                                   |

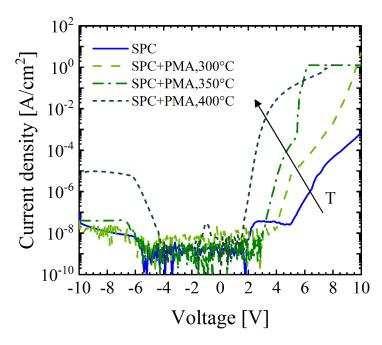

| 6.7 | Impact of the PMA temperature on the leakage current density of MISH capacitors                                                                                                                                          |

|     | having 16 nm ALD-Al <sub>2</sub> O <sub>3</sub> as gate dielectric subjected to PMA treatment at the                                                                                                                     |

|     | annealing temperatures of 300 °C, 350 °C and 400 °C for 10 minutes in $N_2$ atmosphere                                                                                                                                   |

|     | (Samples E.III). Each measurement was performed on a fresh device from 0 V to -10                                                                                                                                        |

|     | V and from 0 V to +10 V, respectively                                                                                                                                                                                    |

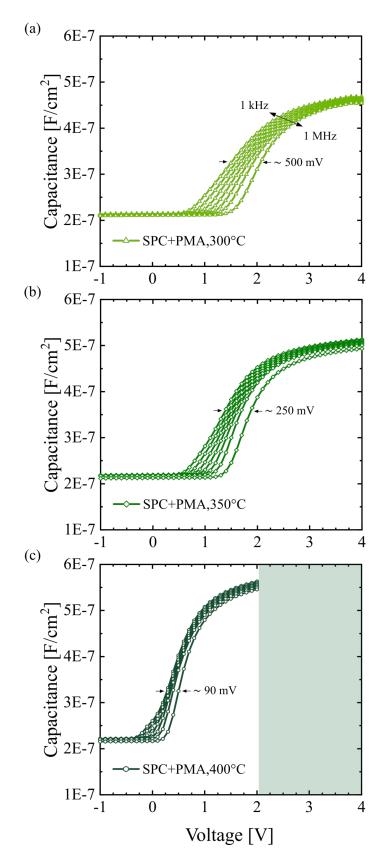

| 6.8 | Frequency dispersion in forward bias region of the C-V characteristics of MISH                                                                                                                                           |

|     | capacitors with 16 nm ALD-Al <sub>2</sub> O <sub>3</sub> treated by SPC combined with PMA (Samples                                                                                                                       |

|     | E.III) at (a) 300 °C (b) 350 °C and (c) 400 °C for 10 minutes in $N_2$ . The frequency ranges                                                                                                                            |

|     | from 1 kHz to 1 MHz. The voltage shifts between C–V curves at the frequencies of 1                                                                                                                                       |

|     | kHz and 1 MHz are indicated. The green shadow area in (c) indicates the voltage                                                                                                                                          |

|     | measurement limit for the sample treated by PMA at 400 °C due to large leakage                                                                                                                                           |

|     | currents beyond 2 V                                                                                                                                                                                                      |

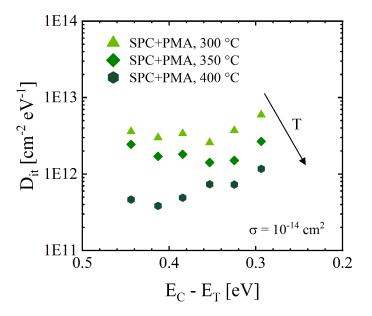

| 6.9  | Interface trap density versus trap energy from the conduction band, extracted from the frequency dispersions of Figure 6.8 for MISH capacitors subjected to SPC combined with PMA at the annealing temperatures of 300 °C (b) 350 °C and (c) 400 °C for 10 minutes in $N_2$ ambient. A reduction of the $D_{it}$ with the increase of the PMA temperature is clearly visible                                                                                                                                                                                                              | 78 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

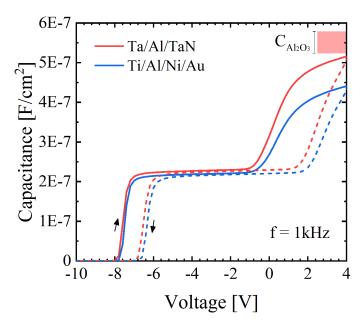

| 6.10 | C–V characteristics of $Al_2O_3/GaN/AlGaN/GaN$ capacitors having 16 nm-thick $Al_2O_3$ fabricated with Ta/Al/TaN (Sample F.I) and Ti/Al/Ni/Au (Sample F.II) ohmic contacts annealed at 550 °C for 3 minutes and at 850 °C for 30 seconds, respectively. The SPC treatment was applied for both samples prior to the $Al_2O_3$ gate dielectric deposition. The DC voltage sweep starts at -10 V and the AC signal frequency is 1 kHz with 30 mV amplitude. Down-sweep curves are indicated by dashed lines in both cases. The ideal range of values of $C_{Al_2O_3}$ is also indicated, in |    |

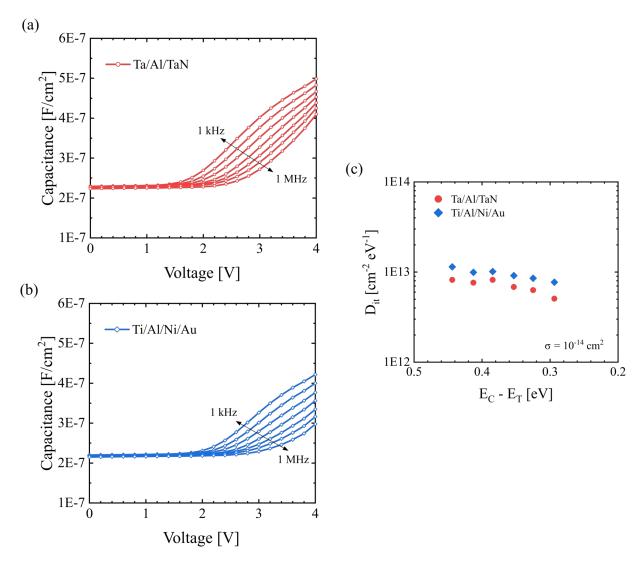

| 6.11 | accordance with the series capacitance model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79 |

|      | dispersion for both samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 |

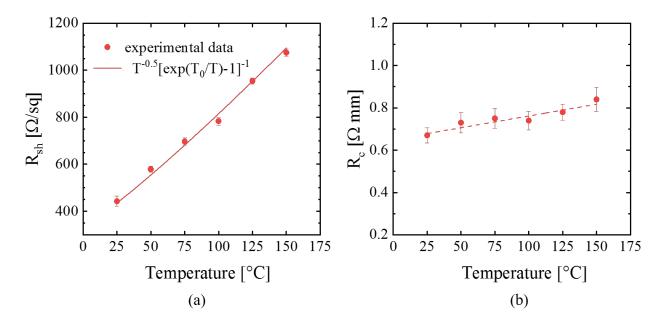

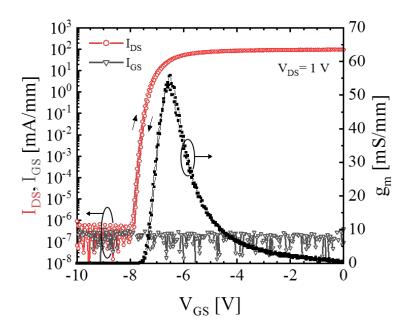

| 7.1  | DC transfer (logarithmic scale) and transconductance characteristics of AlGaN/GaN MIS-HEMT with 16 nm-thick ALD-Al $_2$ O $_3$ as gate insulator and Ta/Al/TaN ohmic contacts, for $V_{DS}=1$ V. The $V_{GS}$ is swept from -10 V to 0 V and then back to -10 V. The device has $L_{GS}=3$ µm, $L_{G}=3$ µm and $L_{GD}=14$ µm. The threshold voltage $V_{th}$                                                                                                                                                                                                                            |    |

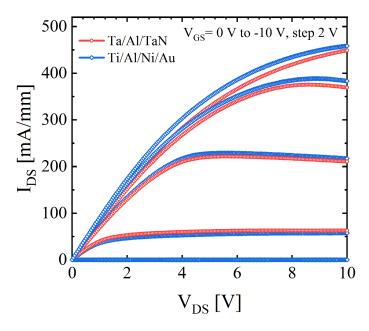

| 7.2  | is -6.5 V, subthreshold swing SS is 75 mV/dec and the peak $g_m$ is 56 mS/mm DC output characteristics of AlGaN/GaN MIS-HEMTs fabricated with 16 nm-thick ALD-Al <sub>2</sub> O <sub>3</sub> as gate insulator and Ta/Al/TaN and Ti/Al/Ni/Au ohmic contacts.                                                                                                                                                                                                                                                                                                                              | 83 |

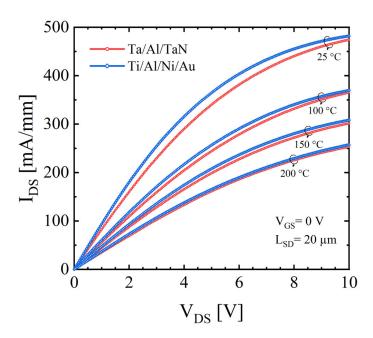

| 7.3  | Design parameters of measured devices are $L_{GS}$ = 3 $\mu m$ , $L_{G}$ = 3 $\mu m$ and $L_{GD}$ = 14 $\mu m$ . Output characteristics at $V_{GS}$ = 0 V of MIS-HEMTs using Ta/Al/TaN and Ti/Al/Ni/Au ohmic contacts measured at 25 °C, 100 °C, 150 °C and 200 °C. A larger degradation of $R_{DS,on}$ for higher temperatures is obtained using Ti/Al/Ni/Au contacts due to the stronger increase of $R_{c}$ with increasing temperature. Design parameters of measured                                                                                                                 | 84 |

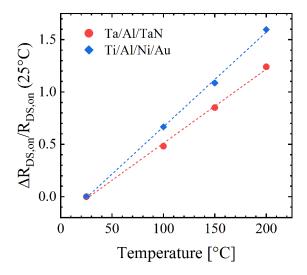

| 7.4  | devices are $L_{GS}=3~\mu m$ , $L_{G}=3~\mu m$ and $L_{GD}=14~\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86 |

| 7.5  | in a more pronounced $R_{DS,on}$ degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87 |

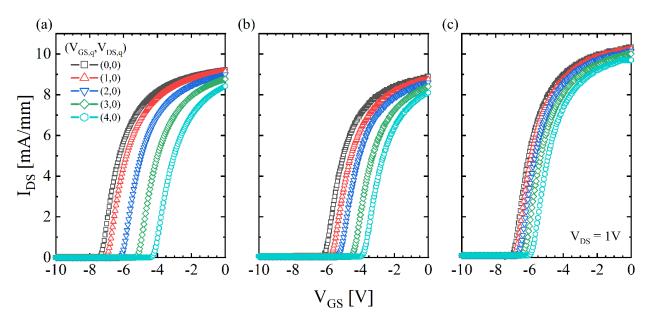

|      | 0 V. The devices have $L_{GS}$ = 3 $\mu$ m, $L_{G}$ = 3 $\mu$ m and $L_{GD}$ = 14 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88 |

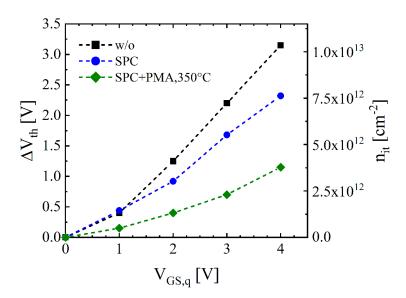

| 7.6 | V <sub>th</sub> shift extrapolated from the pulsed I <sub>DS</sub> -V <sub>GS</sub> characteristics of AlGaN/GaN MIS- |    |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

|     | HEMTs without treatment applied, after SPC and after SPC combined with PMA                                            |    |

|     | at 350 °C for 10 minutes in N <sub>2</sub> shown in Figure 7.5. The corresponding effective                           |    |

|     | interface charge density n <sub>it</sub> calculated using Equation 4.5 is also illustrated. The                       |    |

|     | dashed lines are only guides to the eye                                                                               | 89 |

|     |                                                                                                                       |    |

|     |                                                                                                                       |    |

### **List of Tables**

| 2.1 | Electrical properties at 300 K of group III-nitride bulk materials in comparison to                                                                                                                                                                                                                                                                                                                                   |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | competing semiconductors. Data taken from [12, 15, 16, 17, 18, 19]                                                                                                                                                                                                                                                                                                                                                    | 3  |

| 4.1 | Epitaxial heterostructures used in this work                                                                                                                                                                                                                                                                                                                                                                          | 29 |

| 5.1 | List of metal stacks applied to the fabricated samples investigated in this section. The $R_c$ data extracted from TLM structures for samples with ohmic characteristics at annealing temperature ranging between 500 °C and 600 °C are also shown. The "n/o" refers to a non-ohmic behavior obtained after annealing. Refer to Table 4.1 for specifications on the epitaxial materials indicated in the column "Epi" | 43 |

| 5.2 | Resistivity of sputtered metals used in this work measured by four-point method, before and after annealing at $550$ °C for 3 minutes in $N_2$                                                                                                                                                                                                                                                                        |    |

| 5.3 | Metal stacks and annealing conditions applied to the fabricated samples investigated in this section. Refer to Table 4.1 for specifications on the epitaxial material indicated in the column "Epi"                                                                                                                                                                                                                   | 58 |

| 6.1 | List of MISH capacitor structures highlighting the processing conditions which are compared and investigated in this chapter. Refer to Section 4.2 for more details about the fabrication process conditions and to Table 4.1 for specifications on the epitaxial materials indicated in the column "Epi"                                                                                                             | 67 |

| 7.1 | MIS-HEMTs processing conditions applied to the fabricated samples of this section.  Refer to Table 4.1 for specifications on the epitaxial materials indicated in the column  "Epi" and to Section 4.2 for more details on the fabrication process                                                                                                                                                                    | 83 |

| 7.2 | Comparison of the calculated and measured on-state drain-to-source resistance $R_{DS,on}$ of MIS-HEMTs with Ta/Al/TaN and Ti/Al/Ni/Au ohmic contacts. The input parameters of $R_c^{S/D}$ and $R_{sh}$ for the calculation were obtained in Section 5.2 taking                                                                                                                                                        |    |

|     | into account the $Al_2O_3$ passivation layer                                                                                                                                                                                                                                                                                                                                                                          | 85 |

#### 1 Introduction

Today more than ever, the continuous increase of the global consumption of electric energy urgently demands for more efficient energy convertion systems capable of handling and delivering higher power levels. In fact, traditional power systems based on silicon are quickly approaching their physical limits in terms of power density, conversion efficiency and possibility to operate at higher frequency and higher temperatures. To meet the future expectations of power electronics, novel semiconductors have been exploited as alternative to silicon.

Owing to the outstanding physical properties of large bandgap energy of 3.43 eV, high electric breakdown field of 3.3 MV/cm and large saturation velocity of about  $2.5 \times 10^7$  cm/s, GaN is one of the most promising semiconductor for the future generation of energy efficient power electronics.[1, 2] Beside the unique intrinsic material properties, one of the most attractive property of GaN is the possibility to exploit the polar nature of GaN-based materials to form AlGaN/GaN heterostructures. Featuring a two-dimensional electron gas at the heterointerface with high carrier density and high mobility values exceeding  $2000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , AlGaN/GaN heterostructures enable the fabrication of high electron mobility transistors (HEMTs) which can significantly outperform the traditional Si power devices in terms of breakdown strength, on-resistance and switching speed, achieving higher power density and higher energy efficiency.[3, 4] First demonstrated by Khan et al. in 1993,[5] GaN-based HEMT lateral devices are now commercially available in the power electronics market.[6] Neverthless, technological challenges are being still faced in parallel in order to bring the GaN technology to an industrial maturity and cost-effective level suitable for mass markets.[7]

One of the most serious problems that limit the performance of AlGaN/GaN HEMTs is the high leakage current at the Schottky-gate electrode.[8] For this reason, the Schottky-gate is replaced by a metal-insulator-semiconductor (MIS)-gate structure providing reduced power consumption, larger gate bias swing and better immunity to gate breakdown,[9] which are important requirements especially for power switching devices. However, in contrast to Si-based devices, the introduction of an insulator in MIS-HEMT devices is complicated by the absense of a high-quality native oxide for GaN. Due to the wide bandgap of GaN-based materials, trap states at the dielectric/III-nitride interface and within the dielectric can be deeply located in the bandgap and lead to long charge/discharge processes which strongly affect the device performance.[10] Various dielectric materials have been employed, being Al<sub>2</sub>O<sub>3</sub> and SiN<sub>x</sub> the most promising gate dielectrics.[11] However, even though excellent device characteristics have been reported, trap states in MIS gate structures still remain one of the biggest challenge for GaN-based MIS-HEMTs. In particular, the commercialization of these devices has been hindered by concerns over the gate dielectric reliability. In this respect, the delivery of a gate dielectric with low interface and bulk trap density and robust reliability under stringent electrical and thermal stresses is still of primary importance.

Another major concern for GaN-based devices is represented by the absence of high quality and

large freestanding GaN substrates. For this reason, GaN-on-Si platforms are typically used for device fabrication. As a consequence, the cost-effective and large-scale production of GaN-based devices sees the manufacturing of these devices in existing Si facilities as the most natural strategy for a significant price reduction accompanied by improved handling capabilities. However, this comes with the stringent requirement of developing a manufacturing process for GaN-based devices which is fully compatible with the restrictions of Si fabs in terms of source of contaminations.[12] In particular, since conventional source and drain ohmic contacts have been using gold (Au)-containing metallization schemes, the development of Au-free ohmic contacts with a low contact resistance is a key aspect to enable the processing of GaN-based devices in Si production lines.[13] In general, the fabrication of low-resistive ohmic contacts is mainly complicated by the absence of metals which are able to prevent the formation of a Schottky barrier between the metal and wide bandgap GaN-based materials. In this respect, low-resistive and Au-free ohmic contacts seem even more challenging than Au-containing contacts. Another important aspect is that conventional Au-containing contacts require thermal annealing treatments at high temperatures (>800 °C) for contact formation. Lower annealing temperatures below 600 °C would be also preferable to beneficially add flexibility and opportunities in device process integration. For these reasons, enourmous efforts have been devoted to the study and development of low-resistive and Au-free ohmic contacts to GaN-based materials annealed at low temperatures. The latters have recently contributed to first demonstration of Au-free complementary metal-oxide-semiconductor (CMOS)compatible AlGaN/GaN HEMT processing on 200 mm Si substrates in a Si fab.[14] Neverthless, the topic of ohmic contacts still contains several open scientific issues among which the reproducibility of Au-free ohmic contacts with contact resistance below 1.0  $\Omega$  mm and even more the mechanism of ohmic contact formation represent the most challenging and debated.

The focus of this work was the fabrication, characterization and optimization of AlGaN/GaN MIS-HEMTs for high-power electronics. The thesis is structured as follows: in Chapter 2, the fundamental concepts of heterostructure field-effect transistors are introduced and the operation principles of Schottky-gate HEMTs are presented. Chapter 3 introduces the requirements of the epitaxial materials used to obtain high performance AlGaN/GaN devices. The challenges encountered in the integration of a MIS-gate in HEMT devices for power applications and the difficulties in the realization of low-resistive ohmic contacts to AlGaN/GaN heterostructures are also highlighted. In Chapter 4, the experimental fabrication and characterization methods applied in this work are briefly described. Chapter 5 focuses on the development and investigation of low-temperature and Au-free ohmic contacts to AlGaN/GaN heterostructures using sputtered Ta/Al-based metal stacks. In Chapter 6, the MIS-gate module of AlGaN/GaN heterostructure capacitors using ALD-Al<sub>2</sub>O<sub>3</sub> as gate insulator is investigated and optimized in terms of trap states at the dielectric/III-nitride interface and inside the dielectric. Chapter 7 concludes with the process integration in AlGaN/GaN MIS-HEMTs of the developed Au-free ohmic contacts and of the optimized MIS-gate module, which result beneficial in terms of on-state drain-to-source resistance degradation in devices operating at high temperature and device threshold voltage stability under positive gate bias stress, respectively. Finally, overall conclusions and outlooks are given.

# 2 Fundamentals of heterostructure field-effect transistors

In this chapter, the fundamentals of heterostructure field-effect transistors (HFETs) are reviewed. In particular, the unique intrinsic properties of the group III-nitrides are briefly described in the view of their application into AlGaN/GaN heterostructures, which also benefit from the high-density and high-mobility two dimensional electron gas (2DEG) confined at the heterojunction interface. Finally, the operation principles of AlGaN/GaN HEMTs with a Schottky-gate are introduced and the main electrical parameters which are used to characterize the device performance are presented.

#### 2.1 Group III-Nitrides

The basic group of III-nitrides is composed by the binary compound semiconductor materials of aluminum nitride (AlN), gallium nitride (GaN) and indium nitride (InN). The superior intrinsic properties of these materials compared to silicon (Si), silicon carbide (SiC) or other III-V compound semiconductors make them extremely suitable for a wide variety of applications. Particularly, the III-nitrides have a wide range of direct bandgap energies from 0.7 eV to 6.2 eV which covers emission wave lengths from the infrared to the deep ultraviolet. The wide range of the emission spectra can be tuned through the material composition and be tailored for various optoelectronic applications, such as light-emitting diodes, lasers, photodetectors and solar cells. The wide tuning range of the bandgap energies of III-nitride materials is also very suitable for electronic applications, allowing for extremely high critical breakdown field strength and excellent capability to operate at high temperatures as well as low electron effective mass and high electron mobility.

**Table 2.1:** Electrical properties at 300 K of group III-nitride bulk materials in comparison to competing semiconductors. Data taken from [12, 15, 16, 17, 18, 19].

|                                           | AlN | GaN  | InN  | GaAs | 4H-SiC | Si   |

|-------------------------------------------|-----|------|------|------|--------|------|

| Energy bandgap (eV)                       | 6.2 | 3.43 | 0.7  | 1.42 | 3.26   | 1.12 |

| Dielectric constant                       | 8.5 | 9.5  | 15.3 | 12.9 | 9.7    | 11.7 |

| Electron mobility (cm <sup>2</sup> /Vs)   | 300 | 1200 | 3200 | 8500 | 800    | 1500 |

| Breakdown field (MV/cm)                   | 8.4 | 3.3  | 1.4  | 0.4  | 3.5    | 0.3  |

| Saturation velocity ( $\times 10^7$ cm/s) | 1.4 | 2.5  | 1.8  | 0.7  | 2.0    | 1.0  |

In this perspective, GaN is one of the most promising III-nitride material for high-voltage electronics compared to conventional semiconductors. Its large bandgap energy of 3.43 eV results in an electric breakdown field of about one order of magnitude larger than in Si. Additionally, even though GaN exhibits about the same electron mobility than Si, the larger saturation velocity of GaN which can be achieved at high electric fields offers a great potential to target high-frequency and high-power switching applications, such as DC-DC converters, DC-AC converters or switching power amplifiers. Table 2.1 compares the inherent material properties of III-nitride materials to the competing semiconductors. A comprehensive overview of the material properties of group III-nitride semiconductors and their electronic applications is given by Rüdiger Quay.[20]

Figure 2.1: Crystal structure of wurtzite (a) Ga-face and (b) N-face GaN, taken from [21].

The great potential of III-nitride materials additionally stems from the presence of a strong spontaneous and piezoelectric polarization arising from the crystal structure of these materials. The group III-nitrides AlN, GaN, and InN can crystallize in the three crystal structures of wurtzite (hexagonal), zinc-blende (cubic), and rock-salt (cubic). The wurtzite structure is currently utilized for electronic applications since this phase is thermodynamically stable at ambient conditions. The unit cell of the wurtzite lattice is hexagonal and consists of alternating closely-packed hexagonal planes of cations and anions pairs stacked along the c-axis. The non-centrosymmetric nature of the wurtzite structure in combination with a pronounced ionic character of the metal-nitrogen bond of III-nitrides lead to polar faces and a strong macroscopic polarization along the c direction. Since this polarization effect occurs in the equilibrium lattice of III-nitrides at zero strain, it is called spontaneous polarization. Bernardini et al. predicted that the spontaneous polarization is very large in wurtzite group-III nitrides compared to other III-V compound materials and its magnitude increases from GaN over InN to AlN.[22] The wurtzite crystal structure of GaN is schematically represented in Figure 2.1. Due to the inversion asymmetry along the *c*-axis in the wurtzite phase, the crystal surface of GaN can have either Ga-face or N-face polarity when grown along the [0001] and [0001] directions, respectively. [21] With a few exceptions, [21, 23, 24] most research in III-nitride optoelectronic and electronic devices in the past has focused on bulk materials grown in the Ga-polar direction.