**SHUBHAM RAI**

**SHUBHAM RAI**

### **THESIS**

At the faculty of Computer Science of the Technical University of Dresden to obtain the academic degree Doktoringenieur (Dr.-Ing.) submitted

by Shubham Rai

born on the 26.01.1988 in Patna, India

#### Doctoral Committee:

- Prof. Dr. Akash Kumar (Supervisor and Reviewer) Technische Universität Dresden, Germany

- Prof. Dr. Giovanni De Micheli (Reviewer) Ecole Polytechnique F ed erale de Lausanne, Switzerland

- Prof. Dr. Walter Michael Weber (Fachreferent) Technische Universität Wien, Austria

- Prof. Dr. Thomas Mikolajick (Committee Member) NaMLab gGmbH Dresden, Germany

- Prof. Dr. Diana Göhringer (Committee Chair) Technische Universität Dresden, Germany

Design Automation and Application for Emerging Reconfigurable Nanotechnologies / by Shubham Rai - Dresden : Technische Universität Dresden, 2022.

A catalogue record is available from the Technical University of Dresden Library Keywords: EDA / Reconfigurable / emerging / nanotechnology / logic synthesis / Hardware Security/ Physical Synthesis/ Logic Synthesis

© Shubham Rai 2022. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner. Printing: Printservice Technical University Dresden

### **Abstract**

In the last few decades, two major phenomena have revolutionized the electronic industry – the ever-increasing dependence on electronic circuits and the Complementary Metal Oxide Semiconductor (CMOS) downscaling. These two phenomena have been complementing each other in a way that while electronics, in general, have demanded more computations per functional unit, CMOS downscaling has aptly supported such needs. However, while the computational demand is still rising exponentially, CMOS downscaling is reaching its physical limits. Hence, the need to explore viable emerging nanotechnologies is more imperative than ever. This thesis focuses on streamlining the existing design automation techniques for a class of emerging reconfigurable nanotechnologies. Transistors based on this technology exhibit duality in conduction, i.e. they can be configured dynamically either as a p-type or an n-type device on the application of an external bias. Owing to this dynamic reconfiguration, these transistors are also referred to as Reconfigurable Field-Effect Transistors (RFETs).

Exploring and developing new technologies just like CMOS, require tackling two main challenges – first, design automation flow has to be modified to enable tailor-made circuit designs. Second, possible application opportunities should be explored where such technologies can outsmart the existing CMOS technologies. This thesis targets the above two objectives for emerging reconfigurable nanotechnologies by proposing approaches for enabling an Electronic Design Automation (EDA) flow for circuits based on RFETs and exploring hardware security as an application that exploits the transistor-level dynamic reconfiguration offered by this technology.

This thesis explains the bottom-up approach adopted to propose a logic synthesis flow by identifying new logic gates and circuit design paradigms that can particularly exploit the dynamic reconfiguration offered by these novel nanotechnologies. This led to the subsequent need of finding natural Boolean logic abstraction for emerging reconfigurable nanotechnologies as it is shown that the existing abstraction of negative unate logic for CMOS technologies is sub-optimal for RFETs-based circuits. In this direction, it has been shown that duality in

Boolean logic is a natural abstraction for this technology and can truly represent the duality in conduction offered by individual transistors. Finding this abstraction paved the way for defining suitable primitives and proposing various algorithms for logic synthesis and technology mapping.

The following step is to explore compatible physical synthesis flow for emerging reconfigurable nanotechnologies. Using silicon nanowire-based RFETs, .lef and .lib files have been provided which can provide an end-to-end flow to generate .GDSII file for circuits exclusively based on RFETs. Additionally, new approaches have been explored to improve placement and routing for circuits based on reconfigurable nanotechnologies. It has been demonstrated how these approaches led to superior results as compared to the native flow meant for CMOS.

Lastly, the unique property of transistor-level reconfiguration offered by RFETs is utilized to implement efficient Intellectual Property (IP) protection schemes against adversarial attacks. The ability to control the conduction of individual transistors can be argued as one of the impactful features of this technology and suitably fits into the paradigm of security measures. Prior security schemes based on CMOS technology often come with large overheads in terms of area, power, and delay. In contrast, RFETs-based hardware security measures such as logic locking, split manufacturing, etc. proposed in this thesis, demonstrate affordable security solutions with low overheads.

Overall, this thesis lays a strong foundation for the two main objectives – design automation, and hardware security as an application, to push emerging reconfigurable nanotechnologies for commercial integration. Additionally, contributions done in this thesis are made available under open-source licenses so as to foster new research directions and collaborations.

## Acknowledgments

#### The Blind Side

A Ph.D. is a transformation, not only does it transform your name with a preceding title but also transforms you as a person. This transformation is very similar to simulated annealing. You go through various recovery and growth phases to become a better individual. With my dissertation, I would like to take this opportunity to sincerely thank everyone who has helped me in various stages of this transformation.

I think the most earnest appreciation is (and will always) be reserved for Prof. Dr. Akash Kumar. First, to accept me as a Ph.D. candidate and then continuously guiding and motivating me throughout this wonderful journey. He has been an exceptional mentor and a great friend. His working style and his encouragement are truly remarkable. He provides complete scientific freedom and yet was also involved in research sometimes even to the level of minute algorithmic details.

I would like to specially mention three people whom I would like to thank from the bottom of my heart – Dr. Jens Trommer from whom I can go and ask about RFETs technology anytime, Dr. Heinz Riener who helped me during my stay at EPFL, and from whom I learned a lot about logic synthesis and last but not the least Dr. Siva Satyendra Sahoo, my badminton buddy and the guy who is always willing to discuss and from whom I have learned all the nitty-gritty details such as writing paper, presenting results, etc. These guys have been instrumental at various stages of my Ph.D.

I would also like to extend my sincere gratitude to the doctoral committee comprising of stalwarts – Prof. Dr. Giovanni De Micheli, Prof. Dr. Thomas Mikolajick, Prof. Dr. Walter M. Weber, and Prof. Dr. Diana Göhringer. I would

like to express my appreciation towards my collaborators – Dr. Andreas Krinke, Dr. Andrè Heinzig, Dr. Dennis Walter, and Dr. Satwik Patnaik.

The researchers at the Chair of Processor Design had been an amazing group of people to work with. Martin, with who I first interacted here in the group, helped me immensely in the beginning when I moved here. Michael with whom I have all my initial RFETs discussions. Conny, for helping me out with all the formalities related to my Ph.D. Tuan and Golsa, for our small coffee group. Salim, with whom I started my Ph.D. journey, our discussions on various topics—ranging from research to family to social life. Ash, who is just like my younger brother, someone from whom I can ask for any help at any time of the day. My present roommate is Steffen, one of the coolest German I have met. Behnaz, Yuhao, and Zahra with whom I had various kinds of discussions. Thanks to all of you guys for making my time invaluable here. I would also like to extend my thanks to the graduate and undergraduate students I worked with — Pallab, Aditya, Abhiroop, Martin, Nishant, Yasasvi, and Gopal.

I would also like to thank my family, particularly my parents who have been a constant support. My mother who was always worried that I don't have the capacity to study. Thanks, mummy for your consistent effort in pushing me throughout my life. My father, who himself holds a Ph.D. degree, has been my first inspiration to pursue this transformation. Bhaiya, bhabhi, Chotu, and my in-laws – thanks for your encouragement at various stages.

The biggest support and the staunchest believer in my abilities has been my wife without whom, I think I would not have even stepped on this journey. She was the one who encouraged me to pursue this and had been always motivating me whenever I was feeling down. She has been very understanding during deadlines when I had to work on weekends and late nights. Special thanks to her for having the greatest gift of our life—our daughter, Avriha.

Shubham Rai

## Contents

| Aı | ostra | Ct      |                                                                | 1    |

|----|-------|---------|----------------------------------------------------------------|------|

| Li | st of | Figure  | es                                                             | xvii |

| Li | st of | Tables  | 3                                                              | xx   |

| 1  | Intr  | oducti  | ion                                                            | 1    |

|    | 1.1   | What    | are emerging reconfigurable nanotechnologies?                  | 3    |

|    | 1.2   | Why d   | loes this technology look so promising?                        | 5    |

|    | 1.3   | Electro | onics Design Automation                                        | 5    |

|    | 1.4   | The ga  | ame of see-saw: key challenges vs benefits for emerging recon- |      |

|    |       | figural | ble nanotechnologies                                           | 8    |

|    |       | 1.4.1   | Abstracting ambipolarity in logic gate designs                 | 9    |

|    |       | 1.4.2   | Enabling electronic design automation for RFETs                | 11   |

|    |       | 1.4.3   | Enhanced functionality: a suitable fit for hardware security   |      |

|    |       |         | applications                                                   |      |

|    | 1.5   | Resear  | rch questions                                                  | 15   |

|    | 1.6   | Entire  | RFET-centric EDA Flow                                          | 16   |

|    | 1.7   | Key C   | Contributions and Thesis Organization                          | 19   |

| 2  | Pre   | limina  | ries                                                           | 23   |

|    | 2.1   | Recon   | figurable Nanotechnology                                       | 23   |

|    |       | 2.1.1   | 1D devices                                                     | 26   |

|    |       | 2.1.2   | 2D devices                                                     | 28   |

|    |       | 2.1.3   | Factors favoring circuit-flexibility                           | 29   |

|    | 2.2   | Feasib  | ility aspects of RFET technology                               | 31   |

|   | 2.3 | Logic  | Synthesis Preliminaries                                           | 33        |

|---|-----|--------|-------------------------------------------------------------------|-----------|

|   |     | 2.3.1  | Circuit Model                                                     | 34        |

|   |     | 2.3.2  | Boolean Algebra                                                   | 34        |

|   |     | 2.3.3  | Monotone Function and the property of Unateness                   | 34        |

|   |     | 2.3.4  | Logic Representations                                             | 35        |

| 3 | Exp |        | Circuit Design Topologies for RFETs                               | 37        |

|   | 3.1 |        | ibutions                                                          | 38        |

|   | 3.2 | Organ  | ization                                                           | 38        |

|   | 3.3 |        | ed Works                                                          | 39        |

|   | 3.4 |        | ring design topologies for combinational circuits: functionality- |           |

|   |     | enhan  | ced logic gates                                                   | 39        |

|   |     | 3.4.1  | List of Combinational Functionality-Enhanced Logic Gates          |           |

|   |     |        | based on RFETs                                                    | 39        |

|   |     | 3.4.2  | Estimation of gate delay using the logical effort theory          | 42        |

|   | 3.5 |        | able design of Inverters                                          | 44        |

|   | 3.6 |        | ntial Circuits                                                    | 44        |

|   |     | 3.6.1  | Dual edge-triggered TSPC-based D-flip flop                        | 44        |

|   |     | 3.6.2  | Exploiting RFET's ambipolarity for metastability                  | 45        |

|   | 3.7 |        | ations                                                            | 47        |

|   |     | 3.7.1  | Evaluation of combinational logic gates                           | 47        |

|   |     | 3.7.2  | Novel design of 1-bit ALU                                         | 51        |

|   |     | 3.7.3  | Comparison of the sequential circuit with an equivalent           |           |

|   |     |        | CMOS-based design                                                 | 54        |

|   | 3.8 | Concl  | uding remarks                                                     | 55        |

| 4 | Sta | ndard  | Cells and Technology Mapping                                      | <b>57</b> |

|   | 4.1 |        | ibutions                                                          | 58        |

|   | 4.2 | Organ  | ization                                                           | 59        |

|   | 4.3 |        | ed Work                                                           | 59        |

|   | 4.4 | Standa | ard cells based on RFETs                                          | 60        |

|   |     | 4.4.1  | Interchangeable Pull-Up and Pull-Down Networks                    | 60        |

|   |     | 4.4.2  | Reconfigurable Truth-Table                                        | 61        |

|   | 4.5 |        | ing standard cells                                                | 63        |

|   | 4.6 | HOF-   | based Technology Mapping Flow for RFETs-based circuits .          |           |

|   |     | 4.6.1  | Area adjustments through inverter sharings                        |           |

|   |     | 4.6.2  | Technology Mapping Flow                                           | 67        |

|   |     | 4.6.3  | Realizing Parameters For The Generic Library                      | 68        |

|   |     | 4.6.4  | Defining RFETs-based Genlib for HOF-based mapping                 | 69        |

|   | 4.7 | Exper  | iments                                                            | 70        |

|   |     | 4.7.1  | Experiment 1: Distilling standard-cells from a benchmark          |           |

|   |     |        | suite                                                             | 71        |

|   |     | 4.7.2  | Experiment 2A: HOF-based mapping                                  | 71        |

|   |            | 4.7.3         | Experiment 2B: Using the distilled standard-cells during |          |

|---|------------|---------------|----------------------------------------------------------|----------|

|   |            |               | TTO                                                      | 76       |

|   | 4.8        | Conclu        | ding Remarks                                             | 79       |

| 5 | Log        | ia Crost      | thesis with XOR-Majority Graphs                          | 33       |

| J | 5.1        |               |                                                          | 84       |

|   | 5.2        |               |                                                          | 85       |

|   | 5.2        | _             |                                                          | 85       |

|   | 5.4        |               |                                                          | 87       |

|   | 0.1        | 5.4.1         |                                                          | 87       |

|   |            | 5.4.1         |                                                          | 87       |

|   |            | 5.4.2 $5.4.3$ |                                                          | 88       |

|   |            | 5.4.4         |                                                          | 88       |

|   |            | 5.4.5         |                                                          | 89       |

|   | 5.5        |               |                                                          | 89       |

|   | 0.0        | 5.5.1         |                                                          | 89       |

|   |            | 5.5.1         |                                                          | 90       |

|   | 5.6        |               |                                                          | 90<br>91 |

|   | 5.0        | 5.6.1         |                                                          | 91<br>92 |

|   |            | 5.6.2         |                                                          | 92<br>93 |

|   | 5.7        |               | ~                                                        | 95<br>95 |

|   | 5.7        | 5.7.1         |                                                          | 95<br>95 |

|   |            | 5.7.1         |                                                          | 95<br>96 |

|   | 5.8        |               | 11 1 0                                                   | 90<br>97 |

|   | 5.8<br>5.9 |               | 0                                                        | 91<br>98 |

|   | 5.9        |               |                                                          |          |

|   |            | 5.9.1         |                                                          | 98       |

|   |            | 5.9.2         | 1                                                        | 99       |

|   |            | 5.9.3         |                                                          | 99       |

|   | F 10       | 5.9.4         | Cryptographic benchmark suite                            |          |

|   | 5.10       | Concil        | iding remarks and future research directions             | 07       |

| 6 | Phy        | sical s       | ynthesis flow and liberty generation 10                  | 9        |

|   | 6.1        |               | butions                                                  | 10       |

|   | 6.2        | Organi        | ization                                                  | 11       |

|   | 6.3        | _             | round and Related Work                                   |          |

|   |            | 6.3.1         |                                                          |          |

|   |            | 6.3.2         | Motivation                                               |          |

|   | 6.4        | Silicon       | Nanowire Reconfigurable Transistors                      |          |

|   | 6.5        |               |                                                          | 14       |

|   | -          | 6.5.1         | ~                                                        | 14       |

|   |            | 6.5.2         |                                                          | 14       |

|   | 6.6        |               | •                                                        | 15       |

|   | 6.7        |               |                                                          | 16       |

|   | - •        | 6.7.1         |                                                          | 17       |

|   |            |               | $\sim$                                                   |          |

|                  |              | 6.7.2 Open-source Flow                                              |       |

|------------------|--------------|---------------------------------------------------------------------|-------|

|                  |              | 6.7.3 Concept of Driver Cells                                       |       |

|                  |              | 6.7.4 Native Approach                                               |       |

|                  |              | 6.7.5 Island-based Approach                                         |       |

|                  |              | 6.7.6 Utilization Factor                                            |       |

|                  |              | 6.7.7 Placement of the Island on the Chip                           |       |

|                  | 6.8          | Experiments                                                         |       |

|                  |              | 6.8.1 Preliminary comparison with CMOS technology                   |       |

|                  | 0.0          | 6.8.2 Evaluating different physical synthesis approaches            |       |

|                  | 6.9          | Results and discussions                                             |       |

|                  |              | 6.9.1 Parameters Which Affect The Area                              |       |

|                  | C 10         | 6.9.2 Use of Germanium Nanowires Channels                           |       |

|                  | 0.10         | Concluding Remarks                                                  | . 131 |

| 7                |              | ymporphic Primitives for Hardware Security  Contributions           | 133   |

|                  | $7.1 \\ 7.2$ | Organization                                                        |       |

|                  | 7.2          |                                                                     |       |

|                  |              | The Shift To Explore Emerging Technologies For Security             |       |

|                  | 7.4          | Background                                                          |       |

|                  |              |                                                                     |       |

|                  | 7.5          | 7.4.2 Preliminaries                                                 |       |

|                  | 1.5          | 7.5.1 RFETs for logic locking (transistor-level locking)            |       |

|                  |              | 7.5.2 RFETs for split manufacturing                                 |       |

|                  | 7.6          | Security Vulnerabilities                                            |       |

|                  | 1.0          | 7.6.1 Realization of short-circuit and open-circuit scenarios in an | 140   |

|                  |              | RFET-based inverter                                                 | 1/12  |

|                  |              | 7.6.2 Circuit evaluation on sub-circuits                            |       |

|                  |              | 7.6.3 Reliability concerns: A consequence of short-circuit scenario |       |

|                  |              | 7.6.4 Implication of the proposed security vulnerability            |       |

|                  | 7.7          | Analytical Evaluation                                               |       |

|                  | • • •        | 7.7.1 Investigating the security promises                           |       |

|                  |              | 7.7.2 Investigating the security vulnerabilities                    |       |

|                  | 7.8          | Concluding remarks and future research directions                   |       |

| 8                | Con          | nclusion                                                            | 161   |

|                  | 8.1          | Concluding Remarks                                                  |       |

|                  | 8.2          | Directions for Future Work                                          | 165   |

| $\mathbf{A}_{]}$ | ppen         | dices                                                               | 169   |

| A                | RFI          | ETs-based Genlib                                                    | 171   |

| R                | Dist         | tilling Standard-Cells                                              | 173   |

| ·                | וטועב        | mme Sumuai a-Coms                                                   | T 1 O |

| $\mathbf{C}$ | Layout Extraction file (.lef) for SiNW RFETs | 189 |

|--------------|----------------------------------------------|-----|

| D            | Liberty (.1ib) file for SiNW RFETs           | 193 |

# List of Figures

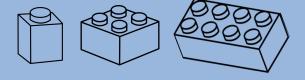

| 1.1          | Various emerging technologies have been compared in [BY17]. The figure shows switching energy and delay for a 32-bit arithmetic logic unit circuit                                          | 2  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

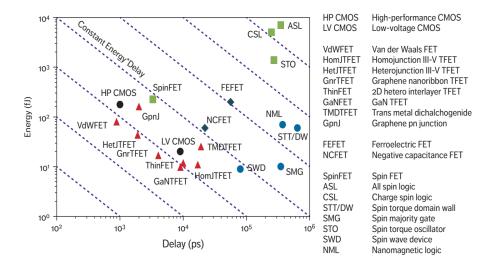

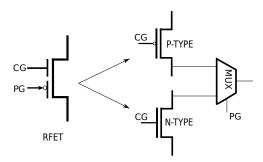

| 1.2          | unit circuit                                                                                                                                                                                | Δ  |

|              | between p- and n-type behavior. Experimental data showcasing near-symmetrical electrical properties for both p- and n-type behavior.                                                        | 4  |

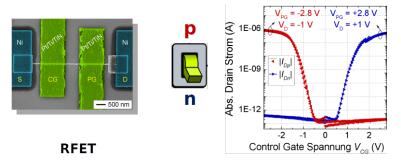

| 1.3          | Various stages in EDA                                                                                                                                                                       | 6  |

| 1.4          | RFET based logic Gate and comparison with CMOS                                                                                                                                              | 10 |

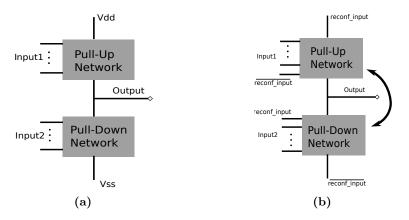

| 1.5          | (a) Fixed pull-up and pull-down network in the case of complimentary MOS logic gates. (b) Interchangeable pull-up and pull-down network in case of RFET-based logic gates. The reconf_input | 10 |

| 1.0          | decides the logic functionality.                                                                                                                                                            | 10 |

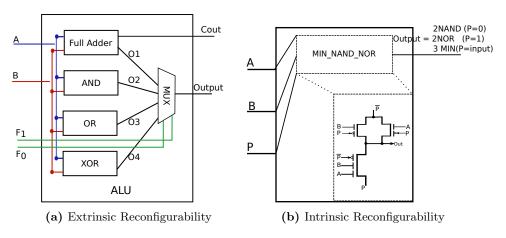

| $1.6 \\ 1.7$ | Reconfigurability in terms of logical abstraction                                                                                                                                           | 11 |

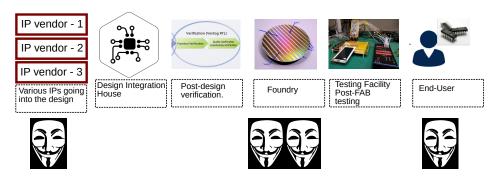

| 1.8          | various phases                                                                                                                                                                              | 13 |

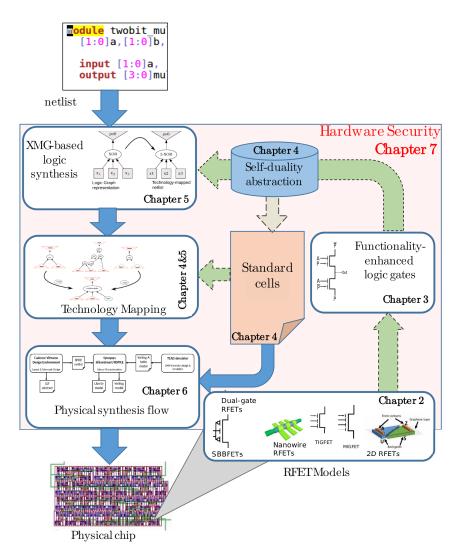

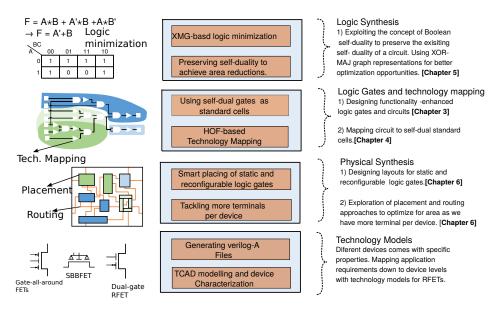

| 1.9          | Entire RFET-centric EDA flow starting from a given netlist to the                                                                                                                           | 14 |

| 1.0          | final layout of the circuit.                                                                                                                                                                | 17 |

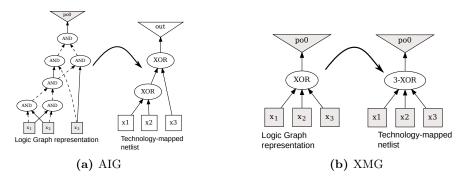

| 1.10 | Using different graph representations for mapping to different logic gates in case of RFETs                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Schematic representation of various RFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |

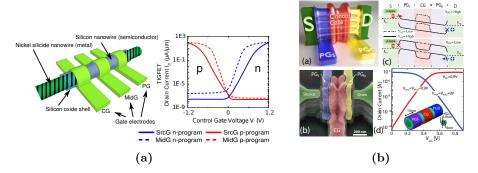

| 2.2  | (a) A representation of a nanowire-based RFETs with three all-around gate structure [Rai+17]. The right figure shows the I-V characteristics. (b) It shows an all-around RFET, called <i>Three-Independent Gate FETs</i> (TIGFETs). The band diagrams are shown from [Rai+18b]                                                                                                                                                                                                                                                        | 26 |

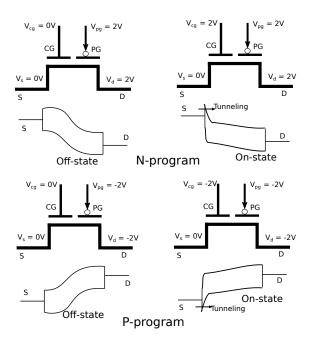

| 2.3  | Conceptual representation of a working principle for a nanowire-based RFET. One can notice how the bands move on application of potential at PG and CG. On-state is $ V_{CG}  = 2V$ and $ V_{CG}  = 0V$ for n and p-type operation, respectively [Tro+15]                                                                                                                                                                                                                                                                             | 27 |

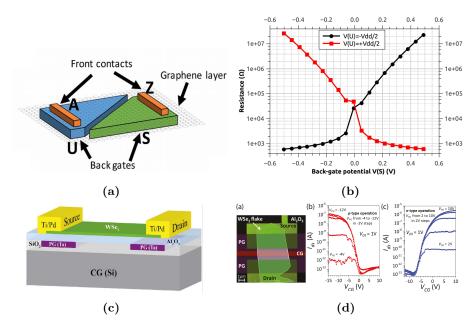

| 2.4  | (a) It shows a graphene p-n junction where the back gates (S and U) work as a control knob to control the ambipolarity. (b) Resistance variation vs backgate potential [Ten+18]. (c) Cross-section of the WSe $_2$ device [Res+16]. (d) Demonstration of WSe $_2$ TIGFET along                                                                                                                                                                                                                                                        |    |

|      | with the transfer characteristics [Res+16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

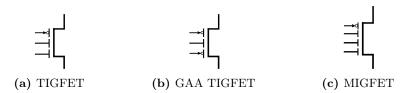

| 2.5  | RFETs with multiple-independent gate terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

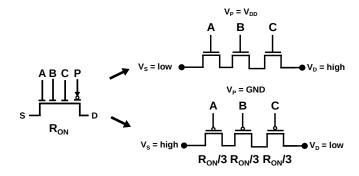

| 2.6  | Equivalent circuit of a multigate RFET with four gates. One single transistor resembles three single gated transistors in series. All three transistors are programmed to p- or n-functionality depending on the applied voltage scheme. In addition, they virtually operate with an effective resistance of only $\frac{1}{3}$ of the internal resistance of                                                                                                                                                                         |    |

|      | the device [Rai+19b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

| 2.7  | Various operating modes in the case of Gate-All Around (GAA) Three-independent gate Field-Effect Transistor (TIGFET)                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

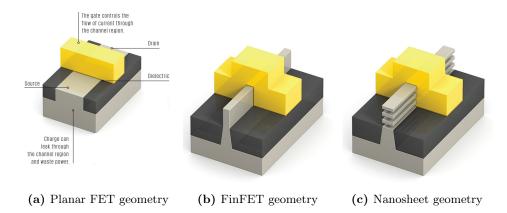

| 2.8  | Evolution of geometry for field-effect transistors [YEK19]. (a) Planar FET designs were popular till 2011. (b) FinFET design were proposed to further reduce the channel width. This covers the channel region from three sides. (c) Stacked nanosheet designs where the gate completely surrounds the channel region to give                                                                                                                                                                                                         |    |

|      | better control than FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 |

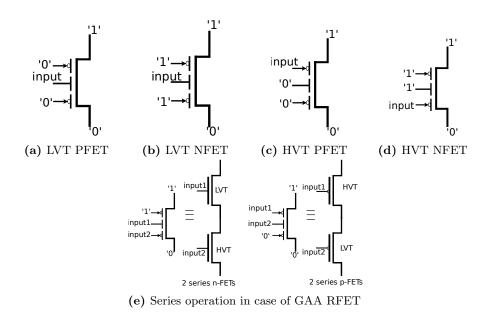

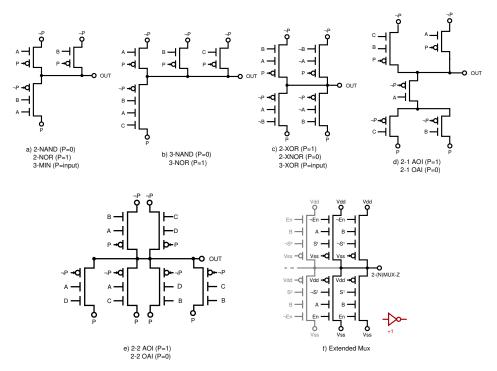

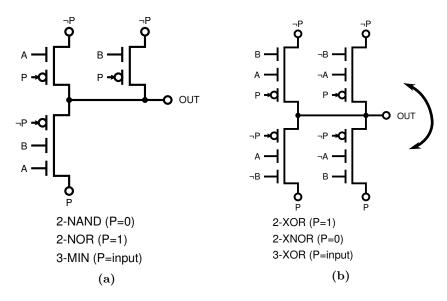

| 3.1  | Efficient combinational logic gates built from multi-independent-gate RFET technology (a) 2NAND and 2NOR; (b) 3NAND and 3NOR; (c) 2XOR and 2XNOR; (d) 2-to-1 AOI and OAI (e) 2-to-2 AOI and OAI and; (f) extended MUX functionality. In the static case, the program signal P is set to GND (0) or $V_{DD}$ (1). A dynamic switching between both functions can be achieved by altering the program signal. In addition the gates (a) and (c) can be executed in a transmission gate style by applying the program gate as additional |    |

|      | input signal to map the 3MIN and 3XOR function, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

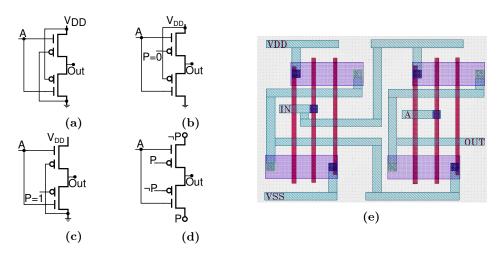

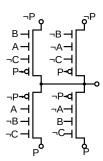

| 3.2 | Different design for inverters (a) static design – the drain, source and program gate are fixed to $V_{dd}$ and $V_{ss}$ respectively (b) One of the transistor's program terminal is connected to 0 (c) One of the transistor's program terminal is connected to 1 (d) Fully reconfigurable design (e) layout for fully polymorphic inverter design as shown in Figure 3.2d | 43       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

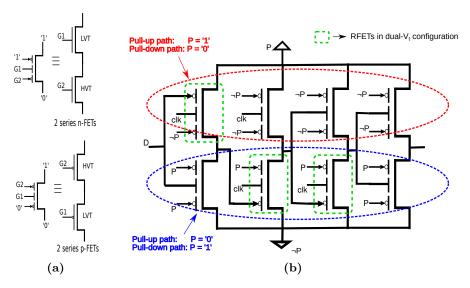

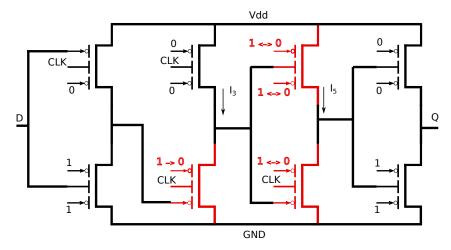

| 3.3 | (a) N-MOS and P-MOS transistor level equivalent models for TIGFETs in dual-threshold voltage configuration (b) A configurable dual edge-triggered D-flip flop based on TSPC logic style                                                                                                                                                                                      | 45       |

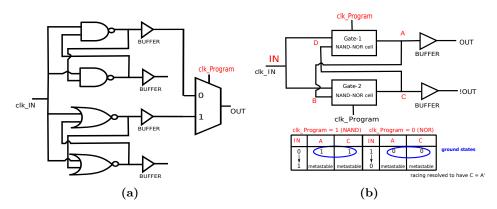

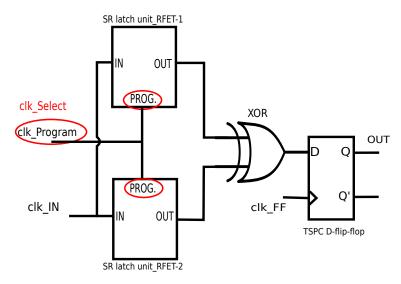

| 3.4 | (a) A configurable <i>Minority</i> (MIN) gate behaving as a NAND gate when $P=$ '1' and NOR gate when $P=$ '0'. (b) An SR latch unit based on minority based NAND-NOR cell                                                                                                                                                                                                   | 46       |

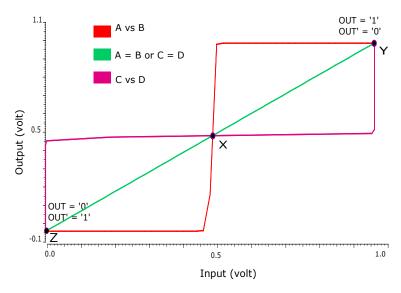

| 3.5 | Butterfly curve in the Voltage-Transfer Characteristic (VTC) for<br>the SR latch unit (Figure 3.4b). 'B' and 'D' are respectively the<br>inputs to Gate-2 and Gate-1, while 'A' and 'C' are respectively the                                                                                                                                                                 | 4.77     |

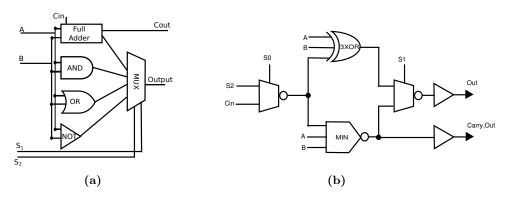

| 3.6 | outputs of Gate-1 and Gate-2                                                                                                                                                                                                                                                                                                                                                 | 47<br>51 |

| 3.7 | A representative RNG schematic. The simulation model consisting of two SR latch units, an XOR gate in DG configuration and the configurable dual edge-triggered TSPC D-flip flop based on RFETs. The CMOS implementation shown in Figure 3.4a is used as the equivalent circuit for comparison                                                                               | 54       |

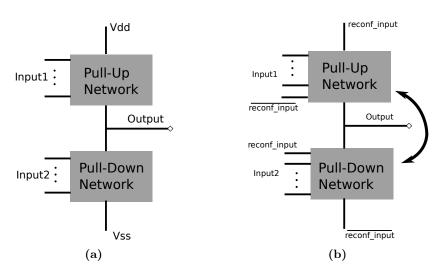

| 4.1 | (a) Fixed pull-up and pull-down network in case of complimentary MOS logic gates. (b) Interchangeable pull-up and pull-down network in case of RFET-based logic gates. The reconf_input decides the logic functionality.                                                                                                                                                     | 60       |

| 4.2 | Reconfigurable logic gate MINORITY and XOR3 demonstrated in [Hei+12; Rai+19b]. It shows how functionality changes with the value of P. With the change in the value of P, pull-up and pull-down networks get interchanged                                                                                                                                                    | 61       |

| 4.3 | Truth-Table for Minority logic gate. The truth-table is split over<br>the value of C (or any other input) which is the reconfigurable input.                                                                                                                                                                                                                                 | 62       |

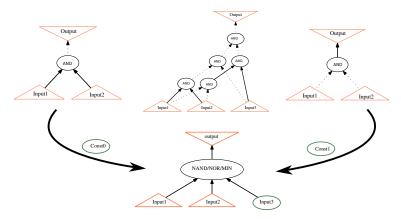

| 4.4 | HOF-based mapping. Three different AIGs using the same logic gate during mapping, albeit with the addition of constant logics. The third input can be const0, const1 or just another input for NAND, NOR or MINORITY logic respectively                                                                                                                                      | 65       |

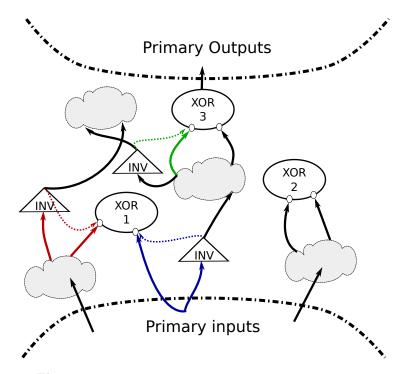

| 4.5 | Area optimization using inverter adjustment                                                                                                                                                                                                                                                                                                                                  | 66       |

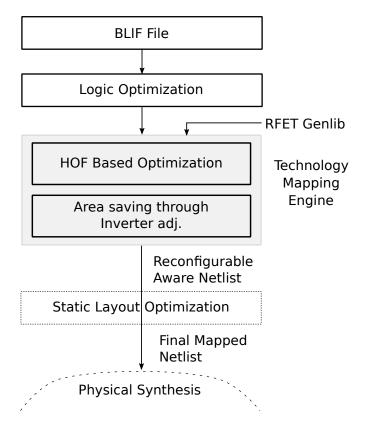

| 4.6 | Entire technology flow suited for RFETs                                                                                                                                                                                                                                                                                                                                      | 68       |

| 4.7 | Realizing parameters for a given function                                                                                                                                                                                                                                                                                                                                    | 69       |

|     |                                                                                                                                                                                                                                                                                                                                                                              |          |

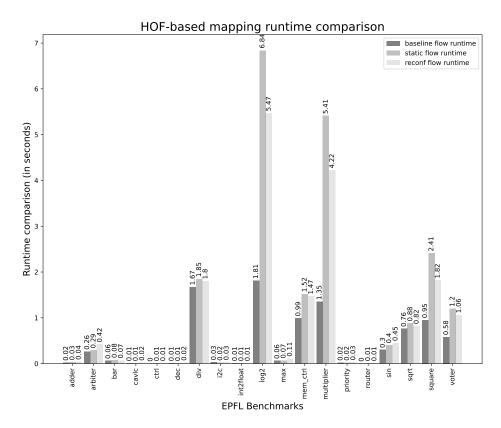

| 4.8        | Runtime comparison. The reconfigurable and static flow has a higher runtime as compared to the baseline flow due to inverter                                                                                                                                                                            |     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

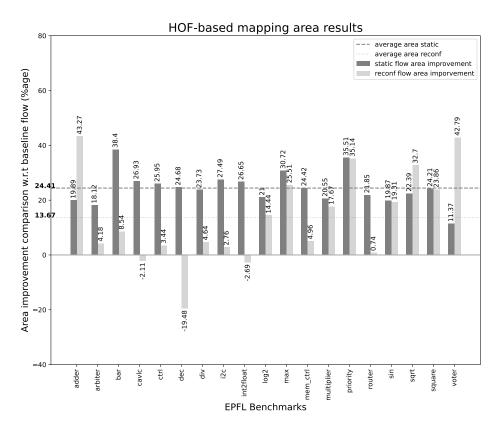

| 4.9        | adjustments                                                                                                                                                                                                                                                                                             | 72  |

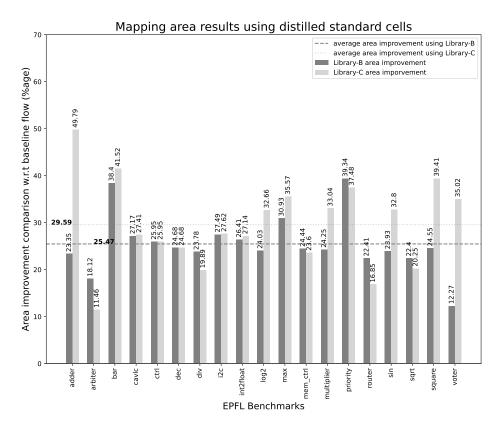

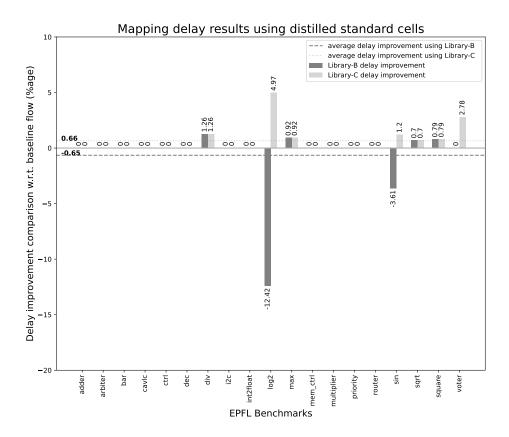

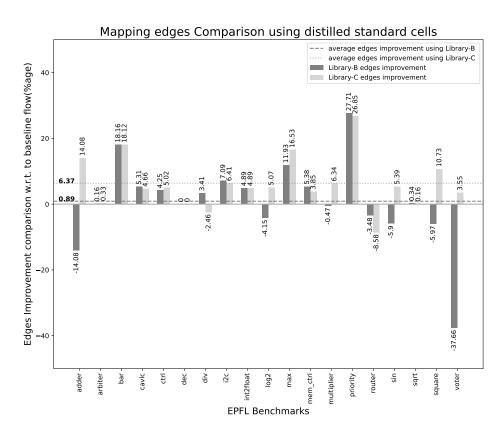

| 4.10       | the baseline is 24.43%                                                                                                                                                                                                                                                                                  | 73  |

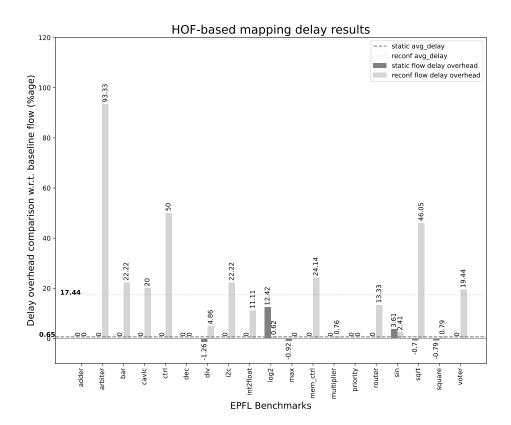

| 4.11       | as compared to the other two flows                                                                                                                                                                                                                                                                      | 75  |

| 4.12       | two flows                                                                                                                                                                                                                                                                                               | 77  |

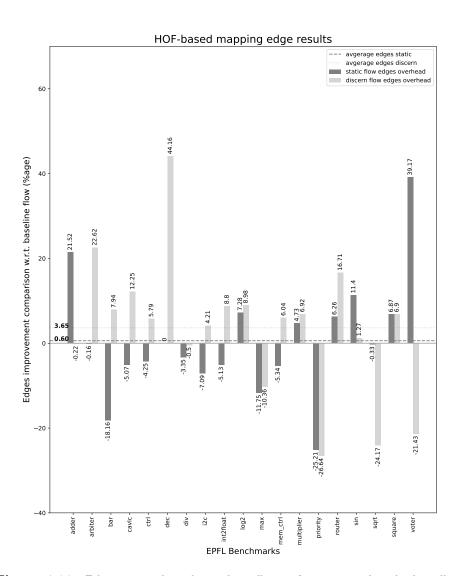

| 4.13       | to the baseline, library-C achieves the best area improvement Delay comparison for various flows. With library-C, the delay                                                                                                                                                                             | 78  |

| 4.14       | improvement of 0.66 is achieved as compared to the baseline flow. Edge comparison for various flows. Both library-B and library-C show an average improvement of 0.89% and 6.37% respectively over                                                                                                      | 79  |

|            | the baseline                                                                                                                                                                                                                                                                                            | 80  |

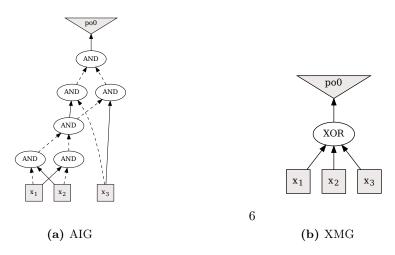

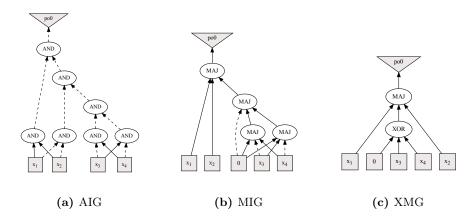

| 5.1<br>5.2 | Edges and nodes representation in case of AIG and XMG representation for the function, $f=x_1\oplus x_2\oplus x_3$ (3-input XOR). The AIG has 6 gates and 13 edges, while the XMG has 1 gate and 4 edges. Different logic representations of the function, $f=\langle x_1,x_2,(x_3\oplus x_4)\rangle$ . | 86  |

| 5.3        | One can notice that the number of nodes and edges are the lowest in the XMG representation                                                                                                                                                                                                              | 90  |

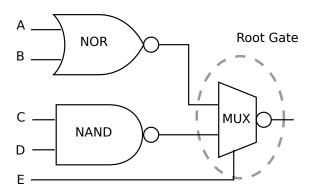

| _ ,        | and NORs as the new input pins. The supergate thus generated has five inputs.                                                                                                                                                                                                                           | 96  |

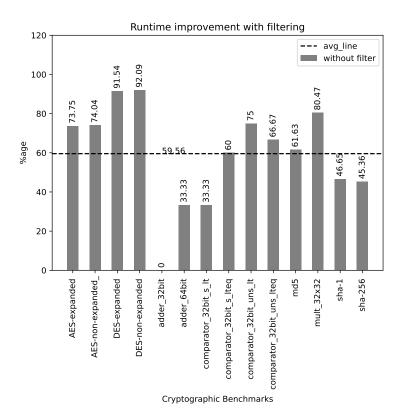

| 5.4        | Runtime improvement in XMG resubstitution using the proposed filtering rule                                                                                                                                                                                                                             | 102 |

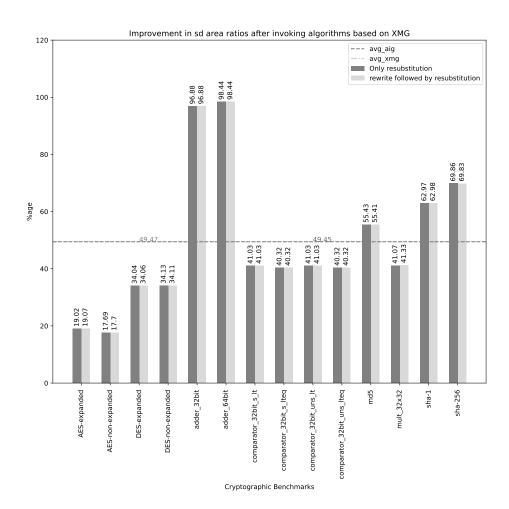

| 5.5        | Improvement of self-duality ratio after calling only resub, rewrite followed by resub. All the algorithms are called until convergence. Self-duality almost remains the same for both these function calls – only resubstitution (49.45%), and rewriting followed by resubstitu-                        |     |

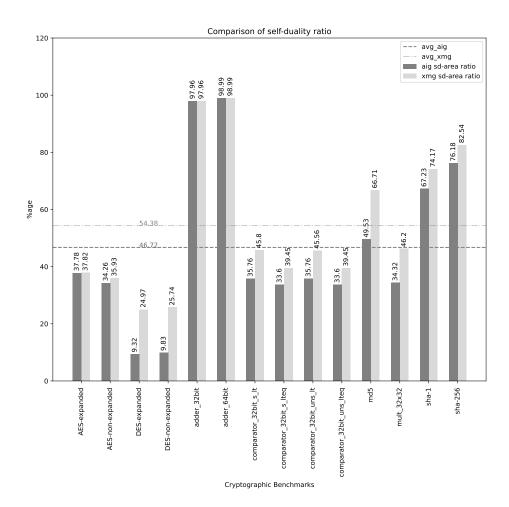

| 5.6        | tion (49.47%). That is why the two lines almost overlap Comparison of final self-duality area ratio between AIG and XMG.                                                                                                                                                                                |     |

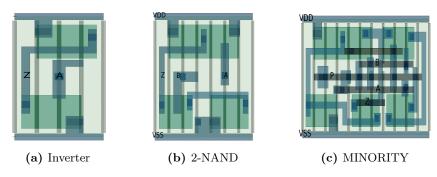

| 6.1        | Layouts of Logic Gates. The first two layouts are for static logic gates while the third one is for the reconfigurable MIN logic gate                                                                                                                                                                   | 113 |

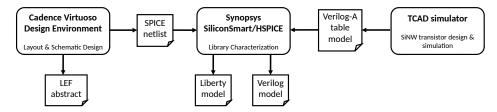

| 6.2        | Tool Flow for liberty characterization for Silicon Nanowire (SiNW) based RFETs.                                                                                                                                                                                                                         | 116 |

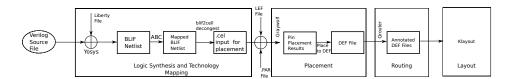

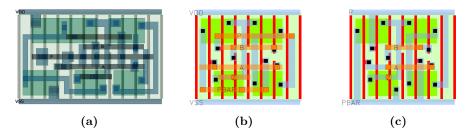

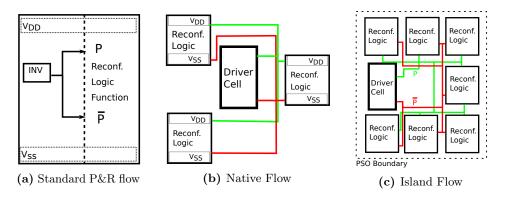

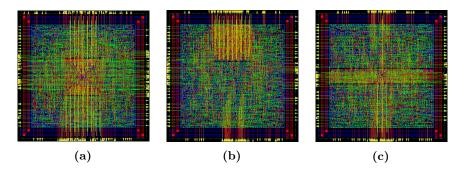

| 6.3  | Open-source physical synthesis flow                                                                                              | 117 |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.4  | (a) Layout of the minority (MIN) logic gate containing an inverter.                                                              |     |

|      | (b) Our newly proposed layout of a $MIN$ gate with P, $\overline{P}$ as separate                                                 |     |

|      | input signals. (c) Our improved MIN gate layout for the PSO                                                                      |     |

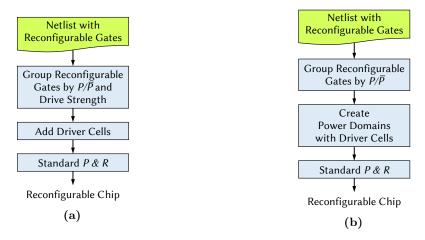

|      | approach                                                                                                                         | 119 |

| 6.5  | Design flows for (a) the native approach and (b) the island-based                                                                |     |

|      | approach                                                                                                                         | 119 |

| 6.6  | Three different approaches for physical synthesis of RFETs-based                                                                 |     |

|      | circuits. (a) Layout of reconfigurable logic gate proposed in [RRK18].                                                           |     |

|      | $P$ and $\overline{P}$ signals are driven by inverting logic embedded within the                                                 |     |

|      | logic gate. (b) Out native approach which removes the inverting                                                                  |     |

|      | logic and uses separate driver cells for generating $P$ and $\overline{P}$ . (c)                                                 |     |

|      | Our PSO-based approach that groups reconfigurable logic gates in                                                                 |     |

|      | power domains which are driven by common $P$ and $\overline{P}$ signals                                                          | 121 |

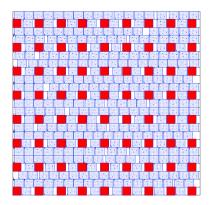

| 6.7  | Power domain for reconfigurable gates in an island-based approach                                                                |     |

|      | that share the same $P/\overline{P}$ . Driver cells are highlighted in red. In                                                   | 100 |

| 60   | this example, we added one driver cell for five reconfigurable gates.                                                            | 122 |

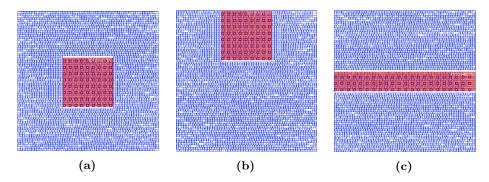

| 6.8  | Power domain configurations that we investigated in our experiments: (a) square in the center, (b) square in the top center, and |     |

|      | (c) rectangle covering the whole width in the center (stand style).                                                              | 122 |

| 6.9  | Layouts of the EPFL $bar$ benchmark with 10% reconfigurable logic                                                                | 144 |

| 0.5  | using the island-based approach. The three layouts correspond to                                                                 |     |

|      | the floorplans in Figure 6.8                                                                                                     | 123 |

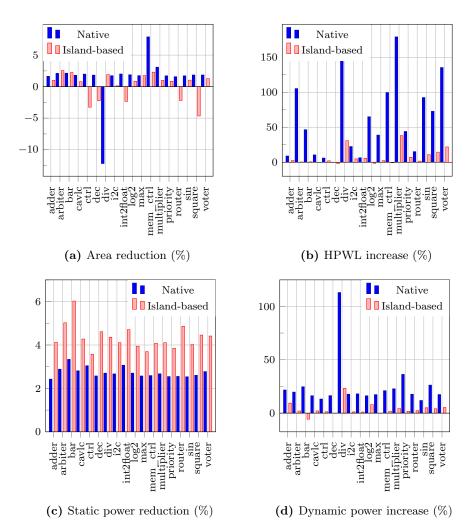

| 6.10 | Comparison of the native approach and the island-based approach                                                                  | 120 |

| 0.10 | with the baseline for a replacement ratio of 0.1, i.e. 10% of the logic                                                          |     |

|      | gates are replaced by reconfigurable logic gates. For each EPFL                                                                  |     |

|      | benchmark, the changes in (a) core area, (b) Half-Perimeter Wire                                                                 |     |

|      | Length (HPWL), (c) static power consumption, and (d) dynamic                                                                     |     |

|      | power consumption from the baseline are shown. For the island-                                                                   |     |

|      | based approach we use the best results of the three power domain                                                                 |     |

|      | configurations in Figure 6.8. Please note that in (a) and (c) higher                                                             |     |

|      | values are better, while in (b) and (d) lower values are desired                                                                 | 127 |

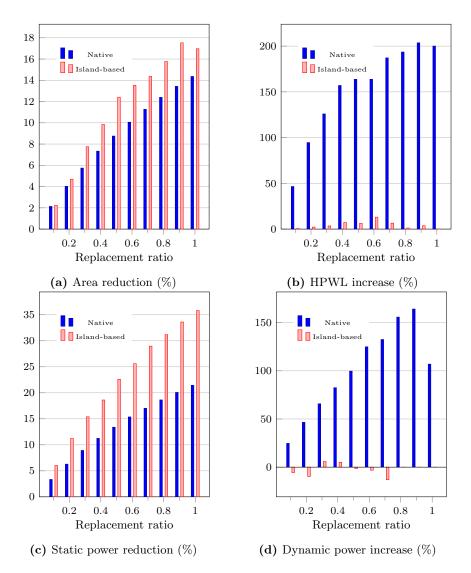

| 6.11 | Changes in (a) core area, (b) HPWL, (c) static power consumption,                                                                |     |

|      | and (d) dynamic power consumption from the baseline for the EPFL                                                                 |     |

|      | bar benchmark with the amount of reconfigurable logic ranging from                                                               |     |

|      | 10 to 100%. For the island-based approach we used the best results                                                               |     |

|      | of the three power domain configurations in Figure 6.8. Please note                                                              |     |

|      | that in (a) and (c) higher values are better, while in (b) and (d)                                                               | 129 |

|      | lower values are desired                                                                                                         | 129 |

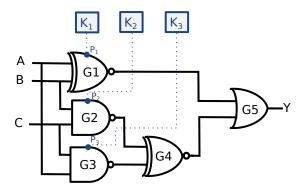

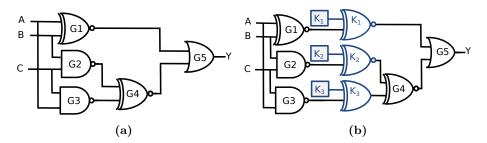

| 7.1  | Illustration of logic locking. (a) Original circuit. (b) Circuit locked                                                          |     |

|      | with three XOR/XNOR key-gates labeled as $K_1$ , $K_2$ , and $K_3$ , re-                                                         |     |

|      | spectively for traditional CMOS technology. The key-bits $K_1$ , $K_2$ ,                                                         |     |

|      | and $K_3$ are driven from an on-chip tamper-proof memory                                                                         | 137 |

|      | · · ·                                                                                                                            |     |

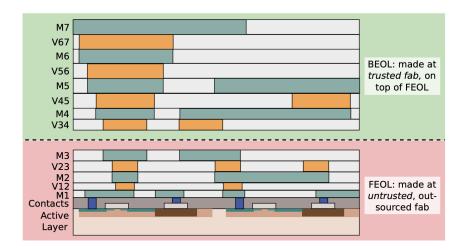

| 7.2  | Concept of classical split manufacturing, i.e., the separation of a physical layout into (Front-End-Of-Line (FEOL)) and Back-end-of-line (Back-End-Of-Line (BEOL)). The different pitches across the metal layers facilitates split manufacturing. © 2018 IEEE. Reprinted, with permission, from [Pat+18c]                                                                                                                                                                                                  | 139 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

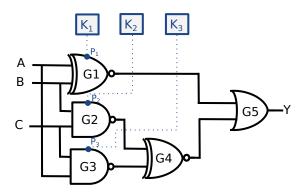

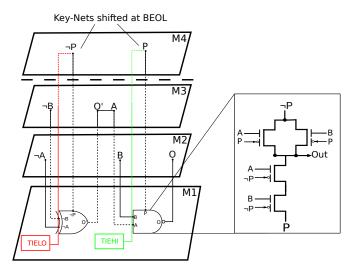

| 7.3  | Logic locking using RFETs, where the program gate (PG) acts as the key-input. Realizing logic locking in conventional CMOS necessitates insertion of additional logic gates whereas in case of RFETs, the program gate can enable logic locking without requiring insertion of additional logic gates. The PG signals are driven from                                                                                                                                                                       | 141 |

| 7.4  | Split manufacturing for RFETs; here, only the program gate (PG) signals are lifted beyond the split layer (in this example, M3) to BEOL (M4). The inset shows the internal transistor-level schematic of the underlying logic gate. These lifted PG signals will be driven by constant 0/1 signals (generated by TIELO/TIEHI cells placed in the FEOL), routed in the BEOL. The absence of placement- and routing-related hints for the key-nets makes the key indecipherable for an FEOL-centric attacker. |     |

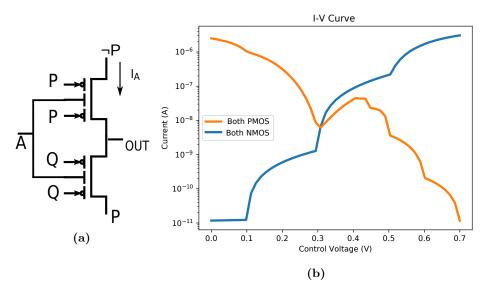

| 7.5  | Exemplifying security vulnerabilities in an RFET-based inverter: (a)                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.6  | two short-circuit configurations, (b) two open-circuit configurations. 1 a) Short-circuit operation possible in case of an inverter by switching on both the transistor in either p-type or n-type at runtime b) Simulation results showing current reaching $10^{-7}$ A range for inverter                                                                                                                                                                                                                 | 144 |

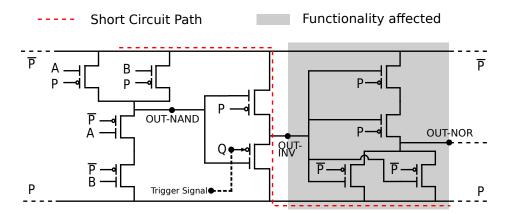

| 7.7  | in two configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 145 |

| 7.8  | through the inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 146 |

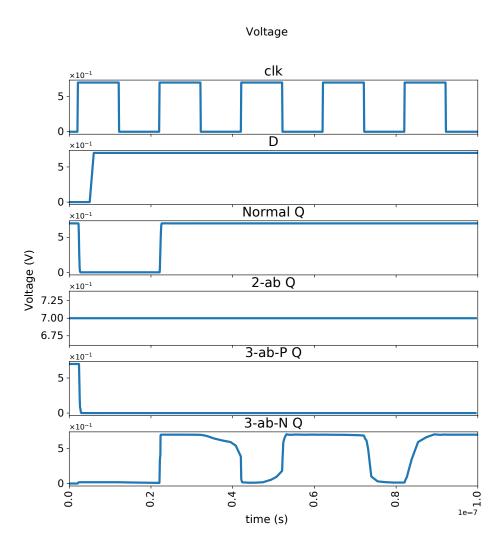

| 7.9  | Voltage values in normal and both short-circuit and open-circuit condition for TSPC-DFF. 2-ab means when the transistor in the                                                                                                                                                                                                                                                                                                                                                                              | 148 |

|      | second stage is configured incorrectly. 3-ab-N and 3-ab-P implies that both the transistors in the third stage are either configured as NMOS and PMOS respectively                                                                                                                                                                                                                                                                                                                                          | 149 |

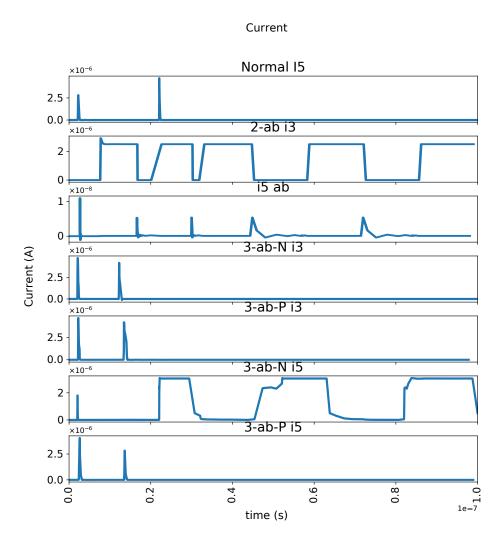

| 7.10 | Current values in normal and both short-circuit and open-circuit condition for TSPC-DFF. 2-ab means when the transistor in the second stage is configured incorrectly. 3-ab-N and 3-ab-P implies that both the transistors in the third stage are either configured as                                                                                                                                                                                                                                      |     |

|      | that both the transistors in the third stage are either configured as NMOS and PMOS respectively                                                                                                                                                                                                                                                                                                                                                                                                            | 150 |

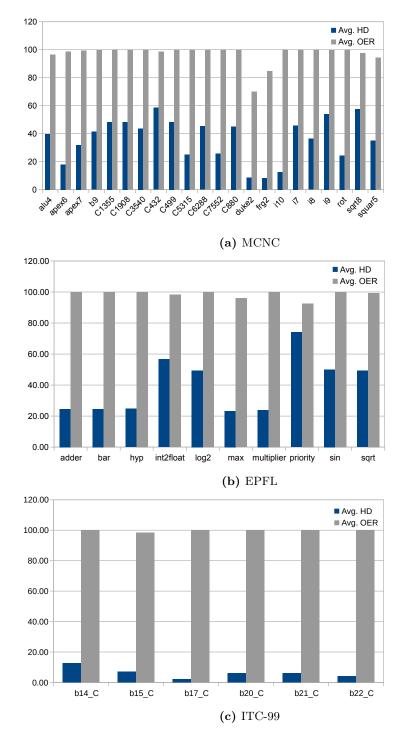

| 7.11 | Evaluation of OER and HD to study the impact of voltage effects on |     |

|------|--------------------------------------------------------------------|-----|

|      | the proposed security vulnerability (a) Average Hamming distance   |     |

|      | and Output error rate for MCNC benchmarks (b) Average Hamming      |     |

|      | distance and Output error rate for $EPFL$ benchmarks (c) Average   |     |

|      | Hamming distance and Output error rate for ITC-99 benchmarks.      | 158 |

|      |                                                                    |     |

| 8.1  | Thesis correlation and important contributions towards enabling    |     |

|      | EDA flow for RFETs-based circuits                                  | 162 |

## List of Tables

| 1.1 | Correspondence between topics, chapters, publications and challenges.                                                                                                                                                                                                      | 21  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Programming RFETs [Tro+15]                                                                                                                                                                                                                                                 | 28  |

| 3.1 | Comparison of transistor count $\#T$ , total logical effort gTot, logical effort per input signal gS and parasitic delay p for static logic implementations of the gates depicted in Figure 3.1                                                                            | 48  |

| 3.2 | Comparison of transistor count #T, total logical effort gTot, logical effort per input signal gS and parasitic delay p for the 6 functionality-enhanced logic gates depicted in Figure 3.1                                                                                 | 50  |

| 3.3 | Novel ALU selection signals                                                                                                                                                                                                                                                | 52  |

| 3.4 | Comparison in terms of area, normalized delay, activity and for the 1-bit ALU designs as shown in Figure 3.6a and Figure 3.6b                                                                                                                                              | 53  |

| 3.5 | A comparison between RFET-based SR latch unit and its CMOS equivalent                                                                                                                                                                                                      | 55  |

| 4.1 | Comparison in the area savings due to inverter adjustments for static and reconfigurable logic gates                                                                                                                                                                       | 74  |

|     | static and reconfiguratic logic gates                                                                                                                                                                                                                                      | 11  |

| 5.1 | Distribution of self-dual functions in NPN                                                                                                                                                                                                                                 | 88  |

| 5.2 | Post-mapping area comparison for synthetic self-dual benchmarks using different synthesis flows. It can be noticed that the proposed XMG-based flow gives the best results. Additionally, it can be noted that the gain (%) is higher for circuit with higher self-duality |     |

|     | density. Hence, improvement increases with higher SD-index 1                                                                                                                                                                                                               | 100 |

| 5.3        | Runtime for XMG resubstitution with and without the proposed filtering rule.                                                                                                                                                                                                | 103 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4        | Comparison of the post-mapping area without the use of supergates. The use of supergates leads to a better area across all the flows particularly with the mockturtle framework (mtl_AIG and Proposed). High self-duality density leads to higher improvement over baseline |     |

|            | for XMG-based flows                                                                                                                                                                                                                                                         | 105 |

| 5.5        | Comparison of ratios of self-dual cuts between AIG and XMG-based representation                                                                                                                                                                                             | 106 |

| 6.1        | Preliminary comparison of post-physical synthesis area between CMOS and SiNW RFET technologies over MCNC benchmarks                                                                                                                                                         | 124 |

| 7.1<br>7.2 | Simulation results showing current drawn and voltage values for different cases of inputs and configurations                                                                                                                                                                | 147 |

| 7.3        | different randomly locked configurations on selected <i>ITC-99</i> benchmarks. Time-out (t-o) is 48 hours. For each benchmark ten trials are used                                                                                                                           | 155 |

|            | function of lifting of program gate signals                                                                                                                                                                                                                                 | 156 |

| A.1        | Contents of the generic library for RFETs                                                                                                                                                                                                                                   | 171 |

| B.1        | List of distilled self-dual functions                                                                                                                                                                                                                                       | 173 |

## CHAPTER 1

#### Introduction

#### Inception

At the time, when I started writing this thesis, the iPhone 13-series was being launched. And, the most striking thing, for me as a researcher, is that the new generation iPhones have been able to shrink the CMOS channel width by yet another 2nm. They used a 5nm technology node which allowed them to use 27% more transistors than the previous generation. Still, this progression is not too far from the quintessential Moore's Law prediction [Moo+65]. Although, area scaling continues roughly at the rate of 0.5 times every two years [BY17], the cost to build transistors and the power consumption per unit transistor have not been able to follow the promises of Moore's law and Dennard scaling methodology [Den+74]. This trend has not been abrupt and the Moore's Law that has been guiding and predicting transistor downsizing from the last five decades is really pushing the physical limits of transistor's channel width, as 1nm is equivalent to the thickness of just 5 silicon atoms!

Transistor downscaling refers to the decrease in the size of the channel length of individual transistors. This has a clear impact on the resistance and power consumption by individual transistors. Particularly at lower technology nodes, power consumption and heat management issues in high-performance integrated circuits are huge problems. It is not about the crude reality of transistor downscaling, but it is about the real physical challenges that lie in the transistor's geometry and routing of metal interconnects at low technology nodes. In spite of these issues, two major factors that allowed CMOS to flourish in the past and the present are

Figure 1.1: Various emerging technologies have been compared in [BY17]. The figure shows switching energy and delay for a 32-bit arithmetic logic unit circuit.

its increased circuit robustness and reduced power dissipation with every new generation.

While the exploration to reach the physical limits of 1 silicon atom widths for integrated circuits still continues, another plausible approach is to look for emerging technologies that can bridge the requirements of future electronics circuits with their unique feature sets [Rai+18b]. The efforts are not directly aimed at replacing CMOS technology for future electronics circuits but to investigate the possibility of using emerging technologies to complement (or supplement) the CMOS technology. Figure 1.1 shows various emerging technologies compared with both high-performance and low-power CMOS technology. All these emerging technologies are compared in terms of switching energy and delay. The figure shows a clear perspective on various technologies and indicates which technologies are worth exploring in terms of these two parameters. While this figure showcases experimental data for various technology, another crucial factor that drives the adoption of a specific emerging technology is the ease of fabrication and coherence with the existing fabrication setup of CMOS. Establishing a new foundry setup requires a multi-billion dollar investment. Hence, an emerging technology can be readily adopted if there is a partial or full overlap with the established setup in terms of their manufacturing. And, this is where the emerging reconfigurable nanotechnology can be a game-changer as it promises new computational capabilities and is also compatible with the existing top-down fabrication stack of the contemporary CMOS [Sim+16; Mik+17].

One of the decisive prerequisites to efficiently integrate emerging nanotechnologies into commercial electronics is the consideration of the physical properties of

1. Introduction 3

the technologies within the EDA flow [Ama+15b; Rai+18b]. Devising efficient flows is necessary to accelerate the commercial feasibility of newer nanotechnologies. The recent development of a modern RISC-V processor made with Carbon Nanotube Field-Effect Transistors (CNTFETs) is one such example of a practical circuit based on beyond-CMOS technologies [Hil+19]. The constant debate over emerging nanotechnologies compared to existing silicon-based CMOS technologies and the complexities involved in the overall design flow, has so far precluded realization and development of strong examples for electronic circuits. The work done in [Hil+19] stands out as a stepping stone to solve the ever-increasing problem with CMOS dimension-scaling and the growing skew between cost and performance for CMOS-based circuits [BY17]. Hence, exploring emerging nano-devices is not just an academic exercise but an imperative demand to meet the requirements of future electronics [Rai+18b].

In this direction, the thesis explores the feasibility of emerging nanotechnology called Reconfigurable Nanotechnology through the lens of design automation. Reconfigurable nanotechnology boasts of a remarkable feature where individual transistors can be tuned to either demonstrate a p-type or an n-type functionality. Within the research community, such devices are termed as Reconfigurable Field-Effect Transistor (RFET) or Polarity-Control devices. Apart from exhibiting transistor-level dynamic reconfiguration, these devices offer flexibility in terms of power and come with low leakage power dissipation [Mik+17]. Efficient circuit designs have been proposed in the literature exploiting these exciting properties [Rai+17; Tro+16; Gai+13b]. However, the non-existence of a well-formalized EDA flow to build circuits with RFETs, opens up a major research direction which is still under-explored. Owing to these special benefits offered by reconfigurable nanotechnology, this thesis devises new techniques and approaches for enabling design automation for RFETs-based circuits such as defining logical abstraction for logic synthesis flows, designing standard cells for technology-independent mapping, and formalizing a physical synthesis flow compatible with existing industrial tool-flows for RFETs-based circuits. The circuit design paradigms drive efforts in EDA to propose RFET-centric synthesis flow that (i) gives trustworthy predictions for circuits based on RFETs and (ii) provides complete design flow which can be used to build actual circuits based on RFETs. The thesis also investigates suitable application scenarios for such an exciting technology and maps the technology's feature set with the demands of Hardware Security. It proposes various circuit design paradigms and lays down approaches that can be used in hardware security applications.

# 1.1 What Are Emerging Reconfigurable Nanotechnologies?

Emerging reconfigurable nanotechnology is driven by transistors that exhibit ambipolarity at the transistor level. Ambipolarity is a property by which both

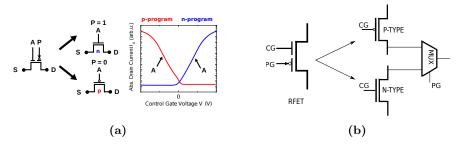

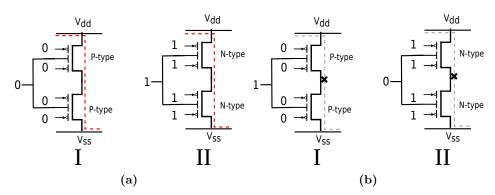

Figure 1.2: Current-Voltage characteristics showing reconfigurable device properties. The switch analogy demonstrate the dynamic reconfiguration between p- and n-type behavior. Experimental data showcasing near-symmetrical electrical properties for both p- and n-type behavior.

charge carriers – electrons and holes – can tunnel through an electrostatic barrier. With process techniques, ambipolarity can be enhanced to demonstrate electrical symmetry in both types of conduction, thereby enabling transistors to demonstrate both p- and n-type properties independently on the application of external bias potential. This enables dynamic reconfiguration of individual transistors either as a p-channel Field-Effect Transistor (PFET) or n-channel Field-Effect Transistor (NFET). This dynamic reconfiguration in RFETs is not facilitated using chemical doping caused by impurities but rather due to electrostatic doping [Mik+17] caused by an external bias potential. Exemplary I-V characteristics for an RFET is shown in Figure 1.2 [Hei+13]. The right figure shows near-symmetrical I-V characteristics for both p and n-type configurations. Reconfigurable transistors encapsulate the functionality of two different devices (PFET and NFET) into a single device. The symmetric I-V characteristics allows (re-)programmability of transistor's conductivity as a device that *switches* its properties from p-type to n-type functionality [Tro+16].

The special property of dynamic reconfiguration enabled by metal-semiconductor-metal contacts further allows symmetric electrical conduction in both p- and n-type behavior [Tro+15]. RFETs, just like CMOS devices come with the same set of terminals – source, drain, bulk, and gate. However, unlike CMOS, RFETs have two types of gate terminals – the *Program Gate* (PG) and the *Control Gate* (CG). The Control Gate (CG) is the same as that in the case of CMOS that controls the flow of charge carriers while the PG controls the type of the charge carriers flowing through the channel. The bias applied at the PG configures the transistor to function either as a p-type or n-type device. Additionally, transistors belonging to reconfigurable nanotechnology allow multiple gate terminals on a single channel [Sim+18]. The possibility of having multiple gate terminals on a single channel within a reconfigurable device opens up new circuit design opportunities that were not possible using the classical Field-Effect Transistor (FET). The

1. INTRODUCTION 5

CMOS-style complementary pull-up and pull-down networks are thus, enriched by the above-mentioned features and can be tuned to provide more functionalities per computation unit. To address the atavistic excitement of a reader, a simple manifestation of such interesting properties in a circuit design is to have NANDs and NORs with equal performance and equal area.

# 1.2 Why Does This Technology Look So Promising?

The combination of dynamic reconfiguration between p and n-type behavior at the transistor level, and the possibility of having multiple gate terminals on a single channel opens up new design opportunities for circuits based on reconfigurable nanotechnology. First, since the p- and n-type configurations exhibit symmetrical electrical conduction, pull-up and pull-down networks offer equal current drive strengths. Hence, unlike CMOS technology, effort for transistor sizing can be saved in the case of circuits based on RFETs. This symmetry in conduction for both p- and n-type configuration allows flexibility during (i) the design of circuit topologies [Rai+17; GAM14], (ii) the design of layouts for standard cells [BM15; Reu+21] and (ii) the placement and routing of individual cells [Kri+21]. Second, having multiple gate terminals on a single channel reduces the channel on-resistance per input [Tro+16]. This allows multiple inputs to be connected to a single transistor, thereby allowing efficient logic gate designs with more than 2 inputs. Additionally, multiple gate terminals also play an important role in controlling the performance of a logic gate [Zha+14b].