### **Clemson University**

## **TigerPrints**

All Dissertations **Dissertations**

8-2022

# Holistic Performance Analysis and Optimization of Unified Virtual Memory

Tyler Allen tnallen@clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations

Part of the OS and Networks Commons, and the Systems Architecture Commons

#### **Recommended Citation**

Allen, Tyler, "Holistic Performance Analysis and Optimization of Unified Virtual Memory" (2022). All Dissertations. 3092.

https://tigerprints.clemson.edu/all\_dissertations/3092

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

# HOLISTIC PERFORMANCE ANALYSIS AND OPTIMIZATION OF UNIFIED VIRTUAL MEMORY

A Dissertation Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Computer Science

by Tyler Allen August 2022

Accepted by:

Dr. Rong Ge, Committee Chair

Dr. Amy Apon

Dr. Jon Calhoun

Dr. Jacob Sorber

## Abstract

The programming difficulty of creating GPU-accelerated high performance computing (HPC) codes has been greatly reduced by the advent of Unified Memory technologies that abstract the management of physical memory away from the developer. However, these systems incur substantial overhead that paradoxically grows for codes where these technologies are most useful. While these technologies are increasingly adopted for use in modern HPC frameworks and applications, the performance cost reduces the efficiency of these systems and turns away some developers from adoption entirely. These systems are naturally difficult to optimize due to the large number of interconnected hardware and software components that must be untangled to perform thorough analysis.

In this thesis, we take the first deep dive into a functional implementation of a Unified Memory system, NVIDIA UVM, to evaluate the performance and characteristics of these systems. We show specific hardware and software interactions that cause serialization between host and devices. We further provide a quantitative evaluation of fault handling for various applications under different scenarios, including prefetching and oversubscription. Through lower-level analysis, we find that the driver workload is dependent on the interactions among application access patterns, GPU hardware constraints, and Host OS components. These findings indicate that the cost of host OS components is significant and present across UM implementations. We also provide a proof-of-concept asynchronous approach to memory management in UVM that allows for reduced system overhead and improved application performance. This study provides constructive insight into future implementations and systems, such as Heterogeneous Memory Management.

# Table of Contents

| Ti | itle Page                                                                                                                          | j                           |

|----|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| A  | bstract                                                                                                                            | i                           |

| Li | ist of Tables                                                                                                                      | v                           |

| Li | ist of Figures                                                                                                                     | V                           |

| 1  | Introduction  1.1 Demand Paging Virtual Memory  1.2 Heterogeneous Shared Memory  1.3 The Cost of UVM  1.4 Summary of Contributions | 1<br>3<br>4<br>8            |

| 2  | 2.2 UVM Architecture                                                                                                               | 11<br>14<br>18<br>20        |

| 3  | 3.2 UVM Workload Creation                                                                                                          | 25<br>25<br>26<br>31        |

| 4  | 4.1 Data Movement                                                                                                                  | 35<br>36<br>37<br>40<br>41  |

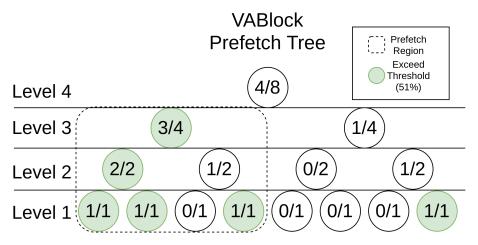

| 5  | 5.1 Prefetching                                                                                                                    | 44<br>49<br>54              |

| 6  | 6.2 Preemptive Asynchronous Host Page Unmapping                                                                                    | <b>58</b><br>58<br>59<br>60 |

| 7  | Conclusion                                                                                                                         | 65                          |

| Bibliog | graphy                              |  |       | <br> |  |  |  |  |  | <br> |  |   | . 70 |

|---------|-------------------------------------|--|-------|------|--|--|--|--|--|------|--|---|------|

| 7.2     | Discussion and Future Work          |  | <br>• |      |  |  |  |  |  | •    |  | • | 67   |

| 7.1     | Key Systems Costs and Optimization. |  |       |      |  |  |  |  |  |      |  |   | 65   |

# List of Tables

| 3.1 | Per-SM Batch Source Statistics      | 30 |

|-----|-------------------------------------|----|

| 4.1 | Per-VABlock Batch Source Statistics | 40 |

|     | Application Fault Reduction         |    |

| 5.2 | SGEMM Fault Scaling                 | 5. |

# List of Figures

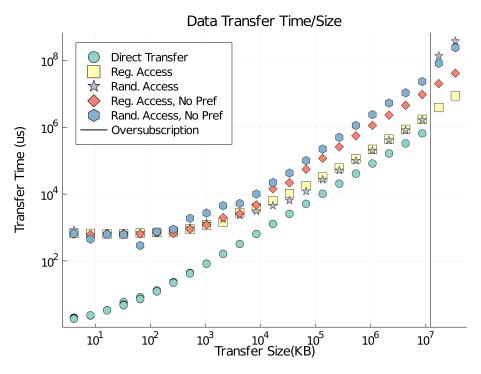

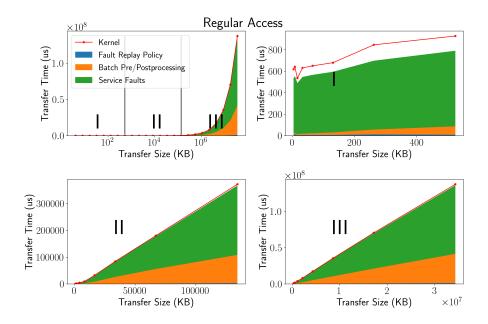

| 1.1 | UVM access incurs one or more orders of magnitude greater latency than direct data transfer                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

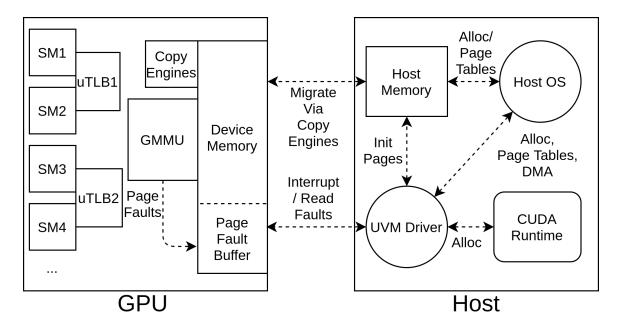

| 2.1 | Faults propagate from SMs through the $\mu$ TLB to the GMMU, which can write faults directly to the fault buffer. The UVM driver reads groups or <i>fault batch</i> of faults from the fault buffer. After processed, the requested data is migrated to the GPU through copy engines and page mapped appropriately                                                                                                                                                                                           | 15 |

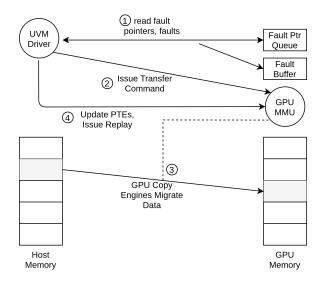

| 2.2 | UVM Fault-Handling Communication Architecture. (1) The UVM driver reads fault pointers out of a queue. The pointers lead to the specific fault entry in the fault buffer. Faults are cached on the host. (2) After processing, the driver will alert the GPU of data to be transferred. (3) The GPU will initiate the data transfer to GPU memory through DMA. (4) After one or more repetitions, the CPU will issue a replay to the GPU. Omitted: The UVM driver is initially prompted by a GPU-originating | 16 |

| 2.3 | trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 |

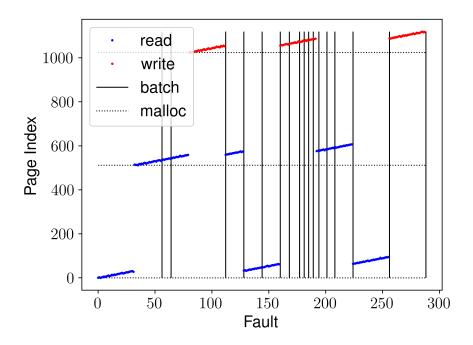

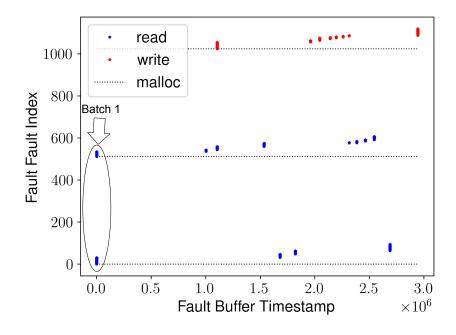

| 3.1 | Relative time series of vector addition faults pulled from fault buffer, divided on the x-axis by <i>driver batch</i> and y-axis by <i>memory allocation</i>                                                                                                                                                                                                                                                                                                                                                 | 28 |

| 3.2 | Fault data from figure 3.1 represented with real-time timestamp of when the fault arrived in the fault buffer. Faults clustered tightly vertically always indicate a batch.                                                                                                                                                                                                                                                                                                                                  | 28 |

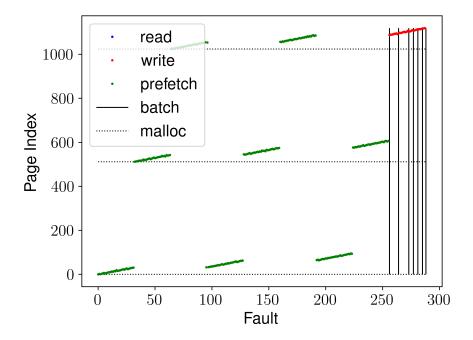

| 3.3 | A single warp is capable of generating faults up to the batch size limit using prefetching. Prefetching is not beholden to outstanding fault limitations, and does not trigger                                                                                                                                                                                                                                                                                                                               |    |

| 3.4 | fault-throttling mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

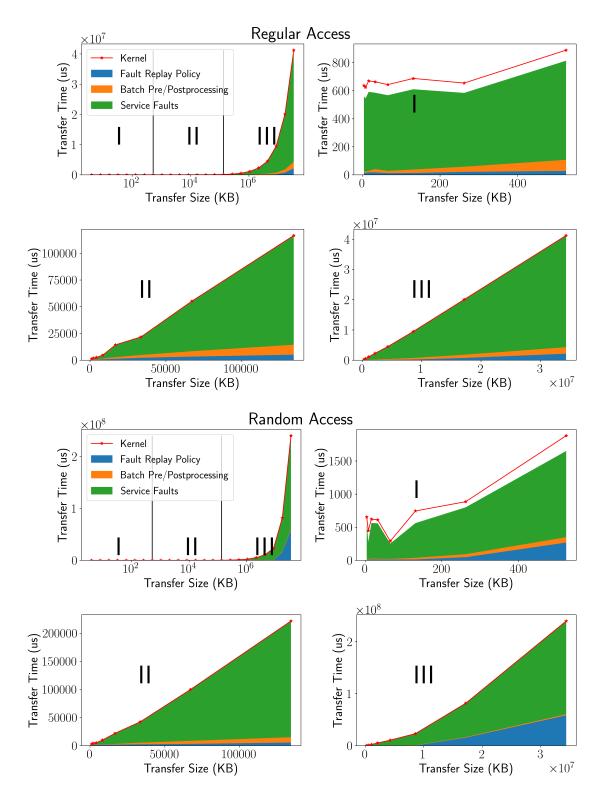

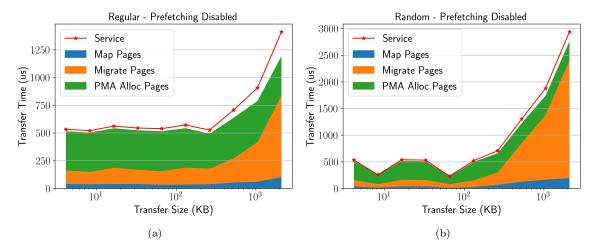

| 3.5 | patterns on the same data size. Random tends to be slower, and has shifted proportions. Breakdown of the fault service cost. PMA Alloc Pages is a call into the proprietary NVIDIA driver to allocate physical memory. It is actually part of the migration process if required. Allocation seems subject to system latency, but allocations are                                                                                                                                                             | 32 |

|     | usually over-provisioned to avoid multiple calls                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

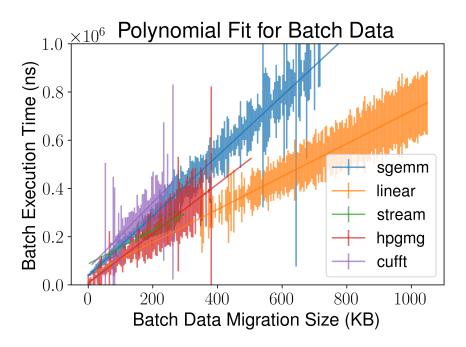

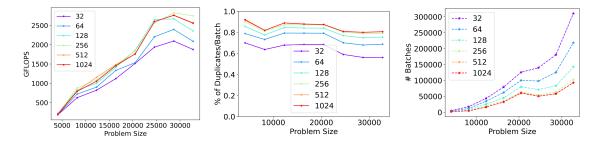

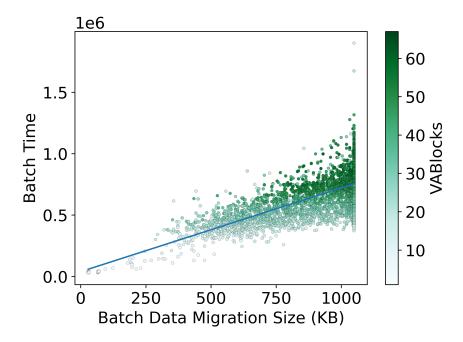

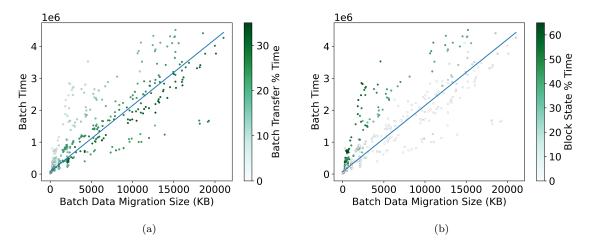

| 4.1 | Best fit of batch sizes vs. data migrated for one run of several applications. Linear least-squares approximation with standard deviation per point.                                                                                                                                                                                                                                                                                                                                                         | 36 |

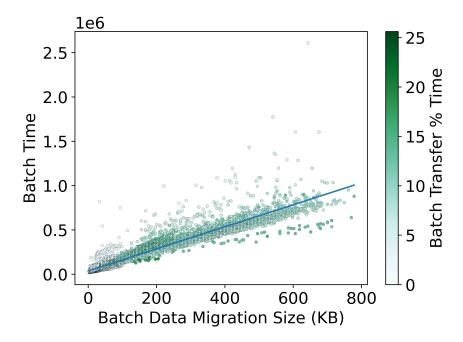

| 4.2 | This figure shows the percentage of time spent per-batch performing data transfer relative to the total batch time for example sgemm. The batch time is approximately 25% at most, but typically far lower.                                                                                                                                                                                                                                                                                                  | 37 |

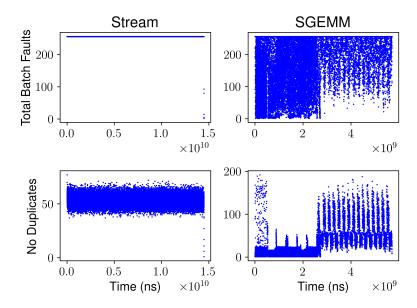

| 4.3 | Time series of batches processed by the UVM driver pairing stream and sgemm. The first row is the total number of faults registered by the driver, and the second row is         |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | the total number of faults after duplicate faults (multiple faults to the same page) are                                                                                         |    |

| 4 4 | removed. Duplicate removal is an early step the driver takes in fault processing                                                                                                 | 38 |

| 4.4 | This figure demonstrates the same experiment as 3.4, except with the Batch Policy as the replay policy. Note that the replay policy cost is severely diminished, while the       |    |

|     | preprocessing cost is greatly increased                                                                                                                                          | 39 |

| 4.5 | Batch size evaluation example with sgemm. While duplicate faults have some overhead, there is a strong correlation with the total number of batches required for processing.     | 00 |

|     | Batch sizes up to 6144 (max) are tested but are not shown as performance does not                                                                                                |    |

|     | change                                                                                                                                                                           | 39 |

| 4.6 | Batches sorted by to-GPU data migration size. Batches are logically divided into VABlocks, so each VABlock adds another layer of overhead. For a given migration                 |    |

|     | size, higher cost is associated with more VABlocks.                                                                                                                              | 41 |

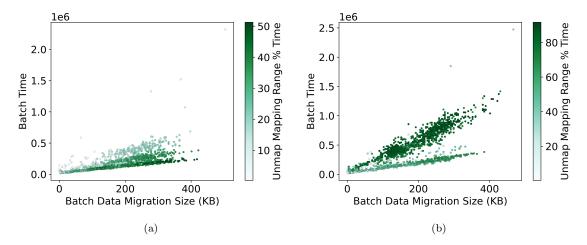

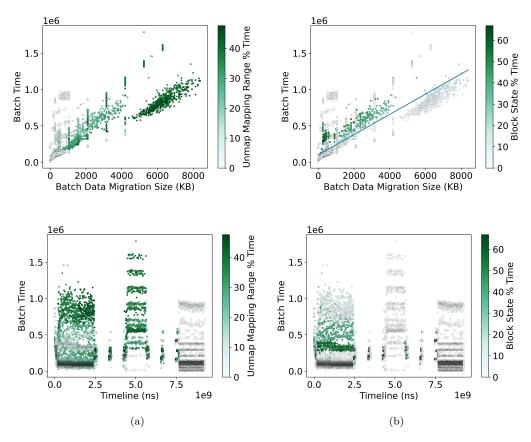

| 4.7 | These figures show two cases of the HPGMG application, where the percentage indicates the relative time per batch spent unmapping resident pages from the CPU as                 |    |

|     | VABlock is logically resident on GPU. Figure 4.7a: single OpenMP thread; Figure                                                                                                  |    |

|     | 4.7b: one thread per CPU core. Unmapping CPU pages takes a larger percentage of time with CPU multithreading, indicating a link between host OS performance, CPU                 |    |

|     | access usage, and GPU paging performance                                                                                                                                         | 42 |

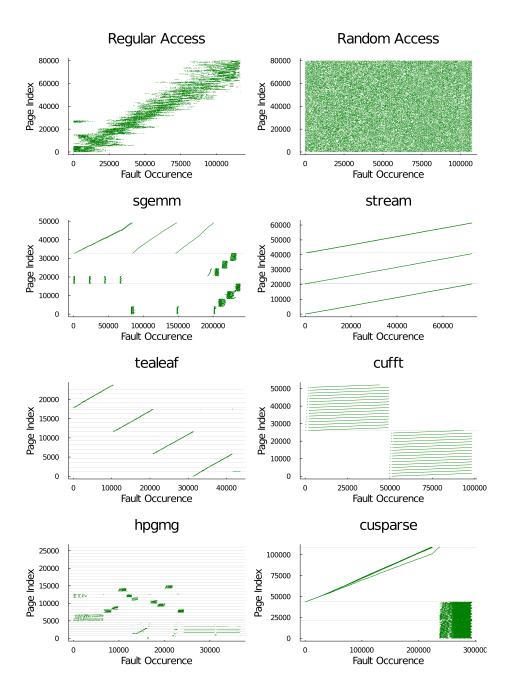

| 5.1 | Application access patterns with prefetching disabled. The page index is the virtual                                                                                             |    |

|     | memory page corresponding to the fault address, adjusted so that there are no gaps in the virtual memory space. Fault occurrence is the relative order that pages were           |    |

|     | processed by the driver.                                                                                                                                                         | 45 |

| 5.2 | An example of the previously-seen <b>sgemm</b> example after prefetching is enabled. The mid-range cost batches have been significantly reduced, reducing the overall time spent |    |

|     | in the driver. There is a large range of values, with high-end outliers corresponding to negative performance impacts from creating and storing DMA mappings                     | 47 |

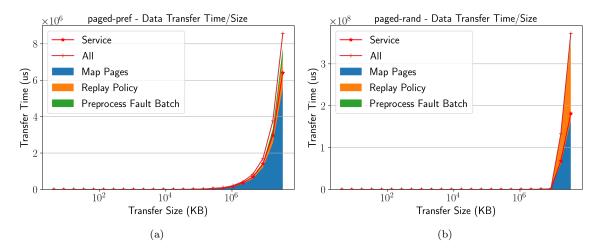

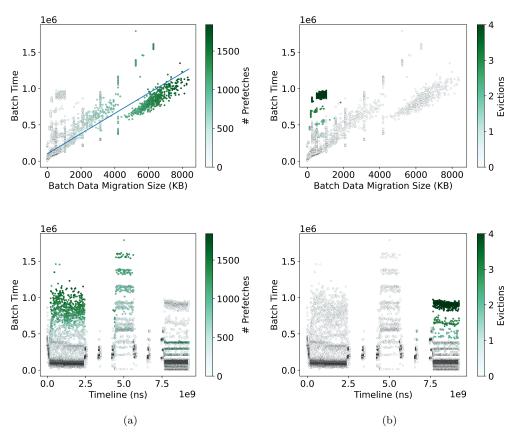

| 5.3 | A breakdown of performance for oversubscribed problem sizes with prefetching enabled. In these figures, "Map" includes page migration and relevant costs. "All"                  | 41 |

|     | refers to the kernel execution time                                                                                                                                              | 49 |

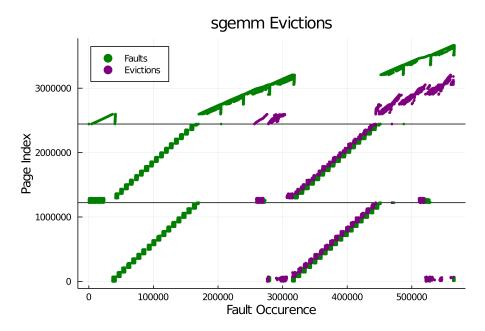

| 5.4 | This figure demonstrates sgemm with a problem size that requires approximately                                                                                                   |    |

|     | 120% of GPU memory. Notably, we show evictions at the relative time step they are                                                                                                |    |

|     | issued. Evict and re-fault is a worst-case performance scenario                                                                                                                  | 50 |

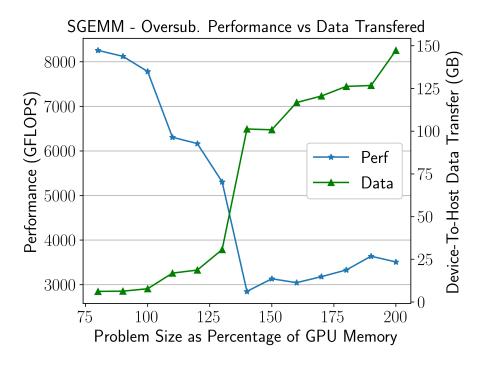

| 5.5 | This figure shows the parallel increase in data requirement as compared to compute                                                                                               |    |

| r c | rate for the sgemm kernel                                                                                                                                                        | 52 |

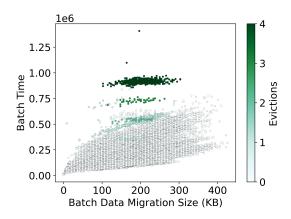

| 5.6 | Batches by the number of evictions for an oversubscribed sgemm. All pages resident on the GPU are migrated back to the CPU                                                       | 53 |

| 5.7 | Oversubscription stream example. Batch characteristics determine the overall per-                                                                                                | აა |

| 9.1 | formance. LEFT: We can see multiple performance "levels" for the same number of evictions. RIGHT: we can see that a level may or may not include a portion of CPU                |    |

|     | unmapping                                                                                                                                                                        | 53 |

|     | Tr o                                                                                                                                                                             |    |

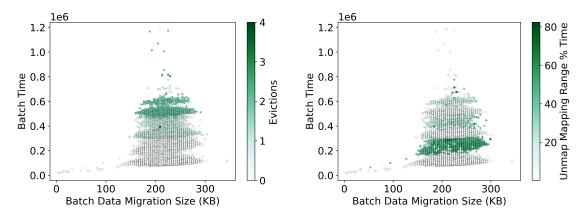

| 5.8         | Batches from sgemm with high-impact performance events discussed in the previous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | section, sorted by data migration but also as a time series. The time series mappings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|             | for these events show when these events occur. Prefetching occurs throughout the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|             | execution but is limited when VABlocks begin to migrate off of the GPU. Evictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|             | typically occur later in computation as it takes some time for the GPU memory to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|             | fill up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55  |

| 5.9         | Additional breakdown of figure 5.8 Unmapping from the CPU occurs regularly through-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|             | out the application until every VABlock has received at least one page fault. GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|             | state setup (DMA time) also occurs throughout the full application, but does not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|             | always have excessively high overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56  |

|             | arrage have encountry ingli everification of the second of | 00  |

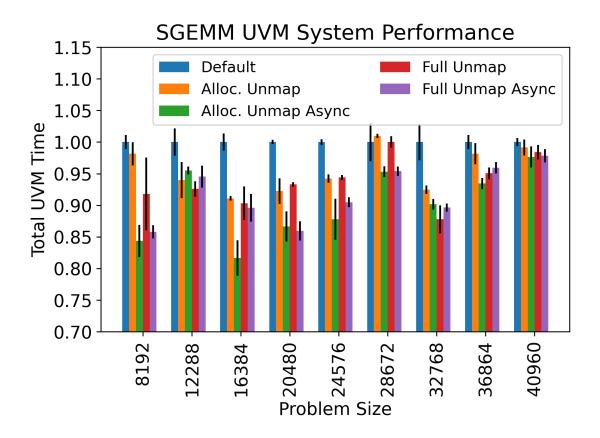

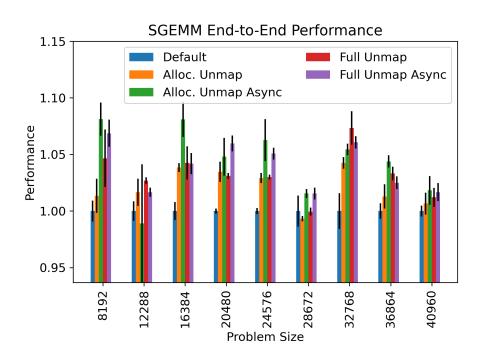

| 6.1         | Total time spent in UVM execution for SGEMM kernels over increasing problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|             | sizes for each driver configuration normalized to the default NVIDIA UVM configura-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|             | tion. Sizes above 30,000 exceed GPU memory and use oversubscription. Preemptive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | unmapping generally improves performance, asynchronous preemptive unmapping al-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | ways outperforms with potential for significant gains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61  |

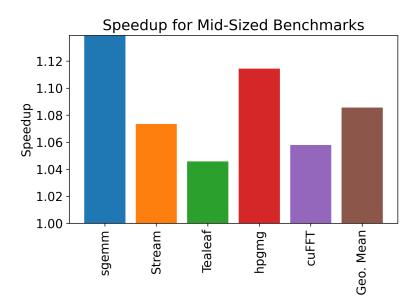

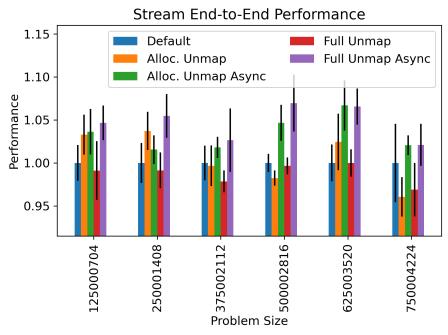

| 6.2         | Performance for moderate-to-high memory usage benchmark sizes on other appli-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -   |

| ٠. <b>-</b> | cations. Performance improvement generalizes, although total system performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | improvement will depend on the memory footprint and hybrid access pattern of indi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|             | vidual applications as described in prior sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62  |

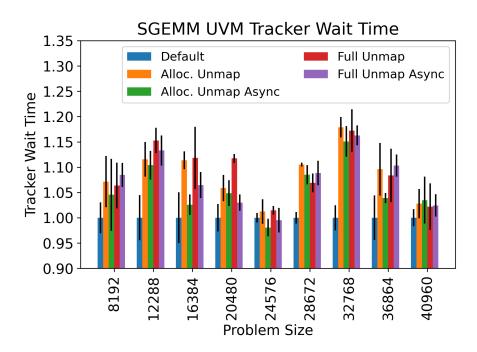

| 6.3         | This figure shows the amount of time spent waiting to synchronize with the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 02  |

| 0.0         | Our unmapping methods increase this as overall performance increases, likely indi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|             | cating that we are shifting the bottleneck towards the device and interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |

| 6.4         | This figure shows the amount of time spent waiting to synchronize with the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.0 |

| 0.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | Our unmapping methods increase this as overall performance increases, likely indi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C A |

|             | cating that we are shifting the bottleneck towards the device and interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64  |

## Chapter 1

## Introduction

Graphics Processing Units (GPUs) have become one of the computational devices in modern high-performance computing (HPC) systems. As of November 2020, six of the top ten Supercomputers on the Top500 are NVIDIA GPU-Based systems[1], and 67% of the Top500 in total as of June 2020[23]. GPUs are now relied upon to enable many modern scientific and machine learning-based applications at critical research centers around the world.

GPUs are a type of hardware accelerator - a specialized hardware unit that functions alongside the CPU in a typical system. Due to the success of GPUs, other types of accelerators are gaining recognition in HPC systems, including Data Processing Units (DPUs) and Field-Programmable Gate Arrays (FPGAs). In HPC systems, accelerators are usually present as dedicated add-on cards connected to the main CPU over some high-speed interconnect. Accelerators typically have their own memory hierarchies and programming models. The inclusion of these accelerators has greatly increased the management and programming complexity of these systems has risen alongside the performance.

As the inclusion of GPUs and other accelerators has and continues to improve the theoretical performance of HPC systems, the complexity of programming for high-performance increases two-fold. First, efficient utilization of accelerators requires effective programming against the target architecture. Adapting to the programming models and paradigms of these devices is difficult even for professional programmers, but HPC systems are often programmed by domain scientists who may not have formal training, increasing the difficulty substantially. Second, the increase throughput enables more advanced domain applications that were previously intractable on lower-throughput

systems. The applications themselves increase in complexity, placing an even greater burden on programmers when paired with an increasingly complex programming environment. Due to this, the barriers to creating and maintaining correct, high-performance applications for advanced domain problems have been steadily rising.

A large step towards reducing the complexity introduced by increasingly heterogeneous systems has been the introduction of heterogeneous shared memory systems. These systems manage separate host and device physical memory domains in systems software, giving the programmer a transparent view of memory and removing the need for programmers to manage these domains themselves. Heterogeneous Memory Management (HMM) and NVIDIA Unified Virtual Memory (UVM) are two independent yet collaborative heterogeneous shared memory implementations. HMM is an upcoming Linux kernel feature providing a generic front-end for OS memory management for commodity systems, but primarily only serves as a host-side virtual memory manager and as a common front-end for device-specific drivers [15, 26]. In contrast, UVM is an all-in-one approach to heterogeneous shared memory that provides near-transparent memory management support for NVIDIA devices only. It can also serve as a backend to interface with HMM [15, 26], although mutual support is still in development [42]. Because HMM is still under development, NVIDIA UVM is currently the most represented heterogeneous shared memory technology in HPC and has been adopted into several common HPC frameworks such as Raja [9], Kokkos [10], and Trilinos [25].

These technologies require hardware and software support to effectively implement the underlying memory management. They create a virtual shared memory space between the host and device by extending the host's virtual demand paging system. With appropriate hardware support, modern NVIDIA GPUs support the full Linux virtual memory paging scheme, particularly the capability of generating page faults when memory is not mapped into GPU page tables. In the event of a page fault, GPU hardware will issue an interrupt to the host CPU. These interrupts are handled by kernel-mode drivers on the host, which will result in the migration of the needed data to the GPU as well as appropriate updates to GPU page tables. This process is complex, and represents a clear source of performance sensitivity as it acts as a data bottleneck in the event of page faults.

The ease of use provided by these technologies comes at the cost of significant overhead. Prior work has shown that many HPC applications suffer significant performance losses from UVM in many HPC applications and micro-benchmarks [22, 20, 29, 14, 20]. This trade-off varies from