# Universidad de Alcalá Escuela Politécnica Superior

# Máster Universitario en Ingeniería de Telecomunicación

### Trabajo Fin de Máster

Diseño de arquitecturas empotradas para la implementación en tiempo real de redes neuronales profundas

# ESCUELA POLITECNICA

Autor: Jorge Martín Catalán

Tutor: Álvaro Hernández Alonso

# UNIVERSIDAD DE ALCALÁ

#### ESCUELA POLITÉCNICA SUPERIOR

#### Máster Universitario en Ingeniería de Telecomunicación

### Trabajo Fin de Máster

Diseño de arquitecturas empotradas para la implementación en tiempo real de redes neuronales profundas

Autor: Jorge Martín Catalán

Tutor: Álvaro Hernández Alonso

#### Tribunal:

Presidente: Daniel Pizarro Pérez

Vocal 1º: Mº del Pilar Jarabo Amores

Vocal 2º: Álvaro Hernández Alonso

Fecha de depósito: 17 de julio de 2022

# Resumen

Este documento detalla la implementación de algoritmos de *Deep Learning* en distintos tipos de plataformas embebidas como son los SoC/FPGA y los microprocesadores. Además se comparan las diferencias en términos de latencias, errores de cuantificación y recursos consumidos. Se parte de una red ya implementada y probada, con sus bases de datos etiquetadas y separadas para realizar la implementación. El problema que trata de resolver se utilizará como base, pero debido a que se quieren probar diversas arquitecturas como perceptron multicapa, redes convolucionales y las recurrentes, se resolverá modificando la estructura de la red neuronal con redes alternativas a las propuestas en dicho trabajo.

Palabras clave: FPGA/SoC, Deep Learning, Microprocesadores, NILM, Sistemas empotrados.

# Abstract

This document details the implementation procedure of different Deep Learning algorithms in embedded platforms such as SoC/FPGA or Microprocessors. Also, the differences in terms of latency, quantification errors and resources are compared. The start point is a tested network and its tagged database. This network will be modified in order to try different types of networks such as Multilayer perceptron, Convolutional Network and Recurrent Network.

Keywords: FPGA/SoC, Deep Learning, Microprocesors, NILM, embedded system.

## Resumen extendido

El campo del Deep Learning es cada vez más importante dentro del campo de la inteligencia artificial y de la vida diaria. Su implementación no tiene cabida únicamente dentro de los servidores con aceleradores para realizar las inferencias en tiempo real; en múltiples casos, por cuestiones de latencias, seguridad o de comunicaciones es necesario realizar los cálculos en el edge. Por lo tanto, su implementación dentro de dispositivos embebidos como las FPGA o los microcontroladores es un aspecto primordial.

El propósito de este trabajo se centra en la implementación de este tipo de redes dentro de los dispositivos empotrados comentados previamente. Por parte de la FPGA, el desarrollo del algoritmo en un lenguaje de descripción hardware como VHDL serviría para obtener un funcionamiento óptimo. Aun así, este desarrollo sería complejo y tendría un tiempo de implementación largo. Por lo tanto, para el desarrollo del trabajo se observarán técnicas de alto nivel que permiten un desarrollo más rápido y sencillo con el paquete hls4ml, que permite desde python generar código hls que herramientas como  $Vivado\ HLS$  son capaces de convertir en firmware.

Por su parte, con el microcontrolador también se observarán herramientas destinadas a la implementación de redes neuronales. Por ejemplo, los procesadores de STM disponen de un paquete denominado X-Cube-AI que permite importar las redes neuronales y convertirlas en una API compatible con sus dispositivos.

Todas estas herramientas se evaluarán a la práctica y se explicará el funcionamiento y utilidades de las que disponen. Como caso práctico se ha seleccionado la implementación de técnicas NILM para la monitorización de hogares, en concreto, para la clasificación de electrodomésticos en función de sus características eléctricas. Con el objetivo de explorar las distintas arquitecturas de Deep Learning se utilizarán distintos tipos de neuronas como perceptrones multicapa, convolucionales y recurrentes con distintos tipos de funciones de activación.

Con los resultados obtenidos se compararán las principales características de cada dispositivo en función del tamaño y tipo de red, y también se compararán entre los dos tipos de componentes, destacando los puntos fuertes y débiles de las FPGA frente a los microcontroladores en la implementación del sistema.

# Índice general

| R            | esum  | ien           |                                                      | vii  |

|--------------|-------|---------------|------------------------------------------------------|------|

| $\mathbf{A}$ | bstra | $\mathbf{ct}$ |                                                      | ix   |

| R            | esum  | nen ext       | tendido                                              | xi   |

| Ín           | dice  | genera        | al                                                   | xiii |

| Ín           | dice  | de fig        | guras                                                | xv   |

| Ín           | dice  | de tal        | blas                                                 | xvii |

| Li           | sta c | le acrá       | ónimos                                               | xvii |

| Li           | sta d | le síml       | bolos                                                | xix  |

| 1            | Inti  | roducc        | ción                                                 | 1    |

|              | 1.1   | Objet         | zivos                                                | 1    |

|              | 1.2   | Estuc         | etura global                                         | 2    |

| <b>2</b>     | Est   | udio te       | eórico                                               | 3    |

|              | 2.1   | Redes         | s Neuronales                                         | 3    |

|              | 2.2   | Técnie        | cas NILM                                             | 4    |

|              | 2.3   | Red n         | neuronal base                                        | 5    |

| 3            | Arc   | quitect       | turas basadas en dispositivos FPGA                   | 9    |

|              | 3.1   | Red n         | neuronal básica                                      | 10   |

|              |       | 3.1.1         | Diseño de la red neuronal básica en <i>Keras</i>     | 10   |

|              |       | 3.1.2         | Conversión de una red neuronal a HLS                 | 12   |

|              |       |               | 3.1.2.1   Análisis de recursos y latencia resultante | 16   |

|              |       | 3.1.3         | Pruebas realizadas en HLS                            | 17   |

|              |       | 3.1.4         | Diseño del sistema en <i>Vivado</i>                  | 17   |

|              |       | 3.1.5         | Diseño del sistema en <i>Vitis</i>                   | 19   |

xiv ÍNDICE GENERAL

|   | 3.2   | Red neuronal de dos capas densamente conectadas |            |                                                                                      |    |  |

|---|-------|-------------------------------------------------|------------|--------------------------------------------------------------------------------------|----|--|

|   |       | 3.2.1                                           | Diseño o   | de la red neuronal de dos capas en Keras                                             | 22 |  |

|   |       | 3.2.2                                           | Convers    | ión de la red de dos capas densas a HLS                                              | 25 |  |

|   |       |                                                 | 3.2.2.1    | Estudio de la cuantificación en el modelo de dos capas densas                        | 25 |  |

|   |       |                                                 | 3.2.2.2    | Análisis de recursos y latencia resultante                                           | 27 |  |

|   |       | 3.2.3                                           | Pruebas    | realizadas en HLS                                                                    | 29 |  |

|   |       | 3.2.4                                           | Impleme    | entación en Vivado                                                                   | 30 |  |

|   |       | 3.2.5                                           | Impleme    | entación en Vitis                                                                    | 31 |  |

|   | 3.3   | Red n                                           | euronal d  | e dos capas utilizando CNN                                                           | 34 |  |

|   |       | 3.3.1                                           | Diseño o   | de la red neuronal convolucional en $\mathit{Keras}$                                 | 34 |  |

|   |       | 3.3.2                                           | Convert    | ir la red neuronal convolucional a HLS                                               | 35 |  |

|   |       |                                                 | 3.3.2.1    | Estudio de la cuantificación en el modelo convolucional $\ \ldots \ \ldots \ \ldots$ | 35 |  |

|   |       |                                                 | 3.3.2.2    | Análisis de recursos y latencia resultante                                           | 37 |  |

|   |       | 3.3.3                                           | Impleme    | entación en Vivado                                                                   | 38 |  |

|   | 3.4   | Comp                                            | arativa de | e las distintas estructuras en FPGA                                                  | 40 |  |

| 4 | Imp   | olemen                                          | tación d   | e Redes Neuronales en sistemas basados en Microprocesador                            | 43 |  |

|   | 4.1   | Red n                                           | euronal b  | ásica en uC                                                                          | 43 |  |

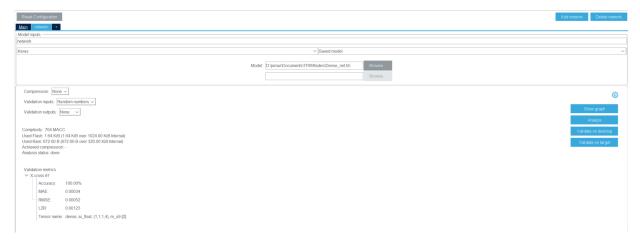

|   |       | 4.1.1                                           | Utilizaci  | ión del paquete STMicroelectronics-X-Cube-AI                                         | 44 |  |

|   |       | 4.1.2                                           | Utilizaci  | ión de la $API$ y resultados                                                         | 46 |  |

|   | 4.2   | Red n                                           | euronal d  | e dos capas densamente conectadas                                                    | 47 |  |

|   | 4.3   | Red n                                           | euronal c  | onvolucional                                                                         | 49 |  |

|   | 4.4   | Red n                                           | euronal re | ecurrente                                                                            | 50 |  |

|   | 4.5   | Comp                                            | arativa er | ntre la implementación de las distintas neuronas en $\mu C$                          | 54 |  |

| 5 | Con   | nclusio                                         | nes y lín  | eas futuras                                                                          | 55 |  |

| 6 | Pre   | supues                                          | sto        |                                                                                      | 57 |  |

| R | blios | grafía                                          |            |                                                                                      | 59 |  |

# Índice de figuras

| 2.1  | Esquema del perceptrón [1]                                                                   | 3  |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | Ejemplo de una red neuronal densamente conectada [2]                                         | 4  |

| 2.3  | División de arquitectura en NILM [3]                                                         | 6  |

| 2.4  | Red original descrita para la detección NILM [3]                                             | 7  |

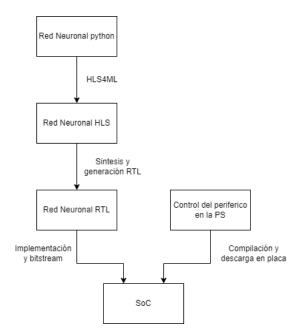

| 3.1  | Esquema de desarrollo de la aplicación                                                       | 10 |

| 3.2  | Placa de desarrollo Zedboard de Digilent.[4]                                                 | 10 |

| 3.3  | Estructura de la $Zynq$                                                                      | 11 |

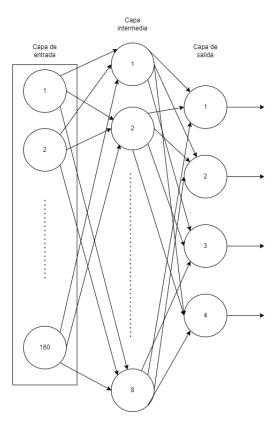

| 3.4  | Topología red neuronal básica.                                                               | 12 |

| 3.5  | Resultados de entrenamiento de la red neuronal básica.                                       | 13 |

| 3.6  | Significado del Reuse factor [5]                                                             | 14 |

| 3.7  | Diagrama implementado en la red básica                                                       | 15 |

| 3.8  | Utilización en función del $reuse\ factor$ para la red neuronal básica                       | 16 |

| 3.9  | Latencia en función del $reuse\ factor$ para la red neuronal básica                          | 17 |

| 3.10 | Resultados en $\emph{Vivado HLS}$ de la Red Básica                                           | 17 |

| 3.11 | Configuración de puertos del IP básico.                                                      | 18 |

| 3.12 | Esquema básico                                                                               | 18 |

| 3.13 | Potencia consumida por la implementación                                                     | 19 |

| 3.14 | Análisis temporal del esquema básico para distintas frecuencias                              | 20 |

| 3.15 | Resultados de la red neuronal básica implementada en la tarjeta                              | 21 |

| 3.16 | Resultados en ILA de la red neuronal básica implementada en la tarjeta                       | 22 |

| 3.17 | Topología de la red neuronal de dos capas densas                                             | 23 |

| 3.18 | Resultados de entrenamiento de la red neuronal de dos capas densas                           | 24 |

| 3.19 | Diagrama del modelo HLS con dos capas densamente conectadas                                  | 25 |

| 3.20 | Cuantificación de los parámetros en la red neuronal de dos capas                             | 26 |

| 3.21 | Respuesta a la variación de la cuantificación en la estructura de dos capas variando la coma |    |

|      | fija                                                                                         | 26 |

| 3.22 | Respuesta a la variación de la cuantificación en la estructura de dos capas                  | 27 |

| 3.23 | Recursos consumidos en la fase de síntesis variando el <i>Reuse factor</i> en la estructura de dos                        | 20 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

|      | capas.                                                                                                                    | 28 |

|      | Latencia variando el <i>Reuse factor</i> en la estructura de dos capas                                                    | 29 |

|      | Resultados en $HLS$ de estructura con dos capas                                                                           | 30 |

| 3.26 | Bloque IP de la red de dos capas densamente conectadas                                                                    | 30 |

| 3.27 | Esquema de conexionado de bloques en Vivado con dos capas                                                                 | 31 |

| 3.28 | $\label{lem:eq:analysis} An \'alisis temporal del esquema de dos capas densamente conectadas para distintas frecuencias.$ | 32 |

| 3.29 | Potencia en la arquitectura de dos capas densamente conectadas                                                            | 33 |

| 3.30 | Resultados de la red neuronal implementada en la Zedboard                                                                 | 33 |

| 3.31 | Diagrama red neuronal convolucional                                                                                       | 34 |

| 3.32 | Resultados de entrenamiento de la red neuronal convolucional                                                              | 36 |

| 3.33 | Cuantificación de los parámetros de la red neuronal convolucional                                                         | 37 |

| 3.34 | Variación del tamaño de palabra de la red neuronal convolucional                                                          | 37 |

| 3.35 | Variación del tamaño de palabra con la parte entera fija en 11 bits de la red neuronal convolucional                      | 38 |

| 3.36 | Utilización de la CNN en función del Reuse Factor                                                                         | 39 |

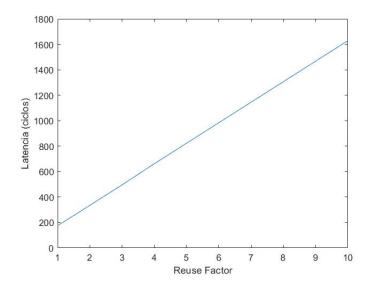

|      | Latencia de la CNN en función del Reuse Factor                                                                            | 39 |

| 3.38 | Análisis temporal de la red CNN para distintas frecuencias                                                                | 40 |

| 3.39 | Latencia de la CNN en función del Reuse Factor                                                                            | 40 |

| 4.1  | Interfaz X-Cube-AI.                                                                                                       | 44 |

| 4.2  | Arquitectura red básica X-Cube-AI.                                                                                        | 45 |

| 4.3  | Tiempo en realizar la inferencia en la validación de la red básica                                                        | 45 |

| 4.4  | Precisión de la red básica según X_cubeX_AI                                                                               | 45 |

| 4.5  | Captura de los resultados de la red básica                                                                                | 47 |

| 4.6  | Análisis de la red de dos capas                                                                                           | 48 |

| 4.7  | Comparativa de resultados de la red de dos capas.                                                                         | 48 |

| 4.8  | Comparativa de tiempos de la red de dos capas                                                                             | 49 |

| 4.9  | Análisis de la red convolucional                                                                                          | 49 |

| 4.10 | Error de cuantificación red convolucional para $\mu$ C                                                                    | 50 |

| 4.11 | Tiempo en ordenador de la red convolucional                                                                               | 50 |

| 4.12 | Esquema de la red recurrente                                                                                              | 51 |

| 4.13 | Resultados de entrenamiento de la red neuronal básica.                                                                    | 52 |

| 4.14 | Análisis de la red recurrente.                                                                                            | 53 |

| 4.15 | Tiempo en la evaluación en ordenador de la red recurrente                                                                 | 53 |

| 1.10 | Precisión entre el modelo de STM y el teórico.                                                                            | 53 |

# Índice de tablas

| 3.1  | Resumen de la red neurona básica                                                         | 11 |

|------|------------------------------------------------------------------------------------------|----|

| 3.2  | Utilización básica con $Reuse\ Factor = 4.$                                              | 16 |

| 3.3  | Recursos de la red neuronal en Vivado                                                    | 19 |

| 3.4  | Resumen de la red neurona de dos capas densamente conectadas                             | 22 |

| 3.5  | Recursos de NN en Vivado para estructura de dos capas con $Reuse\ factor\ de\ 1.\ \dots$ | 28 |

| 3.6  | Recursos de NN en Vivado para estructura de dos capas con interfaz AXI                   | 29 |

| 3.7  | Recursos de NN en implementación del diagrama de dos capas                               | 31 |

| 3.8  | Resumen de la red neurona convolucional                                                  | 35 |

| 3.9  | Recursos de NN en Vivado para estructura CNN                                             | 38 |

| 3.10 | Recursos de NN en Vivado para estructura CNN en la implementación                        | 39 |

| 4.1  | Compresión obtenida para la red básica                                                   | 44 |

| 4.2  | Resultados en $\mu C$ para la red básica                                                 | 47 |

| 4.3  | Compresión obtenida para la red de dos capas                                             | 48 |

| 4.4  | Resultados en $\mu C$ para la red de 2 capas                                             | 49 |

| 4.5  | Compresión obtenida para la red de convolucional                                         | 50 |

| 4.6  | Resultados en $\mu C$ para la red convolucional                                          | 51 |

| 4.7  | Resumen de la red neurona básica                                                         | 51 |

| 4.8  | Compresión obtenida para la red de recurrente                                            | 52 |

| 4.9  | Resultados en $\mu$ C para la red recurrente                                             | 54 |

| 6.1  | Costes Materiales                                                                        | 57 |

| 6.2  | Costes Profesionales                                                                     | 57 |

| 6.3  | Costes Totales                                                                           | 58 |

# Glosario de Acrónimos y abreviaturas

| API           | Application Programming Interface |  |  |

|---------------|-----------------------------------|--|--|

| DSP           | Digital Signal Processor          |  |  |

| E/S           | Entrada/Salida                    |  |  |

| FPGA          | Field Programmable Gate Array     |  |  |

| HLS           | High-Level Synthesis              |  |  |

| LSTM          | Long Short-Term Memory            |  |  |

| LUT           | Look-Up Table                     |  |  |

| NILM          | Non-Intrusive Load Monitoring     |  |  |

| PS            | Processing System                 |  |  |

| PL            | Programmable Logic                |  |  |

| RAM           | random access memory              |  |  |

| RTL           | Real Time Logic                   |  |  |

| SoC           | System On Chip                    |  |  |

| uC / MCU / μC | Microcontrolador                  |  |  |

# Capítulo 1

# Introducción

A día de hoy, las redes neuronales se aplican en la inmensa mayoría de aspectos de nuestra vida. Por ejemplo, al utilizar plataformas de vídeo como *Youtube* o *TikTok*, o redes sociales como *Facebook* o *Twitter*, hay múltiples redes neuronales encargadas de predecir el próximo contenido a visualizar en función de nuestros gustos o intereses. Otro ámbito en el que está encontrando gran relevancia es en el vehículo autónomo, aspectos como la identificación de peatones o guiado del vehículo toman especial importancia.

Otra rama en la que han mejorado bastante la calidad de vida es en la sanitaria. Se aplican en campos como la detección previa de enfermedades o en el reconocimiento de hábitos de vida saludables. Este último tema se detallará en la sección 2.3 dado que ha servido como iniciativa del presente trabajo con la aplicación de redes neuronales dentro de *Smart Meters* para la clasificación de electrodomésticos en función de sus cualidades eléctricas.

En cuanto a la ejecución de las redes neuronales se parte de dos paradigmas, desarrollar la algoritmia en el edge o desarrollarla en el cloud. Para el primer caso, se suelen utilizar microcontroladores o microprocesadores para llevar a cabo la inferencia de la red como puede ser en un móvil. Sin embargo, las FPGA también pueden resultar de gran utilidad en este terreno ya que permiten reducir los tiempos de cálculo debido a su alto grado de paralelización. Aunque su uso no se centra únicamente al edge, empresas como Xilinx tienen ramas de productos como las tarjetas aceleradoras Alveo[6] o Virtex especiales para  $Data\ Centers$ . Por ejemplo, las instancias Amazon EC2 F1 [7] de  $Amazon\ Web\ Services$  utilizan FPGAs de Xilinx para realizar una aceleración en hardware de los algoritmos.

Este trabajo se centra en aplicaciones sobre el edge para ofrecer una visión de la implementación de redes neuronales en microprocesadores y FPGA, a fin de comparar el comportamiento y las características de ambos entornos.

#### 1.1 Objetivos

Los objetivos que trata de cubrir el TFM son:

Diseño de redes con distintos tipos de arquitecturas como perceptrón multicapa, convolucionales o recurrentes.

- Implementación en FPGA de las distintas redes neuronales partiendo del fichero en python y probándolo en la tarjeta.

- Implementación en microcontrolador de las distintas redes neuronales partiendo del fichero en python y probándolo en la tarjeta.

- Evaluación de las herramientas utilizadas.

- Comparativa de resultados entre las diferentes arquitecturas de redes neuronales en cada sistema.

- Comparativa de resultados entre los dos sistemas.

#### 1.2 Estuctura global

En el capitulo 2 se comenzará con el análisis del estado del arte. En el que se explicará los trabajos previos o a la situación actual con respecto a las redes neuronales y a los *Smart Meters*. Además, también se explicará el trabajo previo que ha servido como punto de partida a este documento.

A continuación, en el capítulo 3 se comentará el proceso de implementación para la FPGA analizando las herramientas, programas utilizados y resultados. A lo largo de dicho capítulo se analizarán de igual manera las redes neuronales que se van a llevar a la práctica en la FPGA y en el micro. El proceso en el microprocesador se continuará en el apartado siguiente presentando de igual manera el software empleado y los resultados obtenidos teóricamente y sobre la tarjeta.

Para comparar los resultados obtenidos en los dos capítulos anteriores se dispondrá del capítulo 5 donde también se anotarán las conclusiones obtenidas y las líneas de trabajo futuras que surgen de este TFM.

## Capítulo 2

# Estudio teórico

#### 2.1 Redes Neuronales

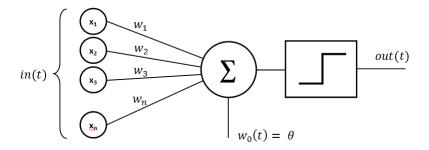

El terreno de la inteligencia artificial ha tenido un gran crecimiento en las ultimas décadas. En concreto, en esta última con la llegada de las redes neuronales profundas ( $Deep\ Neuronal\ Networks$ ). Son inspiradas en el modelo del cerebro y de las conexiones entre distintas neuronas para emular la inteligencia humana. La neurona más sencilla implementada es el perceptrón que se puede visualizar en la figura 2.1. Consiste en una capa de entradas  $X_n$  a las que se les aplica una serie de pesos  $W_n$  y se suma su resultado. Adicionalmente, se le puede insertar un bias. Finalmente, al resultado de esta expresión se suele aplicar múltiples funciones no lineales con el objetivo de evitar un comportamiento lineal. Por lo tanto la función implementada por un perceptrón será:

Figura 2.1: Esquema del perceptrón [1].

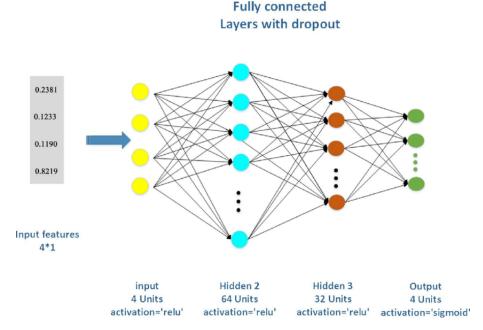

El funcionamiento de una única neurona sería demasiado sencillo por lo que se agregan más en la misma capa o en distintas con el objetivo de aprender comportamientos más complejos de un problema de regresión o de clasificación. Las redes neuronales cuentan con una capa de entrada a la red conectada con distintas neuronas ocultas densamente conectadas. Todas estas pueden tener distintos tipos de neuronas de activación. Finalmente se dispondrá de una capa de salida con el resultado de la clasificación. Un ejemplo de esta red conectada se observa en la figura 2.2. Se define como densamente conectada por que todas las salidas de la capa anterior están conectadas a cada neurona de la capa siguiente.

Figura 2.2: Ejemplo de una red neuronal densamente conectada [2].

El perceptrón es el tipo de neurona más sencillo, encargado de desarrollar una combinación lineal con una función de activación, pero existen otro tipo de neuronas con un mejor funcionamiento en ciertas aplicaciones. Por ejemplo las redes convolucionales [8] destacan en el procesado de imagen y se han utilizado en sistemas como AlexNet [9] o Yolo [10]. Este tipo de neurona se encarga de aplicar un filtro sobre la imagen en lugar de la combinación lineal realizada por el perceptrón. Las capas neuronales suelen venir seguidos con capas de pooling que se encargan de evitar que aumente demasiado el número de parámetros de la red. Para ello seleccionan el número mayor o medio de un subconjunto. Otra clase de redes que funcionan especialmente bien con series temporales son las recurrentes [11], entre las que destacan las LSTM. Su principal característica es considerar valores previos para las siguientes clasificaciones.

Otro concepto relativamente importante dentro de las redes neuronales es el de entrenamiento y back-propagation [12]. Dado que se trata de aprendizaje supervisado, se requiere un conjunto de datos para alimentar la red. Con ello realiza el algoritmo de backpropagation con el que intenta, a partir del error cometido entre el predicho y el correcto, corregir los parámetros de la red para aprender a resolver el problema. A lo largo del entrenamiento pueden suceder dos problemas distintos denominados overfitting y underfitting. El último consiste en que no hay suficientes datos o que las iteraciones del algoritmo son insuficientes para resolver el problema. Mientras que el otro consiste en que la red memoriza los datos de entrenamiento pero es incapaz de comportarse correctamente ante nuevos datos. Este problema se soluciona separando el conjunto de datos en entrenamiento y validación que servirán para probar que no sé este realizando este sobreentrenamiento.

#### 2.2 Técnicas NILM

El área de aplicación en la que se enfoca este trabajo es la monitorización de carga, que permite extraer las características de un electrodoméstico del sistema. Para ello existen las técnicas NILM, por las que tomando medidas de energía eléctrica del edificio se puede estimar el consumo y estado de un único

2.3 Red neuronal base 5

dispositivo. La estimación se suele dividir en dos fases, una de bajo nivel consistente en la adquisición de datos y otra de alto nivel que separará las cargas de los diferentes elementos que componen la red.

Para la adquisición de los datos se requiere de un medidor conectado a la red eléctrica llamado *Smart Meter* [13]. En cuanto a la separación de la energía hay dos diferencias principales. La primera basada en eventos y la segunda que no está basada en eventos. Los eventos consisten en las transiciones de ON a OFF o viceversa de los dispositivos y su algoritmia se enfoca en detectarlos y clasificarlos. Mientras, los que no están basados en eventos se encargan de predecir el estado de los dispositivos. Puesto que la tarea de alto nivel consiste en la clasificación principalmente, se emplea la inteligencia artificial para la resolución del problema. Se pueden optar por métodos supervisados o no supervisados, aunque para este trabajo se hará empleo, como se vio en el apartado anterior, de redes neuronales.

Las aplicaciones de estos sistemas se dividen principalmente en consultar el consumo eléctrico de cierto electrodoméstico por parte del usuario, permitiendo modificar sus hábitos de consumo o cambiar de dispositivo a uno con menor gasto eléctrico. El otro objetivo de los *Smart Meters* y las técnicas *NILM* es el soporte a las personas de la tercera edad, habilitando de manera no intrusiva visualizar y monitorizar las actividades que desarrollan para constatar que están en un buen estado de salud.

#### 2.3 Red neuronal base

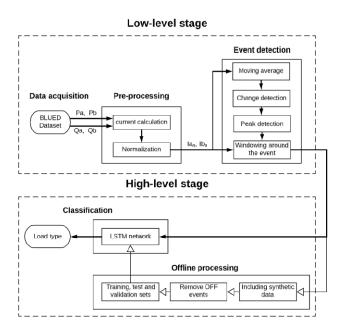

Como se ha podido apreciar en capítulos previos, este trabajo tiene como antecedente otro TFG[3] de la universidad. Su documento se fundamenta en la definición de técnicas no intrusivas para separar el consumo eléctrico de distintos electrodomésticos para el cuidado de personas de tercera edad. Divide por lo tanto la arquitectura de procesado en dos zonas principales que se observan en la figura 2.3. La primera es la de bajo nivel que ya se comentó en la sección pasada que se encargará de la adquisición de muestras, un preprocesado encargado del calculo de la corriente de la red y un último bloque dedicado a encontrar los eventos de ON-OFF que sucedan en las muestras. Para la adquisición, en lugar de conectar el dispositivo a la red se empleó el *Blued Dataset* consistente en una base de datos etiquetada de una familia de Pensylvania, US. La frecuencia de muestreo con la que se adquirió la biblioteca fue con 12 KHz y el experimento duro una semana.

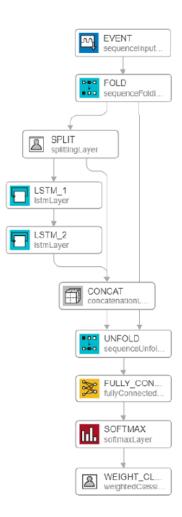

El apartado de alto nivel es el encargado de la clasificación de los electrodomésticos. Para este tipo de señales temporales eléctricas se optó por las redes neuronales recurrentes como mecanismo de clasificación. Siendo las *LSTM* la arquitectura seleccionada para su implementación.

En cuanto al diseño de la red neuronal, en el trabajo se presentan dos opciones, siendo la segunda la más avanzada y representada en la figura 2.4. Como se observa, se emplean para la clasificación dos capas LSTM que destacan por su buen funcionamiento en señales temporales junto con capas densamente conectadas para extraer el porcentaje de pertenencia a cada clase. La precisión de esta red para eventos de ON/OFF es del  $93.90\,\%$  mientras que para eventos únicamente de ON es del  $98.9\,\%$ .

Dado que el presente trabajo se dirige a la implementación de redes neuronales dentro de dispositivos embebidos, el apartado de adquisición queda fuera del estudio y no se llevará ni a la FPGA ni al microcontrolador, quedando como una línea de trabajo futuro. Por lo tanto, el TFM consistirá en la implementación de distintos clasificadores para extraer el tipo de electrodoméstico conectado a la red

Figura 2.3: División de arquitectura en NILM [3].

eléctrica. El punto de partida será el Dataset BLUED preprocesado y con la detección de los eventos para el entrenamiento de diversas redes neuronales.

2.3 Red neuronal base

7

Figura 2.4: Red original descrita para la detección NILM [3].

# Capítulo 3

# Arquitecturas basadas en dispositivos FPGA

A partir de la red neuronal descrita en la sección previa, en este capitulo se adaptará para ser implementadas en una FPGA. Para ello habrá que tener en cuenta los distintos niveles a los que se trabajará y la cuantificación, ya que esta irá vinculada con la utilización de recursos, la latencia y el error cometido con respecto a la red teórica.

El diseño de los distintos sistemas partirá de los resultados obtenidos teóricamente en python y se empleará el paquete hls4ml para adaptar la red a HLS. Esto permitirá que pueda ser probado y sintetizado por el programa Vivado HLS de Xilinx para las distintas arquitecturas de FPGAs. Posteriormente, estas serán sintetizadas e implementadas para el componente seleccionado y finalmente, dado que se introducirán en una arquitectura SoC como periférico, también se tendrá que desarrollar el código correspondiente a la PS que gestione el periférico de la PL. Para este ultimo apartado se empleará el software Vitis de Xilinx. Este esquema de desarrollo se puede visualizar en la 3.1. Además, se probará cada etapa del sistema, pudiéndose volver a fases anteriores del diseño con el objetivo de subsanar los problemas posibles.

El dispositivo seleccionado para el desarrollo de la aplicación es el componente Zynq-7020 de Xilinx implementado en la placa de desarrollo Zeddboard de Digilent de la figura 3.2. Se ha seleccionado este dispositivo para probar la red neuronal con recursos limitados, haciendo que la comparación con la plataforma en  $\mu$ C analizada en el próximo capítulo sea más justa.

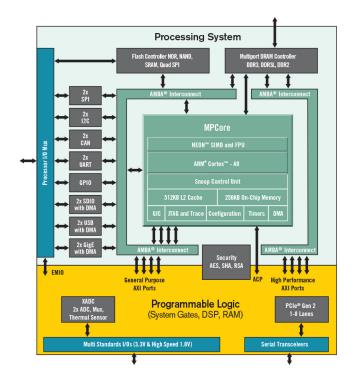

El dispositivo SoC dispone de 2 núcleos de ARM-A9 formando la parte de procesamiento (PS) y una lógica programable con 85.000 celdas lógicas, 4.9 Mb de bloques de RAM y 220 DSP que tendrán una gran importancia como se verá más adelante. Además incorpora más módulos y periféricos como se observa en la figura 3.3 como la UART que se utiliza para visualizar los resultados del test.

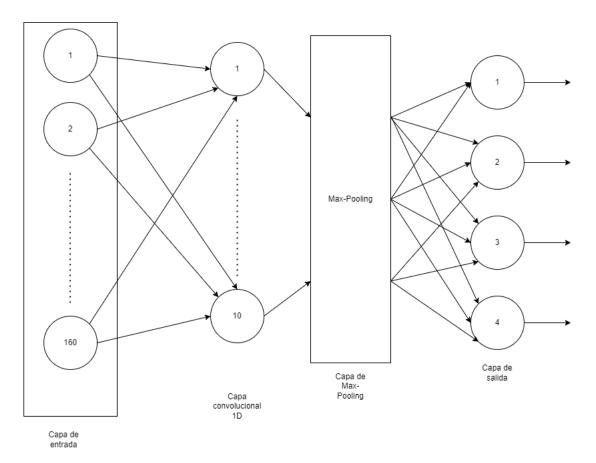

La arquitectura de la red neuronal variará para analizar la dificultad de la implementación desde una red neuronal básica con 4 neuronas de clasificación, hasta una red convolucional. La red presentada en el estado del arte no es posible su síntesis a FPGA debido a que HLS4ML no tiene compatibilidad [14] con las capas recurrentes LSTM.

Figura 3.1: Esquema de desarrollo de la aplicación.

Figura 3.2: Placa de desarrollo Zedboard de Digilent.[4].

#### 3.1 Red neuronal básica

Para comenzar con la implementación de redes neuronales sobre la FPGA se partirá desde un escenario simple, en el que el número de parámetros no sea muy elevado pero la red neuronal consiga aprender y posteriormente se aumentará el número de capas y el tipo de estas. Para ello se empleará diseño de red neuronal orientado a los  $Smart\ Meters$  descrita en el capitulo 2.3 y las fases de implementación vistas en la figura 3.1.

#### 3.1.1 Diseño de la red neuronal básica en Keras

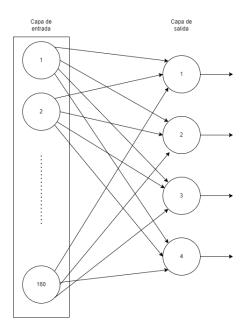

Como se ha comentado previamente, esta solución tratará de resolver el problema de clasificación de cuatro electrodomésticos con el menor número de parámetros posibles. Para ello se utilizarán únicamente las 4 neuronas de clasificación que entregarán como resultado la probabilidad de pertenencia a cada electrodoméstico.

La entrada de la red neuronal serán las 160 muestras temporales de la señal de intensidad preprocesadas, por lo que, teniendo cuatro neuronas densamente conectadas se dispondrá de 644 parámetros en la red. Posteriormente, para la tarea de clasificación se le aplicará una función de activación de tipo Soft-Max

Figura 3.3: Estructura de la Zynq.

| Layer(type)             | Output Shape | Param |  |

|-------------------------|--------------|-------|--|

| input_1 (Input Layer)   | [160,1]      | 0     |  |

| flatten (Flatten)       | [160]        | 0     |  |

| dense (Dense)           | [4]          | 644   |  |

| Total params: 644       |              |       |  |

| Trainable params: 644   |              |       |  |

| Non-trainable params: 0 |              |       |  |

Tabla 3.1: Resumen de la red neurona básica.

para conseguir el porcentaje de pertenencia a la clase. Estas interconexiones se observan en la topología de la red de la figura 3.4 y en el resumen de los parámetros de la tabla 4.7, obtenida utilizando el método summary del modelo creado con Keras. Por otra parte, la capa flatten es prescindible en el modelo simplemente definiendo la entrada como un vector de 160 en vez de una matriz de 160x1, pero dado que su introducción no afecta a los recursos consumidos en la implementación no se ha eliminado.

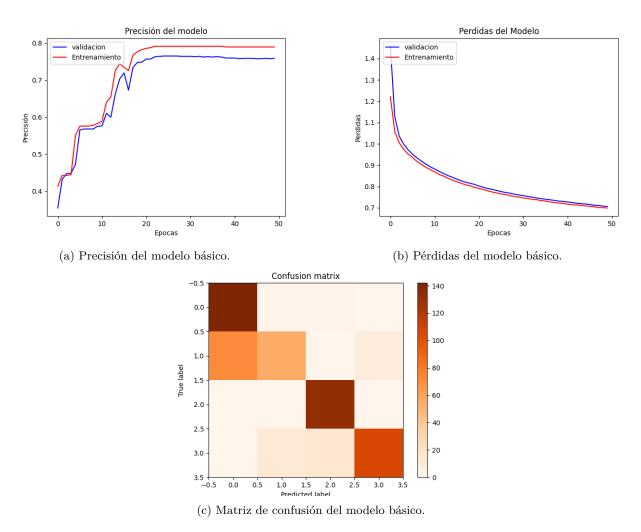

Posteriormente, la red neuronal es entrenada utilizando los mismos hiperparámetros que para el modelo original. El resultado es una precisión de entrenamiento cercana al 80 % a partir de la época 15 y al 77 % en validación como se observa en las dos primeras gráficas de la figura 4.13. Se observa además que a partir de la época 15 se empieza a producir sobreentrenamiento (overfitting) dado que la precisión de aprendizaje sigue aumentando pero la de validación permanece constante. A continuación, se evalúa la mejor red neuronal con los datos de test y se obtiene una precisión del 79.70 % con la correspondiente matriz de confusión que se representa en la última gráfica de la figura 4.13. En la matriz de confusión se observa la producción de falsos positivos destaca entre las dos primeras clases.

Aunque este modelo tiene una precisión bastante mejorable, es bastante sencillo y fácil de implementar, por lo que servirá de utilidad para evaluar el funcionamiento de la herramienta de exportación a HLS que se verá en la siguiente subsección.

Figura 3.4: Topología red neuronal básica.

#### 3.1.2 Conversión de una red neuronal a HLS

Dado que las FPGAs no emplean la notación en coma flotante ya que gastarían muchos recursos disponibles, se emplea la coma fija. La utilización de esta forma de representación permite utilizar números decimales con tamaños de palabra arbitrarios y menores a los estándares de 32 bits de coma flotante. Por lo tanto, un primer paso para implementar la red neuronal en la FPGA es obtener la coma fija a partir de la coma flotante, y un segundo paso es traducir el código de Keras que implementa la predicción de la red neuronal con su estructura de capas a un lenguaje de descripción hardware como VHDL o Verilog. Aunque también se puede convertir en primer lugar a lenguaje de alto nivel como C o C++ y que posteriormente sea traducido a RTL mediante alguna herramienta como el sintetizador de Vivado HLS. Esta última opción será la que se utilizará más adelante pero primero habrá que obtener el proyecto HLS.

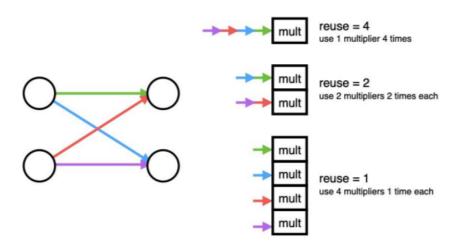

Para ello, se empleará el paquete de *HLS4ML* compatible con *Vivado* que permitirá tanto el paso de coma flotante a fija, como crear el proyecto *HLS* que utilizará *Vivado* por debajo. Por lo tanto, el primer paso para su obtención es la importación del paquete de trabajo como se observa en el código **3.1** y en el que además se incluye una librería para realizar gráficas de manera sencilla y la del sistema operativo para obtener la ruta del programa *Vivado 2019.2*. Posteriormente en el código se creará la configuración correspondiente mediante el comando *hls4ml.converters.convert\_from\_keras\_model*, en el que se introducirá en primer lugar el modelo y posteriormente se fijará la granularidad. Este es un parámetro importante ya que define a que nivel se harán las optimizaciones del proyecto. Tiene tres valores válidos que son: 'model' que permitirá optimizaciones a nivel de modelo, 'type' que las hará para cada tipo de capa, y 'name' que permitirá realizarlas por nombre de capas, siendo esta última la que más grado de detalle alcanza. El segundo parámetro es el *default\_reuse\_factor* que define el número de veces que volverá a utilizar el mismo recurso. Esto se observa claramente en la figura 3.6 en la que a medida que se aumenta el parámetro menos multiplicadores se emplean, pero a su vez aumenta la latencia obtenida.

Finalmente el último parámetro de configuración es el tamaño de coma fija que empleará el datapath del modelo, que en este caso se deja por defecto a 16 bits en los que 10 bits estarán destinados a la

Figura 3.5: Resultados de entrenamiento de la red neuronal básica.

parte fraccionaria y 6 a la parte entera. Cabe destacar que este apartado es importante de cara a que la precisión del modelo sea similar a la obtenida de manera teórica como se observará en futuros proyectos.

Código 3.1: Configuración del modelo.

Figura 3.6: Significado del Reuse factor [5].

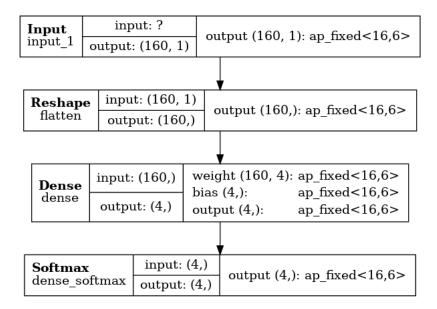

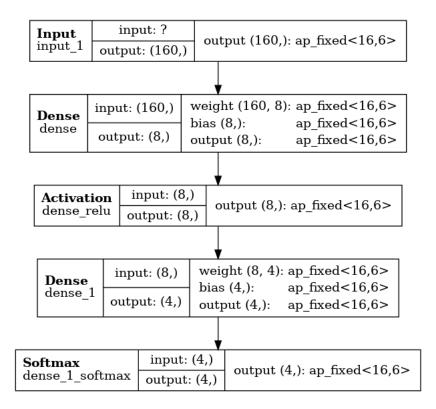

El resumen de las distintas capas generadas previamente convirtiendo el modelo de *keras* en el de *hls4ml* se observa en la figura 3.7. El diagrama se muestra mediante la función *hls4ml.utils.plot\_model*. En ella se puede comprobar que tanto el número de capas como de parámetros es correcto y el tipo de dato que utilizan, que como se ha comentado previamente, es coma fija de 16 bits y 6 de parte entera.

Tras comprobar que el diseño de la red en hls/ml es correcto se procede a generar el proyecto de Vivado HLS que contendrá la red neuronal. Para ello se hará uso de la función hls\_model.compile(). Cabe destacar que esta función únicamente permite ser utilizada en una máquina Linux, por lo que mientras que todo lo demás se ha desarrollado en Windows, será necesario importarlo al otro sistema operativo.

Figura 3.7: Diagrama implementado en la red básica.

Debido a problemas con la creación del entorno, se ha procedido a realizar este procesado en la nube con un entorno de  $Jupyter\ Hub[15]$ . Este sistema permite acceder a recursos computacionales sin necesidad de disponer del hardware y sirve al usuario de un entorno preconfigurado para el  $Data\ Science$ . Además, es la herramienta recomendada por hls4ml para seguir sus tutoriales y dispone de  $Vivado\ 2019.2$  preinstalado que se empleará como backend de la aplicación.

Por lo tanto, al ejecutar la compilación del sistema se generará el proyecto en *Vivado HLS*, aún así se continuará empleando *python* para verificar el comportamiento del sistema. Para ello, mediante el método *hls\_model.predict()* se calcula con la base de datos de test las soluciones del sistema. En este caso se obtiene una precisión del 79.70 %, igual a la obtenida de manera teórica. Por lo tanto, se puede concluir que la cuantificación es correcta para este sistema.

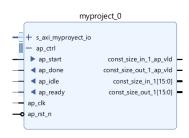

A continuación, se atiende al tema de conexión con el IP que se generaría si se sintetizara y se exportara el sistema. Por defecto, HLS4ML genera una interfaz paralelo con un puerto  $ap\_vld$  para la validación de los puertos de entrada mediante las siguientes sentencias:

```

#pragma HLS ARRAY_RESHAPE variable=input_1 complete dim=0

#pragma HLS ARRAY_PARTITION variable=layer4_out complete dim=0

#pragma HLS INTERFACE ap_vld port=input_1, layer4_out

#pragma HLS PIPELINE

```

Código 3.2: Directivas predeterminadas para I/O.

Dado que para la arquitectura deseada las distintas entradas de la base de datos de test se encuentran en el PS, resulta más sencillo disponer de una interfaz AXI para escribir los datos. Por lo tanto, manualmente se modifican las líneas previamente vistas del fichero myproject.cpp en el que se define la función por las siguientes:

```

#pragma HLS INTERFACE s_axilite port=input_1 bundle=myproyect_io

#pragma HLS INTERFACE s_axilite port=layer4_out bundle=myproyect_io

```

Código 3.3: Directivas para la interfaz AXI para I/O.

El único paso antes de continuar con *Vivado HLS* es la síntesis del sistema. Esto se realiza mediante la función *hls\_model.build()* y tras ello se reproducirán los resultados, lo cual permitirá extraer una comparativa de los recursos empleados, la latencia y si se cumplen las restricciones temporales.

#### 3.1.2.1 Análisis de recursos y latencia resultante

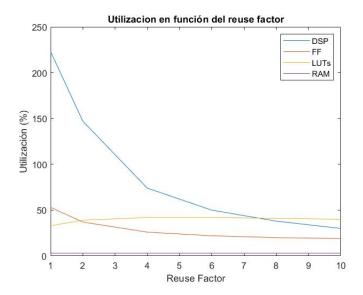

En función del *reuse factor* se puede modificar el consumo de recursos del sistema en la fase de síntesis. Cabe destacar que estos se pueden modificar en el futuro en la fase de la implementación en tarjeta debido a las optimizaciones que realiza el software Vivado, pero dan una idea de los recursos consumidos y la latencia del sistema

Con el reuse factor de 4 se obtiene la utilización mayor con la menor latencia por lo que será el seleccionado para las siguientes etapas. En concreto su utilización de recursos se muestra en la tabla 3.2.

| Name           | BRAM_18K | DSP48E | FF     | LUT   |

|----------------|----------|--------|--------|-------|

| Total          | 3        | 164    | 28420  | 22808 |

| Available      | 280      | 220    | 106400 | 53200 |

| Utilization(%) | 1        | 74     | 26     | 42    |

Tabla 3.2: Utilización básica con  $Reuse\ Factor = 4$ .

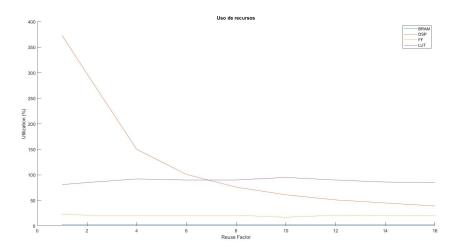

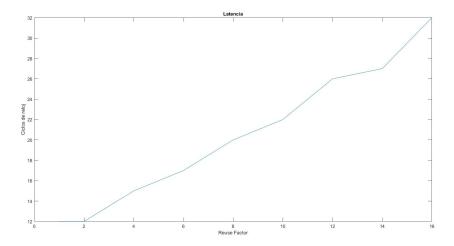

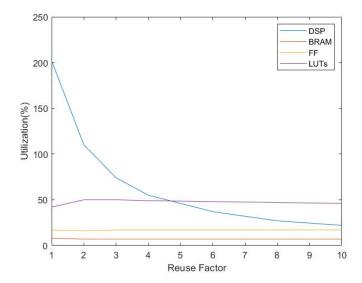

La utilización de BRAM\_18K permanece constante a medida que se varía el parámetro de reutilización pero sin embargo los otros tres varían al modificar su valor como se observa en la figura 3.8. En ella se observa cómo el número de DSP cae abruptamente desde el máximo en el 223 % para el reuse factor de 1 hasta menos del 30 %. Los FF también disminuyen al aumentar el valor pero no es tan significativo. Sin embargo los LUTs sufren un ligero aumento al principio y se mantienen.

Figura 3.8: Utilización en función del reuse factor para la red neuronal básica.

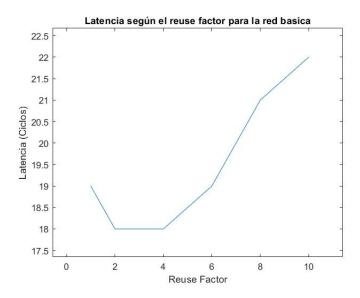

Por otra parte la latencia en ciclos de reloj del sistema aumenta como se evidencia en la figura 3.9, en la que en primer lugar disminuye un poco pero a partir de ahí aumenta. Por lo tanto, se selecciona la configuración con un *reuse factor* de 4 ya que es el primero en convertirse sintetizable en cuanto al número de DSP y es el que tiene una latencia mínima de 18 ciclos de reloj.

Figura 3.9: Latencia en función del reuse factor para la red neuronal básica.

### 3.1.3 Pruebas realizadas en HLS

Todas las pruebas previas se podían haber realizado desde el programa de HLS, pero se ha preferido exprimir al máximo las funciones de HLS4ML ya que permiten gestionar el proyecto de Vivado desde alto nivel. Aún así, a modo de comprobación se prueba el sistema ya sintetizado en  $Vivado\ HLS$  para observar que el código es correcto. Para ello se ha generado un testbench en el que se le alimente a la red neuronal con las muestras de test. En primer lugar se ha almacenado en una variable las  $547 \times 160$  de la señal de entrada en formato de coma flotante que convertirá el compilador en  $ap\_fixed<16,6>$  y las 547 salidas. Estas se han introducido en la red y se han obtenido los mismos resultados obtenidos en la subsección anterior como se evidencia en la figura anterior 3.10.

```

© Console ☼ № Tasks № Problems ○ Executables № Debugger Console

<terminated > (exit value: 0) myproject_prj.Debug [C/C++ Application] csim.exe

Numero de muestras de test: 547

El numero de errores es: 111 y de aciertos 436

Accuracy: 0.797075

```

Figura 3.10: Resultados en Vivado HLS de la Red Básica.

### 3.1.4 Diseño del sistema en Vivado

A partir de la síntesis en HLS se exporta el RTL para poder ser utilizado en Vivado. Con esto se generará un modulo IP con la configuración de entrada/salida de la figura 3.11. Se dispone de un puerto AXI desde el que se controlará la entrada y la salida de la red, los puertos de reloj y reset y finalmente una interfaz  $ap\_ctrl$ . Esta interfaz manejará el inicio de operación del módulo mediante su puerto de

entrada y sus tres puertos de salida. La señal ap\_start marcará el comienzo del cálculo siempre y cuando ap\_ready esté a nivel alto. Por otra parte, ap\_idle y ap\_ready indican cuando se está realizando las operaciones y cuando se han terminado respectivamente. Por otra parte, tiene otras cuatro salidas que indican el tamaño de los datos de entrada y salida y su validez, que no se emplearán.

Figura 3.11: Configuración de puertos del IP básico.

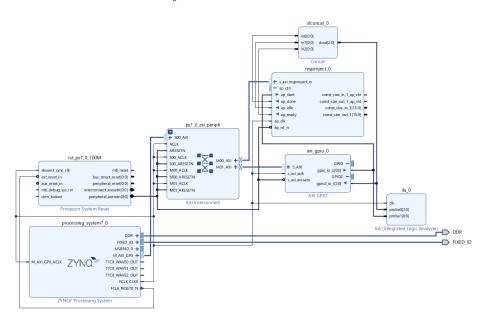

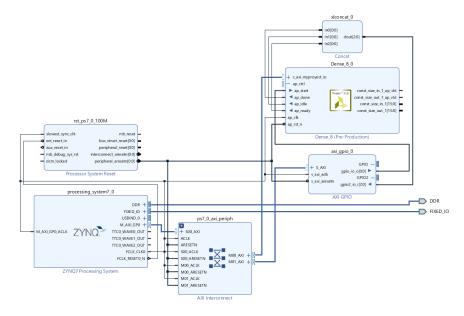

Puesto que se empleará un SoC será necesario conectar el modulo con la PS como se observa en la figura 3.12, en la que el AXI de la red neuronal se conecta mediante un módulo AXI interconnect al igual que los cuatro puertos del  $ap\_ctrl$ , aunque estos necesitarán pasar previamente por un módulo AXI GPIO. Este estará configurado de manera que tenga 2 puertos, el primero de ellos de 1 bit de salida y el segundo de 3 bits de todo entradas, lo que permitirá controlar facilmente estos puertos desde el procesador. Además, estos puertos llevan a un ILA para ser depurados en caso de observarse errores. Finalmente, el pin de reloj es compartido entre todos los modulos y es de 100 MHz. La señal de reset del sistema se creará mediante el IP Processor System Reset.

Figura 3.12: Esquema básico.

Posteriormente se crea el bitstream y se obtiene la utilización de recursos del sistema implementado de la tabla 3.3, en la que se observa que el consumo de recursos con respecto a BRAM y DSP es el mismo con respecto a la tabla 3.2, pero el número de FF y LUTs disminuye significativamente debido a las optimizaciones realizadas por Vivado para la síntesis e implementación en FPGA. Por otra parte, en esta figura no se encuentra únicamente el módulo IP diseñado sino que también habrá otros como el ILA o el AXI Interconnect que consumen recursos, pero su influencia es inferior al 5 % de los recursos disponibles.

| Resource | Total | Available | Utilization (%) |

|----------|-------|-----------|-----------------|

| LUT      | 11775 | 53200     | 22.13           |

| FF       | 15718 | 106400    | 14,77           |

| BRAM     | 3.5   | 140       | 2.5             |

| DSP      | 164   | 220       | 74.55           |

Tabla 3.3: Recursos de la red neuronal en Vivado.

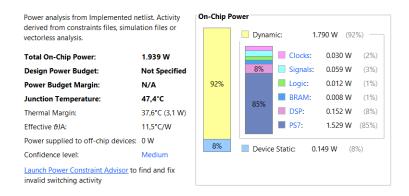

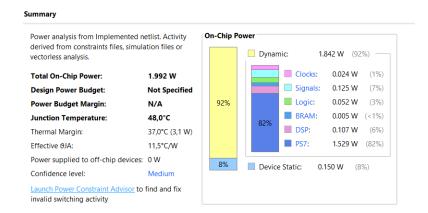

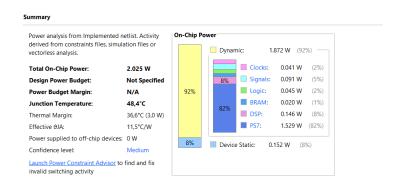

Otro aspecto importante es la potencia consumida por la placa y la temperatura de operación. Vivado ofrece estos resultados como se observa en la figura 3.13. La potencia consumida por el apartado de PL está entorno al  $15\,\%$  mientras que el de la PS es del  $85\,\%$ , aunque este consumo se puede modificar en función de las tareas que realice este apartado.

Figura 3.13: Potencia consumida por la implementación.

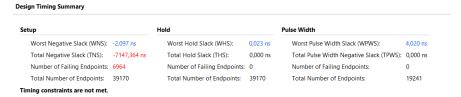

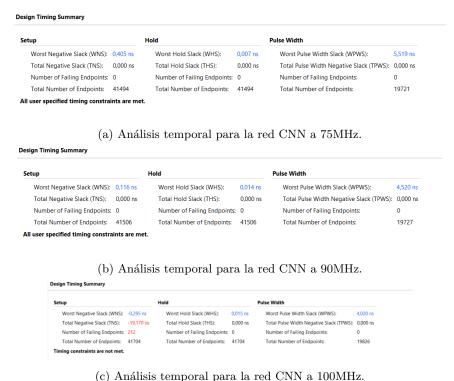

Finalmente hay que analizar el aspecto temporal. Se realizará un barrido desde los 100 MHz hasta que se produzcan errores para observar la máxima frecuencia de reloj que puede soportar el sistema con la implementación realizada. Los resultados para 100 MHz se observan en la figura 3.14a y son positivos ya que se cumplen las restricciones. Para 110 MHz sucede igual como se percibe en la figura 3.14b aunque el margen es mucho menor y muy cercano a cero. Por lo tanto, no se podrán llevar grandes subidas de frecuencia. Esto se corrobora con la figura 3.14c, en la que el tiempo de setup falla para 125 MHz.

A la vista de estos resultados se extrae que la frecuencia máxima es de 110 MHz con la que se tendría una latencia mínima de 162ns. Sin embargo, se emplea una frecuencia de 100 MHz para futuros apartados para tener un margen temporal mayor con una latencia de 180ns.

#### 3.1.5 Diseño del sistema en *Vitis*

Tras diseñar el apartado de hardware para la PL se exporta el bitstream y se comienza con la fase de diseño del software en la PS. Esta se realizará en el programa Vitis de Xilinx, en primer lugar se importará la plataforma de hardware previamente creada y a continuación se procederá con la aplicación. Esta realizará un trabajo similar a las pruebas realizadas en HLS, se les introducirá las 547 muestras de test y se extraerán los resultados. Para extraer los resultados desde la placa se leerán desde la UART.

En primer lugar, se almacenará la matriz  $547 \times 160$  como unidimensional con todos los datos que se utilizarán como entradas en formato de coma fija con 16 bits y 10 de parte fraccional y las 547 salidas.

| Setup                                    |                        | Hold                           |                      | Pulse Width                                  |                                         |

|------------------------------------------|------------------------|--------------------------------|----------------------|----------------------------------------------|-----------------------------------------|

| Worst Negative Slack (WNS                | 5): 0,467 ns           | Worst Hold Slack (WHS):        | 0,028 ns             | Worst Pulse Width Slack (WPWS):              | 3,750 ns                                |

| Total Negative Slack (TNS):              | 0,000 ns               | Total Hold Slack (THS):        | 0,000 ns             | Total Pulse Width Negative Slack (TPWS       | ): 0,000 ns                             |

| Number of Failing Endpoint               | ts: 0                  | Number of Failing Endpoints    | : 0                  | Number of Failing Endpoints:                 | 0                                       |

| Total Number of Endpoints:               | 38666                  | Total Number of Endpoints:     | 38650                | Total Number of Endpoints:                   | 16111                                   |

| All user specified timing const          | traints are m          | et.                            |                      |                                              |                                         |

|                                          |                        |                                |                      |                                              |                                         |

| ,                                        |                        |                                |                      | 1.4.4                                        |                                         |

| (                                        | a) Anál                | isis temporal para el          | esquen               | na básico a 100MHz.                          |                                         |

| sign Timing Summary                      |                        |                                |                      |                                              |                                         |

| etup                                     |                        | Hold                           |                      | Pulse Width                                  |                                         |

| Worst Negative Slack (WNS):              | 0,142 ns               | Worst Hold Slack (WHS):        | 0,021 ns             | Worst Pulse Width Slack (WPWS):              | 3,250 ns                                |

| Total Negative Slack (TNS):              | 0,000 ns               | Total Hold Slack (THS):        | 0,000 ns             | Total Pulse Width Negative Slack (TPWS):     | 0,000 ns                                |

| Number of Failing Endpoints:             | 0                      | Number of Failing Endpoints: ( | )                    | Number of Failing Endpoints:                 | 0                                       |

| Total Number of Endpoints:               | 38666                  | Total Number of Endpoints:     | 38650                | Total Number of Endpoints:                   | 16111                                   |

| ll user specified timing constrai        | ints are met.          |                                |                      |                                              |                                         |

|                                          |                        |                                |                      |                                              |                                         |

| (                                        | b) Anál                | isis temporal para el          | esquen               | na basico a 110MHz.                          |                                         |

|                                          |                        |                                |                      |                                              |                                         |

| Setup                                    |                        | Hold                           |                      | Pulse Width                                  |                                         |

|                                          | -0,087 ns              | Hold Worst Hold Slack (WHS):   | 0,019 ns             | Pulse Width  Worst Pulse Width Slack (WPWS): | 2,750 ns                                |

| Setup                                    | -0,087 ns<br>-0,087 ns |                                | 0,019 ns<br>0,000 ns |                                              | _,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| <b>Setup</b> Worst Negative Slack (WNS): | -0,087 ns              | Worst Hold Slack (WHS):        | 0,000 ns             | Worst Pulse Width Slack (WPWS):              | _,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

(c) Análisis temporal para el esquema básico a 125MHz.

Figura 3.14: Análisis temporal del esquema básico para distintas frecuencias.

Estas serán constantes del sistema y estarán almacenadas en ficheros .h. En el main en primer lugar se inicializará la plataforma. Después habrá que arrancar el periférico correspondiente a la red neuronal. Para ello, cuando se generó el IP en Vivado HLS, se creó automáticamente un driver con funciones que permiten utilizar el periférico. Para la funcionalidad previamente comentada se empleará la funcion int XMyproject\_Initialize(XMyproject \*InstancePtr, u16 DeviceId); en la que se introducirá la estructura de tipo XMyproject y el ID del dispositivo. A continuación, hay que hacer lo mismo con los XGPIO que permiten controlar el comienzo y la lectura del periférico con la función int XGpio\_Initialize(XGpio \*InstancePtr, u16 DeviceId) y fijar la dirección de sus puertos con void XGpio\_SetDataDirection(XGpio \*InstancePtr, unsigned Channel,u32 DirectionMask), en los que el canal 1 será de salida y el 2 de entrada. Por lo que, en el canal 1 se fijará el bit ap\_start y en el canal 2 se leerán los bits del resto de puertos en la interfaz.

Tras esa primera fase de inicialización se procederá con la fase de pruebas. En primer lugar se leerán los 160 números correspondientes a cada fila de la base de datos. A continuación, hay que destacar que el periférico tiene 2 modos de lectura y escritura, en modo palabra (4 bytes) y en modo byte. Por velocidad se empleará el modo palabra, por lo que, dado que las variables están empleando 16 bits, habrá que agrupar 2 variables en una mediante el siguiente código para los datos de entrada:

Código 3.4: Agrupación de dos muestras de 16 bits en una sola palabra de 32 bits.

Para los datos de salida la operación es la contraria, hay que seleccionar únicamente los primeros 16 bits o los siguientes. A continuación, mediante la función del driver u32 XMyproject\_Write\_input\_2\_V\_Words(XMyproject \*InstancePtr, int offset, int \*data, int length) se escribirán los datos en el periférico. Para ello, en los datos se introduce la matriz de entrada colocada en formato palabra y se fijará la longitud en 80. Tras terminar la operación se fijará el GPIO correspondiente al ap\_start a nivel alto y acto seguido a nivel bajo, dando comienzo al procesado.

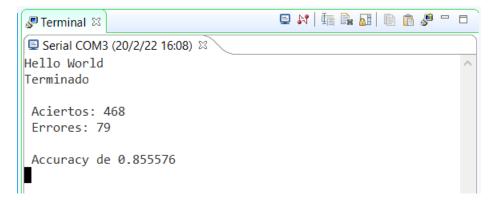

En este caso se opta por una espera activa por facilidad, quedando el programa en un bucle *while* hasta que el periférico esté en estado de *done*. Posteriormente se leen los resultados, se selecciona el que mayor probabilidad tenga como solución del sistema y se almacena en una matriz. Este proceso se repite 547 veces y tras completarse se procede a calcular el número de aciertos y errores ocurridos y la precisión. Cuando dispone de esos datos se los trasmite por la *UART* al ordenador para observar los resultados obtenidos.

Por lo tanto, al ejecutar el código se observará en un terminal unos resultados iguales a los de la figura 3.15 que son exactamente iguales a los obtenidos de manera teórica y en HLS.

Figura 3.15: Resultados de la red neuronal básica implementada en la tarjeta.

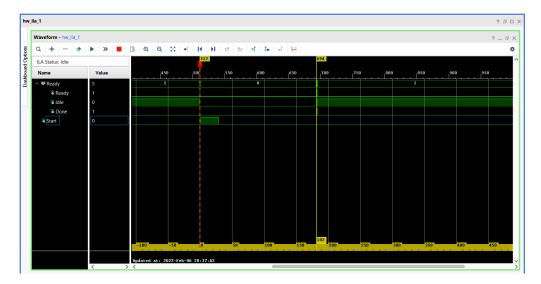

Por otra parte, si mediante el ILA se observa los puertos de  $ap\_ctrl$  para una iteración se obtendrán los resultados de la figura 3.16, en los que se observa que la latencia de reloj es aproximadamente los 80 ciclos de reloj que se calcularon teóricamente en HLS.

Figura 3.16: Resultados en ILA de la red neuronal básica implementada en la tarjeta.

### 3.2 Red neuronal de dos capas densamente conectadas

La sección anterior permitía visualizar un ejemplo sencillo de red neuronal que llegaba a aprender el comportamiento del sistema pero su falta de parámetros no permitía que estos progresaran. En este capítulo se analizará una red neuronal más profunda con dos capas y un número mayor de neuronas densamente conectadas permitiendo un mejor nivel de aprendizaje. Las fases de diseño en este caso serán las mismas que el anterior. Se partirá del diseño en Keras de la red y posteriormente se bajará de niveles, primero convirtiendo el proyecto en HLS, posteriormente en RTL y finalmente uniéndolo con el processing system del SoC.

### 3.2.1 Diseño de la red neuronal de dos capas en Keras

El modelo desarrollado en este apartado tendrá las mismas 160 entradas que en el apartado anterior, pero verá aumentado el número de neuronas. Se ha apostado por hacer dos capas densamente conectadas. La primera tendrá 8 neuronas con una función de activación Relu mientras que la segunda serán 4 neuronas con función de activación Soft-max iguales que en la sección anterior. La topología de la red neuronal se observa en la figura 3.17.

Por lo tanto, en este caso el número de parámetros entrenables para la primera capa serán 1288 y en la segunda 36 como se observa en la tabla 3.4. Para este modelo se han duplicado el número de parámetros con respecto al caso anterior.

| Layer(type)             | Output Shape | Param |  |  |  |

|-------------------------|--------------|-------|--|--|--|

| input_1 (Input Layer)   | [160,1]      | 0     |  |  |  |

| dense (Dense)           | [8]          | 1288  |  |  |  |

| dense_1 (Dense)         | [4]          | 36    |  |  |  |

| Total params: 1324      |              |       |  |  |  |

| Trainable params: 1324  |              |       |  |  |  |

| Non-trainable params: 0 | )            |       |  |  |  |

Tabla 3.4: Resumen de la red neurona de dos capas densamente conectadas.

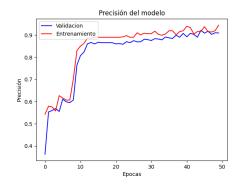

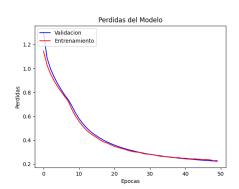

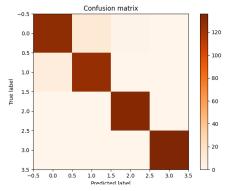

Posteriormente se procede al entrenamiento de la red neuronal empleando los mismos hiperparámetros del modelo original y se consigue una precisión cercana al 90 % para el entrenamiento y la validación a partir

Figura 3.17: Topología de la red neuronal de dos capas densas.

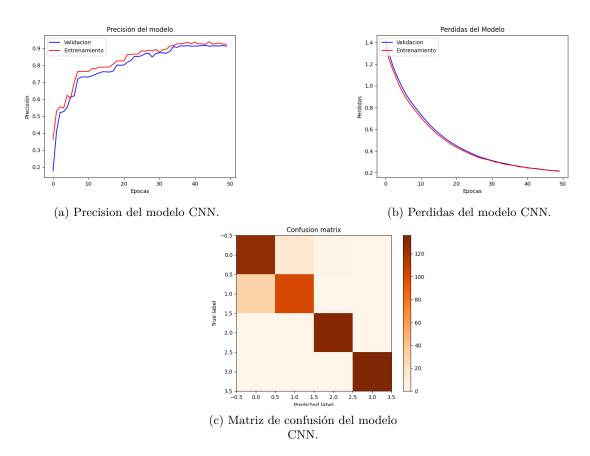

de la época 15 como se observa en la figura 3.18a. Sin embargo, para test se obtiene una precisión del 95.79% y una matriz de confusión en la que la mayoría de errores se producen entre el primer y segundo electrodoméstico como se visualiza en la figura 3.18c. Por lo tanto, este modelo es bastante positivo y se llevará a la implementación en FPGA.

- (a) Precisión del modelo de dos capas densas.

- (b) Pérdidas del modelo de dos capas densas.

(c) Matriz de confusión del modelo de dos capas densas.

Figura 3.18: Resultados de entrenamiento de la red neuronal de dos capas densas.

### 3.2.2 Conversión de la red de dos capas densas a HLS

A continuación se procederá a convertir el modelo de *Keras* en un modelo de *HLS* siguiendo los mismos pasos que para la red anterior. Se tomarán las mismas variables con un *reuse\_factor* inicial de 1 y una cuantificación de 16 bits con 6 bits de parte entera. Con ello se obtiene la arquitectura del modelo de la figura 3.19 con los tamaños de cada variable de la red.

Figura 3.19: Diagrama del modelo HLS con dos capas densamente conectadas.

Se sigue avanzando los pasos convirtiendo el diseño en un proyecto de  $Vivado\ HLS$  y se prueba la precisión de la predicción con las muestras de test. Al realizar este proceso se observa que hay un fallo en la cuantificación ya que mientras la precisión teórica era de 95 % con el modelo HLS se obtiene un 80 %.

Este error puede ser debido a múltiples factores como cuantificación, redondeo o desbordamiento. Para ello en la siguiente sección se llevará a cabo un estudio a nivel de modelo para disminuir el error cometido entre el modelo teórico y el que se va a implementar.

### 3.2.2.1 Estudio de la cuantificación en el modelo de dos capas densas

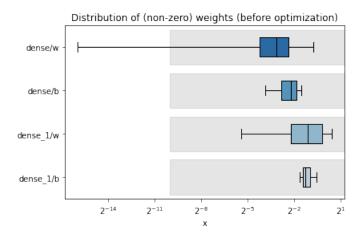

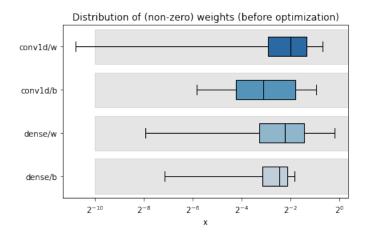

Como se ha comentado anteriormente, hay un problema con la cuantificación del sistema. Para solucionarlo, hls4ml ofrece múltiples herramientas. En primer lugar, se observará la cuantificación necesaria para implementar cada uno de los parámetros entrenados necesarios. Para ello se empleará la función  $hls4ml.model.profiling.numerical(model=model, hls_model=hls_model)$  que mostrará la cuantificación necesaria para cada uno de los parámetros y la que se está garantizando con la configuración seleccionada de manera gráfica como se observa en la figura 3.20. Se aprecia que la cuantificación de coma fija con 16 bits y 10 de parte decimal son correctos a excepción de los pesos de la primera capa densa, que necesitan de hasta 16 bits de parte decimal para estar correctamente representados. Por lo tanto, el primer paso a adoptar es cambiar el tipo de optimización a nivel de capa y fijar el tamaño de bits de los pesos de la capa densa

para que cumplan las restricciones manualmente con config['LayerName']['dense']["Precision"]['weight'] =  $'ap\_fixed < 20,2>$ '. Con ello se obtiene un aumento de la precisión desde el 80 % al 83.72 %, lo cual es significativo pero sigue sin igualar las prestaciones iniciales de la red de diseño.

Figura 3.20: Cuantificación de los parámetros en la red neuronal de dos capas.

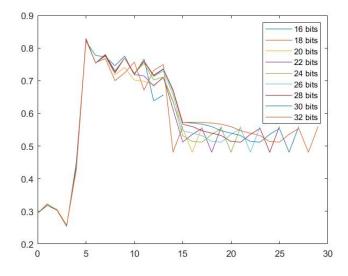

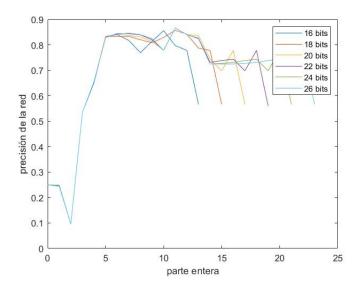

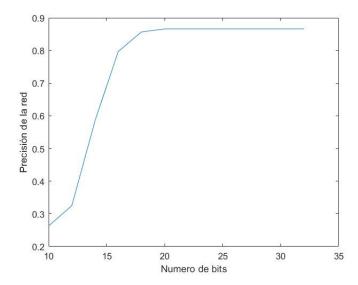

Para solucionarlo se adopta una estrategia distinta en la que se realizan optimizaciones al modelo completo barriendo la utilización de bits desde 16 hasta 32 bits con distintos repartos en el tamaño de las palabras. En concreto, se subirá desde 0 bits de parte entera hasta el casi el número de bits totales. Como figura de mérito se utilizará la precisión obtenida para cada combinación de número de bits y parte entera asignada. La respuesta obtenida se evidencia en la figura 3.22, en la que se observa que cuando la parte entera es menor a 4 el error es máximo y que a partir de ese valor crece abruptamente hasta llegar al máximo con 5 bits. Esto se debe a que antes de 4 bits, no había resolución suficiente para todas las representaciones y en 5 bits se alcanza la resolución de la parte entera óptima. A partir de este valor, la solución empeora dado que cada vez se dedica menos bits a la parte fraccionaria y los añadidos a la parte entera no mejoran la respuesta.

Figura 3.21: Respuesta a la variación de la cuantificación en la estructura de dos capas variando la coma fija.

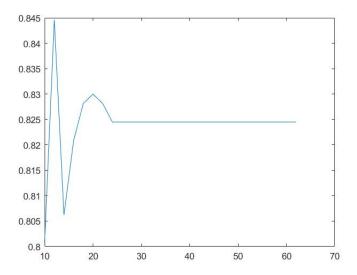

Por otra parte, esta respuesta es muy similar aunque se aumente el número de bits, en todos los casos se alcanzará un valor de 83 % como máximo a los 5 bits de coma fija. Para comprobar esa poca relación entre el número de bits y la mejora de rendimiento se realiza un segundo barrido. En él se fija el tamaño de la parte entera en 5 bits y se aumenta el tamaño de la palabra desde 10 hasta 64 obteniendo un máximo con un tamaño de 12 bits de casi el 85 %. A partir de ahí sufre fluctuaciones alrededor del 82.5 % y a partir de los 24 bits se fija constante en ese valor.

Figura 3.22: Respuesta a la variación de la cuantificación en la estructura de dos capas.

Dado que la resolución a nivel global parece estar bien, se debe analizar más en concreto la capa sobre la que sucede la falta de cuantificación. En concreto, analizando las respuestas de la red se ha observado que a la salida de la función de activación Soft-max hay números negativos, lo cual desde el punto de vista teórico es incorrecto. Por lo tanto, de cara a un diseño e implementación final es necesario hacer una optimización de todas las capas hasta obtener unos resultados cercanos a los obtenidos desde el punto de vista teórico.

Finalmente, dado que este trabajo se basa en el análisis de las herramientas para implementar algoritmos de  $Deep\ Learning$  en sistemas empotrados se toma para la implementación en el sistema tamaños que no son óptimos pero que facilitan el uso del sistema. En primer lugar se selecciona el tamaño de palabra de 16 bits para que la interfaz AXI escriba 2 números por ciclo agilizando las comunicaciones y facilitando el paso de datos desde la PS a la PL. Además, permite que el testbench de la subsección anterior sean reutilizables para esta. Por otra parte, se asignan 7 bits a la parte entera ya que para este valor se alcanza el máximo de la función de 82.44% para las muestras de test.

### 3.2.2.2 Análisis de recursos y latencia resultante

De manera análoga al apartado de las cuatro neuronas de clasificación, será necesario realizar un análisis de los recursos que consumirá la red neuronal dentro de la lógica programable. Para ello, se recuerda que el parámetro de peso para modificar la latencia y el consumo de recursos es el *reuse factor*.

Si se sintetiza el proyecto de HLS para un reuse factor de 1 se obtienen los datos de la tabla 3.5. En ellos se observa que la ocupación del sistema es muy elevado, consumiendo gran cantidad de los LUTs disponibles de la placa y excediendo los DSP disponibles. Sin embargo, para esta estructura se obtiene

una latencia de 12 ciclos de reloj, lo que empleando un reloj de 100 MHz serían 120 ns. Por lo que, para otra FPGA con un mayor número de recursos sería una implementación muy buena en términos de latencia.

| Resource | Total | Available | Utilization (%) |

|----------|-------|-----------|-----------------|

| LUT      | 43204 | 53200     | 81              |

| FF       | 25450 | 106400    | 23              |

| BRAM     | 3     | 280       | 1               |

| DSP      | 821   | 220       | 373             |

Tabla 3.5: Recursos de NN en Vivado para estructura de dos capas con Reuse factor de 1.

A pesar de estos datos, los recursos no son suficientes por lo que es necesario aumentar el  $Reuse\ factor$  para conseguir implementarlo. Para ello se realizan variaciones desde 1 hasta 16, obteniendo los resultados de la gráfica 3.23, en la que se observa que el consumo de FF y BRAM permanece prácticamente constante mientras que el número de DSP disminuye abruptamente siendo implementable con un reuse factor de 8. Por otra parte, los LUTs tienen un comportamiento opuesto, cuanto mayor es el factor de reutilización, más recursos consumen para implementar el control de uso de los DSP.

Figura 3.23: Recursos consumidos en la fase de síntesis variando el *Reuse factor* en la estructura de dos capas.

Al aumentar el factor también aumenta la latencia como se observa en la figura 3.24 desde los 12 ciclos de reloj hasta los 32 de manera casi lineal. Por lo tanto, para la siguiente fase de diseño se utilizará un reuse factor de 10, ya que se considera que con uno de 8, al consumir cerca del 75% de los DSP, puede complicar bastante el enrutado del dispositivo. Con este valor se obtiene una latencia de 22 ciclos de reloj y cerca del 60% de los DSP consumidos.

Por otra parte, los resultados ofrecidos se analizan para un interfaz de E/S paralelo por sencillez, pero de cara a su implementación en el SoC no es eficaz para comunicarse con la PS. Por lo tanto, de manera análoga al apartado anterior se cambia la interfaz de comunicaciones a un AXI Lite. Esto aumenta el número de recursos observados en la figura 3.6 y la latencia hasta 183 ciclos de reloj pero el consumo de DSP permanece constante.

Figura 3.24: Latencia variando el Reuse factor en la estructura de dos capas.

| Resource | Total | Available | Utilization (%) |

|----------|-------|-----------|-----------------|

| LUT      | 50616 | 53200     | 95              |

| FF       | 18411 | 106400    | 23              |

| BRAM     | 6     | 280       | 2               |

| DSP      | 136   | 220       | 62              |

Tabla 3.6: Recursos de NN en Vivado para estructura de dos capas con interfaz AXI.

### 3.2.3 Pruebas realizadas en HLS

Tras completar la conversión y síntesis del proyecto el sistema queda preparado para su desarrollo *RTL*. Para ello, en primer lugar se prueba el sistema en el programa *Vivado HLS*. El *testbench* empleado es exactamente igual, dado que las entradas al sistema son las mismas, únicamente cambia la distribución de bits en coma fija pero su conversión se realiza de manera automática por el simulador. Los resultados observados en la captura de la figura 3.25 tienen un ligero aumento en la precisión con respecto a los obtenidos en *python* con la cuantificación utilizada. Se asume que es debido a cómo se implementa el método *argmax* en python y al desarrollado en C++ mediante el siguiente código.

```

int argmax(result_t y[4])

{

int i;

int location=0;

float maximo=0;

float y_actual=0;

for (i = 0; i < 4; i++)

{

y_actual=y[i].to_float();

if (y_actual > maximo)

{

location = i;

maximo = y_actual;

}

}

```

```

}

return location+1;

}

```

Código 3.5: Código de la función argmax

```

© Console

② ② Tasks № Problems ○ Executables ② Debugger Console

<terminated> (exit value: 0) Dense & prj.Debug [C/C++ Application] csim.exe

Numero de muestras de test: 547

El numero de errores es: 78 y de aciertos 469

Accuracy: 0.857404

```

Figura 3.25: Resultados en HLS de estructura con dos capas.

Dado que este aumento mejora el resultado original sin modificar las probabilidades obtenidas a la salida de la red, los resultados se considerán positivos y se continúa con la fase siguiente del diseño. Para ello se exportará el *RTL* de *HLS* a *Vivado*.

### 3.2.4 Implementación en Vivado

Al exportar el RTL se obtiene un bloque con las mismas entradas y salidas que en la red anterior como se observa en la figura 3.26.

Figura 3.26: Bloque IP de la red de dos capas densamente conectadas.

La funcionalidad de estos puertos es exactamente la misma, por lo tanto se excluye su explicación en este apartado. Su conexionado con el resto de circuitos es exactamente igual al anterior como se observa en la figura 3.27 pero en este caso no se incluirá el *ILA* dado que los resultados obtenidos son iguales a los obtenidos en el apartado anterior y así se excluye su consumo de recursos en la implementación.

Considerando únicamente estos bloques, que harían que el sistema funcionará a la perfección se incluyen los resultados de la figura 3.7, en los que se observa que al igual que en el apartado anterior, se reducen desde el  $95\,\%$  hasta el  $38.67\,\%$ , siendo significativa esta reducción. El número de LUTs también se verá afectado, pero únicamente disminuirá un  $5\,\%$ . Por otra parte, el número de DSP y BRAM permanece constante.

Figura 3.27: Esquema de conexionado de bloques en Vivado con dos capas.

| Resource | Total | Available | Utilization (%) |

|----------|-------|-----------|-----------------|

| LUT      | 20575 | 53200     | 38.67           |

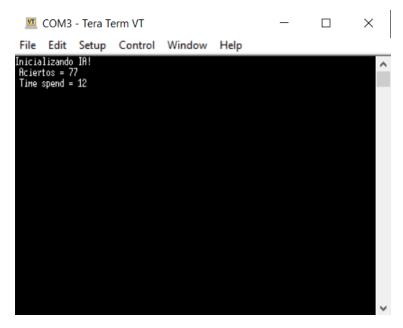

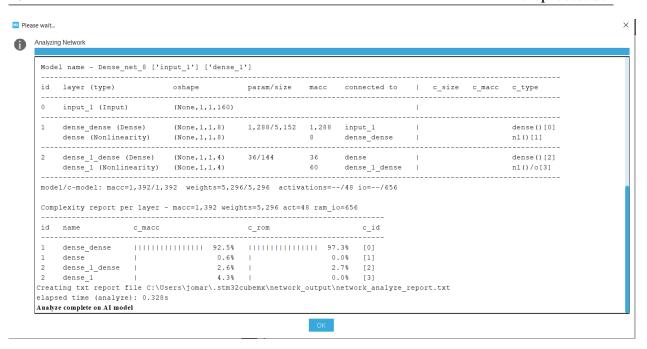

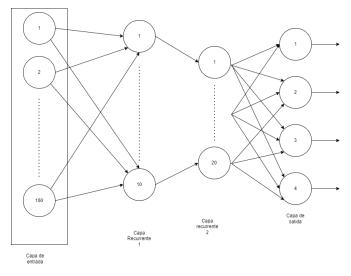

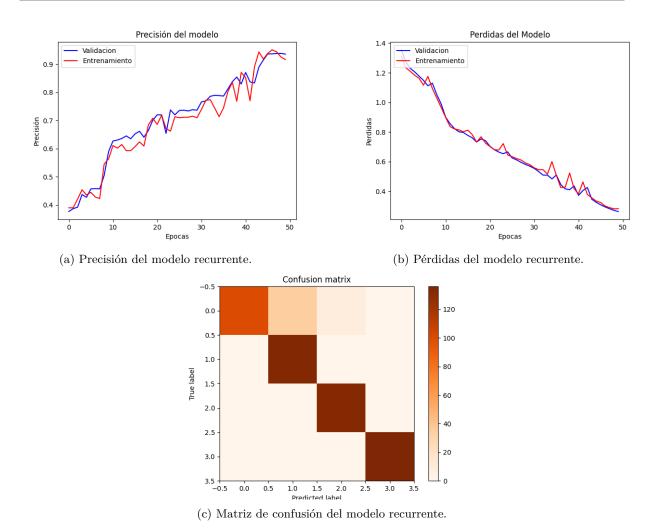

| FF       | 19157 | 106400    | 18              |