Technological University Dublin ARROW@TU Dublin

Articles

School of Electrical and Electronic Engineering

2016

# Three-level hysteresis current control strategy for three-phase four-switch shunt active filters

Samet Biricik

Hasan Komurcugil

Follow this and additional works at: https://arrow.tudublin.ie/engscheleart2

Part of the Electrical and Computer Engineering Commons

This Article is brought to you for free and open access by the School of Electrical and Electronic Engineering at ARROW@TU Dublin. It has been accepted for inclusion in Articles by an authorized administrator of ARROW@TU Dublin. For more information, please contact arrow.admin@tudublin.ie, aisling.coyne@tudublin.ie, gerard.connolly@tudublin.ie.

This work is licensed under a Creative Commons Attribution-Noncommercial-Share Alike 4.0 License

# Three-level hysteresis current control strategy for three-phase four-switch shunt active filters

ISSN 1755-4535 Received on 2nd October 2015 Revised on 15th February 2016 Accepted on 2nd March 2016 doi: 10.1049/iet-pel.2015.0764 www.ietdl.org

### Samet Biricik<sup>1,2</sup>, Hasan Komurcugil<sup>3</sup> ⊠

<sup>1</sup>Department of Electrical and Electronic Engineering, European University of Lefke, Via Mersin 10, Turkey <sup>2</sup>School of Electrical and Electronic Engineering, Dublin Institute of Technology, Ireland <sup>3</sup>Department of Computer Engineering, Eastern Mediterranean University, Gazimağusa, Via Mersin 10, Turkey © E-mail: hasan.komurcugil@emu.edu.tr

Abstract: In this study, a three-level hysteresis current-control (HCC) strategy is proposed for three-phase four-switch shunt active power filters. The four-switch topology which utilises four switching devices together with two series connected capacitors is able to reduce the cost, switching losses and improve the reliability of system. In this topology, when the current control of phases A and B is achieved successfully, the current control of phase C which is connected to the midpoint of the series connected capacitors is achieved automatically. The current control is achieved by using a three-level HCC strategy. An important consequence of using this control strategy is that it enables access to the zero level of the input voltage of active filter so that a switching device is only switched when the current error is negative, while it remains off when the current error is positive. Furthermore, the imbalance in the capacitor voltages is eliminated by adding a feedback term (the difference in the capacitor voltages multiplied by a suitable gain) to the current control. The proposed control strategy offers a reduced switching frequency, losses and cost. The steady-state and dynamic performance of the proposed control strategy is verified through simulations and experimental studies.

#### 1 Introduction

Owing to the common use of power electronics in domestic, industrial and commercial devices, the harmonic current distortion on the utility is increasing. This current distortion causes low-power factor,  $I^2R$  losses and harmful disturbance to neighbour loads which are tied at the point of common coupling (PCC). Conventional switched capacitors with tuned LC filters are usually employed to reduce the current harmonics. However, the use of such filters has many disadvantages such as resonance problem, fixed compensation ability and large size. Also, the performance of the system may be adversely affected from the changes in the filter parameters due to temperature and ageing.

As a remedy to these drawbacks, the use of shunt active power filters (APFs) to solve current harmonic problems has drawn much attention since the 1970s, because they have good filtering characteristics [1-3]. Voltage-source inverter (VSI) with six switching devices is the most preferred topology for the three-phase shunt APF [4-13]. The control methods that have been studied for shunt APFs have three important parts: (i) determination of reference compensation current from the distorted load current; (ii) the current control of the VSI; and (iii) the voltage control on the DC-link capacitor. The compensating current reference generation process usually involves various methods. The quality of the current-control strategy greatly influences the overall performance of the APF system. Besides this, these methods play a very important role in the improvement of steady-state and dynamic performances and the stability of the filter. Since the load current harmonics may change rapidly, the APF should have a fast dynamic response for achieving a high accuracy. The current-control loop is known to be always faster than the voltage-control loop. Therefore, the reference current tracking is accomplished by using the current control. The DC voltage stabilisation is achieved by the voltage-control loop. Despite the satisfactory performance of existing control strategies developed for the three-phase six-switch topology, various control strategies are also developed for the three-phase four-switch

topology which are successfully implemented in the control of rectifiers [14-16], inverters [17-20] and shunt APFs [21-27]. An important consequence of using four-switch topology is that the total cost and switching losses are reduced and the reliability of the system is improved [21]. Reducing the number of converter legs from three to two decreases the switching losses by one third which means that the efficiency of four-switch topology is improved by one third compared with the six-switch topology [21].

The existing control strategies proposed for shunt APFs employing four-switch topology yield various advantages and disadvantages. The control strategies presented in [21, 22] are based on proportional-integral (PI) control which requires four gains. The control strategy presented in [23] has two separate parts, one for three-phase sinusoidal waveform generation and the other for the current control which makes use of the conventional two-level hysteresis current-control (HCC) method. The one cycle control approach presented in [24] offers a good performance and does not require generation of the reference waveform. The space vector pulse-width modulation (PWM) algorithm and DC-side voltage-control strategy proposed in [25] is complicated by the fact that it involves transformations from abc frame to rotating dqframe and vice versa. Moreover, two PI controllers with a total number of four gains are needed for a successful operation. The variable parameter PWM-based current tracking approach presented in [26] improves the utilisation of DC voltage and widens the voltage range of the four-switch topology. In addition, the proposed strategy exhibits better performance in transient response and tracking accuracy compared with the triangle-based PWM. Though the advanced current-control strategy proposed in [27] offers a good steady-state and dynamic response, it does not consider the imbalance problem of the capacitor voltages.

In this paper, a three-level HCC strategy involving an imbalance compensation loop for three-phase four-switch shunt APFs is proposed. An important consequence of using this control strategy is that it enables access to the zero level of the active filter's input voltage so that a switching device is only switched when the current error is negative, while it remains off when the current error is positive. The three-level HCC strategy not only maintains the advantages of conventional two-level HCC (higher accuracy, fast dynamic response, robustness and easy implementation), but also offers additional advantages such as reduced switching frequency and switching losses. Furthermore, the imbalance problem existing in the capacitor voltages is eliminated. The performance of the three-level HCC strategy under non-linear load currents is investigated by computer simulations and experimental study under real time-laboratory (RT-LAB) developed by OPAL-RT.

### 2 Three-phase four-switch shunt APF modelling

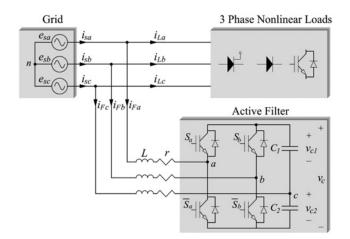

A three-phase four-switch shunt APF configuration is shown in Fig. 1. It can be seen from Fig. 1 that the APF is connected to PCC which makes it shunt with the non-linear load and mains supply. A VSI which contains four switching devices is utilised in the APF. The phase C is connected to the mid-point of the split DC-link capacitors. This implies that the phase C current is forced to flow through the DC-link capacitors which cause a fluctuation in the capacitor voltages. The main goal of the APF is to consume three-phase currents ( $i_{Fa}$ ,  $i_{Fb}$  and  $i_{Fc}$ ) from the mains supply so as to obtain undistorted source currents ( $i_{sa}$ ,  $i_{sb}$  and  $i_{sc}$ ) at unity power factor which are deteriorated by the non-linear load currents ( $i_{La}$ ,  $i_{Lb}$  and  $i_{Lc}$ ). It is required that the source currents are sinusoidal and in phase with the source voltages. Operation of the three-phase four-switch shunt APF can be described by the following equations

$$L\frac{\mathrm{d}i_{Fa}}{\mathrm{d}t} + ri_{Fa} = e_{\mathrm{s}a} - v_{\mathrm{a}\mathrm{n}} \tag{1}$$

$$L\frac{di_{Fb}}{dt} + ri_{Fb} = e_{sb} - v_{bn}$$

<sup>(2)</sup>

$$L\frac{\mathrm{d}i_{F_c}}{\mathrm{d}t} + ri_{F_c} = e_{\mathrm{sc}} - v_{\mathrm{cn}} \tag{3}$$

$$C_1 \frac{dv_{c1}}{dt} = \frac{1}{2} (p_a i_{Fa} + p_b i_{Fb} - i_{Fc})$$

(4)

$$C_2 \frac{\mathrm{d}v_{c2}}{\mathrm{d}t} = \frac{1}{2} (p_a i_{Fa} + p_b i_{Fb} + i_{Fc})$$

(5)

where *r* is the inductor resistance. The phase-to-neutral voltages of phase A, phase B and Phase C ( $v_{an}$ ,  $v_{bn}$  and  $v_{cn}$ ) in terms of the

Fig. 1 Three-phase four-switch shunt APF

capacitor voltages and switching functions are given by [14, 16]

$$v_{an} = \frac{1}{6} \left( 2p_a - p_b + 1 \right) v_{c1} + \frac{1}{6} \left( 2p_a - p_b - 1 \right) v_{c2} \tag{6}$$

$$b_{bn} = \frac{1}{6} \left( 2p_b - p_a + 1 \right) v_{c1} + \frac{1}{6} \left( 2p_b - p_a - 1 \right) v_{c2} \tag{7}$$

$$v_{cn} = \frac{1}{6} \left( -p_a - p_b - 2 \right) v_{c1} + \frac{1}{6} \left( p_a - p_b + 2 \right) v_{c2} \tag{8}$$

The three-phase source voltages are assumed to be balanced as

$$e_{\rm sa} = E_m \cos\left(\omega t\right) \tag{9}$$

$$e_{\rm sb} = E_m \, \cos\!\left(\omega t - \frac{2\pi}{3}\right) \tag{10}$$

$$e_{\rm sc} = E_m \, \cos\!\left(\omega t - \frac{4\pi}{3}\right) \tag{11}$$

The four switching devices are controlled with the bipolar switching functions defined by

$$p_k = \begin{cases} 1 & S_k \text{ closed} \\ -1 & \overline{S}_k \text{ closed}, k = a, b \end{cases}$$

(12)

Also, it is assumed that the series connected capacitors are identical  $(C_1 = C_2)$ . However, in practice, the values of these capacitors may not be equal which cause imbalance between  $v_{c1}$  and  $v_{c2}$ .

#### 3 Control strategy

v

It should be noted that regardless of the topology, the control strategy of a three-phase shunt APF has two objectives. The first objective is to have sinusoidal source currents in phase with the source voltages. The second objective is the stabilisation of the DC output voltage ( $v_c$ ) at a required value. These objectives can be achieved by utilising an inner loop for shaping the source currents and an outer loop for regulating the DC output voltage.

#### 3.1 Two-level HCC

The sinusoidal source currents in phase with the source voltages (the first objective mentioned above) can be accomplished by forcing phases A and B source currents to follow their references defined as

$$i_{sa}^* = I_m(t)\cos\left(\omega t\right) \tag{13}$$

$$i_{sb}^* = I_m(t)\cos\left(\omega t - \frac{2\pi}{3}\right) \tag{14}$$

where  $I_m(t)$  represents the amplitude of three-phase source currents. Having generated  $i_{sa}^*$  and  $i_{sb}^*$ , the active filter current references for phases A and B can be generated by subtracting the measured load current from the reference source current as follows

$$i_{Fa}^* = i_{sa}^* - i_{La} \tag{15}$$

$$i_{Fb}^* = i_{sb}^* - i_{Lb} \tag{16}$$

Here, it is important to note that the control of phase C current is achieved automatically by controlling the currents of phases A and B. In the conventional two-level HCC strategy, the current (in the case of APF, it is filter current) which is supposed to be controlled is maintained inside the hysteresis band in the vicinity of its reference by turning corresponding switching device on and off. The gate signals of the switching devices  $(g_1, g_2, g_3 \text{ and } g_4)$  are generated from the current error obtained for each phase as follows

$$i_{ek} = i_{Fk}^* - i_{Fk} \tag{17}$$

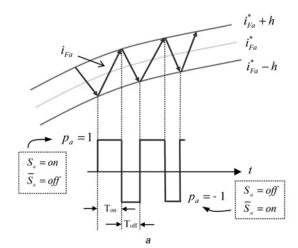

Fig. 2*a* shows the switching in the two-level HCC strategy for phase A. It is obvious that this control strategy has two levels only. The on and off periods of the switching devices  $S_a$  and  $\bar{S}_a$  during the evolution of the active filter current  $i_{Fa}$  are also depicted in Fig. 2*a*. It is worth noting that the DC output voltage should be large enough for effective current tracking. The switching of  $S_a$  and  $\bar{S}_a$  during to the following switching logic

$$S_a = \begin{cases} \text{off} & \text{when } i_{Fa} > i_{Fa}^* + h \\ \text{on} & \text{when } i_{Fa} < i_{Fa}^* - h \end{cases}$$

(18)

$$\bar{S}_a = \begin{cases} \text{on when } i_{Fa} > i_{Fa}^* + h \\ \text{off when } i_{Fa} < i_{Fa}^* - h \end{cases}$$

(19)

The switching for phase B is done similarly, using the corresponding reference and measured current.

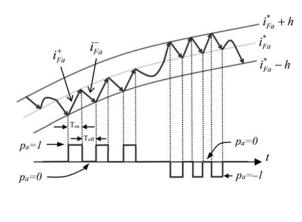

#### 3.2 Three-level HCC

It can be seen from Fig. 2*a* that the current error in the two-level HCC strategy has two levels which means that the switching devices connected to one leg (phase A or B) of the VSI are turned on and off continuously in one cycle. Such operation leads to high switching frequency, and therefore increases the overall switching losses. The three-level HCC strategy proposed here aims at reducing the switching losses. Fig. 2*b* shows the three-level HCC for phase A when the current error is positive. It can be seen that  $S_a$  is turned on and off ( $p_a=1$  and  $p_a=0$ ) when the current error is positive. In this case,  $\bar{S}_a$  is continuously off. When the current error becomes negative,  $\bar{S}_a$  is continuously off. From Fig. 2*b*, the following equations can be written for  $T_{\text{on}}$  and  $T_{\text{off}}$  (for sake of simplicity *r* is neglected)

$$\frac{\mathrm{d}i_{Fa}^{+}}{\mathrm{d}t}T_{\mathrm{on}} - \frac{\mathrm{d}i_{Fa}^{*}}{\mathrm{d}t}T_{\mathrm{on}} = h \tag{20}$$

$$\frac{\mathrm{d}\bar{i}_{Fa}}{\mathrm{d}t}T_{\mathrm{off}} - \frac{\mathrm{d}\bar{i}_{Fa}^*}{\mathrm{d}t}T_{\mathrm{off}} = -h \tag{21}$$

**Fig. 2** HCC for phase A a Two-level b Three-level

Adding (20) and (21) yields

$$\frac{\mathrm{d}i_{Fa}^+}{\mathrm{d}t}T_{\mathrm{on}} + \frac{\mathrm{d}i_{Fa}^-}{\mathrm{d}t}T_{\mathrm{off}} - \frac{1}{f_{\mathrm{sw}}}\frac{\mathrm{d}i_{Fa}^*}{\mathrm{d}t} = 0$$

(22)

where  $f_{sw} = 1/(T_{on} + T_{off})$  is the switching frequency. Subtracting (21) from (20) gives

$$\frac{di_{Fa}^{+}}{dt}T_{\rm on} - \frac{di_{Fa}^{-}}{dt}T_{\rm off} - (T_{\rm on} - T_{\rm off})\frac{di_{Fa}^{*}}{dt} = 2h$$

(23)

Since  $(di_{Fa}^+/dt) = -(di_{Fa}^-/dt)$ , then (22) and (23) can be simplified as

$$T_{\rm on} - T_{\rm off} = \frac{\mathrm{d} i_{Fa}^*/\mathrm{d} t}{f_{\rm sw} \left(\mathrm{d} i_{Fa}^+/\mathrm{d} t\right)} \tag{24}$$

$$\frac{1}{f_{\rm sw}}\frac{{\rm d}i_{Fa}^+}{{\rm d}t} - \left(T_{\rm on} - T_{\rm off}\right)\frac{{\rm d}i_{Fa}^*}{{\rm d}t} = 2h \tag{25}$$

Substituting (24) into (25) and  $(di_{Fa}^+/dt) = (1/L)(e_{sa} - v'_{an})$  into the resulting equation yields

$$f_{\rm sw} = \frac{(e_{\rm sa} - v'_{\rm an})}{2Lh} \left[ 1 - \frac{m^2 L^2}{(e_{\rm sa} - v'_{\rm an})^2} \right]$$

(26)

where  $m = (dt_{Fa}^*/dt)$  and  $v_{an}' = (1/6)[(3 - p_b)v_{c1} + (1 - p_b)v_{c2}]$  is the phase-to-neutral voltage of the active filter when  $S_a$  is turned on  $(p_a = 1)$ . It is clear from (26) that the switching frequency  $(f_{sw})$  is time-varying and is a function of the hysteresis band (h) and inductor L. It is well known that the value of L determines the amount of ripple in the current. Hence, the filter inductor L is to be chosen to make a compromise between targeted switching frequency and current ripple. On the other hand, since the value of h determines  $f_{sw}$ , it should be selected so as to achieve a reasonable total harmonic distortion (THD) of source currents under targeted  $f_{sw}$ .

#### 3.3 Output voltage control

The second objective was the stabilisation of the DC output voltage at a required value. To accomplish this, it is needed to regulate the amplitude of three-phase source currents to a desired reference.

Table 1 Parameters of the system

| Symbol                                            | Value       |  |  |  |

|---------------------------------------------------|-------------|--|--|--|

| $E_m$ – line to neutral voltage amplitude         | 50 V        |  |  |  |

| f – supply frequency                              | 50 Hz       |  |  |  |

| $C_1, C_2$ – DC capacitors                        | 750 µF      |  |  |  |

| L – inductor                                      | 4 mH        |  |  |  |

| r – inductor resistance                           | 1Ω          |  |  |  |

| V <sub>c</sub> – reference voltage                | 250 V       |  |  |  |

| h – hysteresis band                               | 0.1 A       |  |  |  |

| $k_{\rm p}$ – proportional gain                   | 0.12        |  |  |  |

| k <sub>i</sub> – integral gain                    | 1.0         |  |  |  |

| $k_e$ – imbalance compensation gain               | -0.05       |  |  |  |

| $T_{\rm s}$ – sampling time                       | 25 µs       |  |  |  |

| load <sub>1</sub> – non-linear load res. and ind. | 20 Ω, 80 mH |  |  |  |

| $load_2 - non-linear load res. and ind.$          | 40 Ω, 40 mH |  |  |  |

When the source current regulation is achieved successfully, the output voltage reaches to its reference ( $V_c$ ) indirectly. The value of source current amplitude reference is determined by a PI controller which operates as an outer voltage loop [10, 11]

$$I_m(t) = k_{\rm p}(V_{\rm c} - v_{\rm c}) + k_{\rm i} \int (V_{\rm c} - v_{\rm c}) {\rm d}t$$

(27)

where  $k_p$  and  $k_i$  denote the PI gains, respectively.

#### 3.4 Compensation of imbalance in capacitor voltages

It is mentioned in [14, 16] that there exists an imbalance in the capacitor voltages ( $v_{c1}$  and  $v_{c2}$ ). One of the reasons of this imbalance comes from a DC offset caused by the system's initial condition. The other reason is the non-equal capacitance values ( $C_1 \neq C_2$ ) in practice. Inspired from the method presented in [28], this imbalance in capacitor voltages can be eliminated by feeding back the imbalance variable ( $v_{ce} = v_{c1} - v_{c2}$ ), multiplying it by a gain ( $k_e$ ) and adding the multiplication result to  $i_{Fa}^*$  and  $i_{Fb}^*$  as follows

$$i_{Fa,e}^* = i_{Fa}^* + k_e v_{ce}$$

(28)

$$i_{Fb,e}^* = i_{Fb}^* + k_e v_{ce}$$

(29)

where  $k_e < 0$ . In this case, the active filter currents  $(i_{Fa} \text{ and } i_{Fb})$  track the modified references  $(i^*_{Fa,e} \text{ and } i^*_{Fb,e})$  instead of  $i^*_{Fa}$  and  $i^*_{Fb}$ . The capacitor voltage difference  $(v_{ce} = v_{c1} - v_{c2})$  utilised in (28) and (29) converges to zero through imbalance compensation loop action. Let us validate this mathematically. The capacitor currents and their sum are given by

$$i_{dc1} = -p_a i_{Fa} - p_b i_{Fb}$$

$$i_{dc2} = -(1 - p_a) i_{Fa} - (1 - p_b) i_{Fb}$$

$$i_{dc1} + i_{dc2} = -(i_{Fa} + i_{Fb}) = i_{Fc}$$

(30)

In the derivation of  $i_{dc1} + i_{dc2}$ , it is assumed that  $C_1 = C_2$ . The capacitor currents in terms of switching functions and filter

Fig. 3 Non-linear load current waveforms

**Fig. 4** *DC-link capacitor voltage waveforms a* Without imbalance compensation loop *b* With imbalance compensation loop

currents are

$$i_{dc1} = -p_a i_{Fa} - p_b i_{Fb}, i_{dc2}$$

= -(1 - p\_a)i\_{Fa} - (1 - p\_b)i\_{Fb}, i\_{dc1} + i\_{dc2} = -(i\_{Fa} + i\_{Fb})

=  $i_{Fc}$  (31)

Equating (30) and (31) gives

$$\frac{\mathrm{d}v_{\mathrm{ce}}}{\mathrm{d}t} = -\frac{1}{C_1}i_{F_c} \tag{32}$$

Now, adding (28) and (29) gives

$$i_{Fa,e}^* + i_{Fb,e}^* = i_{Fa}^* + i_{Fa}^* + 2k_e v_{ce}$$

(33)

Assuming that the filter currents track their references and substituting (33) into (32) with the fact that  $i_{Fa,e}^* + i_{Fb,e}^* = -i_{Fc,e}^*$ , we obtain

$$\frac{dv_{ce}}{dt} = -\frac{1}{C_1} \left( i_{Fc} - 2k_{ce}v_{ce} \right)$$

(34)

Taking Laplace transform of (34) yields

$$V_{\rm ce}(s) = \frac{1}{C_1(s - 2k_{\rm ce})} I_{Fc}(s) + \frac{1}{(s - 2k_{\rm ce})} v_{\rm ce}(0)$$

(35)

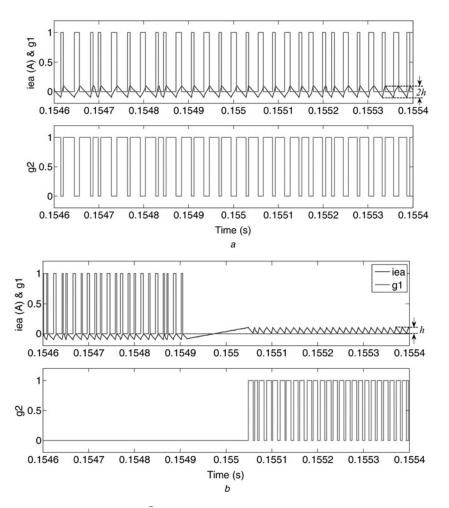

**Fig. 5** *Current error of phase A and gate signals of*  $S_a$  *and*  $\bar{S}_a$  *for a* Two-level HCC *b* Three-level HCC

The solution of (35) in time domain can easily be obtained as

$$v_{\rm ce}(t) = \frac{1}{C_1} i_{F_c}(t) e^{2k_{\rm ce}t} + v_{\rm ce}(0) e^{2k_{\rm ce}t}$$

(36)

Clearly,  $v_{ce}(t)$  decays to zero for all t since  $k_{ce} < 0$ .

#### 4 Computer simulation results

In this section, the effect of imbalance compensation loop on the capacitor voltages is first presented. Then, the simulation results of the three-level HCC and the two-level HCC are discussed. Moreover, the THDs of the three-phase source currents obtained by the proposed control strategy are compared with the results obtained from state-of-the-art using MATLAB/Simulink. The simulation studies have been carried out by using the parameters as shown in Table 1.

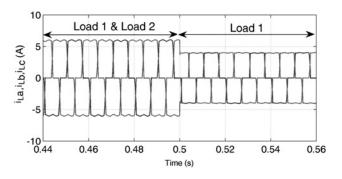

The non-linear load group is modelled such that it draws non-sinusoidal currents from the three-phase supply as shown in Fig. 3.

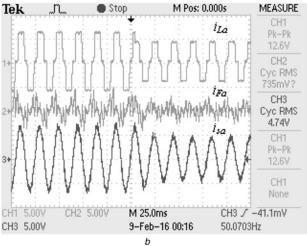

Fig. 4 shows the start-up and dynamic responses of capacitor voltages ( $v_{c1}$  and  $v_{c2}$ ) and DC-link voltage ( $v_c$ ) when load<sub>2</sub> is disconnected from PCC at t=0.5 s. Initially, the system starts with both load<sub>1</sub> and load<sub>2</sub> which are connected in parallel. It is clear from Fig. 4*a* that the capacitor voltages are not equal to each other ( $v_{c1} \neq v_{c2}$ ) when the imbalance compensation loop is not utilised. When the imbalance in the capacitor voltages is eliminated as shown in Fig. 4*b*. This result clearly shows that the imbalance compensation

loop acts correctly to eliminate the imbalance in the capacitor voltages. Also, the oscillations seen on the total capacitor voltage ( $v_c$ ) obtained without imbalance compensation loop are not visible on  $v_c$  when obtained with imbalance compensation loop.

Fig. 5 shows the current error of phase A ( $i_{ea}$ ) and gate signals ( $g_1$  and  $g_2$ ) of  $S_a$  and  $\bar{S}_a$  obtained by two- and three-level HCCs, respectively. It is clear from Fig. 5*a* that the current error remains between the defined upper and lower hysteresis bands by making a zigzag movement between h = +0.1 A and -0.1 A without having a zero level. Having a zigzag motion of  $i_{ea}$  between two levels forces the switching devices ( $S_a$  and  $\bar{S}_a$ ) to be turned on and off continuously. Eventually, this would increase the switching frequency and losses.

In the case of three-level HCC as shown in Fig. 5b, the current error makes a zigzag motion between three levels. When the current error is negative, it changes between h = -0.1 A and 0. On the other hand, when the current error is positive, it changes between h = +0.1 A and 0. With such switching scheme,  $S_a$  is turned on and off when the current error is negative, while  $\bar{S}_a$  is always off and vice versa. Comparing Figs. 5a and b, the number of pulses for three-level HCC is seen to be smaller than that of two-level HCC for the same time interval from t = 0.1546 to 0.1554 s. This means that the three-level HCC leads to smaller switching frequency than two-level HCC.

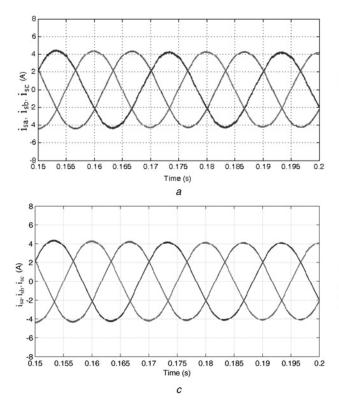

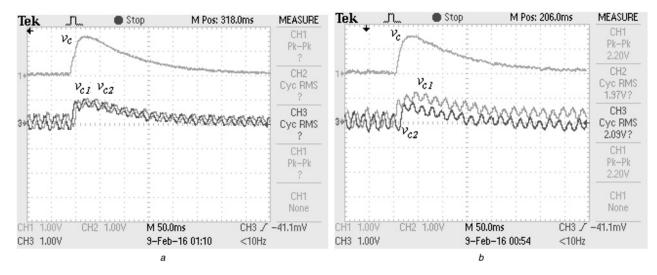

Fig. 6 shows the steady-state waveforms of three-phase source currents obtained by three- and two-level HCCs using four- and six-switch APF topologies. Figs. 6a and b show the source current waveforms obtained by the three- and two-level HCCs using four-switch topology, respectively. The THDs of phase A current are computed as 1.81 and 1.54%. Though the three-level HCC leads to a higher THD than that of three two-level HCC, it is still

**Fig. 6** *Three-phase source current waveforms obtained by*

a Three-level HCC-based three-phase four-switch APF

*b* Two-level HCC-based three-phase four-switch APF *c* Three-level HCC-based three-phase six-switch APF

*d* Two-level HCC-based three-phase six-switch APF

below the IEEE-519 standard. The main contribution of three-level HCC is that it offers smaller switching frequency compared with the two-level HCC. Figs. 6c and d show the source current waveforms obtained by the three- and two-level HCCs using six-switch topology, respectively.

The THDs of three-phase source currents obtained by the proposed control strategy are compared with the THDs of source currents obtained by the four-switch two-level HCC and traditional six-switch APF topology under two- and three-level HCCs. The THDs of phase A current are computed as 1.81 and 1.54% which are equal to the THD values computed for the four-switch case. The THD values regarding the other phases obtained by three- and two-level HCCs under four- and six-switch APF topologies are reported in Table 2. As a consequence of using three-level HCC, the source current distortions are only affected by 0.27% in phase A, 0.06% in phase B and 0.07% in phase C which are still below the IEEE-519 standard.

## 5 Real-time control in software-in-the-loop results

The performance of the proposed control strategy under four-switch topology was investigated in a real-time environment. RT-LAB allows

for the distributed simulation of complex power systems. Specifically, the proposed system is realised on a field programmable gate array architecture using the Xilinx system generator toolbox.

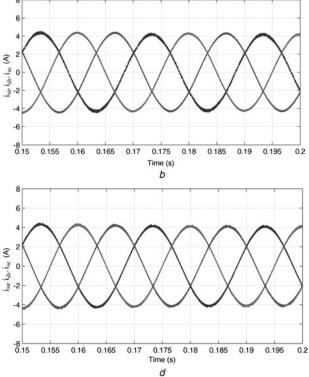

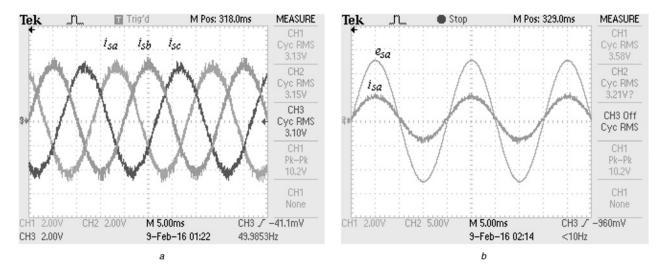

Fig. 7 shows the steady-state waveforms of load current, active filter current, source current and spectrums of load and source currents for phase A obtained by the proposed control strategy. Despite the highly distorted load current, the proposed control strategy works correctly by injecting the required active filter current to PCC so as to produce a sinusoidal source current as shown in Fig. 7a.

The spectrums of the load and source currents are depicted in Figs. 7b and c, respectively. It is clear from Fig. 7b that the load current contains odd harmonics (3rd, 5th, 7th and 9th) which are successfully eliminated by the proposed control strategy so that they do not appear in the source current as shown in Fig. 7c.

Fig. 8 depicts the steady-state waveforms of three-phase source currents and source voltage together with source current for phase A. It is obvious from Fig. 8*a* that the proposed control strategy with four-switch topology is able to control  $i_{sa}$  and  $i_{sb}$ . When the control of phases A and B currents are achieved, the control of phase C current is done automatically. Also, it can be easily noted from Fig. 8*b* that the unity power factor requirement is achieved successfully.

Table 2 Comparisons of four- and six-switch APFs under three- and two-level HCCs

| Topolog <i>y</i>        | Three-phase four-switch APF                               |               |               |                                           |               |               | Three-phase six-switch APF                  |               |               |                                           |               |               |

|-------------------------|-----------------------------------------------------------|---------------|---------------|-------------------------------------------|---------------|---------------|---------------------------------------------|---------------|---------------|-------------------------------------------|---------------|---------------|

| Current control methods | Three-level HCC, proposed method THD of phase currents, % |               |               | Two-level HCC<br>THD of phase currents, % |               |               | Three-level HCC<br>THD of phase currents, % |               |               | Two-level HCC<br>THD of phase currents, % |               |               |

|                         |                                                           |               |               |                                           |               |               |                                             |               |               |                                           |               |               |

|                         | load currents<br>source currents                          | 26.33<br>1.81 | 25.88<br>1.51 | 25.92<br>2.03                             | 26.33<br>1.54 | 25.88<br>1.45 | 25.92<br>1.96                               | 26.33<br>1.83 | 25.88<br>1.67 | 25.92<br>1.75                             | 26.33<br>1.73 | 25.88<br>1.51 |

Fig. 7 Steady-state waveforms of load current, active filter current, source current and spectrums of load and source currents for phase A

a Steady-state waveforms (scale: 5 A/div)

b Load current spectrum

c Source current spectrum

Fig. 8 Steady-state waveforms of three-phase source currents and source voltage for phase A

a Three-phase source currents

b Source voltage and current for phase A (scale: 2 A/div, 20 V/div)

**Fig. 9** Dynamic response of currents for a step change in load a From load<sub>1</sub> to load<sub>1</sub> and load<sub>2</sub> b From load<sub>1</sub> and load<sub>2</sub> to load<sub>1</sub> (scale: 5 A/div)

**Fig. 10** Dynamic responses of  $v_c$ ,  $v_{c1}$  and  $v_{c2}$  when the load<sub>2</sub> is disconnected from PCC *a* With imbalance compensation loop *b* Without imbalance compensation loop

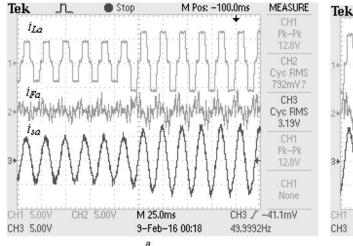

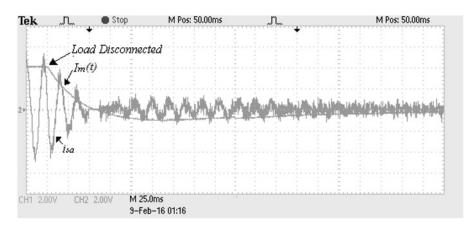

Figs. 9*a* and *b* show the dynamic performance of the proposed control strategy under step changes in the load. Fig. 9*a* shows the response of  $i_{La}$ ,  $i_{Fa}$  and  $i_{sa}$  when load<sub>2</sub> (40  $\Omega$ , 40 mH) is connected in parallel with load<sub>1</sub> (20  $\Omega$ , 80 mH) at PCC and Fig. 9*b* shows the

response of  $i_{La}$ ,  $i_{Fa}$  and  $i_{sa}$  when load<sub>2</sub> is disconnected from load<sub>1</sub>. It can be seen that the dynamic response is reasonably fast in both cases. Fig. 10 shows the dynamic responses of capacitor voltages obtained with and without the imbalance compensation loop when

**Fig. 11** Dynamic responses of  $i_{sa}$  and  $I_m(t)$  when the load  $_1$  is disconnected from PCC

$load_2$  (40  $\Omega$ , 40 mH) is disconnected from PCC. Initially, both  $load_1$ and  $load_2$  are connected in parallel at PCC. It is clear from Fig. 10athat both capacitor voltages are equal to each other which clearly show that the imbalance compensation loop acts correctly to eliminate the imbalance in the capacitor voltages. However, when the imbalance compensation loop is removed, there exists an imbalance in the capacitor voltages as shown in Fig. 10b. In both cases, the DC output voltage is stabilised successfully by the PI regulator existing in the voltage-control loop.

Fig. 11 shows the dynamic responses of source current of phase A and the time-varying reference amplitude  $[I_m(t)]$  produced by the PI regulator for a step change in load from (20  $\Omega$ , 80 mH) to no load  $(load_1 is disconnected from PCC)$ . It is obvious from Fig. 11 that the actual amplitude of the source current tracks its reference amplitude before and after the load<sub>1</sub> is disconnected from PCC. It should be noted that, before the load is disconnected,  $I_m(t)$  is non-zero which means that the load should draw a non-zero current from AC supply. After the load is disconnected from PCC,  $I_m(t)$  converges to zero meaning that the load does not draw a current from the AC supply.

#### 6 Conclusions

In this paper, a three-level HCC strategy employing an imbalance compensation loop is proposed for three-phase four-switch APFs. It is pointed out that regardless of the control strategy the four-switch topology offers a reduced cost than what would be achieved in the widely used six-switch topology. The four-switch APF is controlled by using three-level HCC strategy. An important consequence of using HCC strategy is that it enables access to the zero level of the input voltage of the active filter so that a switching device is only switched when the current error is negative, while it remains off when the current error is positive. The three-level HCC strategy not only maintains the advantages of conventional two-level HCC such as higher accuracy, fast dynamic response, robustness and simplicity in the implementation, but also offers additional advantages such as reduced switching frequency and switching losses. Furthermore, the additional feedback term, which involves the difference in the capacitor voltages multiplied by a suitable gain, is added into current control to eliminate the imbalance in the capacitor voltages. Simulation and experimental results are presented to demonstrate the steady-state and dynamic performance of the proposed control strategy.

#### 7 References

- 1 Singh, B., Al-Haddad, K., Chandra, A.: 'A review of active filters for power quality improvement', *IEEE Trans. Ind. Electron.*, 1999, **46**, (5), pp. 960–971 El-Habrouk, M., Darwish, M.K., Mehta, P.: 'Active power filters – a review', *IEE*

- 2 *Electr. Power Appl.*, 2000, **147**, (5), pp. 403–413 Akagi, H.: 'Active harmonic filters', *Proc. IEEE*, 2005, **93**, (12), pp. 2128–2141

- Akagi, H., Kanazawa, Y., Nabae, A.: 'Instantaneous reactive power compensators comprising switching devices without energy storage components', IEEE Trans. Ind. Appl. IA, 1984, 20, (3), pp. 625-630

- Akagi, H.: 'Trends in active power line conditioners', IEEE Trans. Power Electron., 1994, 9, (3), pp. 263-268

- Verdelho, P., Marques, G.D.: 'An active power filter and unbalanced current compensator', IEEE Trans. Ind. Electron., 1997, 44, (3), pp. 321-328

- 7 Jeong, G.Y., Park, T.J., Kwon, B.H.: 'Line-voltage-sensorless active power filter for reactive power compensation', IEE Electr. Power Appl., 2000, 147, (5), pp. 385-390 Moran, L.A., Dixon, J.W., Wallace, R.R.: 'A three-phase active power filter

- operating with fixed switching frequency for reactive power and current harmonic compensation', *IEEE Trans. Ind. Electron.*, 1995, **42**, (4), pp. 402–408

- Saetieo, S., Devaraj, R., Torrey, D.A.: 'The design and implementation of a three-phase active power filter based on sliding mode control', IEEE Trans. Ind. *Appl.*, 1995, **31**, (5), pp. 993–1000

- Komurcugil, H., Kukrer, O.: 'Globally stable control of three-phase three-wire shunt active power filters', Electr. Eng., 2007, 89, (5), pp. 411-418

- Kukrer, O., Komurcusi, H.: 'A new control strategy for three-phase three wire shunt active power filters'. Proc. IEEE Industrial Symp. on Industrial 11 Electronics, Cambridge, UK, 2008, pp. 896-901

- Chauhan, S.K., Shah, M.C., Tiwari, R.R., et al.: 'Analysis, design and implementation of a shunt active power filter with different schemes of reference current generation', IET Power Electron., 2014, 7, (3), pp. 627-639

- 13 Chauhan, S.K., Tekwani, P.N.: 'Current error space phasor based hysteresis controller for two-level and three-level converters used in shunt active power filters'. Proc. IEEE Annual Conf. of Industrial Electronics Society, Vienna, Austria, 2013, pp. 8522-8527

- 14 Shieh, J.J., Pan, C.T., Cuey, Z.J.: 'Modelling and design of a reversible three-phase switching mode rectifier', IEE Electr. Power Appl., 1997, 144, (6), pp. 389–396

- Klima, J., Skramlik, J., Valouch, V.: 'An analytical modelling of three-phase four-switch PWM rectifier under unbalanced supply conditions', IEEE Trans. Circuit. Syst. II, 2007, 54, (12), pp. 1155-1159

- 16 Lee, T.S., Liu, J.H.: 'Modeling and control of a three-phase four-switch PWM Lee, i.e., i.e., i.e., so that indexing balance control of a three phase role of the Print voltage-source rectifier in d-q synchronous frame', *IEEE Trans. Power Electron.*, 2011, **26**, (9), pp. 2476–2489 Wang, R., Zhao, J., Liu, Y.: 'A comprehensive investigation of four-switch three-phase voltage source inverter based on double Fourier integral analysis',

- 17 IEEE Trans. Power Electron., 2011, 26, (10), pp. 2774-2787

- 18 Dasgupta, S., Mohan, S.N., Sahoo, S.K., et al.: 'Application of four-switch-based three-phase grid-connected inverter to connect renewable energy source to a generalized unbalanced microgrid system', IEEE Trans. Ind. Electron., 2013, 60, (3), pp. 1204–1215

- Xia, C., Xiao, Y., Chen, W., et al.: 'Three effective vectors-based current control 19 scheme for four-switch three-phase trapezoidal brushless DC motor', IET Electr. Power Appl., 2013, 7, (7), pp. 566-574

- 20 Diab, M.S., Elserougi, A., Massoud, A.M., et al.: 'A four-switch three-phase SEPIC-based inverter', IEEE Trans. Power Electron., 2015, 30, (9), pp. 4891-4905

- Haddad, K., Joos, G.: 'Three phase active filter topology based on a reduced switch count voltage source inverter'. Proc. IEEE Power Electronics Specialists Conf., Charleston, SC, USA, 1999, pp. 236-241

- 22 Hoseinpour, A.: 'Three phase active filter with four switching inverter and variable index modulation'. Proc. Power Quality Conf., 2010, pp. 1-7

- Joos, G., Chen, S., Haddad, K.: 'Four switch three phase active filter with reduced 23 current sensors'. Proc. IEEE Power Electronics Specialists Conf., Galway, Ireland, 2000, pp. 1318-1323

- 24 Bala, S., Patel, N., Fernandes, B.G.: 'Reduced-switch three-phase active power filter with one cycle control'. Proc. IEEE Power Electronics Specialists Conf., Aachen, Germany, 2004, pp. 2333-2339

- Wang, W., Luo, A., Xu, X., et al.: 'Space vector pulse-width modulation algorithm 25 and DC-side voltage control strategy of three-phase four-switch active power filters', *IET Power Electron.*, 2013, **6**, (1), pp. 125–135 Tan, X., Li, Q., Wang, H., *et al.*: 'Variable parameter pulse width modulation-based

- 26 current tracking technology applied to four-switch three-phase shunt active power filter', IET Power Electron., 2013, 6, (3), pp. 543-553

- Trinh, Q.N., Lee, H.H.: 'An advanced current control strategy for three-phase shunt active power filters', IEEE Trans. Ind. Electron., 2013, 60, (12), pp. 5400-5410

- 28 Srinivasan, R., Oruganti, R.: 'A unity power factor converter using half-bridge boost topology', IEEE Trans. Power Electron., 1998, 13, (3), pp. 487-500