# Compensation of Non-Linearities in Diode-Clamped Multilevel Converters

Stephen R. Minshull, Christopher M. Bingham, Member, IEEE, David A. Stone, and Martin. P. Foster

Abstract—The application of multilevel converters for exciting permanent magnet machines with low-phase inductance to DC-link voltage ratios facilitates a reduction in high frequency switching harmonics. However, converter non-linearities and, inparticular, on-state device voltage drops, create additional low-frequency harmonics. This paper therefore proposes a generic compensation scheme to accommodate the effects of such converter non-linearities and, in so doing, improve the harmonic quality of the machine phase currents. Experimental results gathered from a prototype 5-level diode clamped converter validate the benefits of the proposed scheme by showing quantitative reductions in low frequency harmonics.

Index Terms—Dead-time compensation, multilevel converter, permanent magnet synchronous motor, space vector modulation.

#### I. INTRODUCTION

MULTILEVEL inverters are an attractive choice for driving high-efficiency brushless permanent-magnet machines (with either sinusoidal or trapezoidal back-emf) that exhibit low phase inductance due to their high fundamental electrical frequency or those that require the series connection of power devices to provide adequate breakdown characteristics. Such inverters allow a reduction in the current ripple on the machine phase currents without an increase in the inverter switching frequency. Reduced current ripple also has associated benefits for torque ripple, eddy current machine losses and electromagnetic interference (EMI) [1, 2].

However, multilevel inverters, like their classical 2-level counterparts, are subject to the non-linear characteristics of their constituent switching devices. Finite switching times dictate that a blanking-time be inserted between one device being turned off in a phase leg and the complementary device being turned on to prevent a short-circuit, or "shoot-through" condition, forming across the inverter voltage source. However, the blanking-time introduces a voltage error at the converter phase terminals that is dependent on the phase current polarity. The effects and compensation of this

Manuscript received February 5, 2009. Accepted for publication May 1, 2009

Copyright © 2009 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org

The authors are with the Department of Electrical and Electronic Engineering, University of Sheffield, Sheffield, S1 3JD, U.K. (e-mail: c.bingham@sheffield.ac.uk).

blanking-time have been well documented for 2-level converters [3-7] and also considered for a 3-level Neutral Point Clamped (NPC) converter [8]. These methods can be divided into schemes that achieve compensation by modifying the commanded converter terminal voltages [4, 5, 8] or pulse-based methods which directly modify the lengths of the gate-drive pulses in the modulator [4, 6, 7].

Other inverter non-linearities such as switching device onstate voltages and device turn on/off times have also been considered in addition to the blanking-time, and their combined impact is often termed "dead-time" effects. For 2level inverters, such dead-time effects have been considered and compensation schemes have been previously reported that adjust the commanded converter terminal voltages accordingly [9-15]. The cycle-by-cycle amount of compensation to be added to the converter terminal voltages depends upon parameters that are often difficult to measure, and typically vary over the operating range of the converter. For this reason, disturbance observers [12, 15], self-commissioning schemes [13] and model reference adaptive systems (MRAS) [14] have also been utilised to increase the accuracy of the dead-time compensation for 2-level converter counterparts, with varying degrees of success.

For multilevel inverters applied to the excitation of machines that exhibit low-phase inductance vs. DC-link voltage ratios, such non-linearities in the converter phase voltages becomes readily apparent as low frequency harmonics in the phase currents. Moreover, the control of multilevel converters has an additional degree of freedom in the choice between redundant switching vectors that produce identical line-line terminal voltages, which is not present in traditional 2-level counterparts. As will be shown, the choice of these redundant vectors affects the dead-time compensation requirement with the compensation value depending on the particular switching vector chosen for a modulation cycle. In addition, the on-state voltage drops are increased due to the series connection of switching devices, when compared to classical 2-level converters.

This paper therefore addresses the compensation of deadtime effects for multilevel converters, complicated by the requirements of redundant vector application, by utilizing a combination of converter terminal voltage modification and pulse-based methods. It is highlighted that the application of redundant vectors, for the multilevel case, makes the use of previously reported adaptive schemes, for 2-level converters, difficult. Nevertheless, this work 'opens the door' for further development in this area.

The presented techniques are implemented on a prototype 5-level, back-to-back connected, Diode-Clamped Converter (DCC). However, it should be noted that the underlying principles presented are generic and more widely applicable to other multilevel topologies with any number of levels.

# II. INVERTER TERMINAL VOLTAGE DETERMINATION

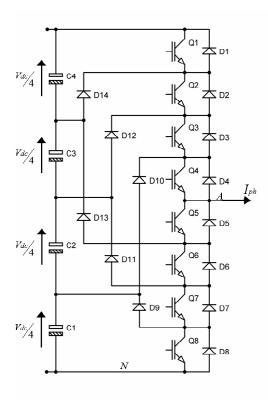

Fig. 1 shows a schematic of a single leg of a DCC connected to the multilevel DC-link that is common to all legs. The IGBT switching devices are shown as Q1-Q8 in Fig.1. D1-D8 are freewheel diodes while D9-D14 are added to clamp the output voltage to one of the multilevel DC-link voltages The high-side switches form formed across C1-C4. complementary pairs with the low-side switches. For example, Q1 switches in anti-phase with Q5, Q2 switches in anti-phase to Q6, and so on. Table 1 shows the desired phase terminal voltages, VAN, the gate drive requirements for Q1-Q8, and the actual phase terminal voltages produced for current flowing from the leg, into the load,  $V_{AN}$ ,  $I_{ph} > 0$ , and current flowing from the load, into the leg,  $V_{AN}$ ,  $I_{ph}$  < 0 . For the gate drive values, "1" indicates the IGBT is turned on and "0" indicates the IGBT is off. It can be seen from Table 1 that an error exists between the commanded phase voltages and those produced at the converter leg and that this error is dependent upon the current polarity. The error is due to the on-state voltage drops across the conducting devices, viz: IGBT (VCEon), the freewheel diodes (Vff) and the clamping diodes (V<sub>fc</sub>). By way of example, referring to Fig.1, a demanded phase voltage of  $V_{dc}/2$  with positive current creates a current path through D12, Q3 and Q4 resulting in the phase terminal voltage being:  $V_{dc}/2 - 2V_{CEon} - V_{fc}$ . A negative current for the same demanded voltage dictates a current path through Q5, Q6 and D11 resulting the phase terminal voltage of:  $V_{dc}/2 + 2V_{CEon} + V_{fc}$ .

$\label{thm:continuous} TABLE\ I$   $\mbox{IDEAL PHASE VOLTAGES, IGBT GATE VALUES AND ACTUL PHASE TERMINAL}$

|             |          | VOLTAGES                       |                      |

|-------------|----------|--------------------------------|----------------------|

| VAN         | Q1-Q8    | VAN, Iph > 0                   | VAN, Iph < 0         |

| 0           | 00001111 | 0-4Vff                         | 0 + 4VCEon           |

| $V_{dc}/4$  | 00011110 | $V_{dc}/4 - V_{CEon} - V_{fc}$ | Vdc/4 + 3VCEon + Vfc |

| $V_{dc}/2$  | 00111100 | Vdc/2 - 2VCEon - Vfc           | Vdc/2 + 2VCEon + Vfc |

| $3V_{dc}/4$ | 01111000 | 3Vdc/4 - 3VCEon - Vfc          | 3Vdc/4 + VCEon + Vfc |

| Vdc         | 11110000 | Vdc - 4VCEon                   | Vdc + 4Vff           |

For a 3-phase system, the actual phase voltages can be transformed into a stationary, orthogonal,  $\alpha\beta$  reference frame using:

$$\begin{bmatrix} \alpha \\ \beta \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(1)

Fig. 1. Single leg of 5-level DCC connected to multilevel DC-link.

A space-vector (SV) diagram for realising space vector modulation (SVM) of the 5-level converter, can then be formed. SVM is employed for the modulation of the back-to-back DCC since it readily lends itself to implementation in regularly sampled digital control systems, and provides a means of balancing the series connected DC-link capacitors with the application of redundant vectors.

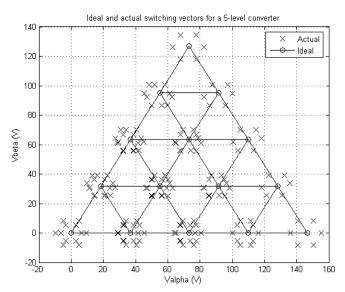

Each switching vector can take 1 of 6 possible values corresponding to the 6 possible 3-phase current polarities. For convenience it is necessary to consider only the first sector of the SV diagram since the remaining 5 sectors can be formed by use of transform tables [16]. The first sector of the 5-level SV diagram is shown in Fig. 2 with the parameters:  $V_{dc} = 220 \text{V}$ ,  $V_{CEON} = 2.0 \text{V}$ ,  $V_{ff} = 1.8 \text{V}$  and  $V_{fc} = 0.8 \text{V}$ .

It can be seen from Fig.2 that there exists an appreciable error between the ideal vector locations and the actual locations when the voltage drops across the conducting devices are included. If ideal vector positions are assumed in the SV modulator, incorrect duty-cycle values will be calculated resulting in a distorted output voltage. The distortion is most noticeable during low speed operation since the on-state voltage error, which is fixed with respect to motor speed, becomes of comparable size to the commanded converter terminal voltages. By assuming ideal vector locations, the actual converter terminal voltage vector inscribes an approximate hexagonal shape in the αβ reference

frame since the direction of the on-state voltage error changes 6 times with every electrical cycle, corresponding to the 6 different current polarities experienced over this period.

Fig. 2. First sector of SV diagram showing ideal and actual vectors.

It is notable that due to the increased number of devices in the current path, for multilevel converters, the distortion caused by the on-state device voltages is typically greater than for classical 2-level counterparts. For example, a demanded phase terminal voltage of  $V_{dc}$  with positive current, results in an actual terminal voltage of a)  $V_{dc}-V_{CEon}$  for a 2-level converter b)  $V_{dc}-4V_{CEon}$  for a 5-level converter.

# III. DC-LINK VOLTAGE BALANCING

The converter terminal voltage is synthesized within each modulation cycle by switching between the 3 nearest vectors to the reference vector, such that the reference and terminal voltage have the same volt-second equivalent value. The reference vector rotates about the centre of the SV diagram in synchronism with the machine rotor.

A control requirement on the DCC is that the voltages across the series connected DC-link capacitors are balanced and is achieved by switching between redundant vectors that produce the same line-line terminal voltages [17-19]. From Fig. 2 it can be seen that the first sector of the SV diagram for the 5-level case is composed of 16 triangular regions. The ideal switching vectors are sited at the corners of each triangular region. A capacitor balancing scheme is realised by choosing a series of 3 switching vectors that, within each modulation period, minimises:

$$E_b = \frac{1}{2}C\sum_{j=1}^{n}\Delta V_{cj}^2 \text{ where } \sum_{j=1}^{n} v_{cj} = V_{DC}, \ v_{cj} > 0$$

(2)

where [17]:

$$\Delta V_{cj} = V_{cj} - \frac{V_{DC}}{n-1} \tag{3}$$

For (2) and (3),  $V_{cj}$ ,  $V_{DC}$ , C and n are the individual capacitor voltages, the DC-link voltage, the individual capacitances and the number of phase-voltage levels, respectively

The application of redundant vectors for capacitor voltage requirements balancing affects the for compensation, since, prior to the calculation of the capacitor balancing equations, the actual phase voltages and the size of the phase voltage steps at the switching instances, are Furthermore, the shape of the phase voltage unknown. waveforms may change from one modulation cycle to the next. In addition, any modification to the commanded converter terminal voltages, for compensation, may move the reference vector from one multilevel region to another, dictating a different set of switching vectors are utilised with correspondingly different blanking-time compensation requirements. This interdependence of factors makes it necessary to implement on-state voltage compensation and blanking-time compensation independently.

At this point it should be noted that, more generally, redundant switching vectors may also be used to satisfy criteria other than for capacitor balancing of DCCs. For example, [20] and [21] utilise switching vector redundancies to eliminate common-mode voltages when using a multilevel cascaded H-bridge topology and a 5-level DCC topology, respectively.

# IV. PROPOSED ON-STATE COMPENSATION SCHEME

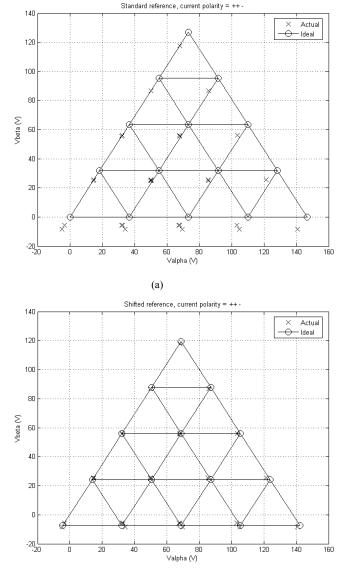

The proposed compensation scheme for the on-state voltage error relies on the fact that, for a known 3-phase current polarity, all the switching vectors share an almost identical offset in the  $\alpha\beta$  coordinate frame. By way of example, Fig. 3a shows the ideal and actual switching vectors for the 3-phase current polarity:  $I_A > 0$ ;  $I_B > 0$ ;  $I_C < 0$ . Given that the vector offsets in the stationary  $\alpha\beta$  reference frame are similar, it is possible to shift the reference diagram such that the mean average error between the actual vectors and the reference diagram, in the first sextant, is zero (Fig 3b). The offsets are calculated from:

$$V_{\alpha offset} = \frac{1}{m} \sum_{i=1}^{m} [V_{\alpha error}(i)]$$

(4)

$$V_{\beta offset} = \frac{1}{m} \sum_{i=1}^{m} \left[ V_{\beta error}(i) \right]$$

(5)

where

$$V\alpha_{error}(i) = V\alpha_{actual}(i) - V\alpha_{ideal}(i)$$

(6)

$$V\beta_{error}(i) = V\beta_{actual}(i) - V\beta_{ideal}(i)$$

(7)

and m is the number of vectors in the first sector.

Shifting the commanded reference vector by an equal amount in the opposing direction to the reference diagram shift, compensates for the shifted switching vectors and removes the error. Removing the error in this way has the

advantage of maintaining the symmetry of the SV diagram, and therefore the simplicity of the region identification and duty-cycle calculation, is maintained. The shifted reference vector is calculated as follows:

$$V\alpha'_{ref} = V\alpha_{ref} - V\alpha_{offset}$$

(8)

$$V\beta'_{ref} = V\beta_{ref} - V\beta_{offset}$$

(9)

Fig. 3. Actual and ideal switching vectors in the sector under current polarity:  $I_A > 0$ ;  $I_B > 0$ ;  $I_C < 0$  (a) uncompensated, (b) compensated.

The offset values  $V\alpha_{offset}$  and  $V_{\beta_{offset}}$  are calculated offline as functions of the device voltage drops:  $V_{CEon}$ ,  $V_{ff}$  and  $V_{fc}$

$$V_{\alpha offset} = AV_{CEon} + BV_{FC} + CV_{FF}$$

(10)

$$V_{\beta offset} = DV_{CEon} + EV_{FC} + FV_{FF} \tag{11}$$

where parameters A-F are stored in a look-up table for the

various current polarities.

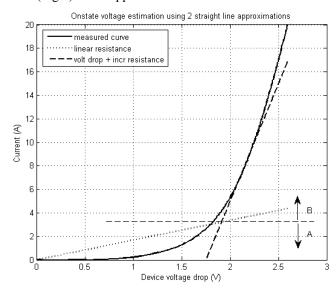

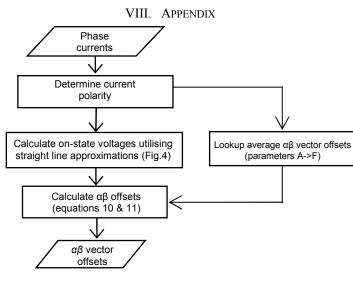

The voltage drops, VCEON, Vff and Vfe, are non-linear functions of current, and values are estimated (on-line) with two-straight line approximations for each parameter. The first is a linear resistance that is calculated at relatively low currents, and for higher currents a constant voltage drop with an incremental resistance is used. The dual slope estimation of the device on-state voltages allows the amount of compensation around the zero-crossing region to be reduced, thereby preventing 'over-compensation'. By way of example, Fig.4. shows VCEON, as a function of current, with two straight lines fitted to the measured curve. The linear resistance approximation is applied in low current region A, while the constant voltage drop + incremental resistance is applied in region B. A flow diagram, for the on-state compensation, is included (Fig.9) in the appendix.

Fig. 4. Measured IGBT on-state voltage,  $V_{CEon}$ , and the corresponding approximations

### V. BLANKING-TIME COMPENSATION

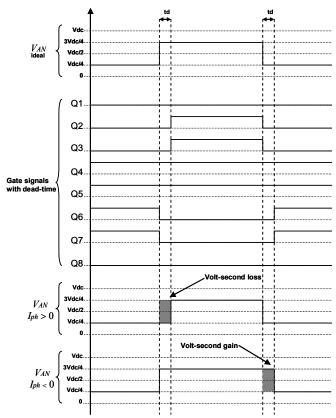

Fig. 5 shows example waveforms of gate drive signals for a commanded phase voltage step between  $V_{dc}/4$  and  $3V_{dc}/4$ , where blanking-time, td, is implemented by delaying the rising edges of the each gate drive signal. For positive current, when the commanded phase voltage steps from  $V_{dc}/4$  to 3Vdc/4, IGBTs Q6 and Q7 are turned off while IGBTs Q2 and Q3 are turned on after the blanking-time td. During the blanking-time, current continues to flow through D10 and O4 and only commutates to D14, Q2 and Q3 when Q2 and Q3 have turned on (after the blanking-time), Fig.1. When the commanded voltage returns from  $3V_{dc}/4$  to  $V_{dc}/4$ , Q2 and Q3 are turned off td seconds before Q6 and Q7 are turned on. When Q2 and Q3 are turned off, positive current commutates back to D10 and Q4. The net result therefore is an error in the voltage appearing at the converter phase terminal. Averaged over the switching period,  $T_s$ , the voltage error is given by:

$$V_{err} = -\frac{V_{dctd}}{2T_s} \tag{12}$$

Fig. 5. Example gate drive waveforms and blanking-time effects.

For the negative current case, the state of Q6 and Q7 determine the point at which the current commutates between the Q5, D13 to Q5, Q6, Q7, D9. When the commanded phase voltage drops from  $3V_{dc}/4$  to  $V_{dc}/4$ , the rising edges of Q6 and Q7 are delayed by the blanking-time, and hence, the phase terminal voltage remains at  $3V_{dc}/4$  during the blanking period. This results in a voltage error averaged over the switching period:

$$Verr = \frac{V_{dctd}}{2T_s} \tag{13}$$

The voltage error for any multilevel step size can therefore be calculated as:

$$V_{err} = -V_{step} \frac{td}{T_s} \operatorname{sgn}(I_{ph})$$

(14)

where  $V_{step}$  is the size of the multilevel voltage step and

$$sgn(I_{ph}) = 1; I_{ph} > 0$$

$sgn(I_{ph}) = -1; I_{ph} < 0$  (15)

The result (14) shows that the error created by the blanking time is proportional to the size of the voltage step at the switching instant. This voltage step size is determined by the choice of switching sequences made by the capacitor balancing algorithm for a particular modulation period.

To compensate for the blanking-time error voltage, it is proposed to vary the length of the commanded phase voltage signal prior to the addition of dead-time. The phase current polarity is sampled at the start of the switching cycle and the commanded phase voltage is extended by td seconds if the phase current is positive, or reduced by td seconds if the phase current is negative, where the value of td is known from converter design. By applying this pulse based compensation, the volt-second error, which is dependent on the size of the multilevel step, is therefore compensated.

It should be noted that the on-state compensation and dead time compensation could be applied to modulation schemes other than SVM, for example multilevel Sinusoidal PWM (SPWM). However, the ability of the proposed schemes to compensate for errors resulting from the application of redundant vectors, makes the proposed scheme particularly suited to SVM techniques.

#### VI. EXPERIMENTAL RESULTS

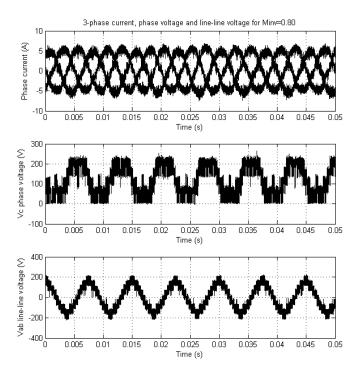

Fig. 6. 3-phase currents, phase and line-line voltage from 5-level inverter

The compensation schemes are applied to a 5-level DCC driving a low-inductance BLAC machine (synchronous inductance 180μH) operating from a 220V DC-link. Field-orientated control along with the on-state voltage compensation is implemented using a Texas Instruments TMS320C6713 development board, while the gate drive signals and blanking-time compensation are implemented on a Xilinx Spartan 3 development board. For both on-state and dead-time compensation schemes, accurate current polarity detection is crucial for correct compensation since incorrect current polarity determination results in a reinforcement, rather

than a reduction of the dead-time errors. A scheme detailed in [9], which low-pass-filters the currents in the rotating dq axis prior to conversion into the stationary  $\alpha\beta$  axis for polarity determination, is therefore employed.

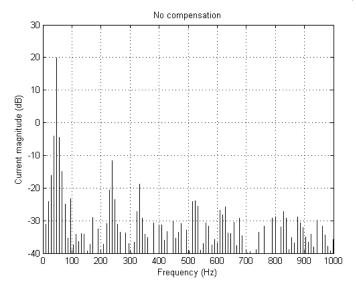

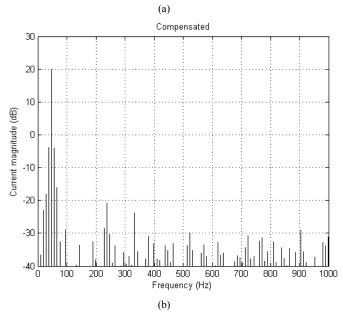

Fig. 7. FFT of phase current, (a) no compensation, (b) blanking-time and onstate voltage compensation.

Fig. 6 shows example 3-phase currents, phase voltage and line-line voltage from the 5-level inverter operating at an inverter modulation index  $m_{\rm inv} = 0.8$ .

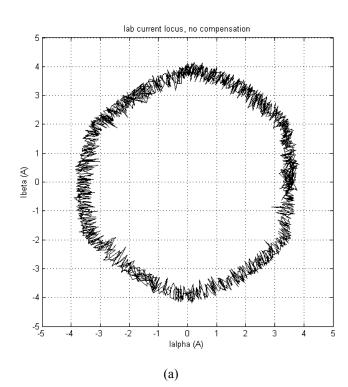

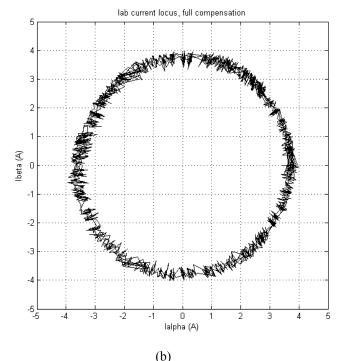

Figs. 7 a-b compare the low frequency phase current harmonics between the non-compensated and compensated cases (both blanking-time and on-state voltage drop compensation). The first notable harmonic is the 5th at around 240Hz with the compensated scheme reducing this harmonic by 9.1dB. Reductions in the 7th and 11th harmonics are also shown to be 5.0dB and 5.9dB, respectively. Figs. 8 a-b show the 3 phase currents, converted into the  $\alpha\beta$  frame and then

plotted as a locus plot for the uncompensated and compensated cases, respectively. The reduction in low frequency harmonics in the compensated case is clearly shown with the uncompensated case appearing more hexagonal rather than the circular form of the compensated case.

Fig. 8.  $\alpha\beta$  current locus, (a) no compensation, (b) blanking-time and onstate voltage compensation.

Harmonics in the current waveform result in torque pulsations from the permanent magnet machine and so

reducing these harmonics, with the proposed scheme, provides for smoother torque production. Furthermore, system efficiency will increase as the harmonics are responsible for extra power losses in the machine and power converter.

#### VII. CONCLUSION

The paper proposes a simple solution to minimise the error created by on-state device voltage drops while also compensating for the blanking-time inserted to prevent shoot-through, for multilevel DCCs, operating with redundant vector selection. To-date, the additional voltage drops and complexity of compensating for dead-time effects, have not been considered in previous literature.

Experimental results, gathered from a prototype 5-level converter, have shown that the compensation scheme reduces the low frequency harmonics when compared to the uncompensated case. The improvement in current quality is readily apparent from a locus plot of the phase currents in the  $\alpha\beta$  reference frame. Low frequency harmonics are shown to create a hexagonal locus for the uncompensated case, while the compensated case shows a circular locus, thereby indicating higher quality sinusoidal phase currents. Furthermore, a harmonic analysis has shown reductions in the 5th, 7th and 11th harmonics by 9.1dB, 5.0dB and 5.9dB, respectively. Ultimately, the mitigation of low frequency harmonics facilitates stable motor torque production with reduced torque pulsations and lower power losses.

Fig. 9. On-state voltage compensation flow diagram

# REFERENCES

- S. R. Minshull, C. M. Bingham, D. A. Stone, and M. P. Foster, "A back to back multilevel converter for driving low inductance brushless AC machines," presented at Power Electronics and Applications, 2007 European Conference on, 2007.

- [2] J. Ewanchuk, J. Salmon, and A. Knight, "Performance of a High Speed Motor Drive System Using a Novel Multi-Level Inverter Topology,"

- presented at Industry Applications Society Annual Meeting, 2008. IAS '08. IEEE, 2008.

- [3] Y. Murai, T. Watanabe, and H. Iwasaki, "Waveform Distortion and Correction Circuit for PWM Inverters with Switching Lag-Times," *Industry Applications, IEEE Transactions on*, vol. IA-23, pp. 881-886, 1987

- [4] J. Seung-Gi and P. Min-Ho, "The analysis and compensation of deadtime effects in PWM inverters," *Industrial Electronics, IEEE Transactions on*, vol. 38, pp. 108-114, 1991.

- [5] L. Ben-Brahim, "On the compensation of dead time and zero-current crossing for a PWM-inverter-controlled AC servo drive," *Industrial Electronics, IEEE Transactions on*, vol. 51, pp. 1113-1118, 2004.

- [6] D. Leggate and R. J. Kerkman, "Pulse-based dead-time compensator for PWM voltage inverters," *Industrial Electronics, IEEE Transactions* on, vol. 44, pp. 191-197, 1997.

- [7] A. C. Oliveira, C. B. Jacobina, and A. M. N. Lima, "Improved Dead-Time Compensation for Sinusoidal PWM Inverters Operating at High Switching Frequencies," *Industrial Electronics, IEEE Transactions on*, vol. 54, pp. 2295-2304, 2007.

- [8] Z. Dongsheng and D. G. Rouaud, "Dead-time effect and compensations of three-level neutral point clamp inverters for highperformance drive applications," *Power Electronics, IEEE Transactions on*, vol. 14, pp. 782-788, 1999.

- [9] G. L. Wang, D. G. Xu, and Y. Yu, "A novel strategy of dead-time compensation for PWM voltage-source inverter," presented at Applied Power Electronics Conference and Exposition, 2008. APEC 2008. Twenty-Third Annual IEEE, 2008.

- [10] C. Jong-Woo and S. Seung-Ki, "Inverter output voltage synthesis using novel dead time compensation," *Power Electronics, IEEE Transactions on*, vol. 11, pp. 221-227, 1996.

- [11] A. Munoz-Garcia and T. A. Lipo, "On-line dead time compensation technique for open-loop PWM-VSI drives," presented at Applied Power Electronics Conference and Exposition, 1998. APEC '98. Conference Proceedings 1998., Thirteenth Annual, 1998.

- [12] K. Hyun-Soo, M. Hyung-Tae, and Y. Myung-Joong, "On-line deadtime compensation method using disturbance observer," *Power Electronics, IEEE Transactions on*, vol. 18, pp. 1336-1345, 2003.

- [13] G. Pellegrino, P. Guglielmi, E. Armando, and I. R. Bojoi, "Self-Commissioning Algorithm for Inverter Non-Linearity Compensation in Sensorless Induction Motor Drives," presented at Industry Applications Society Annual Meeting, 2008. IAS '08. IEEE, 2008.

- [14] H. W. Kim, M. J. Youn, and K. Y. Cho, "New Voltage Distortion Observer of PWM VSI for PMSM," *Industrial Electronics, IEEE Transactions on*, vol. 52, pp. 1188-1192, 2005.

- [15] N. Urasaki, T. Senjyu, K. Uezato, and T. Funabashi, "Adaptive Dead-Time Compensation Strategy for Permanent Magnet Synchronous Motor Drive," *Energy Conversion, IEEE Transaction on*, vol. 22, pp. 271-280, 2007.

- [16] J. Pou, P. Rodriguez, D. Boroyevich, R. Pindado, and I. Candela, "Efficient Space-Vector Modulation Algorithm for Multilevel Converters with Low Switching Frequencies in the Devices," presented at Power Electronics Specialists Conference, 2005. PESC '05. IEEE 36th. 2005.

- [17] M. Marchesoni and P. Tenca, "Diode-clamped multilevel converters: A practicable way to balance DC-link voltages," *IEEE Transactions on Industrial Electronics*, vol. 49, pp. 752-765, 2002.

- [18] J. Pou, R. Pindado, D. Boroyevich, P. Rodriguez, and J. Vicente, "Voltage-balancing strategies for diode-clamped multilevel converters," presented at PESC Record, Aachen, Germany, 2004.

- [19] M. Saeedifard, R. Iravani, and J. Pou, "A Space Vector Modulation Strategy for a Back-to-Back Five-Level HVDC Converter System," *Industrial Electronics, IEEE Transactions on*, vol. 56, pp. 452-466, 2009

- [20] J. Rodriguez, J. Pontt, P. Correa, P. Cortes, and C. Silva, "A new modulation method to reduce common-mode voltages in multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 51, pp. 834-839, 2004.

- [21] M. M. Renge and H. M. Suryawanshi, "Five-Level Diode Clamped Inverter to EliminateCommon Mode Voltage and Reduce dv/dt in Medium Voltage Rating Induction Motor Drives," *Power Electronics, IEEE Transactions on*, vol. 23, pp. 1598-1607, 2008.

**Stephen R. Minshull** received the M.Eng degree in electronic and electrical engineering from The University of Sheffield, Sheffield, U.K., in 2005, where he is currently working towards the Ph.D. degree in the Department of Electrical and Electronic Engineering.

His research interests include the design and control of multilevel converters for electric drive applications and positionsensorless control of brushless machines.

Martin P. Foster received the B.Eng. degree in electronic and electrical engineering, the M.Sc.(Eng.) degree in control systems, and award a PhD for his thesis "Analysis and Design of High-order Resonant Power Converters" from the University of Sheffield, Sheffield, U.K., in 1998, 2000, and 2003, respectively. In 2003 he became a member of academic staff at Sheffield specialising in power electronic systems.

His current research interests include the modelling and control of switching power converters, resonant power supplies, lightweight energy transformation components, power electronic packaging and autonomous aerospace vehicles.

Christopher M. Bingham received the B.Eng degree in electronic systems and control engineering from Sheffield City Polytechnic, Sheffield, U.K., in 1989, the M.Sc.(Eng) degree in control systems engineering from the University of Sheffield, Sheffield, U.K., in 1990, and the Ph.D. degree in control systems to accommodate nonlinear dynamic effects in aerospace flight-surface actuators from Cranfield University, Bedfordshire, U.K., in 1994. He was a Post-Doctoral Researcher at Cranfield University, until subsequently taking up a

research position at the University of Sheffield. Since 1998, he has been a Lecturer in the Department of Electronic and Electrical Engineering, University of Sheffield.

His current research interests include traction control/anti-lock braking systems for electric vehicles, electromechanical actuation of flight control surfaces, control of active magnetic bearings for high-speed machines, sensorless control of brushless machines, analysis and design of resonant converter systems, and the control of high-performance UAVs.

**David A. Stone** received the B.Eng. degree in electronic engineering from the University of Sheffield, Sheffield, U.K., in 1984 and the Ph.D. degree from Liverpool University, Liverpool, U.K., in 1989.

He returned to the University of Sheffield as a member of academic staff specializing in power electronics and machine drive systems. His current research interests are in hybrid-electric vehicles, battery charging, EMC, and novel lamp ballasts for low pressure fluorescent lamps.