TESIS DE LA UNIVERSIDAD

# DE ZARAGOZA

María Ángelica Dávila Gúzman

2022

58

FPGA Accelerators on Heterogeneous Systems: An Approach Using High Level Synthesis

Director/es Villarroya Gaudó, María Suárez Gracia, Darío

Prensas de la Universidad Universidad Zaragoza

ISSN 2254-7606

© Universidad de Zaragoza Servicio de Publicaciones

ISSN 2254-7606

**Tesis Doctoral**

# FPGA ACCELERATORS ON HETEROGENEOUS SYSTEMS: AN APPROACH USING HIGH LEVEL SYNTHESIS

Autor

María Ángelica Dávila Gúzman

Director/es

Villarroya Gaudó, María Suárez Gracia, Darío

#### UNIVERSIDAD DE ZARAGOZA Escuela de Doctorado

Programa de Doctorado en Ingeniería de Sistemas e Informática

# FPGA Accelerators on Heterogeneous Systems: An Approach Using High Level Synthesis

Maria Angélica Dávila Guzmán

November, 2021 Version: Draft

Departamento de Informática e Ingeniería de sistemas Instituto de Investigación es Ingeniería de Aragón Grupo de Arquitectura de Computadores

A thesis submitted in total fulfillment for the degree of Doctor of Philosophy

# FPGA Accelerators on Heterogeneous Systems: An Approach Using High Level Synthesis

Maria Angélica Dávila Guzmán

Supervisors Darío Suárez Gracia María Villarroya Gaudó

November, 2021

#### Maria Angélica Dávila Guzmán

FPGA Accelerators on Heterogeneous Systems: An Approach Using High Level Synthesis A thesis submitted in total fulfillment for the degree of Doctor of Philosophy , November, 2021 Supervisors: Darío Suárez Gracia and María Villarroya Gaudó

#### Universidad de Zaragoza

Grupo de Arquitectura de Computadores Instituto de Investigación es Ingeniería de Aragón Departamento de Informática e Ingeniería de sistemas Calle Maria de Luna 50018 Zaragoza

# Abstract

The emergence of FPGAs in the High-Performance Computing domain is arising thanks to their promise of better energy efficiency and low control latency, compared with other devices such as CPUs or GPUs.

Albeit these benefits, their complete inclusion into HPC systems still faces several challenges. First, FPGA complexity means its programming more difficult compared to devices such as CPU and GPU. Second, the development time is longer due to the required synthesis effort. And third, working with multiple devices increments the details that should be managed and increase hardware complexity.

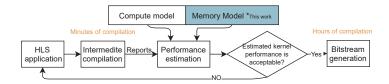

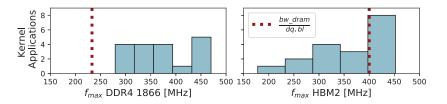

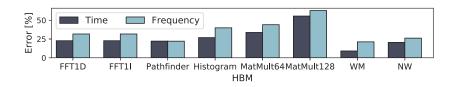

This thesis tackles these 3 problems at different stack levels to improve and to make easier the adoption of FPGAs using High-Level Synthesis on HPC systems. At a close to the hardware level, this thesis contributes with a new analytical model for memory-bound applications, an usual situation for HPC applications. The model for HLS kernels can anticipate application performance before place and route, reducing the design development time. Our results show a high precision and adaptable model for external memory technologies such as DDR4 and HBM2, and kernel frequency changes. This solution potentially increases productivity, reducing application development time.

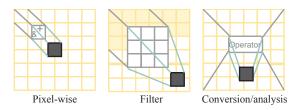

Understanding low-level implementation details is difficult for average programmers, and the development of FPGA applications still requires high proficiency programming skills. For this reason, the second proposal is focused on the extension of a computer vision library to be portable among two of the main FPGA vendors. The template-based library allows hardware flexibility and hides design decisions such as the communication among nodes, the concurrency programming model, and the application's integration in the heterogeneous system, to develop complex vision graphs easily.

Finally, we have transparently integrated the FPGA in a high level framework for co-execution with other devices. We propose a set of high level abstractions covering synchronization mechanism and load balancing policies in a highly heterogeneous system with CPU, GPU, and FPGA devices. We present the main challenges that inspired this research and the benefits of the FPGA use demonstrating performance and energy improvements.

In summary, this thesis contributes to the adoption of FPGAs in HPC domains by offering solutions that help reducing development time and improve performance and energy efficiency.

## Resumen

La evolución de las FPGAs como dispositivos para el procesamiento con alta eficiencia energética y baja latencia de control, comparada con dispositivos como las CPUs y las GPUs, las han hecho atractivas en el ámbito de la computación de alto rendimiento (HPC).

A pesar de las inumerables ventajas de las FPGAs, su inclusión en HPC presenta varios retos. El primero, la complejidad que supone la programación de las FPGAs comparada con dispositivos como las CPUs y las GPUs. Segundo, el tiempo de desarrollo es alto debido al proceso de síntesis del hardware. Y tercero, trabajar con más arquitecturas en HPC requiere el manejo y la sintonización de los detalles de cada dispositivo, lo que añade complejidad.

Esta tesis aborda estos 3 problemas en diferentes niveles con el objetivo de mejorar y facilitar la adopción de las FPGAs usando la síntesis de alto nivel(HLS) en sistemas HPC.

En un nivel próximo al hardware, en esta tesis se desarrolla un modelo analítico para las aplicaciones limitadas en memoria, que es una situación común en aplicaciones de HPC. El modelo, desarrollado para kernels programados usando HLS, puede predecir el tiempo de ejecución con alta precisión y buena adaptabilidad ante cambios en la tecnología de la memoria, como las DDR4 y HBM2, y en las variaciones en la frecuencia del kernel. Esta solución puede aumentar potencialmente la productividad de las personas que programan, reduciendo el tiempo de desarrollo y optimización de las aplicaciones.

Entender los detalles de bajo nivel puede ser complejo para las programadoras promedio, y el desempeño de la aplicaciones para FPGA aún requiere un alto nivel en las habilidades de programación. Por ello, nuestra segunda propuesta está enfocada en la extensión de las bibliotecas con una propuesta para cómputo en visión artificial que sea portable entre diferentes fabricantes de FPGAs. La biblioteca se ha diseñado basada en templates, lo que permite una biblioteca que da flexibilidad a la generación del hardware y oculta decisiones de diseño críticas como la comunicación entre nodos, el modelo de concurrencia, y la integración de las aplicaciones en el sistema heterogéneo para facilitar el desarrollo de grafos de visión artificial que pueden ser complejos.

Finalmente, en el runtime del host del sistema heterogéneo, hemos integrado la FPGA para usarla de forma trasparente como un dispositivo acelerador para la co-ejecución en sistemas heterogéneos. Hemos hecho una serie propuestas de alto nivel de abstracción que abarca los mecanismos de sincronización y políticas de balanceo en un sistema altamente heterogéneo compuesto por una CPU, una GPU y una FPGA. Se presentan los principales retos que han inspirado esta investigación y los beneficios de la inclusión de una FPGA en rendimiento y energía.

En conclusión, esta tesis contribuye a la adopción de las FPGAs para entornos HPC, aportando soluciones que ayudan a reducir el tiempo de desarrollo y mejoran el desempeño y la eficiencia energética del sistema.

# Contents

| 1 | Intr | oduction                                                      | 5  |  |  |  |  |  |  |  |  |  |  |

|---|------|---------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|   | 1.1  | Rationale                                                     | 5  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Objectives and Dissertation Overview                          | 7  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Contributions                                                 | 8  |  |  |  |  |  |  |  |  |  |  |

|   | 1.4  | Thesis Project Framework                                      | 9  |  |  |  |  |  |  |  |  |  |  |

| 2 | FPG  | SAs as Accelerator in Heterogeneous System                    | 11 |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | Introduction                                                  |    |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | P. Heterogeneous System                                       |    |  |  |  |  |  |  |  |  |  |  |

|   | 2.3  | FPGA Device                                                   | 15 |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.1 FPGA Program Design                                     | 19 |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.2 FPGAs as Accelerator on heterogeneous system            | 21 |  |  |  |  |  |  |  |  |  |  |

| 3 | Exp  | erimental Framework                                           | 25 |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Evaluation Hardware                                           | 25 |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Software Framework                                            | 30 |  |  |  |  |  |  |  |  |  |  |

| 4 | Ana  | lytical Time Estimation of Memory-bound Applications for FPGA |    |  |  |  |  |  |  |  |  |  |  |

|   | Usir | ng High-level Synthesis                                       | 33 |  |  |  |  |  |  |  |  |  |  |

|   | 4.1  | Introduction                                                  |    |  |  |  |  |  |  |  |  |  |  |

|   | 4.2  | Related Work                                                  | 35 |  |  |  |  |  |  |  |  |  |  |

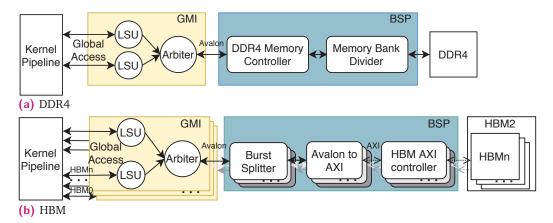

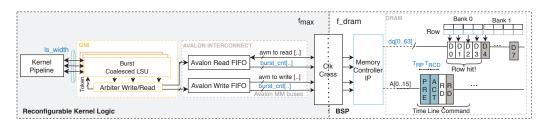

|   | 4.3  | FPGA External Memory and BSP                                  | 36 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.3.1 Global Memory Interconnect                              | 37 |  |  |  |  |  |  |  |  |  |  |

|   | 4.4  | Performance Estimation for FPGAs                              | 40 |  |  |  |  |  |  |  |  |  |  |

|   | 4.5  | 5 Memory Model for FPGA accelerators                          |    |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.5.1 Burst-Coalesced LSU                                     | 45 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.5.2 Atomic-pipelined LSU                                    | 48 |  |  |  |  |  |  |  |  |  |  |

|   | 4.6  | Methodology                                                   | 49 |  |  |  |  |  |  |  |  |  |  |

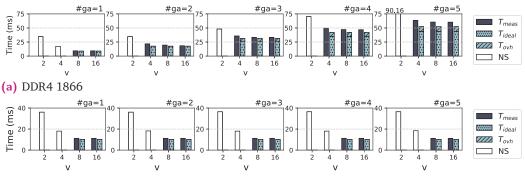

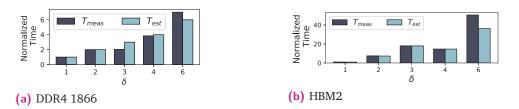

|   | 4.7  | 'Results                                                      |    |  |  |  |  |  |  |  |  |  |  |

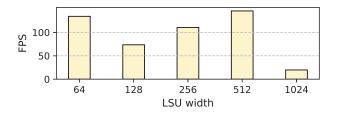

|   |      | 4.7.1 Microbenchmarks                                         | 51 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.7.2 Applications                                            | 56 |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.7.3 Comparison With Other Models                            | 59 |  |  |  |  |  |  |  |  |  |  |

|   | 4.8  | Conclusions                                                   | 60 |  |  |  |  |  |  |  |  |  |  |

|   | 4.9  | Contributions                                                 | 61 |  |  |  |  |  |  |  |  |  |  |

| 5  | FPG   | SA Frameworks to Improve Design Productivity                  | 63  |

|----|-------|---------------------------------------------------------------|-----|

|    | 5.1   | Introduction                                                  | 63  |

|    | 5.2   | Related Work                                                  | 64  |

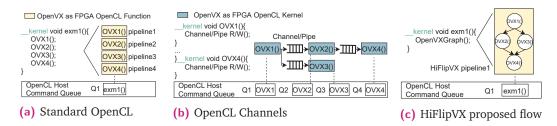

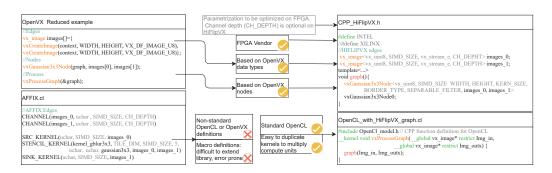

|    | 5.3   | OpenVX Programming Flow Alternatives on FPGA                  | 65  |

|    | 5.4   | HiFlipVX                                                      | 67  |

|    | 5.5   | Methodology                                                   | 68  |

|    | 5.6   | Tuning HiFlipVX for Intel FPGAs                               | 69  |

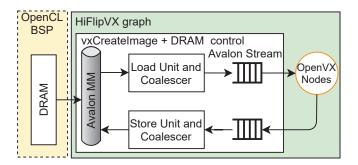

|    |       | 5.6.1 Execution model                                         | 69  |

|    |       | 5.6.2 Kernels                                                 | 70  |

|    |       | 5.6.3 Edges                                                   | 70  |

|    | 5.7   | Results                                                       | 75  |

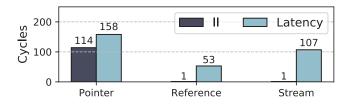

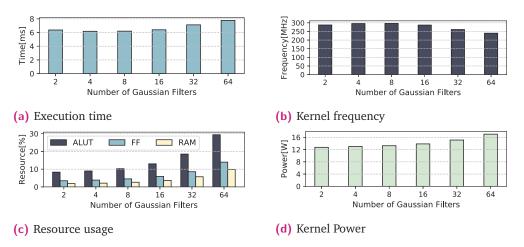

|    |       | 5.7.1 HiFlipVX Scalability Analysis                           | 75  |

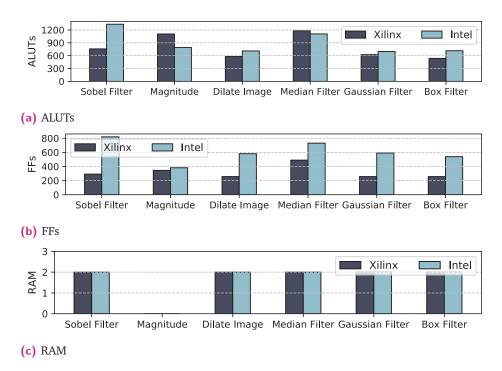

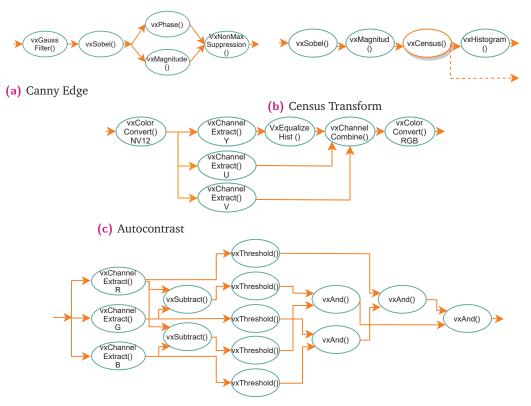

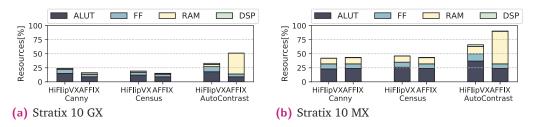

|    |       | 5.7.2 OpenVX Application Resource Utilization                 | 76  |

|    |       | 5.7.3 OpenVX Application Analysis                             | 80  |

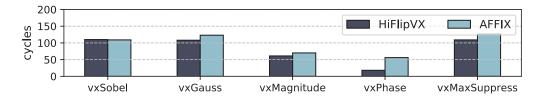

|    |       | 5.7.4 Comparison with Existing Approaches                     | 80  |

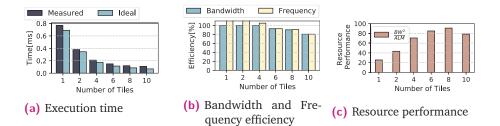

|    |       | 5.7.5 Tiling HiFlipVX for HBM memory                          | 83  |

|    | 5.8   | Conclusions                                                   | 84  |

|    | 5.9   | Contributions                                                 | 85  |

| 6  | FPG   | GAs on Heterogeneous System for Energy Efficiency             | 87  |

|    | 6.1   | Introduction                                                  | 87  |

|    | 6.2   | Related Work                                                  | 89  |

|    | 6.3   | EngineCL Runtime                                              | 90  |

|    | 6.4   | Coupling FPGA to EngineCL                                     | 92  |

|    | 6.5   | Methodology                                                   | 95  |

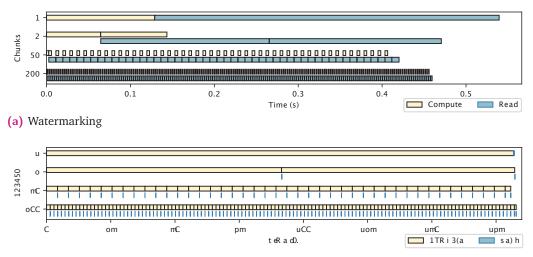

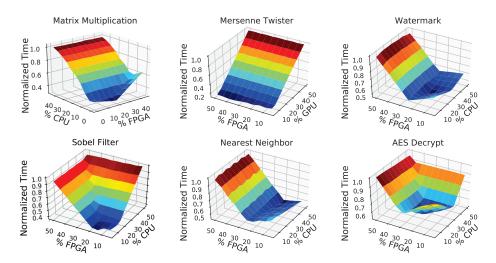

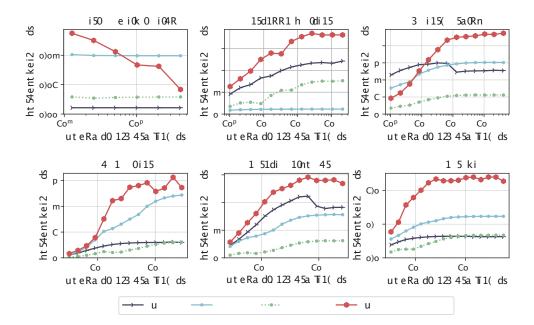

|    | 6.6   | Results                                                       | 96  |

|    |       | 6.6.1 Scheduler Tuning                                        | 96  |

|    |       | 6.6.2 Scheduler comparison                                    | 98  |

|    | 6.7   | Conclusions                                                   | 102 |

|    | 6.8   | Contributions                                                 | 103 |

| 7  | Con   | clusions and Future Work                                      | 105 |

|    | 7.1   | Conclusions                                                   | 105 |

|    | 7.2   | Future Work                                                   |     |

| Bi | bliog | raphy                                                         | 109 |

|    | -     |                                                               |     |

| 8  |       | endix: Memory aware co-execution in heterogeneous system with |     |

|    |       |                                                               | 123 |

|    | 8.1   | Introduction                                                  | 123 |

| 8.2 FPGA with HBM memory in a I | Heterogeneous system |

|---------------------------------|----------------------|

| List of Figures                 | 129                  |

| List of Tables                  | 133                  |

| Listings                        | 135                  |

# Abbreviations

- FPGA Field Programmable Gate Array

- **BSP** Board Support Package

- GMI Global Memory Interconnect

- HBM High Memory Bandwidth

- DDR Double Data Array memory

- HLS High Level Synthesis

- HDL Hardware Design Level

- LSU Load Store Unit

- IP Intellectual Property core

- PCIe Peripheral Component Interconnect express

- RTL Register Transfer Level

# **Publications**

Part of this dissertation includes previous results of published or under review papers of my authorship. The works in collaboration are possible thanks to two tools developed in two universities: 1) a runtime for co-execution in heterogeneous system (EngineCL) from the University of Cantabria, and 2) a HLS open source library for Xilinxs FPGAs (HiFlipVX) from the University of Dresden.

The list of publications in chronological order are:

- Maria Angélica Dávila-Guzmán, Raúl Nozal, Rubén Gran, Maria Villaroya-Gaudó, Darío Suárez, and José Luis Bosque. First Steps Towards CPU, GPU, and FPGA Parallel Execution with EngineCL. Proceedings of the 18<sup>th</sup> International Conference on Computational and Mathematical Method in Science and Engineering. CMMSE 2018.

- Maria Angélica Dávila-Guzmán, Rubén Gran Tejero, María Villarroya-Gaudó, and Darío Suárez Gracia. Caracterización de una FPGA sobre un sistema heterogéneo usando OpenCL. In Jornadas de la sociedad de Arquitectura y Tecnología de Computadoras (SARTECO), pages 75–83, 2018.

- Maria Angelica Davila Guzman, Ruben Gran Tejero, Maria Villarroya Gaudo, and Dario Suarez Gracia. Towards the inclusion of FPGAs on commodity heterogeneous systems. In 2018 International Conference on High Performance Computing Simulation (HPCS), pages 554–556, 2018. *B CORE 2018*

- María Angélica Dávila Guzmán, Raúl Nozal, Rubén Gran Tejero, María Villarroya- Gaudó, Darío Suárez Gracia, and Jose Luis Bosque. Cooperative CPU, GPU, and FPGA heterogeneous execution with EngineCL. The Journal of Supercomputing, 75(3): 1732–1746, 2019. Q2 JCR 2019

- 5. Maria A.Dávila-Guzmán, Rubén Gran Tejero, María Villarroya-Gaudó, and Darío Suárez Gracia. An analytical model of memory-bound applications

compiled with high-level synthesis. In 2020 IEEE 28<sup>th</sup> Annual International Symposium on Field- Programmable Custom Computing Machines (FCCM), pages 218–218, 2020. (Poster). *A CORE 2020. HiPEAC paper award*

- 6. Maria Angélica Dávila-Guzmán, Rubén Gran Tejero, Maria Villaroya-Gaudó, Darío Suárez, and José Luis Bosque. Memory aware co-execution in heterogeneous systems with CPU and FPGA devices. International Conference on Computational and Mathematical Method in Science and Engineering, CMMSE 2020.

- Maria Angélica Dávila-Guzmán, Rubén Gran Tejero, María Villarroya-Gaudó, Darío Suárez Gracia, Lester Kalms, and Diana Göhringer. A cross-platform OpenVX library for FPGA accelerators. In 2021 29<sup>th</sup> Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP), pages 75–83, 2021. C CORE 2021

- Maria A.Dávila-Guzmán, Rubén GranTejero, María Villarroya-Gaudó, and Darío Suárez Gracia. Analytical Model for Memory-centric High Level Synthesisgenerated Applications. IEEE Transactions on Computers, 2021. Q2 JCR 2020

- Maria Angélica Dávila-Guzmán, Rubén Gran Tejero, María Villarroya-Gaudó, Darío Suárez Gracia, Lester Kalms, and Diana Göhringer. A Cross-Platform OpenVX Library for FPGA Accelerators (PDP extension). Journal of Systems Architecture, 2021.

Q2 JCR 2020 (under minor review)

# Introduction

# 1

This chapter presents the reason for including the FPGAs in heterogeneous systems and the uprising programmability challenges. Also, it lists the objectives, the achieved contributions and the project framework that has allowed the development of this thesis.

#### 1.1 Rationale

At the end of Moore's law [108] and Dennard's scaling [35], the emergence of power and temperature constrains in computer system is driving computer hardware architects to new exciting perspectives. Maintain Moore's law was a deliberated choice of chip manufacturers, but in early 2000s, when the transistors size was below 90 nm, the expected benefits of higher computational power with lower energy consumption achieved only by scaling transistors started to fail.

The physical impossibility of placing more transistors in the same area switching at high frequency has forced to stop increasing the clock frequency in processors. To keep moving in the processors Moore's performance curve, during 2010's the number of cores in a processor was increased at lower frequencies, which in turn stopped the excessive power dissipation [104]. Heterogeneous era started with the combination of transistor technologies, evolved to many-core processors, and grew up with the inclusion of specialized processors (accelerators) in the computing systems such as GPUs, FPGAs, DSPs ...

Computer systems with accelerators have demonstrated high energy efficiency and compute power to support the market necessities . Some of these systems have even achieved good positions in the worldwide rankings such as TOP500 [153] of high performance computing and GREEN500 [152] of best energy efficiency in the last years [153].

More devices and hardware heterogeneity come with a burden in programming languages, forcing developers to learn unfamiliar tools and increasing the complexity of software development. One way to reduce heterogeneous system complexity is software abstractions, that can put away the intricacies with high-level frameworks and intelligent runtimes. When they succeed, they enable the computing capabilities of heterogeneous systems without exposing their nuances. The industry is driving initiatives of programming language standardization for heterogeneous systems with languages like OpenCL and SyCL, which abstract hardware architecture details in favor of development productivity. This enables developers to focus on the algorithm development and not on managing system resources. In these terms, the research can be concentrated on how to distribute the work load among the available devices efficiently in a heterogeneous system to improve compute performance and energy efficiency. Still, this approach is not yet broadly supported by industry but has been successfully explored with GPU devices [117, 94, 120, 1, 96, 53, 128, 165], FPGAs devices[53, 5, 160, 141], but it is not fully analyzed with higher heterogeneity including CPU, GPUs and FPGAs[139]. The last part of this dissertation includes one of the first proposals to enable co-execution between the three aforementioned devices.

The FPGAs have recently appeared in the accelerators ecosystem promising high power efficiency and easier programmability. Besides, new programming paradigms try to facilitate and promote their broad adoption. For example, the introduction of High-Level Synthesis has significant importance to improve programmer's productivity using high-level programming languages as C/C++, OpenCL, and recently SYCL[147]. The High-Level Synthesis in FPGAs is not new and has a long history of fails [99], the design space could have thousand of solutions, so it took long time to develop HLS-based tools. The evolution of the transformation from C to RTL was responsible for the take off of the FPGA market in 2004 [99], and in 2015 with the Intel announce of Altera's acquisition, one of the main FPGA manufacturers, the new technological road map was opened with the idea of FPGA integration with Xeon processors [62, 56].

The inclusion of an FPGA accelerator in a heterogeneous system ensuring high programmers productivity is still under development [18]. Although heterogeneous programming languages promise single-source and functional portable programs, the performance portability has not achieved the same level of maturity in industrial framework's yet. FPGA design development has remarkable differences compared with CPUs and GPUs, even using High-Level Synthesis, since the FPGAs architecture is very flexible and requires the expression of low level details to achieve optimal performance. Consequently, the research community has to develop and support the application frameworks for program optimization and even build the set of benchmarks for testing, which mismatch among FPGA vendors.

In summary, adding higher heterogeneity with new devices as FPGAs requires more than a high-level programming framework; the programmers need to understand the device's architecture and main bottlenecks in an early compilation stage to reduce the development time. This approximation to FPGA optimization could be a long way for custom programs. Relying only on the OpenCL standard is insufficient, since developers require specifications with sufficient low level and near the desired task to easily describe the parallelism with specific FPGA-friendly frameworks, forgetting coarse details as FPGA model features, and focusing on performance. These approaches are covered in this dissertation, particularly in Chapters 4 and 5.

#### 1.2 Objectives and Dissertation Overview

The overall goal of this dissertation is to explore the inclusion of a high energy efficient device as the FPGA in a heterogeneous system. This goal entails their programmability as the main deterrent to be broadly adopted by programmers in a productive way.

This dissertation is organized as follow:

Chapter 2 presents the background on heterogeneous systems and the FPGA architecture, including application design, and FPGA support to be used as an accelerator device. The following Chapter 3 presents the experimental framework.

Chapter 4 explores performance modeling as an option to improve FPGA applications using high-level synthesis. We present a new model for memory bound applications in FPGAs, which estimates the time performance of the applications at an early compilation stage, without the long time required for full compilation.

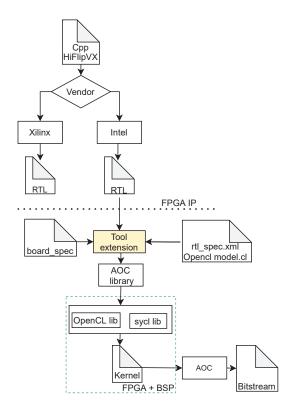

Chapter 5 explores the portability of FPGA applications among vendors using a highlevel framework for computer vision acceleration based on the OpenVX standard. We propose an extension to support Intel FPGA devices in an open library originally designed for Xilinx devices. Also the framework is extended to be used in FPGAs as a discrete accelerator combining C/C++ and OpenCL programming languages.

Chapter 6 presents the exploration of load balancing algorithms in a system with three different accelerators: CPU, GPU, and FPGA. We integrate the FPGA to an existing runtime library that supports the load balancing algorithm and evaluates the performance in terms of time and energy efficiency.

Finally, with all the contributions to the main objective in previous chapters, in Chapter 7 we conclude and brief possible future research lines.

#### 1.3 Contributions

This thesis includes the following contributions:

- Analysis of the FPGA architecture as an accelerator for one of the main FPGA vendors focused in the memory hierarchy. We determine the most time-critical blocks interacting between kernel memory request and the external memory controller.

- We develop a memory model for FPGAs using high-level synthesis in memory bound applications. We validate the model with a set of benchmarks and comparisons with the state-of-the-art, showing the estimation improvements of this proposal using a standard DDR4 and novel HBM2 memory.

- We propose a set of memory-oriented hints for programmers to guide optimizations using high level synthesis.

- We integrate two of the major FPGA vendors in a library for computer vision applications using the OpenVX standard. This library was carefully ported to Intel FPGA devices and extended to support stream communication among functions to allow fully graph implementations, and extensions to work in FPGA accelerators using OpenCL and C++. These results demonstrate portability and performance improvements.

- We present one of the first results of load balancing in a full heterogeneous system including three different accelerator devices: CPU, GPU, and FPGA.

• We analyze performance results of a heterogeneous system in terms of time and energy efficiency considering all three devices running at the same time. We demonstrate the increase in application performance and energy efficiency with the use of more accelerators.

#### 1.4 Thesis Project Framework

This thesis has been developed at the Computer Architecture Group of Zaragoza (gaZ) of the University of Zaragoza, in the Department of Computer Science and Systems Engineering (DIIS) and the Engineering Research Institute of Aragon (I3A).

The Santander - University of Zaragoza collaboration grant for Latin-American during two years (2017-2019) supported me as PhD Student. I have developed a research internship at the Technical University of Dresden, in the Adaptive Dynamic Systems group under the supervision of Diana Goehringer, thanks to a competitive collaboration grant from HiPEAC.

The research work has been funded by the Spanish National Science Research System, under the project PID2019-105660RB-C21: Jerarquía de memoria, gestión de tareas y optimización de aplicaciones, from the Agencia Estatal de Investigación and TIN2016-76635-C2-1-R: Arquitectura y programación de computadores escalables de alto rendimiento y bajo consumo, from the Spanish Ministry of Economy and Competitive. Both projects are in collaboration with the University of Cantabria which led to a fruitful collaboration in this thesis. Also the Aragón Government has partially founded the work through the Research group recognition: T58\_20R research group from Aragón Government and European Social Fund, and (3) 2014-2020 "Construyendo Europa desde Aragón" from European Regional Development Fund. Part of the FPGA board development kits used in this work and Quartus software licenses were a donation from Intel, and Nvidia gave away the GPU.

# FPGAs as Accelerator in Heterogeneous System

This chapter presents an overview of the heterogeneous systems, their programmability, and how they impulse the use of FPGAs. We discusse synthesis challenges from RTL design to the evolution to high-level synthesize. Finally, we emphasize in the FPGAs on heterogeneous system using high level languages which is the main focus of this dissertation.

#### 2.1 Introduction

Hardware heterogeneity as an alternative for high throughput and energy efficient processing includes accelerators as GPUs and FPGAs. One of the main drawbacks of a heterogeneous system is how to use the available hardware resources efficiently. This problem needs to be addressed in two ways: the first one is how to efficiently distribute the workload among available devices since each architecture performs differently according to algorithm requirements, and accelerators entail different sources of overheads as workload dispatch and communication. The second way is device programmability; the heterogeneous programming languages allow the same language for different device architectures, but even with the modern languages as SYCL [138], the code is functionally portable while performance is not. Then, the implementations and optimizations are different among devices, especially in FPGAs.

FPGAs offer high energy efficiency and low latency compared with CPU and GPU, but entails new challenges in its inclusion as an accelerator due to the long design flow and early support [29]. For this reason, the FPGAs need to be studied in deep detail.

#### 2.2 Heterogeneous System

The Dennard Scaling predictions stopped in early 2000's since it ignores two effects on submicron technologies that condition the current processor development. First, leakage current, which becomes more significant with the reduction of transistor size; second, also ignored, was the threshold voltage at which the transistor switches. Combining these effects, a higher number of transistors per Moore's law [108], increases the power density. As a result, more power needs complex and expensive power dissipation. To make things worst, the dynamic current depends on clock frequency, which was one of the main sources of improvement in the processor in Moore's era.

With the ending of Moore's era in computing, many solutions appear as the multicore [89, 156], dark-silicon techniques [40] and, the field of our interest, heterogeneous system [78]. The inclusion of accelerators has proven to be a feasible solution; for example, in the Top500 list of supercomputers of June 2021 [153], seven of the top ten list are heterogeneous systems, and in terms of power efficiency in the Green500, the number one is the MN-3 [152]. This heterogeneous architecture combines Xeon CPUs with MN-Cores for deep learning applications. MN-3 is also on the TOP500, but falls to 335th position, showing the difference in performance objectives and power efficiency.

The idea behind a heterogeneous system is the inclusion of accelerators with different specific architectures, more specialized to an application field. When an application is suitable for the processor device, an improvement of performance-per-watt is expected. Multiple devices in a system provide the opportunity to utilize concurrency and parallelism, offering the benefits of flexible, well known, and strong optimized tools of CPU devices, with greater energy efficiency from dedicated hardware. Nowadays, CPUs with multicore processor have high performance supporting out-of-order execution, branch prediction and improved SIMD instructions with up to 16 operations on 128 bits of data in one clock cycle [7]. When a CPU alone is sufficient for a target application, the heterogeneous execution would be a waste of power and performance [52]. Offload processing to an accelerator adds communication overhead caused by the limited bandwidth available among devices. Also the CPU acts as a host of the devices, adding control overhead. Choosing the right combination device-application is a challenge and requires a good understanding of accelerator features.

One of the most popular accelerators are the graphic processing units (GPU). GPUs are a many-core architecture with several processing units, following the SIMD(Single Instruction Multiple Data) paradigm. The GPUs were initially oriented to process computer vision algorithms, however, with the evolution of programming languages, this devices are widely used in many other applications. The GPUs can be discrete, connected through a PCIe or NVLink, or it can be embedded with the CPU. Although a tightly coupled GPU improves the data transfer cost, it has fewer processing units because it has less available area, limiting performance [175].

Other devices that have become popular in the last decade are the FPGAs, which were initially used as accelerator in datacenters [14, 134], FPGA offers dedicated hardware dynamically reconfigured with low latency and present one of the most relevant characteristics: high energy efficiency. As GPUs are specialized for dataparallel application, FPGAs fit with streaming data parallelism [67], but they are less common than GPUs since they are more difficult to program.

Aside from the aforementioned devices, there are many other accelerators such as the DSP (digital signal processor) and ASIC (application-specific integrated circuit). Those target specific niches of applications and are less versatile.

Although accelerators are designed for high performance, if they are difficult to program, there is more risk of programming bugs that slow their adoption by the programmers' community. For this reason, programmability is almost as important as high performance. For GPUs, a set of programming languages are available such as OpenMP, OpenCL, and CUDA. Specially CUDA (Compute Unified Device Architecture) from NVIDIA transforms the adoption of GPUs as a general purpose processor easing programming with a set of compilers, tools, libraries, and applications [54]. In FPGAs the programming is more difficult and traditionally uses the RTL design. Similarly to CUDA, for FPGAs emerges the High-Level Synthesis with languages as C/C++, OpenCL, and SyCL to speed up the hardware development[138].

Hardware heterogeneity entails diversity in programming languages, forcing developers to learn unfamiliar tools per each device. Thus, the goal is to hide heterogeneous system complexity and improve programmability. Software abstraction can put away the complexities by specifying frameworks and runtimes to more fully exploit the computing capabilities of each device in the heterogeneous system [52]. Furthermore, the portability of programming languages is one of the most promising features of programming frameworks, where the idea is defining the compute kernels to be executed on the devices and also the host code that orchestrates the execution [138].

Industry is one of the main stakeholders in the development of unified programming languages and standards for heterogeneous systems [36]. One of the initiatives is OpenCL[110], it is a standard framework that promises writing only a single kernel, it can run on a wide range of systems, maximizing the portability and with heterogeneous computing in mind [42]. However, all these features come with tedious host code, and the burden must be assumed by the programmer and the runtime. Also, OpenCL cannot mask differences in hardware architectures, as a consequence, programs do not necessarily run at peak performance, and, hence, each program has to be tuned for each architecture [148].

Even although OpenCL is an advance in programming, the exposition of many low level details makes difficult their extended adoption for average programmers [37, 34]. Other high-level frameworks are developed to increase productivity such as CUDA [13] for Nvidia GPUs and OpenACC [126] a more general standard. OpenACC follows the OpenMP philosophy, the applications are migrated to heterogeneous systems inserting compiler directives, reducing the programming migration effort [47, 149]. OpenCL and OpenACC are the independent programming standards to target accelerators [77]. This was valid until 2014 where the Kronos group, the same that proposed OpenCL, published SYCL standard [138] and the first implementations were spread in 2019. SYCL brings OpenCL compute capabilities to C++. It has grown quickly since SYCL integrates high level libraries and is being broadly adopted in many architectures. At least every year, the research community contributes with the framework advances and compilers for heterogeneous platforms such as: OmpSs [37], Halide [136], VirtCL [173], SnuCL [87], EngineCL [120], ... In general high level of abstraction provides programmers the ability to orchestrate the available devices to choose or share the workload among the available ones.

The device orchestration, typically called load balancing, is based on the concept of use all the compute capabilities available in the computer system to avoid the waste of compute and power resources. This task is not straightforward since the performance of each device depends on the program requirements. Conventionally, the programmer should know the benefits of each architecture and then choose the right platform to run the application. This problem could have many answers and depends on the performance target (time, power, ...)[39]. The Table 2.1 shows

| Characteristic                                                          | CPU | GPU        | FPGA |  |  |

|-------------------------------------------------------------------------|-----|------------|------|--|--|

| Programability                                                          | •   | O          | 0    |  |  |

| Easy optimization                                                       | •   | ●          | 0    |  |  |

| Flexibility                                                             | 0   | Ð          | •    |  |  |

| Transfer overhead                                                       | •   | 0          | 0    |  |  |

| Compute latency                                                         | 0   | O          | •    |  |  |

| Massive Parallel                                                        | 0   | •          | 0    |  |  |

| High Branch Divergence                                                  | •   | lacksquare | 0    |  |  |

| Energy Efficiency                                                       | 0   | O          | •    |  |  |

| <sup><i>n</i></sup> $\bullet$ =The best; $\bullet$ =Medium; O=The worst |     |            |      |  |  |

Table 2.1: CPU, GPU and FPGA characteristics as<br/>accelerators in a heterogeneous sys-<br/>tem, classifying in three categories:<br/>best, worst, and intermediate.

a summary of the main characteristics of the CPU, GPU, and FPGA to expose the diversity and the multi-objective optimization problem for programmers. Some proposals enable CPU and GPU co-execution, [94, 96, 120, 79, 17, 116] others CPU and FPGA co-execution [133, 10, 37, 53, 141], some others combine GPU and FPGA [160], but no so many are already prepared to include more heterogeneity with CPU, GPU and FPGA devices [33, 139].

Current frameworks concentrate their efforts in the promise of single-source programs to be run on the accelerators and also on the host that orchestrates execution [138], unfortunately the achievement of this objective is still a long way off, specially in FPGAs devices which demands more knowledge in architecture design to get the desired best performance per watt.

In the next section, we describe in detail the FPGA, as it is the most relevant device used in this dissertation. We discuss its architecture and its integration as an accelerator conceived to work with heterogeneous languages.

### 2.3 FPGA Device

The field programmable gate arrays (FPGA) are today a powerful platform technology thanks to the increase of the number of computational units along with the number of levels in memory and the processor speed that has occurred in recent years. One of the most significant changes in this time is in the inclusion of the intellectual property (IPs) for digital signal processing (DSP) with floating point operations and the inclusion of modern external memory technologies [168]. The FPGAs are in the middle-ground between general purpose processor(CPU) and pplication-specific integrated circuits (ASICs), often providing better performance per watt in comparison with a CPU, but can be  $35 \times \text{larger}$  and  $4 \times \text{slower}$  than an ASIC implementation [12].

FPGAs are mainly attractive for the programmable routing, which provides a highly flexible architecture for application-specific customized hardware and also allows continuous hardware upgrades. They are composed by columns of reconfigurable logic blocks, DSP blocks, and scalable internal memory [70]. Also, the architecture includes hardware IP units to support peripheral interfaces as: PCIe bus standard, general purpose I/O and external memory. As an example, the Figure 2.1 shows the Intel Stratix FPGA family architecture [71].

The reconfigurable logic core is composed of Logic Array Blocks (LAB) with basic logic blocks known as Adaptive Logic Modules (ALMs). The ALMs contain Look Up Tables-bases (LUT) resources that can be divided between two combinational adaptive lookup tables (ALUTs) and four registers, which can be reconfigured to build logic functions, arithmetic functions, and register functions [70]. Several LABs can work cooperatively through the interconnection network to implement large logic functions.

| e PCIe<br>IP Hard IP<br>Logic Interconnect | DSP Blocks<br>Embedded Memory | controeller, I/0             | Logic Interconnect | DSP Blocks<br>Embedded Memory | Logic Interconnect | Controeller, I/0             | DSP Blocks | Embedded Memory | Logic Interconnect | PCle<br>Hard IP |

|--------------------------------------------|-------------------------------|------------------------------|--------------------|-------------------------------|--------------------|------------------------------|------------|-----------------|--------------------|-----------------|

| PCIe<br>Hard IP<br>Logic Inte              | DSP Embedde                   | HardMemory Controeller, I/0. | Logic Inte         | DSP Embedde                   | Logic Inte         | HardMemory Controeller, I/0. | DSP E      | Embedde         | Logic Inte         | PCIe<br>Hard IP |

Figure 2.1: Intel Stratix 10 internal block diagram architecture.

| Device             | Launch | Transistor | Logic    | DSP    | Embedded | External |

|--------------------|--------|------------|----------|--------|----------|----------|

|                    | Date   | size       | Elements | blocks | memory   | memory   |

| Stratix IV 530     | 2008   | 40nm       | 531200   | 1024   | 27,3 Mb  | DDR2     |

| Stratix V 5SGXA7   | 2010   | 28nm       | 622000   | 256    | 57.2 Mb  | DDR3     |

| Arria GX 1150      | 2013   | 28nm       | 427200   | 1518   | 67.2 Mb  | DDR4     |

| Stratix 10 GX 2800 | 2013   | 14nm       | 2753000  | 5760   | 244 Mb   | DDR4     |

| Stratix 10 MX 2100 | 2017   | 14nm       | 1073000  | 3960   | 239.5 Mb | HBM2     |

| Agilex F014        | 2019   | 10nm       | 1437240  | 4510   | 190 Mb   | DDR4     |

Table 2.2:

Intel FPGAs used in board accelerators.

The performance and energy efficiency capabilities of FPGAs accompanied by programmability changed around the year 2004 with the improvements in High-Level Synthesis had attracted the attention of the programmer's community. This impulsed FPGA adoption from embedded fields using the FPGA like a programmable interconnection technology, to high performance or power-efficient applications, making it part of the system as a hardware accelerator. As an accelerator, the FPGA can be embedded in the SoC tightly coupled to the CPU, or can be a discrete device with PCIe communication and external memory for more data storage.

Discrete FPGAs offer higher compute performance per chip area than embedded ones, fitting better in the HPC domain applications. The evolution of FPGAs acceleration cards started with the Stratix IV from Altera manufacturer. This board is part of Stratix series for high-end performance at low cost. In this devices, one of the first implementations using OpenCL was reported [31, 6, 109], and comparing the performance per watt rations with CPU and GPU, the Stratix IV was around  $5\times$ better [15]. The Stratix V FPGA emerged with transistor size reduction and partial reconfiguration features in 2010 with a 28nm technology [72]. Until 2012, Stratix V was the largest device platform with OpenCL support and evidenced the difference of kernel optimization with other devices, centering the efforts in models and optimization methodologies [50, 162, 53] and acceleration of specific applications [163, 164, 183, 113]. A low end FPGA from Arria family was introduced for discrete boards in 2011 with 20nm technology, it was the first FPGA with hardwired floating point capabilities [12]. Arria family was oriented to data structures applications [86], image processing[151], and artificial intelligence [8, 177]. As in other platforms, the main worries in the application development was the methodology to achieve

a good performance with OpenCL in specific applications [183, 185, 75, 160, 184, 143, 48]

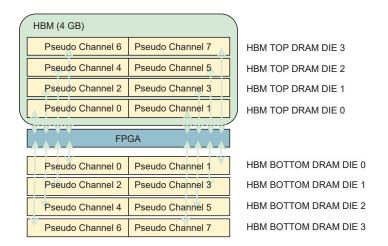

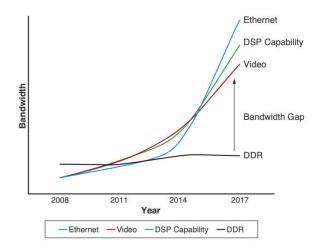

A modern FPGA from the Intel Stratix series is the Stratix 10 with 14nm transistors. Its main novelty was the introduction of the hyper register architecture for high-speed designs [69], achieving a maximum frequency of 500MHz for HLS designs. Also, Stratix 10 MX model was the first FPGA with the modern High Memory Bandwidth (HBM2). The HBM2 is tightly coupled to the die and their interface is composed of multiple banks as Figure 2.2 shows, each HBM bank is completely independent with a 128-bit data bus, operating at DDR data rates. The inclusion of HBM2 memory suppose an increasing of bandwidth and memory I/O interfaces with more power efficiency compared with DDR3/DDR4 memory [61, 107]. Theoretically, in terms of performance Stratix 10 can offer up to 9.2 TFLOPs being this technology near to GPU devices in deep neural applications, compared with the Titan X Pascal with a peak of 11 TFLOPSs, meanwhile Arria 10 offers 1.36 TFLOPSs [123]. The main application focus, as in other areas, is neural networks and stencil computations [23, 41, 185].

As mentioned in the previous section, one of the greatest limitations of accelerators is the communication with the host. As a solution, accelerators should increase the bandwidth among devices. One alternative in discrete FPGAs is to increase the PCIe bandwidth as in Intel Agilex (2019), supporting  $16 \times$  PCIe 4.0, Agilex FPGAs are designed to provide efficiency in AI applications supporting Bfloat operations in DSPs [63]. On another side, the integrated FPGAs into heterogeneous SoCs can solve

Figure 2.2: FPGA with an HBM memory as Intel Stratix 10 MX with 32 pseudo-channels and 8 GB of memory across top and bottom interfaces.

bandwidth issues [20]. Such FPGAs have a processor (ARM Cortex or Intel Xeon) tightly coupled to the FPGA in families such as Stratix 10 and Agilex. A resume of the main FPGA models used in acceleration boards is listed in Table 2.1.

The other main FPGA vendor, Xilinx, uses the same concept of partial reconfiguration for kernel and a static region to implement the communication structure with the host for OpenCL. It offers threes device families with the SDAccel tool to use OpenCL: Virtex-7, Kintex-7, and Kintex-Ultrascale [145]. Virtex architecture. Similarly to Intel, the Kintex is a low end FPGA with a focus on price/performance, instead the Virtex family is HPC oriented, it was the industry's first with  $18 \times 18$  hard multiplier blocks [12]. Furthermore, both vendors share the need of performance models [21, 94] and specific optimizations per application field [83, 137].

#### 2.3.1 FPGA Program Design

As the architecture features, the programmability in FPGAs is crucial and is considered one of their main drawbacks. FPGA design flow is large and complex compared with another processor because of the architecture flexibility.

The main steps of FPGA design comprise [90]:

- 1. Functional design, traditionally with programming models centered on registertransfer level (RTL) or more recently with High level languages.

- 2. Synthesis, the design is translated into circuit elements as a netlist.

- 3. Place and route, this is the implementation performed by the FPGA vendors where the design is mapped on the available resources following the clock and pin assignment conditions.

- 4. Implementation, the generated bitstream is programmed on the device.

At the end of each step of the design flow, verification and simulation should be done.

From a programmer's perspective, the design creation of the microarchitecture is the most time demanding. Programming with hardware description languages (HDL) such as Verilog and VHDL provides programmers the flexibility to make low-level design decisions that can produce high-quality results, however, they are extremely time consuming [26]. In the programming flow, the functional verification needs

a software model and a hardware test bench to simulate and compare with the software model.

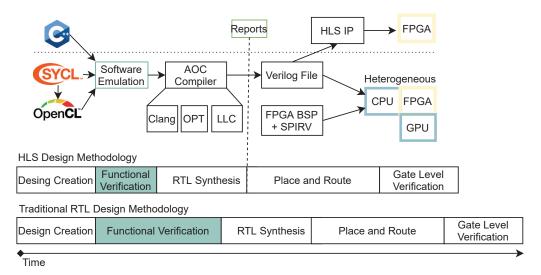

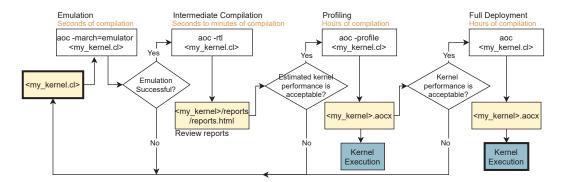

The increasing complexity and hardware resources on FPGA have encouraged the evolution of design abstractions to improve the programmers productivity [99, 95]. The introduction of High-Level Synthesis for FPGAs in commercial tools started in early 2000's. It can often reduce the design effort with more friendly high level languages, from C-extended languages to more high level abstractions to support heterogeneous systems with frameworks as OpenCL, and more recently, over OpenCL, the SyCL framework. The main source of gain using the HLS design flow is the capacity to make faster functional verification compared with the traditional RTL design methodology. With High-Level Synthesis the same program for FPGA is the software test bench, then the verification time could be reduced as the tool design flow for Intel FPGAs in the bottom of Figure 2.3 shows. The compilation details for HLS are part of the section 2.3.2.

Figure 2.3: HLS synthesis tool flow for Intel FPGAs. The lower part compares the timing effort between HLS and traditional RTL design methodologies.

With High-Level Synthesis tools, the programmers can save development time around an order of magnitude because the implementations are more compact, less error prone, and require less hardware expertise. For hardware engineers, High-Level Synthesis tools allow to quickly explore the design space, crucial in the design of complex systems, reducing the time to market [114]. For this reason High-Level Synthesis has been embraced in the programmers community of High Performance Computing (HPC) to develop applications with high performance and power efficiency with FPGAs devices as accelerators.

#### 2.3.2 FPGAs as Accelerator on heterogeneous system

Discrete FPGAs offer high compute performance and match the HPC compute necessities evolving to accelerators. Three parts are identified to couple the FPGA to a host CPU:

- 1. A layer to support and control the communication with host, and external data storage to increase memory capacity typically required in HPC applications.

- 2. The application algorithm.

- 3. The host drivers to support the FPGA transactions.

The partial reconfiguration in FPGAs is an important feature that contributed to the communication and driver support of the FPGA and CPU. Different vendors such as Intel, Bittware, Terasic, and others, provide to programmers a Board Support Package(BSP) which is partially reconfigured on the device in logicLock region in the floorplan for host support with heterogeneous languages as OpenCL and SYCL, including drivers and protocols for communication and programming. The logic region reserved on the chip for the BSP, as for example, in an Stratix 10 FPGA in the Figure 2.1 covers the left side of the FPGA, in gray, for PCIe2 x8 support, and part of the memory controllers, in white. In FPGAs with HBM support, the memory controllers are allocated at the top and bottom of the chip. The free area of the chip is free for programming kernel applications and BSP interconnection.

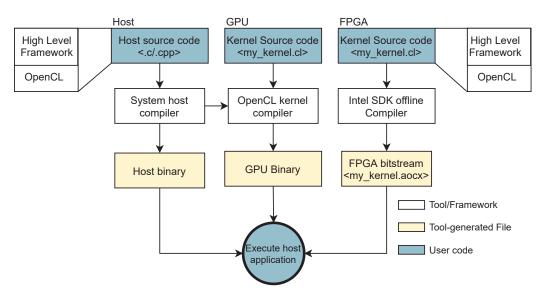

With the lower hardware layer supporting High-Level Synthesis, the application design requires compilation tools as the developed by the Intel FPGA SDK. The AOC compiler, as in other High-Level Synthesis frameworks, rely on LIVM. It uses CLANG front-end to parse the high level code extensions to produce un-optimized LIVM IR, the middle-end performs optimizations with compiler passes. Finally, on the back-end, the compiler instantiates Verilog IPs [166]. In this step, the designer can analyze the hardware blocks to be generated during placement and routing stages. After Verilog transformation, two ways are possible, as Figure 2.3 shows. The first is to generate hardware IP Blocks from C/C++ code that can then be interfaced to the BSP later, as in the OpenVX proposal in Chapter 5. The second path is to generate

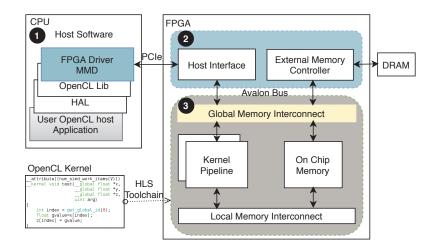

**Figure 2.4:** Main elements of OpenCL BSP for FPGAs. **1** and **2** represent the BSP, and **3** the kernel logic.

kernels directly coupled to the BSP to use the FPGA as an accelerator, such as the kernels synthesized with OpenCL and SyCL.

The BSP and the kernel pipeline composed an FPGA accelerator, and internally they have their own architecture and components described in detail in the next subsection 2.3.2.

#### Kernel pipeline and Board Support Package

The kernel pipeline is part of the total architecture of the FPGA as accelerator, since OpenCL was the first heterogeneous language used for programming FPGA and it is the most extensively used. In this section, as in the Figure 2.4, we present the main components of an OpenCL application using the Intel FPGA SDK for OpenCL as a reference. Without loss of generality, this flow also represents other toolchains (e.g., SYCL). On the host side, **①**, the application communicates with the FPGA device through the board support package <sup>1</sup> (BSP, in blue on the figure). A BSP implements the lower layers of the application stack such as the memory-mapped device (MMD) library, performing the basic I/O with the board, and the PCI express (PCIe) communications. On the FPGA side, the BSP, **②**, provides support to communicate back with the host, and with the device memory, DRAM and external devices.

<sup>&</sup>lt;sup>1</sup>Manufacturers often provide BSP, but advanced users can tune and re-implement them.

From a programmer's perspective, the most important component in a BSP is the kernel logic, **③**, which corresponds mainly to the compiled OpenCL kernel. In fact, programmers seldom need to generate a new BSP<sup>2</sup>. The compilation process consists of two main steps (without lost of generality, OpenCL is used as example). First, a translator generates HDL code from the OpenCL, and second, a synthesis tool generates the bitstream. The translator creates four blocks from the code: local memory interconnect (LMI), on-chip memory, the kernel pipeline, and global memory interconnect (GMI). The last two blocks are the ones that most critically affect performance, and therefore, they are described as part of the study of this dissertation in Chapter 4.

The major vendors of FPGAs, Xilinx and Intel, have developed their HLS compilers to generate pipeline architectures. The main advantage of this strategy is the amount of parallel operations that are executed per clock cycle, splitting the operating with registers, avoiding computation stalls. Splitting up the processing into small pipeline stages also helps to reach higher frequencies, improving kernel and memory performance [138].

In terms of parallelism, the deeper the pipeline is, the greater the number of items that can simultaneously advance. As a result, the FPGA performance mainly depends on two pipeline characteristics: initiation interval and frequency. Initiation interval is the number of clock cycles between two consecutive kernel work-items start, and frequency is the cycle time of the longest pipeline stage.

Although with HLS the programmers uses common languages for CPU and GPU devices the optimization and programming patterns [162, 106] are different. FPGA kernels require detailed annotations to guide the hardware generation, and since the synthesis process is time expensive, the optimization should be done in an intermediate stage, after Verilog generation, called "intermediate compilation". In this phase the designer can analyze the hardware blocks to be generated during place and route stage. Depending of the compiler heuristic and together with the fact that the vast majority of software is not designed for FPGA synthesis [95], makes HLS difficult to adopt. For this reason, the "intermediate compilation" based on reports, is one of the noticeable advances in HLS helping to improve productivity allowing to analyze the generated IP blocks.

<sup>&</sup>lt;sup>2</sup>Also note that HLS tools would always require a BSP to compile an OpenCL kernel for supporting the aforementioned low-level tasks.

# **Experimental Framework**

# 3

This thesis comprises several studies that were carried out with multiple heterogeneous systems using several programming models, such as OpenCL or OpenVX, running on a host CPU with accelerators, mainly FPGAs and, in some cases, in combination with a GPU.

This chapter presents a general overview of the software and hardware frameworks together with the general methodology used for modeling, running the experiments, and computing relevant metrics such as throughput, portability, and load balancing. Since the results are extracted from different compilation stages in the FPGA compilation flow and high level frameworks, specific details change and are detailed in each Chapter's methodology section.

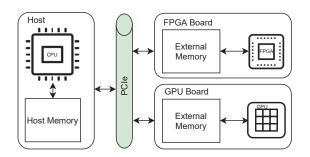

# 3.1 Evaluation Hardware

The heterogeneous systems used in this work consist of a host CPU connected to one FPGA, or one FPGA plus a GPU device as Figure 3.1 shows. In these systems, the devices are connected to the CPU through an external PCI-express (PCIe) bus, and they are common in HPC computing systems.

Four heterogeneous systems have been set up to carry on all the experiments. Table 3.1 shows their configurations based on three host CPUs, listed in Table 3.2,

Figure 3.1: Heterogeneous system with an FPGA board and a CPU.

|        | FPGA Board    | GPU Board | In Chapter |

|--------|---------------|-----------|------------|

| Host 1 | DE5-net       | TITAN X   | 6          |

| Host 3 | Stratix 10 GX | -         | 4 and 5    |

| Host 2 | Stratix 10 MX | -         | 4          |

| Host 3 | Stratix 10 MX | -         | 5          |

Table 3.1: Device combinations used as heterogeneous system in this thesis. The host, FPGAand GPU capabilities are described in Tables 3.2, 3.4, and 3.3.

combined with three FPGA boards in Table 3.4, and one GPU in Table 3.3. The CPU only acts as a host in Chapters 4 and 5, while in Chapter 6, it is considered as another device.

Communication is a key factor in heterogeneous systems' design, and it is the main reason for the multiple combinations used in this work. The PCIe bus allows to connect diverse device architectures through a high-speed serial bus commonly used in motherboard interfaces. Although CPUs and motherboards offer many PCIe port expansions, not all are available to match the maximum bandwidth capabilities of each device. In fact, the first combination used for load balancing with three devices (Host 1, Table 3.1), connects both the FPGA and GPU with 8 lanes, even if the GPU supports 16 lanes, because of the CPU-chipset-motherboard ensemble limitations.

Upgrading the FPGA or the host may not always be enough to overcome these communication issues, and two factors can still prevent to reach the maximum bandwidth. First, as FPGA board increase dimensions, they require a larger space in the motherboard, and depending on the board layout, they can block required PCIe ports to connect other accelerators. Second, the BSP and OpenCL drivers support is limited in some devices. For example, in order to improve device communication performance, the Host 2 was configured with an AMD processor, but this processor had incompatibilities with Intel FPGA PCI drivers and the PCIe OS support should be emulated, reducing the PCIe throughput. Also AMD processors are not yet officially supported by Intel OpenCL SDK.

Host 3 aims for full compatibility with Intel FPGA devices using a CPU manufactured by Intel. This system has more PCIe capabilities with 4 PCIe ports with 16 lanes, but since motherboard implements switch/multiplexation of CPU PCIe lanes, the

| Feature  |              | Host 1    | Host 2        | Host 3           |

|----------|--------------|-----------|---------------|------------------|

|          | Manufacturer | Intel     | AMD           | Intel            |

|          | Model        | i7-6700k  | Ryzen 1920X   | Xeon Bronze 3204 |

| CPU      | Cores        | 8         | 12            | 6                |

|          | Launch date  | 2015      | 2017          | 2019             |

|          | Frequency    | 4 GHz     | 3.4 GHz       | 1.9 MHz          |

| Mother-  | Manufacturer | ASUS      | Micro-Star    | Supermicro       |

| board    | Model        | Z170-PRO  | X399 SLI PLUS | X11SPA-TF        |

|          | Туре         | DDR4      | DDR4          | DDR4             |

| External | Bw. per bank | 17.1 GB/s | 17.1 GB/s     | 17.1 GB/s        |

| Memory   | Capacity     | 64 GB     | 96 GB         | 96 GB            |

|          | Banks        | 4         | 6             | 3                |

|          | Connector    | DIMM      | DIMM          | DIMM             |

| OpenCL   | Version      | 2.0       | -             | 2.0              |

| OS       | Distro       | CentOS 7  | CentoOS 7     | CentoOS 7        |

|          | Kernel       | 3.1       | 3.1           | 3.1              |

Table 3.2:

Main characteristics of the three host systems.

OpenCL FPGA driver does not work <sup>1</sup>. The driver needs direct interconnection to the CPU processor and only one slot position is directly connected, the rest has a switching chip, leaving available one slot for FPGA, limiting the addition of more heterogeneity with more FPGA devices.

On the device side of the heterogeneous system, we used a TITAN X GPU from NVIDIA. This GPU has a Maxwell architecture manufactured with 28 nm technology, and Table 3.3 shows its main features. Compared with the rest of used devices used, this GPU is the most powerful in terms of raw floating-point compute power with 6.6 TFLOPS in single precision given by this equation  $Frequency \times Cores \times 2$  where 2 are the multiply-add operations effectively support for floating point unit (FPU) in each CUDA core. The reported bandwidth is limited by host PCIe lanes and was measured with CUDA bandwidth test. The driver support is highly reliable since its a high end product that has been in the market for a while. It provides CUDA and OpenCL support with runtime compilation of kernel programs.

<sup>&</sup>lt;sup>1</sup>A personal communication with Intel engineers confirms the PCIe driver limitations

| Feature         |                     | GeForce Titan X     |

|-----------------|---------------------|---------------------|

|                 | Manufacturer        | NVIDIA              |

|                 | Cores               | 3072                |

| GPU             | Frequency           | 1.1 GHz             |

|                 | Peak Floating Point | 6.6 TFLOPS          |

|                 | Туре                | GDDR5X              |

| External Memory | Bandwidth           | 480 GB/s            |

|                 | Capacity            | 12 GB               |

|                 | Bandwidth           | 6500 MB/s (8 lanes) |

| PCIe            | Lanes               | 16                  |

|                 | Gen.                | 3                   |

| Board           | Dimension           | 2-slots             |

| OpenCL          | OpenCL Version      | 3.0                 |

Table 3.3:

Characteristic of NVIDIA GeForce GTX TITAN X GPU board.

The other device coupled to the host has been several different FPGAs. Namely, in this work, we have worked with three FPGA board models that were upgraded during the development of this thesis. All of them belong to the Intel Stratix family: Stratix V, Stratix 10 GX and MX. The details of each board are shown in the Table 3.4. The PCIe bandwidth was measured with the board test of each BSP board. The FPGA models evidence the evolution of the FPGA boards, increasing PCIe bandwidth  $4 \times$ , the amount of DSP resources 22  $\times$ , and memory bandwidth 16  $\times$ , comparing the best and worst FPGA features. The FPGA peak FLOPS in single precision are calculated as  $DSP\_Frequency \times DSP\_blocks \times 2$  where 2 is the amount of FLOPS per clock cycle in each DSP block at a rated speed of 450 MHz [101].

FPGA boards and BSPs to support FPGA OpenCL SDK are development kits designed for evaluation proposes provided by Terasic for the Stratix V board and directly from Intel for the two Stratix 10. For most experiments the BSP wasn't recompiled, but an in-house BSP was compiled for the Stratix 10 GX to boost the DDR4 memory data rate from 1866 to 2666 MT/s, the maximum supported by the hardware. This change required to update timing settings of the memory controller in the static part of the BSP based on the memory speed-bin table in data-sheet [102]. Timing adjustments in BSP required a two-step compilation for custom board design [64]. First, a

|                     | DE5-net                                                                                                                                                                                  | Stratix 10 GX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Stratix 10 MX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family              | Stratix V                                                                                                                                                                                | Stratix 10 GX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Stratix 10 MX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Model               | 5SGXA7                                                                                                                                                                                   | 2800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Logic Elements      | 622000                                                                                                                                                                                   | 2753000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1073000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Embeded Memory      | 57.2 Mb                                                                                                                                                                                  | 244 Mb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 239.5 Mb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DSP                 | 256                                                                                                                                                                                      | 5760                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3960                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

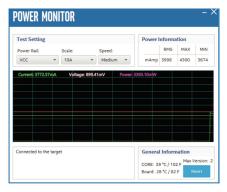

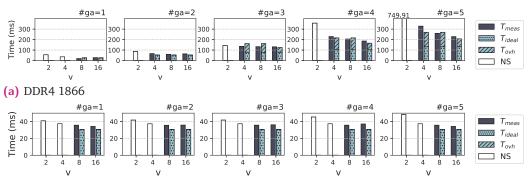

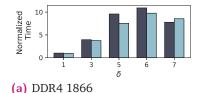

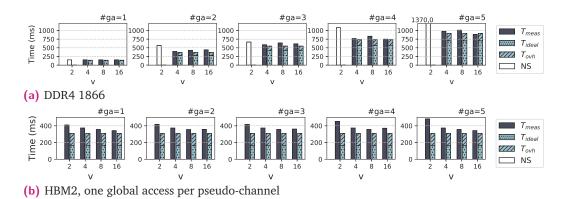

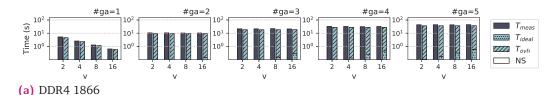

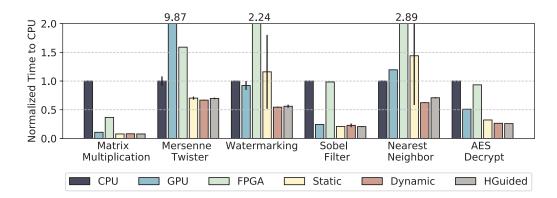

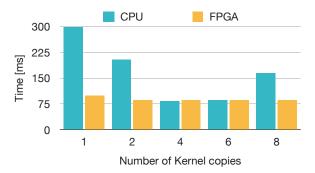

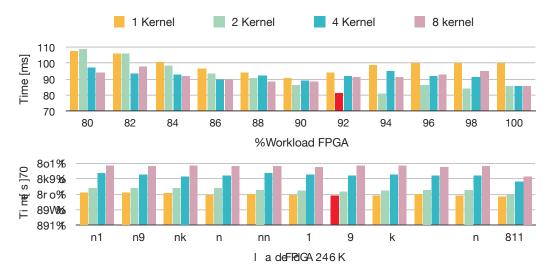

| Peak Floating Point | 0.2 TFLOPS                                                                                                                                                                               | 5.1 TFLOPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.6 TFLOPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |