## **MASTER'S THESIS**

### Happy-flow verification of Cyber-Physical Systems

Ketelaar, J.

Award date: 2022

Link to publication

**General rights** Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain.

You may freely distribute the URL identifying the publication in the public portal.

#### Take down policy

If you believe that this document breaches copyright please contact us at:

#### pure-support@ou.nl

providing details and we will investigate your claim.

Downloaded from https://research.ou.nl/ on date: 19. Nov. 2022

### HAPPY-FLOW VERIFICATION OF CYBER-PHYSICAL SYSTEMS

by

### Jildert Ketelaar, MSc

in partial fulfillment of the requirements for the degree of

**Master of Science** in Software Engineering

at the Open University of the Netherlands, Faculty of Science Master's Programme in Software Engineering to be defended publicly on Friday March 25, 2022 at 11:00 AM.

| Student number:   |                                           |                        |

|-------------------|-------------------------------------------|------------------------|

| Course code:      | IM9906                                    |                        |

| Thesis committee: | Dr. Stefano Schivo (chairman/supervisor), | <b>Open University</b> |

|                   | Dr. Freek Verbeek (secondary supervisor), | <b>Open University</b> |

|                   | Dr. Jacques Verriet,                      | ESI (TNO)              |

## **CONTENTS**

| Su | immary                                                                                                                                                                                                                                                                                                                                                                    | iv                                                                                                         |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1  | Introduction1.1Conquer the state space explosion1.2System under test: High speed Die Attach machine1.3Goal of the research1.4Research context1.5Structure of the report                                                                                                                                                                                                   | 1<br>2<br>2<br>3<br>4                                                                                      |

| 2  | Background         2.1       Formal verification         2.1.1       Formal specification         2.1.2       Formal modelling.         2.1.3       Model checking         2.2       Uppaal.         2.2.1       Concepts & Syntax         2.2.2       Model verification         2.3       Source code to model translation.         2.4       Model Driven Engineering. | 5<br>5<br>6<br>7<br>8<br>9<br>9                                                                            |

| 3  | Related Work3.1Model checking of source code3.2Program Slicing3.3Research contribution                                                                                                                                                                                                                                                                                    | <b>12</b><br>12<br>14<br>14                                                                                |

| 4  | Method4.1Research questions4.2Research method                                                                                                                                                                                                                                                                                                                             | <b>15</b><br>15<br>16                                                                                      |

| 5  | What to verify on the 'Happy Flow'?5.1Definition of happy flow                                                                                                                                                                                                                                                                                                            | <ol> <li>17</li> <li>17</li> <li>17</li> <li>18</li> <li>18</li> <li>19</li> <li>19</li> <li>19</li> </ol> |

| 6  | 'Happy Flow' extraction6.1 Determine the happy flow6.2 Instrumentation6.3 Executing the happy flow                                                                                                                                                                                                                                                                        | <b>20</b><br>20<br>21<br>22                                                                                |

|    | 6.4  | Processing coverage data                                                  |

|----|------|---------------------------------------------------------------------------|

|    |      | 6.4.1 Gcov 22                                                             |

|    |      | 6.4.2 Gcovr and Cobertura                                                 |

|    | 6.5  | Ada Metamodel                                                             |

|    | 6.6  | Generate the intermediate representation                                  |

|    |      | 6.6.1 Package body                                                        |

|    |      | 6.6.2 Subprocedure body                                                   |

|    |      | 6.6.3 Expression Function                                                 |

|    |      | 6.6.4 Task Body                                                           |

|    |      | 6.6.5 Accept statement                                                    |

|    |      | 6.6.6 Select statement                                                    |

|    |      | 6.6.7 Call expression                                                     |

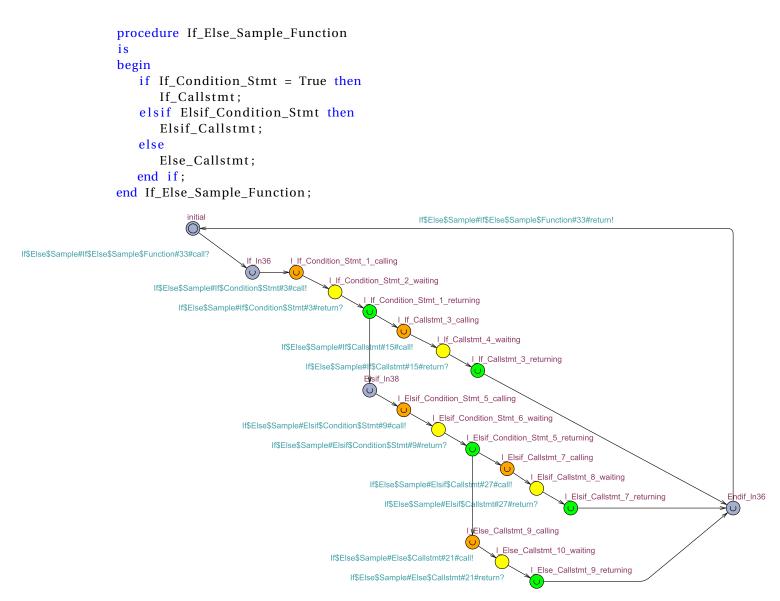

|    |      | 6.6.8 If statement                                                        |

|    |      | 6.6.9 Identifier type                                                     |

|    |      | 6.6.10 Case statement                                                     |

|    |      | 6.6.11 Loop statements                                                    |

|    |      | 6.6.12 Return and Delay statements                                        |

|    | 6.7  | Resulting model                                                           |

| -  | Down |                                                                           |

| 7  |      | nal model generation 37                                                   |

|    | 7.1  | Transformation concept   37     7.1.1   Madal to Madal to Madal to mation |

|    |      | 7.1.1 Model-to-Model transformation                                       |

|    | 7.0  | 7.1.2 Model-to-Text transformation                                        |

|    | 7.2  | Linking calls and implementations                                         |

|    |      | 7.2.1 Subprocedure calls                                                  |

|    | 7.0  | 7.2.2 Accepts, Events and Mutex linking                                   |

|    | 7.3  | Transformation step-by-step   41                                          |

|    |      | 7.3.1 Subprocedure transformation                                         |

|    |      | 7.3.2 Task transformation                                                 |

|    |      | 7.3.3 Statement transformation                                            |

|    | 7.4  | The full Uppaal model    46                                               |

| 8  | Form | nal verification 49                                                       |

|    | 8.1  | Deadlock                                                                  |

|    | 8.2  | Reachability analysis                                                     |

|    | 8.3  | Liveness analysis                                                         |

| ~  |      |                                                                           |

| 9  |      | ussion 51                                                                 |

|    |      | Validation                                                                |

|    | 9.2  | Results                                                                   |

|    | 9.3  | Strengths & Limitations                                                   |

| 10 | Con  | clusions & Future work 57                                                 |

|    | 10.1 | Summary                                                                   |

|    |      | Recommendations                                                           |

|    |      | Future work.   59                                                         |

|    |      |                                                                           |

| 11 Reflection            |    |

|--------------------------|----|

| Bibliography             | i  |

| A Ada intermediate model | iv |

## **SUMMARY**

Cyber-Physical Systems (CPSs) are systems where physical components are controlled by computational components, e.g. computers or micro-processors. Since the early days of the introduction of computers, cyber-physical systems are increasingly around in our day-to-day life and getting more and more complex.

In order to make sure that these systems always do what they are intended to do, validating the software running on these systems is of paramount importance, as very high costs or even human lives can be at stake.

A promising technique to test software is formal verification. Formal verification aims at proving properties on the code such that it is guaranteed that a property holds on the system, in contrast to other testing methods where no guarantees can be given.

One of the main disadvantages of formal verification is the so-called state space explosion. This means that the number of possible system states reaches huge numbers, especially for concurrent systems where parallel processes interact with each other.

In order to limit the state space size and thus potentially enable formal verification on CPSs, we abstract parts of the original source code away. Our approach is to automatically extract the happy-flow code of our CPS and apply verification on this part of the code only. Our main research question is stated as: *To what extent is it possible to prove formal properties on the 'happy flow' code of a real-time, concurrent cyber-physical system with a high ratio of repetitive tasks*?.

During our research a method is developed to automatically extract the happy-flow code by using code coverage tooling. The CPS is executed in a nominal way and by checking how many times each line of code is executed it is found what code is initialization or error handling code, and what code is part of the happy flow.

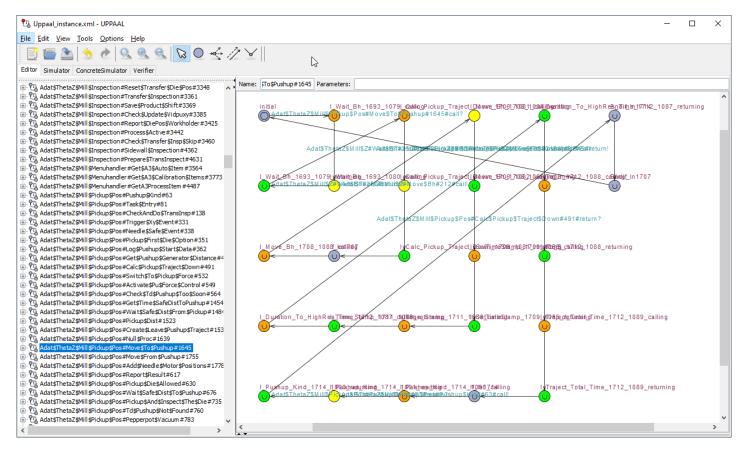

We designed a tool which translates the happy-flow code into an intermediate representation, or model, of the source code. By means of model-driven engineering, a modelto-model transformation has been created which subsequently transforms the model of the source into an Uppaal model.

Uppaal is a model checker which can be used to check properties on a formal model. Using the method and tooling developed during our research, a working Uppaal model of our cyber-physical system can automatically be generated. This makes the modelling process quick and removes the risk of human mistakes compared to creating a model manually.

Some simple properties have successfully been verified on the model, proving that the model mimics the behaviour of the CPS. However, verifying more complex properties still run into the state explosion problem. It is expected that improvements on our work can lead to a better approximation of the source code, which will result in a smaller state space, thus enabling the verification of more complex properties.

1

### **INTRODUCTION**

Cyber-Physical Systems (CPSs) are systems where physical components are controlled by computational components, e.g. computers or micro-processors ([National Science Foundation, 2021]). Since the early days of the introduction of computers in the second half of the 20th century, cyber-physical systems are increasingly around in our day to day life and getting more and more complex.

In order to make sure that these systems always do what they are intended to do, validating the software running on these systems is of paramount importance. As can be imagined, very high costs are at risk when for example a robot cell destroys a valuable workpiece, or even human lives are at stake when looking at computer controlled aerospace systems.

Therefore, in parallel to the rise of software development tools, also a wide range of software testing methods was, and still is being, developed, think of unit testing, system testing, black-box testing, white-box testing, static testing, dynamic testing, etc.

One of the approaches which has been around for quite some time but which is still not mainstream in the software industry is testing by means of formal verification [Bjesse, 2005][Wayne, 2019]. A major benefit of this approach is that it can be automated, but the main reason not being used widely is that it does not scale well for larger or complex systems.

The research carried out in this thesis aims at finding a method to create a formal model of complex CPSs with a high ratio of repetitive and concurrent tasks, while limiting the model size by only looking at the 'happy flow' of the CPS, ultimately to lower the threshold for industry to use formal verification. Therefore our main research question is defined as:

To what extent is it possible to prove formal properties on the 'happy flow' code of a real-time, concurrent cyber-physical system with a high ratio of repetitive tasks?

### **1.1.** CONQUER THE STATE SPACE EXPLOSION

A good introduction to model checking, past developments and the limitations due to the state space explosion is given by Clarke et al. [2012]. As indicated by the authors, a main limitation of formal verification is the tremendous number of states a software program can be in, especially for concurrent systems where different processes run in parallel and interact with each other. Even for an average sized concurrent program, the state space easily grows to numbers where formal verification is not possible anymore.

In order to conquer the state space explosion it can either be tried to design faster verification methods and tools, but it can also be tried to limit the number of states in the model. A lot of research has been conducted on the former option, which resulted for example in tools using symbolic verification methods instead of explicit methods.

In order to reduce the number of states in the model, different options have been used in the past, like removing unused variables or data, limit the possible values of variables, techniques like partial order reduction and symmetry reduction, or abstract away parts of the system behaviour.

Our research focuses on the latter option, i.e. abstract away parts of the system behaviour. By means of filtering the happy-flow code from the full code base, the non-happy flow is abstracted away and the number of states in the model is reduced.

The 'happy flow' is defined here as the nominal machine cycle without interference from the outside world. For the kind of machines with a high ratio of repetitive tasks targeted in this research, it is expected that less than 20% of the source code is used for the happy flow. Therefore a significant state space reduction can be achieved.

### **1.2.** System under test: High speed Die Attach machine

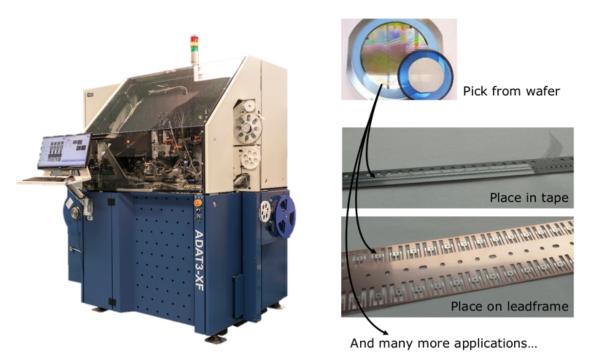

The research described in this document will be carried out in the context of the software development for a high speed die attach machine: Itec's Adat3-XF<sup>1</sup>, shown in Figure 1.1. This Cyber-Physical System is used for the production of semiconductor chips, and picks dies (bare chips) from a wafer and places the dies on a substrate.

The heart of the machine is the *transfer mill* which is a rotating device with multiple *pick & place heads*. On the backside of the wafer there is a *needle* which pushes a single die on the wafer a little bit up. A pick & place head picks the die from the wafer and places it on a substrate a few cycles later. The wafer is held in place by a *wafertable* which indexes the wafer in x and y direction. Furthermore multiple cameras are present in the machine inspecting a product before, between and after it has been picked and placed.

The machine is controlled by a single computer running software written in the programming language Ada. The software contains many real-time parallel processes, e.g. picking, transferring, inspecting, and placing a die, with *real-time* being in the order of microseconds. A full machine cycle takes around 75 milliseconds, and within each cycle many synchronisations between the different processes occur.

Due to the critical production process, formal verification of the software would add a lot of value to guarantee the correct working of the machine. However, because of the complexity of the software and the number of concurrent processes, it is assumed that a direct translation from the source code to a formal model will result in way too many states for formal verification to be possible. Therefore some attempt should be made to reduce the number of states.

### **1.3.** GOAL OF THE RESEARCH

The goal of this research is to come up with a method which makes it possible to apply formal verification on the code of a complex cyber-physical system with a high ratio of repetitive tasks, without running into the state space limits of the available verification tools. In order to do so, a compromise is needed to limit the number of states which in this research

Figure 1.1: Left: Itec's Adat3-XF Die Attacher; Right: The application of the machine, pick chips from a wafer and place them e.g. in tape or on a leadframe.

will be done by only looking at the source code of the nominal machine cycle or 'happy flow' of the machine.

As stated, filtering the source code is a compromise because not all system behaviour is present anymore. Therefore the model becomes an under-approximation of the complete system. As a result when a formal property holds on the model, it cannot be guaranteed that this property also holds for the complete system. However, guarantees can be made the other way around, when a formal property does not hold on the model, it is guaranteed that the property will also not hold for the complete system.

For the developed method to be usable in an industrial environment, the tooling should do as much as possible in an automatic fashion such that no in depth knowledge of formal verification and model checking is required.

### **1.4.** RESEARCH CONTEXT

This research is conducted as a graduation project for the master Software Engineering of the Open University. As the context for this project it is chosen to use the working environment of the author, i.e. the Adat3-XF machine of Itec such that a close relation between the research and the industry is established. At the same time ESI (TNO) carries out a project at Itec aiming at modelling the machine cycle of the Adat and improving the software and software development methods, in parallel to our research. The methods developed during our research can help to bridge ESI's efforts in modelling the machine cycle with foreseen improvements on the source code of the machine.

### **1.5. STRUCTURE OF THE REPORT**

This thesis is structured as follows: Chapter 2 gives some background information on different subjects used throughout the research. Chapter 3 presents an overview of research related to our research and the contribution of our research. The main research question is divided into different sub questions which are given in Chapter 4, along with the research method per sub question. Chapters 5, 6, 7 and 8 describe the performed research per sub question. Chapter 9 discusses the validation and results of our research and summarizes the strengths and limitations of the work. The final conclusions and recommendations are given in Chapter 10. Finally Chapter 11 gives a personal reflection on the research and the process.

## 2

### BACKGROUND

This chapter introduces different concepts and tools which are used throughout our research. If the reader is already knowledgeable on these subjects, the specific section can be skipped.

### **2.1.** FORMAL VERIFICATION

Formal verification is about trying to mathematically prove specifications or properties on a given system [Bjesse, 2005] [Clarke et al., 2012]. This is done by finding a formal proof on a mathematical model of this system. Typically the abstract mathematical models are constructed by means of finite state machines which unambiguously describe the behaviour of the system.

In order to prove properties on a system three steps need to be taken: (1) formally specifying properties of the system, (2) creating a formal model of the system, and (3) assessing whether the formal model behaves as described by the formal specification, also called verification or model checking [Clarke and Emerson, 1982]. The three steps are further described below.

### **2.1.1.** FORMAL SPECIFICATION

Step one in the process of formal verification is specifying formal properties which describe the intended behaviour of the system. In order to reason about a formal model, some form of logic is required. When also the order of events should be considered, which is typically the case for Cyber Physical Systems, temporal logic gives the tools required.

Several kinds of temporal logics have been developed over the years, of which the most important ones are Linear Temporal Logic (LTL) [Pnueli, 1977] and Computation Tree Logic (CTL) [Clarke and Emerson, 1982]. Later, [Clarke et al., 1986] defined CTL\* which is a superset of both LTL and CTL, combining linear and branching temporal logic.

CTL\* formulas have both a path quantifier and a temporal operator. Two path quantifiers are used, specifying either all computation paths **A** or at least one path **E**. The temporal operator describes properties which hold along the path as specified by the path quantifier. CTL\* has 5 of these temporal operators

- $\mathbf{X} p$  in the next state, p holds

- $\mathbf{F} p$  eventually p holds

- **G** p p holds Globally

- $p \mathbf{U} q$  eventually q holds, and until then p holds

$p \mathbf{R} q$  p releases q, or q always holds

Now formal specifications can be given like AG(p) meaning p holds in all states of all execution paths. Combinations of CTL\* operators are also possible, one of the most common combination is  $AG(p \Rightarrow AF(q))$  which denotes the so called liveness property. This property evaluates to: for all execution paths, whenever p holds, then eventually q holds.

By means of CTL\* the following formula could for example be defined:

$$AGEF(p) \tag{2.1}$$

This formula means: for all states of all execution paths it is true that there is an execution path where eventually *p* holds.

### **2.1.2.** FORMAL MODELLING

Software programs are typically described by a model where each position in the program is described by a state. The program can go from one state to another in response to certain inputs. When the set of states of the program is finite, such a model is called a finite state machine or automaton [Rabin and Scott, 1959].

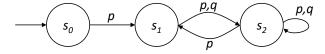

One way to describe finite automata is by means of Labelled Transition Systems [Burkart et al., 2001]. These systems have a finite set of states and between the states, transitions are given which define how the system can go from one state to another. Each transition is labelled by a proposition which should hold in order to take the transition. Figure 2.1 shows such a finite automaton of three states and proposition p and q.

Figure 2.1: Finite automaton or Labelled Transition System

Assume Formula 2.1 is rewritten to  $AGEF(s_2)$ , meaning that from all states of all execution paths eventually state  $s_2$  can be reached. When this formula is applied to the automaton of Figure 2.1 it is found that the formula holds on this state machine because from each state it is possible to reach the state  $s_2$ . Note that the formula  $AGEF(s_0)$  does not hold on this system because from state  $s_1$  and  $s_2$  it is not possible to reach state  $s_0$ .

**Timed Automata** In order to reason about asynchronous timed systems, it is required to add a notion of time to the models of these systems. For this purpose [Alur and Dill, 1994] introduced the concept of Timed Automata. Timed automata are finite automata extended with a finite set of clocks representing continuous time. Clocks are declared by clock variables which are read-only except for resetting to zero. The value of the clock is the time since the last reset of the clock. Note that in timed automata, the state of the system is resembled by the 'location' of each automaton in the system and the value of all clocks in the system. Therefore in timed automata, instead of 'state', the term 'location' is used to denote a node in the automaton.

Now transitions between locations can have clock guards which define at which value of the clock the transition is valid. Besides transitions, locations can contain constraints about clocks as well; called an invariant. The invariant defines for what values of a clock it is allowed to be in that location. Furthermore a clock can be reset on a transition. If with the next time value it is not allowed to be in a certain location, a transition to another location has to be made, when this is not possible a deadlock situation is reached. It is assumed that transitions are instantaneous, hence time only progresses in locations, it is furthermore assumed that all clocks run at the same rate.

To be able to model concurrent processes, different timed automata can synchronize with each other on actions. For this purpose, transitions can be labelled with actions. When two automata have a transition with the same action, the automata need to wait to make the transition until both automata can take the transition at exactly the same time.

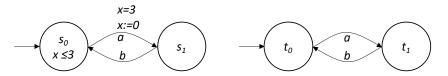

Figure 2.2: Two timed automata which synchronize on an *a* and *b* action

Figure 2.2 shows two timed automata with a clock x. They both start in their initial location, with clock variable x = 0. As soon as x reaches the value of 3, the left automaton is not allowed to stay in  $s_0$  any longer and needs to take the transition to  $s_1$ . This transition was also not allowed to be taken earlier due to the clock guard x = 3. Furthermore the clock variable x is reset to 0 during the transition. Because the two automata synchronize on a, as soon as the left automaton goes from the left to the right location, the right automaton does the same. Note that the automata are allowed to stay infinitely long in  $s_1$  and  $t_1$  respectively, but as soon as one of the automata takes the transition back, the other one will do the same due to the synchronization on b.

### 2.1.3. MODEL CHECKING

By having a formal specification language and a formal modelling method it is possible to verify whether the model satisfies the formal specification. Hence the question is, does model *M* satisfy formula *f*, or:  $M \models f$ .

Different algorithms have been developed to perform this step, both in an explicit and a symbolic manner. But as in both cases the verification is a matter of running the algorithm, a lot of tooling is developed to perform this step automatically. Well known tools are e.g. SPIN<sup>1</sup> ([Holzmann, 1991]), NuSMV<sup>2</sup> ([Cimatti et al., 2002]) and UPPAAL<sup>3</sup> ([Behrmann et al., 2006]). Uppaal is specifically designed to verify Timed Automata and features an easy-to-use interface to construct and check models.

### **2.2. U**PPAAL

For the research given in this thesis it will appear that Uppaal fulfills the requirements we have for a model checking tool. This section describes some more background on Uppaal

<sup>&</sup>lt;sup>1</sup>http://spinroot.com

<sup>&</sup>lt;sup>2</sup>https://nusmv.fbk.eu/

<sup>&</sup>lt;sup>3</sup>https://uppaal.org/

and the way to use it, in order to better understand the rest of this research.

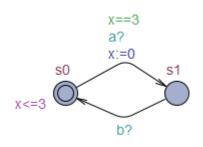

Uppaal is specifically designed to model and verify Timed Automata. Figure 2.3 shows the left automaton of Figure 2.2, using Uppaal notation.

Figure 2.3: An example showing the left automaton of Figure 2.2 in Uppaal

### 2.2.1. CONCEPTS & SYNTAX

This section gives a quick introduction to the concepts and syntax of Uppaal.

#### TEMPLATES

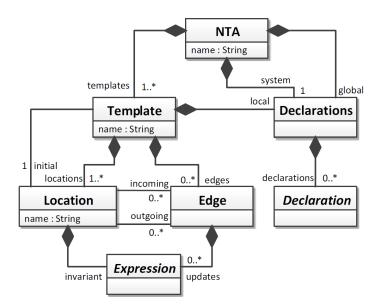

A system as defined in Uppaal is composed of a network of timed automata (NTA), with all automata running in parallel. An automaton in Uppaal can be instantiated multiple times with different parameters when desired, therefore an automaton definition in Uppaal is referred to as a *Template*.

A template is composed of *locations* shown as nodes, and *edges* representing the transitions between the locations.

### LOCATIONS

Figure 2.2 shows two nodes which are locations s0 and s1 of the automaton. An important property which can be given to a location is the invariant; an expression which should always hold in order for the system to be allowed to be in that state. Note that invariants are optional, in Figure 2.2 s0 has invariant x<=3 while s1 has no invariant.

One of the locations in an automaton should be marked as the initial state. In Uppaal this is visualized by the double circle. Referring again to Figure 2.2, location s0 is the initial state of this template.

Lastly there are two more optional properties for a location, being Urgent and Committed, note that a location can either be urgent or committed, not both. An urgent location represents a state of the system in which it is not allowed for time to pass. Before time is allowed to pass again, one of the outgoing transitions should be taken. Because of this, the state space of the model is largely reduced.

Committed locations go one step further compared to urgent locations and do not allow other processes to perform any (non-committed) transitions before an outgoing transition of the committed location is taken.

#### EDGES

Edges represent directed transitions from one location to another. Like locations, edges can be given different optional parameters to control the behaviour of the edge. These options are explained below.

**Synchronization** Edges can be given a synchronization label. This label identifies a synchronization channel which is used to synchronize processes with each other. A synchronization label can either be of the form e? or e! where the question mark defines the receiving end of the channel and the exclamation mark the sending end of the channel. It is like a rendezvous between two concurrent processes. Both transitions will always be taken at the same time. Note that there may be multiple receivers, but only one receiver actually synchronizes.

A special form of synchronization is the use of a broadcast channel. In that case there can be multiple receiving edges. Note that for broadcast channels the sender can always 'fire' while only the receivers which have enabled edges synchronize with the sender.

**Guards** Guards define when an edge is enabled or not i.e., when an edge can be taken or not. Often this involves clock variables which indicate at what value of the clock a transition can be taken or not. But guard expressions are not limited to contain clock variables.

**Updates** Update expressions are used to assign values to variables to moment the edge is taken. These variables can again be clock variables or other system variables.

### **2.2.2.** MODEL VERIFICATION

In Section 2.1.1 we discussed temporal logics LTL, CTL and CTL\*. Uppaal uses a subset of CTL to define properties on the model, or queries as they are called in Uppaal. The main properties which can be checked by Uppaal are:

- **Reachability properties** These properties specify whether a state where property p holds, can be reached. In Uppaal this is written as E<>p.

- **Safety properties** Safety properties specify a property which should always hold. This is either given by A[]p saying that p should hold in all states on all paths; or by E[]p which defines that p should hold in all states of a certain path.

- **Liveness properties** These properties specify that some property p will eventually hold. This can either be written as A<>p, which means that for all paths p should hold eventually, or by p --> q defining that when p holds, then eventually q will hold.

Note that in Uppaal the property p can also represent a location in one of the automata, or templates. This makes it for example easy to write a query which checks on the model whether a certain location is reachable, i.e.: E<> template\_name.location\_name.

### **2.3.** Source code to model translation

In order to apply model checking techniques to a code base, the code needs to be translated to a formal model, e.g. a finite state machine. As most of the time no straightforward translation of language constructs is possible, a mapping from one to the other is required.

In general translating the source code to a model is done in two steps. One, retrieving the semantics of the code in a form which can be easily parsed and traversed, and two, mapping the source code constructs to the available constructs in the modelling language.

Step one is often done by parsing the code, convert it to an Abstract Syntax Tree (AST) and from the AST, create a Control Flow Graph (CFG). An AST is, as the name implies, an

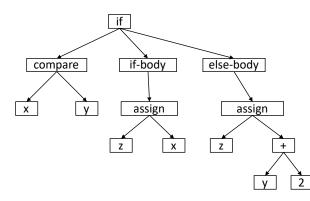

abstract representation of the syntax described in a tree. Each node in this tree maps to a construct in the source code, and any non-informative information like semicolons and parentheses are left out. Figure 2.4 show a simplified AST of the code from Listing 2.1.

Listing 2.1: Code for simple AST

Figure 2.4: Simplified AST of the code from Listing 2.1

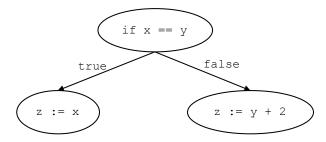

Because an AST provides an unambiguous mathematical representation of the source code, it can be used to create other representations like a Control Flow Graph. A CFG is a directed graph where each node represents a statement, and the edges represent the control flow. Figure 2.5 shows a simplified CFG for the AST of Figure 2.4 and the code from listing 2.1.

Figure 2.5: Simplified CFG of the code from Listing 2.1

The second step of the source code to model translation is mapping the code constructs to the available constructs in the modelling language. The possible approaches for this step heavily depend on the modelling language, but information from both the AST and CFG can be used to perform this translation. Often no one-to-one translation is available, therefore it is important to take the goal of the model into account to give directions on how to do certain translations.

In case of a direct translation, the model will mimic the CFG to a high extent, but in case of a less direct translation, the model abstracts away from the CFG. The further the model abstracts away from the CFG, the more important it is to validate whether the model is still a truthful abstraction of the software program in order to be usable for formal verification.

Both the AST and CFG concept will be used in this research as tools to end up with a formal model of the code.

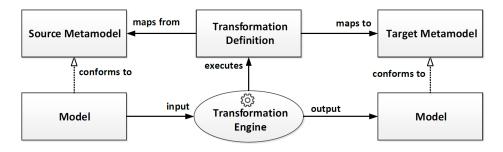

Figure 2.6: The concept of model transformation based on metamodels; from [Schivo et al., 2017]

### **2.4.** MODEL DRIVEN ENGINEERING

Models are an abstraction of a system, giving a simplified description, or showing a part of the complete system. Different models can highlight different parts of a system, or different levels of details. Often these kind of models are used for documentation purposes and knowledge purposes. Model driven engineering is an approach where models are not just used for documentation, but also for the creation of new (software) artefacts [Rodrigues da Silva, 2015].

In order to perform engineering on models, some formalism is required describing how a model should look like, e.g. what parts can it contain, how are relations between parts described, etc. This is what is typically called a meta model, a description of the syntax of the eventual model.

Once a meta model is available, all kind of new possibilities arise like the automatic transformation of models from one domain to the other. An example of this is shown in Figure 2.6. Here both models on the left and right side have their own meta model, describing the respective model syntaxes. Now a transformation definition is given which defines how artefacts from the input meta model should be mapped or transformed to artefacts of the output meta model. Using this transformation definition, tooling can be used to automatically create an output model from an input model.

Different tooling is available supporting the Model Based Engineering approach. A common and widely used framework for this is the Eclipse Modelling Framework (EMF)<sup>4</sup>. In EMF, meta models are defined in so called Ecore files which can be registered inside the framework. An actual model can then be assigned to a meta model, making it an instance of the meta model. This allows Eclipse for example to check whether the model instance correctly adheres to the syntax described in the Ecore file.

Where EMF is build directly on top of Java, the Epsilon framework<sup>5</sup> builds on top of EMF. The Epsilon framework provides an even more user friendly approach to define meta models in its Emfatic notation. Furthermore Epsilon includes notations to write transformations between meta models: the Epsilon Transformation Language (ETL).

ETL allows to write *rules* which define how an element type of the source (meta) model should be translated to one or more elements of the output (meta) model. EMF follows an object oriented flow in which rules can be defined abstract, and rules can extend on other rules.

<sup>&</sup>lt;sup>4</sup>https://www.eclipse.org/modeling/emf/

<sup>&</sup>lt;sup>5</sup>https://www.eclipse.org/epsilon/

## 3

## **RELATED WORK**

This section describes previous research which is related, or has overlap with our research. A division is made between model checking source code (Section 3.1) and program slicing (Section 3.2). Section 3.3 discusses the contribution of our research with respect to the discussed related work.

### **3.1.** MODEL CHECKING OF SOURCE CODE

Back in 1999 [Burns and Wellings, 1999] wrote about using model checking in order to verify concurrent Ada programs. For this they use the UPPAAL model checker which had just been released at that time. The authors explain some aspects of the Ada language which enables powerful concurrent programming, e.g. Tasking and Protected Types. They propose to use Finite State Models (FSM) to verify programs build upon these concurrent Ada aspects. It is noted that model checking can never give a 100% guarantee as there is always an informal relation between the source code and the model, and also between the source code and the compiled machine code. The authors state that model checking can be a good method to verify rather complicated concurrent programs, especially with more mature tools becoming available.

In contrast to the previous work, the research described in the remainder of this section apply automatic model extraction from source code.

[Bowman et al., 1999] present and compare three approaches to extract models from Java code. These approaches are parsing source code, disassembling byte code, and profiling where a model is built by monitoring run-time behaviour. Parsing source code, gives the most accurate model, but is the most complex and slowest of the three options. For the purpose of static analysis the disassembler will be sufficient and is simpler and faster. When information is to be found in the model which is only available from execution of the code, the profiler option works best.

[Corbett et al., 2000] designed a tool called Bandera which extracts and creates models from Java source code for different existing model checkers, e.g. Spin and SMV. In order to reduce the state space, the authors apply slicing to remove parts of the code which are not relevant for checking a given property. Furthermore the tool supports user controlled abstraction of variable values in order to reduce the state space as well.

The slicing is based on a slicing criterion. From the property to be verified it is found what variables and procedures have influence on this property and from there on all irrelevant parts are removed from the program. The slicing approach used is based on [Horwitz et al., 1988] and further described in [Hatcliff et al., 1999a].

[Holzmann and Smith, 2002] show a technique to derive models from ANSI-C source code for the SPIN model checker (also developed by Holzmann). This technique is specifically targeted at distributed and concurrent systems.

In order to reduce the state space, the authors use a map that defines which type of statements are relevant for the current property to be verified and which types are not. According to the authors the number of unique statement types for a given application is in the order of a few hundred, which is accepted to be crafted manually, especially compared to manually crafting a full model. This map is also used to map certain statements or variables to a default value (e.g. *true* or *skip*) which further limits the state space.

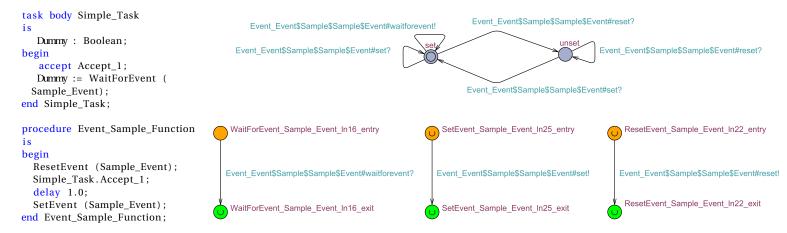

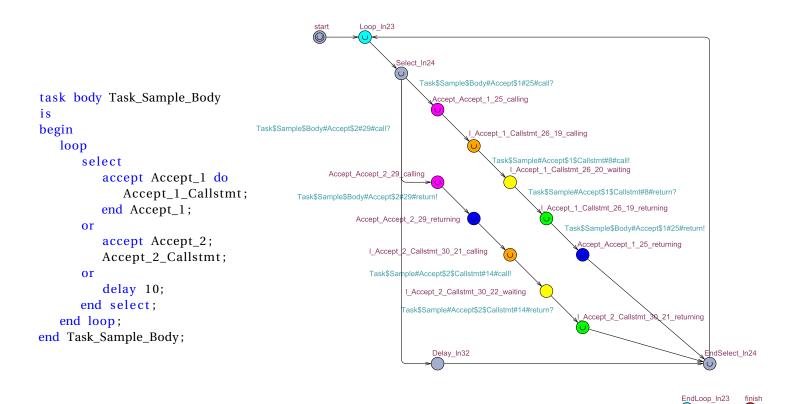

[Silva et al., 2011] and [Faria et al., 2012] both present a tool to construct models from Ada code. [Silva et al., 2011] developed a tool which is capable of automatically extracting UPPAAL models from Ada code. The developed tool is aimed at translating Ada code which complies to the Ravenscar profile [Burns et al., 2003]. This is a subset of Ada tasking, especially targeted to safety-critical hard real-time systems. The tool furthermore uses the Ada Semantic Interface Specification (ASIS) [Bladen et al., 1991] to retrieve the semantics from the Ada source code. Annotations on timing requirements are added in the code. These annotations give an upper bound to timing constraints of functions.

Based on the ASIS representation of the source code, a control flow graph (CFG) is created for each Ada construct and each CFG is eventually translated into an Uppaal template. This template contains the timed automata of the specific Ada construct. Each node in the CFG is therefore mapped to an Uppaal state, and each edge to a transition.

The clocks in the Uppaal templates are also generated from the source code. This is both done based on code constructs like *delay until* and variables of type *Ada.RealTime.Clock()*, but also by means of code annotations. For example the *delay until* construct gives a lower bound on a clock constraint, but there is no language construct which gives rise to an upper bound. Therefore the authors introduce a *deadline annotation* which results in an upper bound for a clock in the Uppaal template.

[Faria et al., 2012] present an approach to extract models from Ada code for the purpose of model checking. The research has a special focus on modelling concurrent programs. In this context a tool called ATOS (Ada TO SPIN) has been developed which generates PROMELA models from Ada code to serve as an input to the model checker SPIN.

The ATOS tool is capable of translating a subset of the Ada language. Again the Ada Semantic Interface is used to extract information from the source code. The tool is also able to automatically infer formal properties from annotations in the code, inspired by SPARK<sup>1</sup> annotations. The annotations can either represent a general assert statement, or pre- and post-conditions for functions, procedures and task entries.

[Yildiz et al., 2017] present a technique to derive Uppaal models from Java byte-code. Their approach is based on the Model-Driven Engineering (MDE) technique as presented by [Schivo et al., 2017]. This framework is a general approach to transform domain specific models to UPPAAL, and also to transform UPPAAL results back to a domain specific representation. [Yildiz et al., 2017] construct a Control Flow Graph (CFG) from the Java byte-code, which is enriched with loop information, timing information and recursion handling to support the transformation to a timed automata. The enriched CFG forms the domain

<sup>&</sup>lt;sup>1</sup>https://www.adacore.com/about-spark

specific model which is fed into the model transformation framework, resulting in an UP-PAAL model.

### **3.2. PROGRAM SLICING**

Program Slicing was first introduced by [Weiser, 1984]. The idea of program slicing is to reduce a program such that it only contains those statements which have influence on the values of a certain variable or point of interest. One of the goals of the author for program slicing is to make it easier to debug code when it is known which variable or at which point in the code something goes wrong.

In the following years, many researchers adapted and used the idea of program slicing in different directions and for different purposes. [Silva, 2012] presents an overview of these directions, with one of the directions also being for the purpose of model checking, i.e. [Hatcliff et al., 1999b]. In the latter work the authors apply an adapted form of slicing in order to reduce the source code such that it becomes less costly to apply model checking on this code. They adapted the slicing criterion such that all information required to prove a certain LTL formula is in the slice, and nothing more than that.

[Korel and Laski, 1988] introduce the concept of Dynamic Slicing. This is a program slice which corresponds to a specific execution of the program for a certain input value, in contrast to *standard* slicing where all possible input values are considered, hence a dynamic slice is much smaller than a static one. [Korel and Laski, 1988] state in their definition that the path of a slice should be identical to the path in the full program. Hence, the slice has the same execution sequence as the full program, which is called a path-aware slice. The purpose of this work is to ease program debugging, as often it is known for which input value a certain bug is present so only this execution needs to be analysed.

[Agrawal and Horgan, 1990] also introduce the concept of Dynamic Slicing, but in contrast to [Korel and Laski, 1988], they do not require that the path of the slice should be equal to the path of the full program. This even further reduces the size of the slice compared to the previous approaches.

### **3.3.** Research contribution

Existing research for translating Ada code into formal models as mentioned in the previous section all use a subset of the Ada language, i.e. the Ravenscar profile, or the Spark subset. Our research aims at translating the complete Ada language. The existing research furthermore uses the Ada Semantic Interface Specification (ASIS) to 'process' Ada code, this interface has been replaced by the LibAdaLang<sup>2</sup> which we will therefore use in our research.

Eventually the contribution of our research is to combine a form of dynamic program slicing (code filtering) with the concept of model checking. The dynamic slicing will be used as a means of source code reduction in order to conquer the state explosion problem such that model checking becomes a realistic option for complex CPS control software.

<sup>&</sup>lt;sup>2</sup>https://github.com/AdaCore/libadalang

## 4

## Метнор

This chapter describes the research method of this thesis in more detail. First the main research question and sub-questions are given and then the research method per question is described.

### 4.1. RESEARCH QUESTIONS

As given in the introduction of this thesis, the main research question of this project is:

To what extent is it possible to prove formal properties on the 'happy flow' code of a real-time, concurrent cyber-physical system with a high ratio of repetitive tasks?

Due to the problem of state explosion, it is generally considered impossible to translate a full code base of a cyber-physical system, featuring real-time and concurrent aspects, to a formal model. Therefore the goal of this research is to only try to model the 'nominal' machine cycle, or 'happy flow', and to prove formal specifications on this part only. As manual extraction of the happy flow from the code base is not only a lot of work, but also error prone, run-time information is used to filter the happy flow code from the full program code.

In order to validate the research results, the research is focused on an existing machine control system written in the programming language Ada.

The research has been divided over four research questions, listed below:

- **RQ-1** Having only a model of the 'happy flow' code of a CPS, what properties of the system can be verified and can reveal interesting information for domain experts?

- **RQ-2** How can the code of the machine's 'happy flow' be extracted automatically, using run-time information?

- **RQ-3** How to automatically translate a partial program written in Ada, as found by answering RQ-2, into a formal model that allows the properties found by answering RQ-1 to be verified?

- **RQ-4** What results can be found from verifying the properties defined by answering RQ-1 on the model, found from answering RQ-3?

### **4.2.** RESEARCH METHOD

Per sub-question different approaches are taken to find an answer to the questions. For each sub-question the research method is discussed here.

- **Method RQ-1** The main goal of the complete research is to be able to verify formal properties on a partial program. However, because of having a partial program, the properties to be checked should be well chosen in order to be meaningful for the full program. Deductive reasoning is used to find an answer to this question. The results are given in Chapter 5.

- **Method RQ-2** In order to answer this question, tooling is designed and built to perform the code extraction automatically. The code is instrumented such that the execution count of each statement can be recorded. After running the machine for a small amount of time in a 'happy flow' mode, it is found which code is used for the happy flow and which code is not. Based on this information, our tool generates an intermediate representation of the happy flow code in an XML based format, ready for further processing. The research to answer this research question is described in Chapter 6.

- **Method RQ-3** This question concerns the generation of a formal model from the intermediate code representation which was the result of RQ-2. As a first step, it has been defined what the formal model should look like, e.g. which artefacts of the system should be present in the model such that the properties found by answering RQ-1 can be verified. The next step is to translate the code to a formal model. For this step tooling is again designed which performs a model to model conversion from the intermediate Ada representation to an Uppaal model.

In order to be useful for the future and to be less error prone, the model generation is done in a fully automatic fashion. Chapter 7 describes the research done to answer this question.

Method RQ-4 After the formal model generation, the model can be used to verify the properties as defined by answering RQ-1. This reveals information of the system which was not known before. During this phase, first the defined properties haven been formalised to temporal logic in the Uppaal query language. These queries are verified on the formal model. The result of this research question is described in Chapter 8.

# 5

## WHAT TO VERIFY ON THE 'HAPPY FLOW'?

The first research question, RQ-1, of this research is stated as:

Having only a model of the 'happy flow' code of a CPS, what properties of the system can be verified and can reveal interesting information for domain experts?

In this chapter will try to give an answer to this question.

### **5.1. DEFINITION OF HAPPY FLOW**

In order to answer RQ-1, it is required to further specify 'happy flow'. For this research, the happy-flow code is defined to be the CPS's source code which is actually executed when the machine performs its nominal machine cycle without any interruptions. Any source code not executed during the happy flow will not be part of the happy-flow model and therefore any formal property tested on the model will not consider this code.

In the case of our CPS under test, the Adat3-XF Die Attacher, the happy-flow cycle is the nominal pick & place sequence without e.g. a run out of materials, operator interventions or motion errors.

### **5.2. PROPERTIES OF INTEREST**

This section elaborates on system properties which can be verified on a model of the source code given the fact that only the happy flow, as defined in Section 5.1, is available.

### 5.2.1. DEADLOCK & LIVELOCK

In general, interesting properties of concurrent systems are deadlock and livelock situations. Hence a state of the system where two or more processes wait for each other forever.

It is noted that a specific happy flow execution will itself not contain a deadlock situation (otherwise it would not be a *happy* flow), but the code extracted from the happy flow potentially *can* contain deadlocks.

Therefore deadlock and livelock situations are interesting properties to verify on a happyflow model.

### **5.2.2. R**EACHABILITY PROPERTIES

Just checking whether a certain state in the model, i.e. a certain statement in the code, is reachable is not very meaningful for the happy flow. Due to the nature of the happy flow, only source code which is actually executed is part of the model, hence any state should also be reachable in the model.

For model validation this is however a useful property in order to check whether certain states are reachable as expected. Furthermore reachability analysis is in general faster then analysis of safety properties because a single trace satisfying the property is enough to prove the property, i.e. there is no need to search the complete state space.

As our CPS has concurrent tasks, it is interesting to check whether indeed all (main) tasks of the machine cycle get their start signal. This is a good indicator that the start-up behaviour of the machine is correctly captured in the model.

### **5.2.3.** SAFETY PROPERTIES

Safety properties indicate that "something bad will never happen". Hence, this is a property which should hold in all states of the model. Because our CPS performs multiple complex moves where a wrong move can potentially damage products or the machine itself, different safety properties can be thought of related to the physical state of the machine.

Examples could be:

- 1. The wafertable is not allowed to move when the needle is up in order to not damage the wafer.

- 2. The transfer mill should not rotate when the pick & place heads are still in an outward position in order to not damage the heads.

- 3. The wafertable is not allowed to move when a pick & place head is close to the wafer in order to prevent damaged dies.

Situations like example 1 and 2 have a high observability as the machine would no longer function properly when this property is violated. For example when the wafer foil is damaged or the heads are damaged no pick & place is possible anymore. Therefore these situations will not be part of the happy flow and it is not meaningful to test the corresponding safety properties.

Situations like example 3 however, can be more subtle and might actually happen unnoticed. These situations are possibly part of the captured happy-flow execution and therefore very interesting to test on our model.

All three examples define properties related to the physical state of the machine. Therefore, somehow one or multiple states in the model should represent this physical state. Note that in this research we automatically capture the control flow from the source code. Hence knowledge on the physical state of the machine is not directly available and needs to be added to the model for example by adding it as code annotations and extracting it with the happy flow, or by adding it after model extraction.

The latter will not be part of this research, hence it will not be possible to verify safety properties on the model which consider a physical state of the machine. This is left as future work.

### **5.2.4.** LIVENESS PROPERTIES

A liveness property means "something (good) will eventually happen", or when p holds, then eventually q will hold. The model we will eventually have is that of the happy flow of a repetitive machine cycle. Therefore it is tempting to think that liveness in general will be satisfied, but is this really the case?

We have modelled the source code corresponding to the happy flow of the CPS, but this one execution we used to capture the happy flow is not necessarily the only execution flow through the captured code. Therefore liveness properties can actually reveal potential issues in our source code, and therefore are an important category of properties to take into account.

Examples of liveness properties for our CPS are:

- 1. Is it always possible to pick up a next product?

- 2. When a pick & place head goes into an unsafe (outward) position, will it always return to its safe position again?

In the context of a repetitive machine cycle there is also another category of liveness properties. That is: is it always possible to return to a defined state in the cycle? This is a property which can be checked for each parallel task in the model and gives a good indication of the absence of deadlock.

### **5.2.5.** SEQUENCE VALIDATION

A different category of domain properties are certain sequence of actions, e.g. is Task A always executed before Task B? Typically this concerns a sequence within one cycle of the machine, because in the example Task A will probably be again executed in the next cycle. Hence to verify these kind of properties, the model needs to have some notice about the separation of cycles.

Examples of interesting sequences in our CPS are:

- 1. Is the pick & place head in position before the needle pushes a die towards the head?

- 2. Are all inspections of a product OK before the product is placed?

A caveat for example 2) is that it should somehow be possible to identify a unique product. This is because the inspection of a certain product and the placement of that same product is spread over multiple cycles. It should be noted however that adding unique identifiers will significantly increase the state space of the model.

### **5.2.6.** CYCLE TIME ANALYSIS

An important aspect of our CPS, and production machines in general, is machine speed. For a machine conducting a repetitive task the machine speed is determined by the time required for one cycle.

In this research it is decided not to add the dimension of time to the model for the sake of simplicity. With the choice for Uppaal it is however possible to extend the model in future with timing information of the happy flow.

If the execution time of functions will be retrieved from the code, it becomes possible to perform statistical analysis on the cycle time of the machine. Furthermore one can conduct a critical path analysis of the different parallel tasks.

## 6

## **'HAPPY FLOW' EXTRACTION**

This chapter is about research question 2, or how to retrieve the code which is used for the happy flow of a Cyber-Physical System. RQ-2 is stated as:

How can the code of the machine's 'happy flow' be extracted automatically, using run-time information?

The first part of the happy flow extraction is done by means of existing profiling and coverage tools. These tools instrument the source code and record the execution count of each line of source code while the program is running.

In case of a CPS with a repetitive task, code executed at each repetition is executed many times where initialization code and error handling is executed much fewer times. Therefore it is possible to use coverage data to give an indication about which code belongs to the normal machine operation, i.e., happy flow, and which code belongs to the non-happy flow code.

The second part of the extraction concerns the generation of a representation of the source code which only contains the happy flow. Tooling is designed and created to perform this part automatically.

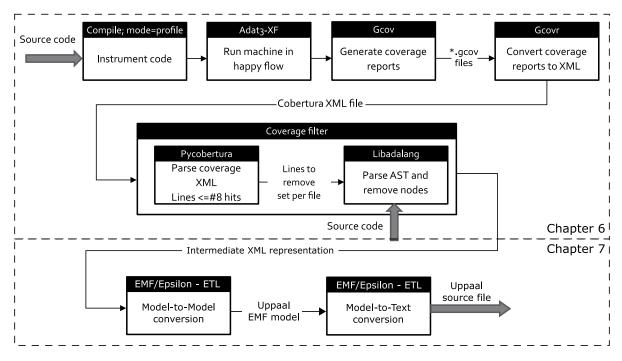

Figure 6.1 shows the different steps taken to come from source code to the intermediate representation. This chapter explains the details of the top part of the figure. The bottom part of the figure is explained in the next chapter. The repository of our happy flow extraction tooling is available on GitHub<sup>1</sup>.

### **6.1.** DETERMINE THE HAPPY FLOW

As discussed in the introduction of this section, we look at the execution count of the source code to find the happy flow. When the execution count is above a certain threshold we consider it happy flow. Code which is executed below the threshold is considered to be part of the initialization code or to the non-happy flow like error handling.

For the system under test, the Adat3-XF, the threshold is put at a number equal to the amount of pick & place heads. This is because initialization code is typically executed for each pick & place head. All code executed more times than the amount of heads is thus considered part of the normal production flow, or 'happy flow'.

<sup>&</sup>lt;sup>1</sup>https://github.com/jildert17/happyflow-extractor

Figure 6.1: Schematic overview of the tool-chain to come from source code to a formal model; The top part is described in this capter, the bottom part in the next chapter.

### **6.2.** INSTRUMENTATION

As a first step the source code needs to be instrumented in order to retrieve the execution count of each line. Because we want to minimize the state space, we choose not to take the full source code of the CPS into account. Support packages related to e.g. the user interface, system libraries and motion planning libraries, do not change often and are therefore less likely to contain issues. Therefore these parts are left out. Later it can be chosen to include more source code if it appears that our tooling works on the smaller code base. This is left as future work.

Initially a relatively new tool called GNATcoverage<sup>2</sup> was tried to find the coverage information of the source code. It appeared however that this tool only indicates whether a line is executed or not, while it cannot tell how many times a line is executed. Therefore we were forced to use older tooling called gcov<sup>3</sup>. gcov is the default coverage tool shipped with the GNU Compiler Collection (GCC) and therefore already available in the research setup. Our supplier of the Ada compiler, AdaCore, did however indicate that it will drop support for gcov in the near future in favor of GNATcoverage.

For both GNAT coverage and goov instrumentation is done on object level which is inserted during compile time. Therefore the source code itself is kept untouched.

In order to enable gcov instrumentation on an Ada project, recompilation is required using compiler switches -fprofile-arcs and -ftest-coverage and linker switch -fprofile-arcs.

During compile time for each object file a '\*.gcno' file is created containing information to later reconstruct blocks and link them to line numbers.

<sup>2</sup>https://www.adacore.com/gnatcoverage

<sup>3</sup>https://gcc.gnu.org/onlinedocs/gcc/Gcov.html

### **6.3.** EXECUTING THE HAPPY FLOW

Once the source code is compiled including instrumentation, the software is ready to control the Cyber-Physical System and record coverage information. For this a (simulation) of the Adat3-XF machine is started and the nominal machine cycle is executed for a certain amount of time. For the experiment described in this thesis the nominal cycle of the CPS is executed for 30 seconds. The specific machine configuration used has a speed of around 600 units per minutes, hence when running the machine for 30 seconds, an execution count of 300 is expected for code that is called once per cycle.

The gcov coverage information is written to disk the moment the program receives the shutdown command; i.e., C-exit(). For each source file a separate file is saved with the '\*.gcda' extension, containing the count data for the source code. It is important to note that this is cumulative data; i.e., when the program is run again, the coverage data is added to the data of the previous run.

### **6.4.** PROCESSING COVERAGE DATA

Once the coverage data has been gathered and stored in the \*.gcda files, gcov can be invoked to generate human-readable coverage reports, see Section 6.4.1. However, in this project we want the coverage data to be processed further, hence human-readable formats are less suitable. For that purpose the gcov output is translated to a machine-readable format which is described in Section 6.4.2.

### 6.4.1. GCOV

#

When gcov is invoked on the code, it scans for the \*.gcno and \*.gcda files and by using the original source code it generates a report for each original source file. Listing 6.1 shows a snippet of the gcov output of one of our source files.

The leftmost column indicates the coverage count of the specific line, e.g. 288 times for line 81, which corresponds to the expected 300 times as discussed above. A dash in the same column indicates that no coverage data is available for that line; lines marked by ##### have not been executed.

Lines for which no coverage data is available can for example be lines which belong to a previous line which is the case for line 82 and 83 in listing 6.1, both lines belong to line 81. Other examples are blank lines, or lines which only contain a keyword and cases where lines are removed during compiler optimizations.

| -:    | 80: | overriding                                                      |

|-------|-----|-----------------------------------------------------------------|

| 288:  | 81: | <pre>procedure Task_Entry (Mp : access Attach_Process;</pre>    |

| -:    | 82: | E : Entry_Type;                                                 |

| -:    | 83: | Collet : Integer) is                                            |

| -:    | 84: | begin                                                           |

| 288:  | 85: | case E is                                                       |

| 288:  | 86: | <pre>when Start =&gt; Mp.Process_Task.Start (Collet = 1);</pre> |

| -:    | 87: | when others => null;                                            |

| -:    | 88: | end case;                                                       |

| 288:  | 89: | end Task_Entry;                                                 |

| -:    | 90: |                                                                 |

| ####: | 91: | overriding procedure Task_Wait (Att : access Attach_Process;    |

| -:    | 92: | Result : out Boolean;                                           |

| -:    | 93: | Skip_Status : out Integer) is                                   |

|       |     |                                                                 |

| -:     | 94: | <pre>pragma Unreferenced (Att);</pre> |

|--------|-----|---------------------------------------|

| -:     | 95: | begin                                 |

| #####: | 96: | Result := True;                       |

| #####: | 97: | <pre>Skip_Status := Success;</pre>    |

| #####: | 98: | end Task_Wait;                        |

Listing 6.1: gcov report snippet

### 6.4.2. GCOVR AND COBERTURA

The gcov output as shown in listing 6.1 is easily readable by humans but not very suitable for further processing. For this purpose  $gcovr^4$  is used. This is a Python tool which calls gcov and is able to translate the gcov output to different formats. One of these formats is the widely used XML-based Cobertura format<sup>5</sup>.

Listing 6.2 shows the gcovr output in Cobertura format of the same source lines as shown in listing 6.1. One Cobertura file is generated containing the coverage information for all source files. This format is suitable for further processing, especially because of the availability of different Cobertura format parsers.

```

e number="81" hits="288" branch="true" condition-coverage="50% (1/2)">

<conditions>

<condition number="0" type="jump" coverage="50%"/>

</conditions>

</line>

<line number="85" hits="288" branch="true" condition-coverage="50% (2/4)">>

<conditions>

<condition number="0" type="jump" coverage="50%"/>

</conditions>

</line>

<line number="86" hits="288" branch="true" condition-coverage="50% (1/2)">

<conditions>

<condition number="0" type="jump" coverage="50%"/>

</ conditions>

</line>

e number="89" hits="288" branch="false"/>

e number="91" hits="0" branch="true" condition-coverage="0% (0/2)">

<conditions>

<condition number="0" type="jump" coverage="0%"/>

</conditions>

</line>

e number="96" hits="0" branch="false"/>

e number="97" hits="0" branch="false"/>

e number="98" hits="0" branch="false"/>

```

Listing 6.2: gcovr XML output snippet corresponding to listing 6.1

Using pycobertura<sup>6</sup> we developed a Python program which parses the Cobertura coverage data as shown in Listing 6.2. This program receives two parameters: the first one being the path to the Cobertura file, and the second one being a number indicating the execution-count-threshold for the happy flow. All line execution counts above this threshold are considered part of the happy flow, and all line frequencies equal or below this num-

<sup>4</sup>https://gcovr.com/

<sup>&</sup>lt;sup>5</sup>https://github.com/cobertura/cobertura

<sup>&</sup>lt;sup>6</sup>https://pypi.org/project/pycobertura/

ber are deliberately considered not being part of the happy flow. Note that there are also lines for which no coverage data is available.

The program returns a text file in JSON format which contains per source file a list of line numbers above the threshold and a list of line numbers equal or below the threshold. An example of this is shown in Listing 6.3.

```

{"nr_of_files": 2, "line_nr_data": [{"filename": "C:/SVN/Trunk_Clean/source/Applic/

Adat/adat_thetaz-mill-attach_pos.adb", "below_thres": [40, 43, 91,96,97,98, 115,

119, 120, 122, 124, 149, 154, 158, 159, 161, 162, 163, 164, 165, 166, 168, ...],

"above_thres": [64, 81,85,86,89, 100, 102, 129, 132, 135, 139, 144, 145, 156,

253, 256, 258, 260, 263, 268, 271, 275, ...]}]

```

Listing 6.3: Parsed Cobertura output in JSON format. The marked numbers correspond to the line numbers of the GCOV output in listing 6.1

The Python script saves the JSON text file to the C:/temp folder as a means of cache. By giving a '-f' flag to our Coverage\_Filter (described below in Section 6.6.), regeneration of the JSON file is forced, otherwise the cache file is used if available.

### **6.5.** ADA METAMODEL

The goal of this project is to end up with a formal model of the happy flow of our CPS and be able to verify properties on the model by a model checker. From the different model checkers listed in Section 2.1.3 it is chosen to use Uppaal [Behrmann et al., 2006] for this research.

The main reason for this choice is that Uppaal supports *timed* automata, although adding a notion of time to our models is considered as a next step and not part of the current research.

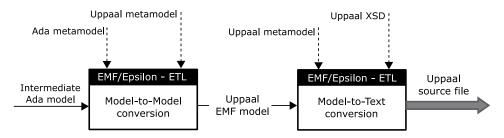

The second reason to choose for Uppaal is the availability of an Uppaal meta model and a corresponding model to text transformation in the Eclipse EMF framework, presented by [Schivo et al., 2017]. Refer to Section 2.4 for an introduction to EMF.

This framework is widely used to do model to model conversions, e.g. by [Yildiz et al., 2017] to translate Java byte code into Uppaal models. The latter work is taken as a starting point to do our Ada to Uppaal conversion.

The decision to use EMF leads to the need for some intermediate representation of the Ada code which complies to the EMF/Epsilon modelling syntax. For this purpose a metamodel of the Ada code is designed. The metamodel provides the syntax to construct the intermediate Ada representation or model. Next to that, the metamodel is also used to define the model-to-model transformation which is described in Chapter 7.

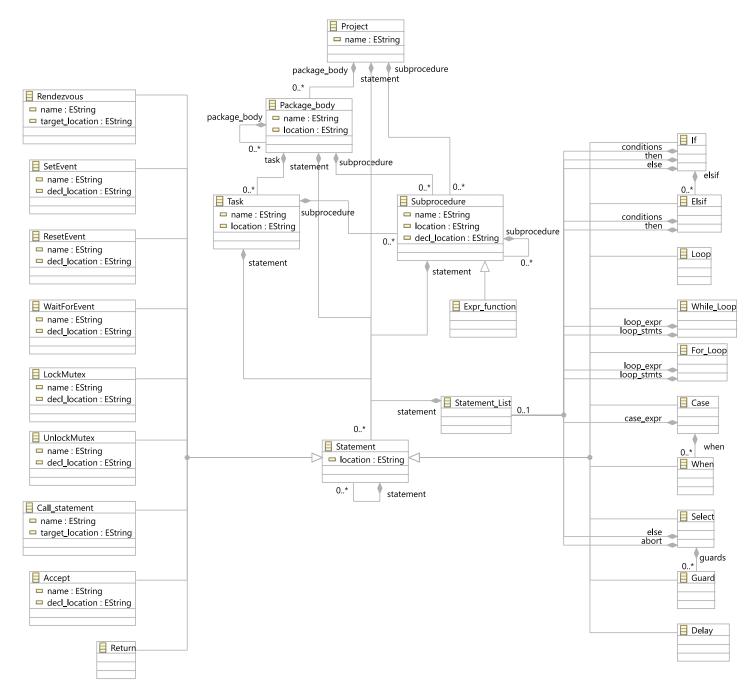

The full metamodel is shown in Figure 6.2, using standard UML class diagram notation. The main hierarchy of the model is that of a single Project class at top level which has leaves of type Package\_body. A Package\_body then contains Subprocedures and/or Tasks which both are the main containers of the abstract type Statement.

There are a few other relations in the model which are required to capture more subtle and infrequently used features of the Ada language.

On the left and the right hand side of the figure different kinds of statements are shown, reflecting most of the common statement types of the Ada language. Besides the common Ada constructs, also statements related to custom-defined concepts are added. These concepts are Events and Mutexes. These concepts have their own types in our metamodel

Figure 6.2: Diagram of the Ada metamodel in EMF/Epsilon

because they play an important role in our inter-process communication and will therefore impact our Uppaal model of the CPS.

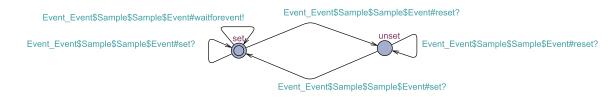

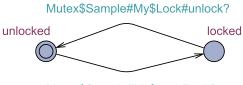

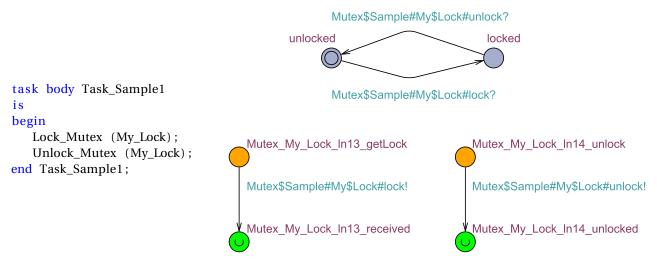

The event construct is a kind of global signal which has three functions associated to it: SetEvent, ResetEvent and WaitForEvent. By means of this concept concurrent tasks can synchronize with each other.

Mutexes are widely used in computer science to lock certain resources in order to prevent race conditions in concurrent systems. The custom-defined mutexes in our CPS has two related functions, LockMutex and UnlockMutex. Also this concept will get its own representation in the Uppaal model and therefore has its own statement types in the metamodel.

All statement types inherit from the abstract Statement type. Note that statements can again contain statements, such that a tree of statements is supported.

In order to support grouping of child statements, a Statement\_List type is added. This is for example used to be able to distinguish between the condition statements and else statements of an if statement.

### **6.6.** GENERATE THE INTERMEDIATE REPRESENTATION

Now that it is known from the coverage data which lines we need to keep and which lines should be removed, and we have an EMF metamodel, we are able to filter the happy flow from the original source code and translate it to the metamodel syntax.

For this step we designed a custom tool called the 'Coverage\_Filter' which reads the JSON file with coverage data and retrieves the AST of the source code. It then translates the happy flow code into an intermediate Ada model. This model is written in XML and complies to the metamodel from Section 6.5.

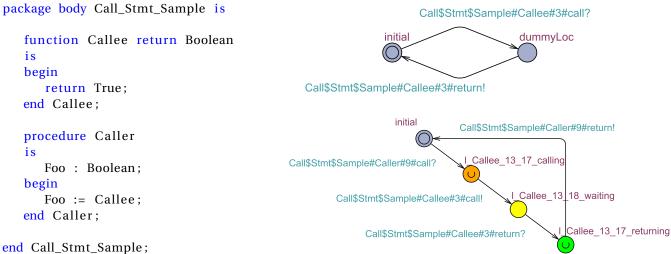

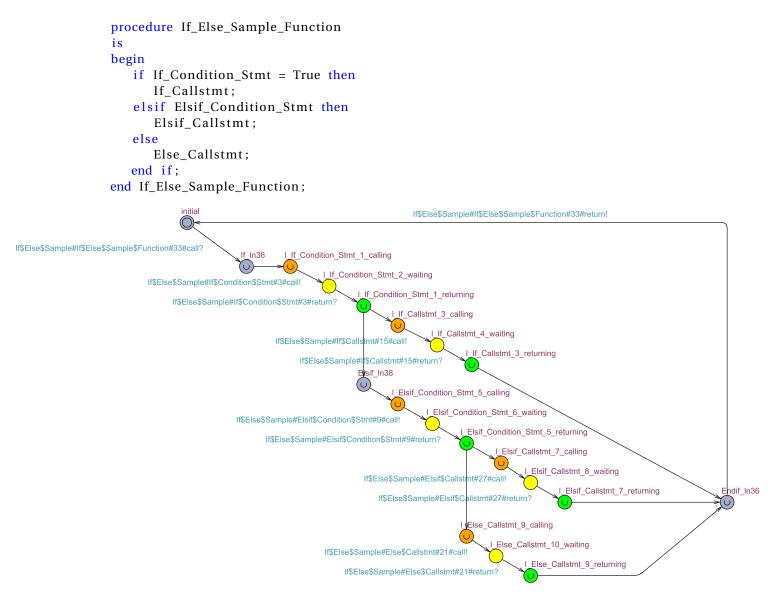

The tool is, like the CPS source code, written in Ada. To retrieve the AST from each source code file, the LibAdaLang<sup>7</sup> libraries are used. Once the AST is available, the tree is traversed by means of a recursive function. Each node matching a language construct which needs to translated is processed as described below.

### 6.6.1. PACKAGE BODY

For the AST nodes of type Ada\_Package\_Body it is not checked whether it is in the happy flow or not as these nodes are not executed and no coverage data is available.

These nodes are translated to an XML node with name package\_body and attributes location and name.

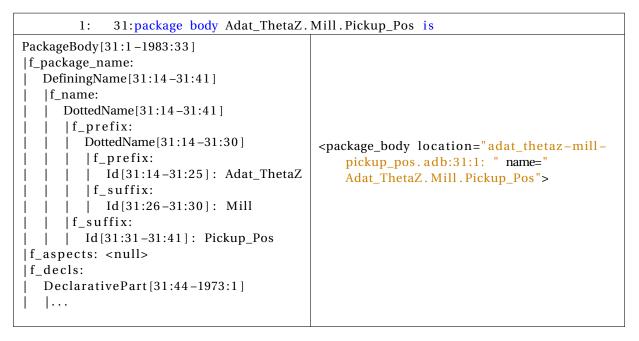

Table 6.1 shows an example of the translation of the Package body source code via the AST to the intermediate Ada model.

<sup>7</sup>https://github.com/AdaCore/libadalang

Table 6.1: Package Body translation; Top: Source code, annotated with coverage information; Bottom-Left: AST as retrieved from LibAdaLang; Bottom-Right: translated XML code complying to the metamodel.

### **6.6.2. SUBPROCEDURE BODY**

AST nodes of type Ada\_Subp\_Body represent the bodies of all procedures and functions in the source code. First the line number of a subprocedure is checked against the coverage information: only if the execution count is above the threshold, the node is processed, otherwise it is skipped. An exception is made for the subprocedure named 'Adat\_Dietransfer-A3' as this procedure is only executed once, but does contain the main loop of the machine cycle.