### Karlsruher Institut für Technologie Fakultät für Elektrotechnik und Informationstechnik

# DATA ACQUISITION FOR GERMANIUM-DETECTOR ARRAYS

Zur Erlangung des akademischen Grades eines

DOKTORS DER INGENIEURWISSENSCHAFTEN (DR.-ING.)

von der KIT-Fakultät für Elektrotechnik und Informationstechnik

des Karlsruher Instituts für Technologie (KIT)

genehmigte

#### DISSERTATION

von

Mario Schütt, M.Sc.

geboren in Freiburg im Breisgau, Deutschland

Tag der mündlichen Prüfung: 26.09.2022

Erstgutachter: Prof. Dr. Ivan Peric

Institut für Prozessdatenverarbeitung und Elektronik

Zweitgutachter: Prof. Dr. Werner Hofmann

Max-Planck-Institut für Kernphysik, Heidelberg

| _  |                                                                                                                                                                                                 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D  | Declaration of authorship                                                                                                                                                                       |

| Ι  | declare that I have developed and written the enclosed thesis in hand completely by myself, and ha                                                                                              |

| us | sed sources or means without any declaration in the text.                                                                                                                                       |

| E  | Erklärung der Selbstständigkeit                                                                                                                                                                 |

|    | Iiermit versichere ich, die vorliegende Arbeit selbständig angefertigt, alle dem Wortlaut oder Sinn<br>ntnommenen Inhalte anderer Werke an den entsprechen Stellen unter Angabe der Quellen ker |

| ge | emacht und keine weiteren Hilfsmittel verwendet zu haben.                                                                                                                                       |

|    |                                                                                                                                                                                                 |

|    |                                                                                                                                                                                                 |

|    |                                                                                                                                                                                                 |

|    | Mario Schütt                                                                                                                                                                                    |

| ]  | Heidelberg, den 08.08.2022                                                                                                                                                                      |

|    |                                                                                                                                                                                                 |

## Zusammenfassung

Die Wandlung von analogen zu digitalen Signalen und die anschließende online/offline Verarbeitung ist die technologische Voraussetzung zahlreicher Experimente. Für diese Aufgaben werden häufig sogenannte Analog-Digital-Wandler (ADC) und FPGAs ("field-programmable gate array") eingesetzt. Die vorliegende Arbeit beschreibt die Evaluierung der FPGA und ADC Komponenten für die geplante FlashCAM 2.0 DAQ (FC2.0 DAQ). Die Entwicklung der ersten FlashCAM (1.0) DAQ (FC1.0 DAQ) wurde unter Federführung des Max-Planck-Instituts für Kernphysik im Jahre 2012 begonnen und war ursprünglich eine exklusive Entwicklung für das Cherenkov Telescope Array (CTA) Experiment. In der Zwischenzeit wird FlashCAM in zahlreichen Experimenten (HESS, HAWK, LEGEND-200, etc.) eingesetzt, die sowohl Photomultiplier (PMTs) als auch High Purity Germanium (HPGe) Detektoren umfassen. Beide Detektorentypen unterscheiden sich massiv in ihren Anforderungen und können auch von der neuen DAQ abgedeckt werden.

Das Themengebiert der Arbeit umfasst den gesamten funktionellen Umfang einer modernen DAQ. Moderne DAQ Systeme benötigen eine möglichst hohe Read Out Performance zwischen dem DAQ Board und dem es kontrollierenden Server. Die Umsetzung eines leistungsfähigen Firmware Designs und das Design einer hierauf angepassten Hardware/Softwareschnittstelle wird am Beispiel der Zynq Familie vorgestellt. Die Zyng-Familie von Xilinx ist von besonderem Interesse, da der Hardwarehersteller Trenz Elektronik ein flexibles, einfach aufsteckbares Modulkonzept mit verschiedenen SoCs der Zyng-Serie anbietet. Neben der Read Out Performance einer DAQ ist ihre Auflösungsgrenze von entscheidender Bedeutung für das Gelingen des finalen Experiments. Die verwendete FADC Karte muss sich daher durch exzellente SNR und Linearitätseigenschaften auszeichnen. Die Evaluierung solcher FADC Karten setzt ein Testsetup voraus, dass in Signalreinheit und Stabilität die hohen Anforderungen der devices under test übertreffen muss. Praktisch sind diese Bedingungen nur unter hohem (Kosten) Aufwand erreichbar. Im Rahmen der Arbeit wurden daher auch alternative Testkonzepte entwickelt, die mit akzeptablen Abstrichen in der Genauigkeit eine Messung im experimentellen Umfeld ermöglichen können. Da sich die Themengebiete in ihrem Inhalt deutlich unterscheiden, wurde die vorliegende Arbeit in zwei Themenkomplexe aufgeteilt. Der erste Teil der Arbeit beschäftigt sich mit dem Einsatz der Zyng Familie in der geplanten "FlashCAM" Nachfolger DAQ. Der zweite Teil widmet sich der ADC Nichtlinearitätsbestimmung.

Die wichtigsten Ergebnisse der Arbeit lassen sich folgt zusammenfassen:

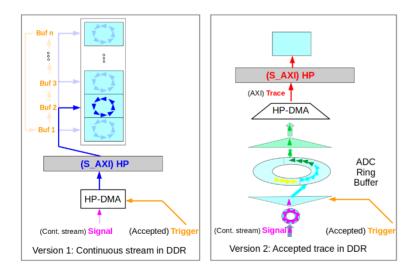

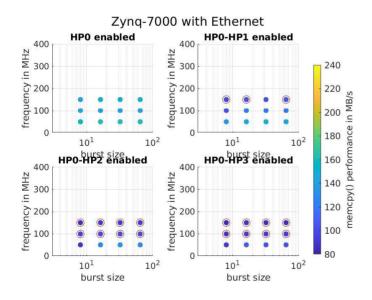

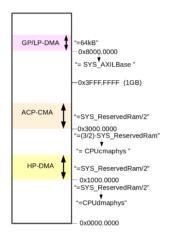

■ Die "High Performance" (HP) Schnittstellen der Zynq-UltraScale+ haben eine aussetzerfreie Bandbreite von 2.4 GB/s in den externen Arbeitsspeicher der Trenz Module. Wird noch zusätzlich die standardmäßig vorhandene 1 Gb PS-Ethernet Verbindung betrieben, verbleibt der CPU noch eine Bandbreite von mindestens 0.5 GB/s in den Arbeitsspeicher. Im Fall der Zynq-7000 Serie ist eine effiziente Implementierung der HP Schnittstellen schwierig, da die CPU nur vergleichsweise

niedrige Arbeitsspeicherzugriffsraten erreicht. Die HP Schnittstellen sind eine wichtige Designalternative da ein durchgehender Datentransfer in den externen Arbeitsspeicher ein Design ermöglichen würde dass weniger stark durch den verfügbaren FPGA internen Speicher begrenzt ist. Dies wäre besonders für Anwendungen in der HPGe-Spektroskopie wünschenswert, da der praktische Nutzen des verwendeten Designs stark von der zur Verfügung stehende Puffergröße abhängt.

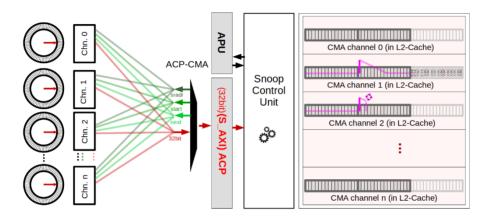

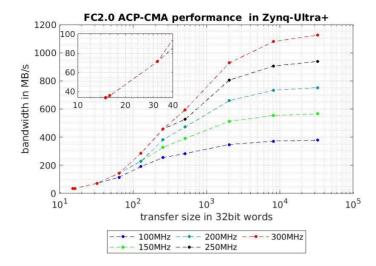

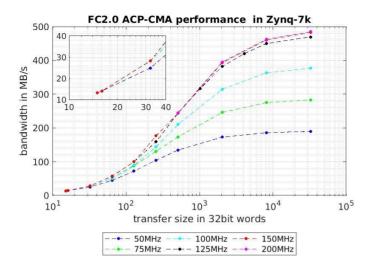

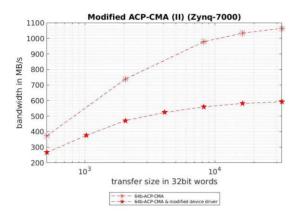

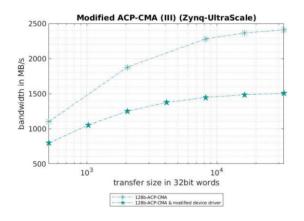

- Die "Accelerator Coherency" Schnittstelle (ACP) ermöglicht ein direkter Datentransfer aus der FPGA in den Cache der Zynq-CPU. Die entworfene ACP-CMA hat eine Bandweite von bis zu 2.4 GB/s und bietet für Cache-CPU Zugriffe noch ausreichend Reserve. Dass die Zynq-CPU die Cachedaten ohne ein Abwürgen der ACP-CMA verarbeiten kann, ist entscheidend. Wäre dies nicht der Fall könnte die CPU im Parallelbetrieb von Ethernet und ACP-CMA nicht die notwendigen Vorarbeiten zur Ethernet-Übertragung ("Event Building") bewältigen. In der Evaluierung wurde eine maximale Event Building Bandbreite von 0.7 GB/s festgestellt. Wahrscheinlich ist die reale maximale Bandbreite deutlich höher anzusiedeln. Einschränkend muss betont werden, dass in praktischen Applikationen zusätzliche Einschränkungen in Kraft treten, die de-facto einen kontinuierlichen Betrieb der ACP-CMA unmöglich machen. Diese Einschränkungen die nicht prinzipieller Natur sind wurden in der durchgeführten Ermittlung nicht berücksichtigt. Da weiterhin alle Zynq-FPGAs über einen Cache verfügen, ist die ACP-CMA eine Designlösung, die auf allen verfügbaren Zynq-FPGAs sinnvoll implementiert werden kann. Dies unterscheidet sie von der entwickelten HP-DMA, die häufig nur für Implementierungen in einer Zynq-UltraScale FPGA interessant ist.

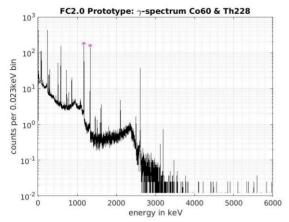

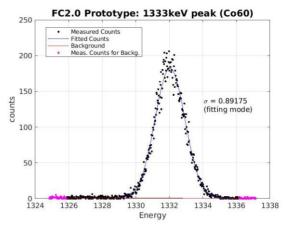

- Der neuentwickelte FC2.0 Prototype wurde bereits in experimentellen Setups eingesetzt. Als Anwendungsbeispiel dient die Messung und Analyse eines γ-ray Spektrums eines HPGe-Detektors.

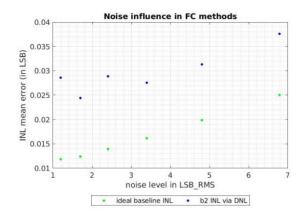

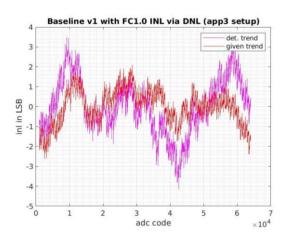

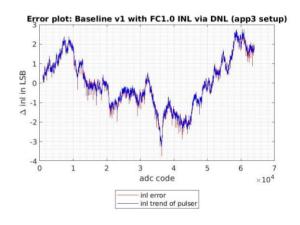

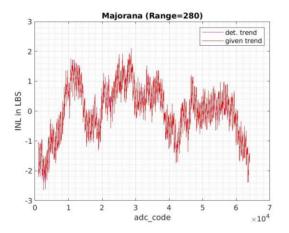

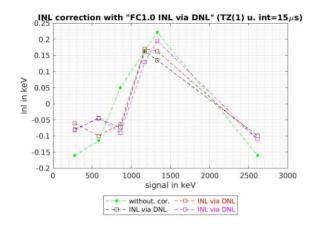

- Der Erfolg einer ADC Nichtlinearitätsbestimmungen ist stark von der Signalreinheit des verwendeten Eingangssignal abhängig. In Simulationen konnte gezeigt werden, dass die neu entwickelten Verfahren nur relativ schwach durch Pulsernichtlinearitäten verfälscht werden. Einen praktischen Vergleich zwischen den neuen und einer klassischen Methode konnte keinen signifikanten Unterschied feststellen. Die untersuchten Methoden können daher für eine zukünftige Implementation in FC2.0 empfohlen werden.

## **Abstract**

Experiments often need to digitize analog signals that are then processed either online or offline. The data acquisition (DAQ) for such systems needs analog-to-digital converters (ADC) and the digital data are processed by field programmable gate arrays (FPGA). The thesis describes the evaluation of the FPGA and ADC devices of the designated FlashCAM 2.0 DAQ (FC2.0 DAQ).

2012 started the development of the first FlashCam DAQ (FC1.0). Initially FC was an exclusive development for the Cherenkov Telescope Array (CTA) Experiment and therefore fixed to photomultiplier tube detectors (PMTs). In the meantime, FC is implemented in several experiments (HESS, HAWK, LEGEND-200, etc.) and additionally has high-pure-germanium-detector (HPGe-detector) features. Both detector types significantly differ in their requirements and both detector types must be handled by the successor DAQ.

In the thesis the development of a DAQ firmware design is presented on instance of the Zynq System on the Chip device family. The Zynq-devices from Xilinx are of particular interest as Trenz Electronic has a hereupon basing flexible module system. Besides the performance of its implemented firmware design, the feasibility of a DAQ relies on its achievable resolution limits. As the resolution limit depends on the signal-noise-ratio (SNR) and nonlinearity properties of the DAQ implemented FADC card, its accurate determination is especially important. The evaluation of such eligible FADC cards requires a test setup whose signal integrity and nonlinear behavior must exceed the already high requirements of the FADC under evaluation. In practice, eligible test setups require high spendings and efforts that mostly prevent an implementation of such a setup in an experimental environment. A focus of this thesis was the development of alternative nonlinearity determination procedures that facilitate a sufficient precision with default instrumentation. As the firmware and the ADC evaluation topics significantly differ, it was decided to split the thesis in two segregated parts. The first part is centered around the Zynq SoC devices as substitute of the current FlashCAM DAQ. The second part is dedicated to ADC nonlinearity determination.

#### Main results of the evaluation are

The "High Performance" (HP) ports of the Zynq-UltraScale+ devices have a total interrupt free memory bandwidth of at least 2.4 GB/s. In enhanced designs with a parallel running 1 Gb/s ethernet unit, the CPU remains a concurrent memory read-write bandwidth of at least 0.5 GB/s. In Zynq-7000 devices an interrupt-free implementation of the HP ports can be thwarted by the poor memory access performance of the CPU. As the HP ports have direct access to the external DDR memory their interrupt-free bandwidth can be used to develop designs that do not require FPGA internal

Abstract iii

- RAM. This is especially useful in HPGe-spectroscopy, as where the digitized waveform length and hence the event data buffer capacity is decisive.

- The "Accelerator Coherency" Port (ACP) enables (interrupted) data writes into the CPU Cache of the Zynq devices. The developed ACP-CMA framework has a bandwidth of up to 2.4 GB/s. The CPU can access the data without stalling a concurrent ACP operation in all Zynq devices. This is important as the CPU must handle all data processing requirements ("event building") of the ethernet transfer. A concurrent maximum event building performance of 0.7 GB/s was determined. The real maximum event building performance is likely higher. It should be noted that a real application can face limitations that prevent a continuous operation of the ACP-CMA. These limitations that are not fundamental were not considered in the event building performance investigation. As all Zynq devices have a performant CPU Cache, the ACP-CMA is a feasible solution for all available Zynq devices.

- The new designed FC2.0 prototype firmware design was already used in experimental setups. As application example a HPGe-detector measurement will be shown.

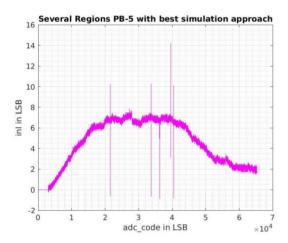

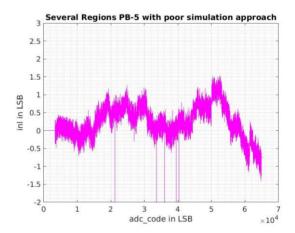

- ADC nonlinearity investigation setups strongly depend on the distortion level of their implemented signal source. In simulations was shown that INL determination procedures exist whose accuracy is only slightly degenerated by the implementation of a nonlinearity distorted pulser. A practical comparison of these new methods with a classic INL determination procedure roughly confirmed the determined INL trend of the new procedures. The methods therefore can be recommended for a practical implementation in future ADC evaluation campaigns.

Abstract iv

## Acknowledgment

At this spot I would like to thank all persons who supported me during my time at MPIK. Many persons have contributed to the success of my thesis, but unfortunately due to lack of space I am not able to mention them all.

First, I would like to thank to Ivan Peric and Werner Hofmann for their willingness to be the referees of my thesis. In my first suggestions the feasibility of the desired new DAQ was utterly unclear as a lot of information was missing and no similar publication was available. Regardless Professor Peric immediately offered his support. The adaption of the originally suggested DAQ design (cheap Zynq-7000 device whose firmware transfers a continuous data stream into memory and has an option to do online analysis) soon proved to be not feasible. Though this unexpected outcome, both referees were still eager to participate in the development process of a modified FlashCam 2.0 prototype. For this support I want to express my special gratitude.

Furthermore I would like to express my deepest sense of gratefulness to my supervisor Bernhard Schwingenheuer. His insightful comments, valuably advices and unremitting commitments are the pillar of this thesis.

I am thankful to my fellows Thomas Kihm, Michael Bantel, Christian Bauer and Christian Föhr. Their substantial knowledge of FlashCam (and many other loosely connected topics) was the basis requirement for the succeeded thesis.

## Table of Content

| Z  | usammentas    | sung                                                                              | 1      |

|----|---------------|-----------------------------------------------------------------------------------|--------|

| A  | bstract       |                                                                                   | iii    |

| A  | cknowledgn    | nent                                                                              | 5      |

| T  | able of Cont  | ent                                                                               | 6      |

| Li | ist of abbrev | iations                                                                           | 11     |

| Li | ist of symbo  | ls                                                                                | 13     |

| 1  | Introduct     | ion                                                                               | 1 -    |

| 2  | General 1     | DAQ consideration                                                                 | 3 -    |

|    | 2.1 Ana       | log signal chains for HPGe-detectors                                              | 5 -    |

|    | 2.2 Neg       | ative digitization effects on resolution                                          | 5 -    |

|    | 2.2.1         | Noise and Jitter in digitization                                                  | 6 -    |

|    | 2.2.2         | Temperature drift effects of the reference voltage and ADC gain-offset amplifiers | 6 -    |

|    | 2.2.3         | Crosstalk in ADCs                                                                 | 7 -    |

|    | 2.2.4         | ADC Nonlinearity                                                                  | 7 -    |

| 3  | Zynq De       | vice Family                                                                       | 8 -    |

|    | 3.1 Gen       | eral FPGA architecture and FPGA architecture in Zynq-Devices                      | 9 -    |

|    | 3.2 Prod      | cessing system architecture in Zynq devices                                       | 11 -   |

|    | 3.2.1         | Application Processing Unit (APU)                                                 | 14 -   |

|    | 3.2.2         | Coherent Memory Access Management                                                 | 14 -   |

|    | 3.2.3         | DDR Controller                                                                    | 16 -   |

|    | 3.3 The       | Processing System/Programmable Logic Interface in Zynq-Devices                    | 18 -   |

|    | 3.3.1         | M-GP and M-LPD ports                                                              | 19 -   |

|    | 3.3.2         | S-HP ports                                                                        | 19 -   |

|    | 3 3 3         | S-ACP Port                                                                        | - 20 - |

|   | 3.3 | .4    | S-HPC Ports                                             | · 22 -        |

|---|-----|-------|---------------------------------------------------------|---------------|

| 4 | Fla | shCar | n 2.0 Prototype Firmware Design                         | - 23 -        |

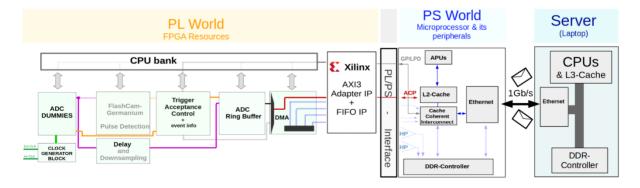

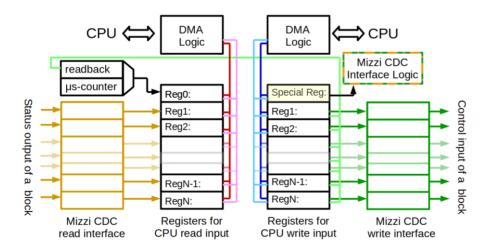

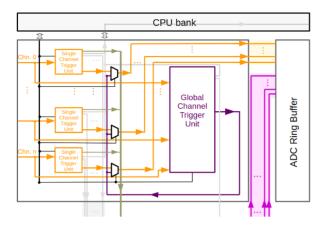

|   | 4.1 | Glo   | bal FC2.0 prototype firmware design                     | - 24 -        |

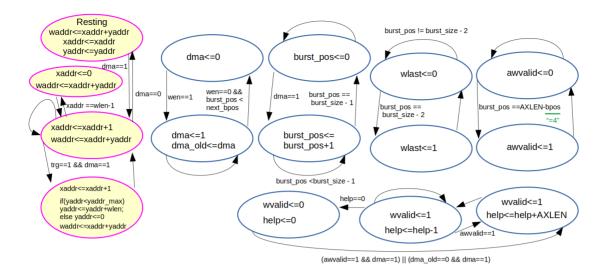

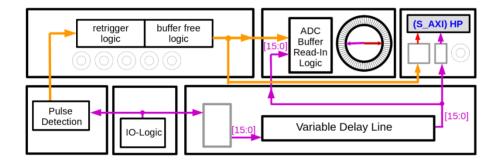

|   | 4.2 | DM    | A design                                                | - 28 -        |

|   | 4.2 | .1    | ARM AMBA protocol                                       | - 29 -        |

|   | 4.2 | .2    | GP/LPD IO unit                                          | - 34 -        |

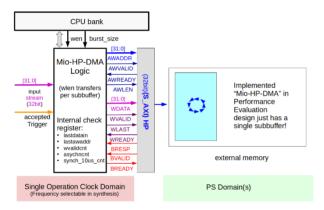

|   | 4.2 | .3    | HP-DMA design                                           | - 35 -        |

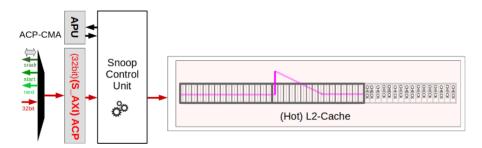

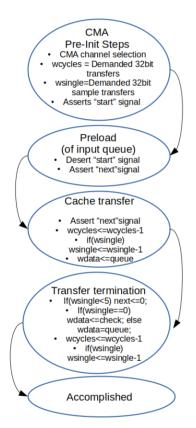

|   | 4.2 | .4    | ACP-CMA design                                          | - 38 -        |

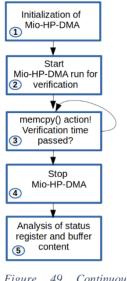

| 5 | Fla | shCar | n 2.0 Prototype Software Design                         | - 43 -        |

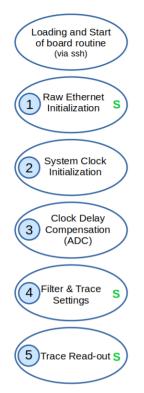

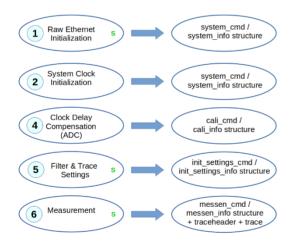

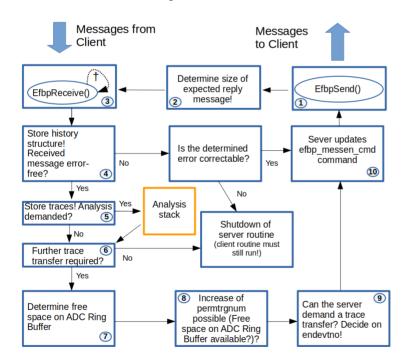

|   | 5.1 | Тур   | ical sequence of a FC2.0 prototype measurement          | - 43 -        |

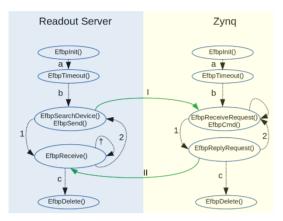

|   | 5.2 | The   | FC2.0 ethernet read-out protocol                        | - 44 -        |

|   | 5.3 | DM    | A frameworks in FC2.0 prototype                         | - 47 -        |

| 6 | Fla | shCar | n 2.0 Prototype evaluation                              | - 49 -        |

|   | 6.1 | Eva   | luated Trenz Zynq modules                               | · 49 <b>-</b> |

|   | 6.2 | Setu  | p Zynq-APU performance evaluation                       | - 55 -        |

|   | 6.3 | Res   | ults Zynq-APU performance evaluation                    | - 56 -        |

|   | 6.4 | Setu  | p for performance evaluation of ACP-CMA                 | - 58 -        |

|   | 6.4 | .1    | Bare ACP-CMA performance setup                          | - 58 -        |

|   | 6.4 | .2    | Setup for ACP-CMA event building performance evaluation | - 59 -        |

|   | 6.5 | Res   | ults for performance evaluation of ACP-CMA              | - 60 -        |

|   | 6.5 | .1    | Default ACP-CMA performance                             | - 60 -        |

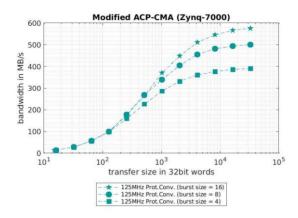

|   | 6.5 | .2    | Possible ACP-CMA variations and their performance       | - 62 -        |

|   | 6.5 | .3    | ACP-CMA event building performance results              | - 66 -        |

|   | 6.6 | Setu  | p for performance evaluation of HP-DMA                  | - 70 -        |

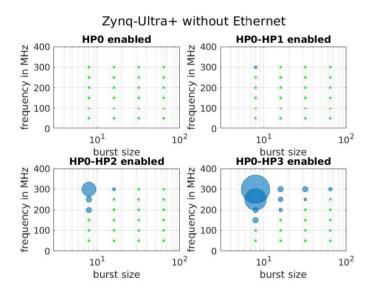

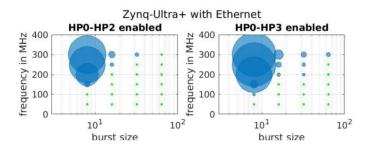

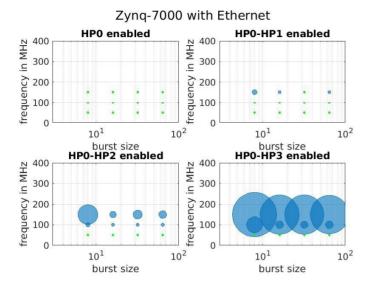

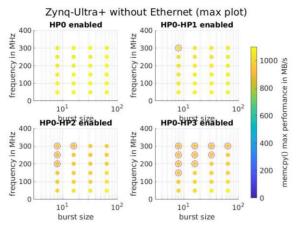

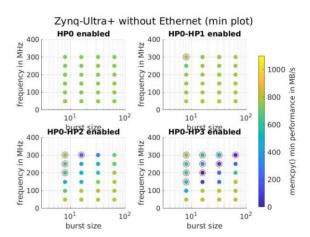

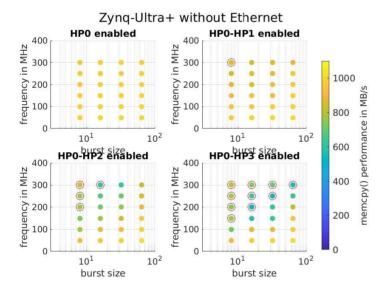

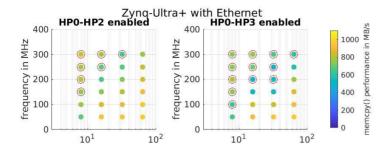

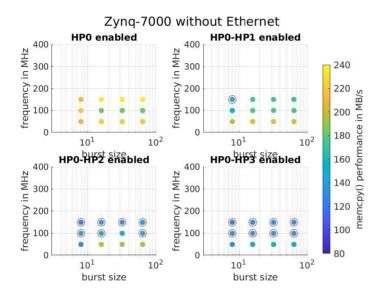

|   | 6.7 | Res   | ults of HP-DMA                                          | - 72 -        |

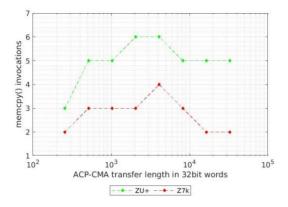

|   | 6.7 | .1    | Interrupt rate in dependence on the parameter settings  | - 73 -        |

|   | 6.7 | .2    | Memcpy performance                                      | - 76 -        |

|   | 6.8 | Sun   | nmary                                                   | - 80 -        |

| 7 | AD  | C noi | nlinearity                                               | 89 -  |

|---|-----|-------|----------------------------------------------------------|-------|

|   | 7.1 | Def   | initions of differential and integral nonlinearity       | 89 -  |

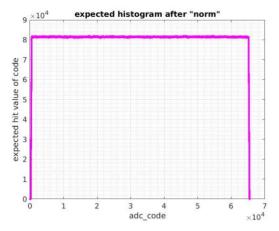

|   | 7.2 | Clas  | ssic histogram test                                      | 91 -  |

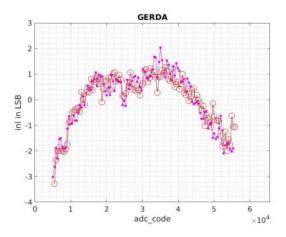

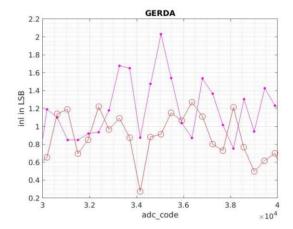

|   | 7.3 | INL   | determination in GERDA                                   | 92 -  |

|   | 7.4 | INL   | determination in Majorana                                | 94 -  |

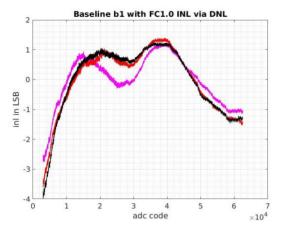

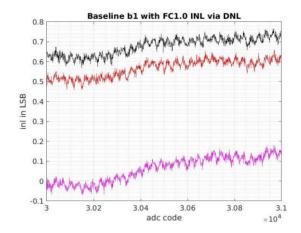

|   | 7.5 | FC1   | .0 INL determination nominee approach in FC2.0           | 97 -  |

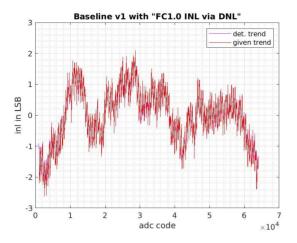

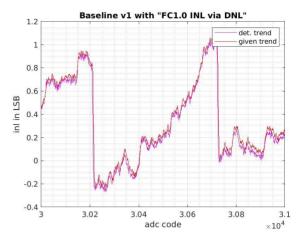

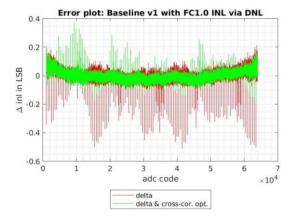

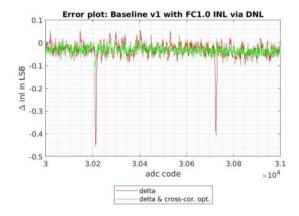

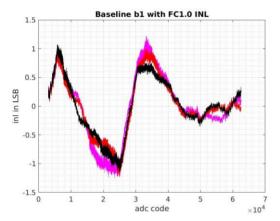

|   | 7.5 | .1    | The FC1.0 INL determination                              | 100 - |

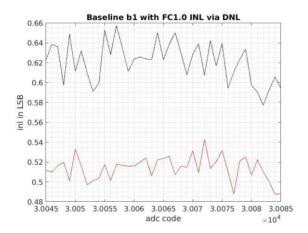

|   | 7.5 | .2    | The FC1.0 INL via DNL determination                      | 103 - |

|   | 7.6 | INL   | correction in HPGe-spectroscopy                          | 104 - |

| 8 | AD  | C noi | nlinearity investigation setups and their results        | 106 - |

|   | 8.1 | Sim   | ulation setups and procedure                             | 107 - |

|   | 8.1 | .1    | Nonlinearities in the simulation                         | 107 - |

|   | 8.2 | Gen   | eral simulation procedure                                | 108 - |

|   | 8.3 | Sim   | ulation results                                          | 110 - |

|   | 8.3 | .1    | FC1.0 results                                            | 110 - |

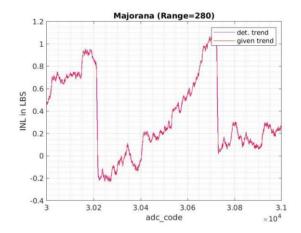

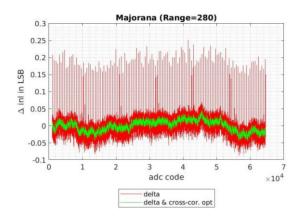

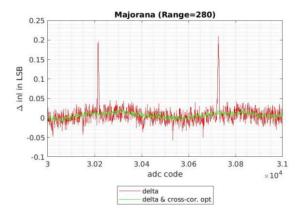

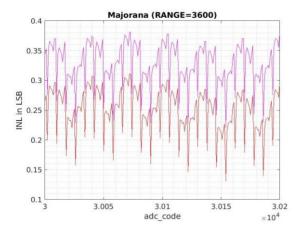

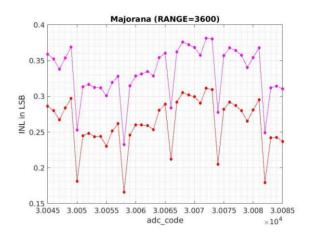

|   | 8.3 | .2    | Majorana results                                         | 118 - |

|   | 8.3 | .3    | Compare between Majorana and FC1.0 methods               | 122 - |

|   | 8.4 | Setu  | up of the used experimental INL determination approaches | 126 - |

|   | 8.4 | .1    | FC1.0 nonlinearity determination setup                   | 127 - |

|   | 8.4 | .2    | Majorana setup                                           | 130 - |

|   | 8.4 | .3    | GERDA setup                                              | 131 - |

|   | 8.5 | Res   | ults of the experimental INL determination setups        | 132 - |

|   | 8.5 | .1    | FC1.0 INL determination setup                            | 132 - |

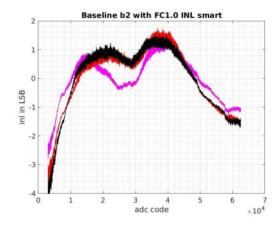

|   | 8.5 | .2    | Majorana setup                                           | 138 - |

|   | 8.5 | .3    | GERDA results                                            | 141 - |

|   | 8.6 | Setu  | p for a γ-ray spectrum measurement with a HPGe detector  | 142 - |

|   | 8.7 | Res   | ults of γ-ray spectrum measurment                        | 143 - |

|   | 8.8 | Sun   | nmary INL determination                                  | 147 - |

| 8.9       | Final prospect                                                 | 151 -               |

|-----------|----------------------------------------------------------------|---------------------|

| List of t | figures                                                        | 153                 |

| List of t | tables                                                         | 159                 |

| List of 1 | references                                                     | 161                 |

| List of 1 | publications                                                   | 166                 |

| Curricu   | lum vitae                                                      | ke nicht definiert. |

| Append    | lix                                                            | I                   |

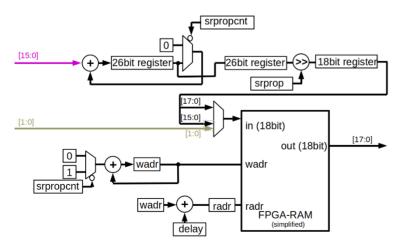

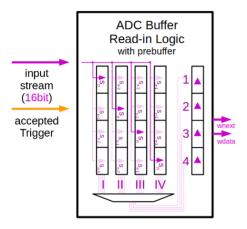

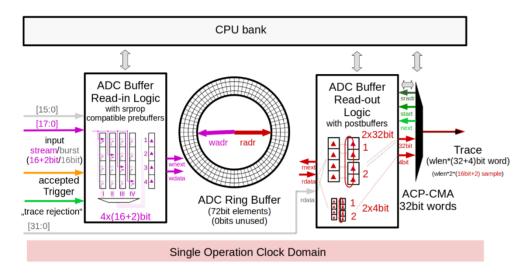

| A.1       | Firmware design: ADC data read in dummy design                 | I                   |

| A.2       | Delay and down sampling block design                           | III                 |

| A.3       | Firmware design: CPU bank block in design                      | V                   |

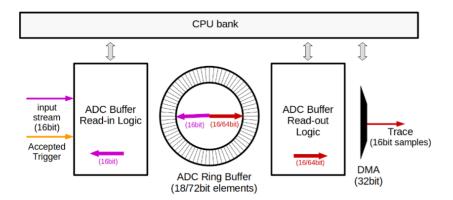

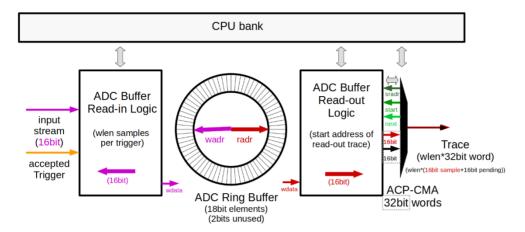

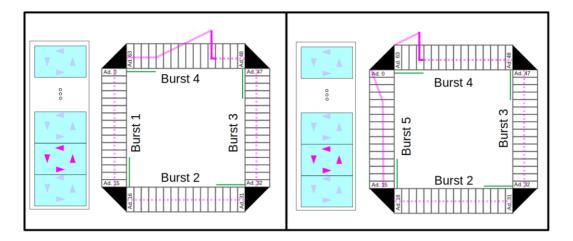

| A.4       | Firmware design: ADC Ring buffer design                        | VIII                |

| Α.        | 4.1 Simple ADC Ring buffer design                              | IX                  |

| Α.        | 4.2 Efficient ADC Ring Buffer                                  | XII                 |

| Α.        | 4.3 FC 2.0 prototype ADC Ring Buffer design                    | XIV                 |

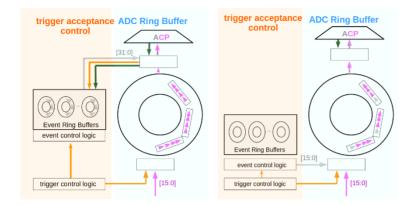

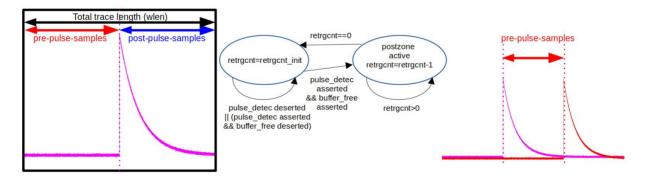

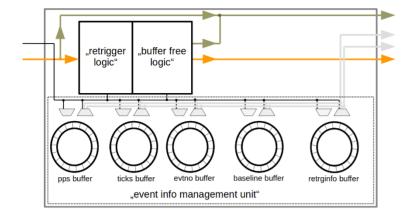

| A.5       | Firmware design: Trigger acceptance control design             | XVIII               |

| A.:       | 5.1 Components of the FC 2.0 Trigger acceptance control block  | XXV                 |

| A.6       | Firmware design: Practical implementation of continuous HP-DMA | XXIX                |

| A.7       | Software Design: User Space DMA Device Driver Implementation   | XXXIV               |

| A.8       | Software design: The FC2.0 ethernet read-out protocol          | XXXVI               |

| A.9       | Software design: Server-Read-Out Routine                       | XXXIX               |

| A.        | 9.1 Read-Out Routine procedure in Measurement State            | XXXIX               |

| A.        | 9.2 Trace read-out state machines                              | XLI                 |

| A.        | 9.3 Overview read-out server analysis chain                    | XLIV                |

| A.10      | Speed 2: Detailed operation performance discussion             | XLVIII              |

| A.11      | Setup Zynq netcat performance evaluation                       | L                   |

| A.12      | Results Zynq netcat performance evaluation                     | LI                  |

| A.13      | Setup for the GP/LPD-IO unit performance evaluation            | LIII                |

| A.14      | Results of the GP/LPD-IO unit performance evaluation           | LV                  |

| A.15 | Res  | sults of event building performance evaluation    | LVII   |

|------|------|---------------------------------------------------|--------|

| A.1  | 5.1  | Results with the Znyq-7k                          | LVII   |

| A.1  | 5.2  | Results with the Zynq-UltraScale+                 | LIX    |

| A.16 | Setu | up of the PB-5 INL determination approach         | LXII   |

| A.17 | Res  | sults of the PB5 INL determination approach       | LXV    |

| A.18 | Sign | nal processing chain in HPGe-detector experiments | LXVII  |

| A.1  | 8.1  | Shaping                                           | LXIX   |

| A.1  | 8.2  | Pole-zero-compensation (PZ) and its DC issue      | LXXI   |

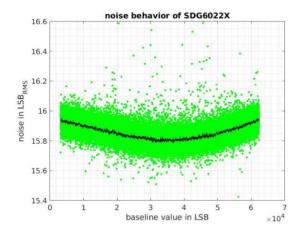

| A.1  | 8.3  | Baseline reconstruction                           | LXXI   |

| A.19 | Exa  | ample DAQ designs on FC2.0 prototype basis        | LXXIII |

| A.1  | 9.1  | First experiment: HPGe-array DAQ                  | LXXIII |

| A.1  | 9.2  | Second experiment: PMT-array DAQ                  | LXXIV  |

| A.1  | 9.3  | Third experiment: Ultra-High-Event Rate DAQ       | LXXVI  |

## List of abbreviations

ADC Analog to Digital Converter

**Amp** Amplifier

**APU** Application Processing Unit

**AXI4** Advanced eXtensible Interface 4 (protocol)

CM Common Mode

**CSA** Charge Sensitive Amplifier

**DAC** Digital to Analog Converter

**DAQ** Data acquisition (system)

**DC** Direct current

**DDR** Double Data Rate

**DMA** Direct Memory Access

**DMM** Digital multimeter

**DNL** Differential Nonlinearity

**DSP** Digital Signal Processing

**EMI** Electromagnetic interference

FC FlashCam

**FPGA** Field Programmable Gate Array

FR Full range

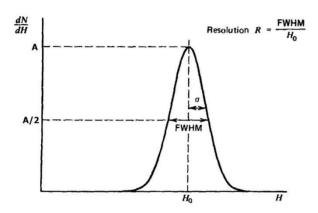

**FWHM** Full width at half maximum

**GERDA** Germanium Detector Array (experiment)

**HPGe** High Pure Germanium (detector)

HV High Voltage

**INL Integral Nonlinearity** IO Input Output IP **Intellectual Property IPC Inter Process Communication ISA** Instruction Set Architecture L1 Level 1 L2 Level 2 LSB Least significant bit **LVDS** Low-voltage differential signaling **MGT** Multi Gigabit Transceiver **MPIK** Max-Planck-Institut für Kernphysik (Heidelberg-Germany) OS Operation System PL Programmable Logic **PMT** Photomultiplier Tube PS **Processing System RAM** Random Access Memory **RMS** Root meets square **SNR** Signal-Noise-Ration SoC System on the Chip **TUM** Technische Universität München (Munich, Germany) Z7k Zynq-7000 ZU+ Zynq-UltraScale+

# List of symbols

| $\Delta oldsymbol{U_{c_{ideal}}}$ | Ideal bin width of the ADC                 |

|-----------------------------------|--------------------------------------------|

| $U_{FR}$                          | Full range input voltage of ADC            |

| $U_c[i]$                          | Transition code voltage of ADC Code i      |

| G                                 | Gain                                       |

| $F_S$                             | Sample frequency                           |

| S                                 | (ADC Code) Value of sample                 |

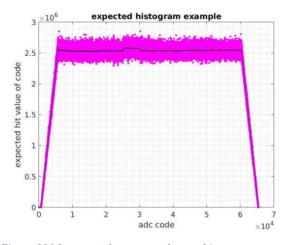

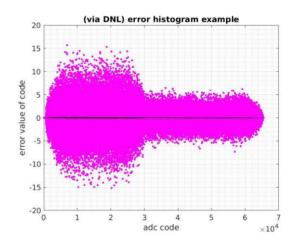

| $n_{ideal}(i)$                    | Expected Count Histogram Bin of ADC code i |

| $n_{real}(i)$                     | Real Count Histogram Bin of ADC code i     |

| M                                 | Waveform size in samples                   |

| k                                 | Sample position in waveform {0M-1}         |

| N                                 | Bit width of ADC                           |

| i                                 | ADC code $\{02^N\}$                        |

## 1 Introduction

In several experimental collaborations of MPIK, for instance in HESS, CTA and LEGEND-200, the FlashCam (FC) DAO is a key component for the experiment's successful operation. FlashCam is especially popular as it is versatile and cheap (in the cheapest setup 70€ per channel). The cheap price and its high scalability are an essential advantage together with the adaptation to experiment specific needs. For instance, in the CTA experiment the FlashCAM DAQ must comprise up to 2304 channels in one global trigger domain. A contrary application example is the use in HPGe-detector evaluation setups of the former GERDA collaboration that comprise merely a single channel. In this example FC is used to due to its high signal quality. Though both experiments differ strongly, their setups have the FC design philosophy in common. They use exactly the same boards and are being controlled by a central (ethernet) read-out server that has the complete read out responsibility. The experiments merely differ in the number of boards and server performance. FlashCam is popular, but due to the estimated end-of-life of the implemented Spartan-6 FPGA a successor development was started. In the meantime, Xilinx strongly promotes its available successors series, including its Zynq device family. The Zynq-device family is especially appealing to the successor DAQ "FlashCam2.0" (FC2.0) as its hard-wired ARM processors could enable an event building and analysis framework directly operating on the DAQ board. Another important point of a DAQ is its FADC card. Using a high-quality ADC is essential, especially in HPGe-spectroscopy experiments like LEGEND. A development of a FC successor is an opportunity to improve the FADC cards. As the progress in ADC technology is not as fast as in microprocessors (or FPGAs) the FADC evaluation setup must be capable to quantify reliably smallest distinctions in the signal quality. The demanded high resolution makes such setups particular challenging.

The target of this thesis mainly was mainly the inspection of the Zynq family as potential successor devices for the next generation FC2.0 DAQ. FC2.0 must preserve all supreme properties of FC1.0 and therefore just a limited selection of the Zynq devices is a potential nominee. Note that the device selection was mostly driven by the cost. Besides determining the Zynq device performance by implementation of highly specific test designs, a potential FC2.0 firmware was developed. This "successor" firmware misses merely some specific features of the designated FC2.0 trigger system and otherwise already fulfills all requirements of FC2.0. Furthermore, a prototype DAQ with the most likely Zynq nominee was developed. The FC2.0 prototype DAQ uses the new developed firmware and was already used for first HPGe-spectroscopy measurements.

The nonlinearity characterization – especially the integrated nonlinearity (INL) – of an ADC developed into a second central topic of this thesis. In various publications the influence of the ADC nonlinearities and their compensation is elaborated. Also, in various works it is described how to measure the INL with a signal

pulser of sufficient resolution. But less frequently it is discussed what sufficient resolutions actually means and even less how to respond in cases when such a signal quality is not achievable by additional filtering. The latter will be decisive for INL determinations in experimental environments, at which it is not possible to input a pulser signal of the demanded quality. In this thesis two promising alternative INL determination methods are investigated.

## 2 General DAQ consideration

The new "FC2.0 DAQ" has the aspiration to be applicable in many experiments, especially those using PMTs or HPGe detectors. A real data acquisition (DAQ) system which can be implemented in a plenty of experiments is mostly not the DAQ system which offers the best price-performance ratio. So experimental designers always used to consider the DAQ (components) costs, the strongly needed experimental requisites and the wishful capabilities and then try to find a balance. Some important DAQ properties in this process are:

- Maximum channel amount (in one clock domain/per board)

- Maximum event rate

- Available Sample Rates and Sample Bit Width

- (Effective) Signal Noise Ratio (SNR)

- Nonlinearity (of signal chain)

- Signal stability (thermal influence)

- Available readout interfaces (Ethernet, VME Bus, PCIe, USB)

- Available trigger and synchronization links

- Temporal trigger resolution

- Available trigger schemas

- Maximum readout bandwidth (between Readout Server and Single Board)

- Software support

The final DAQ design is influenced by detector specific signal processing requirements. Before the advent of the digital signal processing with eligible DSPs and FPGAs the signal processing in pulse spectroscopy was done with analog electronic and just the last step included digitization. A proper modified digital signal processing chain in pulse spectroscopy adopts analog signal processing, but it should not be build up as an 1:1 replica in order to gain the advantages of digital processing. It is important to consider that digital signal processing chain comprises a FPGA with its main task to trigger and record an event and a second segregated signal processing chain in the analysis routine on a segregated analysis server that transforms the event data into an energy spectrum. How to arrange such an interplay is unfortunately poorly discussed in common recommended textbooks like [1] and [2]. At MPIK the DAQ development efforts iterated in the FlashCam DAQ, but FlashCam is for sure not the only possible solution. It is worth to note that the optimal signal processing of PMTs and HPGe-detectors is different, and these differences must be considered in FlashCam too.

Though in all nowadays experiments the resolution is getting improved by enhanced digital filtering methods, a well-designed analog setup of the DAQ is still important. A bad designed analog signal chain

can charge the signal with hum and noise so far, that the final analysis conditions are out of reach despite usage of latest digital analysis approaches. Chapter 2.1 is therefore focused on the analog components of the DAQ signal chain which affect the filter settings of the final analysis.

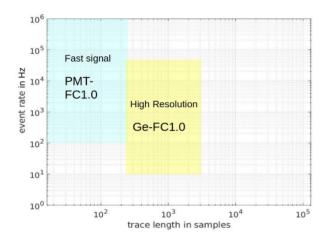

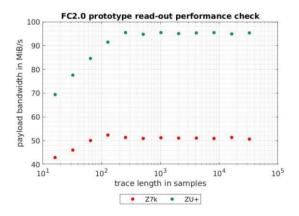

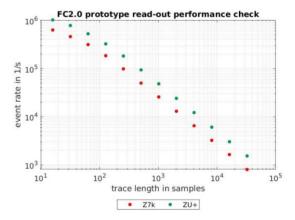

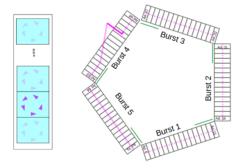

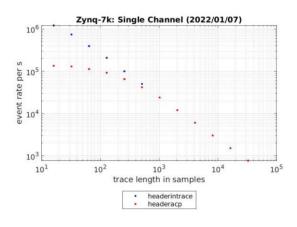

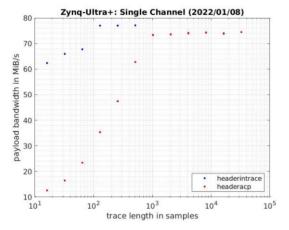

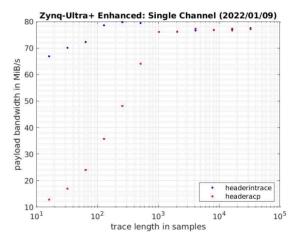

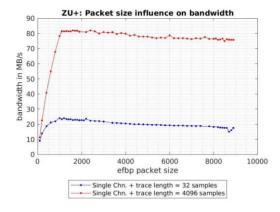

The strong focus on bandwidth in the performance elaboration chapters of this thesis is caused by the linear relation between maximum event rate and readout bandwidth. This relation is important as experimental PMT/HPGe-detector setups need to require a minimum event rate that the DAQ must handle without event loss. Otherwise in this experiments coincidence analysis would not be possible. Figure 1 lists typical trace lengths and event rates for common PMT/HPGe-detector FC1.0 setups. Pay attention that experiments exist that violate the limits of Figure 1. For instance, LEGEND-200 would be a contrary HPGe-detector example where the majority of the measurement campaign is done with an event rate below 1Hz. An event rate in the kilohertz region it only has during calibration.

Figure 1 Overview on common FC experimental setups and their event rate/trace length requirements. It is important to note that the experimental setups also differ in sample rate. A typical sample rate for PMTs is at least 250MHz. HPGe-detector systems usually have a higher resolution, but also a lower sample rate. The trace length (and the sample rate) is also driven by the used preamplifier circuit and not only by the detector type.

The upper limit of the trace lengths in Figure 1 is motivated by feasible bandwidth considerations of a DAQ and not all detectors may be eligible for this rate. The upper limit is highly setup specific and therefore the event rate indications in Figure 1 must be observed with some caution. The bottom limit of the trace length is given by the analysis requirements. They differ a lot and therefore the specifications in Figure 1 are only a good guess trend. The (permanently) stored event data has to consider a given format which contains all required information in an inherent structure. The required information in PMT/HPGe-experiments is frequently the signal trend for a region of interest (already introduced under the term "trace"), the systems point of time and the channel identifiers. All tasks which belong to the management of this structure are part of the so-called event building process. On command of the read-out server the FC event building is done locally on the FPGA boards without any further server support. In fact, in FC the server only verifies and reassembles the received ethernet packets. Hence the major workload of the event building process has to

be done on the boards. This makes sense, as the reaction time of the server influences the systems performance and therefore all tasks which can be done in hardware should not be done by the server.

#### 2.1 Analog signal chains for HPGe-detectors

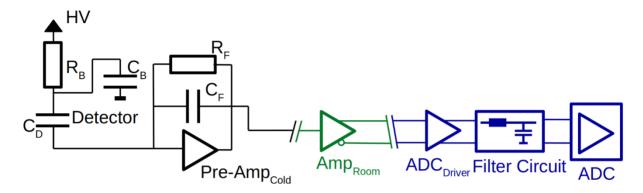

In this chapter it is just assumed that the best possible resolution is given by the detector and the analog signal chain has to comply with this resolution. Remember that the possible resolution and the time range of signal strongly depends on the detector type. Figure 2 depicts a HPGe-detector single channel analog signal path with all main components.

Figure 2 Analog signal chain of a HPGe-detector experiment. The analog signal chain has a front-end electronics part (black), buffers (green) and digitization electronics (dark blue).

The analog signal chain consists out of the front electronics (black components in Figure 2), buffers (green) and the digitization electronics (dark blue). The front-end electronics is centered around the detector. The HPGe-detectors need a high voltage (HV) supply to bias the detector. The required voltage level and operation currents depend on the implemented detector. Another central component of the front end-electronics is the preamplifier (preamp). In this thesis the corresponding topics are only a side elaboration and therefore the discussion is omitted here. More information is available for instance in [1], [2] and [3]. Designing a proper FADC card is a challenge on its own. Its filter circuits must consider the famous "aliasing" caused by ADC sampling, but the FADC cards design also must tackle other effects. An instance of a less known issue are the charge spike injections caused by sample switching of the ADC. The charge injections can be attenuated by so called "absorption" filters [4]. In the most DAQ systems with a proper designed FADC card the major noise contributor is the charge sensitive preamplifier and not the FADC card. But a proper designed FADC card is the error source of other deterministic signal issues that are more elaborately discussed in chapter 2.2.

#### 2.2 Negative digitization effects on resolution

The resolution is one of the key specifications of a DAQ. In the analog signal chain of the HPGe-spectroscopy DAQ the noise behavior of the Front-End electronics and the resolution of the FADC card are decisive for the DAQ resolution. The Front-End electronics has a minor part in this thesis. Therefore, the

discussion of Front-End electronics influence on the final DAQ resolution is omitted. The resolution of a HPGe-spectroscopy DAQ that uses a properly designed FADC card is commonly dominated by the influence of the Front-End electronics and not be the FADC card. This is especially true for its noise characteristics that mainly determine the needed signal shaping approach.

#### 2.2.1 Noise and Jitter in digitization

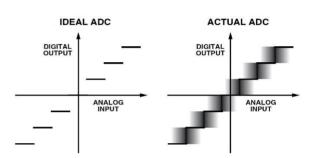

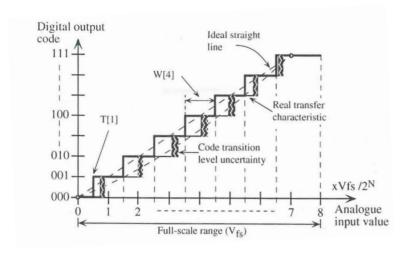

The analog signal inputs of the ADCs also act as noise source and therefore influence the final resolution of the DAQ system. As the ADC input noise influences the ADC code transition voltages (Figure 3), it is also labeled as code transition or as code edge noise. Many different ADC types with significant design (differences in their noise filtering properties) exist and consequently the effective noise behavior varies

much. Data sheets contain the code edge noise of the ADC. Besides the code edge noise, ADCs have quantization noise. An ADC maps a continuous signal into a limited discrete signal range. This quantization means information loss. The quantization information loss correlates with the signal trend and therefore it is not a real noise, as noise is an uncorrelated signal. With real varying

Figure 3 Input noise influence on code transition [5]. The ideal ADC of this example has no input noise and therefore its code transition voltages are constant.

signals (with just loose patterns), the effects of the rounding loss look like a random error and therefore the term quantization noise was impressed. The portion between the (ideal) quantization noise and the analog ADC input signal is the signal quantization ratio SNR<sub>Quant</sub> which follows as

$$SNR_{Ouant} \approx 6.02 \cdot N + 1.76dB \tag{1}$$

The above equation is an approximation which is valid for an ADC with 7bits or higher. For instance, in [6 S. 100] an elaboration of SNR<sub>Quant</sub> is done.

#### 2.2.2 Temperature drift effects of the reference voltage and ADC gain-offset amplifiers

In ADCs the reference voltage serves as comparison voltage in the ADCs comparator operations and consequently has a direct influence on the ADC output codes. The internal composition of the ADC determines the temperature drift effects on the ADCs gain and offset. Simply said, with increasing ADC/DAC resolution the stability of reference voltage gets more critical. Designing a reference voltage of sufficient stability for FADC cards in HPGe spectroscopy is a non-trivial task. ADC manufactures provide several designer guides to combat the connected issues. Note that a stable reference voltage does not guarantee a stable ADC gain and offset as these ADC properties not only rely on the voltage reference. The

operation of such a FADC card is therefore only permitted in an environment with stable temperature or in application tasks whose time duration is sufficiently small.

#### 2.2.3 Crosstalk in ADCs

Typical sources of crosstalk in ADCs include [7]

- Power supply coupling: In this case digital currents pulling on a power supply which is shared with an analog supply

- Capacitive crosstalk between digital and analog signals: Digital signals which are transmitted close to the analog signal path can couple into the analog signal path.

- Capacitive crosstalk between analog signals: If an ADC has more than one input channel, also the analog input signal of input x can couple into the analog signal path of input y.

- Ground ("bouncing") currents: Return currents effect a local movement of the ground potential. As the ground potential is the reference potential, this behavior distorts the signal value.

Crosstalk is therefore strongly influenced by the chosen ADC design and the ADC implementation in the FADC card. In the thesis only a single channel FADC is investigated.

#### 2.2.4 ADC Nonlinearity

The derivation of the quantization noise (equation (1)) is valid for ideal, memory-less ADCs whose nominal transfer function is a linear staircase function with intervals of the same size (Figure 3). Manufacturing such an ideal ADC is not possible. The staircase function of a real ADCs has intervals of deviating size and is also dependent on the input signal itself. Commonly ADC data sheets poorly refer to input signal influence on the ADCs nonlinear behavior and surprisingly it is rarely discussed in literature. It is possible to show that the ADCs nonlinear behavior influences the typical performance metrics of a  $\gamma$ -ray spectrum. Some of its major consequences in HPGe spectroscopy are discussed for instance in [3]. In HPGe spectroscopy a precise knowledge of the nonlinear ADC behavior is a critical design key parameter. As not always an ADC with a sufficient nonlinearity characteristic is available, post-measurement correction strategies were developed. An important compensation technique, that will be elaborated in chapter 7.4, is for instance given by the MAJORANA collaboration [8]. The concepts of differential nonlinearity (DNL) error and integral nonlinearity (INL) error will be introduced as feasible description of the real ADC transfer function behavior. Chapter 7.1 is dedicated to them.

## 3 Zynq Device Family

In 2000 Xilinx announced its first "Virtex II Pro" hybrid devices with PowerPCs CPUs from IBM. Over the time the PowerPC architecture declined and the market position of ARM ecosystem steadily increased. In 2011 Xilinx unveiled its Zynq-7000 family as "the industry's first Extensible Processing Platform". Soon after Xilinx also employed the System on the Chip abbreviation "SoC" in its Zynq publications. Figure 4 shows the hybrid structure and the Zynq components. Note that the FPGA area is labeled as "Programmable Logic" (PL) and the Embedded CPU as "Processing System" (PS). Zynq systems use a CPUs out of the ARM ecosystem. ARM is with its SoC infrastructure the leader of the mobile segment and supports the full hardware/software stack development. ARM CPUs commonly have their own Linux maintaining line.

- CPU

- DDR Controller (with access to external DDR RAM)

- Gigabit Ethernet Controller

• ...

- Logic

- IO-Banks

- Clock (Management) Resources

- Internal RAM

Figure 4 Hybrid devices consist out of an Embedded Microprocessor with its peripherals and a FPGA fabric area.

2015 Xilinx launched the enhanced Zynq-UltraScale+ family. Table 1 lists the main differences between the series.

PS/PL Interface

Table 1 Main differences between Zynq-7k a. Zynq-Ultra+. Information is out of [9] and [10]

|                          | Zynq-7k                | Zynq-Ultra+                 |

|--------------------------|------------------------|-----------------------------|

| Market launch            | 2011                   | 2015                        |

| CPU Architecture         | ARM Cortex-A9          | ARM Cortex-A53              |

| Main Interconnect in PS  | ARM CoreLink Network   | ARM CoreLink Cache Coherent |

|                          | Interconnect "NIC-301" | Interconnect "CCI-400"      |

| ISA                      | ARMv7 (32bit)          | ARMv8 (64bit)               |

| FPGA Fabric Architecture | Artix-7, Kintex-7      | Zynq-UltraScale+            |

The differences between Zynq-7k and Zynq-Ultra+ devices are significant. In this PhD thesis both series were scrutinized for their eligibility as FlashCam successor devices. More emphasis is given on the Zynq-

UltraScale+ devices because of their better performance. The introduction to the Zynq devices is split in 2 parts. The first part discusses general FPGA architectures and special features of the Zynq devices which are relevant for the FlashCam 2.0 Prototype. The second part is dedicated to the processing system components that significantly influence the performance results of the setup.

#### 3.1 General FPGA architecture and FPGA architecture in Zynq-Devices

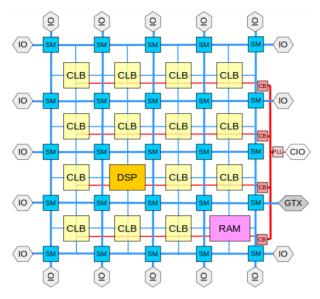

The devices used in this PhD thesis base on 3 different FPGA architectures (Artix-7, Kintex-7, Zynq-UltraScale+). Roughly said, the Artix-7 devices offer the poorest performance, the Zynq-Ultra+ devices the best. The evaluation which was done in the scope of this thesis confirmed the superiority of the Zynq-UltraScale+ fabric. The firmware setups for the FC2.0 prototype do not have the intention to determine the performance/channel limit of the architecture. The main intention is to determine the feasible readout performance. But this performance is mainly given by the PS infrastructure of the device, not by the PL architecture which mainly influences the possible channel count per device and the operation frequency of the signal processing. The Zynq device implemented in the future FC2.0 card will depend on the application and its requirements. In some low channel count applications, the Artix-7 fabric architecture is sufficient. Requirements of other applications will have a better match with the Zynq-UltraScale+ architecture. The precise FPGA architecture of the devices under test is a company secret of Xilinx. In order to support the customers in their development process, Xilinx published an extensive documentation. The published documents do not have the elaboration depth which is required to enable an utter reengineering of the FPGA architecture. Commonly they just give a glimpse to understand the high level of the architecture. As all FPGA have some common blocks, a tiny FPGA example could have an architecture like in Figure 5.

Figure 5 Model of a simple FPGA device Extended and revised version of original figure out of [11 S. 440]. The setup is simplified and far from a realistic implementation. For instance, already the first FPGA, the XC2064, was consisting out of 64 CLBs.

The simplified FPGA architecture in Figure 5 consists out of

- IO-Resources (IO (IO circuitry of pins), GTX (Multigigabit Transceiver/Receiver Pins)

- Clock Resources (CB (Clock Buffer), PLL (Phase Locked Loop), CIO (pins with clock optimized IO circuitry)

- (Configurable) Logic Resources (CLB)

- Routing Resources including Switch Matrix (SM)

- (Addressable) Memory Resources (RAM)

- Integrated Intellectual Property (IP)

Resources (for instance "DSP" slices that include a multiplier)

Nowadays FPGA devices have all above listed resources in common, but the implemented resources design may differ significantly.

#### 3.2 Processing system architecture in Zynq devices

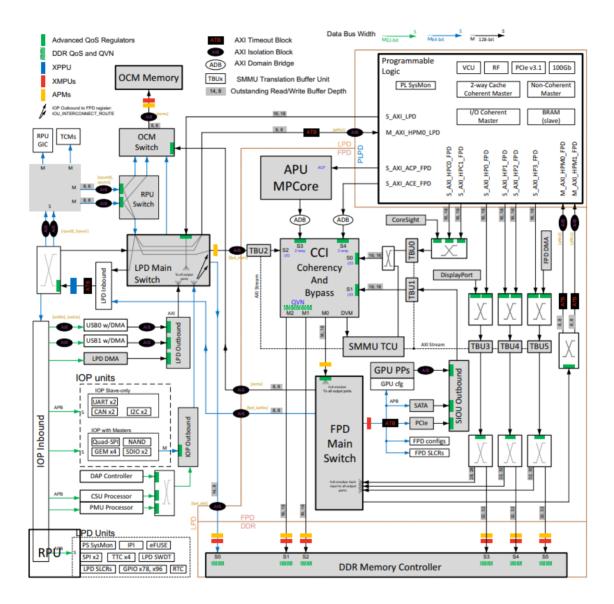

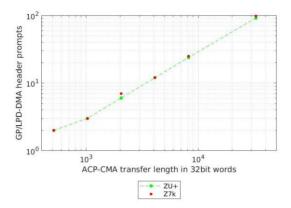

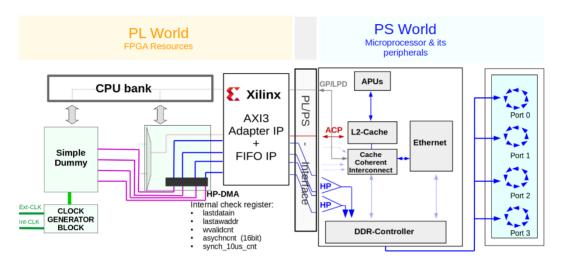

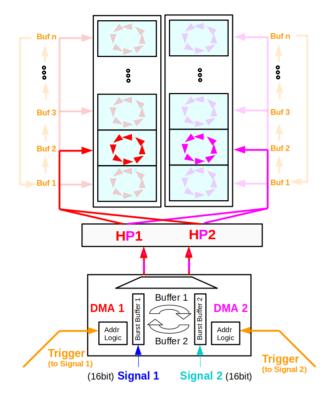

In the Prototype the ARM CPU and its peripherals are responsible for read out control, the event building process and the ethernet transfer. The processing system is the bandwidth bottleneck of the design and thus main contributor to the final performance of the Prototype. The processing system of the Zynq-UltraScale+devices is illustrated in Figure 6.

Figure 6 System Level View PS Zynq-Ultrascale+ [12 p. 1050]

Not all these components are available in the Zynq-7k PS. For instance, the Cache Coherent Interconnect (CCI) and the connected high performance coherent (HPC) port are a Zynq-Ultra+ exclusive component. Such exclusive components are not used in the FC2.0 prototype design. The main point behind this decision is the FC2.0 aspiration to run on Zynq-Ultra+ and Zynq-7k devices. Like already mentioned, the Zynq-

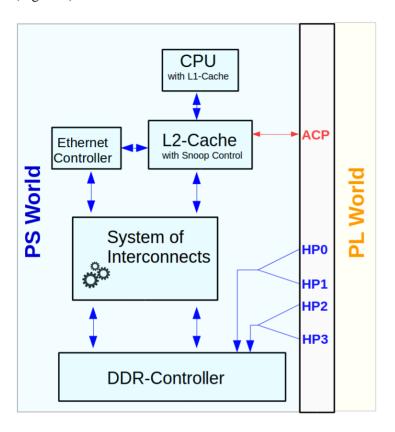

Ultra+ is a further development of the Zynq-7k and therefore both series are sharing a common PS structure (Figure 7).

Figure 7 Common structure elements of Zynq-7k/Zynq-Ultra+ Architecture. The series have further units in common (like the Memory Management Unit (MMU), On Chip Memory (OCM), Real Time CPU, Interrupt Controller, etc). As in the performance evaluation the effect of these components is not discussed, they are not depicted in this figure. Note that the ACP Port (marked red) is directly connected with the Cache, the HP Ports (marked blue) relate to the DDR controller.

The processing system of both Series have a Level-2 Cache (with Snoop Control Unit), Ethernet Controller(s) and a PS/PL-Interface with four High Performance Ports (HP) and one Accelerator Coherent Port (ACP). In both architectures the HP ports are directly connected with the DDR-Controller of the external DDR3/DDR4 memory. The external memory is the main memory of the PS system. A main memory of sufficient size is inevitably required to operate default Linux kernels on the system. The ACP port always has a direct Cache System Access. Both Zynq device families contain a (less performant) Real Time Processing Unit (RPU) and a more performant Application Processing Unit (APU). The performance of the RPU is not adequate for event building tasks in a high performance DAQ system like FlashCam. Again, it should be underlined that event building is mainly an IO task and so the bandwidth of the memory system is the critical system point, the APUs arithmetic/logic operation performance is less significant in event building tasks. In event building tasks its (multi)store/load performance matters!

The motivation of caches is the relative high access time of (external) main memories. If a CPU has a value not in its registers and has no cache system, it must wait until the desired data arrives from its main memory.

In consequence the CPU store/load performance drops. A CPU with cache system has less average waiting time as cache access times are much lower. Building up a memory with the velocity of a cache demands many architectural trade-offs. Simplified, the access time grows with cache size. As with a dwindling cache size the chance of a cache miss increases, the final cache size is a settlement between many considerations. The best performance is commonly achieved with a hierarchical cache system where several caches with different sizes exist. The lowest level L-1 (tightest unit to the CPU) has the highest access rate, but also the smallest size.

The efficiency of the cache system strongly depends on the program sequence. Common code obeys to the "principles of temporal and spatial locality" [13 S. 388]. The cache controller utilizes this knowledge in order to increase the hit rate and preventing useless traffic between memory and cache. The final performance of the cache system strongly depends on the intelligence of the cache controller and its design matching on the cache architecture.

#### 3.2.1 Application Processing Unit (APU)

The architecture difference between the ARM Cortex-A9 (part of the PS in Zynq-7k) and the ARM Cortex-A53 is significant. The ARM Cortex-A9 represent one of the first "high-end application processors" of ARM and was disclosed 2007. Several important ARM SoC concepts were unknown at that time – for example the Big.LITTLE approach (and the corresponding AMBA ACE protocol). The ARM Cortex-A53 ("LITTLE") was unveiled 2012 and could build up on the (multicore) SoC experience which was gained in the meantime. Table 2 lists all important key parameters of both processors.

Table 2 List the most important specifications of the ARM APUs used in the Zynq devices. The listed values are always related to the common value in the corresponding Zynq devices of the FC 2.0 prototype. As ARM sells IP which is adjusted by their customers the official ARM specification differs in a wider range. The information is, if not otherwise marked, out of [12] and. [14].

| APU                          | ARM Cortex-A9                 | ARM Cortex-A53                 |

|------------------------------|-------------------------------|--------------------------------|

| Instruction Set Architecture | ARM_v7                        | ARM_v8                         |

| (ISA)                        |                               |                                |

| Clock Frequency in MHz       | 667 [15 S. 15]                | 1200 [16 S. 26]                |

| Number of cores              | 2                             | 2/4                            |

| Interrupt Controller         | Implemented                   | Implemented                    |

| Memory Management Unit       | Implemented                   | Implemented                    |

| Floating Point Extension     | Implemented                   | Implemented                    |

| NEON Extension Unit          | Implemented                   | Implemented                    |

| DMA Controller               | 8 non-coherent 64bit channels | 8 non-coherent 128bit channels |

|                              | (scatter-gather support)      | 8 IO coherent 64bit channels   |

|                              |                               | (scatter-gather support)       |

| L1-D-Cache Size              | 32kB                          | 32kB                           |

| L2-Cache Size                | 512kB                         | 1MB                            |

| (L2) Cache Type              | 8-way set-associative         | 16-way set-associative         |

| Cache Line Size              | 32B                           | 64B                            |

| On Chip Memory (OCM)         | 256kB                         | 256kB                          |

An elaborated discussion of the Cortex A53 APU is done in [13]. As the arithmetic operation performance of the APU is decisive in analysis, but not in event building, their analysis is omitted.

#### 3.2.2 Coherent Memory Access Management

Caching is for high performing computing a requirement, but it also has its perils. In systems without cache, the data just exists in the memory, but in systems with cache the data can concurrently exist in the memory and in the cache system. This has no effect as long as the data value is constant, but as soon the value is changed the challenge starts. The main memory is an independent slave unit, who is strictly controlled by

the CPU or Cache Controller respectively. The parts actualize each other if it is demanded by the CPU (or the Cache Controller). When a routine changes a value of a cache element, the alteration is invisible for the memory. Hence the old value will persist until the memory is actualized by the CPU or the Cache Controller. In systems with one cache per memory the time of actualization does not matter. In systems with several (distributed) caches potential issues can arise as soon the caches work with inconsistent data elements. In systems with DMAs it is also possible that the memory elements are getting changed without any CPU intervention. In this case the content of the cache would be outdated and is therefore "invalid". In order to have data coherency, Cache Controller must be informed that its cache contains invalid data. The invalidation of this outdated data must be done by software or by hardware. As hardware support demands corresponding (complex) logic and a suitable snooping protocol it is not supported by default in all SoC systems. Hardware support is granted by the HPC ports in the Zynq-UltraScale+ devices. The development of snooping protocols was driven by multi core systems. In multi core systems, the same element can be deposited in several caches (there each cache depends to its own CPU core). The data coherency management process needs to handle such cases too. 2011 ARM released its AMBA4 ACE protocol for its multicore ecosystem. In order to maintain cache coherency between its CPUs and the ACP Port, the Zynq Devices have a Snoop Control Unit.

In the previous discussion it was assumed that the CPU uses its Cache and does not bypass it. But this is not always beneficial (as not always the code obeys the "principles of temporal and spatial locality"). For instance, if the CPU data just needs once, buffering it in the Cache can be derogatory, as caching it, may expulse data (from the cache) which may be required in one of the subsequent steps again (keyword is "cache trashing"). Therefore, the CPU read access to memory has two feasible important options: "Write-Allocate" and "Non-Write-Allocate". In "Write-Allocate" Mode the desired read data is buffered in the Cache, in "Non-Write-Allocate" Mode the Cache is bypassed and the demanded element is directly passed in one of the CPU registers. For results of CPU operations, the same thoughts can be applied. In some cases it is useful to write the results directly to memory (and bypassing the cache system), in other cases the buffering of the result(s) in cache system might be a better idea, as they soon might be invoked (by the CPU) again. In textbooks the latter approach is called "Write-Back", the former "Write-Through". As it is beneficial to manage this property dependent on the memory page, it is a task of the Memory Management Unit (MMU) to manipulate the Cache Controller behavior accordingly.

#### 3.2.3 DDR Controller

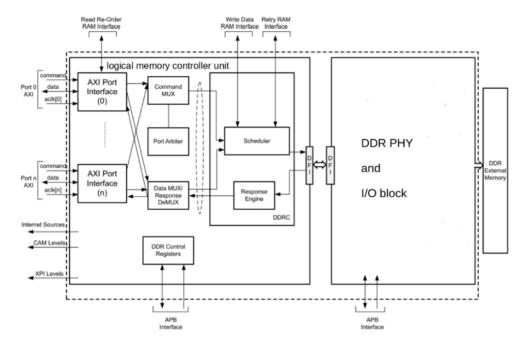

Figure 8 depicts the setup of the DDR controller subsystem and its interconnections in Zynq-Ultra+ devices. The logical memory controller unit is responsible for the read/write operation prioritization and therefore must handle the given "Quality of Service" requests.

Figure 8 DDR Subsystem Block Diagram Zynq-Ultra+ [12 S. 436] (Modified by M. Schuett)

Besides the logical memory controller unit, the DDR subsystems has special DDR PHY and I/O block (Figure 8). This is a requirement as the DDR memory is an external chip on the module and is not a part of the Zynq devices. As several DDR memory designs with substantial performance differences exist, the final performance depends also on the implemented external DDR memory specifications. The logic part has besides the address adapter units (AXI Port Interface), a port arbiter, a content addressable memory (CAM) and a scheduler. The CAM supports the scheduling algorithms in traffic optimization management based on priority, bank/rank status and DDR timing constrains [12 S. 437].

The most important difference between the DDR controller in the Zynq-Ultra+ and Zynq-7k devices is the DDR4 compatibility of the Zynq-Ultra+ devices. Table 3 lists important DDR controller specifications of the Zynq-Devices.

Table 3 Compare of the DDR controller high level properties in Znyq-7k a. Zynq-Ultra+. The table is a summary of the corresponding chapters in [12] a. [9]. Remember that in the case of DDR3/DDR4 a width of 64bit (or less) is a "single rank", 128bit is a "dual rank".

|                             | Zynq-7k                         | Zynq-Ultra+                       |

|-----------------------------|---------------------------------|-----------------------------------|

| DDR Type                    | DDR2, DDR3, DDR3L and           | DDR3, DDR3L, LPDDR3,              |

|                             | LPDDR2                          | DDR4 and LPDDR4                   |

| Channel                     | Single channel                  | Dual channel                      |

| Total data width (bits)     | 16,321                          | 32,64                             |

| Component data width (bits) | 8,16,32                         | 8,16,32                           |

| Implemented external DDR    | 2*512M*DDR3L-1600 SDRAM         | DDR4-2400 SDRAM                   |

| memory on corresponding     | (listed Z7k modules of Table 9) | (total size depends on ZU+ modul) |

| Trenz Modules (chapter 6.1) |                                 |                                   |

The effective performance of the DDR controller depends on the chosen DDR memory implementation and on the addressing style ("random address distribution" or "sequential incremental addressing"). Table 4 shows the theoretical bandwidth of common embedded DDR memories.

$Table\ 4\ Theoretical\ performance\ for\ common\ embedded\ DDR\ memory\ .\ Note\ that\ the\ Zynq-7k\ series\ just\ complies\ with\ 32-bit\ DDR3\ modules.$

|                                         | DDR3L-800 SDRAM | DDR4-2400 SDRAM |

|-----------------------------------------|-----------------|-----------------|

| Theoretical bandwidth per 64-bit module | 6.4 GB/s        | 19.2 GB/s       |

| Theoretical bandwidth per 32-bit module | 3.2 GB/s        | 9.6 GB/s        |

In operation a DDR controller never achieves its theoretical bandwidth. The effective bandwidth strongly depends on the addressing style, the complexity of the scheduler/arbiter logic and the chosen (Zynq device external) DDR memory implementation.

Chapter 3: Zynq Device Family

<sup>&</sup>lt;sup>1</sup> In some Zynq-7k devices the total data width is limited to 16bit. None of these devices is used in the FC2.0 prototype evaluation.

#### 3.3 The Processing System/Programmable Logic Interface in Zynq-Devices

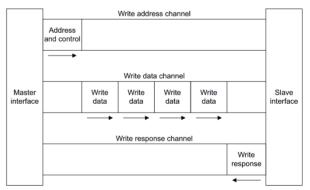

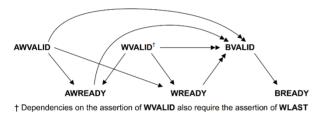

The Zyng devices are hybrid devices out of an embedded microprocessor and FPGA fabrics. The FPGA portion is ideal in order to do all signal processing jobs in the field of pulse detection and triggering. Event building is a typical CPU task. CPU routines are working in addressed space. This means that unaddressed data elements of the FPGA area must be aligned to a corresponding destination address before they enter the PS area. In the simplest (not feasible) case, every data element has its own corresponding address element, the addressing just requires an address bus. In a SoC every unit has its own (overlap free) address range. In order to show that a data element is invalid, the corresponding address has to be out of the range of all units. In principle it is possible to build up a SoC system with this simple protocol. But its simplicity has many serious drawbacks that challenge its practical implementation. For instance, every unit has always to accept every input immediately as no ready/valid signals exist. Furthermore, error communication is not possible. Another fatal lack is the missing of bursts and the impossibility of data width adaption ("expansion/downsizing"). ARM therefore developed its AMBA4 protocol (AMBA is acronym for "Advanced Microcontroller Bus Architecture"). The AMBA protocol was developed under the focus of SoC development and OS considerations. In the PS area of the Zynq devices communication between different blocks is almost always handled on basis of the AMBA protocols. Xilinx decided that the data ports of the PS-PL interface are a subject of the AMBA AXI3/AXI4 protocol (Z7k/ZU+). The AXI3 protocol is a subset of the AXI4 protocol which Xilinx recommends to use for IP development in Vivado. The PS-PL interface signal and interfaces have besides the data ports amongst others following features:

- PS internal access to (some) special registers

- System error signals

- MIO-EMIO signals and interfaces

- Clock and Timer signals

The (Extended) Multiplex IO ((E)MIO) Interface intention is mainly to forward signals from units in the PS area into the PL area. This offers the advantage that these signals also can be routed to pins which are assigned to the PL area. A brief discussion of the data ports was already done in the introduction of chapter 3. The prescribed letters "S"/"M" are acronyms for Slave/Master. The S-HP and ACP data ports exist in both Zynq device series and significantly differ in their data transfer method. The M-HP ports exist like the S-HP ports in both Zynq devices series. Their design implementation is strongly PS centered and has optional PS traffic information which is the S-HP ports not accessible<sup>2</sup>. But their PS centered design impedes also continuous data transfers. The HPC and ACE ports depend on the CCI and are therefore Zynq-Ultra+ exclusive. The HPC port is an intermixture of the HP/ACP method and offers one-way coherent data

.

<sup>&</sup>lt;sup>2</sup> This assumption depends on the Zynq device series.

transfers. The ACE port was established for "fully" two-way coherent data transfers. Its focus is on design extensions with cache coherence and not on IO-DMA tasks like the HP/HPC/ACP ports. The M-LPD port of the Zynq-Ultra+ is the functional equivalent in the M-GP port of the Zynq-7k. They offer low latency CPU accesses into the FPGA area and are therefore essential for PL register setting and control. In a SoC design not only the available amount of data ports, also their mutual dependence is important. All data ports have in all devices their own clock and reset signals, so that they can be driven independently. Furthermore, every data port has its own asynchronization unit. A clock domain crossing via the PS-PL interface therefore needs no additional measures which the firmware designer has to care about. This is an enhancement in contrast to MicroBlaze designs, like FF1.0, where the firmware designer must consider measures against clock domain crossing (CDC) issues.

#### 3.3.1 M-GP and M-LPD ports

Both ports have direct PL access and are therefore ideal for APU programmed IO with the FPGA area. The M-GP port obeys the AXI4\_Lite protocol, the M-LPD port uses the unreduced AXI4 complement. Both ports have their low latency architecture in common – this means that they just have an asynchronization unit implemented in their path (in order to enable clock domain crossing), but no further FIFO buffering options.

#### 3.3.2 S-HP ports

All S-HP ports have in common that they have a direct access to the external DDR memory (Figure 7). HP ports therefore could be a possibility to buffer a data stream directly on the external main memory. This enables firmware designs that do not need to buffer the accepted waveforms in Zynq internal RAM. In these (future) designs some restrictions due to FPGA RAM limitations could be surmounted. In order to set up a high performance data transfer in the HP port paths a FIFO buffer is implemented. A burden of this approach is an increased access latency. As the AXI FIFOs and their management logic are also responsible for address forwarding, the AXI FIFO performance partly depends on the implemented AXI protocol settings. Special care should be taken to data width and burst size settings. As all connected data links pass the DDR controller the effective S-HP performance is dependent on the DDR memory and controller performance. The design approach of the HP ports paths is roughly the same in the Zynq-7 and Zynq-Ultra+ series. In the Zynq-Ultra+ series the components were significantly enhanced and some additional units (regarding virtualization support) implemented. For all proposed setups in this thesis the functionality of the new units is not significant, as virtualization is not relevant. Table 5 lists all significant HP port properties for Zynq-7k a. Zynq-Ultra+ designs.

Table 5 Listing of all noteworthy HP port settings.

|                                      | Zynq-7k   | Zynq-Ultra+ |

|--------------------------------------|-----------|-------------|

| Protocol Interface (PL side)         | AXI3      | AXI4        |

| Data Width in bit                    | 64        | 128         |

| FIFO Size                            | 128×64bit | 128×128bit  |

| Outstanding Transaction (read/write) | 8/8       | 16/16       |

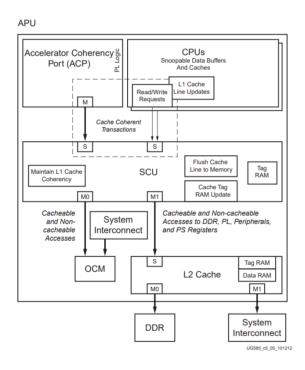

#### 3.3.3 S-ACP Port

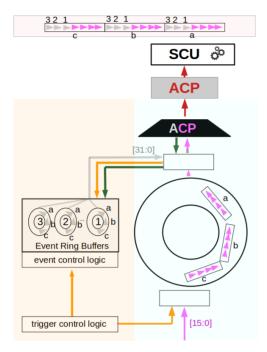

The Accelerator Coherency Port (ACP) Port has L2-Cache access via the Snoop Control Unit (SCU) (Figure 9). The ACP port data needs not to make a detour via the main memory – the event building process can be completely done in the cache without invalidation operations and memory accesses.

Figure 9 ACP Connectivity Diagram in Zynq-7k devices [14 p. 137]. The setup in Zynq-Ultra+ devices is despite implementation of different interconnects in principle comparable. The acronym SCU means Snoop Control Unit.

The ACP port has the same rank as the APUs. This means that the ACP port competes with the APUs for the L2-Cache space and the APUs possibly expel ACP content out of Cache. Running jobs therefore might show influence on the ACP port performance. The job dependent behavior contrasts with the HP ports for which the performance is influenced by the total memory access rates which is not necessarily linked to the CPU job burden. The biggest burden of CPU centered transfers is their non-continuous data transfer. A DAQ which uses the ACP port therefore needs to prebuffer its data with FPGA-RAM. Furthermore, the ACP port does not offer prioritization. The ACP port implementation in the Zynq devices is not completely

AXI protocol conform. The discrepancies, which also depend on the Zynq series, are in [12] and [14]. A summary of all important ACP port properties in Zynq devices is in Table 6.

Table 6 ACP Port Properties in Zynq-Devices. The information is out of [14] and [12]. The listed "Cache Line Friendly Access Style" properties are incomplete, but sufficient for the understanding of the FC2.0 performance trends. The not listed limitations refer to AXI properties that are not used in FC2.0.

|                              | Zynq-7k                             | Zynq-Ultra+                     |  |  |

|------------------------------|-------------------------------------|---------------------------------|--|--|

| Protocol Interface (PL side) | AXI3                                | AXI4                            |  |  |

| ACP Port width               | 64b                                 | 128b                            |  |  |

| Cache Line Size              | 32B                                 | 64B                             |  |  |

| Cache Line Friendly          | Transaction size must be a          | Only transaction size of 64/16B |  |  |

| Access Style                 | multiple of the cache line size, in | with incremental addressing     |  |  |

|                              | particular cases the AXSTRB         | (AXI4 signal AXBURST has a      |  |  |

|                              | signal is limited [14 p. 105]       | value of 2'b01)                 |  |  |

|                              |                                     | [12 S. 1064]                    |  |  |

#### 3.3.4 S-HPC Ports

The HPC ports are Zynq-Ultra+ exclusive. HPC ports are HP ports whose PS data path crosses the Cache Coherent Interconnect (CCI). As classic HP ports, HPC ports transfer the data into the memory (and not into the L2-Cache). If accordingly selected, the CCI invalidates the corresponding cache elements. In opposite to the classic HP ports, the CPU has not to care about cache invalidation. The CPU can immediately access the memory. Accessing the memory is still a requirement, as the Cache was just invalidated and not preloaded with the new HPC data. The HPC system implementation also has its strains. The CCI is passed by several units (Figure 6) and has a lower spare bandwidth than the classic HP port data path. So, the chance of a non-continuous data transfer situation rises. A detailed comparison between the HP, ACP and HPC ports of the Zynq-Ultra+ devices is done in the Table 7.

Table 7 Compare between HP, HPC and ACP port in Zynq-Ultra+ devices. In the Zynq-7000 devices a HPC port is not available, and all ports have a maximum data width of 64bit. Also, the DDR controller port occupation is different.

|                                    | S-HP           | HPC         | ACP     |

|------------------------------------|----------------|-------------|---------|

| Number of PS/PL interface ports    | 4              | 2           | 1       |

| Number of DDR Controller input     | 3              | 2           | 2       |

| ports                              |                |             |         |

| Interference with L2-Cache         | No             | Via CCI     | Via SCU |

| Controller                         |                |             |         |

| Mutual units with CPU interference | DDR Controller | CCI and DDR | Cache   |

|                                    |                | Controller  |         |

| Continuous transfers               | Yes            | Yes         | No      |

| Data width in bit                  | 32, 64, 128    | 128         | 128     |

| Burst/Data shaping via AXI FIFOs   | Yes            | No          | No      |

| and APB in PS                      |                |             |         |

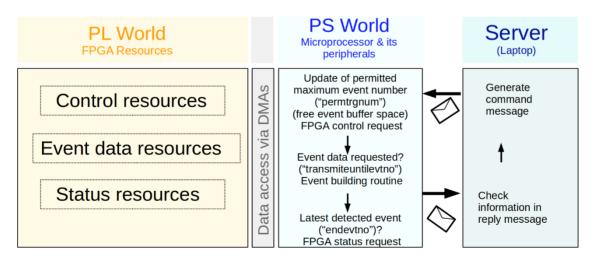

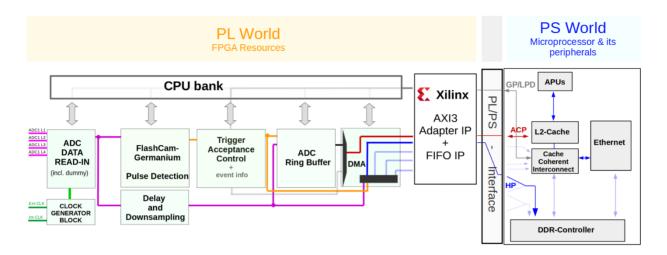

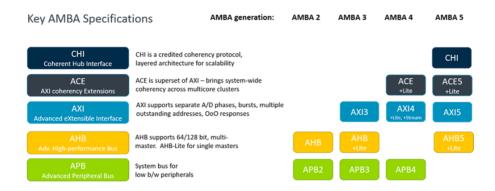

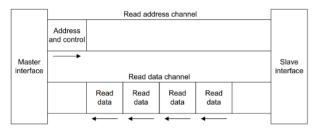

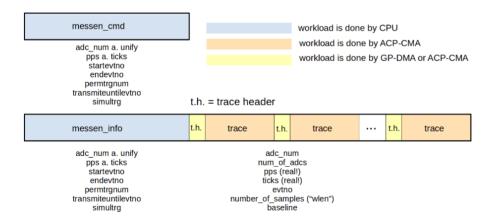

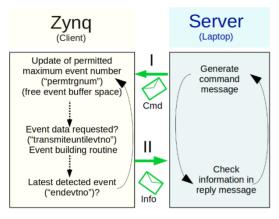

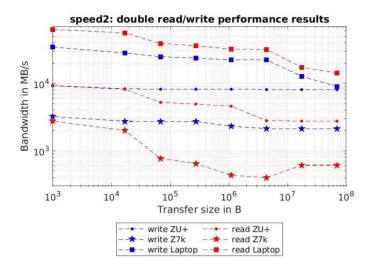

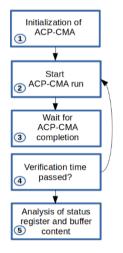

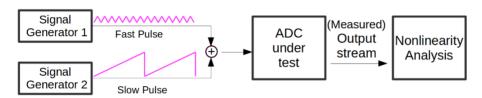

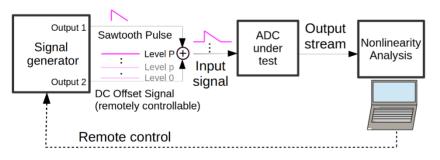

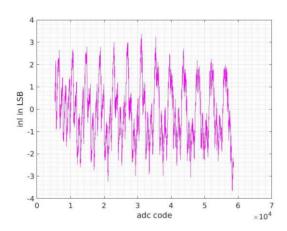

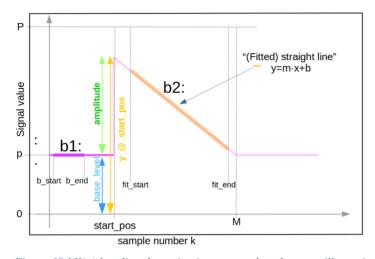

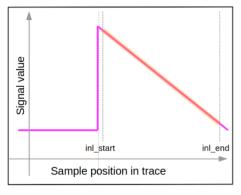

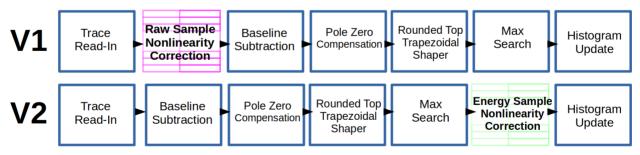

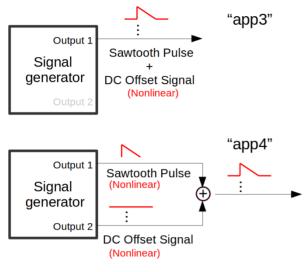

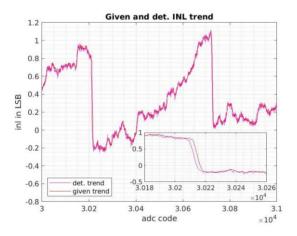

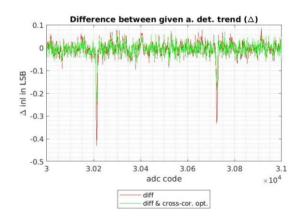

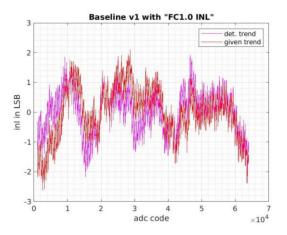

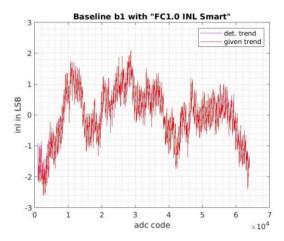

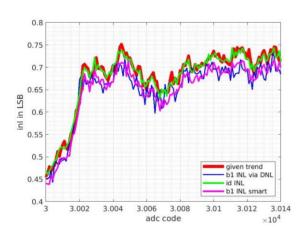

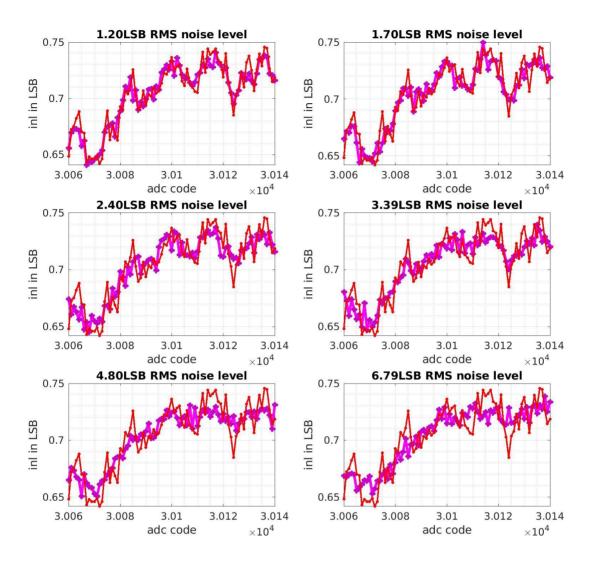

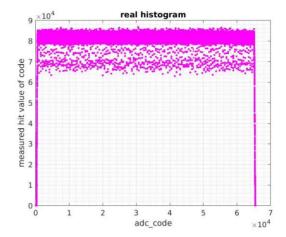

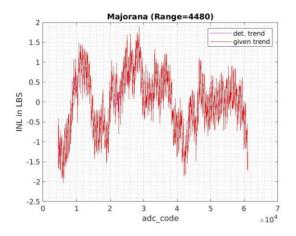

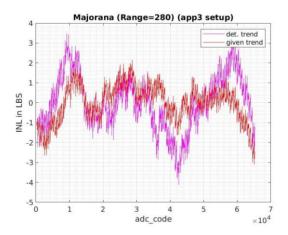

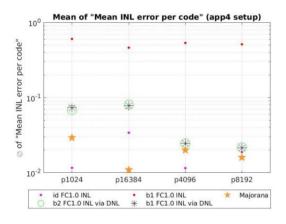

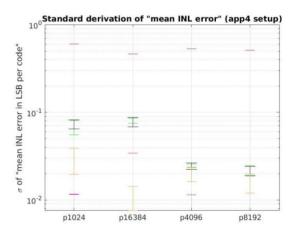

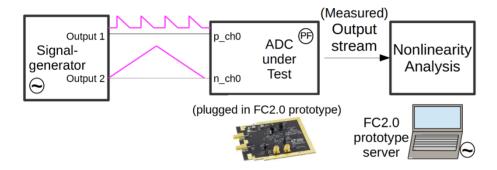

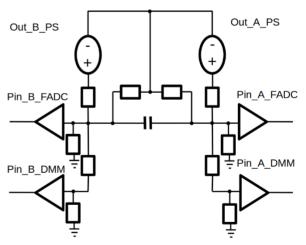

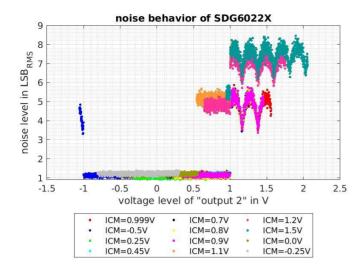

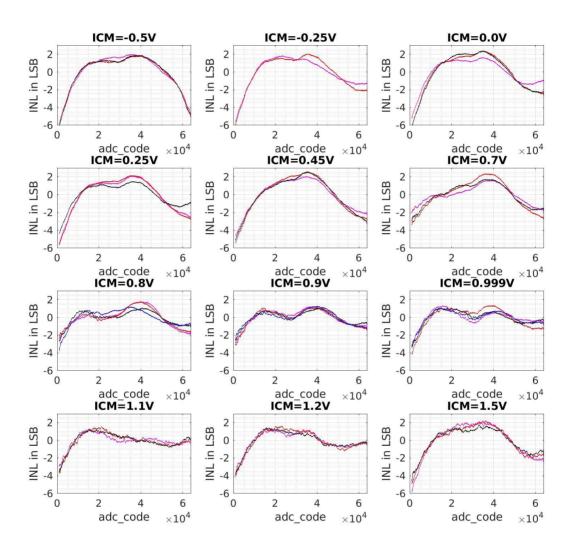

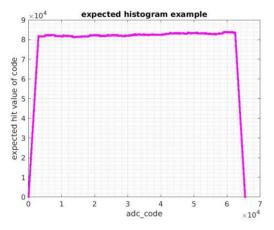

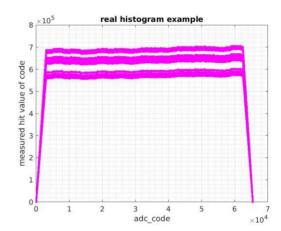

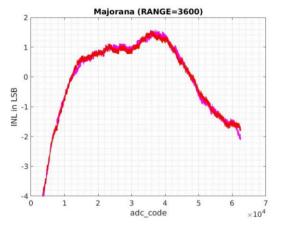

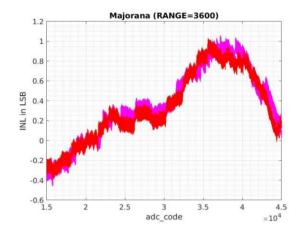

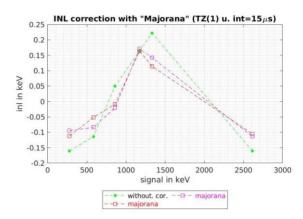

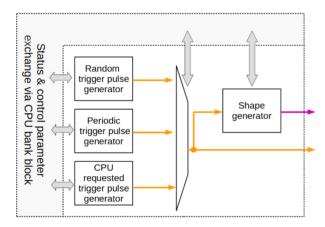

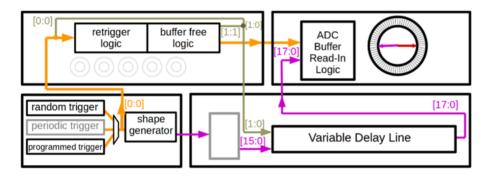

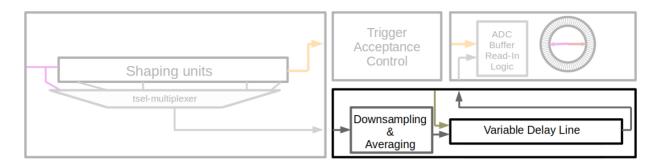

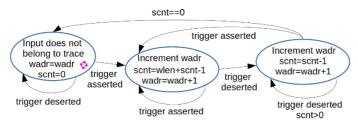

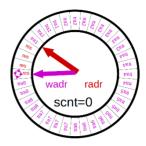

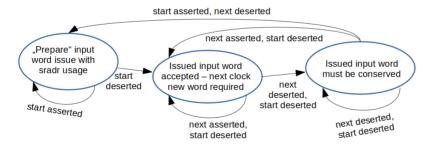

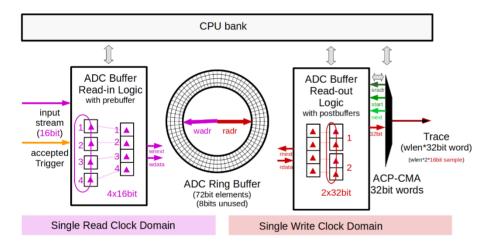

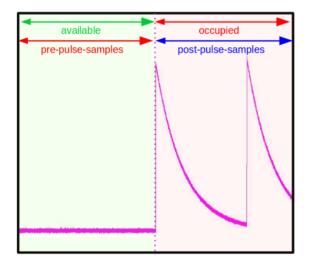

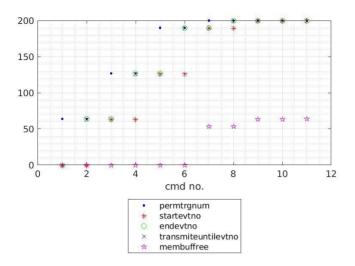

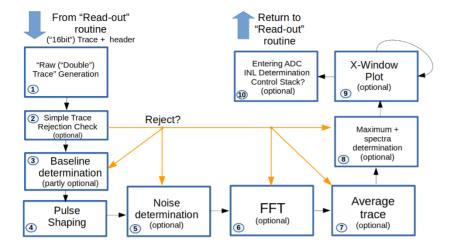

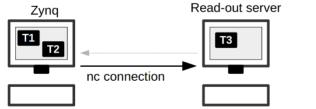

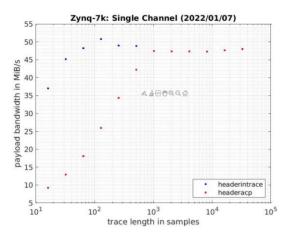

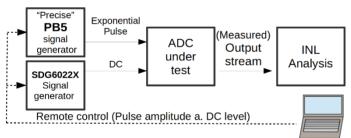

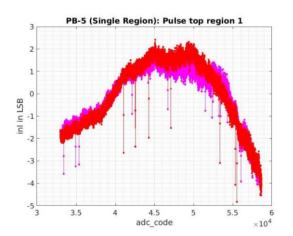

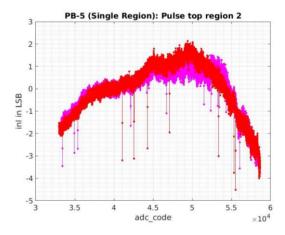

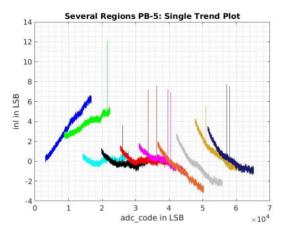

# 4 FlashCam 2.0 Prototype Firmware Design