#### University of Verona

#### DEPARTMENT OF COMPUTER SCIENCE

GRADUATE SCHOOL OF NATURAL SCIENCE AND ENGINEERING

DOCTORAL PROGRAM IN COMPUTER SCIENCE

CYCLE XXXIII

## Modeling and Simulation Methodologies for Digital Twin in Industry 4.0

S.S.D. ING-INF/05

# Coordinator: Prof. Massimo Merro Tutor: Prof. Franco Fummi Doctoral Student:

Stefano Centomo

#### **Abstract**

The concept of Industry 4.0 [1] represents an innovative vision of what will be the factory of the future. The principles of this new paradigm are based on interoperability and data exchange between different industrial equipment. In this context, Cyber-Physical Systems (CPSs) cover one of the main roles in this revolution. The combination of models and the integration of real data coming from the field allows to obtain the virtual copy of the real plant, also called Digital Twin. The entire factory can be seen as a set of CPSs and the resulting system is also called Cyber-Physical Production System (CPPS). This CPPS represents the Digital Twin of the factory with which it would be possible analyze the real factory. The interoperability between the real industrial equipment and the Digital Twin allows to make predictions concerning the quality of the products. More in details, these analyses are related to the variability of production quality, prediction of the maintenance cycle, the accurate estimation of energy consumption and other extra-functional properties of the system.

Several tools [2] allow to model a production line, considering different aspects of the factory (*i.e.* geometrical properties, the information flows etc.)

However, these simulators do not provide natively any solution for the design integration of CPSs, making impossible to have precise analysis concerning the real factory. Furthermore, for the best of our knowledge, there are no solution regarding a clear integration of data coming from real equipment into CPS models that composes the entire production line.

In this context, the goal of this thesis aims to define an unified methodology to design and simulate the Digital Twin of a plant, integrating data coming from real equipment. In detail, the presented methodologies focus mainly on: integration of heterogeneous models in production line simulators; Integration of heterogeneous models with ad-hoc simulation strategies; Multi-level simulation approach of CPS and integration of real data coming from sensors into models.

All the presented contributions produce an environment that allows to perform simulation of the plant based not only on synthetic data, but also on real data coming from equipments.

#### **Contents**

| Pa      | rt I F | reliminary                                                                   |    |

|---------|--------|------------------------------------------------------------------------------|----|

| 1       | 1.1    | Introduction                                                                 | 3  |

| Pa      | rt II  | Homogeneous Models                                                           |    |

| 2       | Inte   | egrating synthetic and real components of a cyber-physical production system | ç  |

|         | 2.1    | Introduction                                                                 | ç  |

|         | 2.2    | Background                                                                   | 11 |

|         |        | 2.2.1 OPC UA Communication Protocol                                          | 11 |

|         |        | 2.2.2 AutomationML                                                           | 12 |

|         |        | 2.2.3 Functional Mockup Interface                                            |    |

|         |        | 2.2.4 MATLAB/Simulink                                                        |    |

|         |        | 2.2.5 Tecnomatix Plant Simulation                                            |    |

|         | 2.3    | Methodology                                                                  | 16 |

|         |        | 2.3.1 Mapping Simulink components in AutomationML                            |    |

|         |        | 2.3.2 AML to MATLAB                                                          | 20 |

|         |        | 2.3.3 OPC UA server from FMU                                                 | 22 |

|         | 2.4    | Experimental Results                                                         | 23 |

|         | 2.5    | Simple producer-consumer                                                     |    |

|         | 2.6    | The ICE lab model                                                            | 27 |

|         | 2.7    | Conclusions                                                                  | 28 |

| –<br>Pa | rt III | Heterogeneous Models                                                         |    |

| 3       | Aut    | omatic Integration of HDL IPs in Simulink using FMI and S-Function           |    |

|         |        | erfaces                                                                      | 33 |

|         | 3.1    | Introduction                                                                 | 33 |

|   | 3.2 | Related Works                                                           | 34 |

|---|-----|-------------------------------------------------------------------------|----|

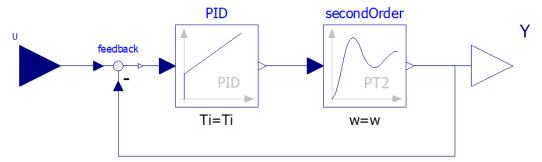

|   |     | 3.2.1 Running example                                                   | 35 |

|   |     | 3.2.2 FMI-Standard                                                      | 35 |

|   |     | 3.2.3 Simulink C MEX S-Functions                                        | 37 |

|   |     | 3.2.4 Automatic abstraction of HDL IPs                                  | 37 |

|   | 3.3 | Methodology                                                             | 38 |

|   |     | 3.3.1 Data-type abstraction                                             | 41 |

|   |     | 3.3.2 Automatic generation of Functional Mockup Units                   | 42 |

|   |     | 3.3.3 Automatic generation of C MEX S-Functions                         | 46 |

|   | 3.4 | Experimental Results                                                    | 48 |

|   | 3.5 | Conclusions and Future Outlook                                          | 50 |

| 4 | Ger | neration of Functional Mockup Units for Transactional Cyber-Physical    |    |

|   |     | tual Platforms                                                          | 53 |

|   | 4.1 | Introduction                                                            | 53 |

|   | 4.2 | Background and Related Work                                             | 55 |

|   |     | 4.2.1 Functional Mock-up Interface (FMI) Standard 2.0 for co-simulation | 55 |

|   |     | 4.2.2 Simulation coordination in the FMI standard                       | 56 |

|   |     | 4.2.3 Related Work                                                      | 58 |

|   | 4.3 | FMI Standard Advantages and Limitations                                 | 59 |

|   | 4.4 | Methodology                                                             | 60 |

|   |     | 4.4.1 Functional Mock-up Units (FMUs) generation and timing backward    |    |

|   |     | propagation                                                             | 60 |

|   |     | 4.4.2 A better coordinator for discrete systems                         | 62 |

|   | 4.5 | Methodology Application                                                 | 63 |

|   | 4.6 | Recent Development and Discussion                                       |    |

|   | 4.7 | Concluding remarks                                                      | 69 |

| 5 | Cyb | per-Physical Systems Integration in a Production Line Simulator         | 71 |

|   | 5.1 | Introduction                                                            | 71 |

|   | 5.2 | Plant Simulation and Integration Alternatives                           | 72 |

|   |     | 5.2.1 Production Line Simulators                                        | 72 |

|   |     | 5.2.2 Siemens Plant Simulation: SimTalk C-Interface                     | 73 |

|   |     | 5.2.3 Functional Mockup Interface (FMI)                                 | 74 |

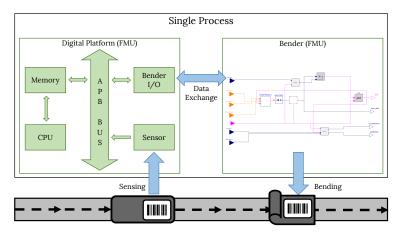

|   | 5.3 | Integration Methodology                                                 | 75 |

|   |     | 5.3.1 Cyber System: Modelling and FMU Generation                        | 76 |

|   |     | 5.3.2 Physical System: Modelling and FMU Generation                     | 77 |

|   |     | 5.3.3 Cyber-Physical System: Coordination and Integration               | 77 |

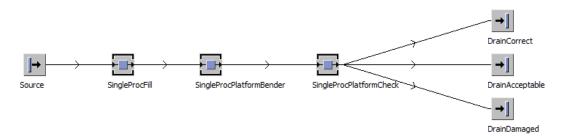

|   | 5.4 | Methodology Application                                                 | 78 |

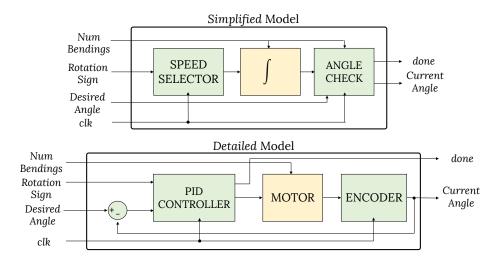

|   |     | 5.4.1 Bending machine CPS                                               | 79 |

|   |     | 5.4.2 Alternatives Taxonomy                                             | 81 |

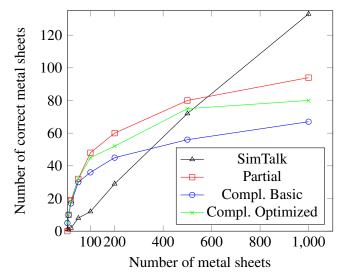

|   |     | 5.4.3 Simulation speed                                                  | 81 |

|   |      | 5.4.4 Simulation errors                                                 |            |

|---|------|-------------------------------------------------------------------------|------------|

|   | 5.5  | Conclusions                                                             | 32         |

| 6 | Aut  | omatic Integration of Cycle-Accurate Models into Cyber-Physical Virtual |            |

|   | Plat | tforms                                                                  | 33         |

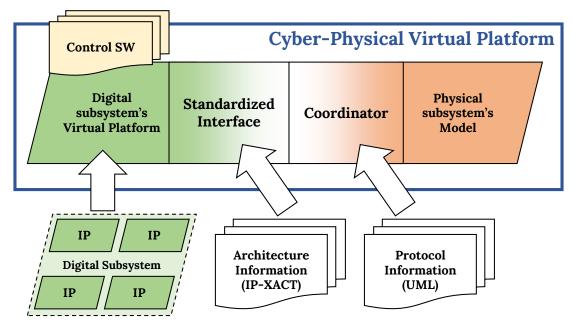

|   | 6.1  | Introduction                                                            | 33         |

|   | 6.2  | Background 8                                                            | 34         |

|   |      | 6.2.1 Related work                                                      | 34         |

|   |      | 6.2.2 Code Generation for Virtual Platform Integration                  | 35         |

|   |      | 6.2.3 Interface technologies for system simulation                      | 36         |

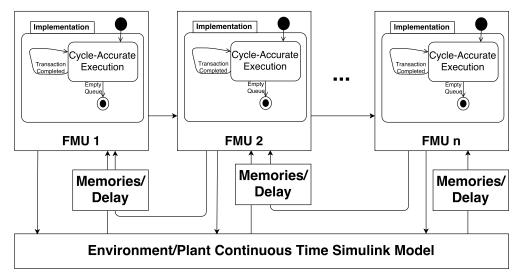

|   | 6.3  | Integration methodology                                                 | 37         |

|   |      | 6.3.1 Mapping HDL primitives to FMI and S-Functions                     | 37         |

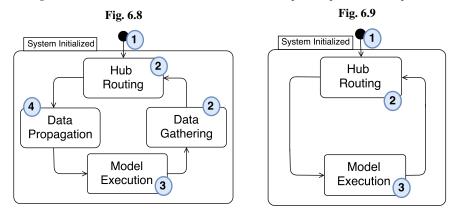

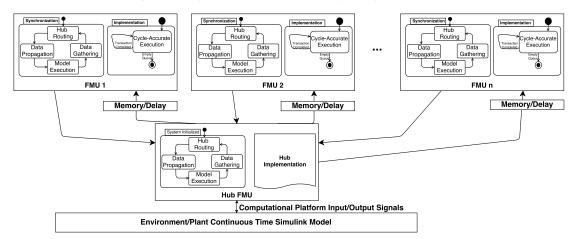

|   |      | 6.3.2 Monolithic model approach                                         | 38         |

|   |      | 6.3.3 Hub-based approach                                                | 90         |

|   |      | 6.3.4 Alternatives Taxonomy                                             | 1          |

|   | 6.4  | Methodology Application                                                 | 92         |

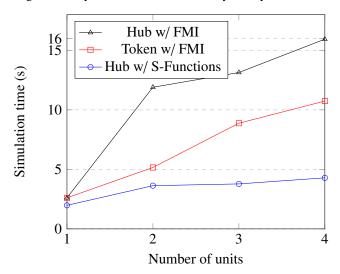

|   |      | 6.4.1 Simulation performance                                            | <b>)</b> 3 |

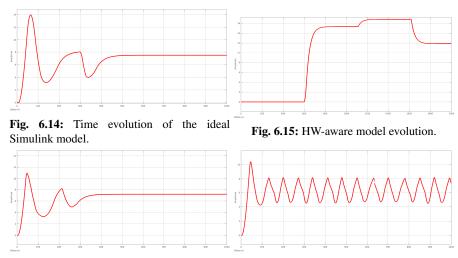

|   |      | 6.4.2 Design Space Exploration                                          | 94         |

|   | 6.5  | Conclusions                                                             | 96         |

| 7 | Imr  | proving FMI-based simulation by Exploiting System–level Information     | 97         |

|   | 7.1  |                                                                         |            |

|   | 7.2  | Preliminaries                                                           |            |

|   |      | 7.2.1 Standardized interfaces and the FMI standard                      |            |

|   |      | 7.2.2 FMI Standard for co-simulation                                    |            |

|   |      | 7.2.3 Simulation coordination in the FMI standard                       |            |

|   |      | 7.2.4 Specification Languages for Hardware Platforms                    |            |

|   |      | 7.2.5 Automatic abstraction of digital components                       |            |

|   | 7.3  | Methodology Overview                                                    |            |

|   |      | 7.3.1 Running Example                                                   |            |

|   | 7.4  | Generation of Cycle-Accurate FMUs                                       |            |

|   |      | 7.4.1 Data-type mapping                                                 |            |

|   |      | 7.4.2 Automatic generation of Functional Mockup Units                   |            |

|   | 7.5  | Generation of Transactional FMUs                                        |            |

|   | 7.6  | Generating the coordinators                                             |            |

|   | 7.0  | 7.6.1 Cycle-Accurate Coordinator                                        |            |

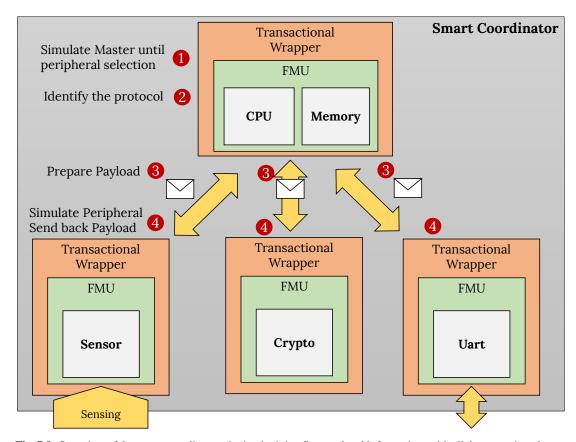

|   |      | 7.6.2 Smart Coordinator                                                 |            |

|   | 77   | Experimental Results                                                    |            |

|   |      | 7.7.1 Experimental setup                                                |            |

|   |      | 7.7.2 Experimental setup                                                |            |

|   |      | 7.7.3 In-depth analysis of the experimental results                     |            |

|   |      | 1.7.5 In-depth analysis of the experimental results                     | O          |

| Pai | rt IV | Multi-Level Modeling and Simulation                                |     |

|-----|-------|--------------------------------------------------------------------|-----|

| 8   | Fro   | om Multi-Level to Abstract-Based Simulation of a Production Line   | 123 |

|     | 8.1   | Introduction                                                       | 123 |

|     | 8.2   | Background                                                         | 123 |

|     | 8.3   | Multi-Level Modeling and Simulation                                | 125 |

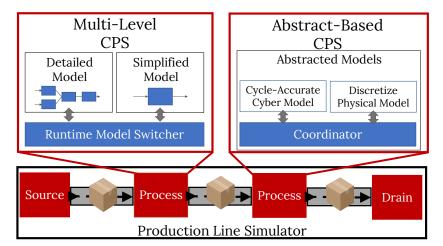

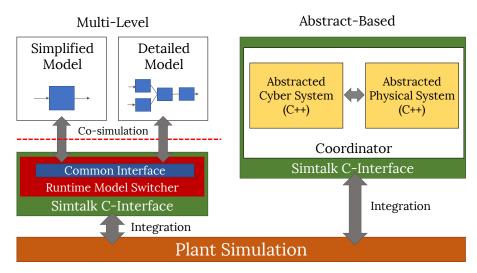

|     |       | 8.3.1 Application of Multi-Level Simulation to a Production Line   | 126 |

|     | 8.4   |                                                                    |     |

|     |       | 8.4.1 Application of Abstract-Based Simulation to Production Line  |     |

|     | 8.5   | Experimental Results                                               | 127 |

|     |       | 8.5.1 Multi-Level Experiment                                       |     |

|     |       | 8.5.2 Abstract-based Experiment                                    | 129 |

|     |       | 8.5.3 Simulation Results Comparison                                |     |

|     | 8.6   | Concluding Remarks                                                 | 131 |

| 9   | A D   | Design Methodology of Multi-level Digital Twins                    |     |

|     | 9.1   |                                                                    |     |

|     | 9.2   | 8                                                                  |     |

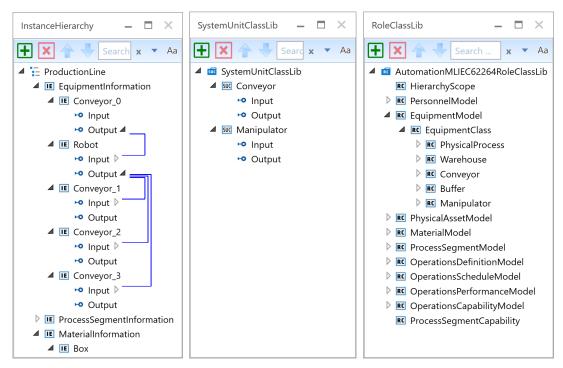

|     |       | 9.2.1 AutomationML - IEC 62714                                     |     |

|     |       | 9.2.2 CAEX - IEC 62424-2                                           |     |

|     |       | 9.2.3 Plant and Kinematics Simulators                              |     |

|     |       | 9.2.4 Running Example                                              |     |

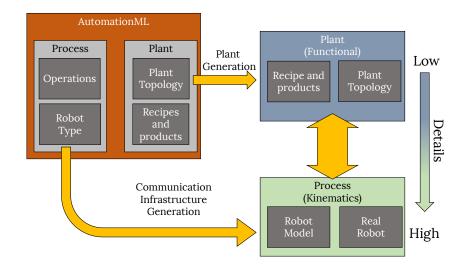

|     | 9.3   | 2,                                                                 |     |

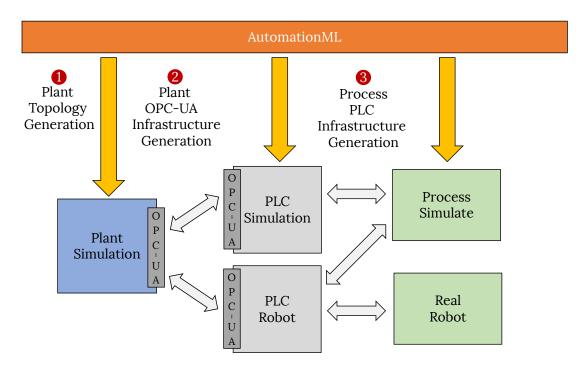

|     |       | 9.3.1 Plant Topology Generation                                    |     |

|     |       | 9.3.2 Plant OPC-UA Infrastructure Generation                       |     |

|     |       | 9.3.3 Process PLC Infrastructure Generation                        |     |

|     | 9.4   |                                                                    |     |

|     | 9.5   | Conclusion                                                         | 146 |

| Par | rt V  | From Real Data to Information                                      |     |

| 10  |       | dustrial-IoT Data Analysis Exploiting Electronic Design Automation |     |

|     |       | chniques                                                           |     |

|     |       | 1 Introduction                                                     |     |

|     | 10.2  | 2 HoT Data Analysis                                                |     |

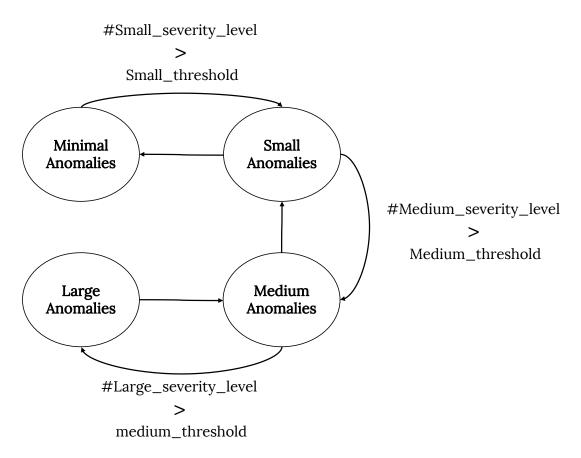

|     |       | 10.2.1 Severity levels                                             | 151 |

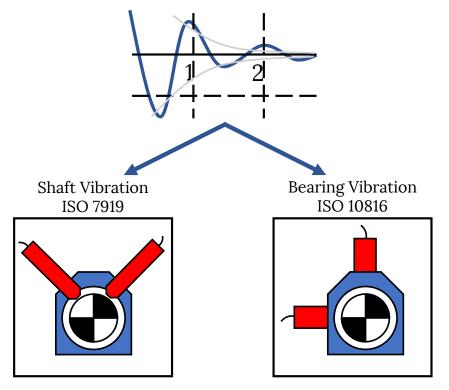

|     |       | 10.2.2 Measurement points                                          |     |

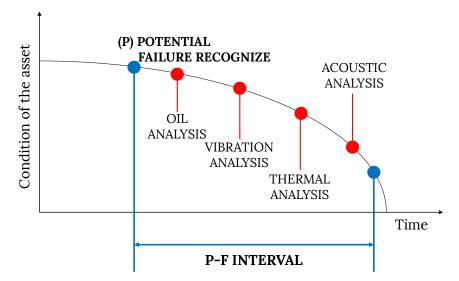

|     |       | 10.2.3 P-F intervals                                               |     |

|     |       | 10.2.4 Common variables in condition monitoring                    | 154 |

|     | 10.3  | 3 Predictive Maintenance                                           | 155 |

|     | 10.4  | 4 Experimental Validation                                          | 158 |

|     | 10.4.1 Experiment Setup                                          |     |

|-----|------------------------------------------------------------------|-----|

|     | 10.4.2 Abstract model of a real machine                          |     |

|     | 10.4.3 Methodology validation with a mutation analysis technique |     |

|     | 10.4.4 Experiment results                                        |     |

|     | 10.5 Conclusions                                                 | 162 |

| 11  | The Design of a Digital-Twin for Predictive Maintenance          | 163 |

|     | 11.1 Introduction                                                | 163 |

|     | 11.2 Background & State of the art                               | 165 |

|     | 11.2.1 Technologies                                              | 165 |

|     | 11.2.2 Related Work                                              | 166 |

|     | 11.3 Modeling The Problem                                        |     |

|     | 11.4 From Sensor Data to Severity Levels                         | 167 |

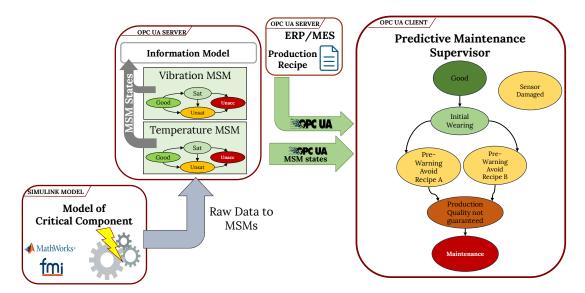

|     | 11.5 Monitoring State Machine (MSM)                              | 169 |

|     | 11.6 Developed Technique                                         | 169 |

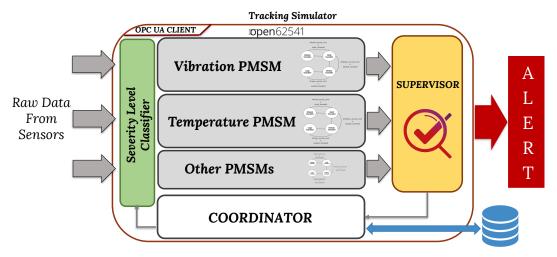

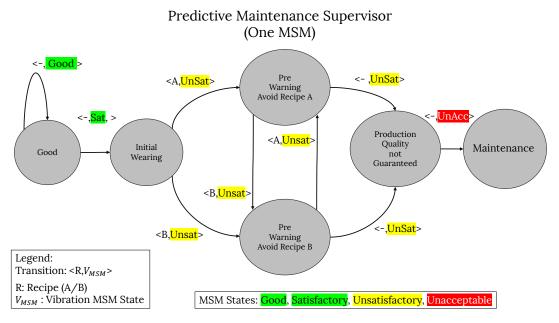

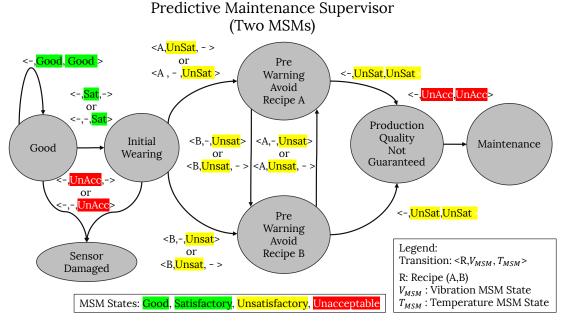

|     | 11.6.1 Predictive Maintenance Supervisor                         | 169 |

|     | 11.7 Alternative Use of MSM and PSM                              | 172 |

|     | 11.7.1 Structure Validation Mode                                 | 172 |

|     | 11.7.2 Condition-based-Maintenance Continuous Mode               | 172 |

|     | 11.7.3 Predictive Maintenance Structure Training Mode            | 173 |

|     | 11.7.4 Predictive Maintenance Mode                               | 173 |

|     | 11.8 Methodology Application                                     | 173 |

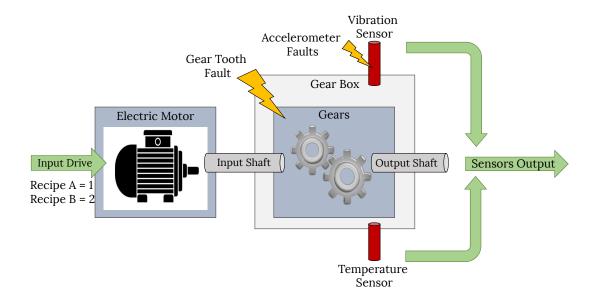

|     | 11.8.1 Experimental Setup                                        | 173 |

|     | 11.8.2 Abstract Model of a Real Machine                          | 175 |

|     | 11.8.3 Structure Validation Mode in Action                       | 176 |

|     | 11.8.4 Experimental results                                      | 176 |

|     | 11.8.5 Standards                                                 | 177 |

|     | 11.9 Conclusions                                                 | 178 |

| Pai | rt VI Unified Example & Conclusions                              |     |

| 12  | Industrial Computer Engineering Laboratory & Conclusions         | 181 |

|     |                                                                  |     |

| 13  | Published Contributions                                          | 183 |

| Ref | ferences                                                         | 185 |

| Lis | st of Figures                                                    | 193 |

| Lic | et of Tables                                                     | 105 |

**Preliminary**

#### Introduction

#### 1.1 Introduction

The concept of Industry 4.0 [1] represents an innovative vision of what will be the factory of the future. A smart factory should be able to optimize efficiency and productivity by extending the capabilities of both manufacturing devices and people. By focusing on creating an agile, iterative production process through data collection, smart factories can aid decision-making processes with stronger evidence. By continuously improving the productivity of manufacturing processes, smart factories can lower costs, reduce downtime and minimize waste. Identifying and reducing misplaced or underused production capacities mean opportunities for growth without investing in additional monetary and/or physical resources. This concept defines a set of design principles needed to enable industrial plant transformation into smart factories, capable to take decisions based on the status of the plant.

- Interoperability: This first principle explores the ability of machines, devices, sensors, and people to connect and communicate with each other via the Internet of Things (IoT). Connect your Smart Tools, sensors and operators on the shop floor to collect valuable data and integrate it with your Manufacturing Execution System (MES), Enterprise Resource Planning (ERP) or other smart factory solution for real-time analysis. It creates a network of interconnected data-generating points that can be accessed and manipulated anytime anywhere. This principle dwells on the technology's ability to provide enhanced information for future decision-making.

- **Modularity**: This is the essence of the production by order. It provides the possibility to change certain parts of a product or an equipment during production in accordance with customer's desires. This principle allows to obtain a dynamic and reconfigurable production line.

- **Virtualization**: The ability of information systems to create a virtual copy of the physical world by enriching digital plant models with sensor data. This requires the aggregation of raw sensor data to higher-value context information. In other words, embracing this industrial revolution's design principle helps monitor processes on the shop floor and allows the management to instantly adjust and optimize for higher efficiency.

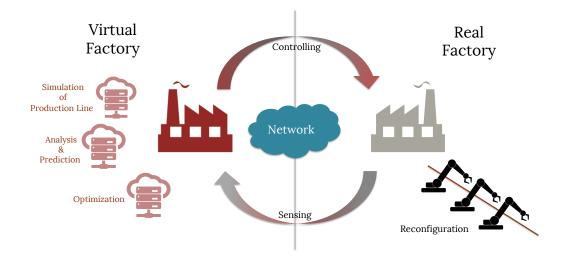

Fig. 1.1: Role of Digital Twin in Industry 4.0.

• **Decentralization**: The decentralization of decisions stems from the ability of Cyber-Physical Systems (CPSs) to make decisions on their own and to perform their tasks as autonomous as possible. Only in case of exceptions, interferences, or conflicting goals, tasks are delegated to a higher level. A decentralized system is also highly adaptable and scalable which determines how efficiently can you respond to industry changes.

The virtualization of the production plant covers a central role in this new revolution. This virtual copy is also called Digital Twin and has the role to mime, predict and optimize what is happening in the real plant (see Figure 1.1).

The entire factory can be represented as a set of CPSs and the resulting system is also called Cyber-Physical Production System (CPPS). This CPPS represents the Digital Twin of the Factory with which it would be possible to make analysis regarding the real factory [3]. The interoperability between the real industrial equipment and the Digital Twin [4] allows to make predictions concerning the quality of the products. Several tools [2, 5] allow to model a production line, considering different aspects of the factory (*i.e.* geometrical properties, the information flows). However, these design principles define only guidelines and actually they are not totally explored in research with methodologies, tools or solutions.

For instance, plant modeling tools [2,5] do not allow to model the plant with a certain level of details. Some works defines coupling solutions between physical and production simulators, but without defining a unified flow to design and simulate the entire factory. Furthermore, most of the works defined only simple equipment models without considering the integration of raw data coming from real equipment. In particular, the problem of model realignment with the data coming from sensors. Scope of this thesis is the investigation on Digital Twin in Industry 4.0 in order to define a set of methodologies to enable virtualization and the interoperability principle.

#### 1.2 Objectives & Methodology Flow

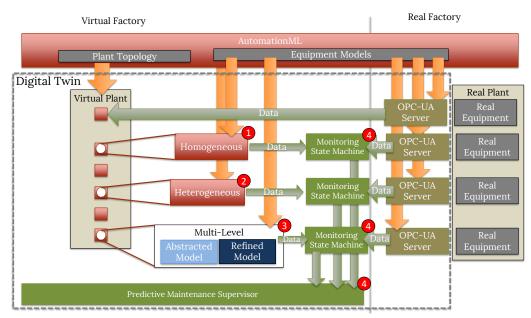

This thesis proposes a set of methodologies to define solutions for the design of Digital Twin in Industry 4.0 (see Figure 1.2). These novel solutions can be summarized in

- Design methodology for Digital Twin;

- Integration of equipment models;

- Integration of real data to enable Predictive Maintenance.

The entire flow is based on the definition and integration of modeling information of the plant in AutomationML, a neutral standard used to exchange data between different designers and stakeholders. Figure 1.2 shows all the different flows that cover the proposed methodologies. On the top of the Figure, there is the abstracted description of the factory, in AutomationML. We have first to distinguish between the information of the plant (topology and material) and the information of each node that composes the entire factory (equipment models) that needs to be integrated in AutomationML. The proposed metholodogies focus mainly on:

- (1) Homogeneous Models;

- ② Heterogeneous Models;

- (3) Multi-Level Models;

- (4) From Real Data to Information.

Each equipment that composes the entire factory can be seen as a CPS, where the cyber part controls physical processes.

The term *Homogeneous model* is used to represents CPS that are modeled using a unique framework or language. For instance, environments that support model-based design paradigm

Fig. 1.2: Overview of the proposed methodologies. Circles represents the aspects discussed in this thesis.

#### 6 1 Introduction

like Ptolemy, Modelica, or Simulink. The proposed approach allows to obtain synthetic nodes, through the OPC Unified Architecture (OPC UA) transmission protocol, that can be used to evaluate equipment models or production recipes effects on the production line.

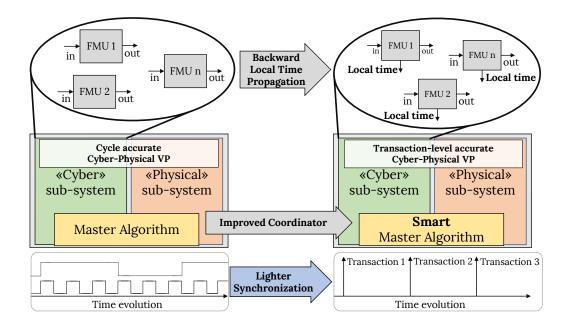

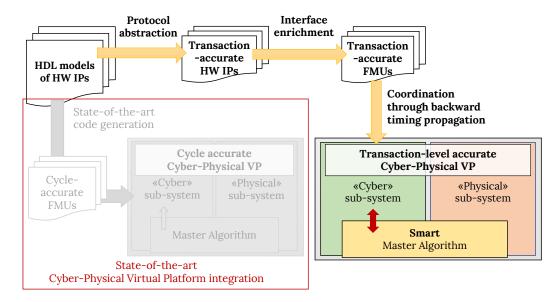

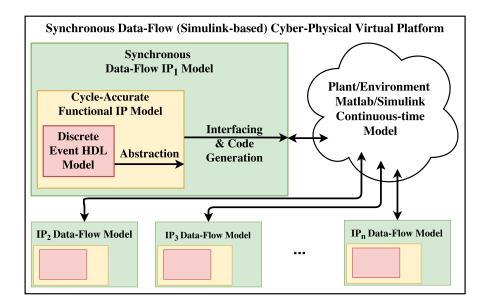

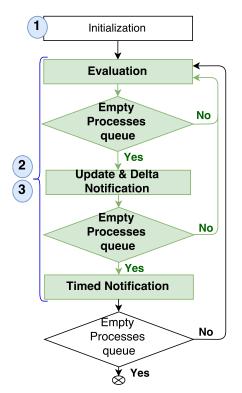

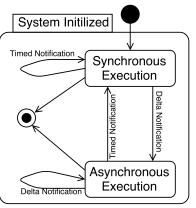

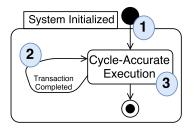

With the term *Heterogeneous Models*, we refer to CPSs that are modeled considering different tools for cyber and physical models. In particular, the use of Hardware Description Languages (HDLs) to model the cyber part and tools to model dynamic systems for the physical process. In this scenario, we focused mostly on the definition of simulation strategies, moving from co-simulation environments to simulation. Moreover, the investigation on the definition and automatic generation of ad-hoc simulation coordinator based on system-level information.

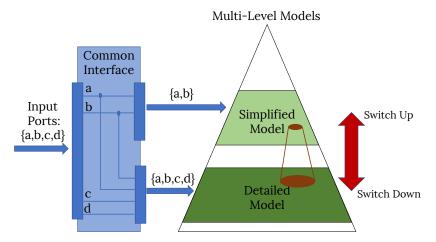

In the *Multi-level* approach, the use multiple descriptions of the same system is discussed. The goal of this approach is to reduce the global complexity of the system by considering two descriptions of the same system with different levels of detail. This approach is based mainly on a simple idea: switching between two models, referring to the same system, to reduce computational effort or increment the level of details when desired.

Finally, with *From Real Data to Information* the investigation on the integration of real data coming from the field. This part seems to be far from what has been explained, but the Digital Twin can not be based only on models. It needs data from the field to be synchronized to analyze the status of the plant. The interconnection within models and real data is necessary for the Digital Twin in order to perform predictions or take decisions regarding equipment maintenance or production plans. From the Digital Twin perspective, raw data needs to be manipulated and transformed in order to dig up information that can be used to plan strategies. This part of the thesis aims to put a first step in this direction, defining a methodology to retrieve equipment status from real data coming from sensors.

The thesis is structured as follows: Part II introduces the proposed approach for the automatic generation of synthetic nodes by integrating *Homogeneous Models* in AutomationML. Part III explores the modeling and simulation of *Heterogeneous Models*, with a particular focus on the discrete part of the system, proposing solutions regarding ad-hoc coordinators based on system-level information. The *Multi-level* approach is shown in Part IV. Part V explains the obtained approach regarding the detection of information from raw data coming from equipment sensors. Finally, Part VI sum-up all the proposed methodologies in a unified example, drawing conclusions, while reporting the publications developed during this thesis in Chapter 13.

**Homogeneous Models**

### Integrating synthetic and real components of a cyber-physical production system

#### 2.1 Introduction

Since their first introduction in 2003 by Michael Grieves, *Digital Twins* have come a long way. They are one of the fundamental pillar of the *Fourth Industrial Revolution* and for a good reason, as they can make things like smart manufacturing a realistic thing.

When we talk about *smart manufacturing*, we refer to a series of technologies that through the usage of interconnected *Cyber-Physical Systems* manage to reach a great production flexibility and things like customized products can be automatically produced by an already operational assembly line, which is impossible with the current mass production as it would require a complete manual readjustment of the assembly line machines. This is only one aspect of *Industry 4.0*. There are a lot of other technologies involved like *Cloud Computing*, *Big Data* analysis, etc., each of them having a specific role for covering a specific aspect.

Digital twins saw many implementations, all of them having usage of models in common. Machine models can be created in many ways at various degrees of abstraction. The important aspect is that these models have to communicate with each other and work together. We call this *Machine-to-Machine* communication and this is what let them to self-configure depending on the condition of the other machines. The most promising protocol for realizing Machine-to-Machine (M2M) communication is OPC Unified Architecture (OPC UA), which offers a platform-independent service-oriented infrastructure. AutomationML [6–8] represents a new standard that allows to exchange information of equipment of plant, between different vendors or designers to make models and in general plant descriptions to be freely exchanged by modeling tools.

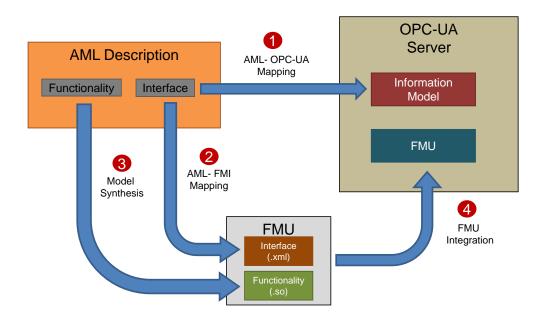

This research work analyzes these technologies and a then presents a case study about the automatic generation of synthetic OPC UA server. Figure 2.1 shows the proposed methodology. The model is defined in a vendor-neutral standard, AutomationML, then synthesized in MATLAB-Simulink, and exported as a stand-alone block with the use of Functional Mock-up Interface (FMI) standard. Finally, the obtained block, called Functional Mock-up Unit (FMU), is wrapped into an OPC UA server. The automatic generation of an OPC UA server from a FMU and its integration within a real virtual twin is also presented. Figure 2.1 reports the overview of the proposed methodology.

Fig. 2.1: Overview of the proposed methodology.

The benefits of the proposed approach are:

- Integration of Simulink semantic in AutomationML vendor-neutral standard;

- Automatic synthesis flow of mechanical models from AutomationML;

- Fully automatic generation of synthetic OPC UA servers for equipment evaluation.

The presented work focuses on mapping Simulink into AutomationML as a proof-of-concept, buts supporting other modeling frameworks can be done by following a similar flow.

The sematic gap between AutomationML and Simulink has been filled with the definition of a special AutomationML class called SimulinkRoleClassLib.

A Simulink model can be the *AutomationML Editor* using this SimulinkRoleClassLib. The use of FMI standard allows to export the synthesized model as a standalone block called FMU.

This can be embedded inside an OPC UA server automatically, and then be added to a production plant simulator to perform production product evaluation. A real digital twin integration example is then presented using Siemens Tecnomatix Plant Simulation, by adding an automatically generated FMU to the plant description of the ICE lab of University of Verona.

Some works tried to generate simulable models from an AutomationML description [9]. The problem of this approach is that while it's very powerful and flexible, it requires the definition and usage of complex ontologies. In [8] the authors explored the usage of semantic web technologies to support AutomationML model exchange, but the major issue comes from lacks in the definition of the used onthology.

This research work is organized as follows: Section 2.2 introduces the main concepts needed to properly understand the rest of the work, like a general overview of the aforementioned standards. Section 2.3 will discuss about the proposed methodology, while Section 2.4 will show practical appliance of the work to a real world example, the ICE laboratory from University of Verona. Finally, Section 2.7 will present some remarks and shows possible future works.

#### 2.2 Background

#### 2.2.1 OPC UA Communication Protocol

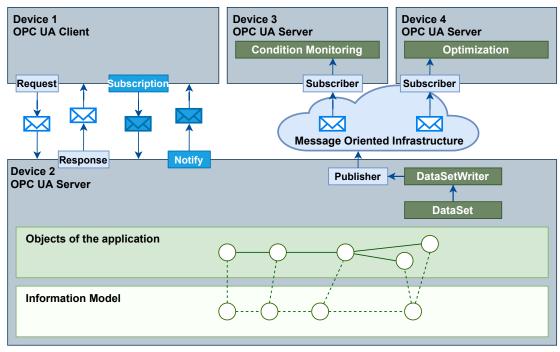

OPC Unified Architecture (OPC UA, [10]) aims to standardize M2M communication [11].

Definition of OPC specifications [12] started to simplify and to standardize data exchange between software applications in industrial environment. The rapid diffusion of the first version of OPC specifications was due to the choice of Microsoft DCOM as the technological basis. However, exactly this point raised the majority of criticism regarding OPC because it was too focused on Microsoft, platform-dependent and not firewall-capable, and thus not suitable for use in cross-domain scenarios and for the Internet. When XML and Web Services technologies have become available, the OPC Foundation adopted them as an opportunity to eliminate the shortcomings of DCOM. Since 2003 the *OPC XML Data Access* (DA) specification has offered a first service-oriented architectural approach besides the "classic" DCOM-based OPC technology. This Web services-based concept enabled applications to communicate independently of the manufacturer and platform.

Few years later, the OPC Foundation has introduced the OPC UA standard which is based on a *service-oriented*, *technology* and *platform-independent* approach, creating new and easy possibilities of communicating with Linux/Unix systems or embedded controls on other platforms and for implementing OPC connections over the Internet. The new possibilities of using OPC components on non-Windows platforms, embedding them in devices or implementing a standardized OPC communication across firewall boundaries allow speaking of a change of paradigms in OPC technology. OPC UA servers can be varied and scaled in their scope of functions, size, performance and the platforms they support. For embedded systems with limited memory capacities, slim OPC UA servers with a small set of UA services can be implemented; at the company level, in contrast, where memory resources are not that important, very powerful OPC UA servers can be used with the full functionality.

OPC UA specifications now offer a security model, which wasn't available in the previous versions of OPC specifications; the OPC UA security governs the authentication of clients and servers and ensures data integrity, trustworthiness and authorization within OPC communication relationships [13].

The OPC UA architecture models Clients and Servers as interacting partners. Each system may contain multiple Clients and Servers. Each Client may interact concurrently with one or more Servers, and each Server may interact concurrently with one or more Clients. An application may combine Server and Client components to allow interaction with other Servers and Clients. Server to Server [14] interactions in the Client Server model are interactions in

which one Server acts as a Client of another Server. Server to Server interactions allow for the development of servers that:

- exchange information with each other on a peer-to-peer basis, this could include for example redundancy;

- are chained in a layered architecture of Servers to provide aggregation of data from lowerlayer Servers, higher-layer data constructs to Clients, concentration interfaces to Clients for single points of access to multiple underlying Servers.

OPC UA can be used at different levels of the automation pyramid for different applications within the same environment. At the plant floor level, an OPC UA server may run in a controller providing data from field devices to OPC UA clients (e.g. HMIs, SCADA). On top of the plant floor at operation level, an OPC UA application may be a client collecting data from the server at the lower level, performing special calculations and generating alarms; an example is represented by an OPC UA client integrated in an ERP system, obtaining information about used devices in the plant floor (e.g. working hours) and creating a maintenance request.

Fig. 2.2: OPC UA stack example

#### 2.2.2 AutomationML

AutomationML is a standard based on XML which aims to provide reliable data exchange in the engineering process of production systems [15]. An interesting aspect of AML is that it doesn't develop any new data format for achieving its purpose, but instead it uses already existing formats, adapted and extended when needed, then merged properly. So far, the representation of

plant specific data in general and in special the plant structure, geometry and kinematics, and logic description is possible. Additional representations for networks, mechatronics systems, and others are in progress. Within IEC62714 all parts of AML are going to be standardized internationally. AutomationML has a lean and distributed file architecture. It does not define any new file format but combines existing established XML data formats which have been proven in use for their specific domain. This is why the normative part of the IEC62714-1:2018 document consists of 32 pages only. The data formats for the following modelling domains are:

- object topologies including hierarchies, properties and relations of objects: CAEX according to IEC 62424

- geometries and kinematics of objects: COLLADA 1.4.1 and 1.5.0 (ISO/PAS 17506:2012)

- *discrete behavior* of objects: PLCopen XML 2.0 and 2.0.1; in addition, IEC62714-4 will allow the usage of IEC61131-10

CAEX according to IEC62424 forms the base of AutomationML. It stores object-oriented engineering information, e.g. a plant hierarchy structure (see AutomationML topology). Each CAEX object can contain properties and reference geometry, kinematics or logics information stored in third party XML files. This enables cross-domain modelling and is designed for future extension.

#### **Topologies**

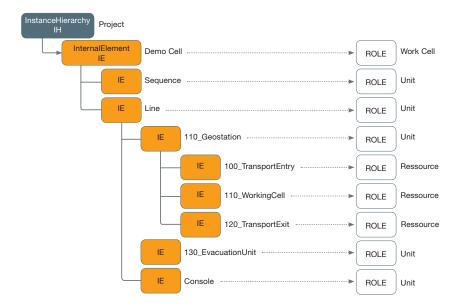

Object hierarchies in CAEX form the core of AutomationML (as in figure 2.3). A CAEX object is a data representation of any asset. It can model physical assets, e.g. a motor, a robot, a tank; or abstract assets like a function block, a model or a folder. CAEX allows to link those objects to systems, since every physical or logical system is characterized by internal elements (objects) which may contain further internal elements, and all elements may have interfaces, attributes and connections with each other. Finally, CAEX allows the modeling of any plant topology, communication topology, process topology, resource topology etc.

#### Geometry and kinematics

As mentioned above AutomationML exploits the international standard COLLADA 1.4.1 and 1.5.0 for the representation of geometry and kinematics information which is standardized as ISO/PAS 17506:2012. Therefore, AutomationML has developed a two-stage process:

- 1. relevant geometries and kinematics are modelled as COLLADA files.

- 2. these files and the data objects within them are referenced out of the CAEX file.

COLLADA stands for COLLAborative Design Activity. It was developed by the KHRONOS association under the leadership of Sony as an intermediate format within the scope of digital content creation in the gaming industry.

It is designed to enable the representation of 3D objects within 3D scenes covering all relevant visual, kinematic, and dynamic properties needed for object animation and simulation.

Fig. 2.3: Example of a plant topology in AML.

COLLADA is an XML-based data format with a modular structure enabling the definition of libraries of visual and kinematic elements. It can contain libraries for the representation of geometries, materials, lights, cameras, visual scenes, kinematic models, kinematic scenes, and others.

The most important feature of AutomationML is the clear identifiability of objects in COLLADA files, which allows the integration of these files into AutomationML. Several data objects within a COLLADA file have a unique identification (ID) like geometries, visual scenes, kinematic models and kinematic scenes.

In order to reference these objects, AutomationML has defined a special interface class within the AutomationMLInterfaceClassLib named COLLADAInterface which shall be applied to derive the needed interfaces for geometry integration. This interface class itself is derived from the interface class ExternalDataConnector and therefore has an attribute refURI. This attribute can be used to reference into a COLLADA file, thereby referring to an ID of an object modelled in the COLLADA file.

Thus, the value of the refURI attribute shall contain a string structured like

file:///filename.dae#ID. The attribute refType is used to differentiate between various ways of embedding objects in a modeled scene. It can provide information on how static an object in the scene is in relation to other objects, e.g. whether a work piece and the conveyor belt move at the same time.

#### Modeling behaviour

AutomationML with its object-centric modelling approach enables a dedicated storing of logic information on object level. For this purpose, certain object semantics as well as object interface semantics are developed. In addition to that, logic models are identified, commonly used in the

engineering process of a production system, and made exchangeable, but also transformable among each other. This allows and supports an information enrichment process in terms of logic information that is required for the scope of AutomationML. All concepts are going to be standardized in IEC 62714-4.

Logic information is an important aspect for raw system planning, electrical design, HMI development, PLC and robot control programming, for simulation purposes, and virtual commissioning. To support the different phases in the iterative production system engineering process covering different levels of detail, AutomationML needs to be able to store logic information from different tools and disciplines.

#### 2.2.3 Functional Mockup Interface

The FMI standard defines an interface that allows to encapsulate models from different tools. The primary goal is to support the exchange of simulation models between suppliers and OEMs even if a large variety of different tools are used. Actually the 2.0 version of the standard has been released, and it consists of two main parts: Model Exchange and Co-Simulation.

The *Model Exchange* interface provides a method to generate C-code in the form of an input output block. This method is used by different simulators to export only the descriptions of their models without exposing their internal solver algorithm which, in general, is closed source.

The *Co-Simulation* interface provides a method to export a model in the form of a block including also a mathematical solver needed to execute correctly that model. This allows a simulator to load and execute other models correctly even when the correct solver is not available. The provided model description is very similar to the *Model Exchange* one. The main difference between the two approaches is the location of the solver: in the first case it is provided by the simulator tool while in the second is integrated into the model exported.

A component which implements the interface is called FMU.

#### 2.2.4 MATLAB/Simulink

MATLAB is a multi-paradigm numerical computing environment, featuring a proprietary scripting language developed by MathWorks. MATLAB allows matrix manipulations, plotting of functions and data, implementation of algorithms, creation of user interfaces, and interfacing with programs written in other languages. The environment is highly configurable and extensible with plugins, and in fact one of the most popular one is Simulink, which frequently comes directly with the default MATLAB installation. Simulink adds graphical multi-domain simulation and model-based design for dynamic and Embedded Systems. In Model-Based Design, a system model is at the center of the workflow. Model-Based Design enables fast and cost-effective development of dynamic systems, including control systems, signal processing systems, and communications systems. Model-Based Design allows you to:

- use a common design environment across project teams

- link designs directly to requirements

- refine algorithms through multi-domain simulation

• automatically generate embedded software code and documentation

Till version 2019b Simulink had a plugin, called "Tool-Coupling Co-Simulation FMU Export", that allowed to export a model as an FMU, supporting the Co-Simulation technique. The problem is that this approach required to have a local MATLAB installation to effectively simulate the model, and it wasn't a robust approach. Starting from MATLAB 2020a, Simulink allows to export a standalone FMU without requiring an external MATLAB instance, but embedding a fixed-step solver.

#### 2.2.5 Tecnomatix Plant Simulation

Tecnomatix Plant Simulation is a computer application developed by Siemens PLM Software for modeling, simulating, analyzing, visualizing and optimizing production systems and processes, the flow of materials and logistic operations. By using Tecnomatix Plant Simulation, users can optimize material flow, resource utilization and logistics for all levels of plant planning from global production facilities, through local plants, to specific lines. Tecnomatix Plant Simulation belongs to the Product Lifecycle Management Software (PLM) portfolio. Plant Simulation is a Material Flow simulation or Discrete Event Simulation (DES) Software. Material flow refers to the description of the transportation of raw materials, pre-fabricates, parts, components, integrated objects and final products as a flow of entities. This means that a computer model allows to execute experiments and to run through "what if scenarios" without either having to experiment with the real production environment or, when applied within the planning phase, long before the real system exists.

#### 2.3 Methodology

This section describes the methodology adopted to implement the synthetic OPC UA node, starting from AutomationML. First, the semantic map between Simulink and AutomationML is explained. Then, the entire generation flow is discussed. Detailed steps are explained for the actual AutomationML document parsing and also a look at the final OPC UA server, discussing the adopted solutions.

#### 2.3.1 Mapping Simulink components in AutomationML

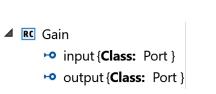

This section discusses about the semantic mapping between Simulink and AutomationML. AutomationML, or more precisely CAEX, uses the concept of *Role* to define semantics. A role describes an abstract functionality without defining the underlying technical implementation. Thus, it has to be seen as an indicator for the semantics of an object which can be described in an abstract way. Roles can include general attributes (size, number of axes, etc.) and interfaces (PPRConnector, ...) to describe the interaction possibilities of the element which assigns this role. Roles are organized hierarchically in libraries and can have interrelations to other roles and further elements to describe their dependencies.

- - ▲ RC Commonly Used Blocks

- RC Out1

- ▲ RC Math Operations

- RC Add

- ▶ RC Product

- RC Gain

- ▶ RC Continuous

- > RC Sources

- ▶ RC Signal Routing

- ▲ RC Simscape

- ▲ RC Foundation Library

- ▶ RC Mechanical

- ▲ RC Utilities

- ▶ RC Simulink-PS Converter

- ▶ RC PS-Simulink Converter

- ▶ RC Solver Configuration

- ▶ RC Driveline

- RC Simulation Control

Fig. 2.4: The final result of SimulinkRoleClassLib

AutomationML defines some basic role sets by default. These roles are based on the general role class library (AutomationMLBaseRoleClassLib) defined in the AutomationML standard. The role class AutomationMLBaseRole in the AutomationMLBaseRoleClassLib is a basic abstract role type and the base class for all standard or user-defined role classes. All AML objects shall be associated directly or indirectly to the role class AutomationMLBaseRole to have a common basis, e.g. for simplifying the implementation. Role class libraries can be defined for general use cases but can also relate to specific domains. They don't need to be standardized or defined by AutomationML but can also be created by user groups or single users of AutomationML. The main contribution of this work is the definition of a specific AutomationML RoleClassLib, called SimulinkRoleClassLib, that contains all the Simulink components semantic with their respective properties (see figure 2.4).

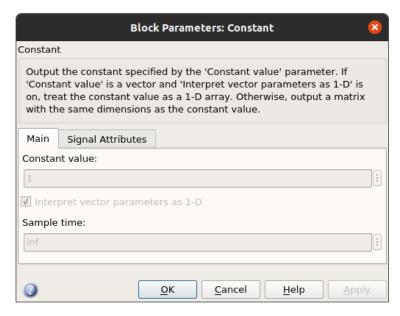

#### Mapping of Constant

Simulink Constant, represents a simple component that gives as output a constant value. Inside the *Library Browser*, the Constant can be found in Sources section, thus the correspondent RoleClass path will be SimulinkRoleClassLib/Sources/Constant. As the

Fig. 2.5: Attributes of the Simulink Constant component

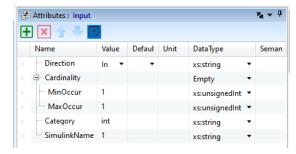

- AutomationMLBaseRoleClassLib

- ▲ SimulinkRoleClassLib

- ▶ RC Commonly Used Blocks

- RC Math Operations

- ▶ RC Continuous

- ▲ RC Sources

- ▲ RC Constant

- output (Class: Port )

- RC Ground

- RC In1

- ▶ **RC** Signal Routing

- ▶ RC Simscape

- RC Simulation Control

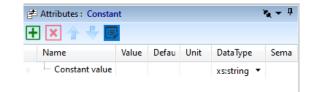

Fig. 2.7: The Constant RoleClass only mapped attribute

Constant component doesn't have any input port, in the correspondent AML RoleClass only the output port was instantiated (2.6). Attributes of this component are very simple, the only interesting one being Constant value, mapped in AML through a xs:string data type (2.7). In general, all the attributes will be mapped as strings, because Simulink accepts only strings (that will be parsed by MATLAB internally).

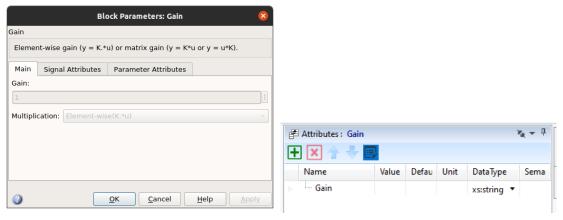

#### Mapping of Gain

Another simple yet fundamental component being mapped is the Simulink Gain (2.8). In this case, the component has both an input and an output port (2.10) representing the initial value and the value multiplied by the gain, and the gain's value itself is stored in the appropriate attribute (2.9). It is worth mentioning the port attributes, common to all I/O ports in

Fig. 2.8: Attributes of the Simulink Gain component

Fig. 2.9: The Gain RoleClass only mapped attribute

Fig. 2.10: The Gain RoleClass

Fig. 2.11: The Gain input port attributes

SimulinkRoleClassLib. Being instance of the Port base AML interface, all shares the following attributes:

- Direction

It can be In, Out or InOut and it specifies if that port receives or sends data.

- Cardinality

This combined attribute specifies how many connections the port is supposed to have.

- Category

This specifies the type of the data that's passing through that port.

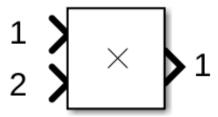

In addition to these, a fourth attribute was added, SimulinkName. This is because MATLAB uses special names for manually linking components' ports. When Simulink components are used, ports gets numbered starting from 1, both for inputs and outputs, in the way shown in 2.12.

Fig. 2.12: How the ports gets named for a Simulink component

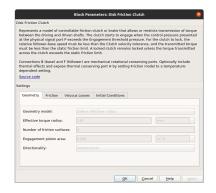

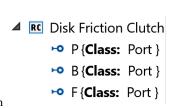

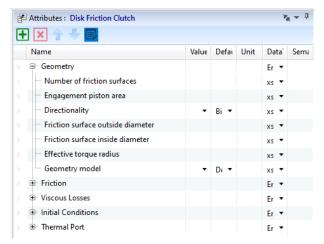

#### Mapping of Disk Friction Clutch

This component belongs to the Simscape library, an extension toolbox of Simulink, which provides a lot of specific and complex blocks for modeling and simulating multidomain physical systems (mechanical, rotational, electrical *etc.*).

$\textbf{Fig. 2.13:} \ \textbf{Attributes of the Simscape Disk Friction Clutch component}$

Fig. 2.14: The Disk Friction Clutch RoleClass

This component has a lot of attributes, distributed among tabs. Inside AutomationML this logical division can be achieved through "composite" attributes as shown in 2.15. Being a Simscape component, the SimulinkName attribute is different. In fact here ports get named by position plus number, so the first port at the right will be named RConn1, while the second will be RConn2 and so on. The same goes for the left sided ports, the only difference being the first letter which will be L, so we'll have LConn1, LConn2, etc. as shown in 2.16.

#### 2.3.2 AML to MATLAB

First thing to do is analyzing the AutomationML document and grab the useful information for converting it to a MATLAB script. Being AutomationML a combination of CAEX, COLLADA and PLCOpenXML, parsing it is equal to parsing XML. Before beginning to write a parser, research was done in order to understand if there were already existing parsers, also seeing if they could be

Fig. 2.15: The Disk Friction Clutch mapped attributes

Fig. 2.16: Port names for Simscape components

reused for our purpose. The methodology has been implemented in an automatic parser written in C++.

The conversion from an AutomationML model written with SimulinkRoleClassLib to a MATLAB script takes place in a dedicated class, called AML2MATLAB. Before the actual conversion process, the MATLAB scripting commands for generating Simulink models are explained.

#### **MATLAB** script

MATLAB provides two basic primitives respectively for adding and connecting Simulink blocks:

- add\_block()

- add\_line()

In addition to these commands there are a set of other methods needed to set model parameters, auto-arrange the model's layout, and so on.

The add\_block() primitive takes *n* parameters as input, with the first one being the Simulink absolute path of the object, the second one the relative path of the model along with the block instance name, and from the third onwards the object's parameters, expressed as

'NAME\_OF\_THE\_PARAMETER', 'PARAMETER\_VALUE'

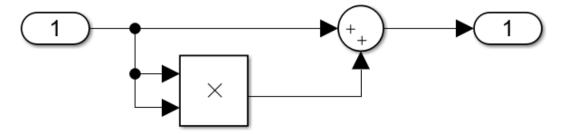

Listing 2.1: Matlab script that generates simple Simulink model.

```

model = 'AdderAndMultiplier';

1

2

3

new_system(model);

4

open_system(model);

add_block('simulink/Commonly Used Blocks/In1',[model,'/Input']);

7

add_block('simulink/Commonly Used Blocks/Sum',[model,'/Sum']);

8

add_block('simulink/Commonly Used Blocks/Product',[model,'/Product']);

9

add_block('simulink/Commonly Used Blocks/Out1',[model,'/Output']);

10

11

add_line(model,'Input/1','Sum/1');

add_line(model,'Input/1','Product/1');

add_line(model,'Input/1','Product/2');

add_line(model,'Product/1','Sum/2');

14

add_line(model,'Sum/1','Output/1');

```

The add\_line() primitive takes three input. The first is the name of the system, the second is the origin of the line (RefPartnerSideA in AML) and the third is the endpoint (RefPartnerSideB in AML).

Fig. 2.17: The result of the script reported in listing 2.1

Listing 2.1 shows a simple matlab script that represents the simple model shown in figure 2.17. Lines 6,9 represent the instantiation of all the blocks that composes the model. All the blocks are then linked add\_line function (lines 11,15).

#### 2.3.3 OPC UA server from FMU

The generated model can be easily exported as an FMU through a set of predefined function, using MATLAB GUI or also through a set of function and embbeded in the matlab script. Now that the Simulink script has been produced, it can be run inside the MATLAB environment to produce a standalone co-simulation FMU. The limitation of MATLAB FMU exporter is that the encapsulated solver used a fixed-step strategy that is not precise like the variable-step solvers.

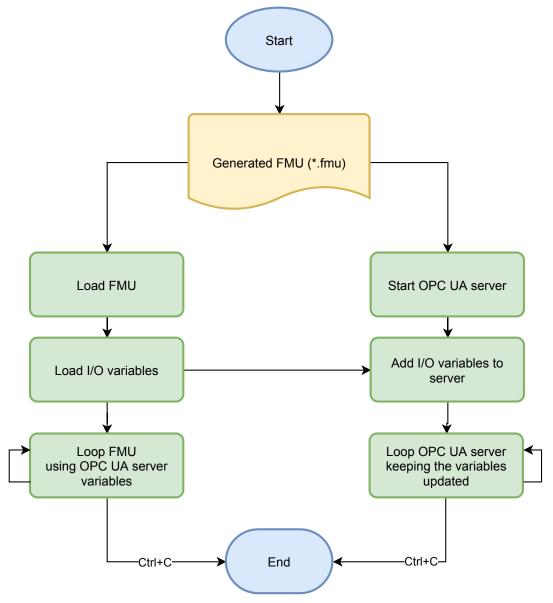

For the simulation of the generated FMU inside an OPC UA server, a wrapper is needed. The wrapper has to load the FMU, read its I/O variables, start an OPC UA server and put those I/O variables in it. This routine has to be executed with a certain frequency and for each loop

executing a simulation step, using the values from the OPC UA server for I/O, as shown in 2.18. This wrapper has been developed using C++, using FMI4CPP to manage the FMU and the

Fig. 2.18: Structure of the wrapper routine.

open62541 OPC UA stack [16] to create the OPC UA node.

#### 2.4 Experimental Results

In this Section the result of the model generation flow is integrated first into a simple model and then into the *Digital Twin* of the ICE lab, an educational lab of University of Verona for

demoing Industry 4.0 concepts and research. Both the examples are made using Tecnomatix Plant Simulation.

The model which gets integrated into both project is the *Two Speed Transmission* which represent an electric mechanical engine with two speeds gearbox. It was first mapped to AutomationML using the SimulinkRoleClassLib, then parsed with amlparser and the resulting script was run inside MATLAB, thus generating an FMU. This FMU is then hosted by running FMU2OPCUA.

#### 2.5 Simple producer-consumer

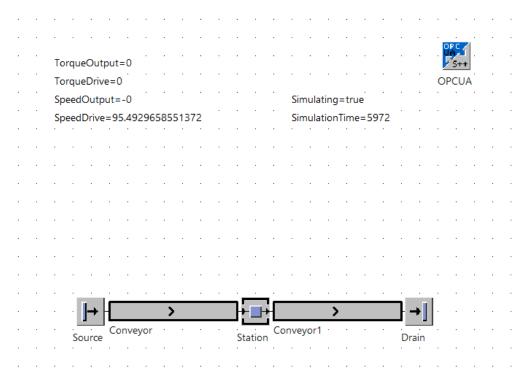

The simple model (2.19) is composed of a *Source* which produces *Mobile Units* (MUs) in a certain amount, a *Station* which represents a generic processing step and a *Drain* which consumes the processed unit.

Fig. 2.19: The simple model scheme.

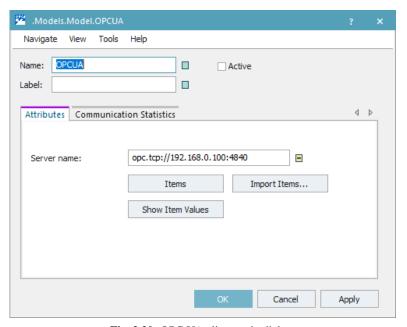

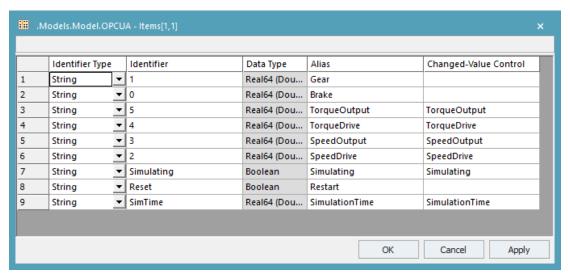

Plant Simulation offers an integrated OPC UA client (the one on the top right of 2.19) which is fairly simple to use. Once added to the model, its dialog window asks for the IP address and the port (2.20). Global model variables can be directly connected to the ones exposed by the server through the Items dialog as shown below in 2.21. By doing this way, whenever the server variables' values change, the Plant Simulation variables written in the far-right column gets updated with the same value automatically.

Fig. 2.20: OPC UA client main dialog.

Fig. 2.21: Model variable - Server variable connections.

On the *Station* block in the middle, a method is added on the exit control section, which means that whenever an MU exits the machine the method is going to get called. As the FMU2OPCUA program supports different simulation modes, one can either choose to produce a predefined input signals set based on time and use the SimulationTime exposed variable to change signal values accordingly, or just rely upon the default stop experiment time and just set values in that restricted time slice. There's also another way which was the chosen one, which is the manual mode. In this mode the simulation gets controlled by the client through the DoStep port.

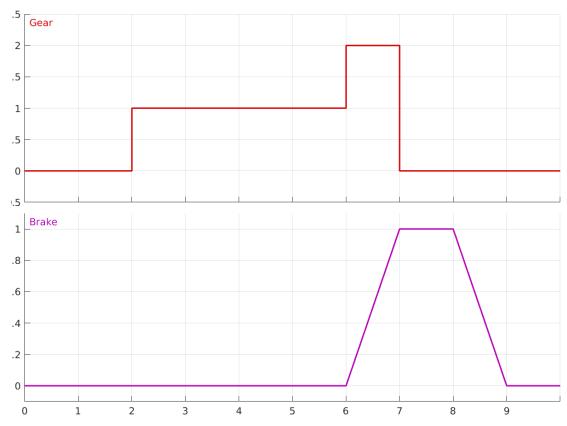

Fig. 2.22: The Brake and the Gear signals for the Station.

In this case, the response is quiet, as the maximum gear value reached is 1 and the brake gets up till 0.5, so when the simulation time is 10 the SpeedOutput will already be 0. The result is that for every MU produced by the source, 10 seconds will pass when entering the station, regardless of the simulation speed.

# 2.6 The ICE lab model

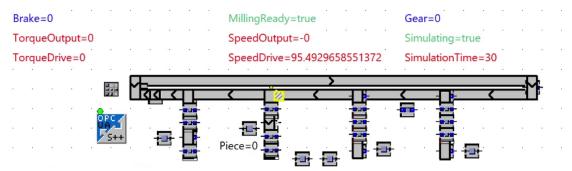

Fig. 2.23: The ICE lab Digital Twin.

The ICE lab model is quite complicated as shown in 2.23. It's composed of many parts:

- A vertical storage

- The conveyor belt system and a mini pallet

- An electronic control panel

- A milling machine

- Two 3D printers

- An assembly station

- A robotic vision system

This digital twin simulates the following process:

- 1. The MUs stored in the vertical storage are taken on the mini pallet

- 2. When the mini pallet reaches the stations, it gets processed

- 3. The milling station is where the FMU has been inserted

The *Two Speed Transmission* model can be used to mimic the processing time of the milling machine. Different "recipes" can be used, each one representing a different signal set, selectable from a menu on the top right corner. This is useful for simulating the different effects that different input signal sets can have on the processing times.

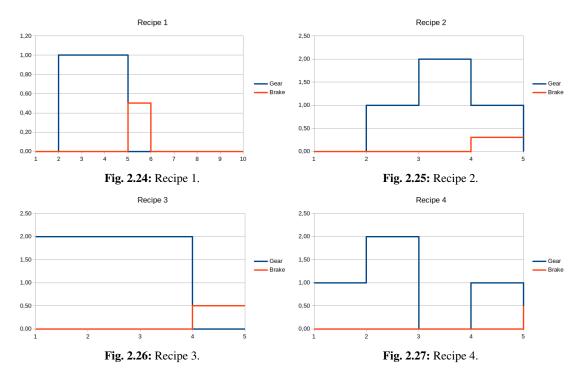

Fig. 2.28: The four recipes input signals

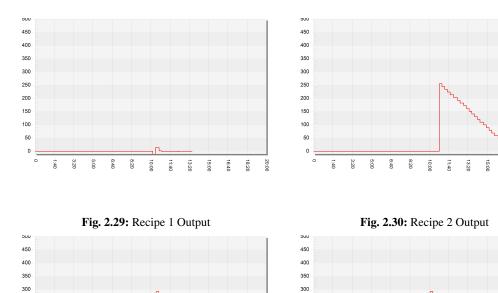

Four recipes were made, represented in 2.28. Figure 2.33 reports the different output obtained with the recipes.

It can be observed that when the gear reaches value 2, the speed output goes up to 250-300, while in the first recipe it doesn't even go beyond 30. In the first recipe the gear has a maximum value of 1 and it lasts 2 seconds, while the brake is also more powerful reaching 0.50. In the other recipes the relation between the speed and the brake intensity and duration can be easily observable. The As the brake gets 0 after the 5th second of simulation, the speed slowly goes down to 0 because of the inertia.

Note that the timing reported in the graphs are the ones of Plant Simulation, which is running at 47× the real speed, while the FMU is running at real time, so for example in the second recipe the actual time that the motor took for reaching a speed value of 0 is 30 seconds.

# 2.7 Conclusions

This work proposed a flow to model generic models in a vendor neutral language as AutomationML and showed a semi-automatic flow of model generation and simulation.

This work showed the possibility to map a Simulink model into AutomationML without the use of ontologies [9].

Then, it showed the integration of OPC UA protocol that enable the interconnection with real equipment and synthetic equipment.

Fig. 2.31: Recipe 3 Output.

250

200

150

100

Fig. 2.32: Recipe 4 Output.

Fig. 2.33: Output of the four recipes.

250

200

150

There are many possible areas of improvement in this flow, and also some ideas that could be useful in some scenarios. Improvements that can be applied to the prototypes for making them usable software products are:

- Map in the SimulinkRoleClassLib the entire Simulink library

- Further expand the AML lib with Simscape library

- Add correspondent mapping behavior in the JSON files

- Implement support for subsystems during the MATLAB model generation

- Making AML parser better in supporting SystemUnits and multiple RoleClasses

In addition to these improvements, there are also some ideas based on this work that could be worth exploring, such as:

- Explore the possibility to develop a MATLAB plugin that exports a Simulink model in AutomationML

- After having implemented support for subsystems, implement support to combine different models in AML, expressing a full production chain

- Mapping other modeling languages such as Modelica

**Heterogeneous Models**

# **Automatic Integration of HDL IPs in Simulink using FMI and S-Function Interfaces**

# 3.1 Introduction

Model-based design is nowadays one of the most used approach to tackle heterogeneity and complexity of modern systems [17]. High-level models are step-by-step refined to reach the final system implementation. Over the years, Simulink by Mathworks [18] became the standard "de-facto" in Model-based systems engineering. It provides a nice graphical environment that allows designers to easily model physical systems and their controllers. It provides many different libraries (*i.e.*, toolboxes) full of models and functionalities useful to build and analyze simulations. These features lead it to became the favorite tool of many control and system engineers.

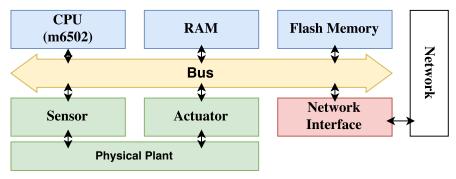

However, Simulink does not provide mechanisms that allows to simulate computational systems. For instance, it does not natively allow to simulate the exact behavior of a SW running on top of an actual HW platform. A task that can be necessary to accurately evaluate timing of HW/SW components controlling cyber-Physical systems [19]. Thus, to perform such kind of analysis in Simulink it will be necessary to exploit HW-in-the-loop and co-simulation techniques. These require specific expertise and are extremely error prone and time consuming: as such, they may negatively impact the time-to-market. This limitation must be overcome as cyber-physical systems and smart devices are everyday more used to control physical processes. In this work we propose a methodology to automatically generate Simulink-compliant blocks from HW Description Language (HDL) models.

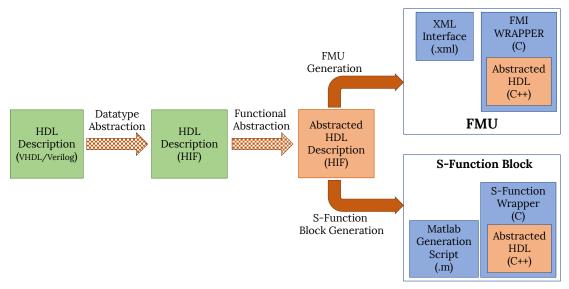

The methodology starts from either a Verilog or a VHDL Register Transfer Level (RTL) model. The HDL model is automatically abstracted into an equivalent cycle-accurate C++ model by a state-of-the-art abstraction methodology [20]. We extend this code-generation step to map the abstracted models into two interfacing technologies supported by Simulink: the Functional Mock-up Interface (FMI) [21] and the proprietary C MEX S-Functions.

The models of HW devices generated by the presented methodology can be easily imported within Simulink. Thus, they provide a simpler and more efficient alternative to co-simulation and HW-in-the-loop techniques. To show the advantages of the approach we compared the performance in terms of simulation speed on a set of HDL benchmarks. First, we integrated them within Simulink by co-simulating them using a commercial HDL simulator. Then we

integrated the benchmarks by applying the proposed methodology. The experimental results showed up to one order of magnitude speed-up with respect to state-of-the-art co-simulation environments, while preserving accuracy.

Section 3.2 presents some literature about heterogeneous systems simulation, the necessary background and will introduce a running example used throughout the paper. Section 3.3 will present the methodology and its application to the running example. Section 3.4 reports the experimental evaluation of the methodology. After discussing our results, in Section 3.5 we draw some conclusions and give an overview about our ongoing and future research directions.

# 3.2 Related Works

Model-Based Systems Engineering [22, 23] requires a multitude of tools to be integrated at each design step. This is imposed by the amount of heterogeneous domains involved in modern systems [24]. Many design steps (e.g., validation or performance estimation, etc.) require holistic system simulation, usually achieved through co-simulation [25]. Multiple domain-specific simulators are connected to each other; one of the simulator takes care of coordinating and synchronizing all the involved simulators to achieve the complete system emulation. At the state-of-the-practice, Mathworks Simulink [18] is the standard de-facto system simulation tool. For this reason, many attempt to extend its capability to specific domains have been carried out. It has been connected to network simulators [26,27], digital HW simulators [28], instruction-set simulators [29] and many other different kinds of simulators. Furthermore, it has been coupled also with other specific multi-physics simulators. For instance, Haoping et al. used Synopsys Saber [30], Wang et al. proposed an approach using Adams [31] or While in [32] it has been presented a scenario mixing PSpice with Simulink. Another work shows the benefits of coupling Simulink with a Manufacturing Simulator, with the objective of obtaining more accurate estimation about the production quality of a manufacturing system [33]. Other approaches propose solutions to couple complex computational systems with Simulink in order to model and verify cyber-physical systems. In [34] Kawahara et al. connected SysML and Simulink to test and verify the correctness of an embedded system. In [35] Tudoret et al. uses the SIGNAL programming language to model real-time constraints of a software controlling a a physical scenario designed using Simulink, Kung et al. coupled an HDL commercial simulator with Simulink for early validation of HW constraints [36]. All the approaches mentioned above use co-simulation techniques that have been proven to be computational demanding, while its setup may be an error-prone and time consuming processes [24]. As such, some alternative approaches have been defined: they aim at integrating models by translating and importing them into the target simulation environment [37, 38]. However none of the previous works provides neither abstraction nor automation. These features are focal in the approaches presented in [39, 40]: the heterogeneous models of the system components are translated into a homogeneous holistic representation of the cyber-physical system to simulate. However, these approaches requires that the designer can access the original source code of each single part of the system: a rare eventuality in real design flows. The methodology presented in this chapter aims at exploiting tools integration, while providing automation. It automatically integrates cycle-accurate models of digital HW components within Mathworks Simulink through automatic abstraction and translation of the original HW IP cores, and then automatically enriching the generated code to interface it with the target simulator.

# 3.2.1 Running example

For the sake of clarity, in the following of the chapter we pair the presentation with a running example that represents a IP core HDL description. Its code is depicted in Listing 3.1. It is a Verilog model of a HW module counting the number of positive bits in a 64-bit integer given as input to the module. It carries on such a task by employing a synchronous process performing combinational operations and an asynchronous process controlling the counting algorithm. It has been written to provide a minimal while complete example for the proposed methodology.

# 3.2.2 FMI-Standard

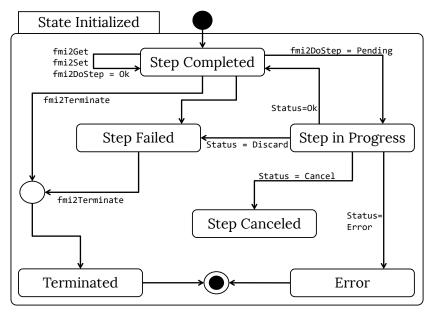

The basic blocks of a FMI-based simulation environment are called *Functional Mock-up Units* (*FMUs*). Multiple FMUs can be imported within simulation environments such as Simulink that takes care of managing FMUs execution. Each FMU may implement the *Model Exchange* or the *Co-simulation* version of the FMI standard. A Model Exchange FMU requires an external solver to simulate. A Co-simulation FMU must provide the solver within its functionalities. This work focuses only on the Co-simulation version of the standard, being more suitable to model discrete behavior.

A co-simulation FMU is composed by an XML file and a dynamic library implementing its functionality. The XML file specifies all the variables that are exposed to the simulation environment by the FMU [21]. For each variable, the XML file must specify its name, causality (e.g., input, output, parameter, etc.), its type and a value reference. The supported variable types are 32 bit integer, real, string and boolean. The value reference of a variable is required to be unique for all variables of each type: each variable will be uniquely identified by its type and value reference pair.

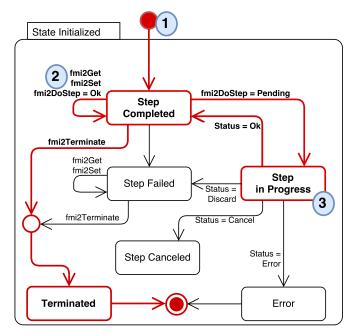

The dynamic library must be generated using C-like linking. It must implement the functionality through a set of functions defined by the standard:

- The fmi2SetupExperiment function is usually used to initialize the internal variables of the FMU

- The fmi2Set function sets the value of an internal variable of the FMU *i.e.*, assigns a value to an input.

- The fmi2Get function gets the value of an internal variable of the FMU *i.e.*, returns the value of an output.

- The fmi2DoStep advances the simulation time of the component executing the behavior defined by the model.

**Listing 3.1:** Original Verilog code of the running example.

```

1

module bit_counter(clk,reset,number,nready,result,rready);

2

3

input clk, reset, nready;

input [63:0] number;

4

output reg rready;

output reg [4:0] result;

8

integer state, next_state, index;

9

localparam state_reset=0, state_counting=1, state_output=2;

10

11

always @ (posedge clk or negedge reset) begin

12

if( reset == 1'b0 )

13

state <= state_reset;</pre>

14

else begin

state <= next_state;</pre>

15

case( next_state )

16

17

state_reset: begin

18

index \ll 0;

19

result <= 5'b00000;

20

rready <= 1'b0;

21

end

22

state_counting: begin

23

if( number[index] == 1'b1 )

24

result = result + 1;

25

index = index + 1;

rready <= 1'b0;

26

27

end

28

state_output:

29

rready <= 1'b1;

30

endcase

31

end

32

end

33

always @ ( state or nready or index or number ) begin

34

35

case( state )

state_reset:

36

37

if( nready == 1'b1 ) next_state <= state_counting;</pre>

38

else next_state <= state_reset;</pre>

39

state_counting:

40

if( index > 63 ) next_state <= state_output;</pre>

41

else next_state <= state_counting;</pre>

42

state_output:

43

next_state <= state_output;</pre>

44

endcase

45

end

endmodule

```

While the standard defines the signature of all the functions to implement, it does not define the sequence in which these functions should be called. It rather defines only some limitations on the possible combinations. In the last months the FMI Steering Committee announced a new version of the standard (*i.e.*, version 3.0) introducing a new interface called *Hybrid Co-Simulation*, and inspired by the some recent research [41]. It should introduce the possibility to easily handle Discrete-Event Systems. As of today, this new interface is in a pre-alpha status and some of the currently proposed features might end up to be not approved in the final version of the standard update.

#### 3.2.3 Simulink C MEX S-Functions

C MEX S-Functions are the main mechanism provided by Mathworks Simulink to import custom C/C++ code. They provide similar concepts with respect to the FMI standard. However, they do not impose the signature of the functions to implement. S-Functions require to fill a configuration file specifying, among other parameters, the signature of some functions (*i.e.*, callback methods) that will be used by the simulators to execute the functionality. In this work we will use two of these callback methods, that are:

- the *Initialization function* performs initialization actions at the simulation startup. Its name is specified in the configuration file through the mdlStart method.

- The *Outputs function* is a C function that takes as parameter a set of input values and a set of references to output variables. It defines the functionality the S-Function must implement at each simulation time. It is specified through the mdlOutputs callback method.

The simulator executes the initialization function when the model is instantiated. Then, it executes its output function at each simulation step. Thus, the order in which the input-reading, execution, and output-writing operations are performed is managed internally to the output function by the programmer.

# 3.2.4 Automatic abstraction of HDL IPs

Efficient HDL simulation has been achieved in the recent years by applying automatic abstraction [42] and code generation [43,44]. HDL models are translated into functionally equivalent, cycle-accurate C/C++ models.

Since this work aims at generating cycle-accurate models based on the FMI Standard or Mathworks' S-Functions, state-of-the-art abstraction and code generation techniques are suitable to be reused. This work relies on the technique described in [20] to generate the C++ models that will be later wrapped within FMUs or S-Functions. The approach in [20] works as follow:

- a front-end phase parses and analyzes the input HDL model. It extracts the digital processes described in the model and all the dependencies between processes (*e.g.*, sensitivity lists, signal writing and reading, *etc.*). Dependencies analysis is required in order to manage descriptions involving both synchronous and asynchronous processes.

- The analysis produces a dependencies graph: it is used to generate a process scheduling

that allows to reproduce the cycle-accurate behavior of the model. The scheduling generation starts from synchronous processes and then proceeds considering the dependencies

of already scheduled processes. Furthermore, the scheduling generation procedure resolves eventual circular dependencies between processes: resolution feasibility is guaranteed by synthesizability of the considered HDL models. As such, the RTL protocol is abstracted into a Transaction-level protocol [42] and the abstracted model is externally synchronous while reproducing asynchronicity internally.

• The model is translated into C++. Each process is translated into an equivalent C++ implementation. A mechanism based on replicated variables, flags and supporting functions is automatically generated to emulate processes concurrency. Each transaction is executed by the execution of a function (*i.e.*, simulate function) to which is passed a pointer to a payload data structure (*i.e.*, model\_iostruct). This structure contains a field for each input or output port of the original model (except for the clock signal, being it abstracted away). As such, each simulation cycle starts by populating the input/output data structure, then the simulation function is called and at its completion the data structure is read.

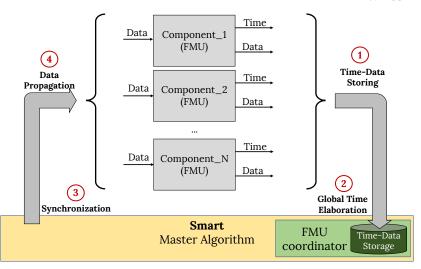

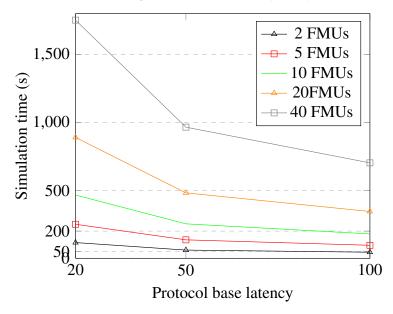

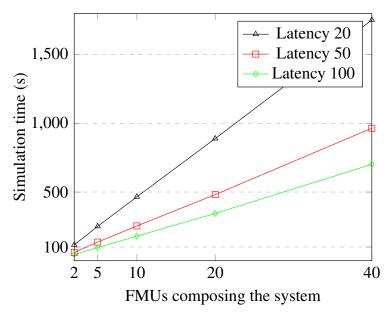

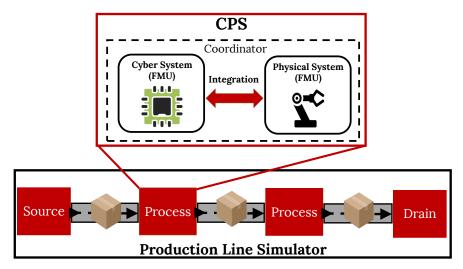

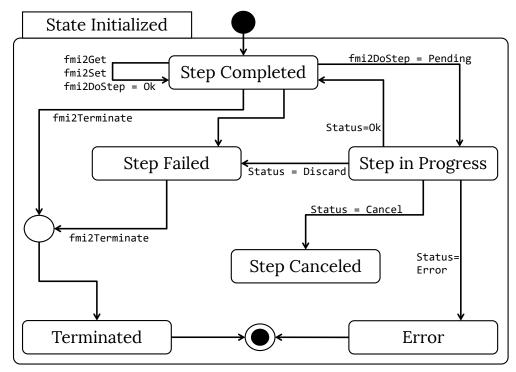

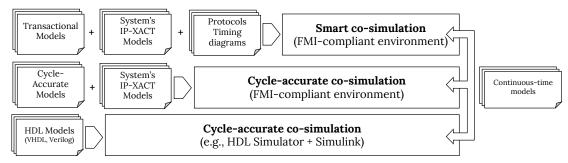

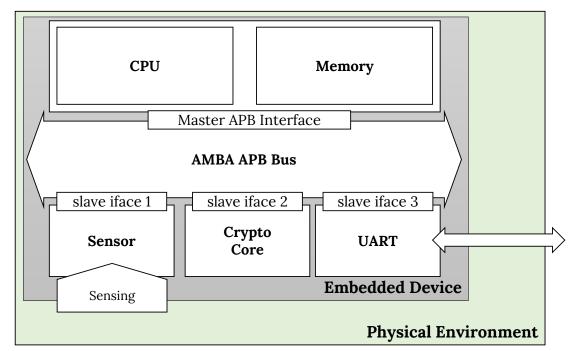

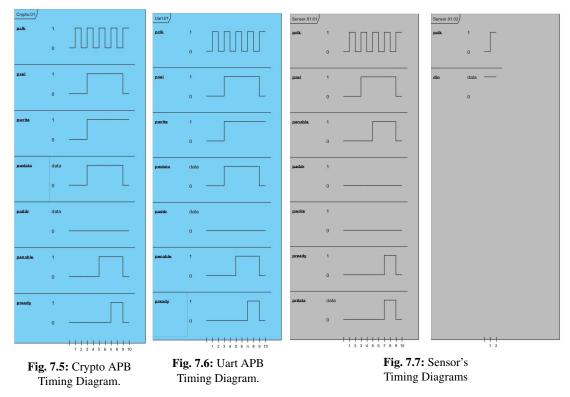

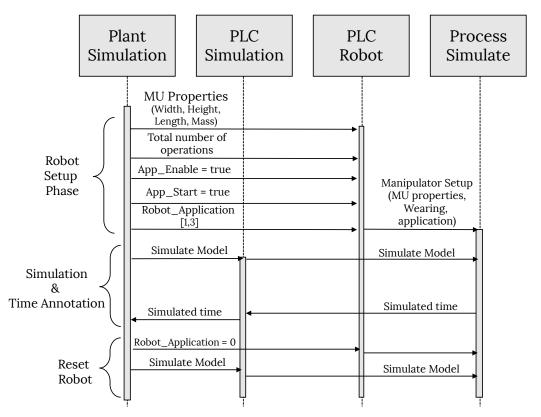

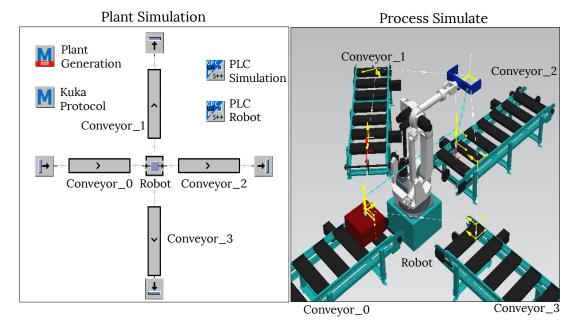

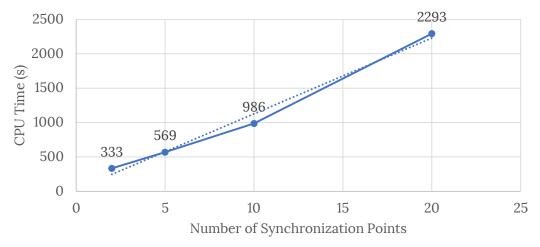

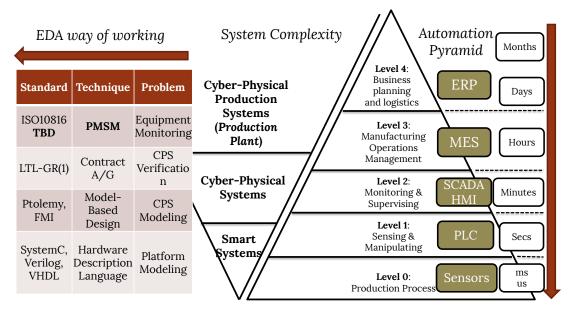

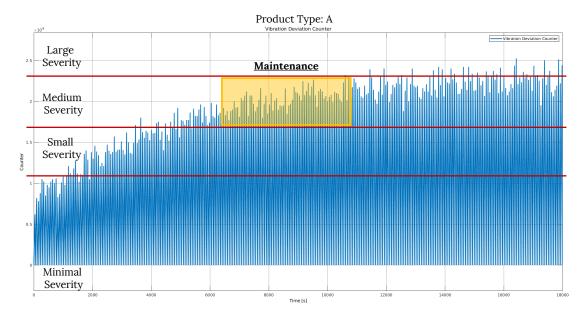

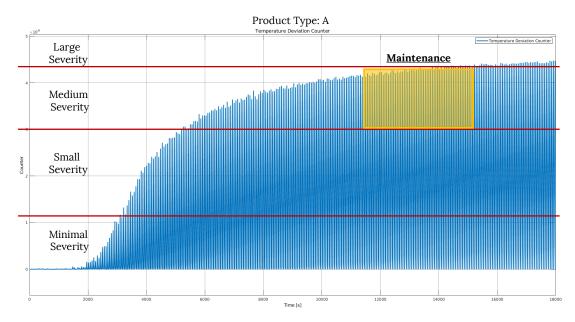

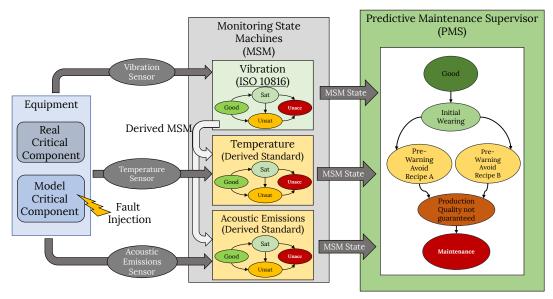

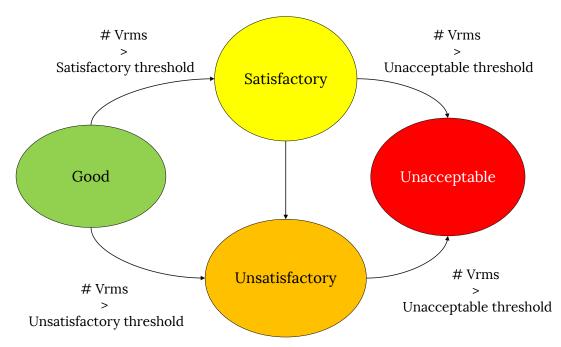

Listing 3.2 sketches the code generated by applying [20] to the guiding example in Listing 3.1. The simulate function (Lines 1-10) performs an input phase to read the values in the io\_exchange structure. Then, execution of synchronous processes is managed by synch\_elaboration function (Lines 12-20). Concurrency is reproduced by combining the flag\_elaboration (Lines 22-29) and update\_event\_queue (Lines 31-53) functions that manages variables replication and the supporting flags.