# Integrated Circuits and Systems for Smart Sensory Applications

Edited by Francesc Serra-Graells, Michele Dei and Kyoungrok Cho Printed Edition of the Special Issue Published in Sensors

www.mdpi.com/journal/sensors

# Integrated Circuits and Systems for Smart Sensory Applications

## Integrated Circuits and Systems for Smart Sensory Applications

Editors

Francesc Serra-Graells Michele Dei Kyoungrok Cho

$\texttt{MDPI} \bullet \texttt{Basel} \bullet \texttt{Beijing} \bullet \texttt{Wuhan} \bullet \texttt{Barcelona} \bullet \texttt{Belgrade} \bullet \texttt{Manchester} \bullet \texttt{Tokyo} \bullet \texttt{Cluj} \bullet \texttt{Tianjin}$

*Editors* Francesc Serra-Graells Department of Microelectronics and Electronic Systems, Universitat Autònoma de Barcelona Spain

Michele Dei Department of Information Engineering, University of Pisa Italy Kyoungrok Cho Department of Information and communication Engineering, Chungbuk National University Korea

*Editorial Office* MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Sensors* (ISSN 1424-8220) (available at: https://www.mdpi.com/journal/sensors/special\_issues/IC\_Smart\_Sensory).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-3264-6 (Hbk) ISBN 978-3-0365-3265-3 (PDF)

© 2022 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Editors                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Integrated Circuits and Systems for Smart Sensory Applications"                                                                                                                                                                                                                                                                                                                     |

| Imran Ali, Muhammad Asif, Muhammad Riaz Ur Rehman, Danial Khan, Huo Yingge, Sung         Jin Kim, YoungGun Pu, Sang-Sun Yoo and Kang-Yoon Lee         A Highly Reliable, 5.8 GHz DSRC Wake-Up Receiver with an Intelligent Digital Controller for         an ETC System         Reprinted from: Sensors 2020, 20, 4012, doi:10.3390/s20144012                                                   |

| Imran Ali, Muhammad Asif, Khuram Shehzad, Muhammad Riaz Ur Rehman, Dong Gyu         Kim, Behnam Samadpoor Rikan, YoungGun Pu, Sang Sun Yoo and Kang-Yoon Lee         A Highly Accurate, Polynomial-Based Digital Temperature Compensation for Piezoresistive         Pressure Sensor in 180 nm CMOS Technology         Reprinted from: Sensors 2020, 20, 5256, doi:10.3390/s20185256         23 |

| Reza Ranjandish and Alexandre Schmid         A Review of Microelectronic Systems and Circuit Techniques for Electrical Neural Recording         Aimed at Closed-Loop Epilepsy Control         Reprinted from: Sensors 2020, 20, 5716, doi:10.3390/s20195716                                                                                                                                     |

| Saad Arslan, Syed Asmat Ali Shah and HyungWon Kim         An Ultra-Wide Load Range Voltage Converter Using Proactive Phase Frequency Modulation         for IoT Sensors         Reprinted from: Sensors 2020, 20, 6279, doi:10.3390/s20216279                                                                                                                                                   |

| Anca Mihaela Vasile (Dragan), Alina Negut, Adrian Tache and Gheorghe Brezeanu         A Digital Improvement—Trimming a Digital Temperature Sensor with EEPROM         Reprogrammable Fuses         Reprinted from: Sensors 2021, 21, 1700, doi:10.3390/s21051700         Khuram Shehzad, Deeksha Verma, Danial Khan, Qurat Ul Ain, Muhammad Basim, Sung                                         |

| Jin Kim, Behnam Samadpoor Rikan, Young Gun Pu, Keum Cheol Hwang, Youngoo Yang<br>and Kang-Yoon Lee<br>A Low-Power 12-Bit 20 MS/s Asynchronously Controlled SAR ADC for WAVE ITS Sensor<br>Based Applications<br>Reprinted from: <i>Sensors</i> <b>2021</b> , <i>21</i> , 2260, doi:10.3390/s21072260                                                                                            |

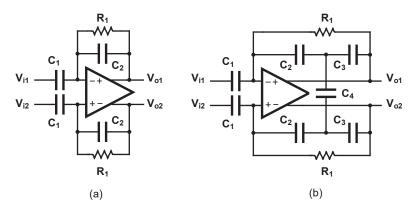

| <b>Beata Trzpil-Jurgielewicz, Władysław Dąbrowski and Paweł Hottowy</b><br>Analysis and Reduction of Nonlinear Distortion in AC-Coupled CMOS Neural Amplifiers with<br>Tunable Cutoff Frequencies<br>Reprinted from: <i>Sensors</i> <b>2021</b> , <i>21</i> , 3116, doi:10.3390/s21093116                                                                                                       |

| Seongwon You, Jason K. Eshraghian, Herbert C. Iu and Kyoungrok Cho<br>Low-Power Wireless Sensor Network Using Fine-Grain Control of Sensor Module Power Mode<br>Reprinted from: <i>Sensors</i> <b>2021</b> , <i>21</i> , 3198, doi:10.3390/s21093198                                                                                                                                            |

| Malik Summair Asghar, Saad Arslan and Hyungwon Kim<br>A Low-Power Spiking Neural Network Chip Based on a Compact LIF Neuron and Binary<br>Exponential Charge Injector Synapse Circuits<br>Reprinted from: <i>Sensors</i> <b>2021</b> , <i>21</i> , 4462, doi:10.3390/s21134462                                                                                                                  |

| Mattia Cicalini, Massimo Piotto, Paolo Bruschi and Michele Dei                               |

|----------------------------------------------------------------------------------------------|

| Design of a Capacitance-to-Digital Converter Based on Iterative Delay-Chain Discharge in 180 |

| nm CMOS Technology                                                                           |

### About the Editors

**Francesc Serra-Graells** received his PhD degree in Electronics Engineering at the Universitat Politècnica de Catalunya, Spain, in 2001. He is currently Associate Professor at the Department of Microelectronics and Electronic Systems of the Universitat Autònoma de Barcelona, Spain. Since 1994, he is also with the Integrated Circuits and Systems group of the Institut de Microelectrònica de Barcelona, Centro Nacional de Microelectrónica, IMB-CNM(CSIC), Spain. His research interests are very low-power, both low-voltage and low-current, design techniques for analog and mixed-signal CMOS circuits, like programmable amplifiers with automatic gain control, phase-locked loops, analog-to-digital and digital-to-analog data converters, oscillators and power managment units, among others. The results of his research activities are application-specific integrated circuits (ASICs) and intellectual-property (IP) cores targeting smart sensing systems, like hearing aids, IR and X-ray imagers, NEMS interfaces, chemical sensors and biosensors, space instrumentation and neural recording systems. He is co-author of more than 60 publications and has participated in more than 30 research and industrial ASIC projects.

Michele Dei received the Laurea degree cum Laude in Electronic Engineering and the Ph.D degree in Information Engineering at the University of Pisa (Italy) in 2007 and 2010, respectively, working on the design of smart sensors for detection of physical quantities. He is currently working at the Information Engineering Department of the University of Pisa (Italy), through of a Marie Skłodowska-Curie Individual Fellowship contract (H2020-MSCA-IF-2019/893544) as Principal Investigator of the SWeaT project regarding wearable electro-chemical instrumentation. Previously he worked within the IMB-CNM (Barcelona, Spain) and with the School of Information and Communication Technology at KTH (Stockholm, Sweden). His engineering background involves low-power analog-mixed signal integrated circuit for sensor interfacing, data converters in the context of a number of high-impact research and industrial projects.

**Kyoungrok Cho** received a B.S. degree in Electronic Engineering from Kyoungpook National University, Taegu, Korea, in 1977, and an M.S. and Ph.D. degree in Electrical Engineering from the University of Tokyo, Japan, in 1989 and 1992, respectively. From 1979 to 1986, he was with TV research center of LG Electronics in Korea. He is currently a Distinguished Professor at the College of Electrical and Computer Eng. of Chungbuk National University, Korea. His research interests are in the field of high-speed and low-power circuit design, SoC and platform design for the communication system, and prospective IOT sensor networks. He has been a director of a regional center of IDEC(IC Design Education Center) in Korea covering Chungcheong provinces and Taejon city from January 2004. In 1999 and again in 2006, he spent a year at Oregon State University, USA, as a visiting scholar.

## Preface to "Integrated Circuits and Systems for Smart Sensory Applications"

Connected intelligent sensing reshapes our society by empowering people with increasing new forms of mutual interactions. As integration technologies keep their scaling roadmap, the horizon of sensory applications is rapidly widening, thanks to myriad light-weight low-power or, in some cases, even self-powered smart devices with high-connectivity capabilities. CMOS integrated circuits technology is the best candidate to supply the required intelligence and to pioneer these emerging sensory systems. As a result, new challenges are arising around the design of these integrated circuits and systems for sensory applications in terms of low-power edge computing, power management strategies, low-range wireless communications, and integration with sensing devices. In this Special Issue, recent advances in application-specific integrated circuits (ASIC) and systems for smart sensory applications are presented via the following five emerging topics:

- I. Dedicated short-range communications transceivers for radio communications in intelligent transportation systems [1,6];

- II. Digital smart sensors featuring digital compensations [2], re-programmable fuse trimming [5] and all-digital implementation for ultra-low power operation [10];

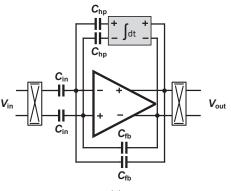

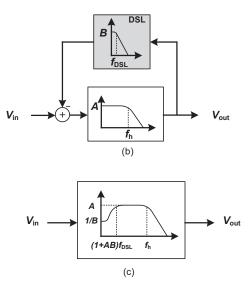

- III. Implantable neural interfaces, including a review on closed-loop implantable electronics for epilepsy control [3] and an AC-coupled neural amplifier design with improved linearity [7];

- IV. Power Management Strategies in wireless sensor nodes, both from the hardware [4] and the software [8] perspectives;

- V. Neuromorphic hardware systems for image recognition [9].

Dedicated short-range communications (DSRC) services designate one-way or two-way wireless communication for automotive use involving vehicle-to-vehicle and vehicle-to-infrastructure communications. In 2020, The United States Federal Communications Commission (FCC) allocated the 5.895-5.925 GHz band for Intelligent Transportation System (ITS) services. Equipment in the DSRC Service comprises On-Board Units (OBUs) and Roadside Units (RSUs). An OBU is a transceiver (which is normally battery operated) fitted inside the vehicle. In such scenarios, a high-speed reliable radio link need to be established under power-constrained requirements. Ali et al. [1] presents a new wake-up receiver (WuRx) to support he main RF receiver of the OBU by providing wake-up detection to exit the OBU hibernation state. The proposed ASIC features an intelligent digital controller (IDC) for improving WuRx reliability and for replacing complex and power-hungry analog blocks such as band-pass filters and frequency detectors. The IDC implements a number of smart power-management techniques such as: (i) self-hibernation of the IDC and range communication (RC) oscillator; (ii) digital hysteresis for accommodating wake-up signal frequency variation and enhancing WuRx accuracy; (iii) a watch-dog timer for IDC self-recovery to avoid uncertain conditions during poor and false wake-up; (iv) configurable wake-up signal cycles before enabling a power-hungry RF transceiver. The IDC prototype in 130 nm CMOS technology occupies a modest silicon area (94  $\times$  82  $\mu$ m<sup>2</sup>). The resulting WuRx shows comparable sensitivity (-46 dBm) with the state-of-the-art, while outperforming it in terms of power consumption (2.48  $\mu$ W), thus demonstrating the effectiveness of the proposed IDC. DSRC transceivers also comprise analog-todigital converters

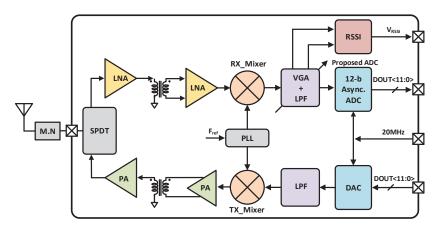

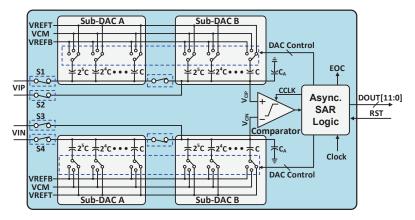

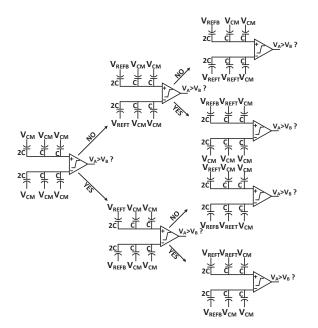

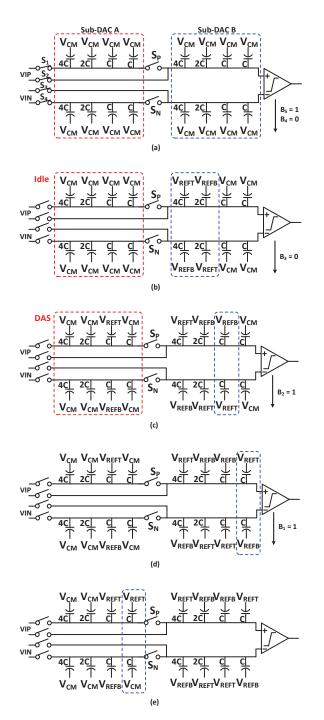

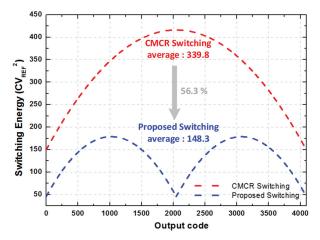

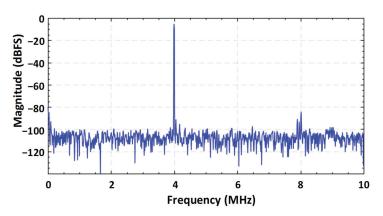

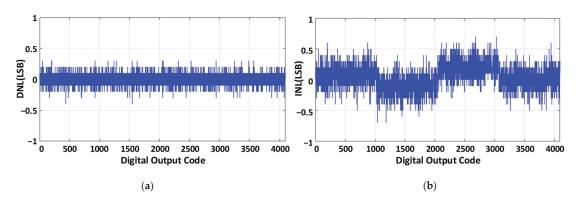

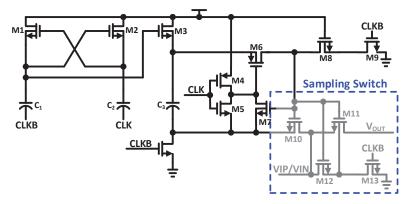

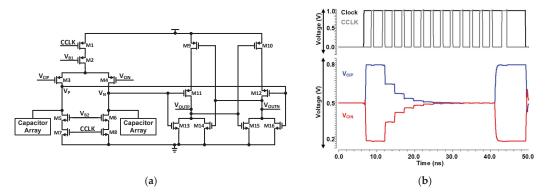

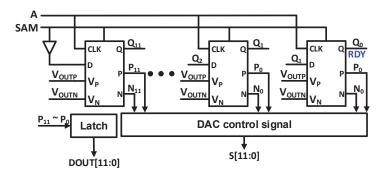

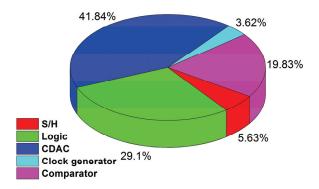

(ADC) to allow the transceiver to communicate with the digital base-band electronics, with speed and resolution requirements of few tens of MS/s and 10 bits, respectively. To meet these requirements, Shehzad at al. [6] proposed a 12 bit 20 MS/s successive approximation register (SAR) ADC fabricated in 65 nm CMOS with an active area of 0.14 mm<sup>2</sup>, performing a SNDR of 65.44 dB while consuming only 472.2  $\mu$ W with 1 V power supply. Low-power operation has been achieved employing various circuital techniques such as specific capacitor-switching strategy, asynchronous control logic, and custom modification of the dynamic-latch comparator.

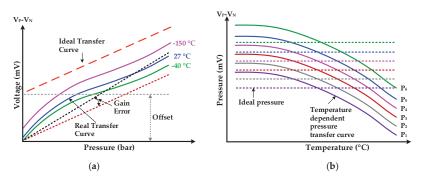

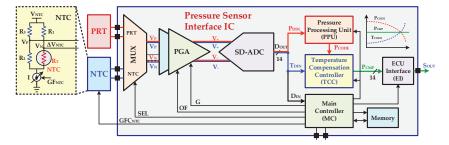

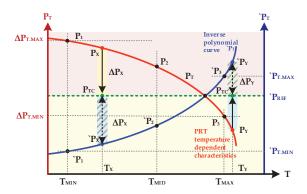

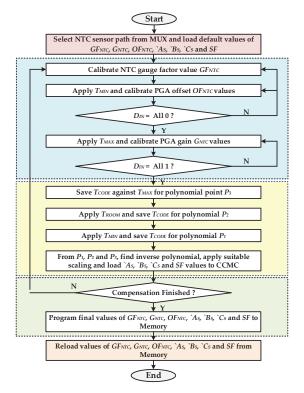

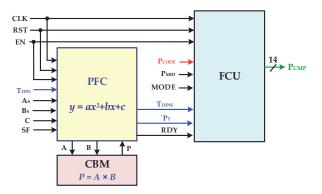

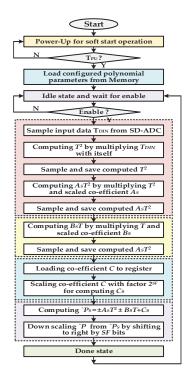

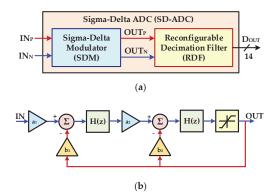

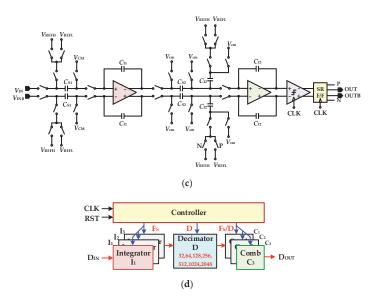

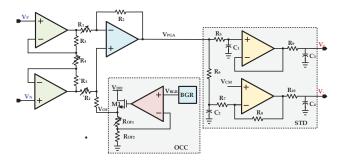

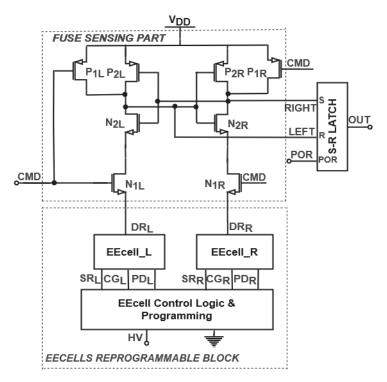

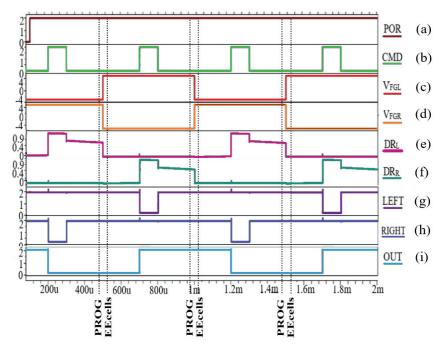

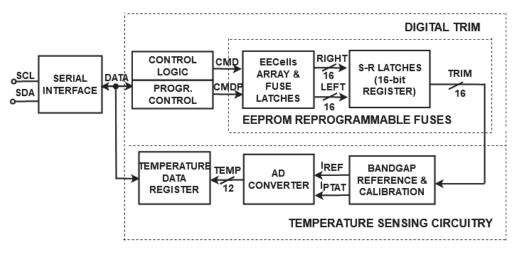

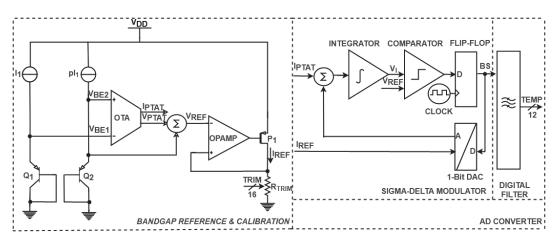

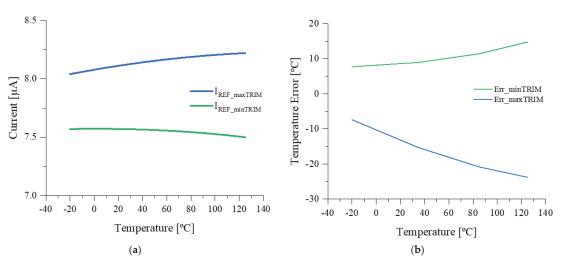

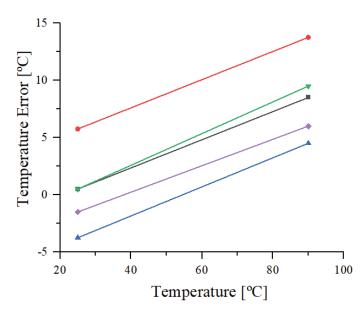

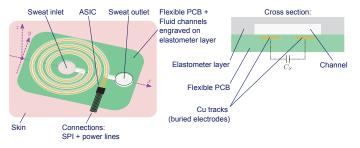

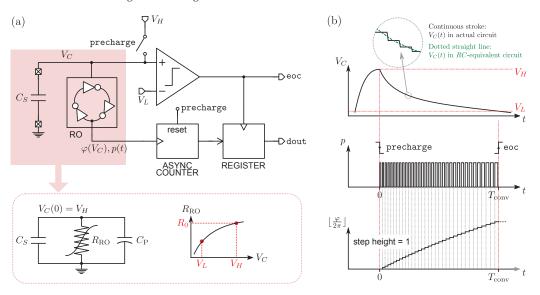

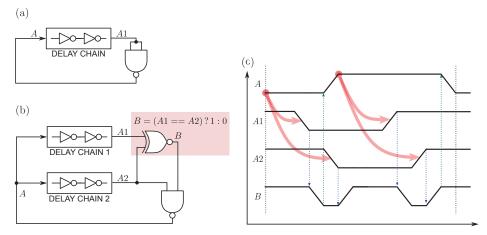

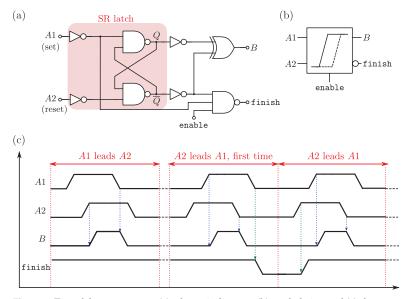

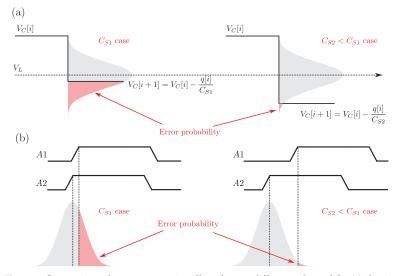

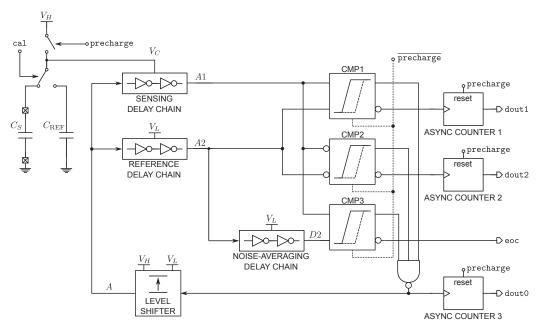

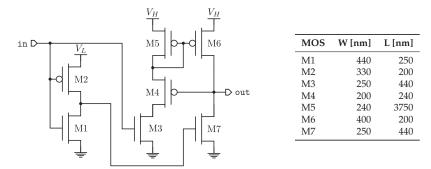

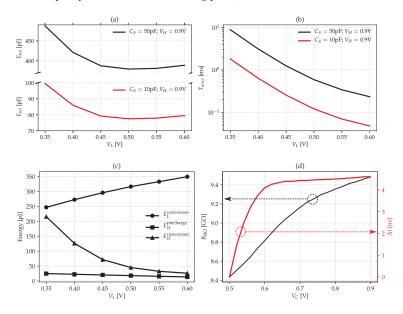

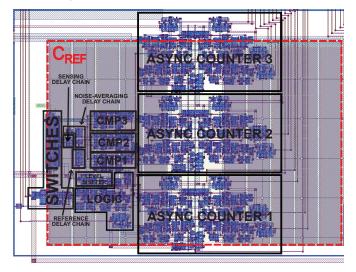

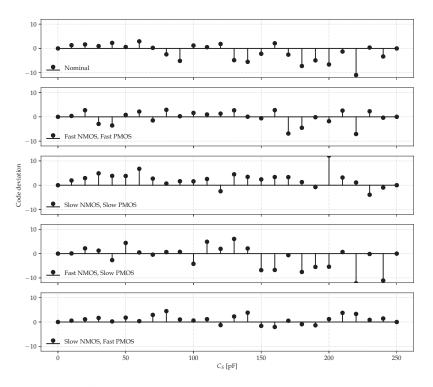

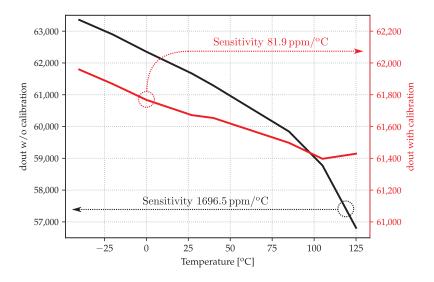

Digital smart sensors are at the heart of IoT development, ranging from consumer gadgets, sensor networks, and image sensors to biomedical instruments, thanks to their digital-ready output and their added functionalities over classical analog-domain transducers, with almost zero impact on the device cost. Such added functionalities comprise sensor compensation, trimming and/or full-digital CMOS implementation for rapid IP embedding on complex system on chips (SoC). Ali et al. [2] propose polynomial-based adaptive digital temperature compensation for piezoresistive-type (PRT) pressure sensors. Such sensors have gained attention in a variety of applications due to their simplicity, low cost, miniature size, and ruggedness; however, their electrical behavior is temperature dependent and highly nonlinear. To avoid severe impairment of measurement accuracy, the authors propose an ASIC fabricated in 180 nm CMOS technology, delivering compensation accuracy within  $\pm 0.068\%$  of full scale when temperature varies from -40 to  $\pm 150$  °C. On the other hand, low-cost and low-power temperature sensors, often targeting challenging requirements in terms of accuracy, precision, and linearity, are ubiquitously demanded. When cost per unit is considered, higher accuracy for a thermal sensor is based on a trade-off between the production costs for calibration and the required precision. Vasile et al. [5] show a trimmed digital sensor with a +1.5/-1.0 °C inaccuracy in the temperature range of -20 to +125 °C using a 180-nm CMOS EEPROM process by one-point calibration. Finally, Cicalini et al [10] show the implementation of an innovative, all-digital 180 nm CMOS capacitive-to-digital converter adequate for medium-low resolution body sweat-flow rate in wearable applications. They demonstrate the operation of 10.3 effective-number-of-bits resolution readout interface at 0.9 V-supply for a 0–250 pF input capacitance featuring  $\geq$  1.884 nJ/conversion, excellent linearity and robustness against process/temperature corners, while using only 0.0192 mm<sup>2</sup> of silicon area.

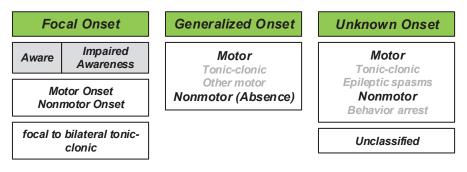

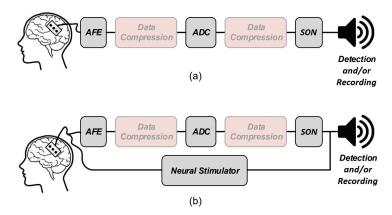

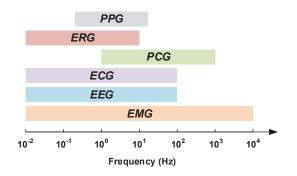

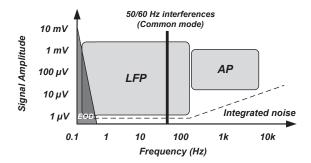

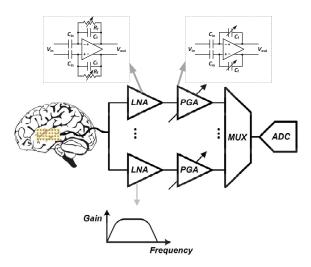

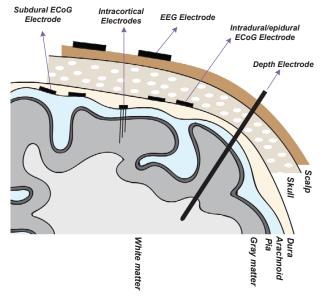

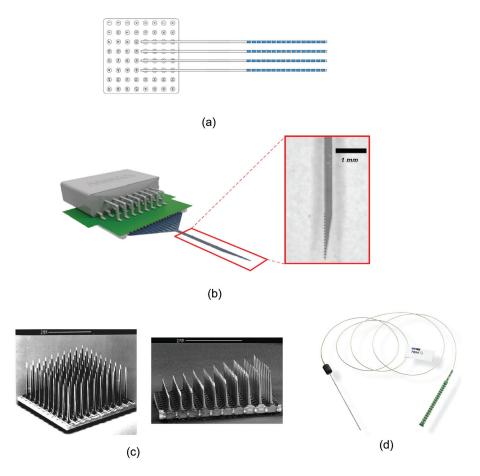

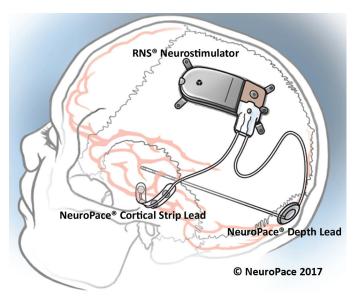

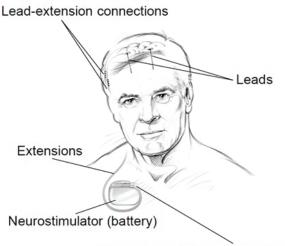

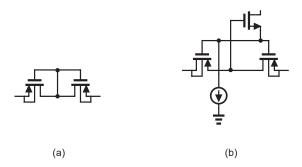

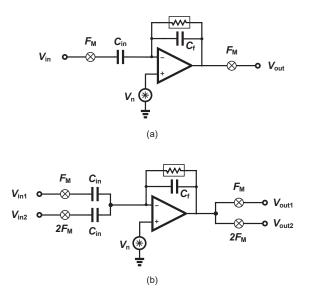

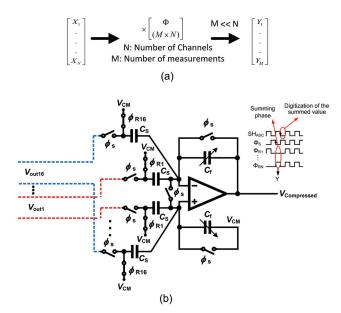

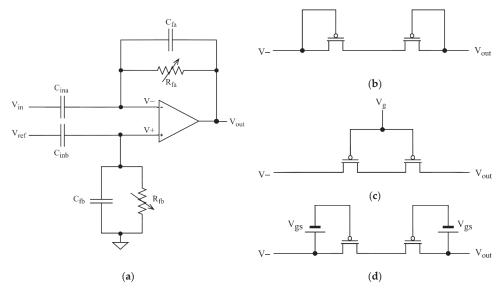

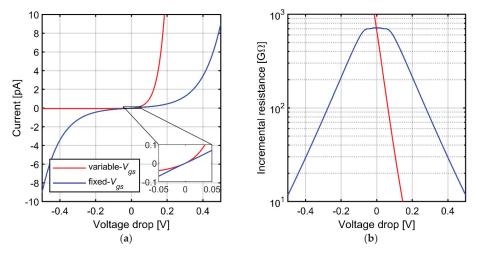

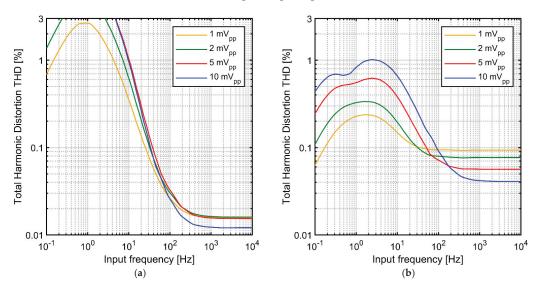

**Implantable neural interfaces** concern multi-electrode systems routinely designed as Application Specific Integrated Circuits (ASIC), which comprise hundreds or thousands of recording amplifiers on a single chip. To this aim, the signal recording chain must be very carefully designed so as to operate in low power and low latency, while enhancing the probability of correct event detection. High-fidelity recording of neuronal signals, comprising the action potentials (AP) range (300 Hz–10 kHz) and the local field potential (LFP) (1–300 Hz) range, requires strict noise (>10  $\mu$ VRMS) and a total harmonic distortion (THD) (>2%) specifications, when dealing with signals up to 10 mVpp. Minimization of the dissipated power and silicon area is also critical for the design of neuronal interfaces with a very large number of recording channels. The large DC voltage at the input of the amplifier results from electrochemical interactions between the electrode and the tissue. The recording circuit must cut off this DC electrode voltage with high-pass filter (i.e., AC coupling) with a lower cutoff frequency, typically in the order of 1 Hz, and amplify the remaining AC signals with a gain in the order of 40 dB. Ranjandish and Schmid [3] report the latest advances in closed-loop implantable electronics for epilepsy control, focusing on both implantable and external commercial systems and pointing out the following research challenges: (i) size and weight; (ii)

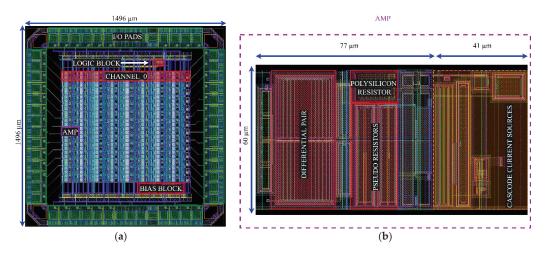

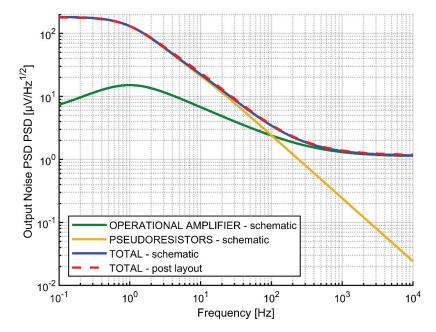

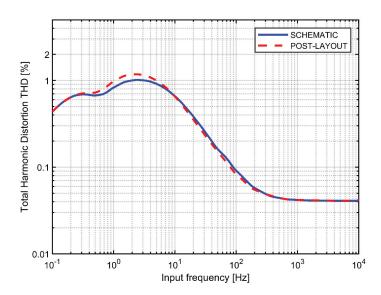

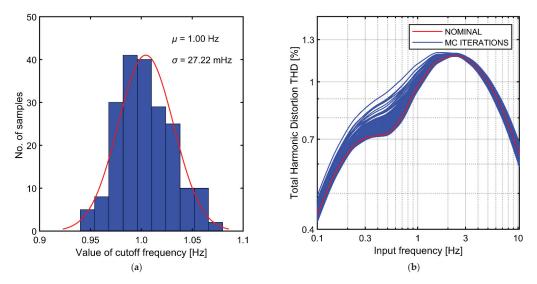

power consumption and temperature elevation; (iii) battery powering and rechargeability; (iv) the biocompatibility of the package and enclosure; (v) data compression and storage. Trzpil-Jurgielewicz [7] propose a linearity-enhancing circuital technique for AC-coupled neural amplifiers to remove the electrode DC voltage. A prototype preamplifier fabricated in 180 nm CMOS technology shows THD values are below 1.17% for signal frequencies 1 Hz–10 kHz and signal amplitudes up to 10 mV peak to peak. While using only 0.0046 mm<sup>2</sup> of silicon area, the prototype has an input-referred noise of 8.3  $\mu$ VRMS in the 1 Hz–10 kHz range, while consuming 7.2  $\mu$ W per channel.

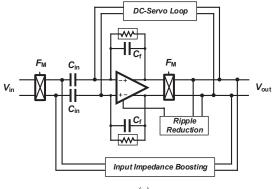

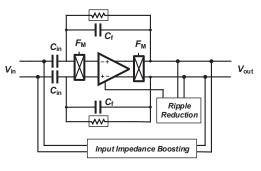

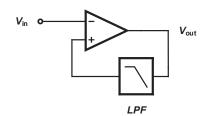

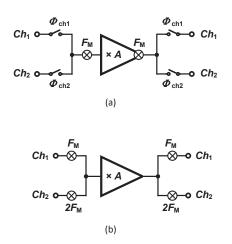

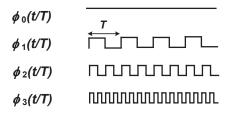

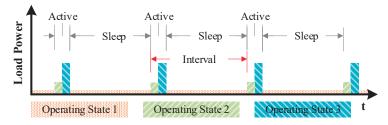

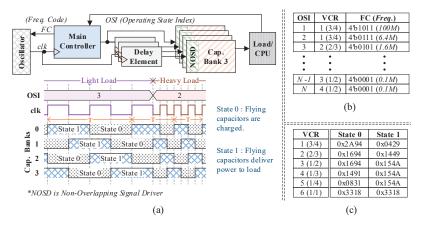

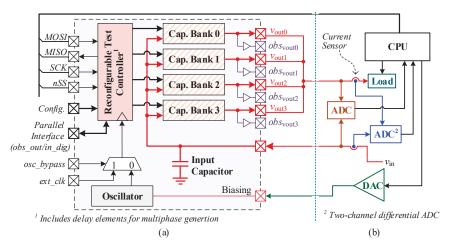

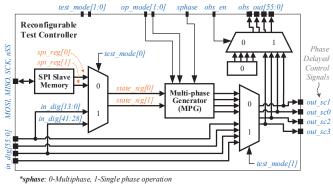

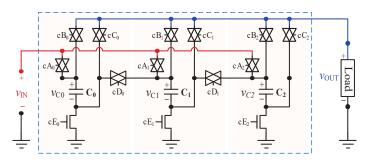

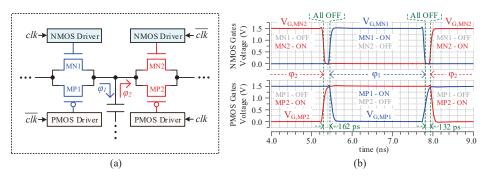

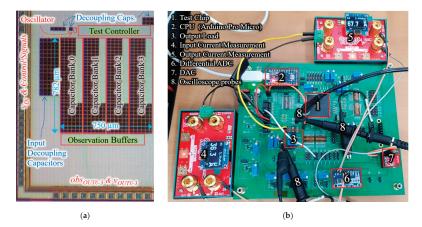

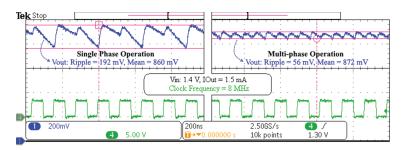

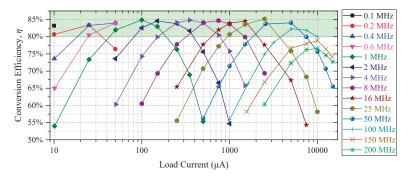

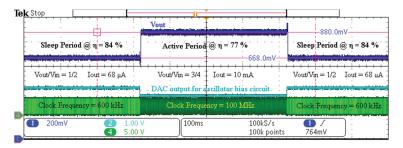

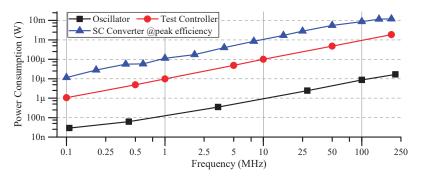

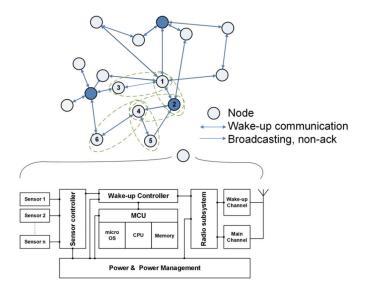

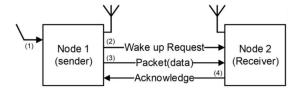

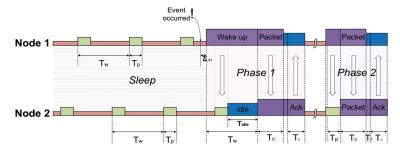

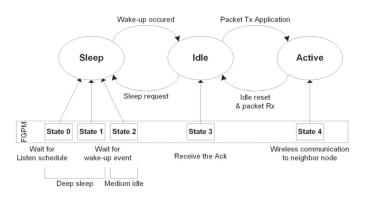

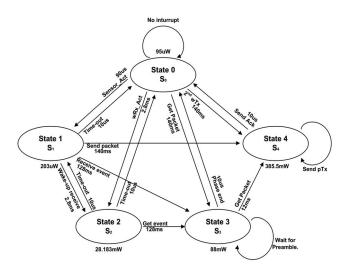

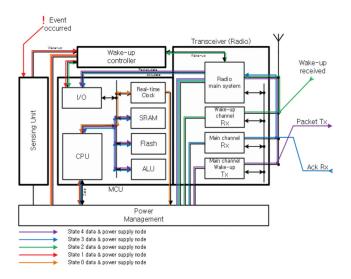

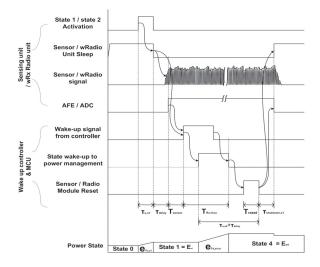

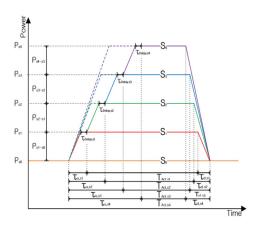

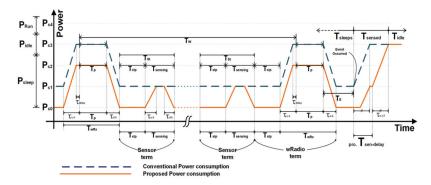

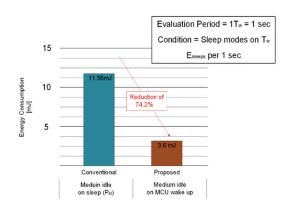

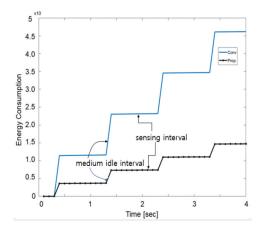

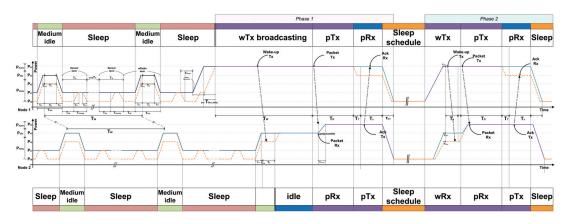

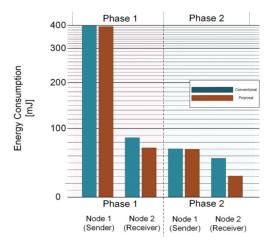

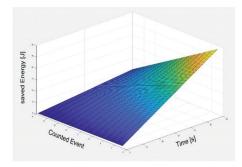

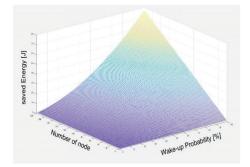

Power Management Strategies in wireless sensor nodes (WSN) involves both hardware and software techniques. Smart sensor nodes perform a set of tasks, often corresponding to different load states. The predictable transition schedule allows the software to proactively reconfigure the voltage converter to supply required amount of current for various load conditions. Under varying load conditions, however, a large Switched Capacitor (SC) converter often provides poor efficiency at smaller loads. An output voltage ripple is often alleviated by having a large output capacitor and/or high switching frequency, which represents another challenge faced by modern SC converters. Arslan et al. [4] propose a voltage converter whose switching frequency and output voltage are proactively adjusted to maintain high conversion efficiency based on the schedules of load current demanded by the target load. Multiphase operation is also implemented to provide low-output ripple. The ASIC prototype, fabricated in 130 nm CMOS technology, supports a load current range between 10 µA and 10 mA for switching frequencies ranging from 100 kHz to 200 MHz, while providing an efficiency of above 80%. The area of the converter is 0.59 mm<sup>2</sup>, operating a 1.5-V supply; it delivers a tunable output voltage between 0.4 and 1.1 V with maximum ripple of 56 mV. Apart from transistor-level power optimization, software control over the operating states of WSN is important for overall power saving of the battery-constrained system. You et al. [8] proposes a novel power management method (PMM) that leads to less energy consumption in an idle state than conventional PMMs. While conventional PMMs rely on operation between Sleep, Idle, and Run modes, the proposed approach splits the Sleep mode into three different modes: Deep-Sleep and Semi-Idle Sensor and Semi-Idle WuRx. The proposed PMM strategy has been tested on a gas-sensing WSN using the commercial Mica2 platform and compared to conventional PMM. The proposed approach offers power savings between 2 and 74.2% depending on event rate, thus demonstrating its effectiveness in low-event-probability WSNs.

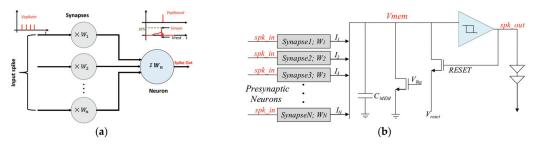

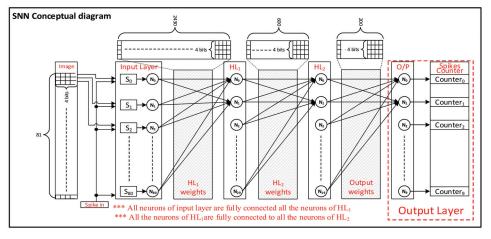

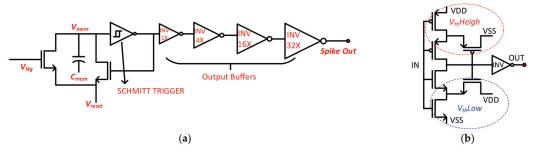

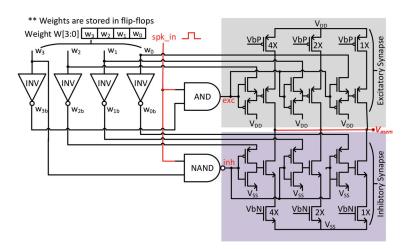

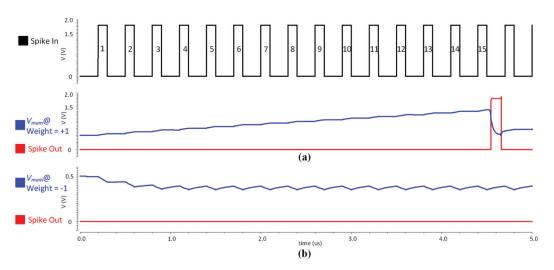

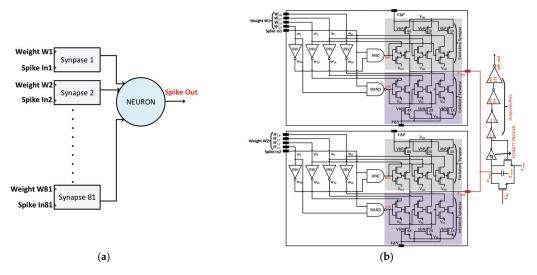

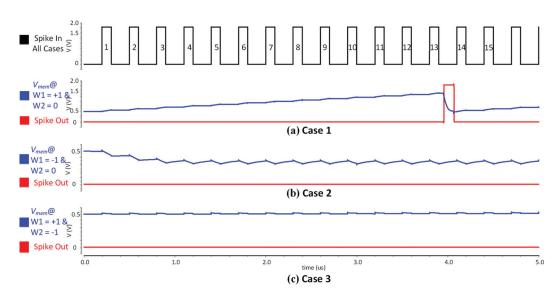

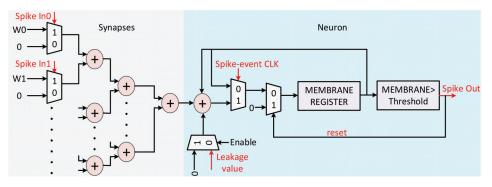

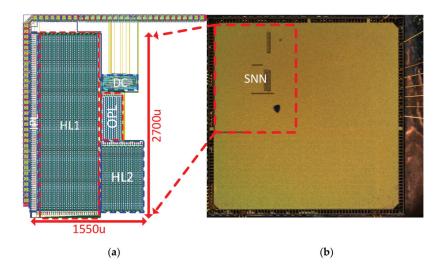

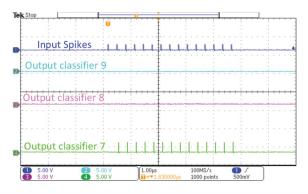

Neuromorphic hardware systems differ from classical von Neumann processor architectures since they are naturally configured for parallel information processing. Mimicking the vastly and densely connected neurons of the human brain, neuromorphic architectures encode information in sequences of action potentials called spike trains, theoretically promising a breakthrough in energy efficiency for signal processing. In this sense, specific and power-optimized hardware implementation of such neural networks is a hot topic in this research area. Asghar et al. [9] present an CMOS implementation of a Spiking Neural Network (SNN) for real-time 9 × 9 pixel input image for pattern recognition. Fabricated using 180 nm CMOS process, the proposed chip achieves a classification accuracy of 94.66% for the MNIST dataset while occupying 3.6 mm<sup>2</sup> chip core area and presenting an average power consumption of 1.06 mW.

#### Francesc Serra-Graells, Michele Dei, Kyoungrok Cho Editors

## A Highly Reliable, 5.8 GHz DSRC Wake-Up Receiver with an Intelligent Digital Controller for an ETC System

#### Imran Ali, Muhammad Asif, Muhammad Riaz Ur Rehman, Danial Khan, Huo Yingge, Sung Jin Kim, YoungGun Pu, Sang-Sun Yoo and Kang-Yoon Lee \*

College of Information and Communication Engineering, Sungkyunkwan University (SKKU), Suwon 16419, Korea; imran.ali@skku.edu (I.A.); m.asif@skku.edu (M.A.); riaz@skku.edu (M.R.U.R.); danialkhan@skku.edu (D.K.); yingge@skku.edu (H.Y.); sun107ksj@skku.edu (S.J.K.); hara1015@skku.edu (Y.P.); rapter@kaist.ac.kr (S.-S.Y.)

\* Correspondence: klee@skku.edu; Tel.: +82-31-299-4954

Received: 18 June 2020; Accepted: 17 July 2020; Published: 19 July 2020

**Abstract:** In this article, a highly reliable radio frequency (RF) wake-up receiver (WuRx) is presented for electronic toll collection (ETC) applications. An intelligent digital controller (IDC) is proposed as the final stage for improving WuRx reliability and replacing complex analog blocks. With IDC, high reliability and accuracy are achieved by sensing and ensuring the successive, configurable number of wake-up signal cycles before enabling power-hungry RF transceiver. The IDC and range communication (RC) oscillator current consumption is reduced by a presented self-hibernation technique during the non-wake-up period. For accommodating wake-up signal frequency variation and enhancing WuRx accuracy, a digital hysteresis is incorporated. To avoid uncertain conditions during poor and false wake-up, a watch-dog timer for IDC self-recovery is integrated. During wake-up, the digital controller consumes 34.62 nW power and draws 38.47 nA current from a 0.9 V supply. In self-hibernation mode, its current reduces to 9.7 nA. It is fully synthesizable and needs 809 gates for its implementation in a 130 nm CMOS process with a 94 × 82  $\mu$ m<sup>2</sup> area. The WuRx measured power consumption is 2.48  $\mu$ W, has –46 dBm sensitivity, and a 0.484 mm<sup>2</sup> chip area.

**Keywords:** wake-up receiver; digital controller; reliability; electronic toll collection (ETC) system; dedicated short range communication (DSRC)

#### 1. Introduction

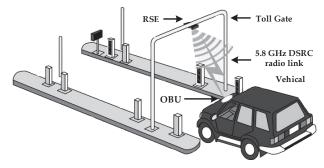

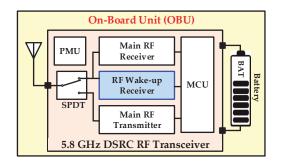

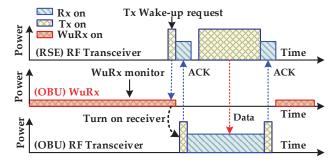

Recently, the radio frequency (RF) wake-up receiver has become an attractive research area for battery-operated transceivers in a variety of applications such as electronic toll collection (ETC) systems, wireless sensor networks (WSNs), wireless body area networks (WBANs), internet-of-things (IoTs), and wearable devices [1–4]. Nowadays, the ETC system (ETCS) is rapidly being adopted as an intelligent transportation solution in automotive vehicles. It uses a 5.8-GHz dedicated short range communication (DSRC) for a high speed radio link between a road side equipment (RSE) fixed at the toll gate and on-board unit (OBU) fitted inside the vehicle [1,5–7], as shown in Figure 1. Without stopping the vehicles, the toll is paid automatically and it saves time and eliminates traffic congestion on the roads. In ETCS, a wake-up receiver (WuRx) is an auxiliary RF receiver, additionally to the main RF transceiver, as shown in Figure 2, and is mandated due to the battery powered OBU. The WuRx is a pure asynchronous communication but also diminishes network latency. Figure 3 shows the asynchronous communication between RSE and OBU with WuRx. The reliability, false wake-up, power dissipation, and sensitivity are key considerations in WuRx design. In WuRx, designed with low power dissipation

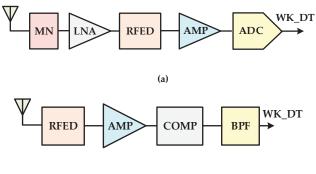

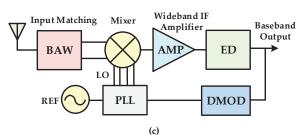

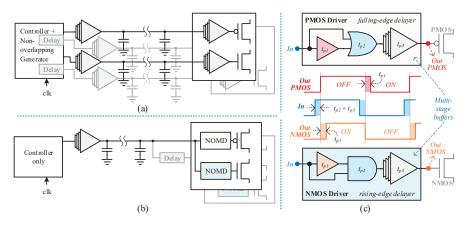

and good sensitivity, false and poor wake-up turns on main transmitter and receiver modules, which reduces battery life and degrades the overall WuRx performance. The numerous WuRx circuits have been investigated in literature to optimize power consumption, maximize sensitivity, and improve reliability [8–11]. The various WuRx architectures are summarized in Figure 4. Based on the type of the power source, the WuRx is categorized in active and passive wake-up circuits. The active WuRx circuits are powered from a battery fitted on an OBU to monitor a possible wake-up signal. The energy for the wake-up circuit is harvested from the incident RF signal in passive receivers. Mostly, the active circuits adopt either RF envelope detector (RFED) structures [1,12,13], shown in Figure 4a,b, or frequency conversion architectures [14,15], depicted in Figure 4c. The frequency conversion based wake-up receivers offer higher sensitivity due to RF amplification before RF envelope detection [16], or local oscillator (LO) generation for down-conversion before amplification and envelope detection at intermediate frequency (IF) [14]. These circuits dissipate more power and occupy a larger area due to a power hungry phase-locked loop (PLL) and automatic channel scanning circuits for two channel receptions [15]. The majority of wake-up circuits are implemented with RFED because of its low power consumption using Schottky diodes [12,13] or metal-oxide-semiconductor field-effect transistor (MOSFET) operating in the weak-inversion region. The WuRx structure shown in Figure 4a uses an analog to digital converter (ADC) after a programmable gain amplifier (PGA) which occupies more area and increases power consumption. The WuRx shown in Figure 4b uses an analog band pass filter (BPF) at the output interface which requires more chip area. Figure 4c shows an envelope detector based WuRx structure with a front end amplifier and bulk acoustic wave (BAV) input network [17,18]. The WuRx in [19] also incorporates ADC at the output; however, in order to achieve better sensitivity and to reduce receiver noise, it incorporates a low noise amplifier (LNA) before an envelope detector and uses a double sampling technique. It offers better sensitivity at the cost of increased power consumption and larger chip area for WuRx. The passive WuRx structure [20] incorporates radio frequency to direct current (RF-DC) converter for harvesting energy from incident RF signals as shown in Figure 4d. For this purpose, an RF-DC converter [21,22] is employed to produce the envelope of the on-off keying (OOK) wake-up message signal, and at the same time, it efficiently converts the RF carrier to a DC voltage in order to supply the comparator and the other WuRx circuits. Although this architecture is power efficient, it exhibits low sensitivity. Furthermore, the deficiency of false and poor wake-up filtering is vulnerable.

**Figure 1.** The dedicated short range communication (DSRC) system overview with road side equipment (RSE) fitted at toll gate, battery operated on-board unit (OBU) fixed inside the vehicle, and a 5.8 GHz DSRC radio link as communication channel.

Figure 2. The DSRC OBU system level block diagram.

Figure 3. The road side equipment (RSE) and OBU pure asynchronous communication with the RF wake-up receiver (WuRx).

(b)

Figure 4. Cont.

**Figure 4.** The previous wake-up receiver architecture: (**a**) RF envelope detector (RFED) based with analog to digital converter (ADC); (**b**) RFED based with band pass filter (BPF); (**c**) frequency conversion with LO; (**d**) passive circuit with RF-DC.

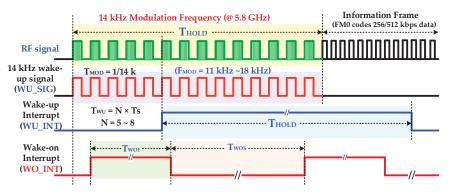

The wake-up signal is categorized as a single wake-up tone of a bit sequence [23]. The bit sequence signal, also called identity-based wake-up, is widely used in WSN and WBAN for addressing a particular destination sensor node for unicasting. For broadcasting, single wake-up tone is adopted [23]. The DSRC wake-up signal is a 14 kHz OOK single tone signal of 15–17 cycles which is modulated with a 5.8 GHz carrier frequency [9].

The precise sensitivity control is essential for ETCS wake-up circuits [1]. Neither a very low nor very high sensitivity is intended. The available communication time will be insufficient when WuRx sensitivity is lower than a minimum level. Similarly, if WuRx has very high sensitivity, it will turn on OBU and start communication even if vehicle is far away from a RSE and toll area. Moreover, very high sensitivity will result in communication failure and interrupts other OBU devices on the road. Therefore, WuRx sensitivity must be in a range, robust, insensitive to process, voltage, and temperature (PVT) variations [11].

The key characteristic of WuRx is to detect and ensure the presence of wake-up request in the received RF signal and decide whether to turn on the power hungry transceiver on OBU. In most previous studies, the WuRx circuits only identify the signal amplitude which is inadequate in ETC systems. If false and poor wake-up signals are not identified and filtered out in the WuRx circuit, these signals turn on power hungry main RF transceiver modules and the battery performance is degraded. In the past, numerous WuRx architectures have been investigated for improving the sensitivity and reducing the power consumption. However, false and poor wake-up problems have been left unaddressed. This paper presents a RFED based highly reliable WuRx. An intelligent digital controller (IDC) is proposed to ensure the WuRx reliability and accuracy by identifying and rejecting unwanted, false, and poor wake-up signals. It also replaces complex blocks such as ADC and BPF after amplifier and comparator [8–10,24] and reduces current consumption and area. Due to its digital nature, it is fully synthesizable, immune to noise and PVT variations [25], offers system flexibility, a wide dynamic range for wake-up and oscillator frequencies, and is adaptive to technology scaling.

The rest of the paper is organized as follows: Section 2 presents a proposed WuRx architecture overview. The detailed design of the proposed digital controller is described in Section 3. The tunable range communication (RC) oscillator is presented in Section 4. The RF front end and baseband analog processing is included in Section 5. Section 6 describes the experimental results. Lastly, the paper is concluded in Section 7.

#### 2. Proposed Wake-Up Receiver Architecture

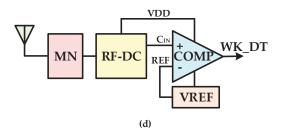

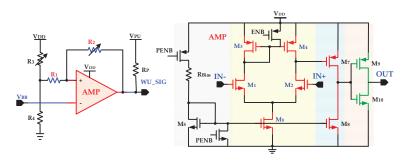

Figure 5 shows the proposed 5.8-GHz RF WuRx in which IDC is integrated to ensure its reliability and accuracy. An antenna receives the incoming RF signal and sends it to an off-chip pi-matching network. The matching network is an essential passive circuit to transfer the maximum RF signal power to the receiver circuit. The pi-matching network matches the antenna equivalent impedance with the input impedance of the proposed WuRx and ensures the maximum power transfer from the antenna to the WuRx circuit. Unlike [8,24], the chip internal matching network in addition to off-chip pi-matching receives a RF wake-up signal, boosts voltage, and improves sensitivity and  $|S_{11}|$ . The high gain RF envelope detector recovers the baseband wake-up signal and improves signal-to-noise ratio (SNR) without additional current consumption. The RFED is a critical circuit and it interfaces WuRx with the antenna, down-converts the amplitude of the modulated RF 5.8 GHz signal, and generates a 14 kHz baseband wake-up signal. The PGA provides flexibility to improve gain and amplify the baseband signal significantly. The main control unit (MCU) enables/disables and configures different programmable parameters of RFED, baseband analog (BBA), comparator (COMP), and IDC. It can either be an on/off chip modem, externally controllable registers, or an external microcontroller. The comparator (COMP) generates digital output for IDC processing. An ultra-low power range communication (RC) oscillator (OSC) with a dynamic tuning range generates a configurable clock for the IDC block. The digital controller is proposed for ensuring WuRx reliability and accuracy by identifying and filtering non-wake-up signals. It is a fully synthesizable block, consumes very low power, and needs a very small chip area. The digital controller also replaces complex power consuming and large area interface blocks, such as ADC, BPF.

Figure 5. Proposed RF wake-up receiver architecture.

#### 3. Multi-Mode, Configurable Intelligent Digital Controller (IDC)

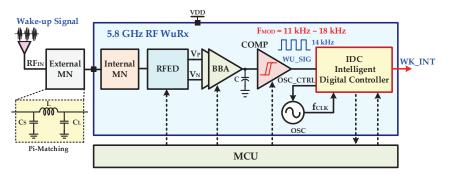

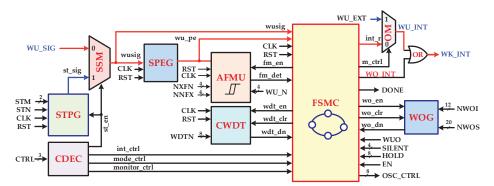

In the DSRC WuRx design, other than high sensitivity and low power consumption, the false and poor wake-up signals identification is very crucial in order to extend OBU battery lifetime. This is achieved by filtering non-wake-up and noise signals and prohibiting turning on main power hungry RF transceiver. For this purpose, a novel, multi-mode, and configurable intelligent digital controller is proposed for ensuring WuRx reliability and accuracy. This controller is also a low power, small area digital replacement of complex, high power analog blocks such as ADC and a band pass filter. Different parameters of wake-up, self-hibernation, digital hysteresis, wake-on, watch-dog timer, and self-test are fully configurable, which make the controller architecture very flexible and adaptive. The simplified architecture of a WuRx digital controller is illustrated in Figure 6 and the timing diagram is elaborated in Figure 7 for DSRC applications. The signal selection multiplexer (SSM) selects either a baseband wake-up signal, WU\_SIG, from the comparator output in normal operation or self-test signal *st\_sig*, generated from self-test pattern generator (STPG) during test mode. The signal positive edge generator (SPEG) detects rising transitions in the final selected signal wusig and generates a pulse signal *wu\_pe*. The finite state machine controller (FSMC) is the key building block of IDC which is designed as control unit and data path. It mainly senses, ensures, and generates the wake-up interrupt and filters unwanted signals. It controls other blocks such as the adaptive frequency measurement unit (AFMU), configurable watch-dog timer (CWDT), and wake-on generator (WOG). When enabled by FSMC ( $fm_en = 1$ ), the AFMU measures the frequency of the wake-up signal and determines by generating signal *fm\_det* if the input signal value is either within the configured range or not. It also ensures the valid successive number of configured (WU\_N) wake-up signal cycles. The CWDT, when enabled by signal *wdt\_en* from FSMC, starts a timer. The timer duration is configurable from the

*WDTN* parameter. It enhances IDC reliability and helps to avoid any halt situation during frequency measuring and signal ensuring states. If there is any abnormal situation, CWDT resets FSMC to its initial state when the configured timer expires. The WOG implements a pseudo-synchronous interrupt generation. When it is enabled, the wake-on interrupt WO\_INT is generated instead of the wake-up interrupt. The STPG enhances WuRx reliability by verifying IDC operation in self-test mode. When enabled (*st\_en* = 1), it is capable of generating a variety of valid and invalid signals with different frequencies and number of cycles. The output multiplexer (OM) outputs *WU\_INT* by selecting either internally generated interrupt signal *int\_r* or external manually control interrupt WU\_EXT. The control decoder (CDEC) decodes interrupt *int\_ctrl*, mode *mode\_ctrl*, and monitor *monitor\_ctrl* control signals from the external CTRL input.

Figure 6. RF WuRx intelligent digital controller (IDC) architecture.

Figure 7. RF wake-up and wake-on interrupt timing diagram.

#### 3.1. Self-Hibernation for Low Power Consumption

A self-hibernation methodology with dynamic frequency and voltage scaling is introduced for reducing the IDC and oscillator power consumption during the non-wake-up interval. The average power consumption  $P_{AV}$  in the CMOS circuit is the sum of dynamic  $P_{DYN}$ , short circuit  $P_{SHORT}$ , leakage  $P_{LEAKAGE}$ , and static  $P_{STATIC}$  power consumptions [26] as explained in (1) as follows:

$$P_{AV} = P_{DYN} + P_{SHORT} + P_{LEAKAGE} + P_{STATIC}.$$

(1)

In CMOS circuits,  $P_{DYN}$  is the dominant power consumption component. It is the linear function of operating frequency f and the quadratic function of the supply voltage  $V_{DD}$  of the circuit as given in (2) as follows:

$$P_{DYN} = KCfV_{DD'}^2 \tag{2}$$

where K is switching activity factor, C is loading capacitance, and  $V_{DD}$  is supply voltage [26].

From Equation (2) it becomes obvious that if the switching frequency reduces, the power consumption of the CMOS circuit is reduced significantly. Furthermore, if the supply voltage is minimized, the dynamic power is reduced. The OSC frequency is configurable from IDC. The IDC programs the OSC at a relatively higher frequency,  $f_{WU}$ , and performs WuRx signal identification during the active interval. After the wake-up interval, it operates at a relatively very low frequency,  $f_{SH}$ , during the sleep period after configuring the OSC for the slowest frequency. Since the communication between RSE and OBU is only for a very short duration and the OBU is in sleep mode for most of the time, the self-hibernation proves its significant impact for reducing WuRx power consumption and extending battery lifetime. The supply voltage is also reduced from 1.2 V to 0.9 V to save battery power.

#### 3.2. Built-In Self-Test for IDC Reliability

For ensuring IDC reliability and accuracy, a built-in self-test technique is integrated. It verifies the IDC full operation and functional accuracy without the presence of an external RF wake-up signal. In the presented self-test scheme, a configurable self-test pattern generator module generates a variety of configurable wide range valid wake-up signals with a frequency described as follows in Equation (3):

$$f_{ST} = \frac{N_{ST}}{f_{WU}},\tag{3}$$

where  $f_{ST}$  is test wake-up signal  $st_sig$  frequency, which is programmable from the  $N_{ST}$  parameter. It is also capable of generating non-wake-up, false and poor wake-up, and noise signals during test mode and guarantees IDC functional accuracy and enhances overall WuRx reliability.

#### 3.3. Configurable Modes

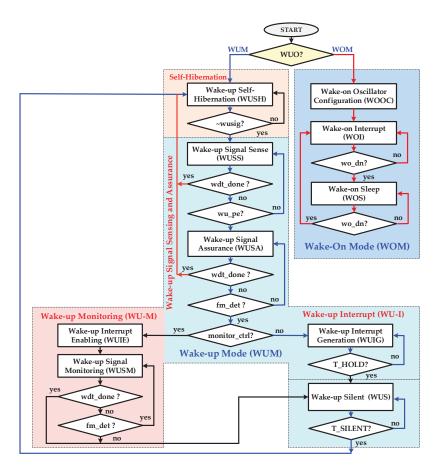

In the proposed IDC structure, two fully configurable modes are explored for WuRx. The wake-up mode (WUM) is for purely asynchronous wake-up signal detection from RSE with reduced latency. It processes the baseband recovered signal from the envelope detector after the comparator for identifying the wake-up signal. On the other hand, the wake-on mode (WOM) is an auxiliary pseudo-synchronous mode. When it is enabled, it turns on the main receiver for a very small configurable time interval, listens to any possible request from RSE, and keeps off for a relatively long duration. The mode control signal wake-up/-on (WUO) chooses the current selected mode. When WUO is low, a wake-up mode is enabled, which is the default mode. For enabling WOM, the WUO is configured as high.

#### 3.3.1. Wake-Up Mode

The FSMC is key building block of IDC, and its flow chart is elaborated in Figure 8. The wake-up mode with self-hibernation, digital hysteresis, and wake-up interrupt (WU-I) is the default flow in the wake-up period for ensuring WuRx reliability and accuracy. On power up, FSMC is in a wake-up self-hibernation (WUSH) state. The proposed self-hibernation technique reduces the power consumption of IDC and OSC significantly in the non-wake-up interval by configuring OSC to its lowest self-hibernation frequency,  $f_{SH}$ . The dynamic power of a circuit is directly proportional to its operating frequency, as shown in (2). If the frequency reduces, the power consumption also reduces. When IDC detects high assertion on the *wusig* signal during self-hibernation, it configures OSC to its normal wake-up frequency,  $f_{WU}$ , and waits for OSC settling in the WUSH state. The  $f_{WU}$  is a much higher frequency than  $f_{SH}$  for achieving higher wake-up signal measuring accuracy. The controller starts sensing a wake-up signal in the wake-up signal sense (WUSS) state. The SPEG detects *wusig* every rising edge and generates a  $wu_pe$  pulse signal which is sensed in the WUSS state. The controller

enables CWDT by asserting a high  $wdt\_en$  signal. The CWDT provides a self-recovery mechanism for FSMC and it is enabled to avoid uncertain situations and improve IDC reliability. If  $WU\_SIG$  is a noise pulse or glitch, it is identified and filtered out at this stage and FSMC moves back to WUSH for self-hibernation. After the sensing stage, the controller clears CWDT by asserting a high  $wdt\_clr$  signal for one clock cycle and moves to next state. The IDC verifies the  $WU\_SIG$  signal in the wake-up signal assurance (WUSA) state. The AFMU evaluates  $WU\_SIG$  each cycle and confirms if its frequency  $f_{SIG}$  is in a configured range. The integrated configurable digital hysteresis technique accomplishes this task and accommodates wake-up frequency variations to improve reliability. The  $WU\_SIG$  is a valid signal if its frequency fulfills the following condition described in (4) as follows:

$$f_{\text{MOD},\text{MIN}} \ge f_{\text{SIG}} \le f_{\text{MOD},\text{MAX}},\tag{4}$$

where  $f_{MOD.MIN}$  and  $f_{MOD.MAX}$  are the lower and upper limits of the valid WuRx signal modulation frequencies. These limits are configurable by parameters  $N_{NFX}$  and  $N_{XFN}$ , respectively, and are described as follows in (5):

$$f_{MOD.MIN} = \frac{f_{WU}}{N_{XFM}},$$

(5a)

$$f_{MOD.MAX} = \frac{f_{WU}}{N_{NFX}}.$$

(5b)

The configurable successive number of wake-up signal cycles,  $WU_N$ , in the allowed frequency bandwidth are ensured in the WUSA state. If the  $WU_SIG$  WuRx signal frequency is not in the allowed range as described in (4) or the signal cycles are less than  $WU_N$ , then it means the signal is not a valid wake-up signal and a main transceiver must remain off to save power. The false and poor wake-up signals are identified and filtered out in the WUSA state by AFMU and CWDT successfully. If a non-wake-up signal is identified in this state, the controller moves back to a self-hibernation state. After sensing and assurance, the wake-up interrupt  $WU_INT$  is initiated for configurable  $T_{HOLD}$ duration in the wake-up interrupt generation (WUIG) state. The interrupt hold duration is defined as follows in (6):

$$T_{HOLD} = \frac{N_{HOLD}}{f_{WU}},\tag{6}$$

where  $N_{HOLD}$  is the configurable parameter for defining wake-up interrupt hold duration. After the interrupt generation, FSMC remains silent for the  $T_{SILENT}$  interval in the wake-up silent (WUS) state and moves back to the WUSH state. The WUS state prohibits the WuRx to detect the current wake-up signal again if  $WU_N$  and  $T_{HOLD}$  parameters are configured to smaller values. The silent interval is programmable from parameter  $N_{SILENT}$  according to (7) as follows:

$$T_{SILENT} = \frac{N_{SILENT}}{f_{WU}}.$$

(7)

If wake-up monitoring (WU-M) is enabled by signal *monitor\_ctrl*, then the FSMC moves to the wake-up interrupt enable (WUIE) state after confirming  $WU_N$  wake-up signal cycles in the WUSA state. It asserts  $WU_INT$  high and moves to the wake-up monitoring (WUSM) state. The controller continuously evaluates  $WU_SIG$  for the presence of a valid wake-up signal and it additionally provides  $WU_INT$  for the entire duration of the wake-up signal instead of  $T_{HOLD}$ . It gives more space to MCU to detect interrupt and trigger an acknowledge signal to RSE at the end of the wake-up signal. The proposed WUM guarantees to pass only a valid wake-up signal and it definitely identifies and filters out all non-wake-up signals. It ensures the accuracy and reliability of WuRx. The IDC turns on a main heavy powered transceiver at OBU only with a valid wake-up request from RSE.

Figure 8. WuRx intelligent digital controller (IDC) finite state machine controller (FSMC) flow diagram.

#### 3.3.2. Wake-On Mode

The pseudo-synchronous wake-on mode (WOM) enhances overall reliability of transceiver in case of an issue in the main WuRx path. When WOM is enabled, the IDC configures OSC to desire frequency  $f_{WO}$  based on configured parameters in the wake-on oscillator configuration (WOOC) state, as shown in Figure 8. The wake-on interrupt  $T_{WOI}$  and wake-on sleep  $T_{WOS}$  intervals are computed according to (8) and (9), respectively, as follows:

$$T_{WOI} = \frac{N_{WOI}}{f_{WO}},\tag{8}$$

$$T_{WOS} = \frac{N_{WOS}}{f_{WO}}.$$

(9)

After frequency configuration and OSC settling, the controller moves to a wake-on interrupt (WOI) state. In this state,  $WO_{INT}$  is asserted high for the  $T_{WOI}$  duration and MCU turns on the main receiver for intercepting any communication request from RSE. After the  $T_{WOI}$  interval, FSMC jumps to a wake-on sleep (WOS) state. The  $WO_{INT}$  is asserted low and MCU turns off the main receiver for the programmed  $T_{WOS}$  duration. After a sleep interval, the controller moves back to the WOI state and periodically generates configurable wake-on interrupt  $WO_{INT}$  for receiver.

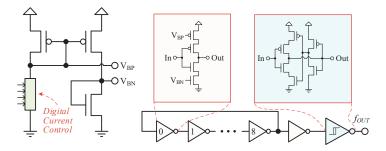

#### 4. Ultra-Low Power Configurable RC Oscillator

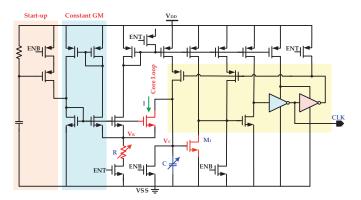

In the proposed WuRx, an ultra-low power configurable RC oscillator is integrated, which is the clock source for IDC. The RC oscillator structure is adopted rather than the crystal oscillator due to its low cost, less power consumption, fast start-up interval, and easy on-chip integration [27]. The fabricated oscillator has a wide controllable tuning range, *f<sub>CLK,MIN</sub>~f<sub>CLK,MAX</sub>*, and IDC configures it for different frequencies in wake-up, self-hibernation, and wake-on mode by controlling its capacitance values. For ultra-low power applications, the circuits are preferred to be operated in a weak inversion region, also known as the sub-threshold region [28,29]. Therefore, the oscillator is designed to operate in a sub-threshold region. Figure 9 shows the ultra-low power RC oscillator [27]. The configurability for various frequencies is achieved by altering resistance R and capacitance C values from IDC. This oscillator is composed of current reference, start-up, capacitor charge/discharge sensing circuits, and a frequency generation part. The current source or sink circuit is preferable to function in a weak inversion region for low power operation. The MOS transistor is operating in a sub-threshold region when the drain current  $I_D$  flows and the gate to source voltage  $V_{CS}$  is less than the threshold voltage  $V_{TH}$ . The diffusion current between source and drain mainly contributes to this current. The start-up circuit prohibits self-biased circuits to work at a zero biasing point. To enhance current sink or source output resistance, the current mirrors in a cascade structure are used. This generated current is mirrored by the current mirror and fed to capacitor, hysteresis controller  $M_1$ , and current-starved invertors for clock generation. The drain current I charges the capacitor C, and when  $V_C$  becomes equal to hysteresis controlling transistor  $M_1 V_{TH}$  value, the  $M_1$  turns on. For clock frequency generator circuit, the voltage  $V_C$  across capacitor C linearly increases with the increase in current I when constant current flows into the capacitor, as described in (10) as follows:

$$\Delta V_C = \frac{I\Delta t}{C}.\tag{10}$$

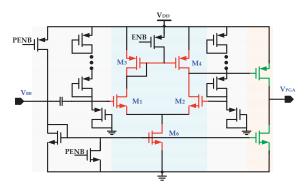

Figure 9. Ultra-low power configurable range communication (RC) oscillator.

The transistor  $M_1$  logical  $V_{TH}$  also controls capacitor voltage. Hence, the capacitor C charging and discharging duration is controlled by current I and transistor  $M_1$ , and a triangular voltage waveform is generated for the capacitor. From (10), single charging or discharging cycle time  $\Delta t$  is given in (11):

$$\Delta t = \frac{C\Delta V}{I}.\tag{11}$$

The current mirror builds a constant current source as a current generator part. The voltage  $V_R$  is always stabilized by the feedback path. Hence, according to Ohm's law, the resistance *R* decides the amount of current. Thus, from (11), the generated clock period  $T_{CLK}$  is described in (12) as follows:

$$T_{CLK} = 2RC \frac{\Delta V_C}{V_R}.$$

(12)

The RC oscillator output frequency  $f_{CLK}$  is given in (13) as follows:

$$f_{CLK} = \frac{1}{T_{CLK}} = \frac{1}{2RC} \cdot \frac{V_R}{\Delta V_C}.$$

(13)

The capacitance *C* is designed as unit weighted capacitor bank, and IDC configures this capacitor back at different values for generating frequencies  $f_{WU}$ ,  $f_{SH}$ , and  $f_{WO}$  for the wake-up mode, self-hibernation, and wake-on mode, respectively.

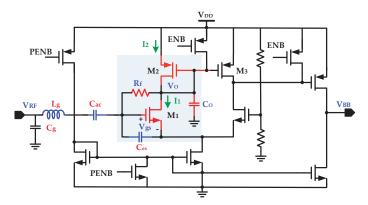

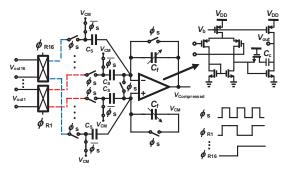

#### 5. RF Front End and Baseband Processing

The RF front end in the proposed WuRx is composed of a high sensitivity RF envelope detector with an embedded internal matching network. The RFED-based approach is most common for designing a WuRx circuit for its low current consumption. With this scheme, the requirement of a LO generation for frequency down-conversion and RF amplification is also eliminated at the cost of reduced sensitivity. The internal matching improves sensitivity of the circuit. The RFED is the key building block in the WuRx circuit for interfacing with an antenna through a matching network and generating a baseband output signal by down-converting the input amplitude-modulated RF signal. Figure 10 illustrates the proposed RF envelope detector circuit with internal matching network [18,30]. The circuit is mainly composed of nonlinear transistor element  $M_1$ , input signal DC blocking capacitor  $C_{ac}$ , self-biasing feedback resistor  $R_f$ , impedance matching network with gate inductor  $L_g$ , and excess capacitor  $C_{ex}$ . The impedance matching network provides passive voltage amplification. With large self-biasing resistance, when RF input signal is not present, the  $M_1$  gate to source voltage  $V_{gs}$  is closed to transistor threshold voltage  $V_{TH}$  with a very negligible biasing current. In this way, the limited sensitivity issue due to  $V_{TH}$  loss is compensated. The  $R_f$  is designed with a pseudo-resistor for large resistance with minimized parasitic capacitance and a small area. It perfectly isolates output voltage  $V_0$  from RF input signal  $V_{RF}$  and prevents envelope detector loading. When  $V_{RF}$  is applied, the drain current  $I_1$ exponentially increases while the biasing current supplied from  $M_2$  is almost constant.

Figure 10. RF envelope detector with internal matching and self-biasing feedback resistor.

The capacitor  $C_O$  discharges and this discharge current decreases  $V_O$  until  $I_1$  and  $I_2$  become almost equal. This generates a 180° phase shift between  $V_{RF}$  and  $V_O$ . The convergence gain  $G_C$ , defined as the ratio of output baseband signal voltage amplitude to the RF input signal voltage amplitude, is evaluated as follows in (14):

$$G_C = \frac{1}{4} \frac{Q^2 I_1}{(n U_T)^2} r_0, \tag{14}$$

where *Q* is quality factor of the matching network, *n* is sub-threshold slope factor,  $U_T$  is thermal voltage, and  $r_0$  is intrinsic output impedance.

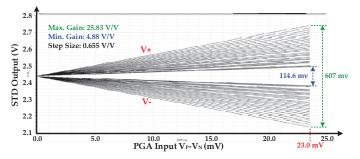

The baseband signal  $V_{BB}$  produced by the RF envelope detector is subsequently processed for enhancing amplitude by a programmable gain baseband amplifier and a comparator before it is fed to IDC for digital processing for generating an interrupt signal. Figure 11 shows the PGA circuit that is a baseband amplification stage. It has high input impedance and its gain is configurable from external MCU. It provides flexibility for improving gain and amplifies the baseband signal  $V_{BB}$  significantly.

Figure 11. Programmable gain amplifier.

The hysteresis comparator, shown in Figure 12, is the final stage of baseband processing to generate a digital signal for IDC processing. It is composed of a positive feedback circuit with an amplifier, AMP. A two stage amplifier with output inverter [31] is used as a low power CMOS amplifier. With feedback resistor  $R_2$ , hysteresis upper and lower threshold values are configured for eliminating multiple transitions caused by noise. The three stage amplifier is composed of a differential amplifier, common source amplifier, and an output inverter. The analog differential input signals IN- and IN+ are applied at differential pair  $M_1$  and  $M_2$ . The differential pair transistor width is increased to reduce input offset voltage and increase gain. To minimize the propagation delay and reduce common source transistor  $M_7$  gate parasitic capacitance, the  $M_7$  is designed with a small size. The final inverter stage also enhances gain and improves the comparator slew rate. The final digital wake-up comparator output signal  $WU_SIG$  is fed to IDC for digital processing. The RF front end and analog baseband processing processes all signals and it does not filter or remove any non-wake-up signal. The IDC differentiates between actual wake-up signals and unwanted signals.

Figure 12. Hysteresis comparator with positive feedback and amplifier.

#### 6. Experimental Results

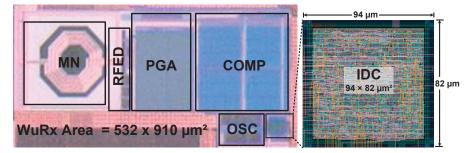

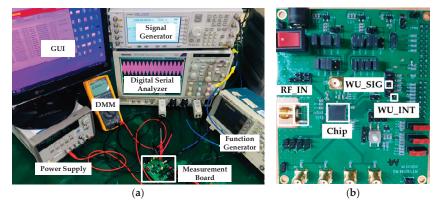

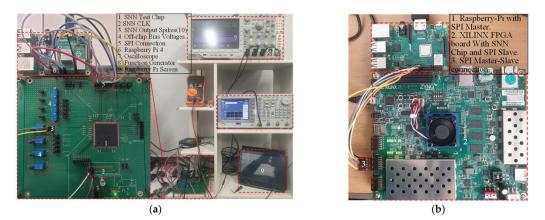

The presented WuRx is integrated in a DSRC transceiver for ETCS applications. It is fabricated with a 130 nm CMOS process. Figure 13 shows the microphotograph of WuRx and magnified IDC layout. The WuRx occupied chip area is  $532 \times 910 \ \mu\text{m}^2$  of which IDC takes only  $94 \times 82 \ \mu\text{m}^2$ . The WuRx is measured extensively to ensure its reliability and accuracy. The experimental lab environment is captured in Figure 14a and the measurement board with the fabricated DSRC transceiver chip is depicted in Figure 14b. The board is powered up from the Agilent® DC Power Supply with 5 V and the on-chip low dropout regulator (LDO) generates 0.9 V for the WuRx circuit, which is measured at the output pin with a digital multi-meter (DMM). The lower supply voltage is used to minimize the power consumption and all blocks, and correct operation is verified at a supply voltage of 0.9 V. The OOK baseband wake-up signal is generated from the Tektronix® AFG3101 Function Generator and modulated at 5.8 GHz with the Agilent® E4438C Signal Generator. This modulated RF signal is fed at a RF\_IN SMA input connector on the board and after passing through external pi-matching network, package pin, and die PAD, it enters the WuRx circuit. The comparator output WU\_SIG and wake-up interrupt WK\_INT are plotted on a Tektronix® DSA71254C Digital Serial Analyzer. Different parameters and configurations are programmed through SPI and the graphical user interface (GUI) running on computer.

Figure 13. WuRx chip microphotograph and magnified IDC layout.

Figure 14. WuRx measurement: (a) experimental lab setup; (b) measurement board with chip.

The IDC performance is summarized in Table 1. The proposed digital controller is fully synthesizable. With an area of 0.007 mm<sup>2</sup> and a 34.62 nW power consumption, it not only ensures WuRx reliability and accuracy but also replaces complex and power hungry analog blocks such as BPF and ADC. The configurability, operating modes, digital hysteresis, and self-hibernation features prove its sublimity. The power consumption with and without self-hibernation for IDC and OSC and its

effect on overall WuRx power performance is summarized in Table 2. Since the DSRC communication between RSE and OBU lasts for a very short interval and the OBU is in sleep mode most of the time, self-hibernation by voltage and frequency scaling has a significant positive impact on battery performance. The performance comparison of the proposed WuRx with the existing designs is listed in Table 3. The wake-up circuits in [8,24] integrate the complex BPF and [9] use the frequency detector (FD) circuit as its interface output stage without ensuring reliability and filtering of non-wake-up signals. The proposed WuRx architecture incorporates a fully synthesizable intelligent controller, which is not only area and power efficient but it also ensures unwanted signals filtering, guarantees WuRx reliability, and improves battery performance. The measurement results report an almost identical sensitivity of -46 dBm and a power consumption of only 2.48  $\mu$ W.

| Value                         |

|-------------------------------|

| value                         |

| 130 nm                        |

| $0.0077 \text{ mm}^2$         |

| 809                           |

| 0.9 V                         |

| 38.47/9.7 nA                  |

| 34.62/8.73 nW                 |

| 1–140 kHz                     |

| Yes                           |

| Digital hysteresis, BIST, WDT |

| WUM (WU-I, WU-M), WOM         |

|                               |

Table 1. IDC performance summary.

<sup>1</sup> Without and with self-hibernation.

Table 2. Power consumption summary with and without self-hibernation.

| Block                                                         | Without Self                  | -Hibernation                    | With Self-H                 | libernation                   |

|---------------------------------------------------------------|-------------------------------|---------------------------------|-----------------------------|-------------------------------|

| DIOCK                                                         | Current                       | Power                           | Current                     | Power                         |

| Intelligent digital controller<br>RC oscillator<br>Total WuRx | 38.47 nA<br>214 nA<br>2.75 μA | 34.62 nW<br>192.6 nA<br>2.48 μW | 9.7 nA<br>107 nA<br>2.62 μA | 8.73 nW<br>96.3 nW<br>2.36 μW |

| Parameter                    | [8] | [9]  | [24] | This Work |

|------------------------------|-----|------|------|-----------|

| CMOS process (nm)            | 130 | 180  | 130  | 130       |

| Wake-up frequency (kHz)      | 14  | 7~42 | 14   | 1-140 1   |

| Operating frequency (GHz)    | 5.8 | 5.8  | 5.8  | 5.8       |

| Sensitivity (dBm)            | -44 | -47  | -45  | -46       |

| Power consumption (µW)       | 36  | 3.8  | 45   | 2.48 *    |

| Chip area (mm <sup>2</sup> ) | -   | -    | -    | 0.484     |

| Interface                    | BPF | FD   | BPF  | IDC       |

Table 3. WuRx performance comparison.

<sup>1</sup> Configurable for any specific range. \* Without self-hibernation.

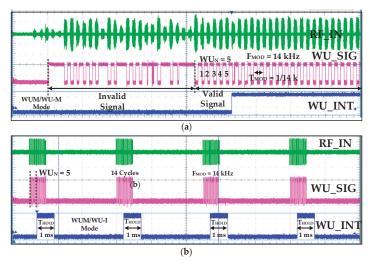

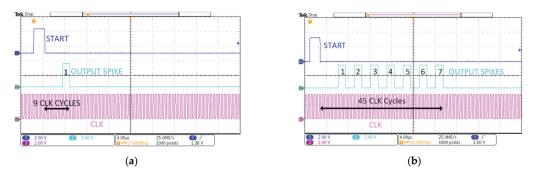

The WuRx accuracy and reliability is verified by applying various RF-modulated valid and invalid signals with different amplitudes and frequencies at the  $RF_IN$  input. When the input signal is valid, meaning its amplitude is greater than the sensitivity and its frequency is in a configured hysteresis range, the WuRx gives out confirmed wake-up interrupt signal. In the measurement results in Figure 15a, initially random, invalid OOK sequence, modulated at 5.8 GHz, with a sensitivity of -46 dBm is applied at the  $RF_IN$  input. The baseband signal is successfully recovered by RFED and the digital  $WU_SIG$  from COMP is fed to IDC. As it is clear from the results, the IDC identifies this invalid sequence and does not generate a confirmation signal. Later, the valid wake-up signal is ensured and

verified by IDC. If IDC is not used at the comparator output, then WuRx reliability degrades as the main power hungry receiver is turned on, even with a non-wake-up signal. The consecutive burst of valid wake-up signals, as shown in Figure 15b, with exactly 14 clock cycles at 14 kHz is applied for proving proposed WuRx robustness, accuracy, and reliability. For each time,  $WU_INT$  is generated for approximately 1 ms after confirming five clock cycles ( $WU_N = 5$ ) and IDC returns to its ideal state for the next wake-up signal sensing.

**Figure 15.** WuRx measurement result: (**a**) initially, invalid random sequence and then valid wake-up signal; (**b**) wake-up valid signal burst for robustness testing.

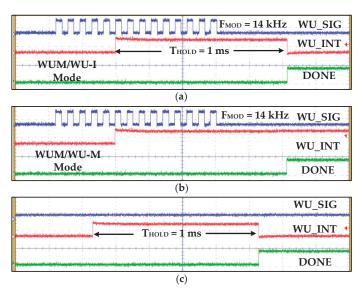

Figure 16 shows different WUM measurement results for various scenarios. In this measurement,  $WU_N$  is set to 5 and digital hysteresis, watch-dog timer, and  $T_{HOLD}$  are configured to 11~18 kHz, 142.8 µs, and 1 ms, respectively. The OSC is configured for wake-up and self-hibernation frequencies of 140 kHz and 14 kHz, respectively. Figure 16a,b show WUM with WU-I and WU-M configurations, respectively, in which the  $WU_SIG$  frequency is 14 kHz. The  $WU_INT$  is generated after sensing and confirming five successive  $WU_SIG$  clock cycles. In normal WUM, IDC and OSC current consumption from a 0.9 V supply is 38.47 nA and 214 nA, which reduces to 9.7 nA and 107 nA in self-hibernation, respectively. The self-test is measured in Figure 16c in which the  $st_sig$  signal of 14 kHz is generated by STPG.

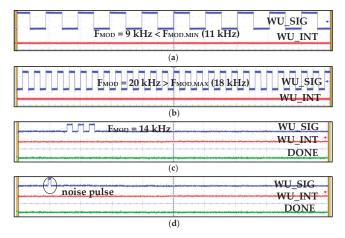

Figure 17 summarizes WuRx measurement results with false, poor, invalid signals. Figure 17a,b shows results when the  $WU\_SIG$  frequency is out of the configured hysteresis range (11 kHz~18 kHz in this case) and identifies false wake-up signals. Poor and false wake-up and noise signals are also perfectly identified and  $WU\_INT$  is not generated. The signal with a valid frequency but insufficient number of cycles (less than  $WU_N = 5$ ) is identified and filtered accurately by IDC, as shown in Figure 17c. Similarly, noise pulses and glitches in the RF signal are converted to a baseband digital signal and sensed and removed by IDC without generating interrupt and prohibits turning on the power hungry main receiver. If IDC is not integrated, then all these invalid signals are identified as wake-up signals, and as a consequence, power on transceiver falsely and degrading battery performance.

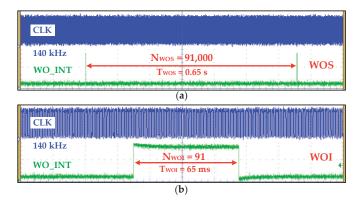

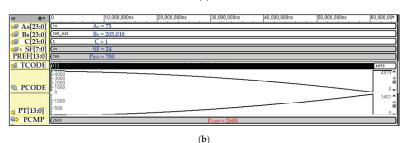

The WOM measurement result is depicted in Figure 18 in which  $T_{WOI}$  and  $T_{WOS}$  intervals are set for 65 ms and 0.65 s by configuring  $N_{WOI}$  = 91 and  $N_{WOS}$  = 91,000 according to (8) and (9), respectively.

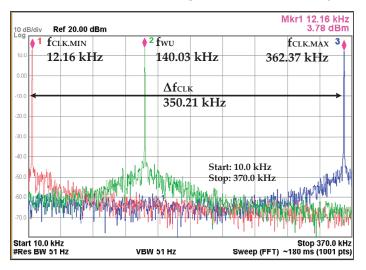

The measured tuning range of OSC is captured in Figure 19. The OSC capacitor *C* is implemented as binary weighted capacitor bank which is controlled from an 8-bit  $OSC\_CTRL$  signal from IDC. The measured  $f_{CLK.MIN}$  and  $f_{CLK.MAX}$  frequencies are 12.16 kHz and 362.37 kHz when  $OSC\_CTRL$  values

are all high and all low, respectively, with a total frequency range  $\Delta f_{CLK}$  of 350.21 kHz. The spectrum also shows the WUM frequency which is configured as approximately 140 kHz. In self-hibernation mode, the OSC frequency  $f_{SH}$  is configured to about 14 kHz. The WOM clock frequency depends on the configured parameters for  $T_{WOI}$  and  $T_{WOS}$  intervals. At  $f_{WUI}$  of 140 kHz, it draws 214 nA current from 0.9 V supply which is reduced to almost half in self-hibernation mode.

Figure 16. WuRx measurement results for different IDC wake-up modes with valid signals: (a) wake-up interrupt (WU-I); (b) wake-up monitoring (WU-M); (c) self-test with WU-I mode.

**Figure 17.** WuRx measurement results for invalid signals and IDC identification and filtering: (a) invalid wake-up signal with modulation frequency of 9 KHz, which is less than the minimum hysteresis configured limit of 11 kHz; (b) invalid wake-up signal with modulation frequency of 20 KHz, which is greater than the maximum hysteresis configured limit of 18 kHz; (c) poor wake-up signal with valid modulation frequency but less number of cycles than the configured value of 5; (d) invalid signal of noise pulse.

**Figure 18.** Wake-on mode measurement result: (a) Wake-on sleep of 0.65 s duration when  $N_{WOS}$  is configured with value of 91,000; (b) wake-on interrupt of 65 ms when NWOI is configured as 91.

Figure 19. Oscillator (OSC) frequency range and measurement result.

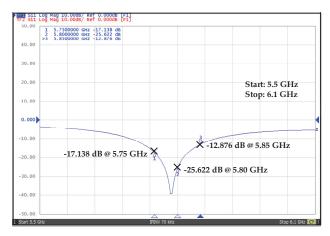

Figure 20 shows the measured reflection co-efficient,  $|S_{11}|$ , for the proposed WuRx. The measured value of  $|S_{11}|$  at 5.8 GHz is about -25.622 dB, which shows the excellent matching. Moreover,  $|S_{11}|$  values at 5.75 GHz and 5.85 GHz are -17.138 dB and -12.876 dB, respectively.

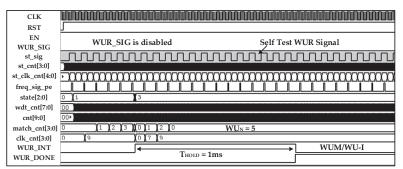

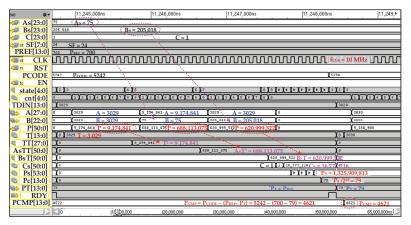

Figure 21 summarizes the detailed IDC post place and route (P&R) simulation results using the NC-Verilog<sup>®</sup> tool. The wake-up interrupt mode simulation result is shown in Figure 21a in which  $WU_SIG$  with different frequencies is applied. It is clear from the simulation results that when the wake-up signal is either less or greater than the configured hysteresis range (11 kHz~18 kHz), it is identified and filtered out without generating interrupt at  $WU_INT$ . The self-test simulation with one of the configurations is shown in Figure 21b. The STPG generates a variety of valid and invalid signals for ensuring the functional accuracy of IDC. Instead of a baseband digital  $WU_SIG$  signal, the test wake-up signal  $st_sig$  is generated internally by STPG. The IDC accurately generates interrupt  $WU_INT$  after identifying and verifying the signal, as shown in Figure 21b. The self-test enhances the reliability of IDC itself. The WOM simulation is depicted in Figure 21c in which  $T_{WOI}$  and  $T_{WOS}$  intervals are set for 20.8 ms and 0.65 s by configuring  $N_{WOI} = 2912$  and  $N_{WOS} = 91,000$  according to (8) and (9), respectively.

Figure 20. RF external on board impedance matching measurement result.

| CLK            |                  | <b>F</b> сlk <b>= 140</b>    | kHz                    |                        |                        |

|----------------|------------------|------------------------------|------------------------|------------------------|------------------------|

| RST            | ļ                |                              |                        |                        |                        |

| EN             | Fs = 5 kHz       | $F_s = 11 \text{ kHz}$       | $F_s = 14 \text{ kHz}$ | $F_s = 18 \text{ kHz}$ | $F_s = 20 \text{ kHz}$ |

| WU_SIG         | mmmm             |                              |                        |                        |                        |

| freq_sig_pe    |                  |                              |                        |                        |                        |

| state[2:0]     | () <sup>(1</sup> | 1 4 5                        | <b>X</b> (1)(4)        | 5 📈 1 🛛 4              | 5 1                    |

| wdt_cnt[7:0]   | 0                | 00                           |                        | 00                     | 00                     |

| cnt[9:0]       | 0                | 00000                        | 00000                  | 00000                  |                        |

| match_cnt[3:0] | 0                | nun o                        |                        | ш <b>и</b> о           |                        |

| clk_cnt[3:0]   | 0 3              | $\Omega \Omega \Omega \circ$ | <b>1</b> 9 <b>1</b> 0  | (7)(0                  | <b>(</b> 6             |

| WU_INT         |                  | <b>←</b> →                   |                        |                        | ▶                      |

| WU_DONE        |                  | THOLD = 1ms                  | THOLD = 1ms            | THOLD = 1m             | 15                     |

(a)

(b)

| CLK        | Fсік = 140 kHz              |

|------------|-----------------------------|

| RST        |                             |

| EN         |                             |

| NWOS       | 16378 NWOS[19:0] = 91,000   |

| NWOI       | B60, WOI NWOI[11:0] = 2,912 |

| state[2:0] | 0 1 WOS Twor= 20.8 ms • 0 1 |

| WO_INT     | Twos= 0.65 s                |

|            | (c)                         |

**Figure 21.** The IDC post place and route (P&R) simulation result: (a) WU/WU-I with different wake-up frequencies; (b) self-test with WU\_I; (c) wake-on mode with interrupt and sleep durations of 20.8 ms and 0.65 s.

#### 7. Conclusions

A highly reliable RF WuRx is presented for ETC systems in this article. For improving WuRx reliability and enhancing battery performance, the IDC is proposed as final stage. The IDC also acts as filter and replaces complex and power demanding analog blocks such as BPF, ADC, and FD. With the proposed configurable digital controller, high reliability and accuracy are achieved by sensing and ensuring a successive, configurable number of wake-up signal cycles before enabling power hungry RF transceiver. The presented self-hibernation technique reduces IDC and RC oscillator current consumption during the non-wake-up period and improves battery life. The digital hysteresis accommodates wake-up signal frequency variation and enhances WuRx accuracy. To avoid uncertain conditions during poor and false wake-up, a watch-dog timer for IDC self-recovery is integrated. During wake-up, the digital controller requires 34.62 nW power. In self-hibernation mode, its current reduces from 38.47 nA to 9.7 nA. It is fully synthesizable and needs 809 gates for its implementation in a 130 nm CMOS process with an area of  $94 \times 82 \mu m^2$ . The WuRx measured power consumption is  $2.48 \mu W$ , has -46 dBm sensitivity, and a  $0.484 \text{ mm}^2$  chip area. The extensive measurement and verification make the proposed WuRx an ideal solution for a highly reliable DSRC wake-up circuit.

**Author Contributions:** K.-Y.L. guided and directed the authors for this research. I.A. proposed, designed, simulated, and implemented the overall architecture and wrote the paper. M.A., M.R.U.R., D.K., and H.Y. contributed to the synthesis and place and route (*P* & R) simulation. They also contributed to the design of the top layout of the chip. S.J.K. helped writing the paper, designing the testing board, and during the measurements. Y.P. and S.-S.Y. gave advice about implementation issues and reviewed the paper before submission. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIP) (2014R1A5A1011478).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Kwon, K.; Choi, J.; Choi, J.; Hwang, Y.; Lee, K.; Ko, J. A 5.8 GHz integrated CMOS dedicated short range communication transceiver for the Korea/Japan electronic toll collection system. *IEEE Trans. Microw. Theory Tech.* 2010, 58, 2751–2763. [CrossRef]

- Moazzeni, S.; Sawanm, M.; Cowan, G.E.R. An Ultra-Low-Power Energy-Efficient Dual-Mode Wake-Up Receiver. IEEE Trans. Circuits Syst. I Reg. Pap. 2015, 62, 517–526. [CrossRef]

- Polonelli, T.; Huy, T.L.; Lizzi, L.; Ferrero, F.; Magno, M. A wake-up receiver with ad-hoc antenna co-design for wearable applications. In Proceedings of the IEEE Sensors Applications Symposium, Catania, Italy, 20–22 April 2016.

- Blanckenstein, J.; Klaue, J.; Karl, H. A Survey of Low-Power Transceivers and Their Applications. *IEEE Circuits* Syst. Mag. 2015, 15, 6–17. [CrossRef]

- Research Institute of Highway Ministry. *Electronic Toll Collection-Dedicated Short Range Communication-Part 1: Physical Layer*; China Nat. Standard GB/T 20851.1-2007; Research Institute of Highway Ministry: Beijing, China, 2007.

- Liu, H.; Qu, X.; Cao, L.; Liu, R.; Zhang, Y.; Zhang, M.; Li, X.; Wang, W.; Lu, C. A 5.8 GHz DSRC digitally controlled CMOS RF-SoC transceiver for China ETC. In Proceedings of the IEEE Asia and South Pacific Design Automation Conference, Jeju, Korea, 22–25 January 2018.

- Sasho, N.; Minami, K.; Fujita, H.; Takahashi, T.; Iimura, K.; Abe, M.; Yasuda, A. Single-chip 5.8 GHz DSRC transceiver with dual-mode of ASK and Pi/4-QPSK. In Proceedings of the IEEE Radio and Wireless Symposium, Orlando, FL, USA, 22–24 January 2008.

- Choi, J.; Lee, I.Y.; Lee, K.; Yun, S.O.; Kim, J.; Ko, J.; Yoon, G.; Lee, S.G. A 5.8-GHz DSRC transceiver with a 10-µA interference-aware wake-up receiver for the Chinese ETCS. *IEEE Trans. Microw. Theory Tech.* 2014, 62, 3146–3160. [CrossRef]

- Zhu, W.; Zhang, D.; Gao, T.; Liu, F.; Yang, H. A 2.1 μA wake-up circuit for Chinese ETC system. J. Electron. China 2013, 30, 308–312.

- Rekhi, A.; Arbabian, A. A 14.5 mm<sup>2</sup> 8 nW –59.7 dBm-sensitivity ultrasonic wake-up receiver for power-, area-, and interference-constrained applications. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2018.

- Masuda, T.; Ohhata, K.; Shiramizu, N.; Hanazawa, S.; Kudoh, M.; Tanba, Y.; Takeuchi, Y.; Shimamoto, H.; Nagashima, T.; Washio, K. Single-chip 5.8 GHz ETC transceiver IC with PLL and demodulation circuits using SiGe HBT/CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2002.

- 12. Marinkovic, S.J.; Popovici, E.M. Nano-power wireless wake-up receiver with serial peripheral interface. *IEEE J. Sel. Areas Commun.* 2011, 29, 1641–1647. [CrossRef]

- Kolinko, P.; Larson, L.E. Passive RF receiver design for wireless sensor networks. In Proceedings of the IEEE/MTT-S International Microwave Symposium, Honolulu, HI, USA, 3–8 June 2007.

- Pletcher, N.M.; Gambini, S.; Rabaey, J. A52 µW wake-up receiver with -72 dBm sensitivity using an uncertain-IF architecture. *IEEE J. Solid State Circuits* 2009, 44, 269–280. [CrossRef]

- Shin, S.; Yun, S.; Cho, S.; Kim, J.; Kang, M.; Oh, W.; Kang, S.M. 0.18 μm CMOS integrated chipset for 5.8GHz DSRC systems with +10 dBm output power. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 March 2008.

- Drago, S.; Leenaerts, D.M.W.; Sebastiano, F.; Breems, L.J.; Makinwa, K.A.A.; Nauta, B. A 2.4 GHz 830 pJ/bit duty-cycled wake-up receiver with -82 dBm sensitivity for crystal-less wireless sensor nodes. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2010.

- Pletcher, N.; Gambini, S.; Rabaey, J. A 65 μW, 1.9 GHz RF to digital baseband wakeup receiver for wireless sensor nodes. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007.

- Cheng, K.; Liu, X.; Je, M. A 2.4/5.8 GHz 10 μW wake-up receiver with -65/-50 dBm sensitivity using direct active rf detection. In Proceedings of the IEEE Asian Solid State Circuits Conference, Kobe, Japan, 12–14 November 2012.

- Huang, X.; Rampu, S.; Wang, X.; Dolmans, G.; Groot, H.D. A 2.4 GHz/915 MHz 51µW wake-up receiver with offset and noise suppression. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2010.

- Kamalinejad, P.; Keikhosravy, K.; Magno, M.; Mirabbasi, S.; Leung, V.C.M.; Benini, L. A high-sensitivity fully passive wake-up radio front-end for wireless sensor nodes. In Proceedings of the IEEE International Conference on Consumer Electronics, Las Vegas, NV, USA, 10–13 January 2014.

- Khan, D.; Oh, S.J.; Shehzad, K.; Basim, M.; Verma, D.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; Lee, K.Y. An Efficient Reconfigurable RF-DC Converter with Wide Input Power Range for RF Energy Harvesting. *IEEE Access* 2020, *8*, 79310–79318. [CrossRef]

- Khan, D.; Oh, S.J.; Shehzad, K.; Verma, D.; Khan, Z.H.N.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; Lee, K.Y. A CMOS RF Energy Harvester With 47% Peak Efficiency Using Internal Threshold Voltage Compensation. *IEEE Microw. Wireless Compon. Lett.* 2019, 29, 415–417. [CrossRef]

- Demirkol, I.; Ersoy, C.; Onur, E. Wake-up receivers for wireless sensor networks: Benefits and challenges. IEEE Trans. Wireless Commun. 2009, 16, 88–96. [CrossRef]

- 24. Choi, J.; Lee, K.; Yun, S.; Lee, S.; Ko, J. An interference-aware 5.8 GHz wake-up radio for ETCS. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012.

- Ali, I.; Rikhan, B.S.; Kim, D.-G.; Lee, D.-S.; Rehman, M.R.U.; Abbasizadeh, H.; Asif, M.; Lee, M.; Hwang, K.C.; Yang, Y.; et al. Design of a Low-Power, Small-Area AEC-Q100-Compliant SENT Transmitter in Signal Conditioning IC for Automotive Pressure and Temperature Complex Sensors in 180 Nm CMOS Technology. Sensors 2018, 18, 1555. [CrossRef] [PubMed]

- Chabini, N.; Chabini, I.; Aboulhamid, E.M.; Savaria, Y. Methods for minimizing dynamic power consumption in synchronous designs with multiple supply voltages. *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.* 2003, 22, 346–351. [CrossRef]

- Joonhyung, L.; Kwangmook, L.; Koonsik, C. Ultra low power RC oscillator for system wake-up using highly precise auto-calibration technique. In Proceedings of the IEEE European Solid-State Circuits Conference ESSCIRC, Seville, Spain, 14–16 September 2010.

- Ali, I.; Abbasizadeh, H.; Rehman, M.R.U.; Asif, M.; Oh, S.J.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. An Ultra-Low Power, Adaptive All-Digital Frequency-Locked Loop with Gain Estimation and Constant Current DCO. *IEEE Access* 2020, *8*, 97215–97230. [CrossRef]

- Abbasizadeh, H.; Ali, I.; Rikan, B.S.; Lee, D.S.; Pu, Y.G.; Yoo, S.S.; Lee, M.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. 260-µW DCO with Constant Current over PVT Variations Using FLL and Adjustable LDO. *IEEE Trans. Circuits Syst. II Exp. Briefs* 2018, 65, 739–743. [CrossRef]

- Cheng, K.; Chen, S. An Ultralow-Power Wake-Up Receiver Based on Direct Active RF Detection. *IEEE Trans. Circuits Syst. I Reg. Pap.* 2017, 64, 1661–1672. [CrossRef]

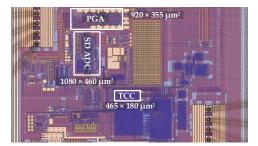

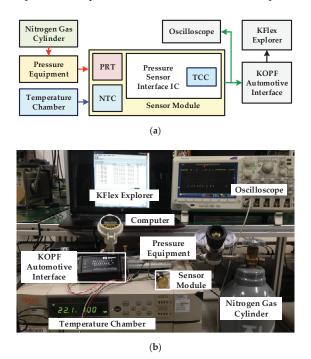

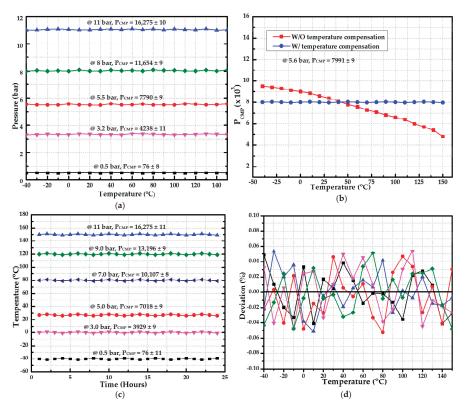

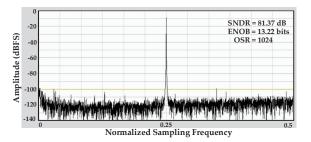

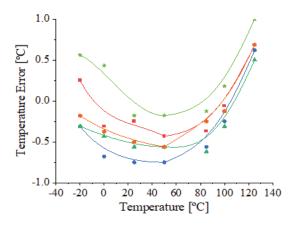

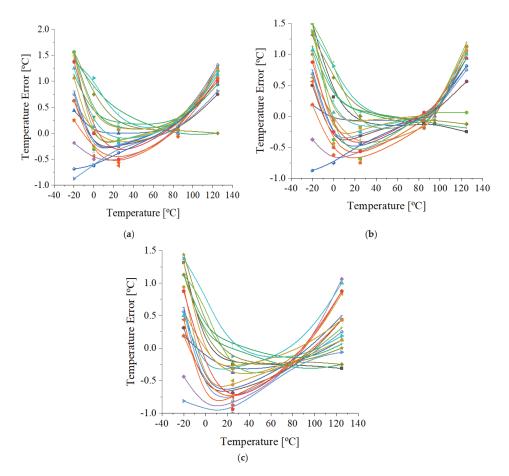

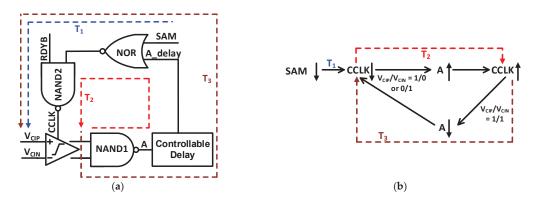

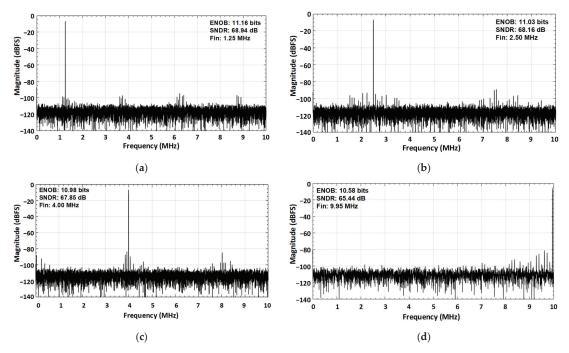

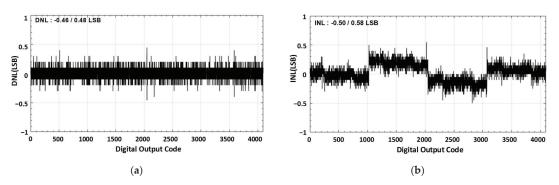

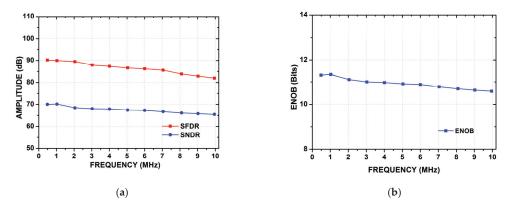

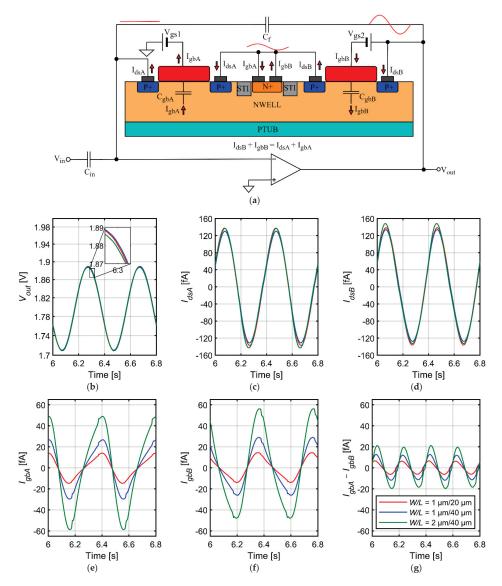

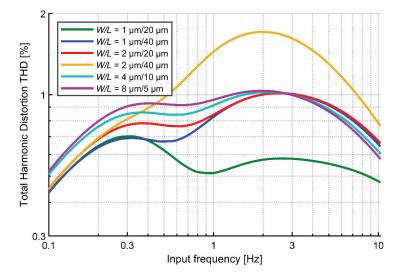

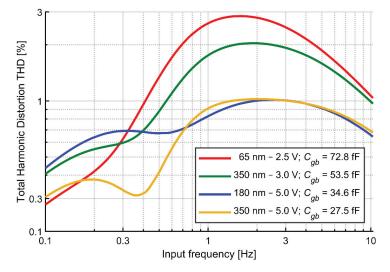

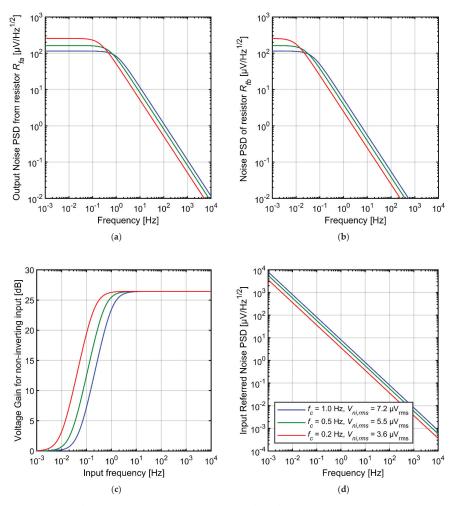

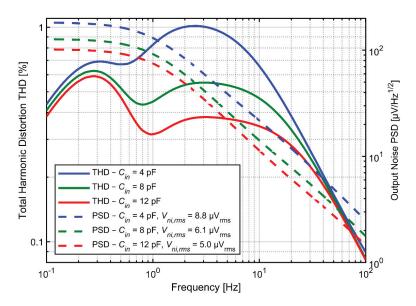

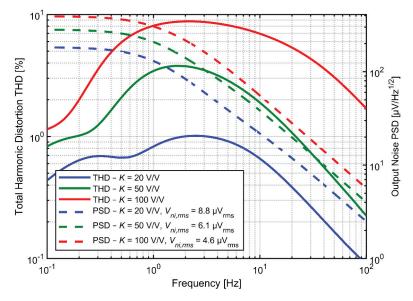

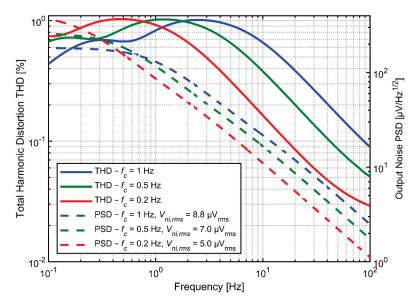

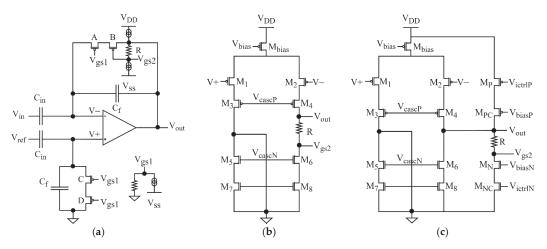

- Furth, P.M.; Tsen, Y.C.; Kulkarni, V.B.; Raju, T.K.P.H. On the design of low-power CMOS comparators with programmable hysteresis. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Seattle, WA, USA, 1–4 August 2010.