# Hardware Implementation of Fixed-Point Decoder for Low-Density Lattice Codes

by

Rachna Srivastava

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2022

$\bigodot$ Rachna Srivastava 2022

# Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Dr. Matthieu Arzel<br>Professor, Mathematical & Electrical Engineering,<br>IMT-Atlantique Bretagne             |

|---------------------------|----------------------------------------------------------------------------------------------------------------|

| Supervisor(s):            | Dr. Vincent C. Gaudet<br>Professor, Dept. of Electrical & Computer Engineering,<br>University of Waterloo      |

|                           | Dr. Patrick Mitran<br>Professor, Dept. of Electrical & Computer Engineering,<br>University of Waterloo         |

| Internal Members:         | Dr. Amir Keyvan Khandani<br>Professor, Dept. of Electrical & Computer Engineering,<br>University of Waterloo   |

|                           | Dr. Mark Aagaard<br>Associate Professor, Dept. of Electrical & Computer Engineering,<br>University of Waterloo |

| Internal-External Member: | Dr. William Melek<br>Professor, Dept. of Mechanical & Mechatronics Engineering,<br>University of Waterloo      |

### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Low-density lattice codes (LDLCs) are a special class of lattice codes that can be decoded efficiently using iterative decoding and approach the capacity of the additive white Gaussian noise (AWGN) channel. The construction and intended applications are substantially different from that of more familiar error-correcting codes such as low-density parity check (LDPC) codes, Polar, and Turbo codes. Lattice codes in general have shown great theoretical promise to mitigate interference, possibly leading to significantly higher rates between users in multi-user networks. Research on LDLCs has concentrated on demonstrating the theoretically achievable performance limits of LDLCs, and until now there has been no reported hardware implementation, mainly due to the complexity of message-passing for LDLC decoding.

This thesis contributes to the hardware implementation of the LDLC decoding. We present several fixed-point decoder implementations covering different parts of the architectural design space, on a field-programmable gate array (FPGA) device.

We first present the FPGA implementation of a fixed-point arithmetic LDLC decoder where the Gaussian mixture messages that are exchanged during the iterative decoding process are approximated to a single Gaussian. A detailed quantization study is performed to find the minimum number of bits required for the fixed-point decoder implementation to attain a frame-error-rate (FER) performance similar to floating-point. Efficient numerical methods are used to approximate the non-linear functions required in the decoder. A two-node serial LDLC decoder is implemented on an Intel Arria 10 FPGA as a hardware proof-of-concept attaining a throughput of 440 Ksymbols/sec at high signal-to-noise ratio (SNR). This throughput is obtained at clock frequency of 125 MHz and for a block length of 1000. By exploiting the inherent parallelism of iterative decoding, several parallel message processing blocks are then used to improve the throughput by a factor of  $13\times$ . Finally, we propose a pipelined architecture where the decoder achieves a throughput of 10.5 Msymbols/sec, that is,  $\sim 24\times$  improvement over the serial decoder.

Then, we implement a multi-Gaussian decoder where the Gaussian mixture messages exchanged during the decoding process have two components. We develop efficient techniques to reduce the decoder complexity for hardware implementation, e.g., selecting the strongest component from the Gaussian mixture as the final decision in iterative decoding, and a simplified method for coefficient computation during the product operation at the variable nodes. With a thorough quantization analysis and applying methods devised to approximate the non-linear functions, we design the multi-Gaussian decoders in fixedpoint arithmetic. We first implemented a serial architecture with a single check node and a single variable node. Then, a partially parallel architecture with a single check node and a variable node message processing block with two-stage pipelining is implemented to achieve an effective parallelism of 5 variable nodes. The pipelined architecture achieves an improvement of  $\sim 0.75$  dB in decoding performance over the single Gaussian decoder of degree 3 with an overall design throughput of 550 Ksymbols/sec.

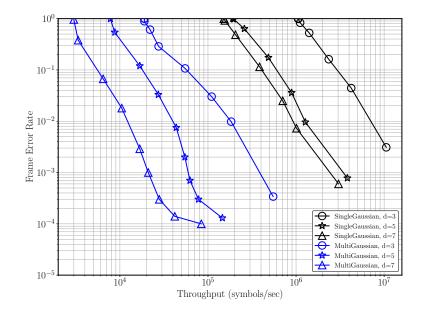

In the final part of the thesis, we further explore the design space and develop complex LDLC decoder designs for higher degrees. We characterize the decoding performance of these decoders and present the design throughputs for different architectures on the target FPGA. Based on these results, we provide insights that will help users to select the most suitable LDLC decoder for a particular application. However this is attained with additional hardware cost and reduced design throughput. A single-Gaussian decoder of degree 7 achieved an FER improvement of 0.75 dB over a single-Gaussian decoder of degree 3 with a throughput of 3.03 Msymbols/sec. The multi-Gaussian Gaussian decoder of degree 7 (with two components in the Gaussian mixture) attains 1.75 dB improvement in FER over the multi-Gaussian decoder of degree 3, and its overall design throughput is  $\sim 84$  Ksymbols/sec. From a broader perspective, the LDLC decoders with higher degrees and larger mixture messages provide a significant improvement in decoding performance. For ultra-reliable applications, a multi-Gaussian decoder of degree 7 is most suitable while for a very high throughput requirement single-Gaussian decoder of degree 3 is the best choice.

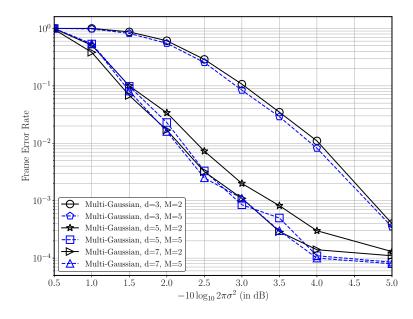

We also characterize the performance of multi-Gaussian decoders where the Gaussian mixture messages contain more than two components. Based on the results, the multi-Gaussian decoder with mixture messages that contain 5 components gain approximately  $\sim 0.1 - 0.2$  dB (for degree 3 and 7) and  $\sim 0.3$  dB (for degree 5) over multi-Gaussian decoder where mixture messages have only two components.

#### Acknowledgements

I would like to take this opportunity to thank the people who are very important in my journey to complete this research work and thesis.

Foremost, I must thank my supervisors Professor Gaudet and Professor Mitran for their continuous support and guidance in my Ph.D. study and research. Their smart inputs, excellent guidance and constant encouragement helped me immensely during my research and writing of the thesis. I have learned so much from working with them and I truly believe these learnings will help me to succeed in my future endeavours. Their expert technical supervision is truly motivating for any student. I highly recommend Prof. Gaudet and Prof. Mitran as supervisors.

I would like to thank my all the committee members, Professor Khandani, Professor Melek, Professor Aagaard for their valuable inputs during my comprehensive exam and thereafter, for taking the time to read my thesis and attend my defense. A special thanks to Prof. Aagaard, for finding time to discuss the data flow and architectural optimizations for the decoder hardware. These insightful discussions were very important to improve the decoder architecture in order to achieve higher design throughput. Furthermore, I would like to express my gratitude to Prof. Matthieu Arzel for accepting to serve as the external examiner for my thesis defense. I must thank all the fellow students who contributed to my learning and a joyful graduate experience, including Meysam Shahrbaf, Subhajit, Ahmed Wagdy, Hai and Kazem. I am also thankful to the ECE computer support staff, and administrative staff at the University of Waterloo. In particular, I am grateful to Phil Regier for all of his help with CAD tool support. I would like to thank the Natural Sciences and Engineering Research Council of Canada (NSERC) for the funding provided for this research and CMC Microsystems for providing the essential CAD tools.

I would like to thank my family members; my parents, parents-in-law, brothers and sisters for their unceasing support and encouragement. Finally, I would like to thank you my husband, Prateek and my son, Daksh who have experienced several ups and downs with me for last several years. Without their tremendous understanding and constant motivation, it would be impossible for me to complete my PhD journey.

# Dedication

To

my PAPA,

$my\ husband,\ Prateek$

& my son, Daksh.

# **Table of Contents**

| Li | st of | Figure | es                                                        | xii |

|----|-------|--------|-----------------------------------------------------------|-----|

| Li | st of | Tables | 5                                                         | xxi |

| 1  | Intr  | oducti | on                                                        | 1   |

|    | 1.1   | Motiva | ation and Contributions                                   | 2   |

|    | 1.2   | Thesis | Outline                                                   | 3   |

| 2  | Lite  | rature | Survey                                                    | 5   |

|    | 2.1   | Chann  | el Capacity and Channel Codes                             | 5   |

|    |       | 2.1.1  | Codes for Binary Channels                                 | 5   |

|    |       | 2.1.2  | Codes for Additive White Gaussian Noise Channels $\hdots$ | 6   |

|    | 2.2   | LDLC   | and Related Codes                                         | 6   |

|    |       | 2.2.1  | Block Codes                                               | 6   |

|    |       | 2.2.2  | Low-Density Parity-Check Codes                            | 9   |

|    |       | 2.2.3  | Low-Density Lattice Codes                                 | 12  |

|    | 2.3   | Param  | eters for LDLC Code Design                                | 15  |

|    |       | 2.3.1  | Constraint Matrix                                         | 15  |

|    |       | 2.3.2  | Distance from Channel Capacity                            | 17  |

|    |       | 2.3.3  | Generating Sequence                                       | 17  |

|    | 2.4   | LDLC   | Decoding for the Additive White Gaussian Noise Channel    | 18  |

|   | 2.5  | LDLC Deco    | ders in the Literature                                                     | 24 |

|---|------|--------------|----------------------------------------------------------------------------|----|

|   |      | 2.5.1 Sam    | pled PDF LDLC decoder                                                      | 25 |

|   |      | 2.5.2 Para   | metric LDLC decoders                                                       | 25 |

|   | 2.6  | Summary      |                                                                            | 34 |

| 3 | Sing | gle-Gaussia  | n LDLC Decoder Implementation                                              | 36 |

|   | 3.1  | Selection of | an LDLC Decoder for Hardware Implementation                                | 36 |

|   | 3.2  | Iterative De | coding for the single-Gaussian LDLC decoder                                | 40 |

|   |      | 3.2.1 Initia | alization                                                                  | 40 |

|   |      | 3.2.2 Basic  | c Iteration: Check Node Message                                            | 41 |

|   |      | 3.2.3 Basic  | c Iteration: Variable Node Message                                         | 42 |

|   |      | 3.2.4 Fina   | l Decision                                                                 | 45 |

|   | 3.3  | Frame Error  | Rate to Measure the Decoder Performance                                    | 45 |

|   | 3.4  | Optimizatio  | ns to Reduce the Decoder Complexity                                        | 46 |

|   |      | 3.4.1 Fixe   | d-Point Arithmetic for Hardware Implementation                             | 46 |

|   |      | 3.4.2 Mini   | mum Variance                                                               | 47 |

|   |      | 3.4.3 Varia  | ances Measured with Respect to the Channel Variance                        | 48 |

|   |      | 3.4.4 Opti   | mizations for the Coefficient Computation at the Variable nodes            | 48 |

|   |      | 3.4.5 Num    | ber of Decoding Iterations                                                 | 50 |

|   | 3.5  | Fixed-Point  | Quantization Study                                                         | 50 |

|   |      | 3.5.1 App    | roximation of Non-Linear Functions                                         | 50 |

|   |      | -            | mal Word Length and Newton-Raphson (NR) Iterations for Fixed-<br>t decoder | 54 |

|   | 3.6  | _            | der FPGA Implementation                                                    | 57 |

|   | 3.7  |              | -<br>                                                                      | 65 |

|   |      |              |                                                                            |    |

| 4 | $\mathbf{M}\mathbf{u}$ | lti-Gau | ussian LDLC Decoder                                                                | 72  |

|---|------------------------|---------|------------------------------------------------------------------------------------|-----|

|   | 4.1                    | Select  | ion of an Appropriate Decoder for the Hardware Implementation                      | 73  |

|   | 4.2                    | Iterati | ive Decoding for Multi-Gaussian LDLC Decoder $(M = 2)$                             | 73  |

|   |                        | 4.2.1   | Initialization                                                                     | 73  |

|   |                        | 4.2.2   | Basic Iteration: Check Node Message                                                | 74  |

|   |                        | 4.2.3   | Basic Iteration: Variable Node Message                                             | 76  |

|   |                        | 4.2.4   | Final Decision                                                                     | 77  |

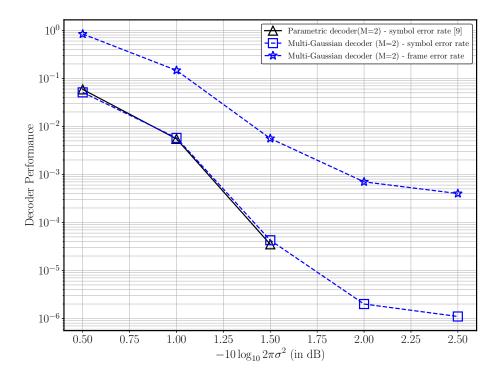

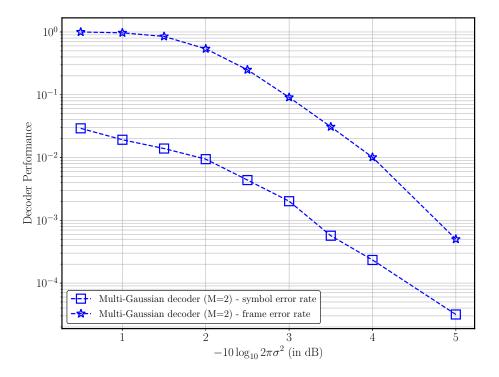

|   | 4.3                    | Frame   | e Error Rate to Measure the Decoder Performance                                    | 78  |

|   | 4.4                    | Optim   | nizations to Reduce the Decoder Complexity                                         | 80  |

|   |                        | 4.4.1   | Fixed-point Arithmetic for Hardware Implementation                                 | 80  |

|   |                        | 4.4.2   | Number of Decoding Iterations                                                      | 81  |

|   |                        | 4.4.3   | Final Decision in Iterative Decoding Algorithm                                     | 82  |

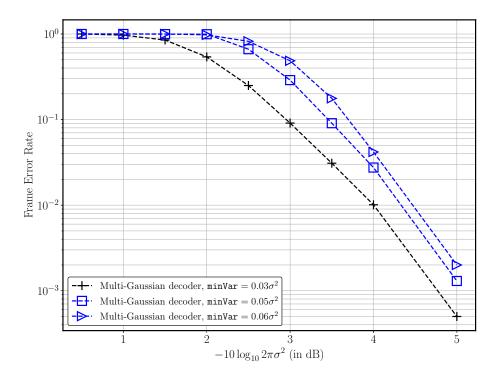

|   |                        | 4.4.4   | Minimum Variance                                                                   | 83  |

|   |                        | 4.4.5   | Variance Measured with Respect to the Channel Variance                             | 84  |

|   |                        | 4.4.6   | Optimizations in the Coefficient Computation at the Variable Nodes                 | 84  |

|   | 4.5                    | Fixed   | Point Quantization Study                                                           | 85  |

|   |                        | 4.5.1   | Approximation of Non-Linear Functions                                              | 85  |

|   |                        | 4.5.2   | Optimal word length and Newton-Raphson (NR) iterations for fixed-<br>point decoder | 87  |

|   | 4.6                    | LDLC    | Decoder FPGA Implementation                                                        | 87  |

|   | 4.7                    | Comp    | arison of Single-Gaussian and Multi-Gaussian LDLC Decoder $(M = 2)$                | 93  |

|   | 4.8                    | Summ    | nary                                                                               | 94  |

| 5 | Pus                    | shing t | he Design Limits                                                                   | 102 |

|   | 5.1                    | Single  | -Gaussian Decoders                                                                 | 103 |

|   |                        | 5.1.1   | Single-Gaussian Decoder, $d = 5$                                                   | 103 |

|   |                        | 5.1.2   | Single-Gaussian Decoder, $d = 7$                                                   | 105 |

|   | 5.2                    | Perfor  | mance and Throughput Comparison of Single-Gaussian Decoders                        | 107 |

|    | 5.3   | Multi-  | Gaussian Decoders                                       | 108 |

|----|-------|---------|---------------------------------------------------------|-----|

|    |       | 5.3.1   | Multi-Gaussian Decoder, $d = 5$ and $M = 2$             | 108 |

|    |       | 5.3.2   | Multi-Gaussian Decoder, $d = 7$ and $M = 2$             | 110 |

|    |       | 5.3.3   | Multi-Gaussian Decoder, $d = 3$ and $M = 5$             | 111 |

|    |       | 5.3.4   | Multi-Gaussian Decoder, $d = 5$ and $M = 5$             | 111 |

|    |       | 5.3.5   | Multi-Gaussian Decoder, $d = 7$ and $M = 5$             | 112 |

|    | 5.4   | Perfor  | mance and Throughput Comparisons                        | 112 |

|    |       | 5.4.1   | Single-Gaussian vs. Multi-Gaussian Decoders             | 112 |

|    | 5.5   | Summ    | ary                                                     | 113 |

| 6  | Con   | cludin  | ng Remarks                                              | 135 |

|    | 6.1   | Summ    | ary of Contributions and Conclusions                    | 135 |

|    | 6.2   | Direct  | ions for Future Work                                    | 137 |

| Re | efere | nces    |                                                         | 139 |

| Al | PPE   | NDICI   | ES                                                      | 147 |

| A  | Der   | ivatior | n of the Squared Distance Equation                      | 148 |

| в  | Nev   | vton R  | aphson Approximation for a Reciprocal Function          | 151 |

| С  | Exa   | mple l  | Exponential Approximation in Fixed Point Representation | 152 |

# List of Figures

| 2.1  | Schematic of a general communication channel                                                                                                                                                                                                                        | 7  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Bipartite graph representation of the example $(4,8)$ LDPC parity-check matrix.                                                                                                                                                                                     | 11 |

| 2.3  | Graphical illustration of an example 2-dimensional lattice with basis vectors $\underline{g}_1$ and $\underline{g}_2$ .                                                                                                                                             | 14 |

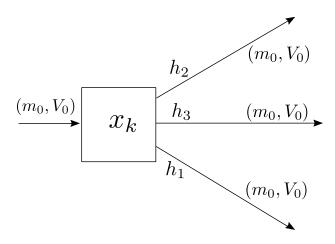

| 2.4  | Initialization - a variable node sends the received channel PDF to all the connected check nodes.                                                                                                                                                                   | 20 |

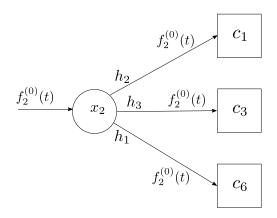

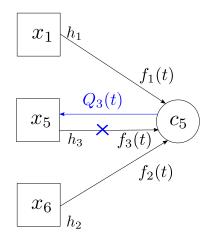

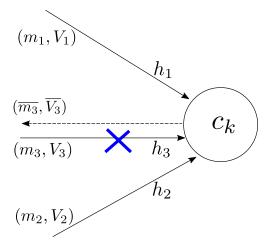

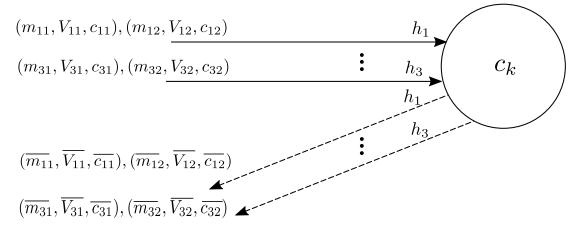

| 2.5  | Check node operation - the outgoing message on the edge with weight $h_3$ is computed with all the incoming messages, except the one on edge with weight $h_3$ .                                                                                                    | 22 |

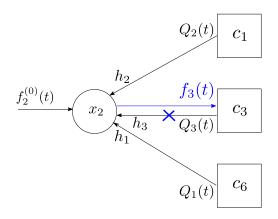

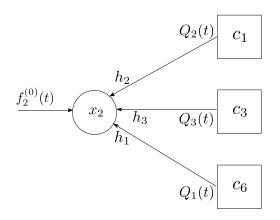

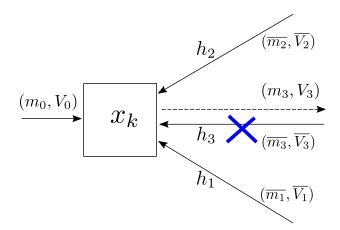

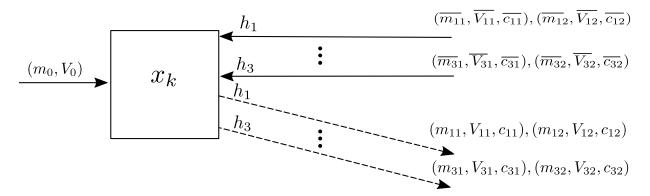

| 2.6  | Variable node operation - the outgoing message on the edge with weight $h_3$ is<br>computed with channel message and all the incoming check node messages,<br>except the one on edge with weight $h_3$ .                                                            | 23 |

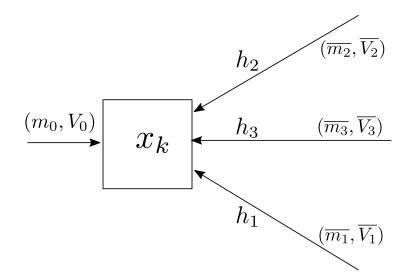

| 2.7  | Final decision in Iterative decoding                                                                                                                                                                                                                                | 24 |

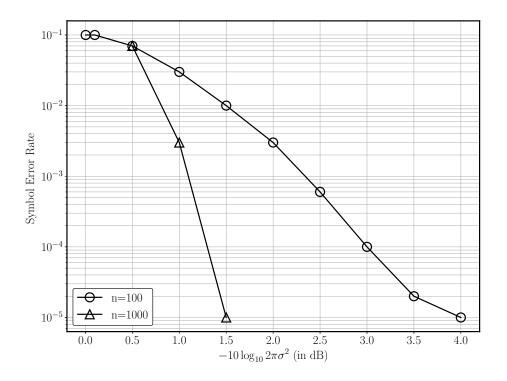

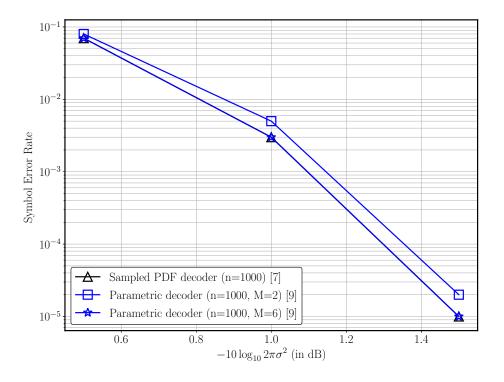

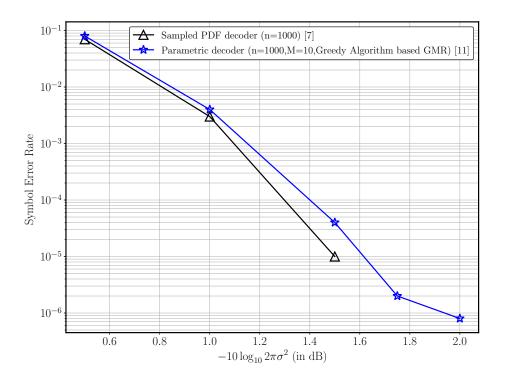

| 2.8  | Symbol error rate versus distance from capacity, $-10 \log 102\pi e^2$ (in dB) of<br>the sampled PDF LDLC decoder for block length, $n = 100$ , $d = 5$ and<br>n = 1000, $d = 7$ with 200 decoding iterations simulated by Sommer et al.                            | 26 |

| 2.9  | Symbol error rate vs. distance from capacity, $-10 \log_{10} 2\pi e \sigma^2$ (in dB) for<br>the parametric LDLC decoder using Gaussian mixture reduction method<br>based on greedy algorithm with $n = 1000$ , $d = 7$ and number of decoding<br>iterations = 200. | 32 |

| 2.10 | Symbol error rate vs. the distance from capacity, $-10 \log_{10} 2\pi e \sigma^2$ , (in dB) using Gaussian mixture reduction method based on merging Gaussians in a range for $n = 1000$ , $d = 7$ with number of decoding iterations = 200                         | 34 |

|      | range for $n = 1000$ , $a = 1$ with number of decoding iterations = 200                                                                                                                                                                                             | 9  |

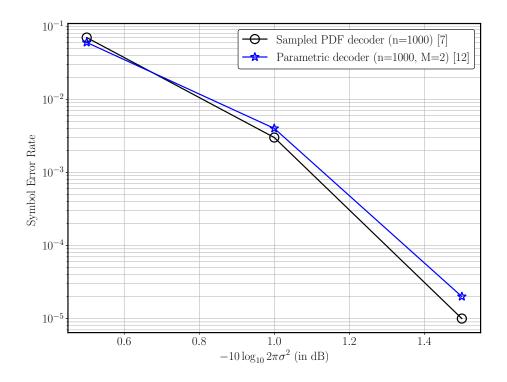

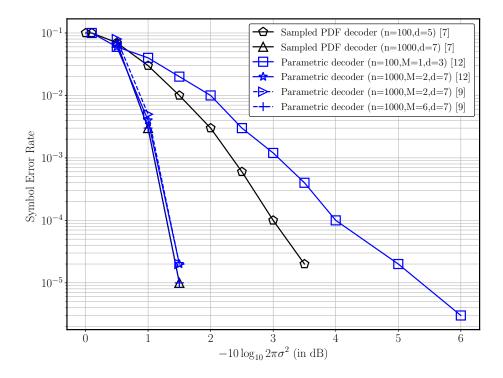

| 3.1  | Comparison of symbol error rate vs. distance from capacity, $-10 \log_{10} 2\pi e \sigma^2$<br>(in dB) between the sampled PDF decoder for block length, $n = 1000$ , $d = 7$<br>and a parametric decoder for $n = 1000$ , number of components $(M) = 10$<br>and $d = 6$ . | 38 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Comparison of performance between the sampled PDF and parametric LDLC decoders for block length 100 and 1000                                                                                                                                                                | 39 |

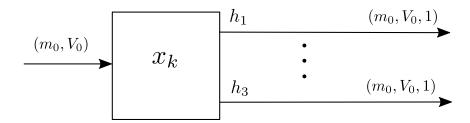

| 3.3  | Initialization in iterative decoding - a variable node sends the message re-<br>ceived from the channel to all connected check nodes.                                                                                                                                       | 41 |

| 3.4  | Illustration of all the incoming messages, and the outgoing message along<br>the edge with weight $h_3$ at a check node. The outgoing message on the edge<br>with weight $h_3$ is obtained by convolving all the incoming messages except<br>the one on this edge.          | 42 |

| 3.5  | Illustration of all the incoming messages and the outgoing message along the edge with weight $h_3$ at a variable node, $x_k$ . Here the outgoing message on the edge with weight $h_3$ is obtained by multiplying all the incoming messages except the one on this edge.   | 43 |

| 3.6  | Final decision at variable node $x_k$ - channel message and all the incoming check node messages are multiplied (without omitting any)                                                                                                                                      | 44 |

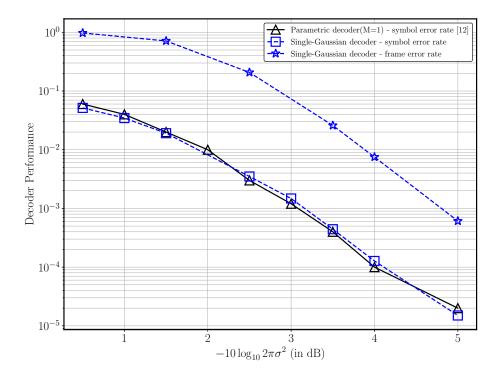

| 3.7  | Comparison of symbol error rate between single-Gaussian LDLC decoder<br>and parametric decoder, $M = 1$ for $n = 100$ and $d=3$ . The corresponding<br>frame error rate for the single-Gaussian LDLC decoder is also shown                                                  | 47 |

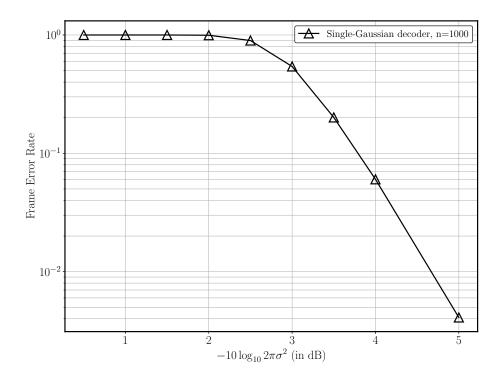

| 3.8  | Frame error rate of the single-Gaussian LDLC decoder for $n = 1000$ and $d = 3$ .                                                                                                                                                                                           | 48 |

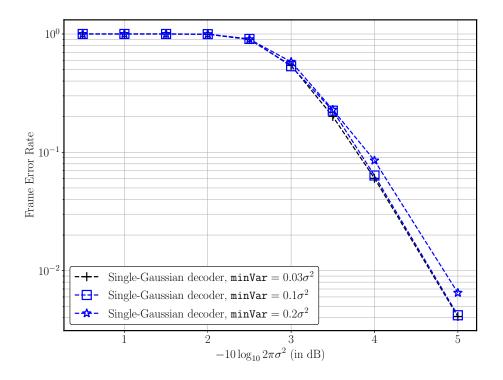

| 3.9  | Frame error rate of the single-Gaussian decoder with different minVar values for $n = 1000$ and $d = 3$                                                                                                                                                                     | 49 |

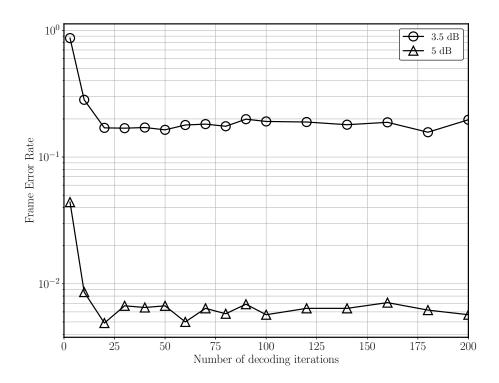

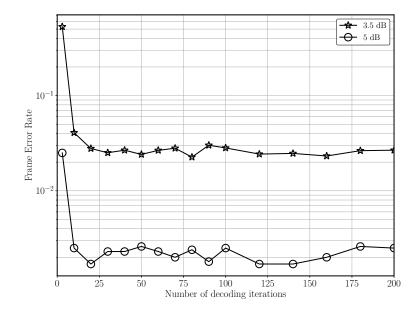

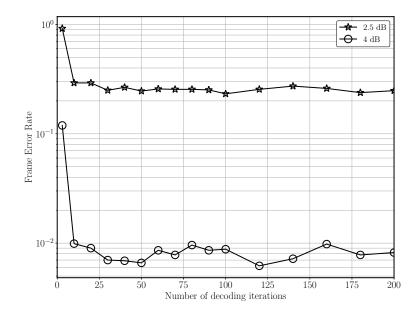

| 3.10 | Performance of the single-Gaussian decoder for different number of decoding iterations at distance from capacity of 3.5 dB and 5 dB for $n = 1000$ and $d = 3$ .                                                                                                            | 51 |

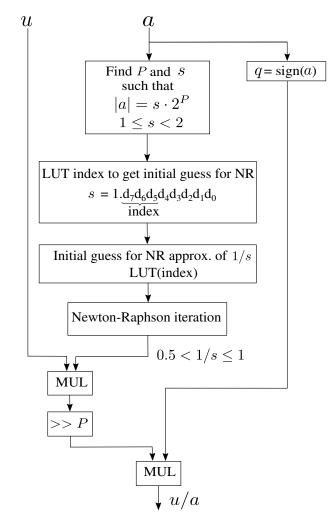

| 3.11 | Flow-chart to demonstrate the division function approximation in fixed-<br>point arithmetic using Newton-Raphson (NR) method, used at the variable<br>nodes.                                                                                                                | 52 |

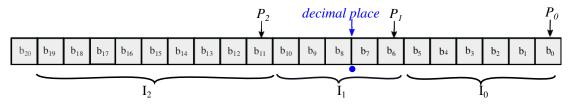

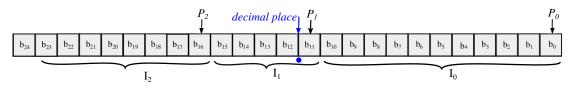

| 3.12 | Diagram to show the relationship between $a$ and $I_0$ , $I_1$ and $I_2$ as used in the approximation of the exponential function in fixed-point arithmetic at the variable nodes.                                                                                          | 55 |

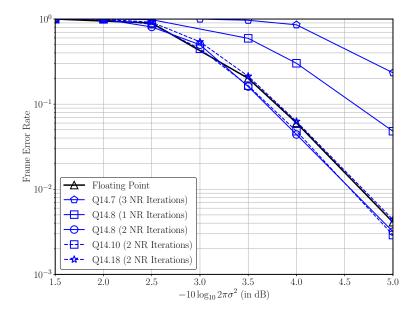

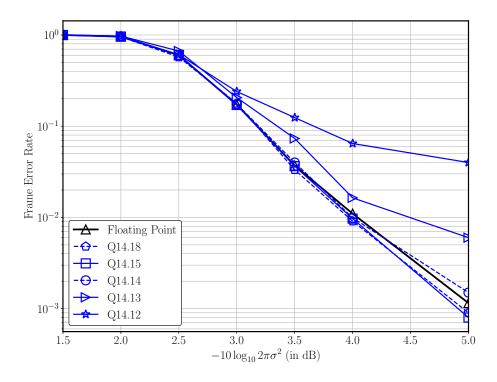

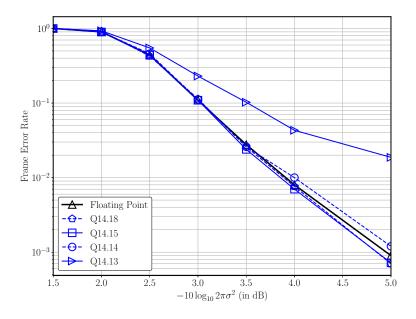

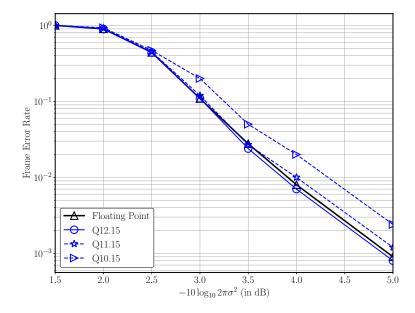

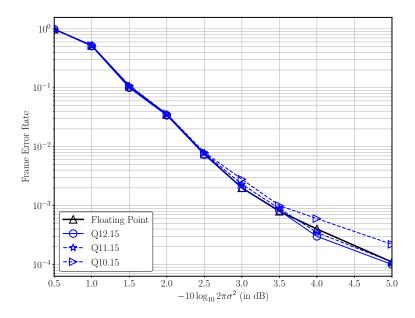

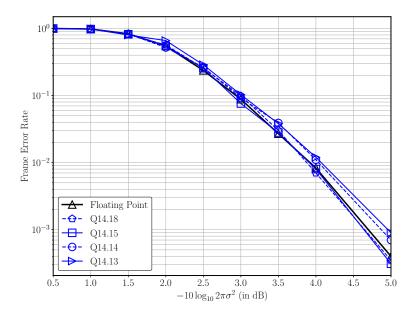

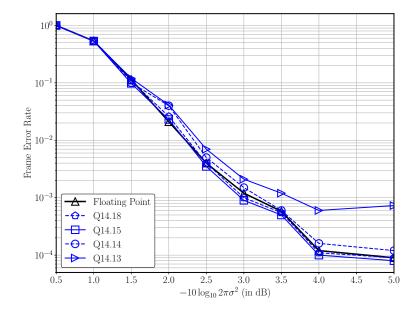

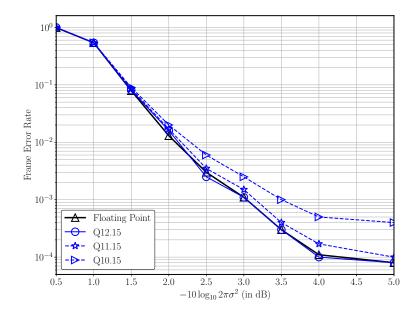

| 3.13 | FER for different numbers of fractional bits and Newton-Raphson iterations<br>for $n = 1000$ , $d = 3$ where $-10 \log_{10} 2\pi e \sigma^2$ is distance from the theoretical<br>noise limit.                                                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

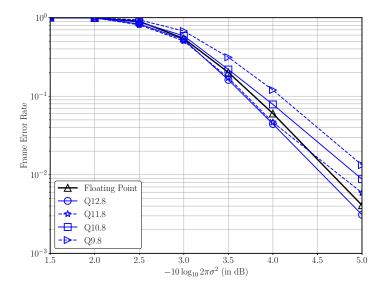

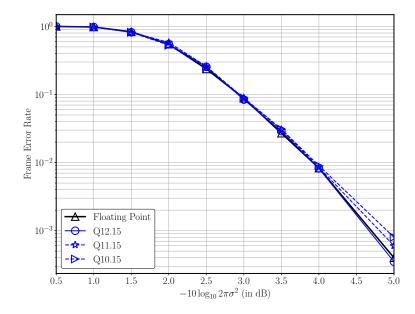

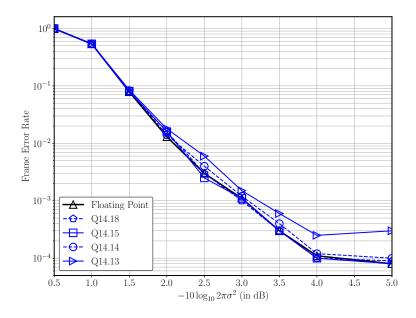

| 3.14 | Frame error rate for different numbers of integer bits and two Newton-Raphson iterations with $n = 1000, d = 3. \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                 |

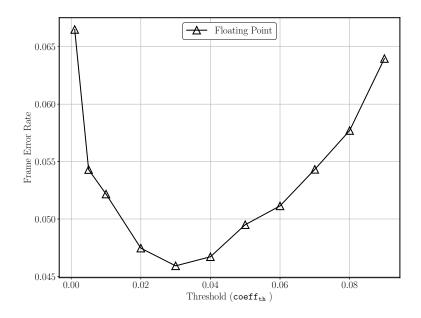

| 3.15 | Effect of removing small coefficients from Gaussian mixture in floating point LDLC decoder at $-10 \log_{10} 2\pi e \sigma^2 = 4 \text{ dB}$ , $n = 1000 \text{ and } d = 3. \dots$                                                                                                                                                                                                                                                                                            |

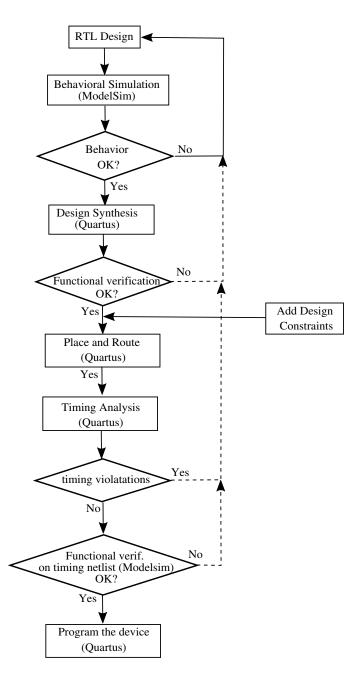

| 3.16 | The design and verification flow                                                                                                                                                                                                                                                                                                                                                                                                                                               |

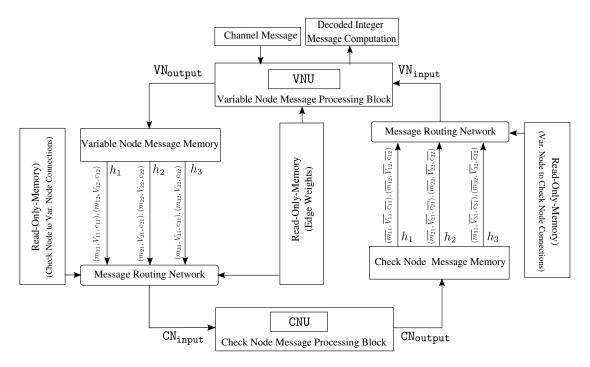

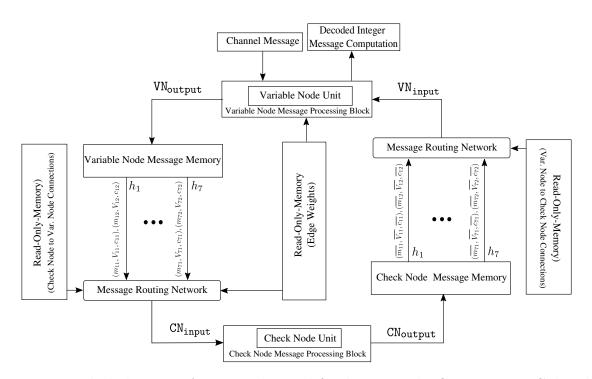

| 3.17 | Block diagram of a two-node serial single-Gaussian LDLC decoder with a single check node and a single variable node (architecture A).                                                                                                                                                                                                                                                                                                                                          |

| 3.18 | Block diagram for the mean computation of the outgoing messages at the check node. The mean is computed by first multiplying each incoming message with its respective edge weight (except the one on the outgoing edge), summing the results and further dividing the result of the summation by the outgoing edge weight and a sign flip.                                                                                                                                    |

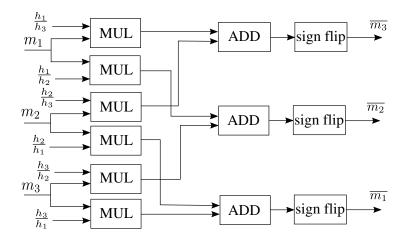

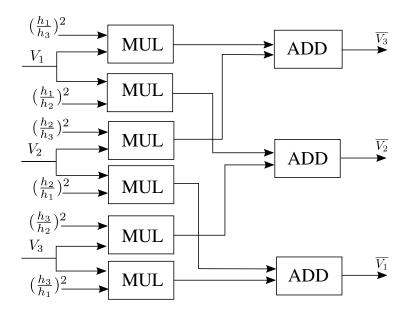

| 3.19 | Block diagram for the variance computation of the outgoing check node messages.                                                                                                                                                                                                                                                                                                                                                                                                |

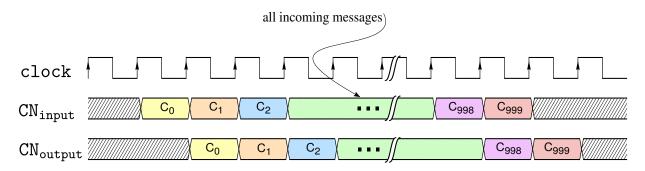

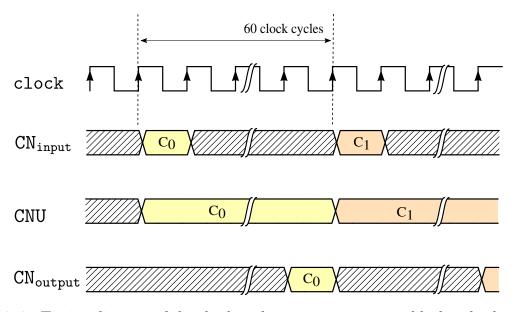

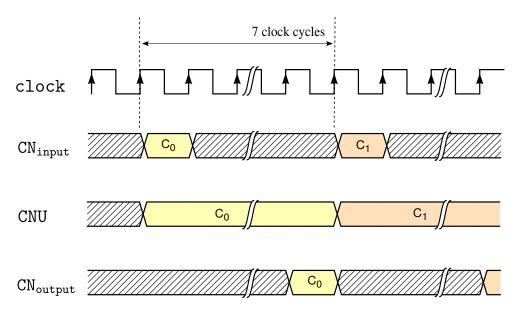

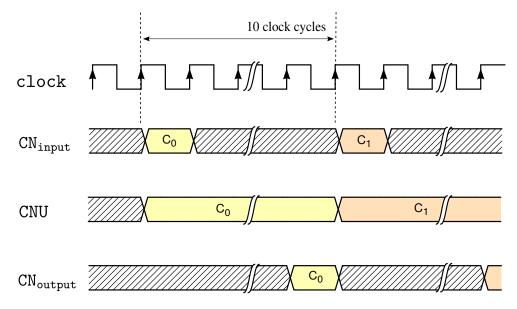

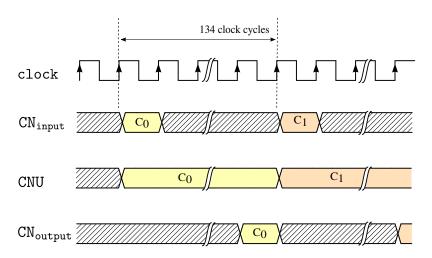

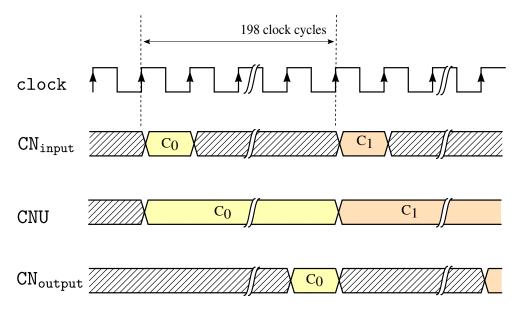

| 3.20 | Timing diagram of the check node message processing block in architecture A , B and C.                                                                                                                                                                                                                                                                                                                                                                                         |

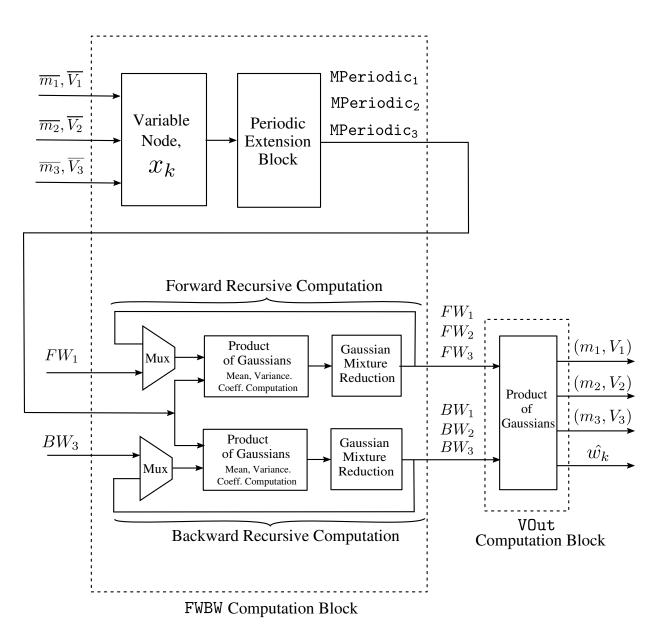

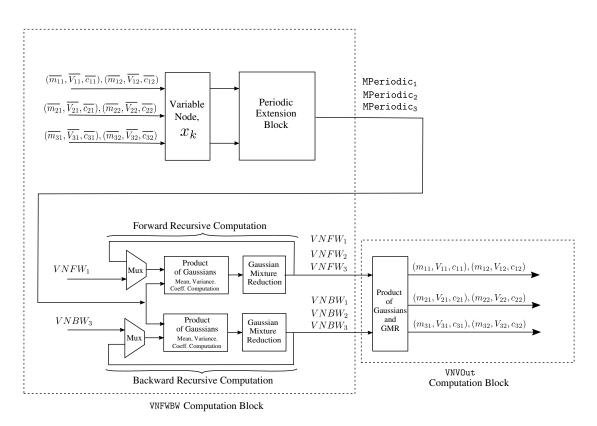

| 3.21 | High-level architecture of a variable node unit (VNU) in single-Gaussian de-<br>coder with $d = 3$ . At a variable node, $x_k$ , the incoming check node messages<br>are periodically extended, $FW_{\ell}$ and $BW_{\ell}$ for $\ell = 1, 2, d$ are computed<br>in FWBW computation block and finally the outgoing variable node messages,<br>$(m_l, V_l)$ for $\ell = 1, 2, d$ and estimate for transmitted codeword, $\hat{w}_k$ is ob-<br>tained in VOut computation block |

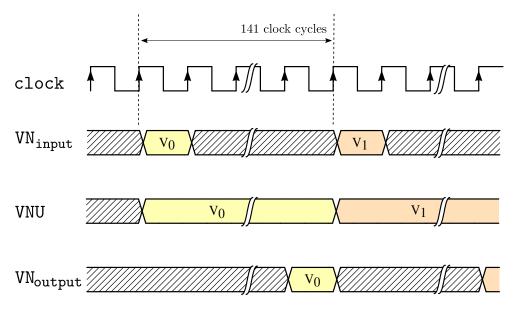

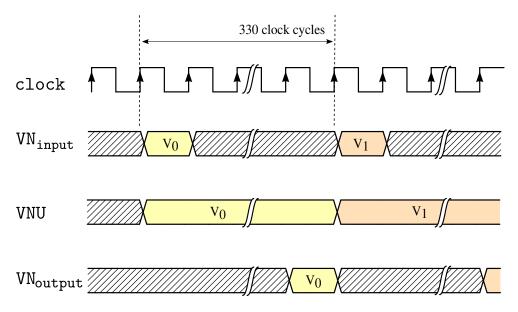

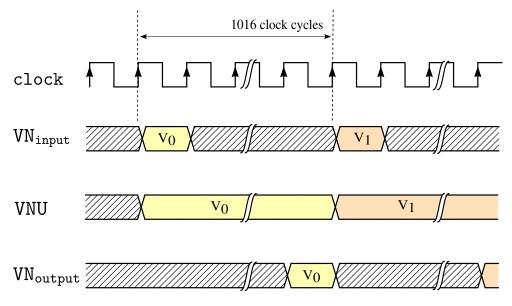

| 3.22 | Timing diagram of the variable node message processing block in architec-<br>ture A                                                                                                                                                                                                                                                                                                                                                                                            |

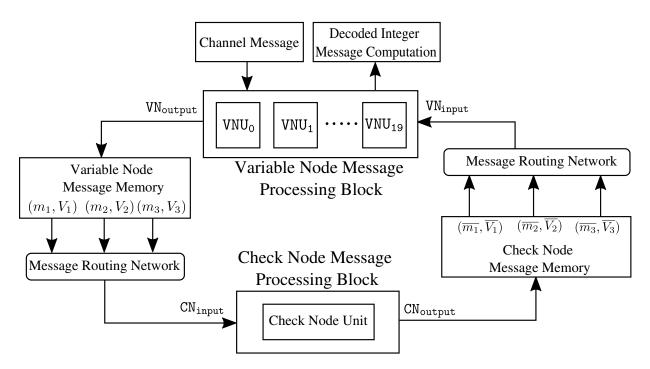

| 3.23 | Top-level block diagram of the LDLC decoder with one check node and 20 parallel variable node units (architecture B).                                                                                                                                                                                                                                                                                                                                                          |

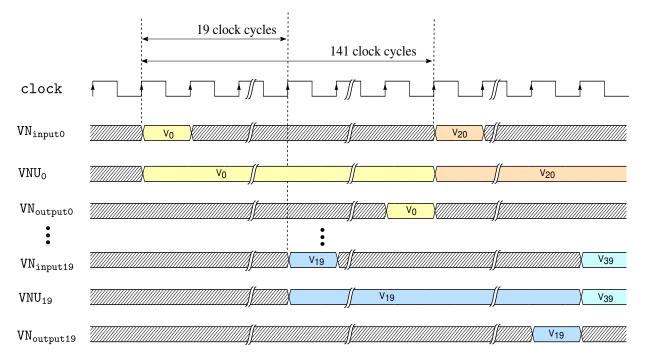

| 3.24 | Timing diagram of the variable node message processing block in architec-<br>ture B                                                                                                                                                                                                                                                                                                                                                                                            |

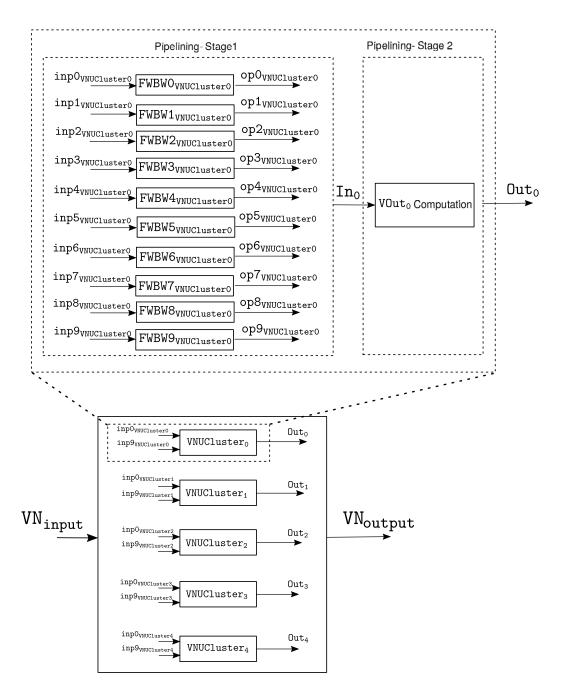

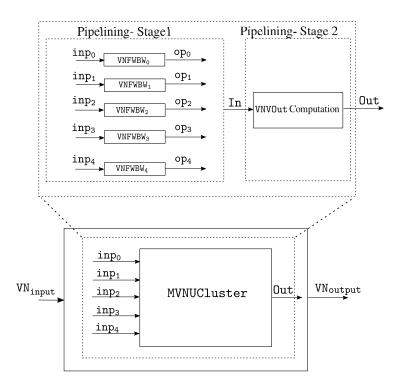

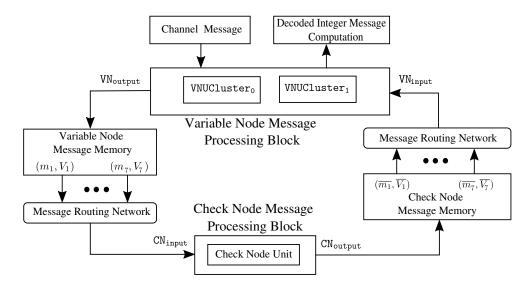

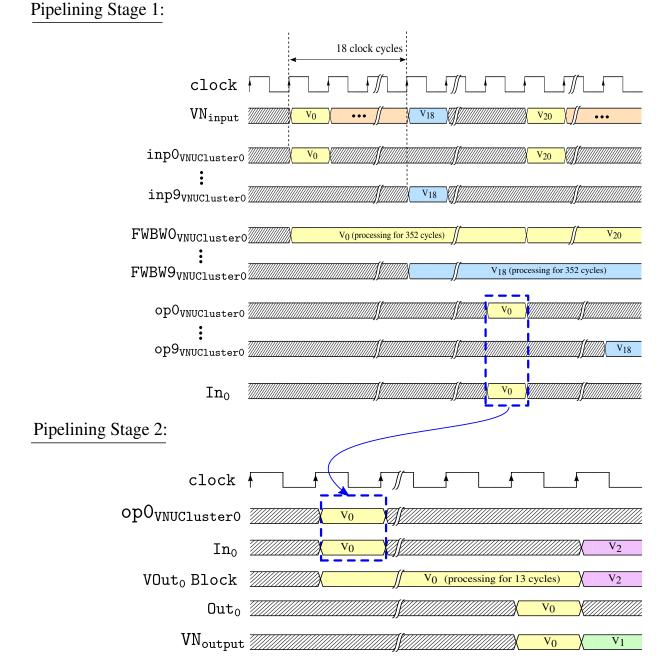

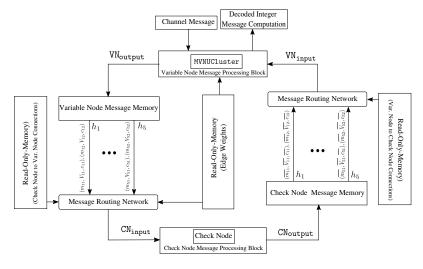

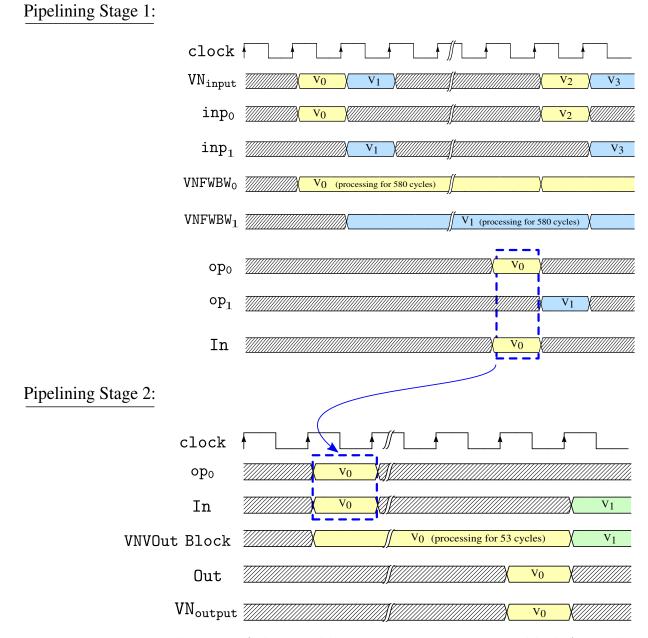

| 3.25 | High-level diagram of the variable node message processing block used in ar-<br>chitecture C, that consists of 5 VNUCluster blocks. The two stage pipelining<br>used in VNUCluster blocks is shown specifically for VNUCluster <sub>0</sub>                                                                                                                                                                                                                                    |

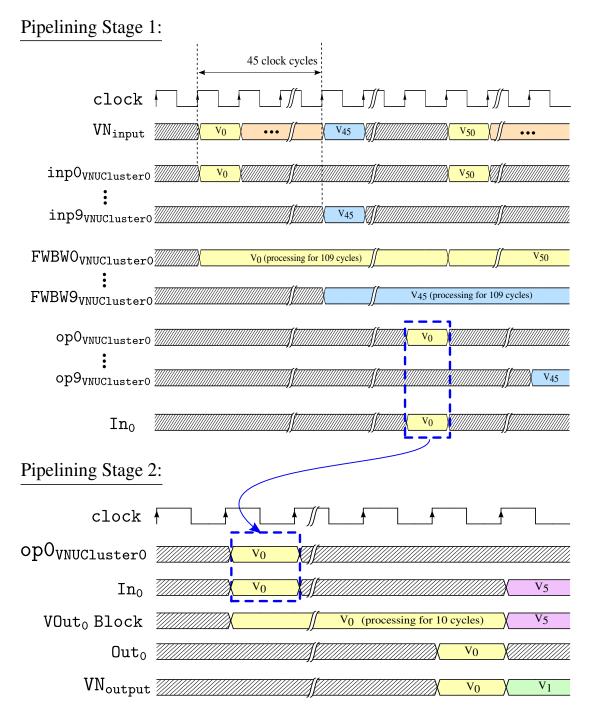

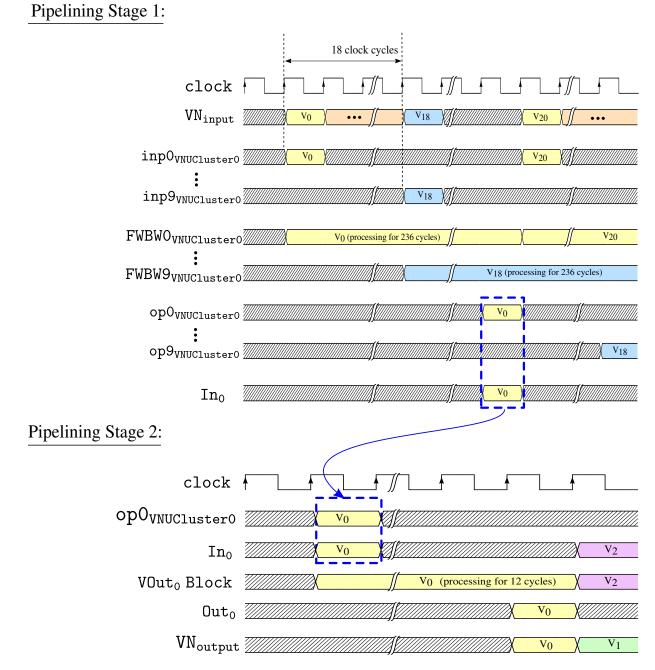

| 3.26 | Timing diagram of VNUCluster block used in variable node message processing block of architecture C. The waveforms are shown particularly for $VNUCluster_0$ block.                                                                                                                                    | 69 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

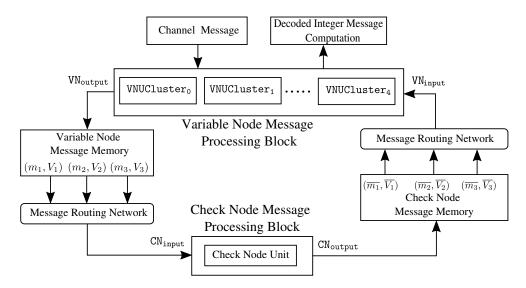

| 3.27 | Top-level architecture for the LDLC decoder with a single check node and with two-stage pipelining to achieve an effective parallelism equivalent to 50 variable nodes (architecture C).                                                                                                               | 70 |

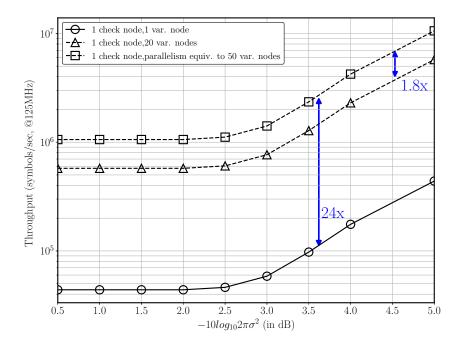

| 3.28 | Throughput comparison of different decoder architectures for $n = 1000$ and clock frequency of 125 MHz.                                                                                                                                                                                                | 71 |

| 4.1  | A variable node, $x_k$ sends the message received from the channel to all connected check nodes                                                                                                                                                                                                        | 74 |

| 4.2  | Illustration of all the incoming and the outgoing messages at a check node in multi-Gaussian decoder with $M = 2$ and $d = 3$ .                                                                                                                                                                        | 74 |

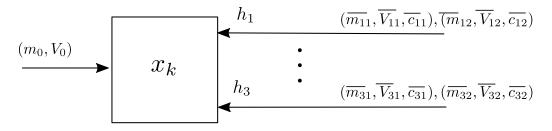

| 4.3  | All the incoming and outgoing messages at a variable node in multi-Gaussian decoder with $M = 2$ and $d = 3$ .                                                                                                                                                                                         | 75 |

| 4.4  | For final decision, the channel message and all the incoming messages to a variable node, $x_k$ , are multiplied.                                                                                                                                                                                      | 75 |

| 4.5  | Frame error rate and symbol error rate performance of a multi-Gaussian LDLC decoder $(M = 2)$ for block length $n = 1000$ and $d = 7$                                                                                                                                                                  | 78 |

| 4.6  | Frame error rate and symbol error rate performance of a multi-Gaussian LDLC decoder $(M = 2)$ for block length $n = 1000, d = 3$ , and 200 decoding iterations.                                                                                                                                        | 79 |

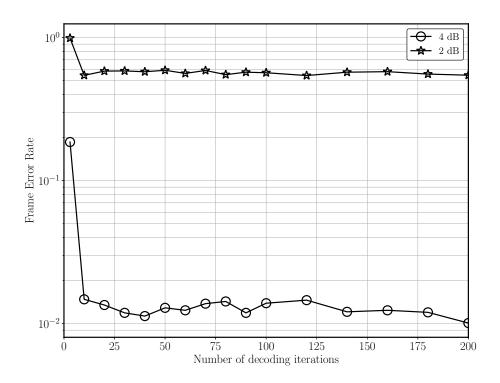

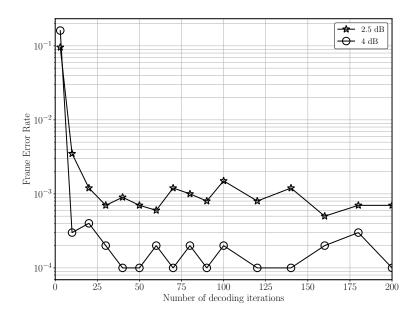

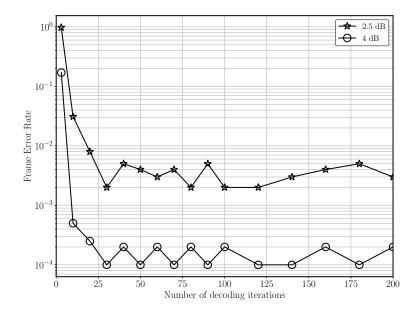

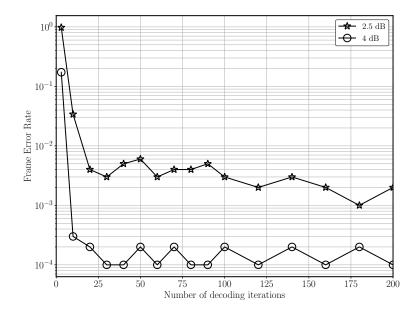

| 4.7  | Frame error rate of the multi-Gaussian decoder (floating-point with no approximations) versus number of decoding iterations for $n = 1000$ and $d = 3$ at distance from capacity of 2 dB ad 4 dB.                                                                                                      | 80 |

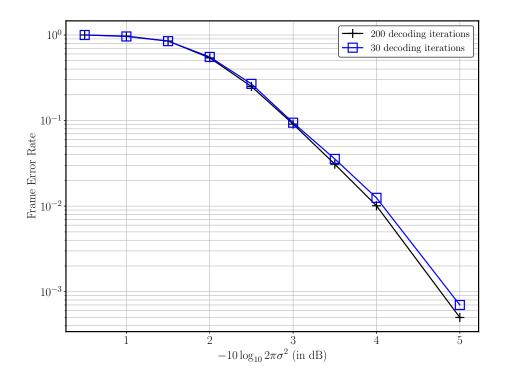

| 4.8  | Frame error rate of a multi-Gaussian decoder (floating-point with no approximations) for $n = 1000$ and $d = 3$ with 200 and 30 decoding iterations.                                                                                                                                                   | 81 |

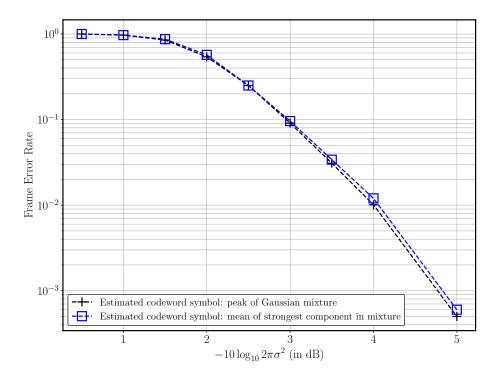

| 4.9  | Frame error rate of a multi-Gaussian decoder using a method for final deci-<br>sion (in iterative decoding) where the mean of the strongest component in<br>the Gaussian mixture is considered as the estimated codeword symbol, $\hat{w}_k$ ,<br>for $n = 1000$ , $d = 3$ and 30 decoding iterations. | 82 |

| 4.10 | Frame error rate of a multi-Gaussian decoder (floating-point) with different minimum variance, minVar values for $n = 1000$ and $d = 3$ .                                                                                                                                                              | 83 |

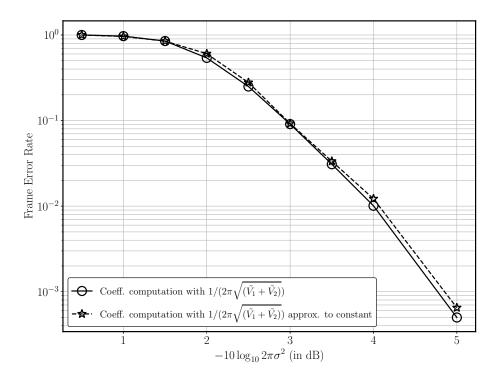

| 4.11 | Frame error rate of a multi-Gaussian decoder (floating-point) for $n = 1000$<br>and $d = 3$ when $\frac{1}{2\pi\sqrt{(\tilde{V}_1 + \tilde{V}_2)}}$ component in the coefficient computation, i.e.,                                          |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (3.6) is approximated to a constant. $\ldots$                                                                                                                                                                                                | 84 |

| 4.12 | Diagram to show the relationship between $a$ and $I_0$ , $I_1$ and $I_2$ , as used in the approximation of the exponential function in fixed-point arithmetic at the variable nodes in the multi-Gaussian decoder.                           | 87 |

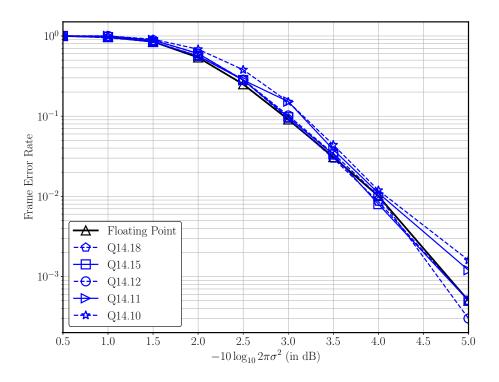

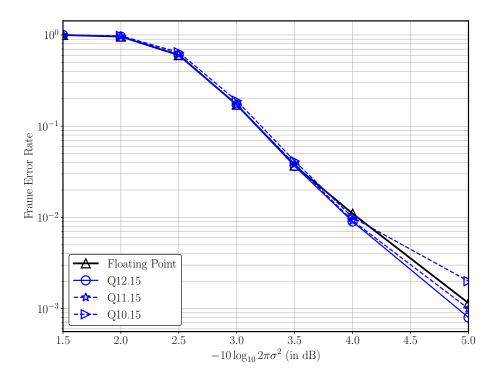

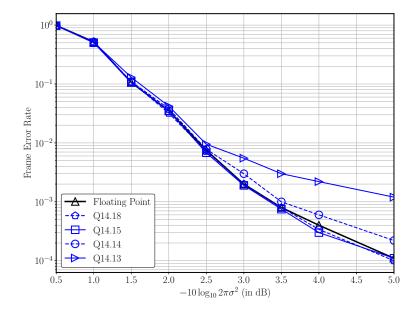

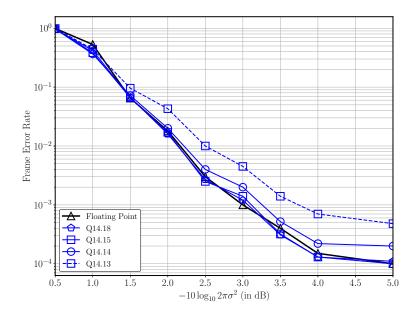

| 4.13 | FER for different numbers of fractional bits and two NR iterations for $n = 1000$ and $d = 3$ where $-10 \log_{10} 2\pi e \sigma^2$ is distance from the theoretical noise limit.                                                            | 88 |

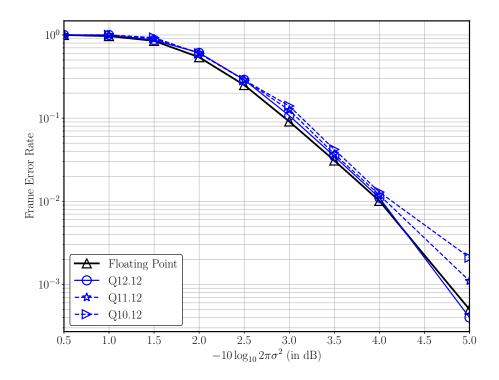

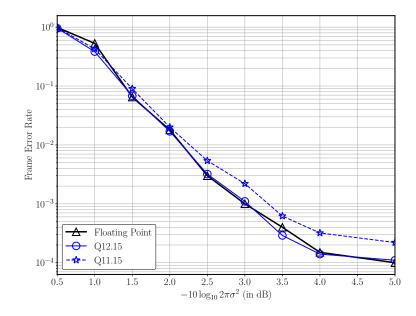

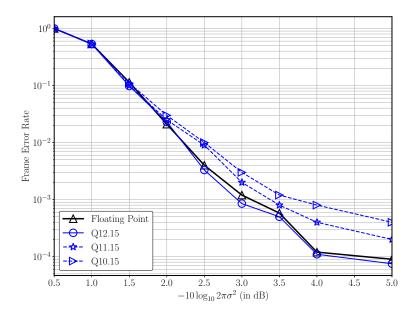

| 4.14 | FER performance of the multi-Gaussian decoder with different numbers of integer bits and two NR iterations for $n = 1000$ and $d = 3. \dots \dots$                                                                                           | 89 |

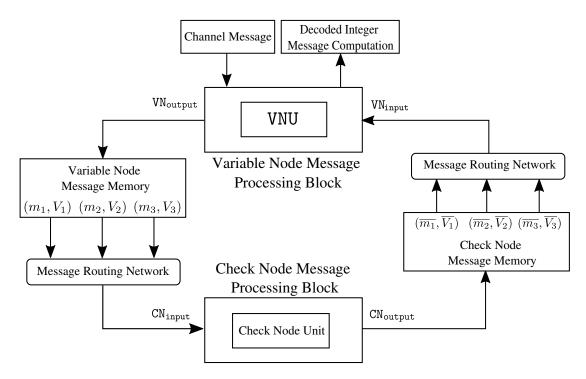

| 4.15 | Block diagram of a two-node serial multi-Gaussian LDLC decoder with one single check node unit, CNU and one single variable node unit, VNU (architecture D)                                                                                  | 90 |

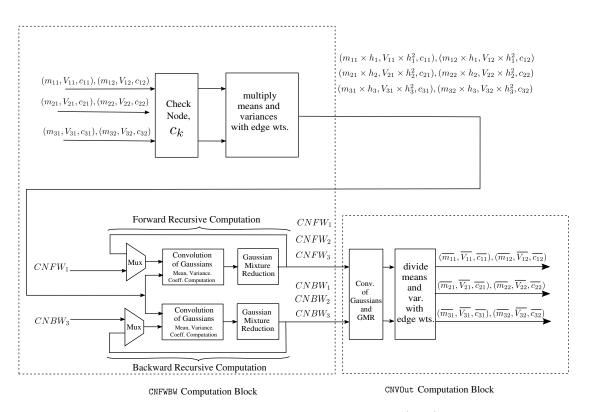

| 4.16 | High-level architecture of a check node unit (CNU) in the multi-Gaussian decoder of degree 3                                                                                                                                                 | 91 |

| 4.17 | Timing diagram of the check node message processing block in both archi-<br>tectures D and E of the multi-Gaussian decoder                                                                                                                   | 92 |

| 4.18 | High-level architecture of a variable node unit (VNU) in multi-Gaussian de-<br>coder of degree 3                                                                                                                                             | 93 |

| 4.19 | Timing diagram of the variable node message processing block in architec-<br>ture D of the multi-Gaussian decoder                                                                                                                            | 94 |

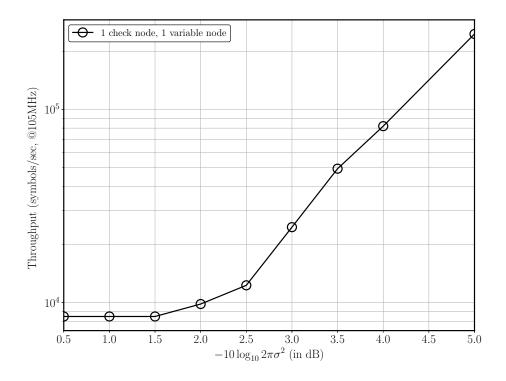

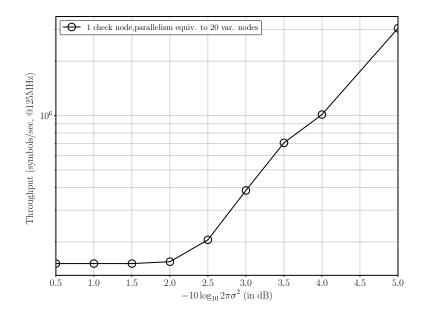

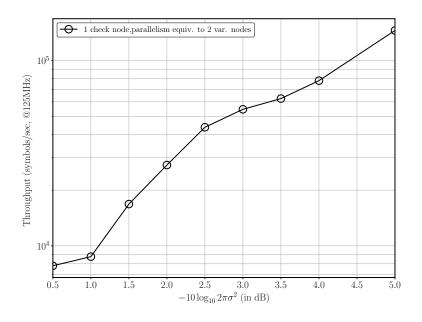

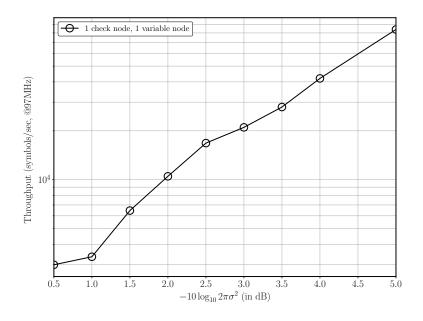

| 4.20 | Throughput of the multi-Gaussian decoder (degree 3) with a single check node and a single variable node                                                                                                                                      | 95 |

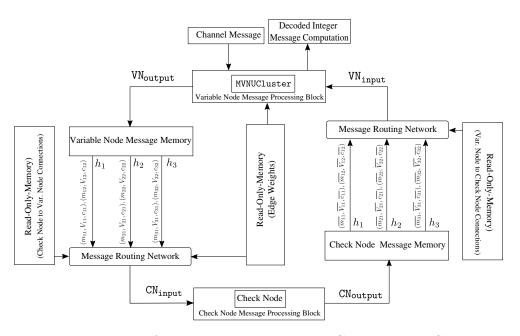

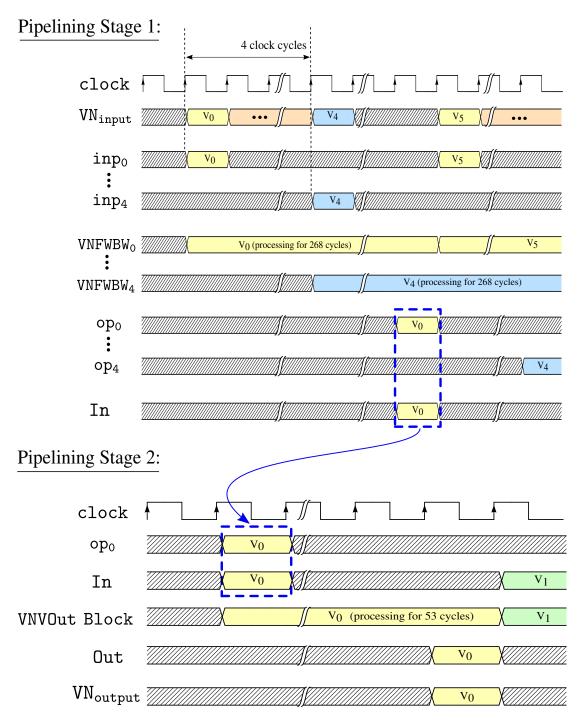

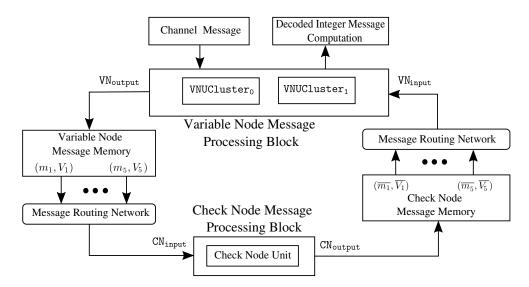

| 4.21 | Block diagram of a partially parallel multi-Gaussian LDLC decoder with one single check node and variable node message processing block with pipelining to achieve an effective parallelism equivalent to 5 variable nodes (architecture E). | 97 |

| 4.22 | Block diagram of two-stage pipelining used in the variable node message processing block (architecture E) of the multi-Gaussian decoder                                                                                                      | 98 |

| 4.23 | Timing diagram of the variable node message processing block in architec-<br>ture E of the multi-Gaussian decoder.                                                                                                                           | 99 |

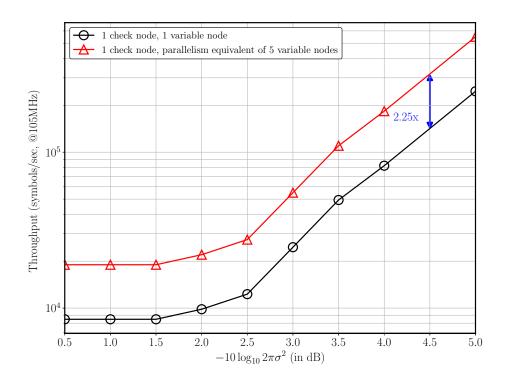

| 4.24 | Throughput comparison of architectures D and E (of the multi-Gaussian LDLC decoder) for block length 1000 and degree 3.                                                                                                          | 100 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

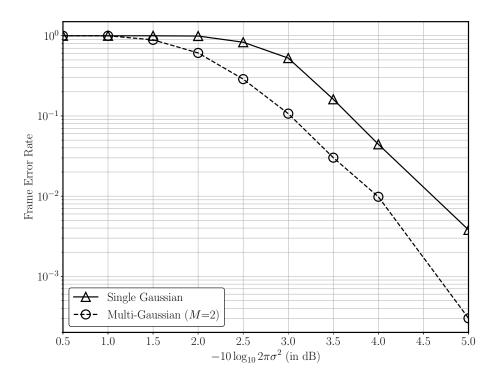

| 4.25 | FER comparison of the single-Gaussian and multi-Gaussian fixed-point LDLC decoder $(M=2)$ implementations for block length of 1000 and degree 3. $$ .                                                                            | 101 |

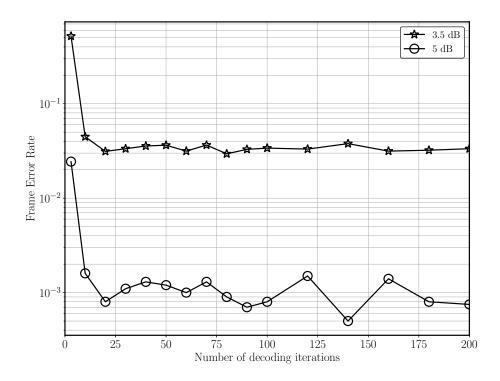

| 5.1  | Performance of the floating-point single-Gaussian decoder for different number of decoding iterations at distance from capacity of 3.5 dB and 5 dB, $n = 1000$ and $d = 5$ .                                                     | 104 |

| 5.2  | Frame error rate comparison between the floating-point decoder (without approximations) and the fixed-point single-Gaussian decoder for different numbers of fractional bits and two NR iterations with $n = 1000$ and $d = 5$ . | 105 |

| 5.3  | Frame error rate of single-Gaussian decoder for different numbers of integer<br>bits and two NR iterations with $n = 1000$ , $d = 5$ (floating-point decoder<br>performance is without any approximation).                       | 106 |

| 5.4  | Top-level architecture for single-Gaussian LDLC decoder of degree 5, with a single check node and two-stage pipelining to achieve an effective parallelism equivalent to 20 variable nodes.                                      | 107 |

| 5.5  | Timing diagram for the check node message processing block in single-Gaussian decoder of degree 5                                                                                                                                | 108 |

| 5.6  | Timing diagram for the variable node message processing block in single-Gaussian decoder of degree 5. The waveforms are shown specifically for <b>VNUCluster</b> <sub>0</sub> block.                                             | 114 |

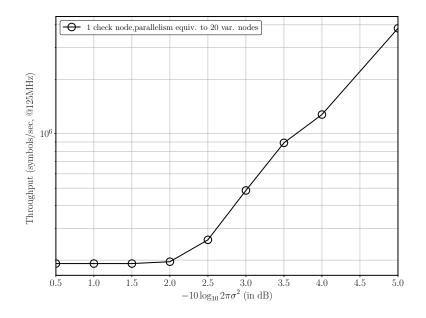

| 5.7  | Throughput of the single-Gaussian decoder of degree 5 for block length 1000.                                                                                                                                                     | 115 |

| 5.8  | Performance of the single-Gaussian decoder (floating-point) versus number<br>of decoding iterations at distance from capacity of 3.5 dB and 5 dB for<br>n = 1000 and $d = 7$ .                                                   | 115 |

| 5.9  | FER comparison of floating-point (without approximations) and fixed-point single-Gaussian decoder for different $W_f$ and two NR iterations with $n = 1000$ and $d = 7$ .                                                        | 116 |

| 5.10 | FER of single-Gaussian decoder for different $W_i$ and two NR iterations with $n = 1000, d = 7$ (floating-point decoder is without any approximation).                                                                           | 116 |

| 5.11 | Top-level architecture for the fixed-point single-Gaussian LDLC decoder of degree 7, with a single check node and two-stage pipelining to achieve an effective parallelism equivalent to 20 variable nodes.                      | 117 |

|      |                                                                                                                                                                                                                                  |     |

| 5.12 | Timing diagram for the check node message processing block in single-Gaussian decoder of degree 7                                                                                                                   | 117  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.13 | Timing diagram for the variable node message processing block in single-Gaussian decoder of degree 7. The waveforms are shown specifically for $VNUCluster_0$ block.                                                | 118  |

| 5.14 | Throughput of fixed-point single-Gaussian decoder with $n = 1000$ and $d = 7$                                                                                                                                       | .119 |

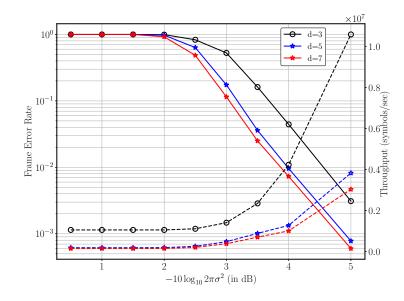

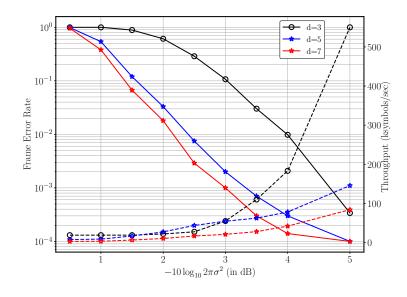

| 5.15 | FER and throughput comparison for the fixed-point single-Gaussian de-<br>coders of degree 3, 5 and 7 with block length 1000.                                                                                        | 119  |

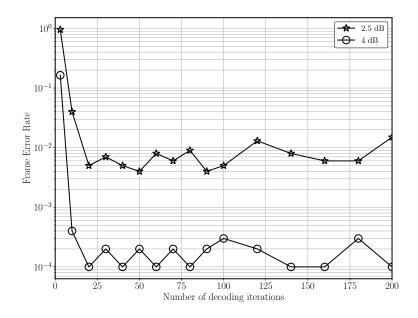

| 5.16 | FER of the floating-point multi-Gaussian decoder at distance from capacity of 2.5 dB and 4 dB for different numbers of decoding iterations with $n = 1000$ and $d = 5$ .                                            | 120  |

| 5.17 | FER of the floating-point (without approximations) and fixed-point multi-Gaussian decoder for different $W_f$ and two NR iterations with $n = 1000$ and $d = 5$ .                                                   | 120  |

| 5.18 | FER performance of the multi-Gaussian decoder with different $W_i$ and two NR iterations for $n = 1000$ and $d = 5$ (floating-point decoder performance is without any approximation).                              | 121  |

| 5.19 | Top-level architecture of the fixed-point multi-Gaussian LDLC decoder (de-<br>gree, 5) with a single check node and with two-stage pipelining to achieve<br>an effective parallelism equivalent to 2 variable nodes | 121  |

| 5.20 | Timing diagram of the check node message processing block in multi-Gaussian decoder (degree 5).                                                                                                                     | 122  |

| 5.21 | Timing diagram of the variable node message processing block for multi-Gaussian decoder (degree 5)                                                                                                                  | 123  |

| 5.22 | Throughput of the fixed-point multi-Gaussian decoder $(M=2)$ with degree 5 and block length 1000.                                                                                                                   | 124  |

| 5.23 | Performance of floating-point multi-Gaussian decoder $(d=7, n=1000, M=2)$ for different number of decoding iterations at distance from capacity of 2.5 dB and 4 dB.                                                 | 124  |

| 5.24 | FER of the floating-point (without approximations) and the fixed-point multi-Gaussian decoder for different $W_f$ and two NR iterations for $d = 7$ and $n = 1000$ .                                                | 125  |

| 5.25 | FER of the multi-Gaussian decoder for different $W_i$ and two NR iterations<br>with degree 7 and $n = 1000$ (floating-point decoder is without approximation)              | .125 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.26 | Block diagram of a two-node serial fixed-point multi-Gaussian LDLC de-<br>coder of degree 7 (one single check node and one single variable node)                           | 126  |

| 5.27 | Timing diagram of the check node message processing block in multi-Gaussian decoder of degree 7                                                                            | 127  |

| 5.28 | Timing diagram of the variable node message processing block for multi-Gaussian decoder of degree 7                                                                        | 127  |

| 5.29 | Throughput of the fixed-point multi-Gaussian decoder of degree 7 for block length 1000.                                                                                    | 128  |

| 5.30 | Performance of the multi-Gaussian decoder for different number of decoding iterations at distance from capacity of 2.5 dB and 4 dB with $M = 5$ , $d = 3$ and $n = 1000$ . | 128  |

| 5.31 | FER of the floating-point (without approximations) and the fixed-point multi-Gaussian decoder $(M=5)$ for different $W_f$ and two NR iterations with $d=3$ and $n=1000$ .  | 129  |

| 5.32 | FER of multi-Gaussian decoder $(M=5)$ for different $W_i$ and two NR iterations with $d = 3$ , $n = 1000$ (floating-point performance is without approximations).          | 129  |

| 5.33 | Performance of the multi-Gaussian decoder for different number of decoding iterations at distance from capacity of 2.5 dB and 4 dB with $M = 5$ , $d = 5$ and $n = 1000$ . | 130  |

| 5.34 | FER of the floating-point (without approximations) and fixed-point multi-Gaussian decoder ( $M=5$ ) for different $W_f$ and two NR iterations for $n = 1000, d = 5.$       | 130  |

| 5.35 | FER of the multi-Gaussian decoder $(M=5)$ for different $W_i$ and two NR iterations with $n = 1000$ and $d = 5$ (floating-point performance is without approximation).     | 131  |

| 5.36 | Performance of the multi-Gaussian decoder for different number of decoding iterations at distance from capacity of 2.5 dB and 4 dB with $M = 5$ , $d = 7$ and $n = 1000$ . | 131  |

| 5.37 | FER of the floating-point (without approximations) and the fixed-point multi-Gaussian decoder ( $M=5$ ) for different $W_f$ and two NR iterations for $d = 7, n = 1000.$   | 132  |

|      |                                                                                                                                                                            |      |

| 5.38 | FER of the multi-Gaussian decoder $(M=5)$ for different $W_i$ and two NR iterations with $d = 7$ , $n = 1000$ (floating-point performance is without approximation). | 132 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.39 | FER and throughput comparison of the fixed-point multi-Gaussian decoders with degree 3, 5 and 7 for block length 1000 and $M=2$                                      | 133 |

| 5.40 | FER of the multi-Gaussian decoder with larger Gaussian mixtures exchanged in iterative decoding (i.e., $M = 5$ ) for degree 3, 5, 7 and $n = 1000$ .                 | 133 |

| 5.41 | Comparison of the frame error rate and throughput of the fixed-point single-<br>Gaussian and multi-Gaussian decoders for block length 1000                           | 134 |

# List of Tables

| 3.1 | Performance and computational complexity of various parametric LDLC decoders with respect to the sampled PDF decoder for different block lengths | 40  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Resource requirements of the variable node message processing block in ar-<br>chitecture A, B and C                                              | 63  |

| 3.3 | Throughput (clock cycles/message) of the variable node message processing block in the architectures A, B and C.                                 | 67  |

| 3.4 | Resource usage of different architectures for single-Gaussian decoder                                                                            | 70  |

| 4.1 | Resource usage of the LDLC decoder, check node and variable node pro-<br>cessing blocks in architecture D                                        | 96  |

| 4.2 | Resource usage of the decoder, check node and variable node processing blocks in architecture E                                                  | 96  |

| 5.1 | Resource usage of single-Gaussian decoder $(M = 1), d = 5, \ldots, \ldots$                                                                       | 109 |

| 5.2 | Resource usage of single-Gaussian decoder $(M = 1), d = 7, \ldots, \ldots$                                                                       | 109 |

| 5.3 | Resource usage of multi-Gaussian decoder, $d = 5$ and $M = 2 $                                                                                   | 110 |

| 5.4 | Resource usage of multi-Gaussian decoder, $d = 7$ and $M = 2 $                                                                                   | 111 |

| 5.5 | Performance and Throughput Comparison of LDLC Decoders                                                                                           | 113 |

| C.1 | Look up table for $\exp(-I_1 2^{P_1}/2)$                                                                                                         | 154 |

# Chapter 1

# Introduction

Over the past decade, there has been significant growth in the number of connected devices. Industry analysis suggests that the number of wireless devices is expected to grow to 29.3 billion by 2023, i.e., an increase of more than a 40% compared to 2020 [1,2].

Widespread network connectivity, with the expectation of reliability and security, poses new challenges for the wireless industry. The increasing demand to support an even larger number of mobile wireless devices with limited bandwidth resources pushes the need for multi-user networks. In these networks, when multiple users transmit and receive data over a shared frequency band simultaneously, *multi-user signal interference* is observed. Due to this interference as well as channel noise, the transmitted data is often not received correctly. Therefore, to transmit data reliably researchers strive to find new error correcting codes (ECCs) with efficient decoding techniques [3–5].

Low-density parity check (LDPC) codes have attained tremendous popularity as the most powerful and practical class of codes implemented in modern wireless networks. The success of LDPC codes can be largely attributed to their capacity approaching performance and relatively low implementation complexity.

While LDPC codes are a class of linear codes over binary (and other finite) alphabets, there is another class of linear codes over the real numbers analogous to LDPC codes, termed *low-density lattice codes (LDLCs)*. LDLCs are continuous-alphabet codes introduced by Sommer *et al.* [6]. These codes have gained attention as many recent coding techniques using lattices have shown to be effective in mitigating multi-user channel interference.

The sparse (low-density) *H*-matrix that is used for the code construction also renders

iterative decoding (also called message-passing) an efficient decoding method [7,8] similar to LDPC codes.

However, the primary focus of LDLC research so far has been to demonstrate the theoretically achievable performance limits of LDLCs [7,9–25]. Not much work has been done towards the hardware implementation of LDLC decoding. This is mainly because in iterative decoding of LDLCs, the messages that are passed are *continuous functions* (e.g., Gaussian mixtures for the AWGN channel). In the literature, to demonstrate the theoretical performance of LDLCs, the continuous functions are either sampled and quantized or represented as Gaussian mixtures using parameter lists. However, even with all these reduction strategies, LDLC decoding is challenging to implement in hardware.

# **1.1** Motivation and Contributions

As practical hardware is key to leverage the proven capabilities of LDLCs, the high-level aim of this thesis is to contribute towards the hardware implementation of LDLC decoding.

More specifically, in this thesis, we present several fixed-point decoder implementations covering different parts of the architectural design space on a field-programmable gate array (FPGA) device. First we describe the fundamental problems encountered on the way to achieving a practical decoder hardware implementation along with a detailed study of the approaches to address those complexities. Then, we demonstrate a proof-of-concept single-Gaussian LDLC decoder on an Intel FPGA. Equipped with the knowledge obtained from single-Gaussian LDLC decoder implementations, we extend the work and achieve a hardware implementation for a multi-Gaussian LDLC decoder. Multi-Gaussian LDLC decoding poses significantly higher design challenges; nonetheless, improved decoding performance is achieved although at a cost of reduced throughput. The multi-Gaussian decoder achieves a performance close to that of [7], where the continuous messages are sampled in 1024 discrete data-points.

The contributions of this thesis are as follows:

In Chapter 3, we study the design and hardware implementation details of a fixedpoint single-Gaussian LDLC decoder of degree 3. In this iterative decoder, the exchanged messages are single Gaussians; the Gaussian-mixture messages generated during the intermediate steps in the iterative decoding are reduced to a single Gaussian using a momentmatching method in each decoding iteration [12].

We also perform a comprehensive quantization analysis to find the minimum word length for fixed-point arithmetic representation of the values in the iterative decoding. Efficient numerical methods are devised to approximate the required non-linear functions, i.e., division and exponentiation, and subsequently characterize their effect on decoder performance.

We then evaluate different hardware architectures and design trade-offs for the single-Gaussian LDLC decoder. A serial architecture with a single check node and a single variable node is implemented as a baseline architecture to provide a proof-of-concept implementation for LDLC decoding in FPGA. To exploit the parallelism of iterative decoding, a decoder architecture with a single check node and 20 variable nodes is included. In order to maximize the re-use of the FPGA resources and enhance the throughput, an LDLC decoder with a single check node and with pipelining to achieve an effective parallelism equivalent to 50 variable nodes is also implemented. Altogether, we can achieve peak decoding at the rate of 10.5 Msymbols/sec on a single Arria 10 FPGA.

In Chapter 4, we study the hardware implementation details of a multi-Gaussian LDLC decoder of degree 3 on the target FPGA. Here the messages exchanged in the decoder are the parametric representation of the Gaussian mixtures instead of a single Gaussian [9,11].

Potential Gaussian mixture reduction methods are compared in terms of computational complexity versus frame error rate (FER) performance, and a suitable method is chosen to reduce a Gaussian mixture to a smaller mixture with a fixed number of components in each decoding iteration. Possible design optimizations to reduce the decoder design complexity in fixed-point arithmetic, and the resulting effect on the decoding performance, are investigated.

A study of possible decoder architectures on target FPGA device is presented along with resource requirements and design throughput details. We further compare single-Gaussian and multi-Gaussian decoders of degree 3 for decoding performance and design throughput on a target FPGA.

In Chapter 5, we push the design limits for the LDLC decoders even further. We implement single-Gaussian and multi-Gaussian LDLC decoders on FPGA devices for a broader range of design parameters, e.g., degrees 5 and 7, and with larger Gaussian mixture messages that contain more than two components. The results obtained from these implementations play a vital role to determine an appropriate LDLC decoder for a certain application.

# **1.2** Thesis Outline

The rest of this thesis is organized as follows.

Chapter 2 provides the basic definitions of lattice codes along with the constraints and properties of low-density lattice codes. The basic iterative decoding algorithm for LDLCs, where the messages exchanged in decoding are continuous functions, is included. It also presents a summary of the LDLC decoders published in the literature and compares their empirical performance.

Chapter 3 presents the implementation details for a single-Gaussian LDLC decoder of degree 3 on a target FPGA device. A study of the optimization techniques to reduce decoder complexity, a detailed quantization analysis of the fixed-point arithmetic, and efficient techniques to implement the required non-linear functions are described.

Chapter 4 presents the hardware implementation details for a multi-Gaussian LDLC decoder with degree 3. Chapter 4 also provides a detailed comparison of the single-Gaussian and the multi-Gaussian decoder with degree 3 and block length of 1000.

In Chapter 5, we push the design space boundaries on the target FPGA and present the single-Gaussian and multi-Gaussian decoder implementations for degrees 5 and 7 and also present multi-Gaussian decoders where the Gaussian mixture messages comprise more than two components.

Finally, Chapter 6 summarizes the contributions of this thesis and outlines the design aspects that were not explored in the thesis but that would constitute a valuable extension as future work.

# Chapter 2

# Literature Survey

# 2.1 Channel Capacity and Channel Codes

Shannon's channel capacity theorem [26] shows that provided the rate of transmission is less than a particular rate called channel capacity it is possible, in principle to transmit information with arbitrarily small probability of error.

Codes that allow data transmission at the rates near channel capacity and with low probability of error are often referred to as 'near Shannon-limit codes' or (sometimes inaccurately as) 'capacity achieving codes'.

## 2.1.1 Codes for Binary Channels

While Shannon's capacity theorem showed that long random codebooks can achieve the capacity of binary (e.g., binary symmetric) and finite alphabet channels, thereafter, it was discovered that capacity could also be achieved using structured linear codes, where each codeword is a linear combination of a set of basis vectors.

Among the class of linear binary codes, turbo codes [27] and low-density parity-check codes are codes which allow efficient iterative decoding [28–31]. Specifically, turbo codes and LDPC codes are regarded as near Shannon-limit error-correcting-codes with practical decoding algorithms. Turbo codes use concatenated convolutional encoders and inter-leavers, whereas LDPC codes are block codes that use a sparse parity-check matrix for

encoding. The sparse nature of the parity-check matrix in LDPC codes provides the flexibility to perform decoding operations in parallel; this is very advantageous for a high-speed and efficient hardware implementation of a decoder.

## 2.1.2 Codes for Additive White Gaussian Noise Channels

Shannon showed that for the additive white Gaussian noise (AWGN) channel, continuous alphabet codes with random codebooks where each code letter is drawn i.i.d. according to a Gaussian-distribution can approach the capacity of the channel [32]. In the class of codes for the AWGN channel, lattice codes are structured codes that are the Euclidean space analogue of linear block codes and have gained much attention lately as they can also, in principle, achieve AWGN channel capacity [33, 34] and many coding techniques using lattices are shown to be effective in mitigating *multi-user channel interference* [4,35]. For example, among lattice based decoding strategies, *compute-and-forward* first recovers enough linear combinations of the received message and then extracts the intended message [3, 5, 36–48]. Lattice codes are well suited for this purpose because their linear structure matches the additivity of the channels, where the sum of two codewords superimposed additively lies in the lattice.

Low-density lattice codes (LDLCs) studied in this thesis are a class of the lattice codes.

# 2.2 LDLC and Related Codes

## 2.2.1 Block Codes

Low-density lattice codes are closely related to *linear block codes* over finite fields. Hence it is worth revisiting the structure and properties of block codes.

In a block code, C, over a finite field  $\mathbb{F}$  of size  $q = |\mathbb{F}|$ , an information sequence is segmented into message blocks of fixed length; each message block, denoted by  $\underline{m}$ , consists of k information symbols over  $\mathbb{F}$  (typically  $|\mathbb{F}| = 2$ ). The encoder generates a block of ncoded symbols, denoted by  $\underline{x}$ , based on the k information symbols. This code with n-tuple codeword and k information symbols is called an (n, k) block code [49–51] over  $\mathbb{F}$ . The rate R of a block code is given as

$$R = \frac{k}{n}.\tag{2.1}$$

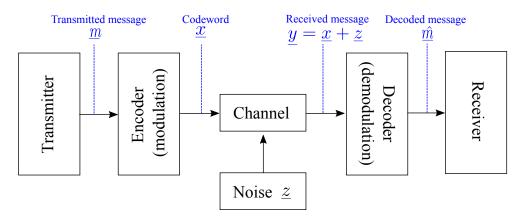

Figure 2.1: Schematic of a general communication channel

There are  $q^n$  distinct sequences of length n over  $\mathbb{F}$  and from this,  $q^k$  codewords are selected to form the code. For a block code to be useful, the  $q^k$  codewords must be distinct. Therefore, there should be a one-to-one correspondence between a message  $\underline{m}$  and its codeword  $\underline{x}$ . A block code is linear over a finite-field  $\mathbb{F}$  if the set of codewords is a linear subspace of dimension k of the space  $\mathbb{F}^n$ .

#### Encoding and Decoding (Generator Matrix and Parity-check Matrix)

For every linear block code k-linearly independent vectors,  $\underline{g}_1, \underline{g}_2, \ldots, \underline{g}_k$  can be identified such that all the codewords can be obtained by a linear combination of these vectors. These vectors,  $\underline{g}_1, \underline{g}_2, \ldots, \underline{g}_k$  are called basis vectors. For every linear code, there exists a k-by-n generator matrix,  $\overline{G}$ , such that,

$$\underline{x} = \underline{m} \cdot G, \tag{2.2}$$

where  $\underline{x} = \{x_1, x_2, \dots, x_n\}, \underline{m} = \{m_1, m_2, \dots, m_k\}$  and G is represented as,

$$G = \begin{bmatrix} \underline{g}_1 \\ \underline{g}_2 \\ \vdots \\ \underline{g}_k \end{bmatrix} = \begin{bmatrix} g_{11} & g_{12} \cdots g_{1n} \\ g_{21} & g_{22} \cdots g_{2n} \\ \vdots \\ g_{k1} & g_{k2} \cdots g_{kn} \end{bmatrix}.$$

A parity-check matrix, H, of a (n, k) linear block code is a full-rank (n-k)-by-n matrix satisfying,

$$H \cdot G^T = 0. \tag{2.3}$$

As a consequence of (2.3),

$$\underline{x} \cdot H^T = 0. \tag{2.4}$$

This condition is also known as parity-check equation.

Using elementary row operations and column permutations, any generator matrix can be converted to a generator matrix for an equivalent code that is in systematic form, in which the left side of the matrix is the identity matrix, i.e.,

$$G = [I_k|P], \tag{2.5}$$

where  $I_k$  is the  $k \times k$  identity matrix and P is a  $(k) \times (n - k)$  parity matrix. Similarly, a systematic form for a parity-check matrix can be obtained, which has an identity matrix at the right side, i.e.,

$$H = [-P^T | I_{n-k}]. (2.6)$$

Fig. 2.1 illustrates the basic communication channel model, where the encoder generates a codeword  $\underline{x}$  corresponding to message  $\underline{m}$ . While codeword  $\underline{x}$  is transmitted over the channel, noise  $\underline{z}$  is added to it and the noisy message  $\underline{y} = \underline{x} + \underline{z}$  is received. The received message  $\underline{y}$  is decoded at the receiver's end and an estimate  $\underline{\hat{m}}$  of the message  $\underline{m}$  is obtained.

#### Minimum Distance

For block codes, the Hamming distance (or simply distance),  $d(\underline{x}_1, \underline{x}_2)$  between two codewords  $\underline{x}_1$  and  $\underline{x}_2$  is the number of positions where  $\underline{x}_1$  and  $\underline{x}_2$  have different symbols, e.g., for  $\underline{x}_1=011001101110$  and  $\underline{x}_2=011001010001$ ,  $d(\underline{x}_1, \underline{x}_2)=6$ .

The minimum distance,  $d_{min}$ , for block code C, is defined as the smallest distance between any pair of codewords in the code. For a given block code C,  $d_{min}$  is then

$$d_{min} = min\{d(\underline{x}_1, \underline{x}_2) : \underline{x}_1, \underline{x}_2 \in \mathcal{C}, \underline{x}_1 \neq \underline{x}_2\}.$$

(2.7)

#### Modulation

Codewords in finite fields cannot be directly transmitted over continuous-time channels. Instead, the codewords are transmitted over the channel using digital modulation, where one or more properties of a periodic waveform, called the carrier signal, is modulated depending upon the symbols to be transmitted. Traditionally, in binary-phase-shift-keying (BPSK), only one sinusoid is taken as a basis function for modulation. Modulation is achieved by varying the phase of the basis function depending on the codeword bits ('0' or '1') [52]. Eqns. (2.8) and (2.9) outline the BPSK modulation technique, where  $S_0(t)$  is transmitted when the bit is '0' and  $S_1(t)$  is transmitted when bit is '1'.

$$S_0(t) = A\cos(\omega t), \tag{2.8}$$

$$S_1(t) = A\cos(\omega t + \pi). \tag{2.9}$$

This modulation is very robust but unsuitable for high data-rate applications as it transmits only one symbol at a time. To overcome this disadvantage, higher-level modulation schemes are used such as 8-PSK, 16-QAM, etc. These modulation schemes can transmit several binary symbols per modulated symbol, each represented by different states of magnitude and phase of the carrier.

Encoding and modulation need not be treated as separate processes; these two can be integrated together by matching the encoding technique to the modulation scheme. The two step process whereby the information bits are converted first into a coded bit stream and then into a modulated signal is then replaced by a single process which converts the data stream directly into a suitable signal for transmission over the channel [53].

## 2.2.2 Low-Density Parity-Check Codes

Low-density lattice codes are motivated by the design simplicity of LDPC block codes. Therefore, the basic concepts of the LDPC code design and decoding methodology are first reviewed.

The term *low-density* in low-density parity check codes refers to the characteristic that the parity-check matrix (H) used for the LDPC code design contains only a few '1's in comparison to '0's (i.e., "the density of '1's is low"). LDPC codes are arguably one of the best error correction codes in existence at present. Their main advantage is that they provide a performance which is very close to capacity and use decoding algorithms with complexity linear to the code size. Moreover, they are well suited for implementations that can make extensive use of parallelism. LDPCs were first introduced by Gallager in his PhD thesis in the 1960s [28]. Due to the high computational effort (for the time) required for encoder and decoder implementation, LDPC codes were mostly ignored until rediscovered in the mid 1990s by Neal and Mackay [29, 30].

To understand LDPC code design and structure, let's assume that an LDPC code is constructed using a parity-check matrix, H, of size (m, n) where m is number of rows and n is the number of columns in the matrix. The number of '1's in each row and column are referred as the row and column weights,  $wt_r$  and,  $wt_c$  respectively. An example of an (4,8) LDPC parity-check matrix, with  $wt_r = 4$  and  $wt_c = 2$  is given below:

$$H = \begin{bmatrix} 0 & 1 & 0 & 1 & 1 & 0 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{bmatrix}$$

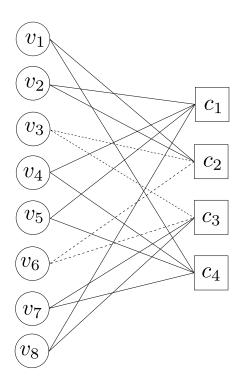

In [54] Tanner introduced an effective graphical representation for LDPC codes. These graphs, known as *Tanner graphs*, are effective as they not only provide a complete representation of the code, but they also help to understand the decoding algorithm. Tanner graphs are bipartite graphs, which means that the nodes of the graph are separated into two distinct sets (or types) and edges can only connect nodes of two different types. The two types of nodes in a Tanner graph are called variable nodes and check nodes. Each row of the *H* matrix represents a check node and each column represents a variable node. An edge in a Tanner graph is a connection between a variable node and a check node so the number of edges in the Tanner graph and the number of ones in the *H* matrix are equal. The  $i^{th}$  check node is connected to the  $j^{th}$  variable node if the element  $h_{ij}$  of *H* is a 1.

A series of interconnected nodes with same origin and termination, given no other nodes repeat, is called a cycle. The length of the cycle is given by the number of edges in it and the girth of a graph is defined to be the size of the smallest cycle. Figure 2.2 shows a graphical representation of the example (4,8) LDPC *H*-matrix described above. This *H* matrix contains a 4-cycle loop highlighted in the bipartite graph using dotted lines.

#### LDPC Encoding

LDPC codes are linear block codes. If the message is  $\underline{m}$  and the generator matrix is G, then the codeword is given as:

$$\underline{x} = \underline{m} \cdot G. \tag{2.10}$$

In order to obtain G from the H matrix, the H matrix is first converted into systematic form by applying proper elementary operations as shown in (2.6). Based on the systematic form of the H matrix, the generator matrix is obtained as

$$G = [I_k | P^T]. (2.11)$$

### LDPC Decoding

LDPC decoding is performed through an iterative decoding algorithm based on the Tanner graph. LDPC decoding algorithms are termed as message-passing iterative decoding algorithms which perform local calculations at check (variable) nodes and pass those local results via messages to variable (check) nodes [29, 30, 55–63]. Based on the information exchanged between the check node and variable nodes, LDPC decoding can be classified into two types:

- Hard-decision decoding

- Soft-decision decoding

**Hard-Decision Decoding:** In hard-decision decoding the messages passed in decoding iterations are binary bits and the decoding decision is based on this binary information. The bit flipping algorithm of [29] is an example of hard decision decoding.

In the bit flipping algorithm, a check node finds the bit in error by checking the parity of the data stream received from all the variable nodes connected to it; the parity may be even or odd. If the number of 1's received at check nodes satisfies the required parity, then it sends the same data back to variable nodes connected to it; otherwise it flips the bit (from variable nodes) which is involved in the largest number of unsatisfied parity checks and re-sends it to the variable node. A variable node utilizes the incoming check node messages to decide if the bit at its position is a '0' or a '1' by majority rule. The variable node then sends this hard-decision to its connected check nodes.

The decoding process is terminated whenever a valid code word has been found, i.e., all the parity check equations are satisfied.

**Soft-Decision Decoding:** Soft-decision decoding is based on the idea of belief propagation. In this scheme, the decoder makes an inference for each bit of the transmitted vector by calculating the marginal distribution of each bit, conditional on the received vector. The sum-product algorithm (SPA) is a soft-decision message passing algorithm which is similar to the bit-flipping algorithm [30]. The main difference between the SPA and bit-flipping algorithm is that in the SPA, check node and variable node messages are conditional probabilities instead of binary bits. These conditional probabilities are expressed as log-likelihood ratios of bits where the log-likelihood ratio is defined as,

$$\log likelihood ratio (LLR) = \log \left(\frac{x_i = `0' | y_i}{x_i = `1' | y_i}\right).$$

(2.12)

## 2.2.3 Low-Density Lattice Codes

Low-density lattice codes (LDLCs) were first introduced by Sommer et al. [6]. As opposed to LDPCs or algebraic codes which are defined over a finite field, lattice codes are defined over real numbers. LDLCs belong to the class of lattice codes.

#### Lattice Codes

Lattice codes are regarded as the Euclidean space analogue of linear block codes. In a lattice code, an integer-valued information sequence is converted to a point in Euclidean

space.

#### **Definition 1.** (Lattice)

An n-dimensional lattice,  $\Lambda \subset \mathbb{R}^n$ , is defined as all the integer linear combinations of n given linearly independent basis vectors,  $\underline{g}_1, \ldots, \underline{g}_n \in \mathbb{R}^n$ . Taking the basis vectors as the columns of the generator matrix G, (i.e.,  $\overline{G} = (\underline{g}_1, \ldots, \underline{g}_n)$ ), the lattice  $\Lambda$  is given by

$$\Lambda = \{ \underline{x} \in \mathbb{R}^n : \underline{x} = G\underline{b}, \ \underline{b} \in \mathbb{Z}^n \}.$$

(2.13)

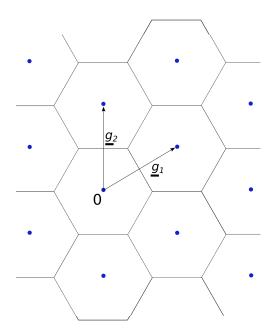

Figure 2.3 shows the graphical illustration of an example 2-dimensional lattice with basis vectors  $\underline{g}_1$  and  $\underline{g}_2$ .

#### **Definition 2.** (Voronoi Region)

The Voronoi region of a lattice point  $\underline{x} \in \mathbb{R}^n$  is the subset of  $\mathbb{R}^n$  which is closer to  $\underline{x}$  than to any other lattice point. It is generally represented as  $\nu$ . For any lattice  $\Lambda(G)$ , all the Voronoi regions have the same volume, denoted as  $V(\Lambda)$ , which is equal to the determinant of the generator matrix, G, i.e.,

$$V(\Lambda) = |\det(G)|. \tag{2.14}$$

Low-density lattice codes (LDLCs) are lattice codes which have some specific constraints on the matrix  $H = G^{-1}$ .