# Implementing FPGA-optimized Systolic Arrays using 2D Knapsack and Evolutionary Algorithms

by

Long Chung Chan

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2021

© Long Chung Chan 2021

### Author's Declaration

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public

### **Statement of Contributions**

This work is an extension of my own work published in Chan et al. (2019) [12].

The initial idea of incorporating CMA-ES in optimization of the partitioning workflow was implemented with the help of Gurshaant Malik.

The following 2D knapsack optimization is implemented with the help of Justin Borromeo.

The systolic array framework is provided by Thomas Kidd and Prof. Nachiket Kapre.

#### Abstract

Underutilization of FPGA resources is a significant challenge in deploying FPGAs as neural network accelerators. We propose an FPGA-optimized systolic array architecture improving the CNN inference throughput by orders of magnitude compared to an un-partitioned systolic array through parallelism-aware partitioning of on-chip resources. We fracture the FPGA into multiple square systolic arrays and formulate the placement of these arrays as a 2D knapsack problem. We simulate the cycle counts needed for each neural network layer given different systolic array sizes using cycle-accurate systolic array simulator - SCALESim. We generate physical implementation and operating frequencies of systolic arrays placed in uniformly staggered locations on Xilinx VU37P and VU9P Ultrascale+ platforms. We use the cycle and frequency information in an optimizer coupling CMA-ES evolutionary algorithm and a simple 2D Knapsack solver to discover packable and routable partitioned designs to maximize throughput. Our experiments' most significant performance improvement comes from the implementation of layers with large kernel sizes. We demonstrate that inference throughput gain of 7-22.7  $\times$  is possible with a 1.2-7.6  $\times$  sacrifice of latency. Our optimization tool can achieve up to  $8 \times$  higher throughput gain on eight MLPerf benchmark network topologies. Our tool also generates designs across various latency and throughput combinations, providing a wide degree of design selection.

#### Acknowledgements

I would like to thank everyone in the WatCAG lab. 2019 and 2020 have made everything different and posed a new challenge to everyone while forcing everyone to adapt to this weird era as soon as possible. Luckily, we have weekly group meetings to share and discuss our research progress. Justin Borromeo is incredible to work with, and his fantastic data handling skills have allowed us to summarize our results quickly.

Next, I would like to thank Prof. Nachiket Kapre. Taking the ECE327 course taught by Nachiket back in Fall 2018 had changed my career path in a way I could not have imagined. Without Nachiket's support, I would not have had the chance to present my paper in ICFPT 2019 or the experience of being a master's student. Without his drive and guidance, I could not have finished this work within the timeframe. I am thankful for all the unique research experiences under Prof. Nachiket Kapre.

Finally, I would like to thank my family and friends for their support. On numerous occasions, they encouraged me to move forward during 2021. Even during this stressful year, they were always there to help and give me endless encouragement. I would not have emotionally survived this pandemic without them.

## Dedication

This is dedicated to the unconditional support and love from my family.

# **Table of Contents**

| Li | List of Figures x   |          |                                                 |           |  |

|----|---------------------|----------|-------------------------------------------------|-----------|--|

| Li | List of Tables xiii |          |                                                 |           |  |

| Li | st of               | Listing  | 5                                               | xiv       |  |

| 1  | Intr                | oductio  | n                                               | 1         |  |

| 2  | Bac                 | kground  | 1                                               | <b>5</b>  |  |

|    | 2.1                 | Convolu  | tion Neural Networks                            | 5         |  |

|    |                     | 2.1.1    | CNNs benchmark                                  | 8         |  |

|    | 2.2                 | Systolic | Arrays                                          | 9         |  |

|    | 2.3                 | Xilinx U | Iltrascale Platform                             | 11        |  |

|    | 2.4                 | Evolutio | onary algorithm                                 | 14        |  |

|    |                     | 2.4.1    | Covariance Matrix Adaptation Evolution Strategy | 15        |  |

|    | 2.5                 | KnapSa   | ck Optimization Algorithm                       | 18        |  |

|    |                     | 2.5.1 I  | Maximal Rectangles Algorithm                    | 19        |  |

| 3  | Our                 | Propos   | sal                                             | <b>21</b> |  |

|    | 3.1                 | Overall  | Architecture                                    | 21        |  |

|    |                     | 3.1.1 l  | Multi Systolic Array Architecture               | 21        |  |

|    |                     | 3.1.2 l  | Device Logic Region Splitting Technique         | 22        |  |

|   | 3.2            | Proble  | em Formulation                 | 24 |

|---|----------------|---------|--------------------------------|----|

|   |                | 3.2.1   | Challenges                     | 24 |

|   |                | 3.2.2   | Complete Formulation           | 29 |

|   | 3.3            | Workf   | low                            | 31 |

|   |                | 3.3.1   | Stage 1 – Database Generation  | 32 |

|   |                | 3.3.2   | Stage 2 – Optimization         | 33 |

| 4 | Imp            | olemen  | tations                        | 37 |

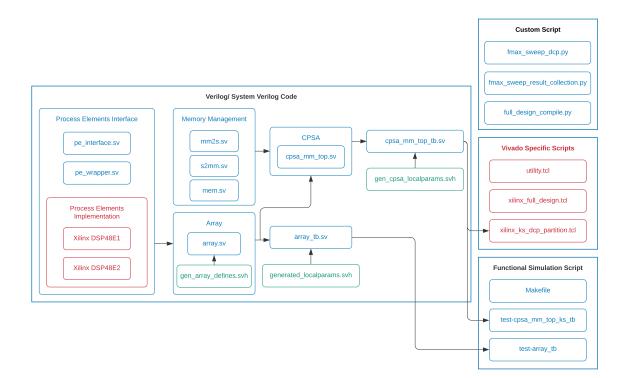

|   | 4.1            | Systol  | ic Array Implementation        | 37 |

|   |                | 4.1.1   | Systolic Array Architecture    | 37 |

|   |                | 4.1.2   | Systolic Array Coding Overview | 39 |

|   | 4.2            | Optim   | nizer Implementation           | 41 |

|   |                | 4.2.1   | Parser                         | 42 |

|   |                | 4.2.2   | Processor                      | 42 |

|   |                | 4.2.3   | Output Generation              | 46 |

| 5 | $\mathbf{Res}$ | ults ar | nd Discussion                  | 48 |

|   | 5.1            | Optim   | nizer Performance              | 48 |

|   |                | 5.1.1   | Optimizer Runtime              | 48 |

|   |                | 5.1.2   | Design Quality                 | 52 |

|   | 5.2            | FPGA    | Implementation Result          | 61 |

|   |                | 5.2.1   | Routability                    | 61 |

|   |                | 5.2.2   | Demo on PYNQ                   | 63 |

| 6 | Cor            | clusio  | ns & Future Directions         | 67 |

|   | 6.1            | Conclu  | usions                         | 67 |

|   | 6.2            | Future  | e Directions                   | 67 |

|   |                | 6.2.1   | Wider Platform Support         | 68 |

|   |                | 6.2.2   | MLIR Integration               | 68 |

| References                                                                                     | 69              |

|------------------------------------------------------------------------------------------------|-----------------|

| APPENDICES                                                                                     | 77              |

| A RECTPACK profiles example and guide                                                          | 78              |

| B Optimizer configuration file detail                                                          | 79              |

| C Systolic Array Codebase Overview                                                             | 82              |

| <ul> <li>D YAML configuration file targeting VU9P</li> <li>D.1 From the Command Line</li></ul> | <b>84</b><br>84 |

| E YAML configuration file targeting VU37P                                                      | 88              |

| E.1 From the Command Line                                                                      | 88              |

# List of Figures

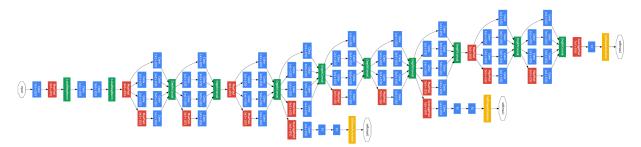

| 2.1  | An overview of the entire GoogleNet V1 [52]                                                                                                                       | 8  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

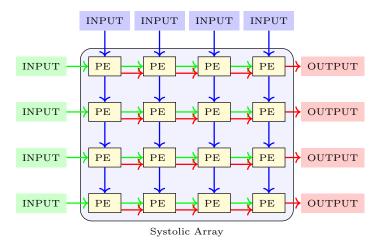

| 2.2  | A high level overview a traditional $4 \times 4$ systolic array                                                                                                   | 9  |

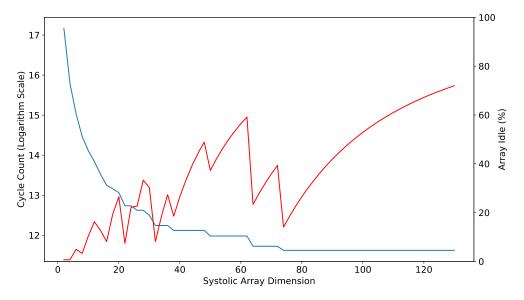

| 2.3  | Under-utilization percentage and cycle count against systolic array size                                                                                          | 10 |

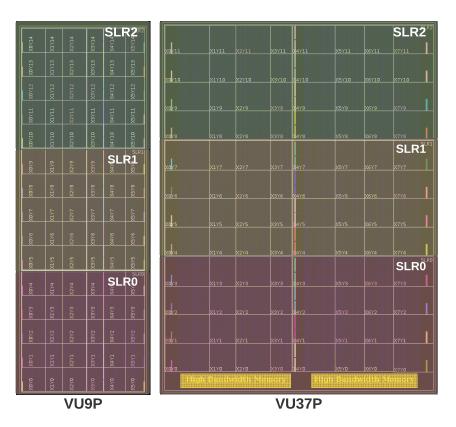

| 2.4  | Device view of VU37P and VU9P                                                                                                                                     | 12 |

| 2.5  | A structured view of a DSP tile on Xilinx UltraScale Platform                                                                                                     | 13 |

| 2.6  | A visual presentation of CMA-ES candidates per generation                                                                                                         | 18 |

| 2.7  | A visual presentation of guillotine split placement                                                                                                               | 19 |

| 3.1  | A visual presentation of the pipeline in the partitioned architecture                                                                                             | 22 |

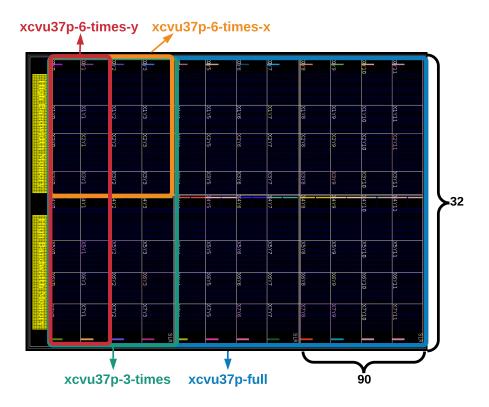

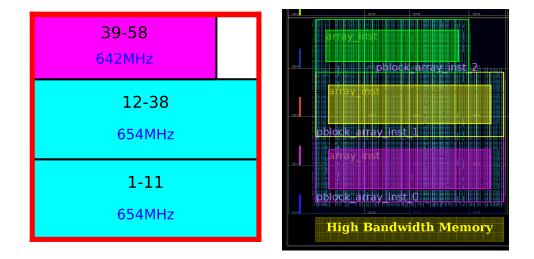

| 3.2  | Visual representation of Knapsack profile modeling VU37P $\ldots$                                                                                                 | 23 |

| 3.3  | Visual representing of Knapsack profile modeling VU9P                                                                                                             | 24 |

| 3.4  | A representation when overlapping occurs                                                                                                                          | 25 |

| 3.5  | A heatmap representation of the operating frequency of a $2 \times 2$ systolic array                                                                              | 26 |

| 3.6  | A distribution histogram of the operating frequency of a $2 \times 2$ systolic array                                                                              | 27 |

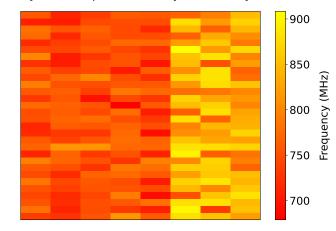

| 3.7  | A heatmap visualization of frequencies collected covering clock region $X3Y0$<br>to $X5Y4$ on VU9P for systolic array size from $4 \times 4$ up to $14 \times 14$ | 28 |

| 3.8  | A side-by-side device view of the same 8×8 systolic array implemented by Vivado 2018.3 with default non-project flow (left) and own custom TCL flow (right).      | 29 |

| 3.9  | High-level diagram of the entire workflow.                                                                                                                        | 32 |

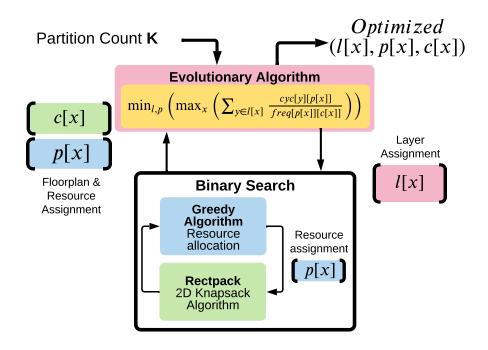

| 3.10 | The optimization loop finds layer assignment $l[x]$ , resource allocation $p[x]$ , and placement allocation $c[x]$ for a partition size $K$ .                     | 34 |

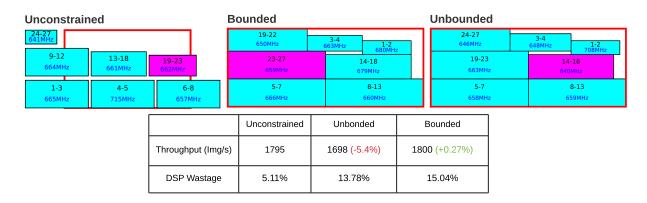

| 3.11 | 1 Comparison between solutions generated by Unconstrained (left), Bounded (middle), and Unbounded (right).                                   |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4.1  | A high level overview of all the data flow in a $4 \times 4$ systolic array                                                                  |  |  |

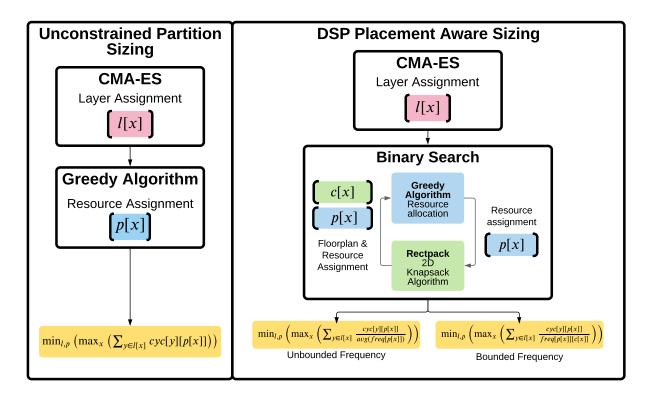

| 4.2  | A progress representation on how $l[x]$ , $p[x]$ and $c[x]$ are generated for each variation                                                 |  |  |

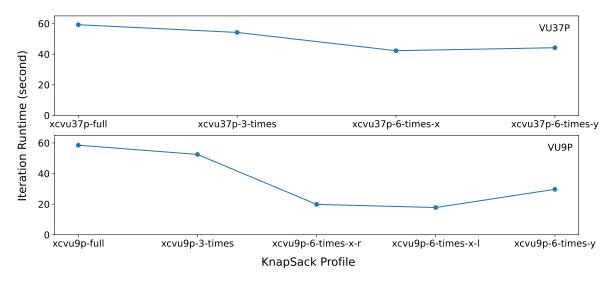

| 5.1  | Iteration runtime against different KnapSack profiles                                                                                        |  |  |

| 5.2  | Average Iteration runtime against different KnapSack profiles                                                                                |  |  |

| 5.3  | Average Iteration runtime against different networks                                                                                         |  |  |

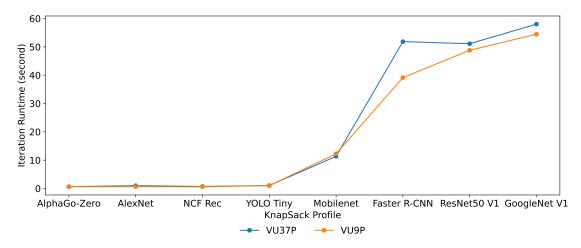

| 5.4  | Legal design percentage per iteration trend                                                                                                  |  |  |

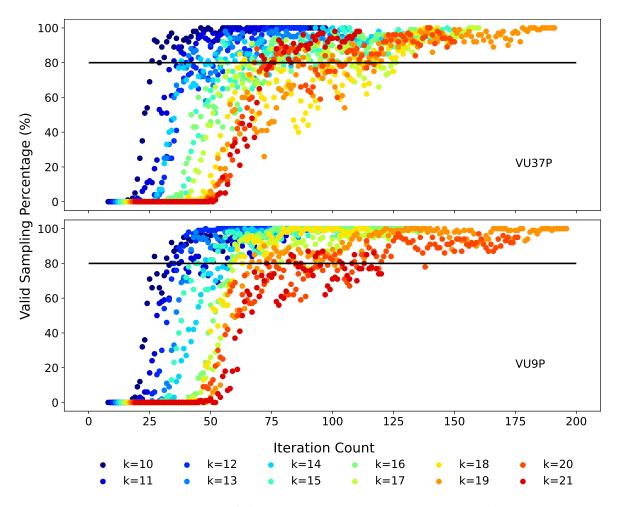

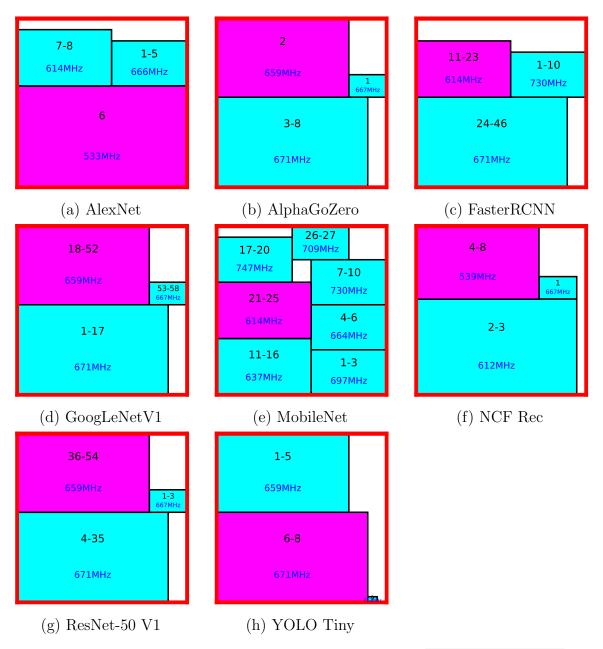

| 5.5  | Partitioned solutions of every topology with the xcvu37p-6-times-y pro-<br>file on VU37P                                                     |  |  |

| 5.6  | Partitioned solutions of every topology with the xcvu9p-6-times-y profile<br>on VU9P                                                         |  |  |

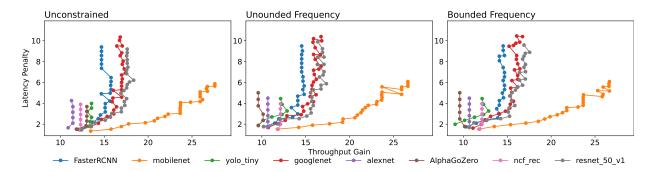

| 5.7  | Latency penalty vs. Throughput gain by partitioning algorithm variation<br>on VU37P                                                          |  |  |

| 5.8  | Latency penalty vs. Throughput gain by partitioning algorithm variation<br>on VU9P                                                           |  |  |

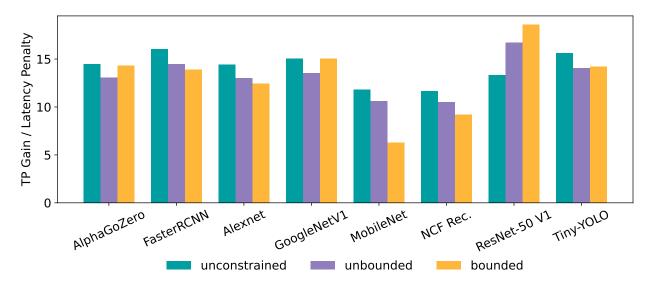

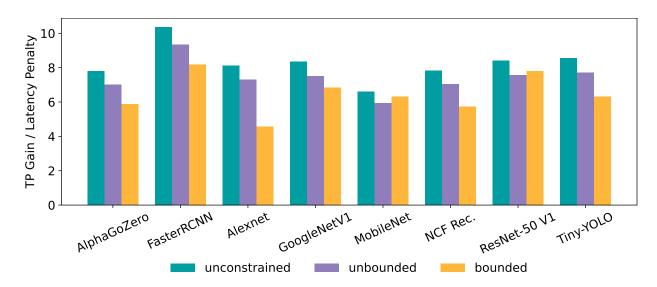

| 5.9  | Ratio of Throughput gain to Latency penalty as a partitioning algorithm variation on VU37P.                                                  |  |  |

| 5.10 | Ratio of Throughput gain to Latency penalty as a partitioning algorithm variation on VU9P.                                                   |  |  |

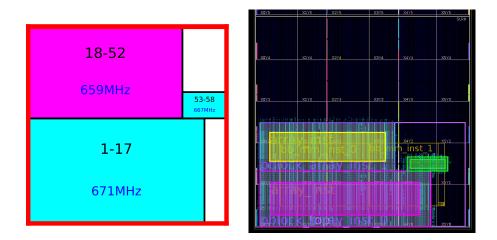

| 5.11 | A side-by-side comparison of software floorplan (left) and Vivado's placed<br>and routed implementation on VU37P (right) with GoogLeNetV1    |  |  |

| 5.12 | A side-by-side comparison of software floorplan (left) and Vivado's placed<br>and routed implementation on VU9P (right) with GoogLeNetV1     |  |  |

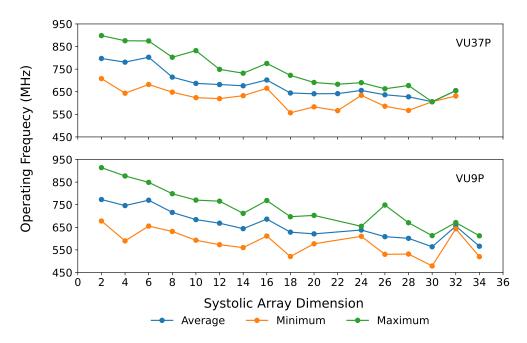

| 5.13 | Systolic Array Dimension vs. Operating Frequency on VU9P (bottom) and VU37P (top). An overall 20.6% and 26.7% frequency drop can be observed |  |  |

|      | in VU37P and VU9P, respectively.                                                                                                             |  |  |

|      | An PYNQ Z2 development board from TUL Corp. [13]                                                                                             |  |  |

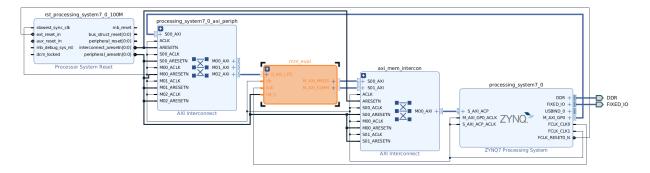

| 5.15 | A overview of the customized systolic array and AXI controller overlay                                                                       |  |  |

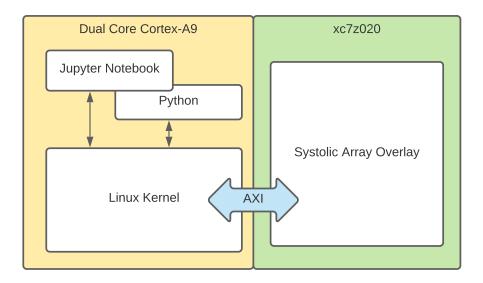

| 5.16 | A high-level system overview of the PYNQ-Z2 demo                                                     | 65 |

|------|------------------------------------------------------------------------------------------------------|----|

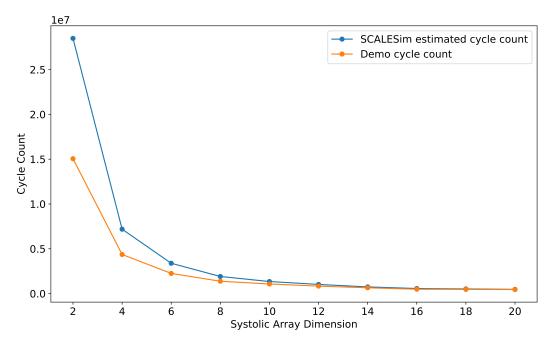

| 5.17 | SCALESim estimation and actual systolic array operating cycle count against systolic array dimension | 66 |

| C.1  | An overview of the systolic array code base.                                                         | 82 |

# List of Tables

| 2.1 | Memory Resource Summary on VU37 and VU9P                                          | 14 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.1 | Variable definitions from Equation 3.1 to Equation 3.6 $\ldots$ $\ldots$ $\ldots$ | 31 |

| 4.1 | Our parameter setting used                                                        | 41 |

| 5.1 | Solution Performance on VU37P                                                     | 53 |

| 5.2 | Solution Performance on VU9P                                                      | 54 |

# Listings

| A.1 | KnapSack profiles example on VU37P and VU9P | 78 |

|-----|---------------------------------------------|----|

| D.1 | Configuration profiles on the VU9P run      | 84 |

| D.2 | KnapSack profiles modelling VU9P            | 86 |

| E.1 | Configuration profiles on the VU37P run     | 88 |

| E.2 | KnapSack profiles modelling VU37P           | 90 |

## Chapter 1

## Introduction

With the slowdown of Moore's law of technology [32, 2], transistor size reduction has plateaued while the demand for computing power becomes more significant than ever. In recent years, the rapid adoption of convolution neural networks has allowed machine learning to be adopted across various fields, including recommendation systems, classification tasks, and natural language processing [28, 16, 6]. Due to the unique power-efficient and programmable computing substrate, Field Programmable Gate Arrays (FPGAs) have emerged as a potential candidate for post-Moore's law computing in data centers where high throughput operation with low power consumption is a significant concern [9, 42, 15]. Over the past decade, FPGA chips have become a popular choice of accelerators or specialized processors [15] in enormous data centers.

FPGA vendors have implemented various features in both software and hardware sides targeting domain-specific applications where one such area is artificial intelligence (AI). Due to the growing interest in using FPGAs as machine learning accelerators, FPGA vendors have fine-tuned the underlying fabrics to increase the computation capability of their products. One of the significant changes is more specialized hard blocks to improve inference performance. Intel introduced Stratix 10 NX, a 14nm FPGA platform including AI tensor blocks allowing 143 int8 TOPS at its peak performance in the fabric, allowing comparable performance to 12nm GPUs [11]. The AI tensor blocks on this platform are specially tuned arrays of lower-precision multipliers targeting throughput focused AI inference applications [11] offering comparable performance to GPU. Xilinx Ultrascale+ platform features hard blocks such as DSP48, BRAM18, and the URAM288. On VU37P and VU9P, Xilinx includes three Super Logic Regions (SLR) connected via Super Long Line (SLL) routing allowing each SLR to communicate with its neighboring SLR. Xilinx also introduces Versal FPGAs [62] in 2020, featuring an AI engine with an array of VLIW SIMD high-performance processors aimed at 5G and DNN applications.

However, it is still up to the applications engineers to utilize all these resources on the FPGA device to develop an efficient implementation for processing the computation of a neural network. The most dominant workloads in a Convolution Neural Network (CNN) are convolution operations with different filter dimensions. A systolic array is one of the most efficient hardware implementations for this workload. The underlying requirement is to convert a convolution operation into a matrix-matrix multiplication where systolic array replaces a single processor with a tightly coupled processing elements network. The significant benefit of using a systolic array is reducing direct memory access via a carefully planned data flow, encouraging the exploitation of neighboring data reuse. Previous works have implemented CNN accelerators using systolic arrays with their clever tweaks targeting different performance metrics, including but not limited to latency and throughput [65, 12, 56, 40, 46].

The first motivation of this work is to consider the FPGA architecture when providing the corresponding systolic array implementation. To fully utilize an FPGA device, it is essential to understand the underlying components in the fabric and carefully craft the hardware implementation with that knowledge. We target the Xilinx Ultrascale+ platform, where we apply double data packing and floor-planning according to the specification of DSP48E2 hard blocks available on the device.

The second motivation of this work is to explore how to close the utilization gap while maxing out the throughput bandwidth available in each of those DSP blocks. As FPGA manufacturers produce larger and larger chips targeting data centers, it is crucial to make sure that we can efficiently utilize all the resources available on the chip. It is not easy since different neural networks have different topologies, filters dimensions, and workload distribution. Relying on a one-size-fits-all architecture will inevitably cause a mismatch between computation power supply and demand, resulting in under-utilization.

This work's last motivation is to develop a standard workflow to achieve a throughput focus FPGA-optimized multi systolic array implementation across different neural network topologies. To achieve this, we must determine how to distribute the workload from different layers of computations across all resources of the FPGA chip. One must also consider the effect of systolic array placement given the irregular DSP layout of the underlying FPGA fabric to achieve high-frequency performance. We abstract the FPGA hardware and neural network topology considerations in our optimization flow.

One may naively reason to build one large systolic array to implement the computation

and map each layer to that array. This results in severe under-utilization due to mismatches between array size and layer compute requirements [49]. On top of that, in the latest Ultrascale+ platform from Xilinx, some of the larger FPGAs have multiple logic regions connected via a slow interconnection between each region [61].

Supertile [56], a state-of-the-art CNN accelerator, provides an architecture with three processors for convolution layers and one dedicated to fully-connected layers. Their design achieves a very high clock rate at 720 MHz with multi-stage processing to balance the throughput and latency. However, they carefully selected the parameters configuring their design without an automatic workflow. This limits their work on CNN with a nested structure similar to GoogleNet. Researchers have proposed new networks with new architecture components and different design philosophies in the ever-changing AI field. It is not feasible to keep up when a sinking time cost is needed to adjust the parameters for an efficient implementation carefully.

AutoSA [54], a state-of-the-art polyhedral compiler for systolic array, provides an endto-end flow compilation framework for generating systolic arrays on FPGA, including I/O control. Their result presents designs operating at 250 MHz on the Xilinx Alveo U250 platform. However, the DSP blocks in that platform can operate at a peak frequency of 775 MHz, meaning the throughput bandwidth of these DSPs is not fully utilized.

Our key insight is to formulate physical DSP constraints as a 2D knapsack problem to determine the final systolic array placement. We perform array sizing using a binary search and maximal rectangles algorithm [29] [48], a polynomial-time 2D knapsack algorithm, to find the greatest number of systolic array partitions that can fit on the chip. Our workflow uses these array dimensions and their identified placement from the maximal rectangles algorithm to determine the maximum clock frequency of each partition. The optimization flow generates a solution that minimizes the latency of the slowest partition, hence maximizing overall throughput.

Another critical insight is to treat each SLR as its unique grid and limit the multisystolic array design within each SLR region. We can then replicate the same design onto each SLR, allowing a linear gain in throughput performance. This allows us to explore more design options in the optimization flow as we further split each SLR into smaller replicating regions. We can also avoid the slow SLR interconnection within one design, negatively impacting the final frequency performance.

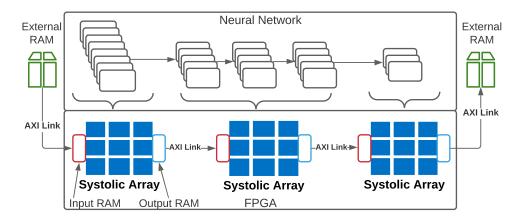

We adopt an approach where layers are grouped and mapped to independent systolic arrays implemented on the same FPGA. We develop a systolic array implementation with simple AXI support for I/O using Verilog. We develop a frequency-aware workflow that partitions the FPGA into multiple square systolic arrays and assigns adjacent layers to these partitions with evolutionary techniques.

#### Summary

- 1. We create an automatic workflow to synthesize, place and route systolic arrays of different sizes in every staggering location on both the Xilinx VU9P and VU37P Ultrascale+ platforms.

- 2. We introduce an optimization formulation for generating square systolic arrays and assigning neural network layers into partitions.

- 3. We use a flexible systolic array RTL generator to create a placement-aware frequency model for the optimization flow. These generated systolic arrays operate between approximately 630–820 MHz,

- 4. We introduce a workflow combining an evolutionary algorithm, binary search, and a 2D rectangular packing algorithm to create a frequency- and placement-aware optimization flow. Partitioned solutions designed by this workflow operate between 550–670 MHz.

## Chapter 2

## Background

## 2.1 Convolution Neural Networks

Convolution neural networks (CNN) are among the most common deep neural network architectures in the machine-learning landscape. Extensive exploration in this type of architecture allows CNNs to become the gold standard of image classification tasks since winning the ImageNet Challenge [31] in 2012. Over the years, researchers have researched applying CNN in different fields, including speech recognition [66, 5], sentiment analysis [27, 19], gesture recognition [64, 39], traffic forecasting [33, 38], medical pattern recognition [41, 30, 7] and etc.

Traditionally, a CNN consists of three significant layer types 1) convolution layers, 2) pooling layers, and 3) fully connected layers. In convolution layers, the primary responsibility is feature extraction via multiple small learning kernels. Several parameters dictate their behaviors, such as padding, stride, and kernel sizes. A few hundred kernels in each convolution layer contribute to the high computation demand. We provide simple pseudocode of a convolution layer in Algorithm 1.

When we calculate the size of the output feature map, we can take the striding and padding parameter into account by following Equation 2.1, where W is the size of the input feature map, F is the size of the filter, P is the number of padding, S is the number of strides, and K is the number of kernels. If the result from Equation 2.1 is not an integer, it indicates that the parameters are invalid.

$$K * \frac{W - F + 2P}{S + 1} \tag{2.1}$$

Algorithm 1: A pseudocode for simple 2D convolution operation

Data: Input feature map  $I(x_i, y_i)$ , Kernel  $K(x_k, y_k)$ ; assuming the K(0, 0) locate at the middle of the kernel where the height and width are  $(h_k, w_k)$ Result: Output feature map  $O(x_o, y_o)$ for  $y_i = 0$  to  $max(y_i)$  do for  $x_i = 0$  to  $max(x_i)$  do sum = 0; for  $i = -h_k$  to  $h_k$  do | sum = sum + K(j, i) \* I(x - j, y - i); end endO(x, y) = sum;end end

As shown in Algorithm 1, the underlying calculation processes are multiplication and accumulative addition of the results from the multiplication. One common trick is transforming the entire convolution layer into one matrix multiplication for efficient hardware implementation. Given an Input feature map of [20 \* 20] with three channels and 64 [3 \* 3] filters, we can perform such transformation by following these steps:

- 1. We stretch every local block of pixels [3\*3\*3] into a column vector of size 3\*3\*3 = 27.

- 2. We then repeat this process for  $(20 3 + 1)^2 = 324$  locations along the width and height and pack all these 324 column vectors to form matrix  $M_I$  of size [27 \* 324].

- 3. We stretch each filter into a row vector of size 3 \* 3 \* 3 = 27 and combine all 64 vectors into to form matrix  $M_K$  of size [64 \* 27].

- 4. We can now find the convolution result by multiplying  $M_K$  and  $M_I$ , forming the resulting matrix  $M_O$  of size [27 \* 324].

- 5. The result can then be reshaped back to the proper dimension [18 \* 18 \* 64].

This is a typical implementation pattern for a forward passing convolution layer.

Pooling layers are similar to the convolution layer, but each filter performs a specific function like max-pooling or average pooling. Their principal responsibility is to reduce dimensionality and exploit the locality of the pixel pool. We provide a simple pseudocode representation in Algorithm 2.

| Algorithm 2: A pseudocode for pooling layers                                  |  |  |  |

|-------------------------------------------------------------------------------|--|--|--|

| <b>Data:</b> Input feature map - $I(x_i, y_i)$ , Pooling Kernel $K(x_k, y_k)$ |  |  |  |

| <b>Result:</b> Output feature map - $O(x_o, y_o)$                             |  |  |  |

| for $y_i = 0$ to $max(y_i)$ do                                                |  |  |  |

| for $x_i = 0$ to $max(x_i)$ do                                                |  |  |  |

| if AveragePooling then                                                        |  |  |  |

| acc = 0;                                                                      |  |  |  |

| <b>for</b> $i = -h_k$ to $h_k$ <b>do</b>                                      |  |  |  |

| for $j = -w_k$ to $w_k$ do                                                    |  |  |  |

| acc = acc + I(x - j, y - i);                                                  |  |  |  |

| end                                                                           |  |  |  |

| end                                                                           |  |  |  |

| $O(x,y) = acc/(h_k * w_k);$                                                   |  |  |  |

| end                                                                           |  |  |  |

| if MaxPooling then                                                            |  |  |  |

| <b>for</b> $i = -h_k$ to $h_k$ <b>do</b>                                      |  |  |  |

| for $j = -w_k$ to $w_k$ do                                                    |  |  |  |

| maxValue = max(max, I(x - j, y - i));                                         |  |  |  |

| end                                                                           |  |  |  |

| end                                                                           |  |  |  |

| O(x,y) = maxValue;                                                            |  |  |  |

| end                                                                           |  |  |  |

| end                                                                           |  |  |  |

| end                                                                           |  |  |  |

Finally, the fully connected layers are the brute force layer in a CNN. They are similar to the output layer of the *multilayer perceptron* (MLP). Effectively, the operation here is matrix-vector multiplication. In this layer, the neurons apply a linear transformation to the input vector using a weights matrix. The output vector O(x) equals to the dot product of the weight matrix w and input vector x where the dimension of x is N plus the bias term  $w_0$  as shown in Equation 2.2

$$O(x) = \sum_{i=1}^{N} (wx_i + w_0)$$

(2.2)

This simple dot product operation allows the fully connected layers to aggregate all the information for feature extraction and generate the final classification result.

### 2.1.1 CNNs benchmark

Different CNNs come with different topologies, and we introduce the CNNs we include in the CNN topology dataset. *AlexNet* [31] is the first CNN that implements the Rectified Linear Units (ReLUs) as their activation functions and contains dropout layers. *AlexNet* contains five convolution layers and three fully connected layers. *GoogleNet* [52] introduces the inception module that reduces the number of tunable parameters from Alexnet's 60 million to 5 million without sacrificing accuracy with even deeper network architecture, as illustrated in Figure 2.1. However, the accuracy improvement diminishes, and the difficulty of training rapidly increases as a neural network increases its depth. *ResNet-50* [25] addresses this issue by adding the concept of residual learning into the architecture by adding shortcut connections.

Figure 2.1: An overview of the entire GoogleNet V1 [52]

There are also other CNNs proposed with a focus on their technical aspect, for example, object detection. Ross Girshick et al. [21] developed the *Regions-with-CNN-features* (R-CNN) system introducing the use of a selective search algorithm [53] in a region proposal to bypass the difficulty of selecting the classifying regions. Due to the long execution time of the selective search method, Ross Girshick also proposed the *Fast R-CNN* [20], which uses CNN the generate a feature map before using the same selective search algorithm.

The latest update on R-CNN is Faster R-CNN from Shaoqing Ren et al.'s work [45]. It achieves near real-time performance by eliminating the selective search and letting the network learn the region proposals. You Only Look Once (YOLO) [44] is another example that focuses on the speed of object detection where it uses a single convolution network to predict both the bounding boxes and the classification of those boxes from the complete image instead of multiple individual regions.

*MobileNets* from Andrew et al. [26] focus on enhancing the efficiency of CNNs for edge devices. This class of efficient models achieves very similar accuracy compared to popular networks like GoogleNet with fewer parameters.

## 2.2 Systolic Arrays

A systolic array is a type of hardware architecture where homogeneous computation elements, referred to as "units", are connected in a regular geometric fashion with pipelined computation [34]. Figure 2.2 presents a  $4 \times 4$  systolic array connecting all the processing element (PE) units squarely. These architectures are highly efficient as they extensively exploit data reuse. Due to their efficiency in convolution and matrix multiplication operations, systolic arrays have become the building blocks of neural network accelerators in systems such as Microsoft Brainwave [15] and Google's TPU [3].

Figure 2.2: A high level overview a traditional  $4 \times 4$  systolic array.

The performance of a systolic array depends on the underlying hardware architecture and dimensions. In this work, the systolic arrays closely follow a conventional systolic array design: processing elements take in two multiplier inputs (a, b) and an init (or flush) signal and are composed of a multiply-accumulate unit and a drain pipeline with a valid bit.

#### Under-utilization vs. Performance Gain

A fundamental limitation of mapping CNNs to systolic arrays is the threat of low array utilization. Since the computation workload in each layer is different, a one-size-fits-all systolic array will inevitably cause under-utilization. In Figure 2.3, we plot the percentage of the idle array and the cycle count needed against the size of the systolic array for the first convolution layer of GoogleNet V1 using SCALESim [47]. SCALESim [47] is a CNN accelerator simulator that provides a cycle-accurate timing based on a systolic array architecture.

Figure 2.3: Under-utilization percentage and cycle count against systolic array size.

As we can see, more arrays stay idle as the systolic array dimension increase, whereas the gain in cycle count becomes minimal. SCALESim [47] simulates the controller for feeding data into the systolic array in the simulation. Due to the implementation of the controller having a coarser update step-size, SCALESim use the same controller to feed a set of systolic arrays with different dimensions result in a mismatch. The unusual spikes in Figure 2.3 come from this quantization effect of SCALESim.

## 2.3 Xilinx Ultrascale Platform

We target the VU37P and VU9P chips on the Xilinx UltraScale platform. Some features specific to this platform allow us to realize a high-performance systolic array design on these chips.

#### Super Logic Regions (SLRs)

To accommodate the rapidly increasing capacity of Look-up Tables (LUTs), registers, Random Access Memory (RAM), and Digital Signal Processing (DSP) Blocks, manufacturers need to produce larger dies. Xilinx proposed their *Large FPGA Methodology* back in 2012, suggesting the architecture that mounts multiple SLR components on a passive silicon interposer where the SLR components connect to its adjacent SLR components via high-bandwidth, low latency connections called *Stacked Silicon Interconnect* (SSI)[61]. On VU37P and VU9P, there are three SLRs on both of the dies. Each SLR region contains multiple clock regions where the LUTs, RAMs, and DSP slices reside in a column arrangement. A device view of the die is provided in Figure 2.4.

Figure 2.4: Device view of VU37P and VU9P

### UltraScale DSP resource

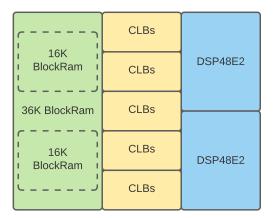

We construct the systolic array by utilizing the DSP slices on the FPGA. There are 6840 and 9024 DSP slices on VU37P and VU9P, respectively [57]. The DSP slices we are targeting are DSP48E2, an update of DSP48E1 from the 7-series FPGA. Some important improvements include a wider multiplier with  $27 \times 18$  and a wider pre-adder width of 27 bits. On top of improvements in the DSP computation capability, DSP resources are organized as a DSP tile on the device [58]. Each tile contains one 36K Block RAM, five configurable logic blocks (CLBs), and two DSP48E2 slices, as illustrated in Figure 2.5.

Figure 2.5: A structured view of a DSP tile on Xilinx UltraScale Platform

For VU37P, each SLR contains 24 clock regions with eight columns and four rows of DSP slices. In each SLR region, 32 columns of DSPs are spread across all clock regions in an asymmetry fashion. Each column in each SLR region has 94 rows meaning that each SLR region contains  $32 \times 94 = 3008$  DSP blocks. For VU9P, each SLR contains 30 clock regions with six columns and five rows of DSP slices. There are 19 columns of DSPs in each SLR region spread across all clock regions. Each column in each SLR region has 120 rows meaning that each SLR region contains  $19 \times 120 = 2280$  DSP blocks.

#### UltraScale memory resource

We utilize the on-chip memory to supply the data flowing into the systolic array. Instead of relying on the distributed RAM, we mainly depend on the block RAM hard blocks due to the better local connectivity, as shown in Figure 2.5. The specific hardblock we infer is RAMB36E2 which is also an update from their 7-series variant. These BRAMs consist of a 36Kbit storage area and two independent access ports [59]. We can treat these BRAMs as two independent 16Kb BRAM.

Other than the readily available BRAMs, the target device also provides UltraRAM and HBM DRAM in applications requiring more on-chip memory. UltraRAM is also compatible with the physical columnar architecture on the FPGA dies. Each clock region contains one column of 16 rows of UltraRAM blocks. UltraRAM is another flexible, high-density 288Kb memory block meaning that each UltraRAM block has 8× the capacity of a BRAM. However, the UltraRAM blocks have only one clock input and only support reading or writing per port per cycle.

Besides the memory embedded in the columnar architecture, VU37P also provides another memory stack - High Bandwidth Memory (HBM). Its physical location on the die was shown at the bottom of the device view in Figure 2.4. These memories can only be accessed via the  $16 \times 16$  AXI crossbar and require a specific AXI High Bandwidth Memory Controller for data transactions. We have summaries of the amount of on-chip memory available on VU37P and VU9P in Table 2.1

|               | VU37P | VU9P  |

|---------------|-------|-------|

| BRAM (Mb)     | 70.9  | 75.9  |

| UltraRAM (Mb) | 270.0 | 270.0 |

| HBM (GB)      | 8     | -     |

Table 2.1: Memory Resource Summary on VU37 and VU9P

## 2.4 Evolutionary algorithm

An Evolutionary algorithm [55, 22] is a class of algorithms that generates a set of individual candidates in every evolution to evaluate the problem space. These algorithms take inspiration from biological evolution with the idea of survival of the fittest. On an abstract level, the algorithm uses an objective function (fitness function) to evaluate the performance of candidates in each evolution. This type of algorithm selects top-performing candidates via the deterministicSurvivorSelection procedure and evolves the distribution representative of the solution space. The algorithm then produces the next generation of candidates with better fitness. This process repeats until future generations stop improving or the algorithm meets a user-defined termination condition.

This technique has been shown to solve complex *Black Box* optimization problems. The actual implementation is not bound to a specific agent or environment. The significant difference between different implementations depends on the *Adaptation Policy*, which determines how to pick the next generation, and the mathematical approach to estimate the expected reward for each generation. The *Adaptation Policy* affects the final quality of the solution by determining how to refine candidate solutions throughout the series of evolution steps. A set of mutations must be performed in each step to produce an ensemble of potential solution models. *Evolution Strategy* is effective for applications where the computation of gradients is intractable, allowing it to be a more robust solution compared to the traditional *Re-enforcement Learning* with back-propagation. In *Covariance*

*Matrix Adaptation Evolution Strategy* (CMA-ES), the algorithm can discover the problem structure by representing the candidate solution as a distribution of random variables.

### 2.4.1 Covariance Matrix Adaptation Evolution Strategy

We also experiment on two other optimization techniques - *Simple Genetic Algorithm* and *Hyperopt* before picking CMA-ES.

Simple Genetic Algorithm starts with an initial population pool where a global cost function is used to evaluate each individual. The algorithms then pick the portion of the population with the highest fitness score to create a mating pool where we perform a crossover operation between each set of the mating population to create a new generation of offspring. We then apply random mutation in the offspring and repeat the process until reaching a user-defined ending condition.

*Hyperopt* [8] is a library that provides parallelization infrastructure and three specific algorithms implementation, including 1) random search, 2) Tree of Parzen Estimators (TPE), and 3) Adaptive TPE to conduct Sequential model-based Bayesian optimization for hyperparameter optimization.

Our previous work [12] reveals that CMA-ES produces the best quality of results compared to these two techniques when adapted into a similar type of optimization problem.

In a simple *Evolution Strategy*, we sample the current generation of candidates from a normal distribution with a mean  $\mu_i$  and a fixed standard deviation  $\sigma$ . After evaluating the fitness of the entire population, we set  $\mu_{i+1}$  to be the best solution in the current population. We then sampled the next generation of candidates from this new normal distribution with  $\mu_{i+1}$  and  $\sigma$ .

The most significant difference of CMA-ES compared to the simple *Evolution Strategy* is that its *Adaptation Policy* allows adjustment to the search space for the next generation. This clever insight enables the algorithm to spread out and cover more search space when compared to the *Simple Genetic Algorithm*, which has a static noise and spread parameter across generations. CMA-ES samples the candidates from a multivariate normal distribution and its formal description is provided in Equation 2.3 [23].

$$x_{i+1}^k \sim \mu_i + \sigma_i \mathcal{N}(0, \mathcal{C}_i) \text{ for } k \in 1, ..., \lambda$$

(2.3)

In Equation 2.3,  $x_{i+1}^k$  is the k-th candidate in generation i + 1;  $\mu_i$  is the mean of the search distribution at generation i;  $\sigma_i$  is the standard deviation of the search distribution

at generation i;  $\sigma_i$  is the standard deviation of the search distribution at generation iand  $C_i$  is the covariance matrix of the search distribution at generation i.  $\mathcal{N}(0, C_i)$  is the multivariate normal distribution with zero mean and the covariance matrix  $C_i$ . At last,  $\lambda$ is the population size of each generation.

CMA-ES iteratively samples new generations of candidates via updating  $\mu$ ,  $\sigma$ , and C based on the population's fitness in the last generation. Instead of calculating the exact C, CMA-ES use the maximum likelihood estimate of the covariance matrix C. For a set of N two-dimensional random samplings (x, y), we estimate the two-dimensional C by calculating the following terms:

$$\mu_x = \frac{1}{N} \sum_{j=1}^{N} x_j \tag{2.4}$$

$$\mu_y = \frac{1}{N} \sum_{j=1}^N y_j$$

(2.5)

$$\sigma_x = \frac{1}{N} \sum_{j=1}^{N} (x_j - \mu_x)^2$$

(2.6)

$$\sigma_y = \frac{1}{N} \sum_{j=1}^{N} (y_j - \mu_y)^2$$

(2.7)

$$\sigma_{xy} = \frac{1}{N} \sum_{j=1}^{N} (x_j - \mu_x)(y_j - \mu_y)$$

(2.8)

However, the five terms  $\mu_x, \mu_y, \sigma_x, \sigma_y, \sigma_{xy}$  only provide us the estimate of two-dimensional covariance matrix in the current generation. To adjust and move the search space across the 2D plane, CMA-ES tweaks the covariance matrix update. CMA-ES achieves this by estimating the covariance matrix of the next generation by using a certain amount of best sampling from the current generation. It first calculates the x and y mean of the  $N_{best}$  samplings in the current generation.

$$mean_x = \frac{1}{N_{best}} \sum_{j=1}^{N_{best}} x_j \tag{2.9}$$

$$mean_y = \frac{1}{N_{best}} \sum_{j=1}^{N_{best}} y_j \tag{2.10}$$

To estimate the 2-dimensional covariance matrix for the next generation, we need three covariance terms:  $\sigma_x$ ,  $\sigma_y$  and  $\sigma_{xy}$ .

$$\sigma_x = \frac{1}{N_{best}} \sum_{j=1}^{N_{best}} (x_j - mean_x)^2$$

(2.11)

$$\sigma_y = \frac{1}{N_{best}} \sum_{j=1}^{N_{best}} (y_j - mean_y)^2$$

(2.12)

$$\sigma_{xy} = \frac{1}{N_{best}} \sum_{j=1}^{N_{best}} (x_j - mean_x)(y_j - mean_y)$$

(2.13)

The clever trick here is to calculate the average value of the selective  $N_{best}$  samplings in Equations 2.9 and 2.10 instead of using the average value over the entire population. This trick allows the algorithm to adjust the search space by estimating the covariance matrix of the next generation. Suppose we use the average value of the entire current generation. In that case, the result is just an estimation of the covariance matrix of the current generation, which does not help the algorithm adjust its search space. Finally, CMA-ES samples a new set of candidates from this new covariance matrix constructed with the updated mean  $mean_x$ ,  $mean_y$  and  $\sigma_x$ ,  $\sigma_y$ ,  $\sigma_{xy}$ .

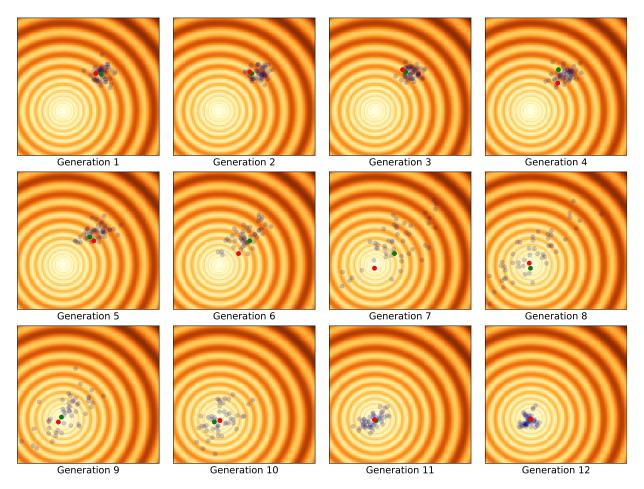

We apply CMA-ES on a shifted second-order Schaffer function, a standard testing function for black-box optimization [50, 14, 22], to visually demonstrate how a two-dimensional CMA-ES evolve across its early generations in Figure 2.6. Equation 2.14 defines a secondorder Schaffer function where its global minimum locates at (0,0).

$$f(x,y) = 0.5 + \frac{\sin^2(x^2 - y^2) - 0.5}{[1 + 0.001(x^2 - y^2)]^2}$$

(2.14)

We represent the best candidate of the current generation as a red dot and the best candidate of the last generation as a green dot. All the other samplings in that generation are represented as transparent blue dots. The global optimal in Figure 2.6 resides in the brightest spot at the bottom left corner - (-2, -2).

Figure 2.6: A visual presentation of CMA-ES candidates per generation

In Figure 2.6, the algorithm expands its search space starting at generation 3. By generation 9, the best candidates had already reached proximity to the global optimal.

We borrow an open-source python implementation of CMA-ES [24].

## 2.5 KnapSack Optimization Algorithm

The 2D knapsack is a family of problems in combinatorial optimization [1]. The general definition of the knapsack problem is "Given n items, each of a given size, and some bins of a certain capacity. Determine an assignment from item to bins using as few bins as

possible." [1, 10] When applied to a 2D space, this rectangular space is referred to as the "knapsack". The problem has been proven to be NP-hard [10]; a brute force approach with  $O(4^{c^2})$  runtime complexity [35] is the only way to find the optimal solution.

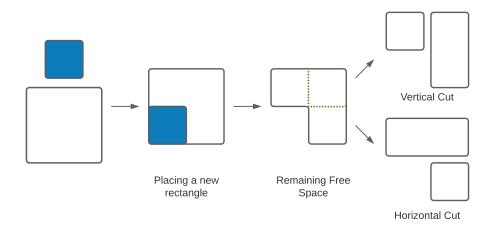

### 2.5.1 Maximal Rectangles Algorithm

The maximal rectangles algorithm [29] is a polynomial-time  $O(n^3)$  greedy algorithm for solving the 2D knapsack problem. This algorithm is an improvement from the *Guillotine* algorithm, another rectangular bin packing algorithm based on the *Guillotine split place*ment. The *Guillotine split placement* places the rectangles to the corner of a free knapsack and then splits the remaining L-shaped space into two disjoint free rectangles via either a horizontal or a vertical cut, as illustrated in Figure 2.7.

Figure 2.7: A visual presentation of guillotine split placement

The *Guillotine algorithm* starts with one new rectangular bin. It then performs the *Guillotine split placement* and creates a list of pairwise disjoint rectangles representing the remaining free space of such bin. It then iteratively repeats the cutting and replaces the original rectangular area with the two smaller rectangular spaces. This procedure then continues until none of the spaces in the list can fit the next item. The algorithm then works on the next bin if there is any.

The maximal rectangles algorithm is very similar to the *Guillotine algorithm*. However, it tweaks the *Guillotine split placement* procedure by considering both possible splits and adding both the rectangular space into the list. The variation of the maximal rectangles

algorithm will always pack the largest item in the queue in each iteration. The algorithm also ends when there are no more items to pack or more room in the bin.

In our optimizer, we adapt an open-source python implementation of the KnapSack algorithm called *RectPack* library [48].

## Chapter 3

## **Our Proposal**

## **3.1** Overall Architecture

This section proposes a throughput-optimized FPGA-based CNN accelerator using systolic array partitions. Next, we introduce splitting the FPGA into smaller replicating regions for further design exploration.

### 3.1.1 Multi Systolic Array Architecture

We present an overview of the accelerator's architecture in Figure 3.1. The architecture consists of multiple square systolic arrays where each systolic array partition operates at its optimal frequency with its separate clock input. Larger systolic array partitions usually operate at a lower frequency to avoid timing violations. If all the partitions follow the same clock input, the smaller partitions are not operating at their highest possible frequency. We, therefore, separate each partition's clock input, allowing all partitions to operate at their optimal frequency to improve the overall throughput performance. We first split the workload of a CNN into several groups continuously, meaning that each group will contain consecutive layers. We then assign each workload grouping to one systolic array partition. The whole architecture then processes the CNN in a pipelined fashion. We decide on this splitting method for these significant reasons 1) ensure high utilization of the FPGA resources, 2) simplify design space for optimization, and 3) allow independent frequency optimization for each array.

Figure 3.1: A visual presentation of the pipeline in the partitioned architecture.

Each systolic array operates at different frequencies while communicating to its neighboring arrays using the AXI interface. The AXI interfaces will adopt the global clock at 400 MHz syncing across all channels while the computation array uses a separate clock domain operating at around 600-700 MHz. Since the on-chip memory resource are limited, and CNNs with millions of parameters will easily exceed the storage capacity on the FPGA die, we need to stream the pixel and weight inputs from the external RAM to our systolic arrays.

We focus on using square-shaped systolic arrays since most of the CNNs' layers have square-sized kernels. Matching the array and kernel shape allows simpler and direct data movement where we can equally exploit data reuse along the horizontal and vertical axis in the systolic array.

### 3.1.2 Device Logic Region Splitting Technique

This section describes how we plan to explore designs targeting different regions on different FPGA die. We observe that we can exploit FPGA symmetry across SLRs and replicate designs. Instead of spreading the workload overall 3 SLRs, we configure our optimizer to only spread the workload on one SLR and half of one SLR. For results using one SLR, we convert the result to a full-chip design by replicating the smaller design three times, yielding the  $3\times$  replicating designs. We also convert the result to a full-chip design using half of the SLR by replicating the design six times, yielding the  $6\times$  replicating designs. We explore all of these design spaces by changing the configuration file of the optimizer.

To realize this replication concept in the optimizer, we create different *KnapSack profiles* for VU37P and VU9P. **xcvu37p-full** is the basic design with no replication and spreading partitions onto the full FPGA die. **xcvu37p-3-times** produce the 3× replicating design focusing on putting all partitions in one SLR region. Both **xcvu37p-6-times-x** and **xcvu37p-6-times-y** produce the 6× replicating design by splitting each SLR region in half along the x-axis and y-axis, respectively.

Figure 3.2: Visual representation of Knapsack profile modeling VU37P

However, each region is not symmetrical along the x-axis. Eleven columns are located in clock regions X0 - X2, and eight in clock regions X3 - X5. xcvu9p-full and xcvu9p-3-times follow similar ideas as xcvu37p-full and xcvu37p-3-times generating the non-replicating designs and the  $3 \times$  replicating designs respectively. xcvu9p-6-times-x-l restrict the design to the left side of the SLR region, including clock region X0 - X2 with 11 columns of DSPs. xcvu9p-6-times-x-r restrict the design to the right side of the SLR region, including clock region X0 - X2 with 11 columns of DSPs. xcvu9p-6-times-x-r restrict the design to the right side of the SLR region, including clock region X3 - X5 with eight columns of DSPs. xcvu9p-6-times-y

produce the  $6 \times$  replicating design by splitting each SLR region half along the y-axis.

Figure 3.3: Visual representing of Knapsack profile modeling VU9P

The complete configuration files targeting VU37P and VU9P are attached in Appendix D and E with the exact command to recreate the dataset we use for the analysis and result chapter.

# 3.2 Problem Formulation

This section introduces the challenges we encountered when reaching the proposed architecture on an FPGA. Next, we summarize all the constraints and combine them into one formulation.

## 3.2.1 Challenges

The proposed architecture has a huge design space and many tunable parameters. To obtain a feasible implementation with optimized throughput performance, we must consider the placement constraints and frequency performance implied by the underlying FPGA fabrics.

#### Mapping Computations to Partitions

To correctly map a CNN's computation to multiple partitions, we must tackle the problem of 1) splitting neural network layers across the arrays on the chip (workload allocation) and 2) sizing multiple systolic arrays (resource allocation). However, we cannot resolve these two problems separately. The optimal amount of resources allocated to a partition depends on the amount of workload allocated to this partition, while the optimal amount of workload allocated to this partition depends on the resources available. We create a nested loop design with CMA-ES to jointly search for the best resource and workload allocation to tackle this entangling problem.

#### **Placement Constraints**

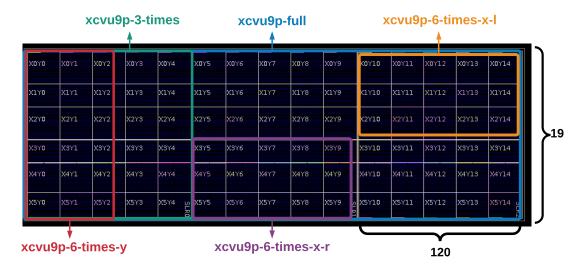

Assuming we now have a set of adequately sized systolic arrays, we still need to place and route each systolic array on the FPGA chip for the final design implementation. Unlike the previous architecture in Chan et al. [12], which relies on a limited 1D shape having a fixed  $9 \times 1920$  thin rectangular structure, fitting multiple arrays with arbitrary dimensions comes with the problem of "overlapping." When overlapping happens, the two partitions fight for the same resource on the FPGA dies, producing infeasible placement and implementation failure. One may argue that we can use the sum of area to determine whether a placement is possible. However, overlapping can still happen even when the total area sum of each partition is smaller than the area available in the grid, as shown in Figure 3.4.

Figure 3.4: A representation when overlapping occurs.

Avoiding overlapping objects is a primary consideration under the 2D knapsack problem formulation. We, therefore, model our DSP placement into a 2D knapsack problem. We model each partition as a unique object and the available DSP grid area as the knapsack. We also constrain each partition to be orthogonal to the edge of the knapsack, i.e., the edges of square partitions must be parallel to the edges of the bounding box. We abstract each SLR on the VU37P as a  $64 \times 94$  bin and each SLR on VU9P as a  $19 \times 120$  bin. This unique abstraction mimics the physical arrangement of DSP48E2 blocks on both chips. Thus, the 2D knapsack problem formulation for this case becomes: "Given a set p of square partition side lengths, determine whether all the squares in p can be packed into three  $X \times Y$  bins where the X and Y values vary depending on the target chip." While bin packing can introduce DSP wastage, most of our experiments with 100% DSP utilization fail in the routing stage.

#### **Frequency Optimization**

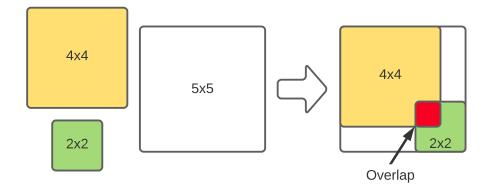

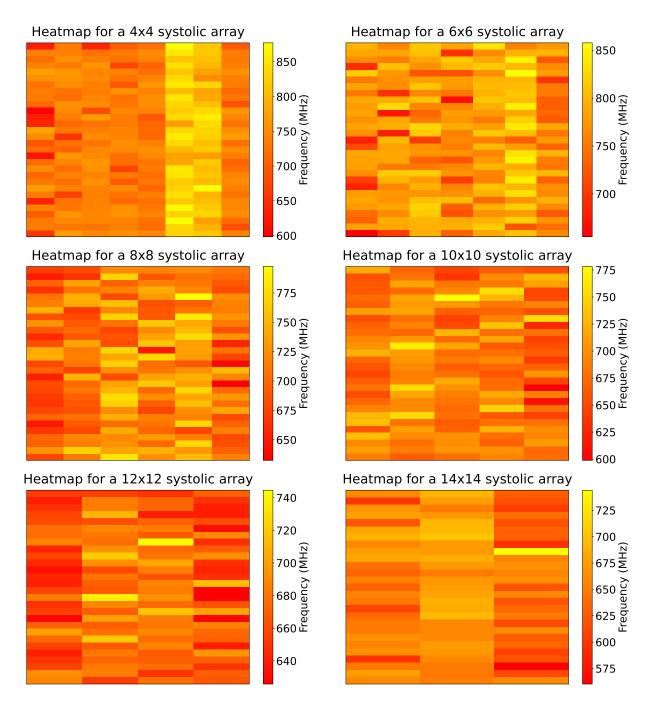

On top of fitting all the partitions on the FPGA, the placement of each partition can lead to varying operating frequencies for each systolic array. We demonstrate this property in Figures 3.5 and 3.6, presenting the frequency data when a  $2 \times 2$  systolic array being placed across the clock region X3Y0 to X5Y4 of VU9P. We collect the frequency data in the report after placing and routing a  $2 \times 2$  systolic array in every staggering location with a step size of 1 in both the vertical and horizontal directions. In Figure 3.5, we visualize the impact of different placement on the operating frequency of a systolic array. The yellower region represents a placed design with a higher operating frequency, whereas a block with a red block represents a design with a relatively lower operating frequency.

Frequency Heatmap for a 2x2 systolic array on VU9P

Figure 3.5: A heatmap representation of the operating frequency of a  $2 \times 2$  systolic array

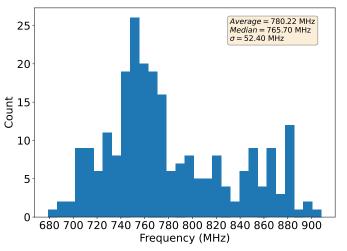

In Figure 3.6, we visualize the distribution of those frequencies in Figure 3.5. We can see that the frequency can vary from 678 MHz to 908 MHz depending on its placement on the FPGA die, even for a small  $2 \times 2$  systolic array.

Frequency Distribution for a 2x2 systolic array on VU9P

Figure 3.6: A distribution histogram of the operating frequency of a  $2 \times 2$  systolic array

In Figure 3.7, we can see this trend continues when we collect the frequency data for systolic arrays with larger dimensions. This frequency discrepancy is most likely due to the interleaving column arrangement of different hard blocks controlled by the manufacturer. A shift on the DSP placement constraints also alters the available LUTs, RAMs, and other hard blocks to be used in place and route, causing a different placement and routing result and thus affecting the frequency performance. This 230 MHz frequency gap leaves us considerable room for improvement to determine the best placement for each partition.

Figure 3.7: A heatmap visualization of frequencies collected covering clock region X3Y0 to X5Y4 on VU9P for systolic array size from  $4 \times 4$  up to  $14 \times 14$ .

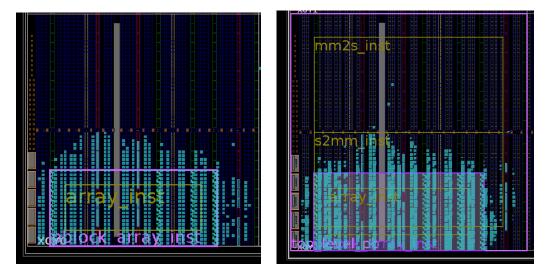

We present two implementations of the same  $8 \times 8$  systolic array subjecting to the same area constraints using the same source code. Using the recommended implementation flow suggested in Xilinx documentation, the implementation achieves operating frequency at 482 MHz, while the design using our custom Tcl script can achieve an implementation that operates at 576 MHz. We accomplish this by 1) selectively pre-routing some most critical paths before routing the entire design and 2) using a placement profile to force Vivido to place in a more congested fashion with our specific floorplanning constraints. This is another room for improvement for operating frequency.

Figure 3.8: A side-by-side device view of the same  $8 \times 8$  systolic array implemented by Vivado 2018.3 with default non-project flow (left) and own custom TCL flow (right).

To achieve the best frequency for each partition, we obtain a similar set of frequency distribution as we present in Figure 3.5 for every dimension of the systolic array on every possible placement. We then incorporate this data set into our optimization workflow. Since building this data set is tedious and time-consuming, we have developed custom scripts to speed up this one-time process.

### **3.2.2** Complete Formulation

The proposed architecture has a huge design space and many tunable parameters. To obtain a feasible implementation with optimized throughput performance, we must consider

the placement constraints and frequency performance implied by the underlying FPGA fabrics.

We provide a complete formulation, as shown in Equations 3.1 to 3.6, by combining 1) the overall architecture design, 2) the "packability" constraint, and 3) frequency optimization concern.

$$\min_{l,p} \left( \max_{x} \left( \sum_{y \in l[x]} \frac{cyc[y][p[x]]}{freq[p[x]][c[x]]} \right) \right), \text{ subject to:}$$

(3.1)

$$\forall x, p[x] \ge 2 \& p[x]\%2 = 0 \& \sum_{x=0}^{K-1} p[x]^2 \le MaxPEUnit$$

(3.2)

$$\forall x, l[x] \ge 1 \& \sum_{x=0}^{K-1} |l[x]| = N$$

(3.3)

$$\forall x, 0 \le c_x[x] < c_x[x] + p[x] \le W \tag{3.4}$$

$$\forall x, 0 \le c_y[x] < c_y[x] + p[x] \le H \tag{3.5}$$

$$\forall \text{ pairs}(i,j) \in x \text{ where } i \neq j, R(i) \cap R(j) = \emptyset$$

(3.6)

We provide the definition of the variables from Equation 3.1 to Equation 3.6 in Table 3.1

| Variable  | Definition                                                              |

|-----------|-------------------------------------------------------------------------|

| x         | Index of the partition                                                  |

| cyc[][]   | The timing model for the systolic array implementing a particular       |

|           | network layer                                                           |

| freq[][]  | The frequency model for a given systolic array size and location        |

| p[x]      | The dimension of the square array corresponding to partition $x$        |

| l[x]      | The set of layers mapped to the partition $x$                           |

| c[x]      | The representation of the location assignment containing the xy         |

|           | coordinate $(c_x[x], c_y[x])$ of the bottom-left corners of partition x |

| MaxPEUnit | The maximum available number of PE units available on the either        |

|           | chip. $MaxPEUnit = 13680$ for VU9P and $MaxPEUnit = 17280$              |

|           | for VU37P                                                               |

| W         | The width of the knapsack                                               |

| Н         | The the height of the knapsack                                          |

| R(x)      | The geometry 2D region covering the partition x where $R(x) =$          |

|           | $[[c_x[x], c_x[x] + p[x]], [c_y[x], c_y[x] + p[x]]]$                    |

Table 3.1: Variable definitions from Equation 3.1 to Equation 3.6

The 2D knapsack problem formulation is used to evaluate whether the constraint in Equations 3.4 to 3.6 is satisfied. Equations 3.4 and 3.5 restrict every partition to be within the boundary of the knapsack. Equations 3.6 prohibit the occurrence of overlapping between any pair of partitions. In the end, the optimizer needs to provide us a design solution containing a list of layers assigned to each partition (l), a list of dimensions for each partition (p), and a list of bounding boxes for each partition (c); in other words, a floorplan for a fully partitioned systolic array design. We can also change the bin dimension and the number of bins in Equations 3.4 and 3.5 to optimize specific clock regions instead of the whole SLR region on the die.

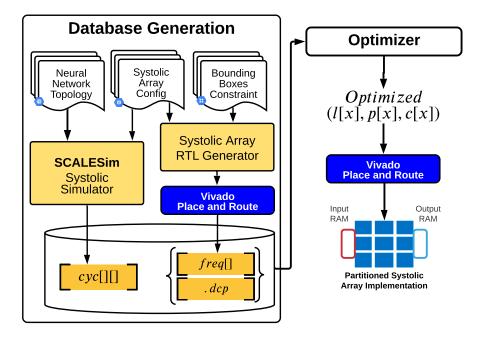

# 3.3 Workflow

This section provides an overview of our workflow containing two major stages - database generation and optimization. Then, we introduce what kind of data we need for the optimization and how to generate them. Finally, we explain the different variations of optimization we perform with our optimizer. In Figure 3.9, we provide a high-level overview of the entire workflow. We use custom scripts to generate the required cycle, cyc[][], frequency, freq[][] data and the design checkpoint (DCP), *.dcp* files in stage  $1 - Database \ Generation$ . The data is then used in stage 2 - Optimization. We search for a legal and optimized partitioned design in the second stage. We then realize the design by re-using the design checkpoint files from stage 1 to reassemble the design on the target device.

Figure 3.9: High-level diagram of the entire workflow.

### **3.3.1** Stage 1 – Database Generation

We present an overview of how we use each abstract input to create the database needed by the optimizer in Figure 3.9. We use two different sets of data to construct the database. We use SCALESim to build the cycle model - cycles[][], and the systolic array RTL generator to construct the frequency model - freq[][].

1. Cycle Modeling: To solve the optimization problem, we require an efficient method for calculating the number of cycles (*cycle*[][]) needed to compute the outputs for a layer given a systolic array configuration. To avoid doing RTL simulation for every

layer in every network with every possible array, we use SCALESim [47], a convolutional neural network simulator that provides cycle-accurate timing simulations for different accelerator configurations as shown in Figure ??. We provide SCALESim, the neural network topologies from MLPerf [43] and our configurations of the systolic arrays as input. This yields a pre-computed cycle dataset for every possible combination of layer type (convolution and fully-connected) and square systolic array size. We create custom scripts in Python to interface with SCALESim to automate and speed up the workflow. To cover more possible dimensions, we focus on even dimensions, increasing the systolic size N by a step size of 2.

- 2. Frequency Modelling: To accurately estimate the expected frequency of an  $N \times N$  systolic array on the target device, we develop custom Tcl scripts to scan the entire SLR systematically. We synthesize and place a square array within boundaries defined by a square Pblock of DSPs for a given dimension and location on the SLR. This process is repeated for every valid location across the SLR regions on VU37P and VU9P in a staggering fashion. We then collect all the timing summary reports and extract the necessary timing information. This empirical data set allows us to predict the maximum  $F_{max}$  of any candidate systolic array on the VU37P and VU9P.

- 3. Design Checkpoint Generation: Our custom Tcl scripts synthesize, place and route all the systolic arrays under the out-of-context mode using the non-project flow in Vivado 2018.3. We generate a checkpoint file of the design after the routing stage. This file preserves the exact placement and routing paths of all the LUTs and hard blocks in the systolic array. We can then re-apply these files directly to assemble the final design containing multiple systolic arrays. This approach allows us to maintain the frequency performance of each partition from the frequency data collection phase to the final re-assembly stage. We can guarantee the feasibility of the final design since each of the partitions has been successfully placed and routed in a previous stage.

## 3.3.2 Stage 2 – Optimization

#### Approach to 2D Partitioning

At a high level, our approach to 2D partitioning is inspired by the 1D partitioning approach proposed in our previous work [12]. Given a partition count K, the evolutionary algorithm we use CMA-ES to solve the optimization problem by assigning layers' workload to partitions (layers allocation). In each iteration of CMA-ES, we perform greedy partition sizing (resource allocation) on each population. We iteratively assign more processing elements (PE) to the bottleneck partition until no spare PE is available. Using the pre-computed cycle and frequency models, we calculate the cost of each population in terms of the runtime of the bottleneck partition. We then feed the cost back into the CMA-ES algorithm, and it will generate a new generation of layer assignments based on the given score. In Figure 3.10, we present the high-level overview of both the layer and resource allocation, indicating the data flow between the two main loops in our optimizer.

Figure 3.10: The optimization loop finds layer assignment l[x], resource allocation p[x], and placement allocation c[x] for a partition size K.

The sizing of each partition depends on the two following components:

• Binary Search: We use a binary search to find the maximum number of PE units that yield a resource assignment that is packable using the maximal rectangles algorithm on the specified layout constraint. We exploit the monotonic relationship between the number of allocated processing units and the packability of the corresponding assignment to achieve an optimal result. We use the maximal rectangles algorithm due to its fast polynomial runtime and availability in an existing software package, rectpack [48]. For most packable solutions, some DSP wastage will

be inevitable due to irregularities in the layout. The higher frequency of operation compensates for this. Furthermore, CMA-ES naturally decreases DSP wastage when solutions evolve to maximize throughput.

• Square Partition Sizing: We sweep across partition sizes in both dimensions with a step size of 2. This step size is selected since we allow double packing of two uint8 inputs on each DSP block, treating one DSP block as two systolic array PE units.

#### Variations of the 2D Partitioning Algorithm

We evaluate the following three variations of the 2D partitioning algorithm target design. The design shorthand name is shown in brackets.

- 1. Unconstrained Partition Sizing (Unconstrained): To determine the upper bound for throughput and latency improvements achievable by square partitioning, we evaluate the case where the chip (i.e., the 2D knapsack bin) is infinitely sized for placement freedom. The only limitation is that the number of PE units must be less than or equal to 17280, the number of DSPs on a VU37P. For VU9P, the PE units must be less than or equal to 13680.

- 2. **DSP Placement Aware Sizing**: We use the maximal rectangles algorithm to determine whether a resource allocation is feasible and can be packed onto the chip.

- (a) Unbounded Frequency (Unbounded): When calculating the frequency of each systolic array, the optimizer only considers the array dimensions. The expected  $F_{max}$  for one systolic array dimension is calculated as the average frequency across all positions on the board. The best result generated by this variation of the optimization process does not have the most accurate performance representation when we realize these designs on the target FPGA chip. The solution generated by this variation is packable, but the throughput is usually lower than the Unconstrained variant.

- (b) **Bounded Frequency** (Bounded): When calculating the frequency of each systolic array, both the array's dimensions and the placement location, provided by the maximal rectangles algorithm, are considered. This variation's packable solution generates the most accurate performance metrics when the design is placed and routed on the FPGA.

Figure 3.11 compares packing plans generated by each of the variations for *MobileNets*. The red boundaries signify DSP grid boundaries, magenta squares represent the slowest bottleneck partition, and the cyan squares represent non-bottleneck partitions. All three PE grids presented here are subject to the same dimensions. In most cases, packing awareness reduces DSP utilization but produces routable implementations, while 100% DSP utilization usually leads to unroutable designs or designs operating at very low frequencies.

Figure 3.11: Comparison between solutions generated by Unconstrained (left), Bounded (middle), and Unbounded (right).

Unconstrained provides a non-packable design with the second-best throughput. However, these designs are usually not optimized and provide a poor performance estimation since the design is usually very congested and has no placement guidance. Therefore, solutions generated by this variation are not feasible and will fail the routing stage. In our experiment, the very few that pass the routing stage result in a design operating at a low frequency of  $\approx 140$  MHz. After enabling the maximal rectangles algorithm, we can see that all the partitions will nicely fit into the PE grid boundaries for design in Unbounded and Bounded designs. In this specific case, Unbounded can provide a packable design while suffering throughput performance loss, while Bounded design is packable and has the highest throughput out of the three. We observe that packing awareness reduces DSP usage but produces more valid and routable solutions by leaving resource space on other hard blocks and routing.

# Chapter 4

# Implementations

# 4.1 Systolic Array Implementation

This section provides a detailed description of the specific systolic array architecture implementation. We also introduce how we inferred the various hard blocks available from the Xilinx Ultrascale+ family to construct the components needed in the systolic array.

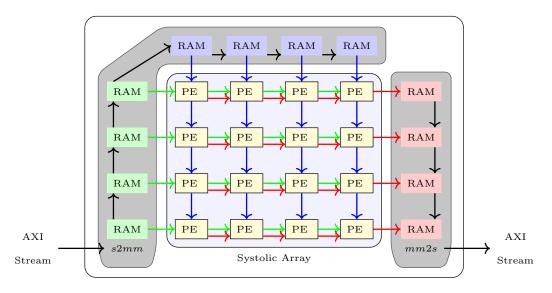

## 4.1.1 Systolic Array Architecture

We present an overview of the systolic array architecture used in this work in Figure 4.1 with the data flow. The green and blue arrows represent the data flow of the pixel matrix - A and the weight matrix - B, respectively. The red arrows represent the data flow of the output matrix - D. Each yellow block represents processing elements while the other blocks represent a mem block. The black arrows represent the data flow from the AXI interface to s2mm and mm2s to the AXI interface.

Figure 4.1: A high level overview of all the data flow in a  $4 \times 4$  systolic array.

We code this implementation in a combination of SystemVerilog and Verilog. We develop and run testbenches in ModelSim 2020.1 to demonstrate the functional correctness of computing different matrix sizes and the first layer of GoogLeNetV1. We identify a matrix multiplication of D = AB as having the pixel matrix A multiplied by the weight matrix B, giving us the result matrix D. There are four major components in our systolic array:

- On-chip IO handling: Each array has an *s2mm* component responsible for translating serial input into pixel and weight input responding to each row and column of the PE array matrix. In contrast, the *mm2s* component repacks output from each row back to one serial output. These components follow the reference AXI connection, allowing easy communication and utilizing RAMB18E2 available on Xilinx UltraScale architecture.

- Computation handling: Each array design can accommodate flexible square dimensions where each of the PE acts as multiply and accumulate (MAC) unit in a traditional systolic array design. We infer all the PEs as DSP48E2 hard blocks on VU37P and VU9P. Besides the simple input of one pixel per row, our computation array can also handle the double-packing of int8 pixel input.

- Variable Pipeline between PEs: To achieve high operating frequency, we have configurable pipeline stages between each PE block row-wise and column-wise. By

splitting the connection between each PE into multiple shorter paths, we can lower the routing difficulty significantly. This turns out to be one of the main contributors to retaining a high operating frequency even at larger dimensions.

• **Controller handling**: Each array has a controller unit to handle all the data coming to and from the AXI stream interfaces and the array. This configurable controller controls data movement from the IO unit to the computation unit by manipulating the reading and writing addresses to avoid excessive use of shift registers.