FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING DEGREE PROGRAMME IN ELECTRONICS AND COMMUNICATIONS ENGINEERING

# **MASTER'S THESIS**

# FIBER WEAVE SKEW AND COPPER ROUGHNESS -EFFECTS ON TRANSMISSION LINE PERFORMANCE ON PCB

AuthorOsmo KitunenSupervisorIlkka Nissinen

Second reviewer Timo Rahkonen

Technical advisor Pekka Kähkölä

August 2022

# Osmo Kitunen (2022) Fiber weave skew and copper roughness - effects on transmission line performance on PCB

University of Oulu, Faculty of Information Technology and Electrical Engineering, Degree Programme in Electronics and Communications Engineering 68 p

### ABSTRACT

Designing manufacturable high performing transmission lines is an essential part of modern electronics design work. This thesis focuses on interconnect design and simulation while also examining how materials and manufacturing affects the designed interconnect. The goal of this work is to find how big and what kind of effects different design and manufacturing variables have and how to be mindful of all the relevant factors during the design phase. Specific focus areas are fiber weave effect and losses caused by copper roughness. In this thesis theory behind transmission lines on PCB is outlined first along with different material properties and relevant material test methods. Effects of different design parameters and material properties are then examined through simulations and literature.

Accurate simulation of fiber weave skew with readily available simulation tools is difficult, but fiber weave skew itself can be mitigated with design choices. Copper roughness can be modelled with various models. Multiple different ways to represent copper roughness in the scope of PCB design exist. These various roughness representations are examined extensively through examples. Copper roughness was found to have significant effects on signal integrity and different roughness models were found to perform very differently.

Keywords: signal integrity, impedance, etch factor, skin effect, dielectric constant, dissipation factor.

# Osmo Kitunen (2022) Lasipunosajoitusvääristymän ja kuparin karkeuden vaikutukset siirtolinjojen suorituskykyyn piirilevyllä

Oulun yliopisto, tieto- ja sähkötekniikan tiedekunta, elektroniikan ja tietoliikennetekniikan tutkinto-ohjelma. Diplomityö 68 s

# TIIVISTELMÄ

Modernin elektroniikkasuunnittelun yksi keskeisistä osista on massatuotantokelpoisten korkean suorituskyvyn, siirtolinjojen suunnittelu. Tämä diplomityö keskittyy yhteyssuunnitteluun ja siirtolinjarakenteiden simulointiin piirilevyllä. Valmistusprosessien ja materiaalien vaikutuksia siirtolinjoihin tarkastellaan myös. Työn tavoitteena on selvittää kuinka paljon ja millaisia vaikutuksia eri suunnittelu- ja materiaalivalinnoilla on sekä miten suunnittelija voi parhaiten ottaa eri seikat huomioon suunnittelun eri vaiheissa. Tarkemmin tarkasteltavat ilmiöt ovat kuparin pinnan karkeuden aiheuttamat häviöt ja piirilevyn eristemateriaalin lasikuitupunosrakenteen aiheuttama ajoitusvääristymä. Teoria piirilevyllä oleville siirtolinjoille on esitelty erilaisten materiaaliominaisuuksien ja materiaalien testausmenetelmien ohella ensin. Teoriaosuuden jälkeen eri suunnitteluparametrien ja materiaaliominaisuuksien vaikutuksia tutkitaan simulaatioiden ja kirjallisuuden pohjalta.

Lasipunosajoitusvääristymän simulointi helposti saatavilla olevilla simulointityökaluilla on haasteellista, mutta ilmiön aiheuttamia vaikutuksia on mahdollista pienentää erilaisilla suunnitteluratkaisuilla. Kuparin karkeuden mallintamiseen on tarjolla useita erilaisia simulointimalleja. Lisäksi kuparin karkeus voidaan esittää usealla eri tavalla. Erilaisia kuparin karkeuden esitystapoja piirilevykontekstissa on tarkasteltu kattavasti esimerkkien kautta. Kuparin karkeuden todettiin vaikuttavan signaalien vaimentumiseen merkittävästi ja eri karkeusmallien huomattiin palauttavan huomattavasti toisistaan poikkeavia tuloksia.

Avainsanat: signaalin eheys, impedanssi, etsauskerroin, skin-efekti, eristevakio, häviökerroin.

# **TABLE OF CONTENTS**

| AI | BSTR       | ACT                                                 | 2  |

|----|------------|-----------------------------------------------------|----|

| ΤI | IVIS       | ELMÄ                                                | 3  |

| TA | BLE        | OF CONTENTS                                         | 5  |

| FC | OREV       | ORD                                                 | 6  |

| LI | ST O       | F ABBREVIATIONS AND SYMBOLS                         | 7  |

| 1  | INT        | RODUCTION                                           | 10 |

| 2  | CHA        | LLENGES OF HIGH-SPEED DIGITAL ON PCB                | 12 |

|    | 2.1        | Transmission line impedance                         | 13 |

|    |            | 2.1.1 Reflections                                   | 19 |

|    | 2.2        | Crosstalk                                           | 20 |

|    | 2.3        | Signal losses                                       | 24 |

|    |            | 2.3.1 Dielectric losses                             | 24 |

|    |            | 2.3.2 Conductor losses                              | 24 |

|    |            | 2.3.3 Skin effect                                   | 25 |

|    | 2.4        | Propagation delay and Skew                          | 26 |

| 3  | PCB        | MATERIAL PROPERTIES                                 | 27 |

|    | 3.1        | Core and Prepreg                                    | 28 |

|    |            | 3.1.1 Relative dielectric constant and loss tangent | 28 |

|    |            | 3.1.2 Dk and Df test methods                        | 30 |

|    |            | 3.1.3 Glass Styles                                  | 31 |

|    | 3.2        | Copper foils                                        | 33 |

|    |            | 3.2.1 Rolled Copper                                 | 33 |

|    |            | 3.2.2 Electrodeposited copper                       | 33 |

|    |            | 3.2.3 Reverse treated foil                          | 34 |

|    | 3.3        | Copper properties                                   | 34 |

|    |            | 3.3.1 Copper thickness                              | 34 |

|    |            | 3.3.2 Copper roughness                              | 35 |

|    | <b>•</b> · | 3.3.3 Roughness unit summary                        | 38 |

|    | 3.4        | Solder mask and surface finishes                    | 39 |

| 4  | MIT        | IGATING MATERIAL AND MANUFACTURING IMPERFECTIONS    | 41 |

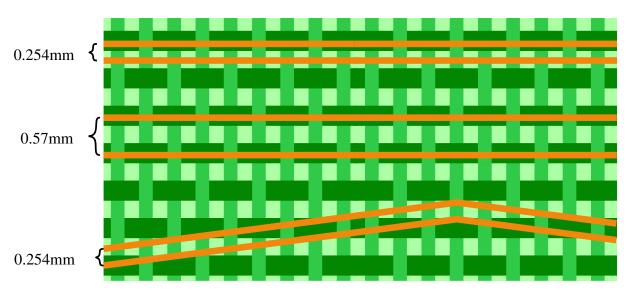

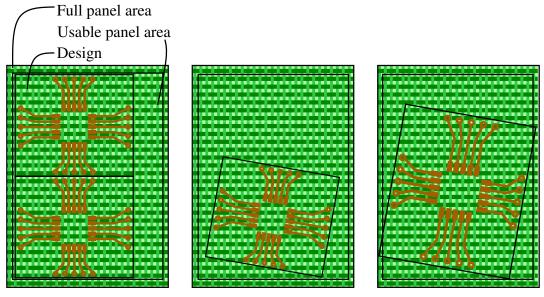

|    | 4.1        | Fiber weave skew                                    | 41 |

|    |            | 4.1.1 Production panel tilting and zigzag routing   | 42 |

|    |      | 4.1.2 Glass fabric selection                   | 43 |

|----|------|------------------------------------------------|----|

|    |      | 4.1.3 Using wider transmission line traces     | 44 |

|    | 4.2  | Conductor uncertainties                        | 46 |

|    |      | 4.2.1 Surface roughness                        | 46 |

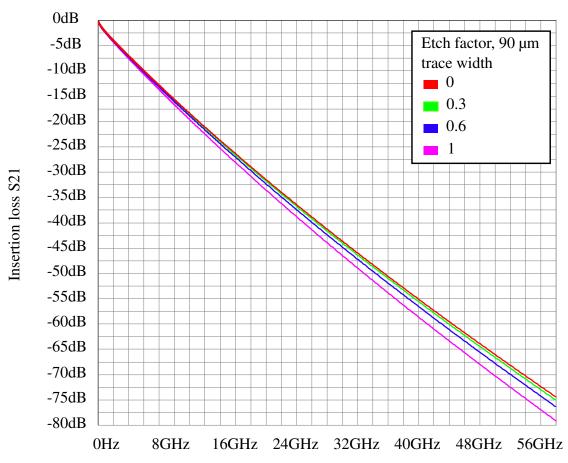

|    |      | 4.2.2 Etch factor                              | 53 |

|    | 4.3  | Combined effects                               | 54 |

|    | 4.4  | Summary of loss and skew mitigation strategies | 55 |

| 5  | DISC | CUSSION                                        | 57 |

| 6  | SUM  | IMARY                                          | 60 |

| RE | FER  | ENCES                                          | 66 |

#### FOREWORD

For my thesis work I wanted to make sure that the subject is genuinely interesting to me and also that the outcomes of the work are useful. I am convinced that this thesis has met both of those requirements. Working on this thesis has been a blast and a great learning experience. Initially I thought that I knew something about printed circuit boards, but it quickly turned out that my initial knowledge was greatly limited. At the beginning of this thesis work learning about all the various factors that need to be considered when designing a high-speed digital PCB felt overwhelming. Judy Warner, as the host of Altium OnTrack podcast said something along the lines: *"it is like drinking from a fire hose"* when she was discussing PCB materials with the Technical Marketing Manager at Rogers Corp, John Coonrod. That quote summarizes quite accurately how I felt when I tried to wrap my head around the subject of this thesis. However, as I delved deeper into the details, things started to make more and more sense and eventually I understood the big picture well enough that I could start compiling this thesis.

I would like to express my gratitude to everyone involved in the subject brainstorming phase and to everyone who shared their knowledge along the way and helped me to put this thesis together. Special thanks to my line manager Markus and to my technical Advisor Pekka, for supporting this work and sharing their ideas and expertise. I would also like to thank Nokia for offering me this thesis work opportunity.

Oulu, 14.07.2022

Osmo Kitunen

# LIST OF ABBREVIATIONS AND SYMBOLS

| 5G        | Fifth generation (mobile network)                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------|

| BGA       | Ball Grid Array - Surface mount component package type                                                    |

| BW        | Bandwidth                                                                                                 |

| CTE       | Coefficient of thermal expansion                                                                          |

| DC        | Direct Current                                                                                            |

| Df        | Dissipation factor                                                                                        |

| DIN       | Deutsches Institut für Normung - German standardization organization                                      |

| Dk        | Relative dielectric constant                                                                              |

| ED copper | Electro-Deposited copper                                                                                  |

| EM        | Electromagnetic                                                                                           |

| EMI       | Electromagnetic interference                                                                              |

| ENIG      | Electronless nickel immersion gold - surface finish for exposed conductors on a PCB                       |

| FEXT      | Far-end crosstalk                                                                                         |

| FR-4      | Common name for woven glass-reinforced epoxy PCB laminates. FR stands for "Flame retardant".              |

| FWE       | Fiber weave effect - same as glass weave effect                                                           |

| FWS       | Fiber weave skew                                                                                          |

| GBd       | Giga Baud - unit for signaling speed                                                                      |

| GIGO      | Garbage in Garbage out                                                                                    |

| GWE       | Glass weave effect - same as fiber weave effect                                                           |

| GWS       | Glass weave skew                                                                                          |

| HASL      | Hot sir solder leveling - surface finish for exposed conductors on a PCB                                  |

| IPC       | Standardization organization specializing to standardizing printed circuit board design and manufacturing |

| ISI       | Inter-symbol interference                                                                                 |

| JIS       | Japanese Industrial Standards                                                                             |

| NRZ       | Non-return-to-zero - modulation for serial signaling one bit per unit interval                            |

| NEXT      | Near-end crosstalk                                                                                        |

| PAM4      | Pulse amplitude modulation 4-level - modulation for serial signaling two bits encoded to one UI           |

| PCB       | Printed circuit board                                                                                     |

| PI        | Power Integrity                                                                                           |

|           |                                                                                                           |

| RA copper | Rolled-annealed copper                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------|

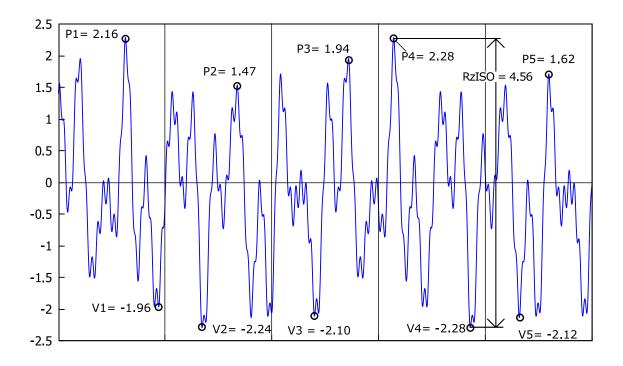

| Ra        | Roughness Average - surface roughness parameter                                                          |

| Rq        | Same as Root Mean Square Roughness Average - surface roughness parameter                                 |

| RMS       | Root Mean Square                                                                                         |

| Rrms      | Root Mean Square Roughness Average - surface roughness parameter                                         |

| RTF       | Reverse Treat Foil                                                                                       |

| Rz        | Maximum height of the profile - surface roughness parameter with varying def-<br>initions                |

| SI        | Signal Integrity                                                                                         |

| UI        | Unit Interval - Single symbol duration in serial communication                                           |

| via       | Plated structure connecting PCB layers together, not intended to be used as component mounting hole. [1] |

| VLP       | Very Low Profile - surface finish name for copper foil.                                                  |

|           |                                                                                                          |

| ft        | feet - imperial unit for length equal to 0.3048 meters                                                   |

| Oz        | ounce - imperial unit for weight equal to 28.34 grams                                                    |

| С         | symbol for capacitance                                                                                   |

| $C_{mL}$  | mutual capacitance per unit length                                                                       |

| $C_L$     | capacitance per unit length of the signal trace                                                          |

| С         | speed of light, 299 792 458 m/s                                                                          |

| D1        | dielectric thickness between transmission line and it's (top) reference plane                            |

| D2        | dielectric thickness between transmission line and it's (bottom) reference plane                         |

| D3        | distance between differential transmission lines. Edge-to-edge spacing                                   |

| F         | farad, unit for capacitance                                                                              |

| f         | symbol for frequency                                                                                     |

| fknee     | knee frequency, most of digital signal's spectral content of is below knee fre-<br>quency                |

| Н         | henry, unit for inductance                                                                               |

| L         | symbol for inductance                                                                                    |

| $L_L$     | inductance per unit length of the signal trace                                                           |

| $L_{mL}$  | mutual inductance per unit length                                                                        |

| R         | symbol for resistance                                                                                    |

| Т         | transmission line thickness                                                                              |

| $T_d$     | time delay                                                                                               |

| t <sub>r</sub>             | <i>t<sub>rise</sub></i> - rise time                |

|----------------------------|----------------------------------------------------|

| $V_a$                      | voltage of the signal line                         |

| $V_f$                      | voltage at the far end of the quiet line           |

| $V_b$                      | backward direction voltage noise on the quiet line |

| V                          | symbol for (signal) speed                          |

| W1                         | transmission line width top side                   |

| W2                         | transmission line width bottom side                |

|                            |                                                    |

| δ                          | skin depth not to be confused with loss angle      |

| $\mathcal{E}_r$            | same as Dk                                         |

| ρ                          | symbol for resistivity                             |

|                            |                                                    |

| $tan(\boldsymbol{\delta})$ | tan of loss angle, Same ass dissipation factor     |

|                            |                                                    |

# 1. INTRODUCTION

High-speed digital data transmission is core functionality of any modern telecommunication or computing device. Demand for faster data rates with as little added cost as possible is here to stay. The number of connected devices increases, processors become faster, and demand for high bitrate content streaming keeps growing. The aforementioned are just few factors driving the need for speed also under the hood of the technology that keeps the wheels of the modern world turning. Fifth generation (5G) mobile networks can offer up to 1 Gbps data rates for individual users [2]. While the massive data rates delivered by 5G network equipment require sophisticated radio hardware, high performance radio hardware is more or less useless if it is not backed up with equally performing hardware all the way to the core network. Not to mention data centers that serve massive amounts of content over the internet. High speed interconnects are everywhere.

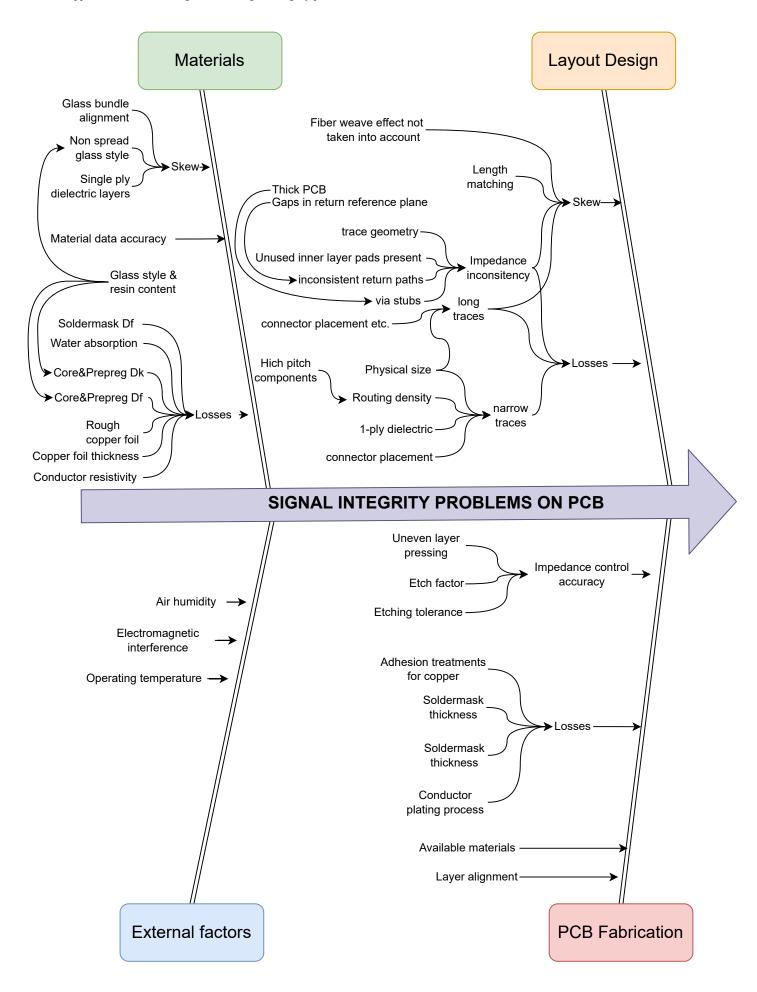

Signals travel between and within systems on different kinds of interconnects such as cables and PCB (Printed Circuit Board) traces. Each of these interconnects is a transmission line. Transmission line is just a signal conductor and a return path. Both of which influence equally to the transmission line performance unless the interconnect is transparent. Interconnect is called transparent if it has no effect on signal quality. Low speed signals i.e., signals with long rise times or short enough interconnects lead to interconnects looking transparent to the signal [3]. Practical high-speed transmission lines on PCB are basically never transparent. There are numerous factors that influence the interconnect performance on PCB: Solder joints between components and PCB, shapes of the solder lands, holes (vias and trough hole pins), connectors, PCB dielectric materials, copper properties, interconnect geometry and layers adjacent to the interconnect as well as other nearby interconnects on the PCB. This thesis will focus on the effects caused by PCB material properties and explore some ways to maintain signal quality as good as possible. The specific focus areas are fiber weave skew and signal degradation caused by copper roughness. Fiber weave skew is caused by non-uniform nature of common PCB materials: Dielectric properties are not constant across the entire PCB, which causes signals to behave differently in different points on the PCB. Copper roughness on the other hand refers to  $\mu$ *m*-scale bumps in the copper surface. These small variations in the conductive surface attenuate signals, especially the high frequency components. The presented mitigation strategies will be supported by literature and simulations where possible.

Transmission lines can be either single-ended or differential. In the scope of high-speed digital most interconnects are differential hence differential pair transmission lines will be examined in this thesis. Differential pair transmission line is essentially just two single-ended transmission lines used to transport a differential signal. While differential signaling offers benefits over single-ended signaling there are also some tradeoffs. Benefits of differential signaling include improved resilience to common mode crosstalk and discontinuities, possibility to use longer rise time drivers and possibility to use higher gain at the receiver. The cost of mentioned benefits is need for more PCB surface area and added complexity. One differential signal requires two conductors and a return path while one single-ended signal only needs one signal and a return path. Differential transmission lines offer more variables that require designer's attention. While this gives room for more versatile design decisions it also adds to the complexity of the design. [4]

Successful interconnect design requires materials understanding, knowledge on how transmission lines behave and awareness on how signals behave while propagating in a transmission line. These topics are described in sufficient detail for the purposes of this thesis in chapters 2 and 3. Ways to counter the performance degrading material effects using the available design variables is discussed in chapter 4, where topics outlined in earlier chapters will be examined from a more practical point of view. Some topics this thesis tries to clarify are:

- Design parameters that are crucial for signal integrity simulations

- The best format to input data to simulators

- Practical signal integrity effects due to imperfections in the PCB manufacturing process

- Is it worthwhile to consider certain effects or will they be negligible in comparison to other factors

- Scales of different effects and relationships between them

- The combined effects of different signal quality degrading factors

Design tool manuals can be very ambiguous when it comes to explaining what different options and parameters actually do. Trying to find an answer that should read directly in the tool's manual from different documentation sources can be a real chore. Lack of quick and easy access to accurate information on what one should input to the simulator, what different simulation options do and when to use each option available in a software is a factor that can worsen the simulation result quality.

# 2. CHALLENGES OF HIGH-SPEED DIGITAL ON PCB

This chapter outlines the general design considerations that constrain a high-speed transmission line. Material considerations are discussed in chapter 3 right after this chapter. High-speed digital signals are wideband from Direct current (DC) to some frequency defined by the shortest rise (or fall) time present in the signal. The data rate of the signal does not determine the signal bandwidth, but high data rate signals need short rise and fall times as the bit durations are short. Signal bandwidth can be approximated with

$$BW = \frac{0.35}{t_{rise}} \tag{1}$$

where *BW* is signal bandwidth and  $t_{rise}$  is signal rise time [4]. If rise time is given in nanoseconds the bandwidth will be in gigahertz. Equation (1) does not approximate the full spectral content of a signal but is rather an assumption of the midpoint of the spectral content associated with the rise time. The upper frequency limit of a digital signal is described with knee frequency

$$f_{knee} = \frac{0.5}{t_{rise}} \tag{2}$$

where  $f_{knee}$  is the knee frequency and  $t_{rise}$  is once again the rise time [5]. The knee frequency is the frequency below which most of the spectral content of a digital signal is. The wideband nature of digital signals imposes constraints to transmission line design as real transmission lines function as low pass filters to some extent. Real world conductors attenuate all frequencies, but different phenomena attenuate high frequencies more than low frequencies thus essentially turning transmission line into a low pass filter.

Along with as low loss as possible, conductors used for high-speed digital signals need to have constant electrical properties all the way from the transmitter to the receiver. Changes in interconnect impedance cause reflections that degrade signal quality. Propagation delay differences between signal conductors cause timing problems and intra-pair skew in differential signals. [4] Intra-pair skew can start causing bit errors with short bit durations. Modern serial differential communication protocols have bit durations that are less than 100 ps, for such short bits intra pair skew tolerance is poor.

Fast signals require that signal voltage levels are kept as low as possible. The lower the logic 1 voltage is the smaller is the slew rate required to achieve certain rise time [3]. Slew rate describes how much driver output can change its voltage level in a time unit [6]. Low voltage levels make signals more susceptible for interference from the surrounding environment as relatively small, coupled voltages can be significant at the receiver when compared to the actual signal. Crosstalk i.e., the undesired coupling between neighboring traces should be kept as low as possible by simply leaving enough space between conductors that should not be coupled [1]. A run-through of factors affecting high-speed digital designs is presented in table 2.1.

| Design parameter  | Describes                                                                                                                                                         | Constant with frequency | Ideal value                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------|

| Trace Impedance   | In this document the<br>time domain input<br>impedance of a trace                                                                                                 | Yes                     | Constant. Matched<br>to driver's output<br>impedance. Usually<br>50 Ω. |

| Dielectric losses | Signal losses caused<br>in the dielectric<br>material to the<br>propagating<br>electromagnetic<br>(EM) wave                                                       | No                      | As low as possible                                                     |

| Conductor losses  | Signal losses due to<br>conductor<br>resistance, skin<br>effect and copper<br>surface roughness                                                                   | No                      | As low as possible                                                     |

| Skew              | Timing difference<br>between signals                                                                                                                              | No                      | As low as possible                                                     |

| Crosstalk         | Unwanted energy<br>transfer between<br>adjacent conductors<br>due to mutual<br>inductance and<br>capacitance [1]                                                  | No                      | As low as possible                                                     |

| Propagation speed | Signal speed (speed<br>of light in the<br>dielectric material)<br>in a transmission<br>line, determined by<br>dielectric constant<br>of the substrate<br>material | No                      | Constant                                                               |

Table 2.1 High-speed design considerations

### 2.1. Transmission line impedance

Transmission line impedance is one key consideration in interconnect design. Usually, the desired impedance is close to  $50 \Omega$ , but not necessarily exactly that. The required impedance is defined by the signaling protocol usually with allowable impedance tolerance around 10% [7–9]. Table 2.2 lists impedances used by different protocols also more specific impedance tolerances are available on the table apart from USB4. Lower impedance generally yields lower crosstalk while higher impedance requires larger termination resistances which dissipate less power [3].

| Protocol                  | Single-ended impedance    | Differential impedance |

|---------------------------|---------------------------|------------------------|

| PCIe Gen 3 and 4 [10, 11] | $42.5\Omega\pm5\%$        | $85\Omega\pm5\%$       |

| DDR2, DDR3, DDR4 [8]      | $50 - 60 \Omega \pm 10\%$ | $100\Omega\pm10\%$     |

| USB2 [9]                  |                           | $90\Omega\pm15\%$      |

| USB4 [12]                 | 42.5 Ω                    |                        |

| Ethernet [7]              | $50\Omega\pm10\%$         | $100\Omega\pm10\%$     |

Table 2.2 Impedances utilized by common differential signaling protocols. Single-ended or differential impedance listed based on what was available in specifications.

Transmission line impedance is not just one value. Impedance is different in time and frequency domains moreover the time domain impedance of a transmission line may not be constant. In the scope of high-speed digital the time domain impedance is of a bigger interest than the frequency domain impedance. Frequency domain transmission line impedance is the steady state input impedance including all reflections that happen in the transmission line and it is useful for RF considerations. In the time domain the more interesting impedance is the impedance seen by the signal as it propagates in the transmission line, this impedance is called the instantaneous impedance. In a uniform transmission line i.e., transmission line that is physically uniform throughout its entire length the instantaneous impedance is the characteristic impedance. For non-uniform transmission lines characteristic impedance cannot be defined as there is no single impedance that would characterize the entire transmission line. Non-uniform transmission lines need to be broken into uniform sections if there is need to describe them in terms of characteristic impedance. The input impedance of a uniform transmission line in the time domain is initially the characteristic impedance of the transmission line and the termination impedance in the steady state. If a step stimulus is launched into a uniform transmission line the input impedance stays constant until the signal has propagated all the way to the end of the transmission line and back. The signal that travels back to the source provides information on how the transmission line is terminated as a reflection. If the input impedance stays constant indefinitely the transmission line is either indefinitely long or perfectly terminated. [3]

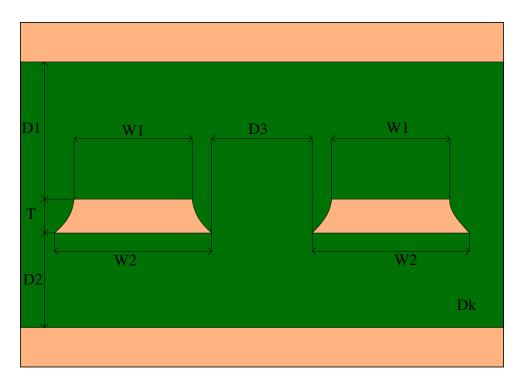

Materials and transmission line geometry determine the characteristic impedance. Dimensions relevant to transmission line impedance have been annotated in figure 2.1 and explained in table 2.3. To keep transmission line uniform and its impedance constant all the listed parameters need to stay constant. The easiest and most reliable way to obtain the transmission line impedance from these parameters is to plug values into an EM field solver and let a computer program solve the impedance. Trace edges are drawn concave to visualize the actual trace edge on a finished PCB. Trace edges become slightly trapezoidal and concave. The origin of finished conductor shape is explained in chapter 3. This trapezoidal conductor shape is described with a parameter called etch factor, which can be approximated with

$$Etch \ Factor = \frac{W2 - W1}{T} \tag{3}$$

Where W1, W2 and T are as defined in figure 2.1. The difference between W1 and W2 is called etchback. The amount of etchback will vary per fabricator and copper thickness. [13]

Figure 2.1. Dimensions affecting stripline trace impedance

Table 2.3 Symbols used in figure 2.1

| Symbol | Description                                                                    |  |

|--------|--------------------------------------------------------------------------------|--|

| D1     | Distance between transmission line and reference plane in the case of a        |  |

|        | symmetrical stripline same as D2                                               |  |

| D2     | Distance between transmission line and reference plane in the case of a        |  |

|        | symmetrical stripline same as D1                                               |  |

| D3     | Distance between differential pair transmission lines, Edge-to-edge            |  |

| 05     | spacing. Can be used to adjust differential impedance.                         |  |

| W1     | Transmission line width top side, one factor determining etch factor           |  |

| W2     | Transmission line width bottom side, one factor determining etch factor        |  |

| Т      | Transmission line thickness, one factor determining etch factor                |  |

| Dk     | Relative permittivity of the dielectric material (green area) i.e., dielectric |  |

|        | constant                                                                       |  |

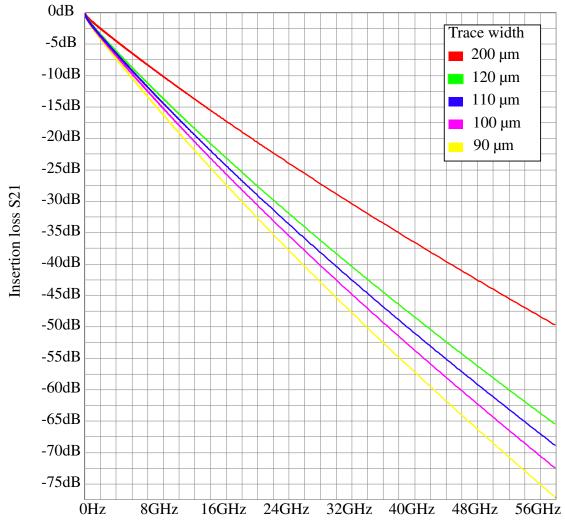

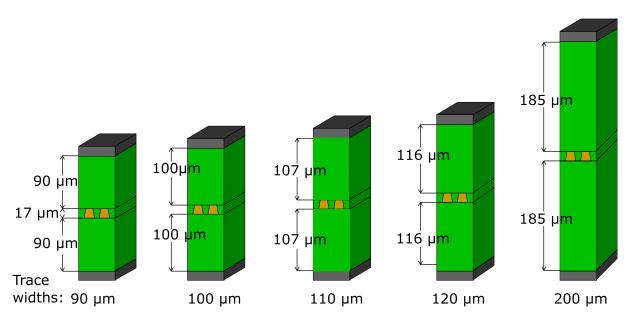

Transmission line dimensions do not only affect the impedance of the transmission line but also have various effects. Distances to reference planes (D1 and D2) obviously affect the final PCB thickness. Additionally, as reference planes are brought closer to a trace the trace impedance will decrease as the coupling between the trace and its reference plane becomes stronger. To maintain the same trace impedance trace width needs to be shrunken assuming that dielectric material stays the same. Thinner traces take less physical space on the PCB but also are more lossy than wider traces. Differential impedance can be adjusted with trace edge-to-edge spacing D3, however edge-to-edge spacing only affects impedance if there is meaningful coupling between the traces. See figure 2.5.

Keeping transmission line's physical dimensions constant might seem like a trivial task. However, things get quickly complicated when routing a signal from a surface mounted device to an internal signal layer and back to the surface of the PCB and to another device or possibly even a connector. How to keep impedance constant when changing PCB layers? Which layer should the signal be routed on to maximize performance and minimize via stubs (=unused remainders of a vias)? What needs to be considered when maneuvering transmission lines between other features on the PCB? How long trace can still work reliably for a certain signal? When it comes to bends and corners in the trace the most important thing is to keep the width of the trace constant by either chamfering corners or by using rounded corners/curved traces. With differential signals corners and bends result in length difference between the traces, which will cause skew that may need to be compensated. On the other hand, vias are a complicated matter by themselves. One particularly important thing to ensure smooth layer transitions using vias is to design current return paths the signal via is the solution as the via connected to reference planes will serve as current return path. Proper current return paths for layer changes also help to contain the electromagnetic interference (EMI) emissions of the board. Calculating via impedances is difficult and the best results are achieved using 3D EM field solver.

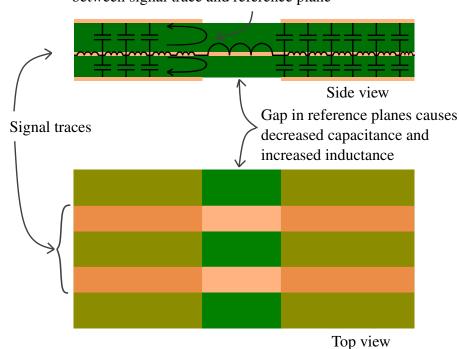

Discontinuities in current return path (e.g., gaps in reference plane, traces, component footprints, copper keep-outs around holes etc.) can cause impedance discontinuities. In case of a gap in a reference plane the reference plane effectively vanishes or jumps one layer further away, which will largely affect impedance. Figure 2.2 visualizes a differential stripline transmission line with a discontinuity in the reference plane. Return current will cross the gap by flowing somewhere else, which will spread out the EM field. Higher impedance section caused by the gap will also increase transmission line insertion loss and cause reflections. On high frequencies return currents travel as close to the signal conductor as possible due to skin effect. Effectively this means that return current flow on the reference plane(s) follows signal trace very closely. Skin effect is explored in further detail later in this chapter.

Return current flow charges capacitance between signal trace and reference plane

Figure 2.2. Reference planes needs to be present and continuous for a high-speed digital transmission line to work properly. This needs to be considered in the PCB layout phase.

For differential signals all factors mentioned above apply, however there are also other things to consider. Coupling between differential traces improves noise immunity and allows higher interconnect density on the PCB as traces are closer together. Increased coupling between two traces increases their mutual capacitance and inductance per length. Therefore, differential impedance of the interconnect decreases, which needs to be accounted for in the impedance planning design phase by either using narrower traces or by moving reference planes further away. If there is no coupling between two traces forming a differential pair the differential impedance will simply be two times the single-ended impedance. As the coupling between traces increases the differential impedance decreases, but single-ended impedance stays constant. This effectively means that common-mode signals and differential signals see different instantaneous impedances when propagating in the transmission line. Differential pair does not need to have any coupling between the traces, the only requirements are constant impedances and length matching to a degree determined by the bitrate of the signal [14]. [4]

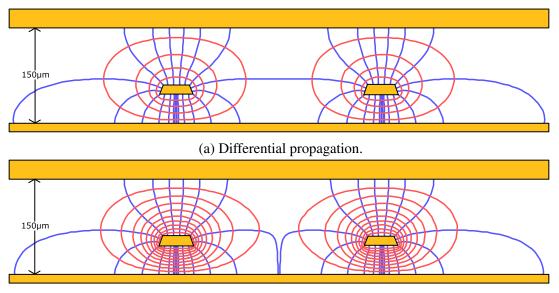

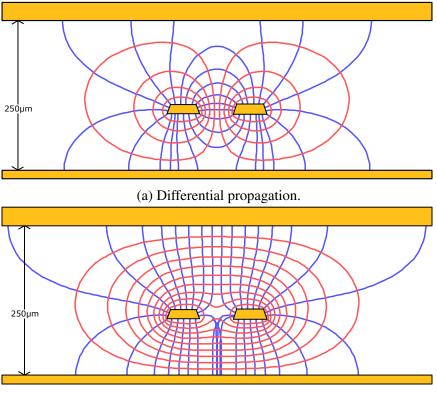

In figures 2.3 and 2.4 electromagnetic fields in differential and common propagation modes are shown for two different asymmetrical stripline configurations consisting of two stripline transmission lines. Figures 2.3 (a) and 2.3 (b) show differential striplines with 50  $\Omega$  singleended impedance and 100  $\Omega$  differential impedance and figures 2.4 (a) and 2.4 (b) show a differential transmission line with single-ended impedance around 66  $\Omega$  and differential impedance at 100  $\Omega$ . Magnetic fields are drawn in red and electric fields in blue. With reference planes further away the EM fields are spread more evenly to larger area, which means that the signal propagating in the transmission line couples more to nearby traces causing crosstalk.

(b) Common mode propagation.

Figure 2.3. Reference planes close to traces, traces have strong coupling to reference planes. Wide trace edge to edge spacing to maintain  $100 \Omega$  differential impedance. Single-ended impedance  $50 \Omega$ .

(b) Common mode propagation.

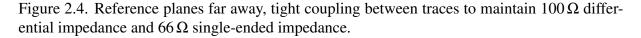

Figure 2.5 visualizes the relationship of trace width and trace separation when aiming for certain differential impedance. The green curve plots all differential pair dimensions that result in a certain differential impedance with certain dielectric thicknesses. The actual numerical values for trace widths and separation depend on factors discussed above. Figure 2.5 aims only to show how differential impedance is affected by these two factors together.

Figure 2.5. As long as there is coupling between the traces forming a differential pair, the differential impedance depends also on the distance between the traces.

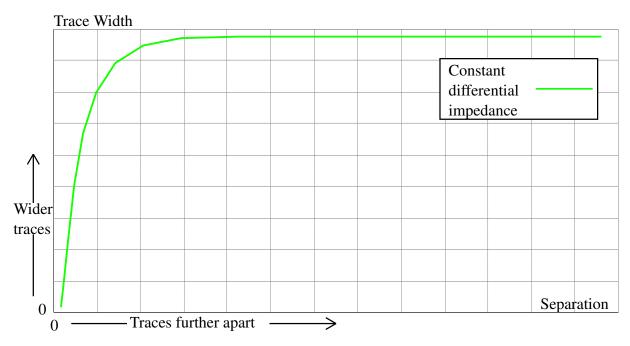

### 2.1.1. Reflections

All changes in the instantaneous impedance seen by the signal will cause reflections. Whether these reflections will affect signal quality or not, depends on the application. If signal rise or fall times are less than twice the time delay of a transmission line reflections need to be considered [15]. If signal rise time is long compared to the time delay of a transmission line, reflections are not likely to be a big concern [3]. Some receivers designed for high-speed signals have internal terminations and thus do not require external termination resistors on PCB. High-speed transmission lines can be terminated by either parallel, series or Thevenin termination network [16]. The objective of terminating a transmission line is to minimize reflections i.e., undershoot and overshoot [17]. Overshoot caused by reflection can exceed the maximum voltage level tolerated by the transmitter circuit and cause damage and undershoot degrades signal quality by lowering the signal voltage [17]. Figure 2.6 presents different termination strategies suitable for high-speed transmission lines. Cylinders represent transmission lines, other symbols ought to be self explanatory.

Figure 2.6. Series, parallel and Thevenin termination topologies

#### 2.2. Crosstalk

Crosstalk is unwanted coupling between signals. Traces running close together on the same layer of PCB will couple together (edge coupling), and traces that are routed on adjacent layers on top of each other will couple together (broadside coupling). When traces run on different layers on top of each other they will couple mostly capacitively, and when traces are side by side on the same layer inductive coupling will dominate [16]. The amount of crosstalk introduced to the quiet line will increase as the length of the coupled section increases. Coupling gets stronger when the switching line is brought closer to the quiet line. The transmission line called *switching line* (sometimes also *aggressor*) has some signal propagating on it that couples to the transmission line called *quiet line* (sometimes also *victim*). As shown earlier the dielectric thicknesses between transmission line and reference plane affects the EM field distribution. Smaller distance to reference planes helps to contain the EM field and thus reduce the crosstalk between adjacent transmission lines. The amount of crosstalk depends on the mutual capacitance and inductance between the switching and quiet lines but also the capacitance and inductance between the individual traces and reference planes.

Far end cross talk (FEXT) produces a short voltage pulse whereas near-end cross talk (NEXT) produces longer voltage pulse. FEXT and NEXT can be calculated if enough data is available. FEXT i.e., the cross talk at the receiver end of the transmission line can be calculated with

$$FEXT = \frac{V_f}{V_a} = \frac{Len}{t_r} \frac{1}{2v} \left( \frac{C_{mL}}{C_L} - \frac{L_{mL}}{L_L} \right)$$

(4)

where FEXT is the far-end crosstalk coefficient as the ratio of voltage at the far end of the quiet line  $V_f$  i.e., the crosstalk voltage and the voltage of the signal line  $V_a$ . Len is the length of the coupled section,  $t_r$  is the rise time of the signal in the switching line, v is the speed of signal on the line,  $C_{mL}$  and  $L_{mL}$  are the mutual capacitance and mutual inductance per unit length.  $C_L$  and  $L_L$  are the capacitance and inductance per unit length of the signal trace. NEXT can be obtained similarly with

$$NEXT = \frac{V_b}{V_a} = \frac{1}{4} \left( \frac{C_{mL}}{C_L} + \frac{L_{mL}}{L_L} \right)$$

(5)

where  $V_b$  is the voltage noise on the quiet line in backward direction and other parameters as above in equation 4. Equations (4) and (5) show that strong coupling to reference planes i.e., high signal trace capacitance and inductance will reduce crosstalk. Extremely tight coupling to reference planes is however not a silver bullet to all crosstalk problems as higher trace capacitance means lower trace impedance and trace impedance obviously cannot be arbitrarily low. A rule of thumb for adjacent trace routing is that spacing between traces should be at least two times the line width to keep crosstalk at an acceptable level. [4]

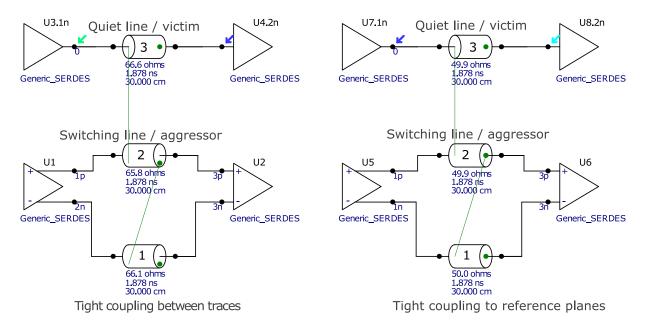

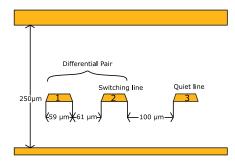

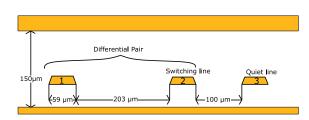

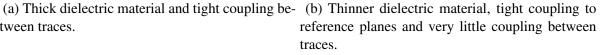

Crosstalk's relation to trace to reference plane distance can be examined with a simple simulation in Siemens HyperLynx. Figure 2.7 shows the simulation schematic and figure 2.8 visualizes the trace edge-to-edge spacings and distances to reference planes for both simulated cases. Drivers U1 and U5 launch a step response with 10 ps rise time to the differential 30 cm long transmission lines connected to them. Outputs of U3.1 and U7.1 are stuck low, and all voltage variation seen at U4.2 and U8.2 is consequently due to crosstalk. Numbers 1, 2 and 3 written on transmission lines on figures 2.7 and 2.8 help to keep track which line is which, while also serving as capacitance and inductance matrix indexes later. Receivers U2, U6, U4.2n and U8.2n shown in the schematic have internal  $50 \Omega$  terminations to keep the schematic as simple as possible

Figure 2.7. Simulation schematic for crosstalk simulation. Switching line is modelled as a transmission line from a differential pair and quiet line as a single-ended transmission line.

tween traces.

Figure 2.8. Cross section drawings for transmission lines in presented in figure 2.7

Capacitance and inductance matrices calculated with Siemens HyperLynx for situation in figure 2.8 (a) are

$$C = \begin{pmatrix} 100.663 & -24.348 & -0.647 \\ -24.348 & 103.077 & -13.981 \\ -0.647 & -13.981 & 96.060 \end{pmatrix} \qquad L = \begin{pmatrix} 413.458 & 100.012 & 17.337 \\ 100.012 & 411.890 & 60.617 \\ 17.337 & 60.617 & 416.744 \end{pmatrix} \tag{6}$$

where the matrix indices match traces in figure 2.8 (a) from left to right, so that the switching line is index two and quiet line three and indexes run from left to right, top to bottom starting from one. Units for capacitance and inductance values are  $\frac{pF}{m}$  and  $\frac{nH}{m}$  respectively. For the situation in figure 2.8 (b) the mutual capacitances and inductances with the same indexing scheme are

$$C = \begin{pmatrix} 125.164 & -1.018 & -0.010 \\ -1.018 & 125.755 & -7.334 \\ -0.010 & -7.334 & 125.744 \end{pmatrix} \qquad L = \begin{pmatrix} 312.995 & 2.544 & 0.172 \\ 2.544 & 312.586 & 18.229 \\ 0.172 & 18.229 & 312.595 \end{pmatrix}$$

(7)

HyperLynx seems to output Maxwell capacitance matrices as off-diagonal elements are negative. Maxwell capacitance matrix is the result of field solver calculations. Diagonal Maxwell capacitance matrix values are capacitances between a conductor and its return path and all other conductors. Off-diagonal values are mutual capacitances between traces. Values are negative to represent the sign of induced charges: positive voltage on conductor induces negative charge on adjacent conductor. A more useful version of capacitance matrix is the SPICE capacitance matrix where each value stands for a capacitance values between a pair of conductors. Diagonal elements of SPICE capacitance matrix are capacitances between conductors and their return paths and values stored in the matrix can be used to construct the equivalent spice circuit. In SPICE capacitance matrix off-diagonal values are numerically equal to Maxwell matrix but positive. Diagonal SPICE capacitance matrix values can be obtained from Maxwell capacitance matrix by summing values in each column of Maxwell capacitance matrix. The sum of a column is the diagonal value in SPICE matrix for the respective column. Values in inductance matrices are loop self-inductances and loop mutual inductances. [4]

SPICE capacitance matrix for tightly coupled traces (figure 2.8 (a)) is

$$C_{SPICE} = \begin{pmatrix} 75.668 & 24.348 & 0.647 \\ 24.348 & 64.811 & 13.981 \\ 0.647 & 13.981 & 81.432 \end{pmatrix}$$

(8)

where diagonal values have been derived from capacitance matrix in equation (6). Correspondingly SPICE matrix for the case where coupling is strong to the reference planes and weak between the differential traces is

$$C_{SPICE} = \begin{pmatrix} 124.127 & 1.018 & 0.010\\ 1.018 & 117.403 & 7.334\\ 0.010 & 7.334 & 118.4 \end{pmatrix}$$

(9)

where values have been derived from the capacitance matrix in equation (7). SPICE matrix values are applicable for FEXT and NEXT formulas in equations (4) and (5). The capacitance between the switching line and the reference planes, is in this case  $C_{22}$  and mutual capacitance between switching line and quiet line is  $C_{23}$  or  $C_{32}$ . Values for mutual inductance and self-inductance can be obtained directly from the matrices outputted by the simulator. Simulation result presented below cannot however be replicated simply by substituting values to equations (4) and (5) because in the simulations non-ideal behavior such as losses have been taken into account.

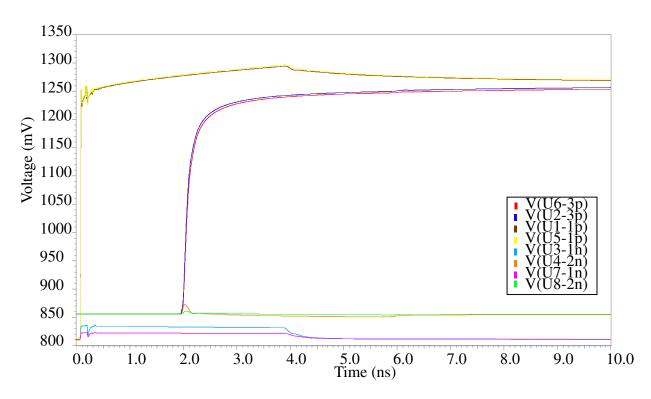

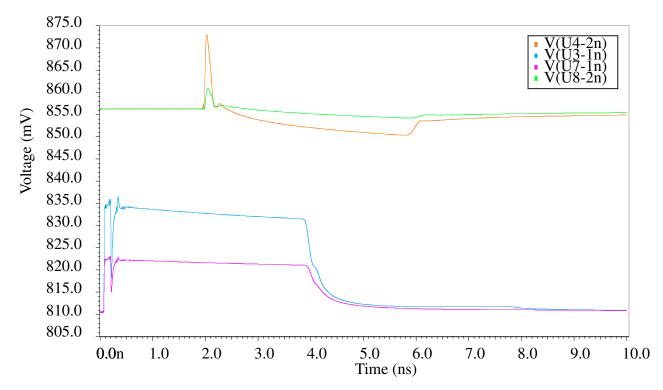

Overview of the Simulation results for the situation in figure 2.7 is shown in figure 2.9. As mentioned before switching lines have 10 ps rise time drivers. Dk on all dielectric layers is 3.5. Voltages at the transmitters of switching lines are V(U1-1p) and V(U5-1p), switching line receiver voltages are V(U2-3p) and V(U6-3p). Crosstalk voltages at the far-ends of the quiet lines are V(U4-2n) and V(U8-2n). Near-end crosstalk voltages are the remaining voltages: V(U3-1n) and V(U7-1n).

Figure 2.9. All voltages from the simulation schematic shown in figure 2.7.

A closer look at the crosstalk voltages is shown in figure 2.10. Waveform colors and labels match figure 2.9. Simulation results confirm that bringing reference planes closer to the traces help to reduce crosstalk. The voltage V(U8-2n) i.e., the far end crosstalk voltage of the configuration with tight coupling to reference planes is much lower than the crosstalk voltage of the configuration where coupling is tight between the traces and loose between traces and reference planes. Same holds true for the near-end crosstalk voltages.

Figure 2.10. Far end and near end crosstalk simulation results. Waveform labels are same as used in figure 2.7.

#### 2.3. Signal losses

All real interconnects are lossy, and losses are generally unwanted in the scope of digital signal transmission. If signal losses were constant on the whole frequency spectrum losses could be compensated with gain at the receiver. However as high frequencies are attenuated more in the transmission line signal rise times get longer and sharp edges become rounded. If the signal rise time is degraded so much that it starts to be comparable to the unit interval (UI) of the signal, inter-symbol interference (ISI) will occur as the signal won't have enough time to reach the desired voltage levels before symbol changes.

#### 2.3.1. Dielectric losses

Dielectric losses are caused by leakage currents through the dielectric material. On DC the dominating mechanism is ionic motion. The amount of mobile charge carriers in dielectric materials is generally small and thus dielectric losses are low on DC. The dominating dielectric loss mechanism on AC is polarization of permanent dipoles. When electric field is applied to the dielectric material dipoles align with the electric field. If the electric field is caused by a sinusoidal voltage the orientation of dipoles will change with the electric field enabling AC current flow. Higher frequencies will cause dipoles to rotate more quickly increasing the leakage current. [4, 15]

#### 2.3.2. Conductor losses

Conductor losses are caused solely by resistance on DC, but as frequency increases the loss caused by DC resistance is dwarfed by other loss mechanisms. While the resistivity of copper stays constant up to frequencies near 100GHz, skin effect forces the current to flow only in the

surface of the conductor which increases losses. Losses caused in conductors can be decreased by either using sorter conductors or by using wider conductors. High-speed materials tend to have lower Dk than regular FR-4 [18]. FR-4 is a common name for woven fiberglass reinforced epoxy resin laminates [19]. Low Dk allows using wider conductors for certain layer thickness and instantaneous impedance, resulting in lower loss interconnects. Conductor losses cause signal loss equally in the signal trace and in the return path.

#### 2.3.3. Skin effect

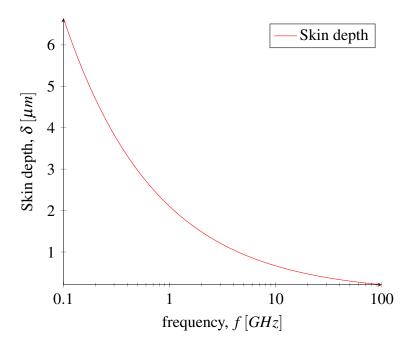

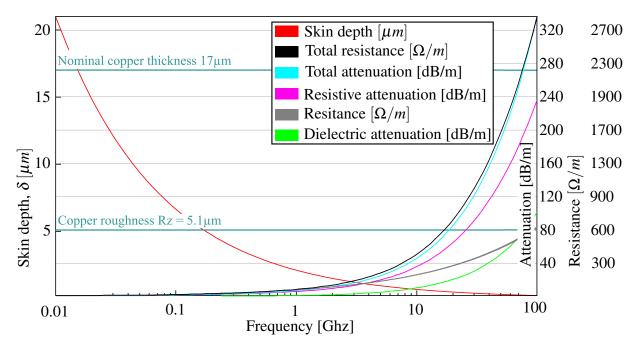

Current's tendency to flow closer to the conductor surface on higher frequencies is called skin effect. The immediate consequence of this phenomena is that high frequency signals do not utilize all of the available cross-sectional conductor surface area. Smaller cross-sectional surface area increases the apparent resistance of the conductor, which in turn causes signal losses [20]. Ways to mitigate skin effect losses are discussed in chapter 4. Skin depth measures the depth in which current flows on a certain frequency and it can be approximated with

$$\delta = 2.1 \sqrt{\frac{1}{f}} \tag{10}$$

where  $\delta$  is the skin depth in  $\mu m$  and f is the (sine wave) frequency in GHz [4]. Equation (10) is plotted in figure 2.11 from 0.1 GHz to 100 GHz. Skin depth is on vertical axis and frequency on horizontal, logarithmic axis. On 100 MHz skin depth is only 6.64  $\mu m$ , which is already less than half of the nominal thickness of 17  $\mu m$  copper foil. On even higher frequencies copper surface profile starts also contributing to signal losses as copper foils used on PCBs have surface bumpiness that exceeds the skin depth. Skin depth approaches zero as frequency increases to hundreds of gigahertz. When skin depth is smaller than the conductor thickness, the conductor surface area seen by the propagating signal is smaller.

Figure 2.11. Skin depth as a function of frequency.

Skin effect originates from the same phenomena that causes return currents to flow right

below (and above) the signal trace. AC currents will travel paths that have the least inductance i.e., the lowest impedance. This phenomenon is amplified as frequency increases.

#### 2.4. Propagation delay and Skew

Signal propagates in an interconnect at a finite speed that is considerably lower than the speed of light in a vacuum. Speed of signal in PCB dielectric is

$$v = \frac{c}{\sqrt{Dk}} \tag{11}$$

where c is the speed of light (roughly 300 000 000 m/s) and Dk is the relative dielectric constant of the material [3]. Propagation delay is then naturally

$$T_d = \frac{conductor \ length}{v} \tag{12}$$

where v is the speed of signal in the dielectric material and  $T_d$  is the time delay or propagation delay caused in the interconnect. Propagation delay alone does not degrade signal quality, it only adds latency to the signal transmission. However, if propagation delay is different between conductors forming a differential pair or different between other time sensitive signals, problems start to occur. Skew causes mode conversion in differential signals, which means that differential signals become common mode signals and vice versa. [20]

How much skew can be tolerated depends on the signaling baud rate and modulation. Pulse Amplitude Modulation 4-level (PAM4) is more sensitive to intra pair skew than non-return-tozero (NRZ) modulation with the same data speed [21]. The allowable skew is decided by the rise time of the receiver and the signal speed in the transmission line [16]. Signal baud rate also gives some insight on the order of magnitude of skew that can be tolerated. For example, a 2.4 GB/s NRZ data stream has a unit interval of 416 ps [16]. When signaling rate is 26.5625 Giga baud (GBd) the unit interval is as short as 37.64706 ps [22]. It is safe to say that with no information about the receiver rise times the skew constraints are tight for high-speed signals. A signal travels 6 mm (Dk=3.5) in the UI of 26 GBd signal and skew cannot be even close to the whole unit interval. While trace length matching of PCB traces is a manageable issue skew is also generated by other factors. One of these is non-uniformity of the substrate material. This skew mechanism is called fiber weave effect and will be discussed later in further detail.

# **3. PCB MATERIAL PROPERTIES**

PCBs are typically constructed of stacks of woven glass fiber sheets laminated together with epoxy resin with copper foil sheets in between the glass fiber layers. This chapter describes how dissimilar materials, material treatments and manufacturing processes affect parameters that influence signal integrity on PCB. The focus is on Glass fiber materials as they enable cost effective mass production with currently available manufacturing technology. Materials other than glass fiber can be used as PCB substrate, however these more exotic materials are out of the scope of this document due to worse availability and higher cost.

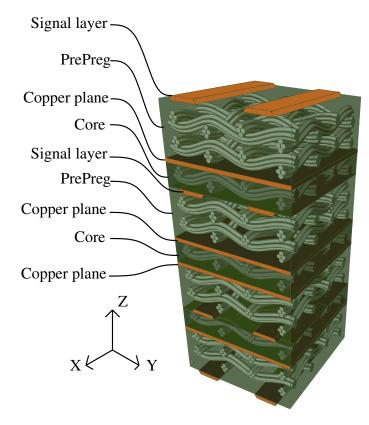

Figure 3.1 shows an example on how an eight-layer PCB layer construction i.e., build-up or stack-up can be done. Different layers have been labeled for the top side of the drawn stack-up. Resin has been drawn transparent to show glass weave structures inside layers. Core layers have a single glass fiber sheet while prepreg layers are constructed from two glass fiber sheets stacked on top of each other. In real application where two glass fiber sheets are used for one layer the fiber bundles would not likely be aligned as they are in the figure 3.1. Prepreg layers could also be constructed from only one glass fiber cloth and one core could on the other hand have two or more glass fiber cloths stacked together. Construction of each layer depends on what is available for the selected resin system.

Figure 3.1. PCB layer construction visualization, not drawn to scale.

#### 3.1. Core and Prepreg

PCB materials referred as core or copper-clad laminates are comprised of cured resin reinforced with glass fiber mesh. Core materials come with copper foil attached to both sides. These materials are cured during the laminate manufacturing process and thus their thickness will not vary during the PCB lamination process. Prepreg on the other hand is only partially cured before PCB lamination process and thus prepreg layer's final thickness depends on the amount of copper present on the adjacent surfaces. Both cores and prepregs can be ordered with various different glass styles. Glass weaves and epoxy resin have different dielectric properties which ultimately affects signal propagation on the finished PCB. [23]

Final prepreg thickness affects the thickness of the finished board as well as the impedances on the signal layer next to the prepreg layer. Some stack-up design utilities such as Siemens Z-planner and ICD Stack-up Planner do calculate the pressed prepreg thickness automatically, however sometimes it may be useful to estimate final prepreg thickness manually. IPC has defined laminate thickness tolerances for different laminate thicknesses and copper types in IPC 4101E WAM1 [24]. IPC is an international standardization organization standardizing electronics product development cycle [25]. One way to estimate final prepreg thickness is

$$T_{FinalPrePreg} = T_{InitialPrePreg} - [T_1(100\% - D_{Trace}\%)] - [T_2(100\% - D_{Plane}\%)]$$

(13)

where  $T_{FinalPrePreg}$  is the finished prepreg thickness,  $T_{InitialPrePreg}$  is initial prepreg thickness,  $T_1$  and  $T_2$  are copper thicknesses of signal and plane layer respectively  $D_{Trace}$  is routing density for signal layer in percentage and  $D_{Plane}$  is the same for the plane layer [26]. The estimate in equation (13) is based only on initial prepreg thickness, copper layer thicknesses and copper layer densities, it does not account for resin content, which also affects the prepreg layer thickness [27].

#### 3.1.1. Relative dielectric constant and loss tangent

Relative dielectric constant ( $\varepsilon_r$ ) or (Dk) is probably the best-known dielectric property of PCB substrate materials. It is material's absolute dielectric constant divided by the dielectric constant of air. To be exact relative dielectric constant compares material's permittivity to vacuum permittivity, but air permittivity differs insignificantly from vacuum permittivity, thus it does not make sense to differentiate between vacuum and air in this context [5]. When referring to material properties relative dielectric constant is often simply called *Dielectric constant*. Dielectric constant creates capacitance between conductors influencing greatly to trace impedances. The dielectric constant seen by the finished transmission line on the PCB is not directly the data sheet value of Dk as surrounding materials influence the dielectric constant that is perceived by the transmission line. This perceived Dk is called effective dielectric constant. [4]

Dissipation factor (Df) is the same as tangent of the loss angle  $(\tan(\delta))$  and it describes the amount of energy that is lost in the electromagnetic field traveling through dielectric material [16]. A great everyday demonstration of dissipation factor is a bowl that heats up in the microwave oven: Bowl's dissipation factor determines how much energy it will dissipate and turn to heat. Ideally one would want the food to heat up and not necessarily the bowl however if the bowl has high dissipation factor it may heat up significantly. Greek letter  $\delta$  as loss angle is unrelated to  $\delta$  as skin depth.

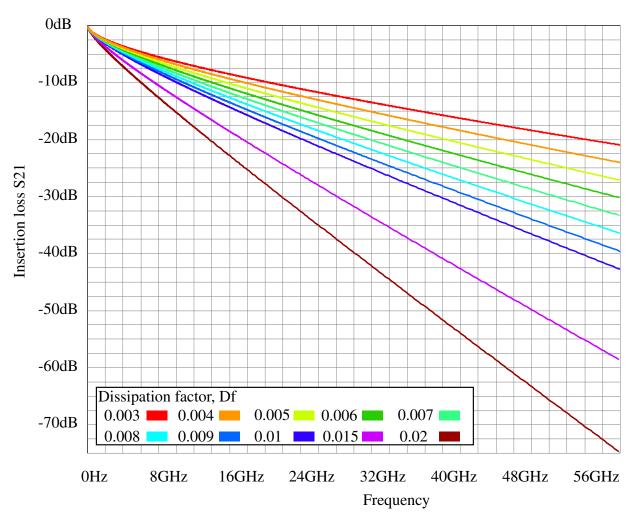

Dielectric properties are not constant across frequencies, both dielectric constant and dissipation factor vary slightly relative to frequency. Dk decreases as frequency increases and Df increases slightly as frequency rises [28]. Material data sheets seem to agree on the increasing of Df with frequency while in Eric Bogatin's Signal and Power Integrity - simplified -book dissipation factor's frequency dependency is described as follows: "*At high enough frequency, the dipoles will not be able to respond as fast as at lower frequency and we would, therefore, expect the dissipation factor to decrease.*" [4]. This sentence sounds contradicting in comparison to the measured Df values available in material data sheets. As Df test methods are well established and documented it should be safe to conclude that Df increases slightly with frequency - at least on the frequency band of interest in the scope of PCB design. Higher Df means bigger losses resulting in higher insertion loss and thus worse performance while lower Dk results in higher trace impedance. Dk and Df values measured with different frequencies are usually available in material data sheets. Dissipation factor's effect to dielectric losses is also heavily frequency dependent even if the dissipation factor itself would stay constant.

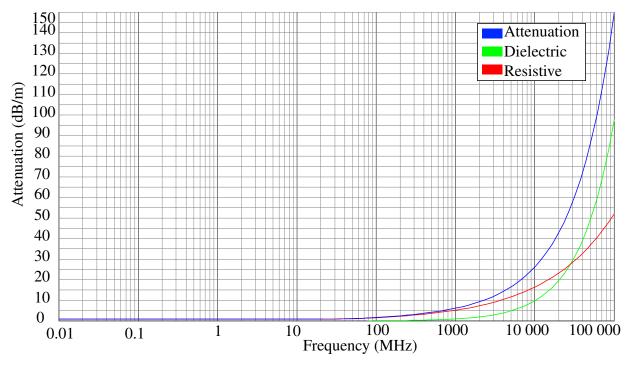

Figure 3.2 shows simulated attenuation per unit length in an asymmetric stripline transmission line. Figure 3.3 shows the construction of the simulated interconnect. Frequency is on the horizontal axis and attenuation on the vertical axis. The dielectric losses (green curve) start increasing rapidly on frequencies beyond 10GHz. Copper roughness effects have not been considered in the simulations for this graph. Resistive losses increase due to skin effect: current flows in the conductor surface only making the conductor effectively thinner. See section 2.3.3. Ways to measure dielectric constant and dissipation factor have been described in further detail in section 3.1.2.

Figure 3.2. Attenuation per unit length HyperLynx

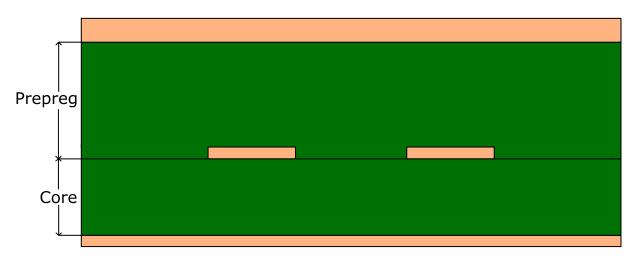

Prepreg thickness in figure 3.3 is 139  $\mu$ m and core thickness is 102  $\mu$ m, different features in the drawing are drawn roughly to scale with each other. Dielectric constants are 3.25 and 3.66 for prepreg and core respectively. Dissipation factor of prepreg material is 0.006, core material has slightly lower loss at 0.0056. Transmission line single ended impedance is around 50  $\Omega$ . The used material parameters are parameters of a real low loss multilayer PCB material from Shengyi [28]. The specific material is Shengyi S7439C/S7439CB.

Figure 3.3. Cross section drawing of the stripline structure simulated in figure 3.2

#### 3.1.2. Dk and Df test methods

An abundance of dielectric property test methods has been developed: IPC has defined 12 different test methods for measuring Dk and on top of the IPC test methods there are numerous test methods defined by other institutions as well [29]. Generally dielectric material test methods are divided to circuit and material test methods. This section will introduce a couple of common test methods: Clamped stripline test (material test method), Split-Cylinder Resonator (material test method) test and microstrip ring resonator test (circuit test method). Material test methods evaluate the dielectric purely without any PCB fabrication variables. Circuit test methods on the other hand evaluate materials based on circuit performance. Both test method categories are affected by different variables and measuring same material using different types of tests will result in different results. Moreover, some test methods evaluate material's properties in Z-direction while other tests evaluate the materials in the XY-plane. See figure 3.1 for coordinate axes reference. Most PCB materials are anisotropic, which means that material's dielectric properties are not homogenous in all directions [29]. Generally dielectric properties in Z direction are of a bigger interest for high-speed digital designs as stripline transmission lines couple to reference planes in Z direction. However as explained in section 2.1 differential pairs also couple to each other in XY direction thus is also worth mentioning that there should be mostly only resin from the prepreg layer between the differential pair and resin has lower Dk than glass.

The test method that seems to be most frequently used in laminate datasheets is the stripline test for Permittivity and Loss Tangent, specified in IPC TM-650 Test Methods Manual 2.5.5.5 [30]. This test method is sometimes called also "clamped stripline test" which is very descriptive name for this test. When performing this test, a resonator structure is clamped between two sheets of the material under test. A stripline structure is formed as the clamping surfaces double as reference planes. Due to this mechanical clamping configuration this test method may report lower Dk than actual as there might be some air trapped in the surface imperfections of the materials. The IPC TM-650 2.5.5.5 evaluates dielectric properties in Z-direction and up to 12.4GHz. Clamped stripline test is a material test method and it does not evaluate the performance of final applications, but rather the consistency of the material in general. The copper clad materials used to conduct this test are destroyed as all copper needs to be etched away before performing the clamped stripline test. [29, 30]

Split Cylinder Resonator Test specified in IPC-TM-650 2.5.5.13 needs similarly prepared

material as the clamped stripline test: all copper needs to be etched away before conducting this test. Unlike clamped stripline test the Split-Cylinder Resonator test evaluates material in the XY-plane. If results obtained by Split-Cylinder resonator test and clamped stripline test on a certain frequency are compared, information about the material anisotropy can be obtained. [29]

Microstrip Ring resonator test method is a circuit test method, which means that it is affected by variables associated with PCB construction such as copper thickness and roughness and manufacturing tolerances. Microstrip Ring resonator test is conducted by building a microstrip ring resonator on the material under test and measuring its performance. [29]

From the three mentioned test methods microstrip ring resonator and the clamped stripline tests are relevant for stripline and microstrip interconnect design where most coupling is to the reference plane(s). The clamped stripline test gives the best consistency as the material under test is the only variable in the test setup, but as stated earlier the obtained Dk values tend to be lower than material's actual Dk. However as clamped stripline test gives consistent results it is a good test method for comparing different materials. Clamped stripline test results are also influenced by the copper roughness, even though all copper is etched away. Rougher copper leaves the laminate surface rougher, and more air can be trapped between the laminate and the test fixture [31]. Microstrip ring resonator test on the other gives Dk value for the particular material and manufacturing combination. Manufacturing tolerances can cause the Dk extraction to be inaccurate, if they are not taken into account in the Dk extraction process [29]. Different test circuit designs can also yield different Dk results on the same material [31].

#### 3.1.3. Glass Styles

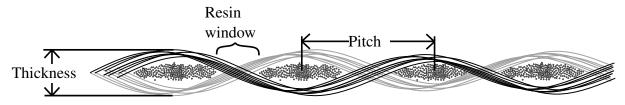

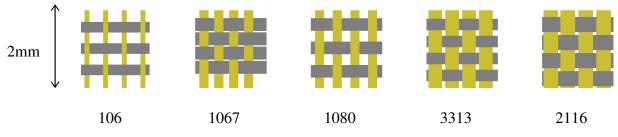

Glass fiber cloth makes PCB materials durable and rigid. It also affects the electrical properties of the finished PCB. Different glass fiber cloths are distinguished with a three- or four-digit number. Unfortunately, there does not seem to exist any common rules regarding glass style numbers. Lack of a common glass style numbering scheme means that it is not possible to deduct dimensions and other features of a glass style solely based on the glass style number. In table 3.1 glass styles available for the earlier mentioned low loss material, Shengyi S7439C/S7439CB are listed [28]. Glass style properties apart from the spread-column are as presented in IPC 4412C [32]. Spread-column is based on [33] as IPC has not defined clearly what should be referred as spread glass [34]. Spread glass in general refers to glass fibers being distributed more evenly in the woven fabric. In standard glass the glass bundles are roundish and there are gaps between bundles, spread glass on the other hand has flattened glass bundles with smaller gaps between glass bundles. Fabric count per centimeter presented in standard has been converted to glass fabric pitch as pitch better describes the spacing between the glass bundles. Although it should be kept in mind that the glass fiber bundles may not always run straight, and the actual fabric pitch may change along the material. Glass used in electronics is usually so-called E-glass, which is electronics grade glass with low alkali content and low water absorption tendency [35]. There are also other glass types such as low dielectric constant glass (D-glass), High-strength glass (S-glass) and chemical glass (C-glass) [35]. Fabric thickness values presented on table 3.1 are marked as "Reference only" in the IPC standard. The thickness of the finished core materials will be presented in laminate manufacturers data sheet and prepreg material thickness will need to be determined based on the resin systems resin content and the amount of copper on the planes adjacent to prepreg layer. Figure 3.4 visualizes how glass bundles are arranged in standard glass like 106. Drawing represents side view of the fabric, in actual printed circuit board this fabric would be soaked in resin and laminated between copper planes from top and bottom.

Figure 3.4. Side view drawing of non-spread glass fiber cloth, drawn neither to scale nor to represent any actual woven fabric.

| Glass Style | Thickness µm | Spread | Pitch X µm | Pitch Y µm |

|-------------|--------------|--------|------------|------------|

| 106         | 33           | No     | 454.5      | 454.5      |

| 1067        | 43           | Yes    | 362.3      | 362.3      |

| 1078        | 43           | Yes    | 469.5      | 469.5      |

| 1080        | 53           | No     | 423.7      | 540.5      |

| 3313        | 84           | Yes    | 423.7      | 409.8      |

| 2116        | 94           | No     | 423.7      | 438.6      |

Table 3.1 Approximate dimensions for a selection of glass styles

Different glass styles obviously have different characteristics and tradeoffs. Bigger resin windows allow resin to flow freely through the glass fiber cloth generally allowing better adhesion to adjacent copper planes while more uniformly spread glass fiber bundles yield more uniform dielectric properties. Spread or flat glass was initially developed to improve consistency in laser-drilling process, but it also helps mitigating glass weave skew and improves resin distribution [34]. Improved resin distribution here probably means that the resin will flow nicely on the flat glass, if there is enough resin to fill everything. However if there is not enough resin on either side of the glass fabric flattened glass bears higher risk of leaving voids as the resin will have hard time flowing through the uniform glass bundles. In figure 3.5 different glass cloths listed in table 3.1 have been drawn proportionally to each other using dimensions presented in [33]. Glass style 2116 has been omitted from the drawing as dimensions were not available. It is clear that spread glass has significantly smaller resin windows: almost no white background can be seen through glass styles 1067, 3313 and 2116. Table 3.2 lists different terms used to describe glass styles based on Isola Group's documentation [33].

Figure 3.5. Visualization of different glass styles

| Term              | Definition                                                         |  |

|-------------------|--------------------------------------------------------------------|--|

| Spread Glass      | Glass bundles are spread out, offers more uniform dielectric prop- |  |

| Spiead Glass      | erties and is flatter than standard glass.                         |  |

| Expanded Weave    | Glass that is spread in more than one direction.                   |  |

| Open Filament     | Same as expanded weave                                             |  |

| Open Weave        | Same as expanded weave                                             |  |

| Mechanically      | Glass that is mechanically spread in both X and Y directions.      |  |

| Spread (MS) Glass |                                                                    |  |

| Squara Waaya      | Glass that has balanced density and/or same glass pitch in both X  |  |

| Square Weave      | and Y directions.                                                  |  |

| Flat Glass        | Glass with fibers that have very little or no twist at all.        |  |

Table 3.2 Glass definitions based on definitions from Isola Group S.a.r.l

#### 3.2. Copper foils

Copper foil is the part of printed circuit board that forms the bulk of conductors, thus its qualities greatly affect printed circuit board's electrical performance. Qualities of the copper foil between dielectric layers of the PCB also determine how well layers adhere together and ultimately how durable the finished PCB is. Copper comes in different thicknesses and surface finishes, common copper thicknesses are  $70 \,\mu m$ ,  $35 \,\mu m$ , and  $17 \,\mu m$ . Generally smoother copper has better electrical properties but worse mechanical properties: it adheres worse to the PCB laminate resulting in worse structural rigidity while electrical losses due to surface roughness are lower. Two different ways to manufacture copper foil can be utilized depending on the desired electrical and mechanical properties. These manufacturing methods are rolling and electrodeposition. Differences between rolled copper or rolled-annealed (RA) copper and Electrodeposited (ED) copper are discussed briefly below based on [36], [27] and [37].

#### 3.2.1. Rolled Copper

Copper foil can be manufactured by flattening a copper ingot to thin foil by series of rollers. Foil manufactured in this kind of process is called rolled copper or RA copper (rolled-annealed copper). Finished RA copper foil is very smooth, surface roughness is defined by the surface finish of the final rollers in the manufacturing process, but generally surface is smoother than ED copper surface and needs to be roughened to some extent before lamination in order to improve bonding to the PCB substrate. Due to the manufacturing process rolled copper has in-plane grain structure which allows it to withstand bending quite well thus allowing use in flexible circuits. Rolled copper is also able to withstand thermal stresses better than ED copper and might be useful material in applications that are expected to face rapid temperature changes.

#### 3.2.2. Electrodeposited copper

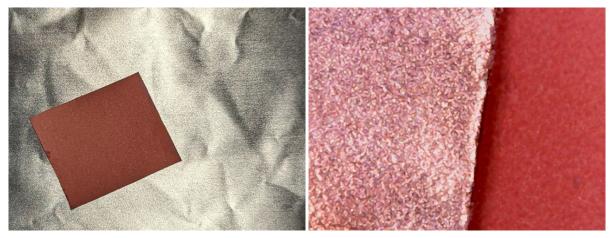

More common and cheaper method of manufacturing copper foil is electrodeposition. Electrodeposited (ED) copper is manufactured by plating a titanium drum with copper using electrolysis. ED copper manufacturing process results in copper foil that has a shiny side and matte side. The shiny side is the drum side and its surface finish is determined by the drum's surface. The matte side is rougher and in the case of standard ED copper the matte side is treated and attached to the PCB core material. ED copper has vertical grain structure which makes etching traces and other patterns to ED copper easier than to RA copper. In practice higher circuit density and tighter trace width tolerances can be achieved with ED copper. Figure 3.6 shows the difference between shiny and matte sides of ED copper.

(a) Shiny side up in the background.

(b) Shiny side up on left

Figure 3.6. Shiny and matte sides of ED copper differ considerably from each other.

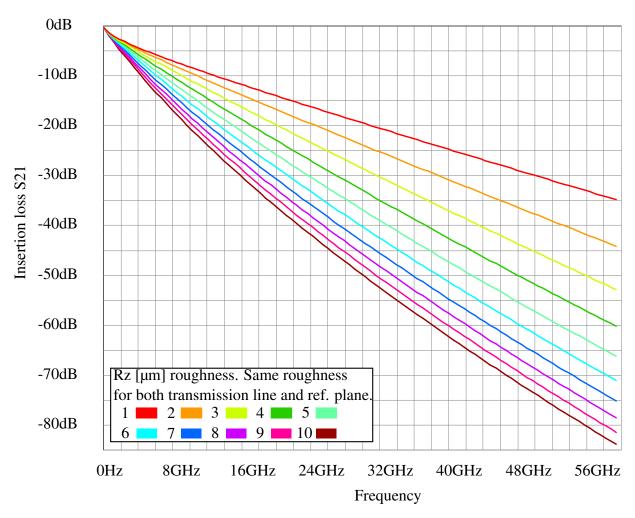

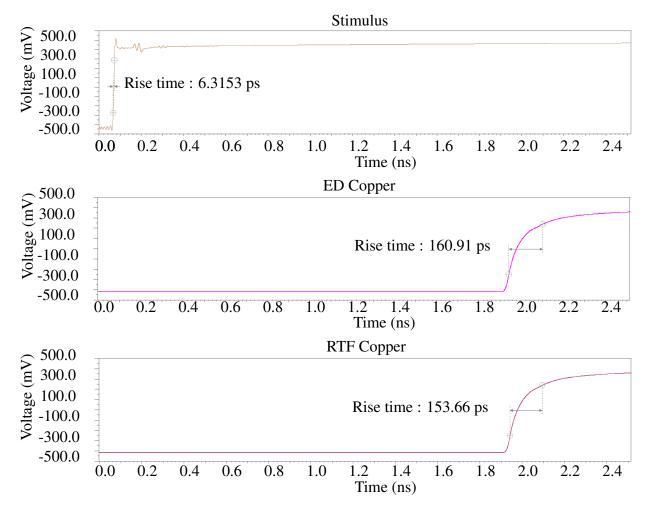

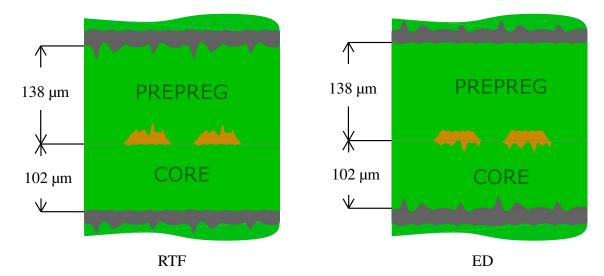

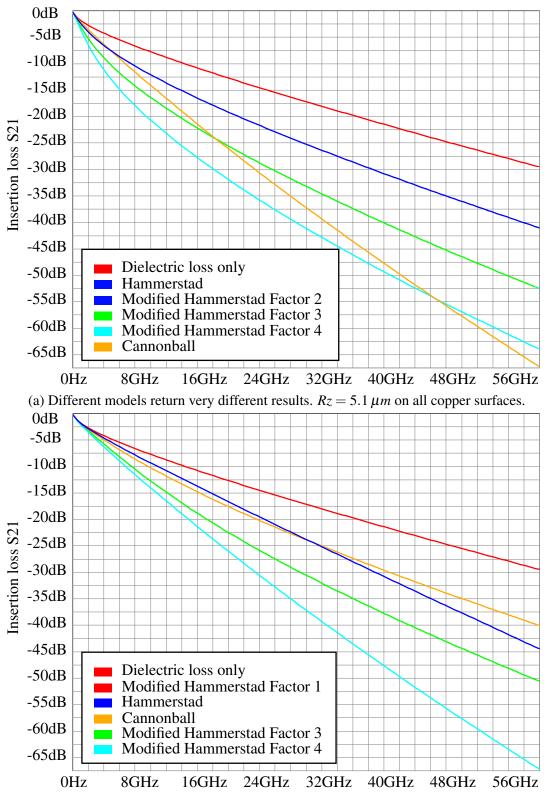

## 3.2.3. Reverse treated foil