FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING DEGREE PROGRAMME IN ELECTRONICS AND COMMUNICATIONS ENGINEERING

# **MASTER'S THESIS**

# DESIGN FOR TESTABILITY OF A LATCH-BASED DESIGN

Author Matti Leinonen

Supervisor Jukka Lahti

Second Examiner Tarmo Ruotsalainen

Technical Advisor Joni Jäntti

**JUNE 2022**

**Leinonen M. (2022) Design for testability of a latch-based design.** University of Oulu, Faculty of Information Technology and Electrical Engineering, Degree Programme in Electronics and Communications Engineering. Master's Thesis, 70p.

#### **ABSTRACT**

The purpose of this thesis was to decrease the area of digital logic in a power management integrated circuit (PMIC), by replacing selected flip-flops with latches. The thesis consists of a theory part, that provides background theory for the thesis, and a practical part, that presents a latch register design and design for testability (DFT) method for achieving an acceptable level of manufacturing fault coverage for it.

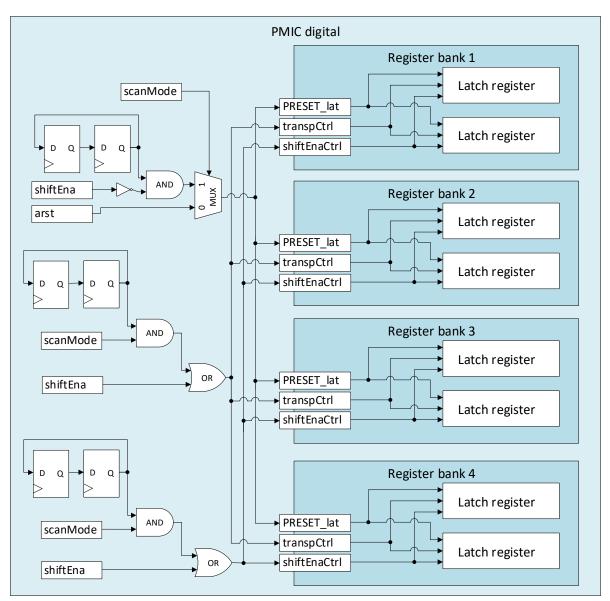

The total area was decreased by replacing flip-flops of read-write and one-time programmable registers with latches. One set of negative level active primary latches were shared with all the positive level active latch registers in the same register bank. Clock gating was used to select which latch register the write data was loaded to from the primary latches. The latches were made transparent during the shift operation of partial scan testing. The observability of the latch register clock gating logic was improved by leaving the first bit of each latch register as a flip-flop. The controllability was improved by inserting control points.

The latch register design, developed in this thesis, resulted in a total area decrease of 5% and a register bank area decrease of 15% compared to a flip-flop-based reference design. The latch register design manages to maintain the same stuck-at fault coverage as the reference design.

Key words: manufacturing testing, partial scan testing, power management integrated circuit, area, power consumption and fault coverage.

Leinonen M. (2022) Salpaperäisen piirin testattavuuden suunnittelu. Oulun yliopisto, tietoja sähkötekniikan tiedekunta, elektroniikan ja tietoliikennetekniikan tutkinto-ohjelma. Diplomityö, 70p.

# TIIVISTELMÄ

Tämän opinnäytetyön tarkoituksena oli pienentää digitaalisen logiikan pinta-alaa integroidussa tehonhallintapiirissä, korvaamalla valitut kiikut salpapiireillä. Opinnäytetyö koostuu teoriaosasta, joka antaa taustatietoa opinnäytetyölle, ja käytännön osuudesta, jossa esitellään salparekisteripiiri ja testattavuussuunnittelun menetelmä, jolla saavutettiin riittävän hyvä virhekattavuus salparekisteripiirille.

Kokonaispinta-alaa pienennettiin korvaamalla luku-kirjoitusrekistereiden ja kerran ohjelmoitavien rekistereiden kiikut salpapiireillä. Yhdet negatiivisella tasolla aktiiviset isäntä-salpapiirit jaettiin kaikkien samassa rekisteripankissa olevien positiivisella tasolla aktiivisten salparekistereiden kanssa. Kellon portittamisella valittiin mihin salparekisteriin kirjoitusdata ladattiin yhteisistä isäntä-salpapireistä. Osittaisessa testipolkuihin perustuvassa testauksessa salpapiirit tehtiin läpinäkyviksi siirto-operaation aikana. Salparekisterin kellon portituslogiikan havaittavuutta parannettiin jättämällä jokaisen salparekisterin ensimmäinen bitti kiikuksi. Ohjattavuutta parannettiin lisäämällä ohjauspisteitä.

Salparekisteripiiri, joka suunniteltiin tässä diplomityössä, pienensi kokonaispinta-alaa 5 % ja rekisteripankin pinta-alaa 15 % verrattuna kiikkuperäiseen vertailupiiriin. Salparekisteripiiri onnistuu pitämään saman juuttumisvikamallin virhekattavuuden kuin vertailupiiri.

Avainsanat: tuotannon testaus, osittainen testipolkuihin perustuva testaus, integroitu tehonhallintapiiri, pinta-ala, tehonkulutus ja virhekattavuus.

# **TABLE OF CONTENTS**

| ABS   | ΓRAC            | TT                       |                                                   | . 2 |  |  |

|-------|-----------------|--------------------------|---------------------------------------------------|-----|--|--|

| TIIVI | ISTEL           | .МÄ                      |                                                   | . 3 |  |  |

| TABI  | LE OF           | F CONT                   | TENTS                                             | . 4 |  |  |

| FORE  | EWOI            | RD                       |                                                   | . 6 |  |  |

| LIST  | OF A            | BBRE                     | VIATIONS AND SYMBOLS                              | . 7 |  |  |

| 1     | INTR            | RODUC                    | TION                                              | . 9 |  |  |

| 2     | SEQU            | JENTL                    | AL LOGIC                                          | 11  |  |  |

|       | 2.1             | Latche                   | s                                                 | 11  |  |  |

|       | 2.2             | Flip-flo                 | ops                                               | 14  |  |  |

|       | 2.3             | Resetta                  | able sequential logic                             | 16  |  |  |

|       | 2.4             | Registers                |                                                   |     |  |  |

|       | 2.5             | Timing                   | g analysis of sequential logic                    |     |  |  |

|       |                 | 2.5.1                    | Timing of flip-flops                              | 19  |  |  |

|       |                 | 2.5.2                    | Timing of latches                                 | 20  |  |  |

|       |                 | 2.5.3                    | Timing of pulsed latches                          | 21  |  |  |

|       |                 | 2.5.4                    | Time borrowing                                    |     |  |  |

|       |                 | 2.5.5                    | Fixing timing violations                          |     |  |  |

|       | 2.6             |                          | consumption of CMOS logic                         |     |  |  |

| 3     | DESI            |                          | R TESTABILITY                                     |     |  |  |

|       | 3.1 Scan design |                          |                                                   |     |  |  |

|       |                 | 3.1.1                    | Muxed-D scan style                                | 26  |  |  |

|       |                 | 3.1.2                    | Clocked-scan style                                | 28  |  |  |

|       |                 | 3.1.3                    | LSSD style                                        | 28  |  |  |

|       |                 | 3.1.4                    | Latches in scan designs                           | 30  |  |  |

|       | 3.2             | Logic built-in self-test |                                                   | 31  |  |  |

|       |                 | 3.2.1                    | Test pattern generation                           |     |  |  |

|       |                 | 3.2.2                    | Output response analysis                          | 33  |  |  |

|       |                 | 3.2.3                    | Logic BIST architectures                          |     |  |  |

|       |                 |                          | 3.2.3.1 LSSD on-ship self-test                    | 34  |  |  |

|       |                 |                          | 3.2.3.2 Self-testing using MISR and parallel SRSG | 34  |  |  |

|       |                 | 3.2.4                    | Latches in logic BIST designs                     | 34  |  |  |

|       | 3.3             | Memor                    | ry built-in self-test                             | 35  |  |  |

|       | 3.4             | Test po                  | pint insertion                                    | 36  |  |  |

| 4     | LATO            | CH REI                   | PLACEMENT                                         | 39  |  |  |

|       | 4.1             | A refer                  | rence PMIC model                                  | 39  |  |  |

|       |                 | 4.1.1                    | AMBA APB protocol                                 | 40  |  |  |

|       |                 |                          | 4.1.1.1 APB write transfer                        |     |  |  |

|       |                 |                          | 4.1.1.2 APB read transfer                         | 42  |  |  |

|       |                 | 4.1.2                    | Register banks                                    |     |  |  |

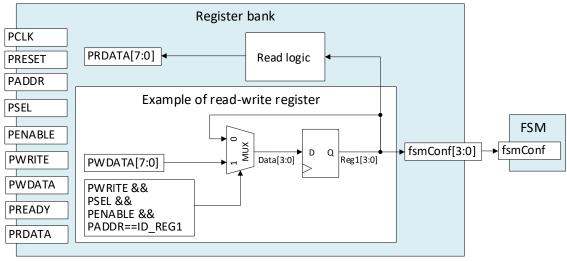

|       |                 |                          | 4.1.2.1 Read-write register                       | 43  |  |  |

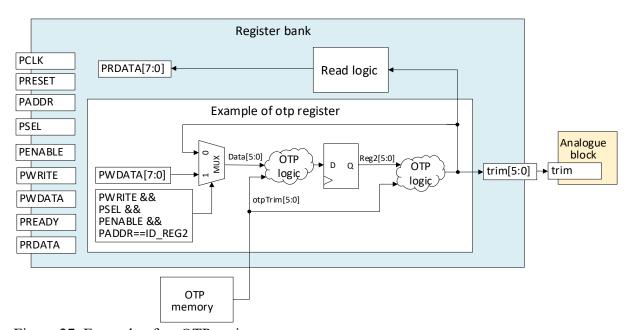

|       |                 |                          | 4.1.2.2 One-time programmable register            | 44  |  |  |

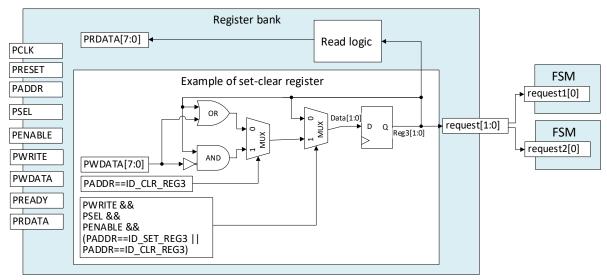

|   |              |                           | 4.1.2.3 Set-clear register                | 44 |  |  |

|---|--------------|---------------------------|-------------------------------------------|----|--|--|

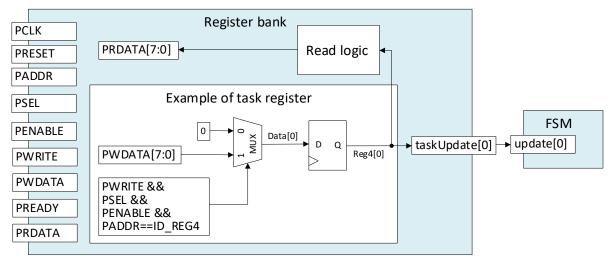

|   |              |                           | 4.1.2.4 Task register                     | 45 |  |  |

|   |              |                           | 4.1.2.5 Read-only register                | 46 |  |  |

|   | 4.2          | Latch                     | replacement selection                     | 47 |  |  |

|   |              | 4.2.1                     | Pulsed latch considerations               | 47 |  |  |

|   |              | 4.2.2                     | Latch considerations                      | 48 |  |  |

|   | 4.3          | Latch                     | register design                           | 49 |  |  |

|   | 4.4          | DFT n                     | nethod selection                          | 53 |  |  |

|   |              | 4.4.1                     | Scan design considerations                | 53 |  |  |

|   |              |                           | 4.4.1.1 Full-scan design consideration    | 53 |  |  |

|   |              |                           | 4.4.1.2 Partial-scan design consideration | 54 |  |  |

|   |              | 4.4.2                     | Logic BIST considerations                 | 55 |  |  |

|   |              | 4.4.3                     | Memory BIST considerations                | 55 |  |  |

|   | 4.5          | Partial                   | l scan design                             | 56 |  |  |

|   |              | 4.5.1                     | Making latches transparent                | 56 |  |  |

|   |              | 4.5.2                     | Improving observability                   | 57 |  |  |

|   |              | 4.5.3                     | Improving controllability                 | 59 |  |  |

| 5 | RESULTS      |                           |                                           |    |  |  |

|   | 5.1          | Area r                    | results                                   | 61 |  |  |

|   | 5.2          | Power consumption results |                                           |    |  |  |

|   | 5.3          | ATPG                      | Gresults                                  | 63 |  |  |

|   |              | 5.3.1                     | Stuck-at fault results                    | 63 |  |  |

|   |              | 5.3.2                     | IDDQ fault results                        | 64 |  |  |

|   |              | 5.3.3                     | Transition fault results                  | 64 |  |  |

| 6 | DISC         | SCUSSION66                |                                           |    |  |  |

| 7 | SUMMARY68    |                           |                                           |    |  |  |

| 8 | REFERENCES69 |                           |                                           |    |  |  |

#### **FOREWORD**

The objective of this thesis was to reduce the digital area in a power management integrated circuit by replacing selected flip-flops with latches. The negative effects of the replacement on power consumption and manufacturing testing were to be minimized. The thesis was carried out at Nordic Semiconductor Finland from January 2022 to June 2022.

I would like to thank my manager Joni Jäntti for acting as the technical advisor for the thesis, providing the subject for the thesis and his invaluable comments and guidance during the thesis work. I would also like to thank University Lecturer Jukka Lahti for supervising the thesis and for his great work teaching several courses that provided helpful background knowledge for the thesis. Lastly, I would like to thank D.Sc. Tarmo Ruotsalainen for being the second examiner for the thesis.

Oulu, June 15, 2022

Matti Leinonen

#### LIST OF ABBREVIATIONS AND SYMBOLS

AMBA Advanced Microcontroller Bus Architecture

APB Advanced Peripheral Bus ATE Automatic test equipment

ATPG Automatic test pattern generation

BIST Built-in self-test CF Coupling fault

CMOS Complementary metal-oxide-semiconductor

CUT Circuit under test

DFT Design for testability

DRAM Dynamic random-access memory

FSM Finite-state machine I/O Input or output

I2C Inter-integrated circuit

IC Integrated circuit

IDDQ Leakage current

IoT Internet of things

LDO Low-dropout

LFSR Linear feedback shift register

LOCST LSSD on-chip self-test

LSSD Level-sensitive scan design

MISR Multiple-input signature register

MSB Most significant bit

ORA Output response analyser

OTP One-time programmable

PMIC Power management integrated circuit PRPG Pseudo-random pattern generator

ROM Read-only memory RTL Register-transfer level

SAF Stuck-at fault

SAIF Switching activity information format

SISR Single-input signature register

SoC System on chip

SRAM Static random-access memory

STUMPS Self-testing using MISR and parallel shift register sequence generator

TF Transition fault

TPG Test pattern generator

a Switching activity factor

$C_L$  Load capacitance f Clock frequency  $I_{lk}$  Leakage current  $I_{sc}$  Short-circuit current

$P_{sc}$  Short-circuit power consumption

$P_{st}$  Static power consumption  $P_{sw}$  Switching power consumption

$t_{borrow}$  Time borrowed

T<sub>c</sub> Clock period

$t_{cd}$  Contamination delay

$t_{cqcd}$  Clock-to-Q contamination delay  $t_{cqpd}$  Clock-to-Q propagation delay  $t_{dqcd}$  D-to-Q contamination delay  $t_{dqpd}$  D-to-Q propagation delay

$t_{hold}$  Hold time

$t_{pd}$  Propagation delay

$t_{pw}$  Pulse width  $t_{setup}$  Setup time  $t_{skew}$  Clock skew  $V_{dd}$  Supply voltage

max(a,b) Maximum of a and b

#### 1 INTRODUCTION

The emergence of the internet of things (IoT) phenomenon has brought an explosion of lightweight sensors being placed in all kinds of objects and sharing the sensor data wirelessly. For the analogue, digital, and mixed signal circuits of these IoT devices to work properly, they should be provided with clean and correct level supply voltages. Such voltages are converted from raw supplies, like batteries, with power management integrated circuits (PMICs).

A simple PMICs can be just a low-dropout (LDO) regulator, that converts the battery voltage to a clean and correct level supply voltage. Most PMICs are much more complicated, often offering safety and control features. These more complex features are often implemented, at least in part, with digital logic.

The cost, size, and power consumption are important characteristics of PMICs. These characteristics are however often in conflict with each other. Integrated circuits (ICs) have traditionally incorporated ever increasing amounts of logic on smaller areas by moving to smaller and smaller technology nodes. PMICs have not been able to fully harness the area benefits of these smaller nodes due to their power requirements. PMICs need to be able to handle all the current going through them that go to the rest of the system. Transistors with large currents going through them need to be made large, regardless of the technology size. Making large transistors in small technologies is more expensive than in larger technologies. The power density also needs to be kept at an acceptable level. If the PMIC is made too small, too much power can be concentrated on a small area, leading to high temperatures. Another consideration, especially for battery powered applications, is the quiescent current consumption. The subthreshold leakage current generally increases when the channel length of a transistor decreases in the smaller technologies.

Another option to decrease the area is to implement the same functionality with fewer transistors. Most of the digital logic area consists of D flip-flops. From the area point of view, large area savings are available if they were replaced with D latches, since D latches are roughly half the size of D flip-flops. Replacing flip-flops with laches would result in either smaller area, and reduced chip cost, or more functionality in the same area, and increased chip value. The area of digital logic directly affects the size and cost of a product. With large volumes, even a slight cost decrease can produce large profits.

The main objective of the thesis is to decrease the area of digital logic in a PMIC, by replacing selected flip-flops with latches. The latch replacement should not significantly increase the power consumption of a PMIC. The latch replacement should also not significantly affect the quality of manufacturing testing.

The scope of the thesis is as follows:

- Literature review of flip-flop and latch characteristics is carried out to help in selecting flip-flops that are suited to be replaced with latches or pulsed latches in a PMIC.

- Literature review of design for testability (DFT) methods is carried out to help in selecting a suitable DFT method for the latch based PMIC design.

- Selecting and implementing a suitable latch based PMIC design, based on findings from the literature review, and the structure of a reference PMIC.

- Selecting and implementing a suitable DFT method, based on findings from the literature review and the structure of the latch based PMIC.

The thesis is organized into the following chapters:

- Chapter 1 introduces the thesis and describes the motivation and objectives for the thesis.

- Chapter 2 presents the background theory of sequential logic.

- Chapter 3 presents background theory of design for testability methods.

- Chapter 4 presents a latch register design using partial scan as the DFT method, that reduces the area of a flip-flop-based reference PMIC design.

- Chapter 5 presents the area, power consumption and automatic pattern generation results for the latch register design, compared against the flip-flop-based reference design.

- Chapter 6 provides discussion on the practical work, the results, and possible future work.

# 2 SEQUENTIAL LOGIC

Digital circuits consist of combinational and sequential logic. Combinational logic consists of logic gates, such as NAND and NOR gates. The outputs of combinational logic depend only on the states of its inputs. Unlike combinational logic, the outputs of sequential logic also depend on the previous state of its inputs through feedback. Sequential logic has memory and is made of flip-flops and latches. [1, 2]

The distinction between latches and flip-flops is not always completely clear. Edge triggered circuits are considered flip-flops in [1] and [2], while level triggered circuits are considered latches. On the other hand, level triggered circuits are considered flip-flops in [3]. This thesis considers edge triggered circuits to be flip-flops, where the output changes on the positive or negative edge of the clock signal. Level triggered circuits are considered synchronous latches, where the output changes when the clock signal is either high or low. Asynchronous latches do not have a clock input and the output changes when the inputs are changed.

#### 2.1 Latches

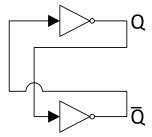

Two cross-coupled inverters form a building block of sequential circuits, a bistable element. The element, in Figure 1, has zero inputs and two complementary outputs, Q and  $\bar{Q}$ . The outputs have two stable states, Q=0 and  $\bar{Q}$ =1 or Q=1 and  $\bar{Q}$ =0, which makes the element bistable. It can store one bit of information, but it is not very useful as it has no inputs to control its state. [1, 2]

Figure 1. Cross-coupled inverter pair.

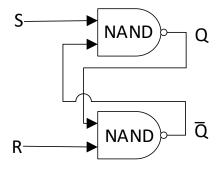

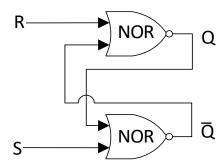

Replacing the two cross-coupled inverters with two NAND gates, like in Figure 2, or two NOR gates, like in Figure 3, gives us the SR latch. The state of the SR latch can now be controlled though the S and R inputs. The difference between the NAND and NOR implementations is the polarity at which the inputs are asserted active. The NOR implementation has active high inputs, and the NAND implementation has active low inputs. The S input sets the output Q high, and the R input resets it low. If neither the S nor R input is asserted, the output keeps its previous state. Having both inputs asserted at the same time, would lead to both outputs, Q and  $\overline{Q}$ , having the same value. It would mean the two outputs are no longer complementary. If both inputs are then de-asserted at the same time, the next output will be unpredictable. For these reasons, having both inputs asserted at the same time is an invalid condition. [1, 2, 3]

Figure 2. Asynchronous SR latch with two NAND gates.

Figure 3. Asynchronous SR latch with two NOR gates.

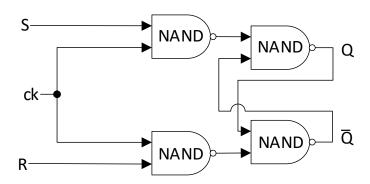

The SR latch presented above is asynchronous by nature, the change in input is seen immediately in the output. It can be made synchronous by slightly modifying it and adding a clock input, like in Figure 4. The clock, ck, signal can now be used to control the transparency of the latch. When ck is low, the outputs of the first two NAND gates will be high, regardless of the values of S and R and the latch keeps its old output value. When ck is high, the S and R inputs have immediate effect on the Q and  $\overline{Q}$  outputs. [2, 3]

Figure 4. Synchronous SR latch with four NAND gates.

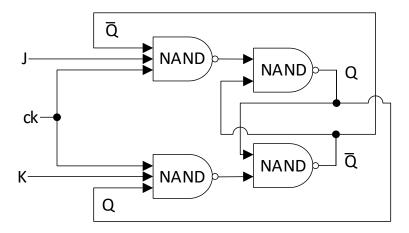

Adding cross coupled feedback to the synchronous SR latch gives use the JK latch of Figure 5. Note that the input signal names have been changed from S to J and R to K. The benefit of the added feedback is that both inputs can be active at the same time because complementary outputs, for Q and  $\overline{Q}$ , are guaranteed. However, there is still the problem that when both inputs and the clock are active, the outputs will oscillate back and forth from high to low, until the clock signal goes inactive. Similarly to the synchronous SR latch, the JK latch is set when the

J input and clock are high and reset when the K input and clock are high. The JK latch also keeps its previous state if the clock is low, regardless of the values of the J and K inputs. [2, 3]

Figure 5. JK latch from the synchronous SR latch with feedback.

The clocked SR latch can be turned into a D latch by connecting an inverter from the S input to the R input. The S input is now renamed the D input and the R input is removed. The result is the D latch presented in Figure 6. The strange behaviour of setting and resetting the SR latch at the same time can now be avoided. It also has the advantage of only having one data input compared to the SR and JK latches. The clock is used to control when the latch is transparent. When ck is high, the latch is transparent, and the value of the D input is continuously loaded to the output of the latch. When ck is low, the output is latched to the last input, and the value of D input does not affect the output. [1, 2]

Figure 6. D latch with four NAND gates and an inverter.

The transparency of the latches makes them problematic to use in sequential circuits. Latches cannot be connected in series with the same polarity clock. If all the series connected latches are transparent when clock is high, a change in the input of the first latch can propagate through all the latches. Latches are prone to race conditions. If the input of the latch changes due to feedback paths, while the latch is still transparent, there will be an additional change to the output. Latches are also prone to glitches. Glitches at the input of the latch can propagate to the output when the latch is transparent. The solution is to modify the latches to be edge-triggered instead of level-triggered, giving us flip-flops. [2, 3]

# 2.2 Flip-flops

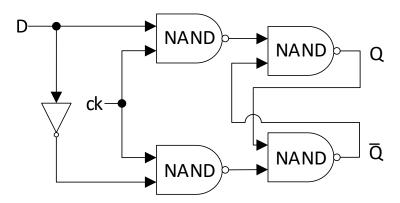

A simple way of making latches edge triggered is to make the clock pulse very short, giving us the pulsed latch or the pulsed flip-flop. An edge detector, often also called a pulser, can be used to detect the rising edge of a normal 50% duty cycle clock signal and convert it to a narrow output pulse. [3]

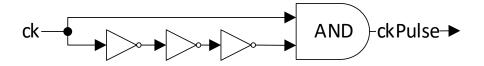

A simple edge detector can be made by connecting the clock signal to the input of an AND gate and connecting an inverted and delayed clock signal to the other input, like in Figure 7. The clock signal is delayed by the gate delay of the inverters and the number of inverters can be used to control the width of the output pulse. An odd number of inverters is needed to invert the clock signal. [3]

Figure 7. Edge detector using an AND gate and three inverters.

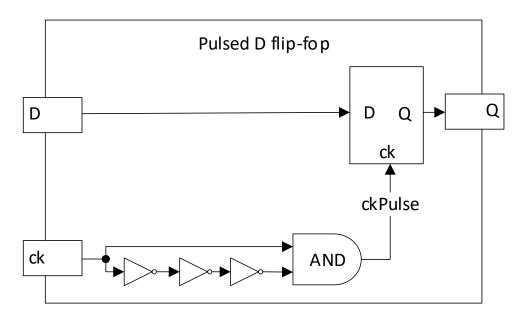

If the edge detector is integrated inside each sequential element, the element is often called a pulsed flip-flop, shown in Figure 8. Several latches can be made to share a single edge detector, often called pulsed latches, to save area and power consumption.

Figure 8. Pulsed D flip-flop from an edge detector and a D latch.

The problem with using edge detection circuitry is guaranteeing the width of the output pulse. The gate delays of logic gates vary with different process and environmental corners such

as temperature and supply voltage. Using pulsed latches can be impractical for designs with fast clocks. [2, 3]

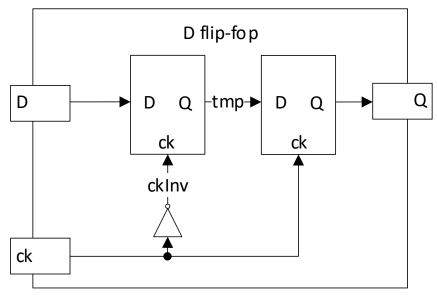

A more widely used method of achieving edge triggered operation is to use a primary-secondary structure, giving us the flip-flop. In it, a primary and a secondary latch are connected in series and using complementary clocks. The first latch is called the primary and the second latch the secondary. Since the latches use complementary clocks, both are never transparent at the same time. The flip-flop will be positive edge triggered if the inverted clock is provided to the primary latch. For negative edge triggering, the inverted clock is provided to the secondary latch instead. [1, 2]

A primary-secondary D flip-flop can be constructed from two D latches, like in Figure 9. It works by loading the value of its data input to its output on the positive edge of the clock signal. When the clock signal is low, the primary latch is transparent, and the value of the data input signal is loaded to the output of the primary latch. On the other hand, the secondary latch is disabled, and it keeps its old state. Changes in the data input can only affect the output of the primary, but not the secondary. When the clock signal rises, the primary latch closes, and it retains the state it had just before the clock edge. At the same time, the secondary latch becomes transparent, and the output of the primary is loaded into the secondary. Since the primary latch is disabled, a change in the data input will not affect the output of the flip-flop. The output of the flip-flop can change only at the positive edge of the clock. A waveform to illustrate the positive edge active operation of the primary-secondary D flip-flop, of Figure 9, is shown in Figure 10. [1]

Figure 9. Primary-secondary D flip-flop from two D latches and an inverter.

Figure 10. An example waveform of a positive edge active primary-secondary D flip-flop.

The D flip-flop is the most widely used type of sequential element [2]. It has the benefit of having only one data input compared to the SR and JK flip-flops. It can also be constructed out of a smaller number of logic gates than the JK flip-flop [4]. It also does not suffer from the transparency of the latches. However, as the D latch is roughly half the size of the primary secondary D flip-flop, it is an enticing option even with its timing problems. The pulsed flip-flop also brings a slight size decrease, being roughly <sup>3</sup>/<sub>4</sub> the size of a primary secondary flip-flop.

# 2.3 Resettable sequential logic

A reset is used to force the digital circuit into a known state, especially after the voltage supplies are provided. When a flip-flop or a latch is reset, it ignores the data input and resets the output low. If the output of the sequential element is instead reset to high, it is then often called a set. The reset can be either active high or active low. An active high reset causes a reset when it is high and an active low when it is low. The reset can be either synchronous or asynchronous. The reset is asynchronous if it resets the flip-flops and latches immediately after the reset is asserted, regardless of the clock signal. The reset is synchronous if it resets the flip-flops and latches only after the clock is active. [1]

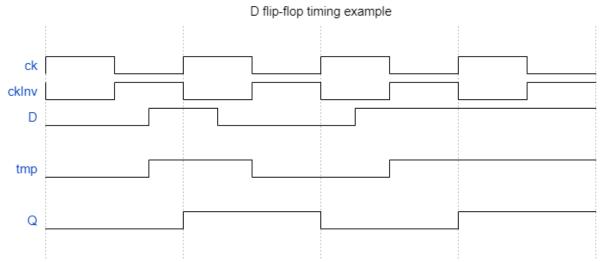

A synchronous reset can easily be implemented with combinational logic to the data input of a latch or a flip-flop. For example, an active low synchronous reset can be implemented by connecting the data signal and the reset signal through an AND gate to the D input of a D flip-flop, like in Figure 11. When the reset signal is low, the output of the AND gate is low, regardless of the data signal. When the reset signal is high, the output of the AND gate is determined by the data signal. [1]

Figure 11. Synchronously resettable D flip-flop.

To implement an asynchronous reset, the internal structure of the of the flip-flop or latch needs to be modified [1]. For example, an active low asynchronous set can be implemented by adding a S input to the NAND gate producing the Q output of a D latch. An active low asynchronous reset can be implemented by adding a R input to the NAND gate producing the  $\bar{Q}$  output. Figure 12 shows an asynchronously settable and resettable D latch. When the reset signal is low, it forces the  $\bar{Q}$  output high and Q output low. When the set signal is low, it forces the Q output high and the  $\bar{Q}$  output low. [3]

Figure 12. Asynchronously resettable and settable D latch.

#### 2.4 Registers

Flip-flops, using the same clock, can be grouped together to form registers. A group of n flip-flops can store n-bits of binary data. In addition to flip-flops, a register can also have combinational logic to control how data is transferred to the flip-flops. [4]

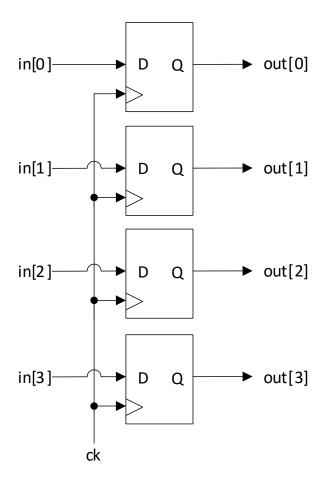

If all the flip-flops of a register are loaded simultaneously, it is called a parallel loaded register. This type of register is an important building block in digital circuits. A simple register with no combinational logic, like in Figure 13, transfers the data from its inputs to the outputs on each active clock edge. Typically, a control signal and additional logic is needed to control whether a new value is loaded to the register or whether the old value is kept. [4]

Figure 13. A four bit register with D flip-flops.

Keeping the old value can be achieved by stopping the clock from running. When the control signal is inactive, a clock gate is used to disable the clock to the register. The flip-flops inside the register are prevented from updating their value due to the lack of the clock signal. This method has the disadvantage of adding logic on the clock path. [4]

Another way to retain the state of the register is to control the data input of the register. The register output can be fed back to the input for the register to retain its value. Multiplexer combinational logic and the control signal can be used to select whether the register output or the regular load signal is fed to the input of the register. [4]

A clock gate is larger than a multiplexer, but as the same clock gate can be used to stop the clock to all the flip-flops in a single register, whereas every flip-flop in a register needs their own multiplexer to feed back the old value, from the area point of view, clock gating is beneficial for multi-bit registers.

A shift register differs from a typical register by the fact that the flip-flops are connected in series. The input of the first flip-flop is connected to a serial input and the output of the last flip-flip is connected to serial output. Data is loaded to the shift register by inputting it to the serial input. On each clock cycle the data is shifted forward from all flip-flops in the shift register to the next one in the shift register. A simple shift register consists only of flip-flops, but combinational logic can be inserted to control when the data is shifted forwards, similar to the case with the parallel loaded register. [4]

Registers are typically made from D flip-flops [1]. The parallel loaded register could be constructed using D latches to save area. Due to the latch being transparent on the whole active clock level, clock gating could be used as the loading control to reduce glitches at the same

time. The shift register is problematic to construct using D latches. Due to the latch being transparent on the whole active clock level, data input to the first latch would propagate through as many latches as the gate delays would permit [2]. A solution would be to have every second latch be positive level active and every other latch negative level active.

# 2.5 Timing analysis of sequential logic

The use of sequential logic allows for orderly operation of a circuit. Sequential storage elements store the state of the circuit. Combinational logic calculates the next state of the circuit from the current state and the external inputs. The next state of the circuit is loaded to the sequential elements on the next active clock edge or level. For the operation of the circuit to be clearly defined, the memory elements cannot mix data from the next or previous cycles with the data from the current cycle [5]. Minimum and maximum propagation delays can be defined between sequential elements.

## 2.5.1 Timing of flip-flops

On the active edge of a clock, the data input of a flip-flop is transferred to the output. The output starts to change after a clock-to-Q contamination delay,  $t_{cqcd}$ , at the earliest and the change has finished after a clock-to-Q propagation delay,  $t_{cqpd}$ , at the latest. [1, 5]

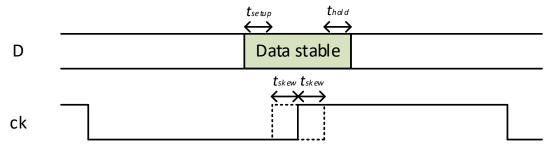

The data propagates through the combinational logic to the next flip-flop after a contamination delay,  $t_{cd}$ , at the earliest and after a propagation delay,  $t_{pd}$ , at the latest. The flip-flop samples the correct value, if the data inputs settle a setup time,  $t_{setup}$ , before the active clock edge and stay stable a hold time,  $t_{hold}$ , after. Possible skew,  $t_{skew}$ , between the clocks to the launching and receiving flip-flops needs to be also taken to account in the timing analysis. The time window, that the data inputs need to be stable in, is show in Figure 14. [1, 5]

Figure 14. The setup and hold requirements of a D flip-flop.

Since the clock period is often a fixed requirement and the clock-to-Q propagation delay, setup time and hold times are specified by the technology used, the only variable usually controllable by the designer is the propagation delay of the combinational logic paths. The maximum propagation delay allowed between flip-flops for the data to arrive setup time before the next active clock edge is

$$t_{pd} \le T_c - t_{cqpd} - t_{skew} - t_{setup},\tag{1}$$

where  $t_{pd}$  is the propagation delay between two flip-flops,  $T_c$  is the clock period,  $t_{cqpd}$  is the clock-to-Q propagation delay of a flip-flop,  $t_{skew}$  is the clock skew between the flip-flops and  $t_{setup}$  is the setup time requirement. [1, 5]

The minimum contamination delay allowed between flip-flops for the data to arrive hold time after the current active clock edge is

$$t_{cd} \ge t_{hold} + t_{skew} - t_{cacd},\tag{2}$$

where  $t_{cd}$  is contamination delay between two flip-flops,  $t_{hold}$  is the hold time requirement,  $t_{skew}$  is the clock skew between the flip-flops and  $t_{cqcd}$  is the clock-to-Q contamination delay of a flip-flop. [1, 5]

# 2.5.2 Timing of latches

Analysing the timing of latches is more complicated, as the latch is transparent on the active clock level and not just the edge. All consecutive latches need to use non-overlapping clocks so that they are not transparent at the same time. The simplest way is to use complemented clocks. This means one latch is transparent for the first half clock cycle and the next latch is transparent for the other half cycle. Another way is to use clocks with less than 50% duty cycle, with enough phase shift between them to not overlap. [5]

Latches load the new data at any point in the active clock level, depending on when it arrives. If the data arrives before the active clock edge, the data is loaded from the input to the output on the active edge of the clock. A change in output is seen after a clock-to-Q contamination delay,  $t_{cqcd}$ , at the earliest and after a clock-to-Q propagation delay,  $t_{cqpd}$ , at the latest. If the data arrives when the clock level is already active, the data is loaded from the input to the output after a D-to-Q contamination delay,  $t_{dqcd}$ , at the earliest and after a D-to-Q propagation delay,  $t_{dqpd}$ , at the latest. [5]

Similarly, to the flip-flops, the data propagates to the input of the next latch after a contamination delay,  $t_{cd}$ , at the earliest and after a propagation delay,  $t_{pd}$ , at the latest. The latch samples the correct value, if the data input has settled setup time,  $t_{setup}$ , before the inactive clock edge and stays stable a hold time,  $t_{hold}$ , after. [5]

Due to the level transparent nature of latches, they can be used in a way that the data arrives more than the setup time and clock skew before the inactive clock edge. In that case the setup time and clock skew can be left out of the maximum allowed propagation delay analysis. The maximum allowed propagation delay between two latches using different clock edges is

$$t_{pd} \le \frac{T_c}{2} - t_{dqpd},\tag{3}$$

where  $t_{pd}$  is the propagation delay between two latches,  $T_c$  is the clock period and  $t_{dqpd}$  is the D-to-Q propagation delay of a latch. The clock period is divided by two, as two back-to-back latches use complemented clocks. [5]

The minimum contamination delay allowed between two latches for the data to arrive hold time after the inactive clock edge to the first latch is

$$t_{cd} \ge t_{hold} + t_{skew} - t_{cqcd},\tag{4}$$

where  $t_{cd}$  is contamination delay between two latches,  $t_{hold}$  is the hold time requirement,  $t_{skew}$  is the clock skew between the latches and  $t_{cqcd}$  is the clock-to-Q contamination delay of a latch. The clock-to-Q contamination delay is used for minimum contamination delay analysis instead of the D-to-Q contamination delay, as the output of the first latch can change from the active edge of the clock at the earliest. [5]

# 2.5.3 Timing of pulsed latches

Pulsed latches behave the same as the normal latch, with the difference being that they use short pulses as clock instead of the normal 50% duty cycle clock. The pulsed latches can use the same clock signal if the clock pulse is shorter than the propagation delay between the pulsed latches and the hold time requirement is not violated. If the pulses are short enough, the timing of pulsed latch starts to resemble that of the flip-flop. [5]

The data input of the pulsed latch must settle setup time and clock skew before the inactive edge of the clock pulse. The setup time may be before the active clock edge or after, depending on the width of the clock pulse and the clock skew. If the clock pulse is wider than the setup time and clock skew combined, the data needs to only arrive when the latch is already transparent, and the timing analysis for the propagation delay is the same as for the normal latch. If the clock pulse is shorter, the data needs to arrive while the latch is not yet transparent. In that case the setup time and clock skew need to be considered in the maximum allowed propagation delay, similarly to the flip-flop case. The maximum allowed propagation delay between two pulsed latches is

$$t_{pd} \le T_c - t_{dqpd} - \max(0, t_{setup} + t_{skew} - t_{pw}), \tag{5}$$

where  $t_{pd}$  is the propagation delay between two latches,  $T_c$  is the clock period,  $t_{dqpd}$ , is the D-to-Q propagation delay of a latch,  $t_{setup}$  is the setup time,  $t_{skew}$  is the clock skew and  $t_{pw}$  is the pulse width of the clock. [5]

The data output of the first latch can change at the active clock edge at the earliest. The data input of the second latch cannot change until a hold time and clock skew after the inactive edge of the pulse. The minimum contamination delay allowed between two latches for the data to arrive hold time after the inactive clock edge to the first latch is

$$t_{cd} \ge t_{pw} + t_{hold} + t_{skew} - t_{cacd},\tag{6}$$

where  $t_{cd}$  is contamination delay between two latches,  $t_{pw}$  is the width of the clock pulse,  $t_{hold}$  is the hold time requirement,  $t_{skew}$  is the clock skew between the latches and  $t_{cqcd}$  is the clock-to-Q contamination delay of a latch. [5]

As can be seen from comparing the contamination delay equations of flip-flops (4) and pulsed latches (6), the contamination delay of the pulsed latch depends on the pulse width and needs to be larger. This can result, in pulsed latch designs, to more hold time violations, that need to be fixed.

#### 2.5.4 Time borrowing

Due to the level transparent nature of a latch, data can arrive to the input of the latch at any time on the active clock level and it will propagate to the output. The propagation delay from one latch to the input of the next does not need to be exactly half a clock cycle. Some logic blocks can have larger delays while some have shorter delays. Slow logic using time allocated to faster logic is called time borrowing. As flip-flops are edge triggered, time borrowing is not possible with them. [5]

The direction of time borrowing depends on when the latches update on the clock cycle. If the latches update in the beginning of the active clock level, the next latch can borrow time and update later in the active clock level. If the latches update at the end of the clock level, the next latch can update earlier and not have to wait for the end of the active clock level, giving more time to the next latches. Time borrowing can happen over multiple latches, as long as the data does not arrive so late as to cause a setup time violation in any of the latches. [5]

As the latches update as soon as the data arrives on the active level, they naturally move to updating at the active clock edge. In that case, the amount of time allowed for borrowing is at its highest. If the data departs the first latch on its active clock edge, it normally arrives at the next latch half a clock cycle later. The circuit will still operate correctly if it arrives setup time and clock skew before the inactive clock edge of the second latch instead. The maximum time that can be borrowed therefore is

$$t_{borrow} \le \frac{T_c}{2} - t_{setup} - t_{skew},\tag{7}$$

where  $t_{borrow}$  is the time borrowed,  $T_c$  is the clock period,  $t_{setup}$  is the required setup time and  $t_{skew}$  is the clock skew between the latches. [5]

If the latches are transparent shorter amount of time in the cycle, the amount of time that can be borrowed reduces. The maximum time that can be borrowed with pulsed latches is

$$t_{borrow} \le t_{pw} - t_{setup} - t_{skew}, \tag{8}$$

where  $t_{borrow}$  is the time borrowed,  $t_{pw}$  is the width of the clock pulse,  $t_{setup}$  is the required setup time and  $t_{skew}$  is the clock skew between the latches. If the pulse width is shorter than setup time and clock skew, time borrowing is not possible. [5]

#### 2.5.5 Fixing timing violations

Violating either the setup or hold time constraints means that memory element can sample the input while it is still changing leading to an ambiguous output. [5]

To fix setup time violations, the designer can redesign the combinational logic paths between the sequential elements to be shorter or add sequential elements in the middle of the combinational logic. As we can see from equations (1), (3) and (5), the clock period can also be made larger to increase the allowed propagation delay.

To fix hold time violations, the designer can add buffers between the sequential elements, that increase the contamination delay. As we can see from equations (2), (4) and (6), the clock period does not affect the contamination delay and so it cannot be used to fix hold time violations. [5]

# 2.6 Power consumption of CMOS logic

The power consumption in digital complementary metal-oxide-semiconductor (CMOS) logic consists of static and dynamic power consumption. Dynamic power consumption results from the switching activity of the circuit and consists of switching power consumption and short-circuit power consumption. When the value of a logic gate changes, its load capacitance needs to be charged or discharged resulting in the switching power consumption of

$$P_{sw} = C_L * V_{dd}^2 * f * \alpha, \tag{9}$$

where  $C_L$  is the load capacitance,  $V_{dd}$  is the supply voltage, f is the clock frequency and a is the switching activity factor. Short-circuit current results from a momentary short-circuit through the transistors from the supply voltage to ground when the logic gate is switching its state. Short-circuit power consumption can be expressed as

$$P_{sc} = I_{sc} * V_{dd}, \tag{10}$$

where  $V_{dd}$  is the supply voltage and  $I_{sc}$  is the average short-circuit current. [6]

The static power consumption represents the power consumption when the circuit is inactive. The transistors in the circuit conduct small amounts of leakage current event when in the cut-off state. The static current consumption can be expressed as

$$P_{st} = I_{lk} * V_{dd}, \tag{11}$$

where  $V_{dd}$  is the supply voltage and  $I_{lk}$  is the leakage current. [6]

#### 3 DESIGN FOR TESTABILITY

Modern integrated circuits (ICs) are made with nanometre-scale lithographic techniques. Some of these manufactured ICs are faulty due to manufacturing defects. During the manufacturing process, all the ICs need to be tested to remove the faulty ones. Inadequate testing leads to faulty ICs being shipped to the customers.

Manufacturing testing of digital logic is typically done with the help of automatic test equipment (ATE) and automatic test pattern generation (ATPG) tools. ATPG tools use algorithms to generate test patterns that detect faults in a faulty circuit. ATE is computer-controlled equipment that applies test patterns to the circuit under test (CUT) and compares the circuit responses to the stored responses of a fault-free circuit. Fault simulations are used to estimate the quality of the generated test patterns. [7]

The test patterns are usually generated based on specific fault models, that represent specific faults resulting from manufacturing defects. The stuck-at fault (SAF) model is a widely used fault model. It assumes that a faulty signal line is stuck to either a logic 1 or a logic 0. The stuck-at fault can be detected by driving the specific signal line to the opposite state than the assumed fault and observing whether the line was stuck or not. Test pattern that detects both stuck at 1 and stuck at 0 faults on every signal line need to be generated to reach 100% stuck-at fault coverage. Test patterns generated based on the stuck-at fault model also detect most faults based on other models. The stuck-at fault model however does not guarantee detecting all possible defects and a combination of tests, made with different fault models, are typically used in digital testing. [7]

For the circuit to behave correctly, it should not only perform the correct logical operation, but also perform it fast enough for the change to propagate to the next flip-flop. At-speed testing refers to tests that detect delay defects from a circuit running at functional speed. The transition fault (TF) model assumes a single faulty gate is either slow to rise or slow to fall, so that the transition does not reach the flip-flop or primary output within the clock period. Transition faults are detected by first setting the target node to an initial value, then causing a transition to the target node, and finally observing the fault effect from a scannable flip-flop or a primary output. [7]

Some defects may not affect the correct operation of the circuit but can result in increased power consumption. Leakage current (IDDQ) test measures the CUT supply current in steady state condition to detect defects. The IDDQ test can detect shorts between signal lines or between signal lines and supply lines, from the increased leakage current of the shorts. IDDQ testing requires that the internal nodes can be controlled, to toggle the internal nodes to different states, but does not require observation, since the pass and fail condition is determined only on the supply current consumption. [7]

Integrated circuits can consist of deep sequential logic. Internal signal lines in this kind of circuit can be extremely hard to control and observe from the primary inputs and outputs of the circuit, which can result in very complex test patterns and low fault coverage. [7]

Design for testability (DFT) methods have been developed to improve the testing of digital integrated circuits. They refer to methods, where the testability of the digital circuit is considered already in the designing of the circuit. Logic structures, meant to facilitate testing, are added to the design to reduce the time and therefore the cost of testing, and to improve testing fault coverage. [7]

#### 3.1 Scan design

Scan design is the most widely used DFT approach for improving testability. In it, the controllability and observability of sequential elements is improved by providing external access to them. This is done by converting the sequential elements to scannable sequential elements, called scan cells, and connecting them to form shift registers, called scan chains. [7]

The use of scan chains allows test stimulus to be easily shifted to the storage elements inside the IC, without having to control the primary inputs of the circuit for several clock cycles in order to bring the internal storage elements to a desired state. The use of scan chains also allows the test response to be easily shifted out of the internal storage elements. Since the inputs to combinational logic blocks can be controlled directly and the outputs of combinational logic blocks can be observed directly, the test pattern complexity required to test specific faults is greatly reduced. [7]

The scan cells have two inputs. The data input is connected to the normal combinational logic path. The scan input is connected to the output of another scan cell. The scan chain is made accessible by connecting the scan input of the first scan cell, in the chain, to a primary input of the IC and connecting the output of the last scan cell, in the chain, to a primary output of the IC. [7]

Shifting the test stimulus in and the test response out of a scan chain made of n storage elements takes n clock cycles. Having several scan chains reduces the clock cycles needed for shifting, with the disadvantage of one primary input and output needed for each scan chain. [7]

A scan design has several modes of operation. In normal mode, all the added scan functionality is disabled, and the design operates like before adding the additional logic. In scan mode, all scan related fixes, to improve test coverage or to guarantee safe operation during scan testing, are turned on. In shift mode, all scan and shift related fixes are turned on, and scan chains are enabled to allow shifting in test patterns or shifting out test results. Table 1 below shows a set of scan design rules and their suggested fixes. [7]

Table 1. Scan design rules

| Rule                                                         | Recommended fix                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Avoid tristate<br>buses during shift                         | Two or more bus drivers trying to drive a tristate bus to opposite logic values causes bus contention. It should be guaranteed that only one driver controls the bus at a time during shift. This can be done by forcing one bus driver enable signal high and all others low during shift.                                                          |

| Avoid bidirectional input or output (I/O) ports during shift | Conflicts can occur at a bidirectional port during shift operation if it is used as an input port and the output tristate buffer is controlled by logic connected to a scan cell. The output tristate buffer should be disabled during shift. This can be done by forcing the enable signal controlling the output tristate buffer low during shift. |

| Avoid gated clocks during shift                              | Clock gating can prevent shift operation from happening correctly by blocking the scan clock from reaching the scan cells. Clock gating should be disabled during shift. This can be done by forcing the enable signal of all clock gates high during shift.                                                                                         |

| Avoid derived clocks during scan                             | A clock generated internally in the digital logic is a derived clock. They should be bypassed during the scan test, in order to test the logic driven by the derived clocks. This can be done by using a multiplexer to provide a scan clock instead of the derived clock during scan.                                                               |

| Avoid combinational feedback loops during scan | The use of combinational feedback loops can lead to loss of fault coverage, since they cannot be controlled, or their value determined. Combinational feedback loops should be removed from the design. If removing is not possible, they should be broken during scan. This can be done by inserting a scan cell in the loop that is used during scan. |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Avoid                                          | Internally generated asynchronous set and reset signals to scan cells,                                                                                                                                                                                                                                                                                  |

| asynchronous set                               | that are not directly controlled from a primary input, can prevent shift                                                                                                                                                                                                                                                                                |

| and reset signals                              | operation from happening correctly. Asynchronous set and reset                                                                                                                                                                                                                                                                                          |

| during scan                                    | signals to scan cells should be forced to inactive state during scan.                                                                                                                                                                                                                                                                                   |

| Avoid clocks                                   | Clock used as a data input can cause race condition when the test                                                                                                                                                                                                                                                                                       |

| driving data during                            | response is captured. Clock path to data input of flip-flop should be                                                                                                                                                                                                                                                                                   |

| scan                                           | blocked during scan.                                                                                                                                                                                                                                                                                                                                    |

| Avoid floating                                 | Bus-holders should be added for the tri-state buses to keep their last                                                                                                                                                                                                                                                                                  |

| buses during scan                              | value.                                                                                                                                                                                                                                                                                                                                                  |

| Avoid floating                                 | Floating inputs should be tied to logic 0 or logic 1 during scan.                                                                                                                                                                                                                                                                                       |

| inputs during scan                             |                                                                                                                                                                                                                                                                                                                                                         |

| Avoid non-scan                                 | Should be made transparent bypassed or initialized into a lenguar                                                                                                                                                                                                                                                                                       |

| storage elements in                            | Should be made transparent, bypassed, or initialized into a known state during scan.                                                                                                                                                                                                                                                                    |

| full-scan designs                              | state during scan.                                                                                                                                                                                                                                                                                                                                      |

The added scan operation of the circuit is controlled with the use of added test signals or test clocks. A primary input pin is often added to the design for the signal that is used to enter scan mode. Extra pins for the rest of the test signals, the scan inputs and the scan outputs can be saved by connecting them to existing primary I/O pins with multiplexers and using the scan mode signal as the enable for the multiplexers. The different test signals and test clocks used in different types of scan designs are discussed in the following sub-chapters.

Typically, all the sequential elements in a design are connected to scan chains. The advantage of full-scan is that all the inputs to combinational logic can be controlled and all the outputs to combinational logic can be observed. It makes it easier for ATPG programs to create test patterns to detect faults. A disadvantage of full scan is that the added propagation delays of scan logic on critical paths might lead to timing violations. Another disadvantage is the increased area overhead caused by the scan logic. [7]

Partial scan refers to designs where some of the sequential elements are not scannable. Sequential elements in critical paths can be left as normal sequential elements to meet timing requirements. Another advantage of partial scan is that it reduces the area overhead of using scan cells. Since not all sequential elements are controllable and observable in partial scan, the test generation complexity is increased. This can result in reduced fault coverage and increased testing time compared to full-scan. [7]

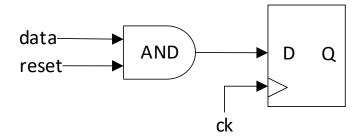

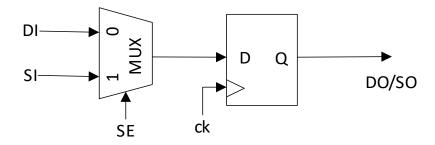

#### 3.1.1 Muxed-D scan style

The most widely used scan style is the muxed-D style. It was developed at Stanford by M. J. Y. Williams and J. B. Angell in 1973 [8]. In it, the D flip-flops are replaced with edge triggered muxed-D scan cells, shown in Figure 15. The muxed-D scan cell is made from a D flip-flop and a multiplexer. The multiplexer is used to select between the data input, DI, and scan input, SI. [7]

Figure 15. Muxed-D scan cell made from a D flip-flop and a multiplexer.

In normal and scan modes, the value at the data input is selected and loaded to the output of the flip-flop on the active edge of the clock. In shift mode, a shift enable, SE, signal is used to select the scan input. The value from the scan input is loaded to the output of the flip-flop on the active edge of the clock. [7]

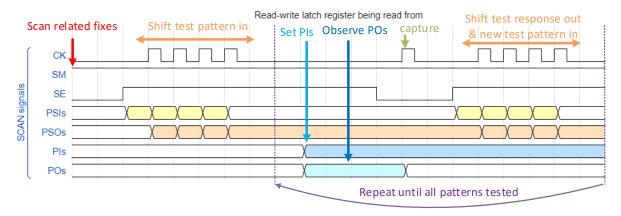

The scan testing of a muxed-D scan design consists of the following steps, also shown in Figure 16 [7].

- All scan related fixes are turned on by setting the scan mode, SM, signal high.

- The scan chain portion of the first test pattern is loaded from the primary scan input, PSI, to the chain by setting the shift enable, SE, signal high and clocking the circuit n times, where n is the number of scan cells in the scan chain.

- The test pattern is applied to the primary inputs.

- The test response is observed from the primary outputs.

- Shift enable, SE, signal is set low, and the CUT is clocked once to capture the test response of the combinational logic to the scan cells.

- The test response from the scan cells is shifted out from the primary scan output, PSO, and at the same time the next test pattern is shifted in from the primary scan input, PSI, by setting the scan enable, SE, high and clocking the circuit n times, where n is the number of scan cells in the scan chain.

- The capture and shift operations are repeated until all test patterns are tested.

Figure 16. Muxed-D scan testing example waveform.

A disadvantage of using muxed-D scan cells is the added multiplexer delay to the data path and the area increase. A benefit is the compatibility of muxed-D scan cells with modern designs

primarily using edge triggered D flip-flops. Another benefit is that the existing design automation tools provide good support for muxed-D scan style. [7]

## 3.1.2 Clocked-scan style

In the clocked-scan style, the D flip-flops are replaced with clocked-scan cells. The clocked scan cell also has a data input and a scan input. In contrast to the muxed-D scan cell, the input selection in the clocked scan cell is done using two independent clocks, the data clock, and the shift clock. [7]

In normal and scan modes, the value from the data input, DI, is loaded to the output on the active edge of the data clock, CKD. In shift mode, the value from the scan input, SI, is loaded on the active edge of the shift clock, CKS, instead. [7]

The scan testing of a clocked-scan design is similar to the muxed-D scan design. The main difference between them is in the shift operation. The clocked-scan design does not have the shift enable signal. The shifting is done through the primary scan input, PSI, and the primary scan output, PSO, by clocking the shift clock, CKS, n times, where n is the number of scan cells in the scan chain. During the shift operation, the data clock, CKD, is held inactive. The shift clock, CKS, is held inactive during the capture operation. The test response is captured to the scan cells by clocking the data clock, CKD, once.

A big advantage of the clocked-scan style is that it does not add any logic delays to the data path. The disadvantage is that it requires routing an extra shift clock to all the clocked-scan cells. [7]

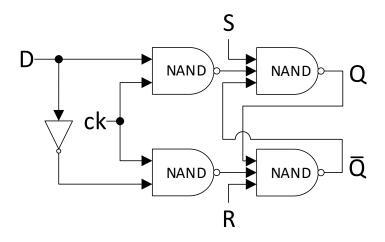

#### 3.1.3 LSSD style

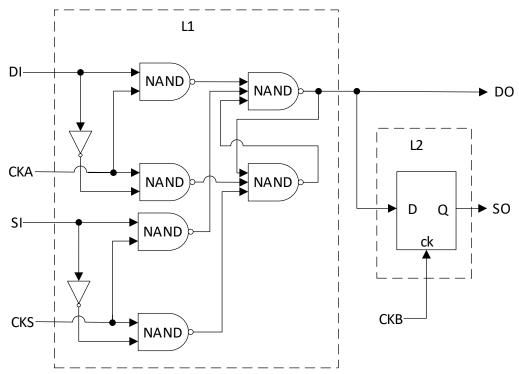

Level-sensitive scan design (LSSD) was developed at the International Business Machines Corporation by E.B. Eichelberger and T.W. Williams in 1977 [9]. It is the primary scan style used for level-sensitive, latch-based designs. In it, the D latches and D flip-flops are replaced with LSSD scan cells, shown in Figure 17. The scan cell contains two latches, a primary D latch, L1, and a secondary D latch, L2, and three clocks, the primary clock, CKA, the scan clock, CKS, and the secondary clock, CKB. The primary latch has a data input, DI, and a scan input, SI. The selection of which input is loaded to the output of the primary latch is made with the primary and scan clocks. The secondary clock is used to load the data at the primary latch output to the secondary latch output. [7]

Figure 17. Single-latch LSSD scan cell from a primary two-input D latch and a secondary D latch.

In normal and scan modes, the value at data input is loaded to the primary latch output on the active level of the primary clock. In shift mode, the value at scan input is loaded to the primary latch output at the active level of scan clock. For flip-flops, the data at the primary latch output is loaded to the secondary latch output on the positive edge of the secondary clock in all modes. For latches, the data is loaded with the secondary clock in only shift mode. All the clocks need to be operated in a non-overlapping manner to avoid race conditions. [7]

When replacing D latches with the LSSD scan cell, the data output, DO, is taken from the output of the primary latch and the scan output, SO, is taken from the output of the secondary latch, like in Figure 17. There also needs to be at least two non-overlapping system clocks, CKA1 and CKA2, supplied to the CKA ports of the LSSD scan cells to prevent back-to-back latches from being transparent at the same time. When replacing D flip-flops with the LSSD scan cell, both outputs are taken from the output of the secondary latch. [7]

The scan testing of a LSSD design is similar to the muxed-D scan design. The shifting is done through the primary scan input, PSI, and the primary scan output, PSO, by clocking the shift clock, CKS, and the secondary clock, CKB, n times in a non-overlapping manner, where n is the number of scan cells in the scan chain. During the shift operation, the primary clock, CKA, is held inactive. The shift clock, CKS, is held inactive during the capture operation. The test response is captured to the D flip-flop scan cells by clocking the primary clock, CKA, and secondary clock, CKB, in a non-overlapping manner once. The test response is loaded to the D latch scan cells by clocking the two system clocks, CKA1 and CKA2, in a non-overlapping manner once. [7]

The scan enabled LSSD scan cell uses a scan enable, SE, signal to choose between the data input, DI, and the scan input, SI, of the primary latch instead of a scan clock. The secondary latch has the same functionality as in the traditional LSSD style. [10]

The advantage of using LSSD is that it allows scan chains to be used in latch-based designs. A disadvantage is that two additional clocks need to be routed when replacing latches and one

additional clock needs to be routed when replacing flip-flops, resulting in increased routing complexity, and ultimately increased area. [7]

Replacing the D latches in a design with LSSD scan cells results in an additional secondary D latch being added for every D latch in the design, wasting a lot of area. The L1L2\* scan optimization technique saves this area by removing these dummy latches. In it, latches in the design, that are independent of each other, are grouped in pairs of L1 and L2\* latches. The logic connected to these latches can be tested independently of each other with two different test modes, L1test and L2test. In the L1test, the L1 latch is the primary latch and L2\* latch is used as the secondary latch for the L1 latch. In the L2test the L2\* latch is the primary latch and the L1 latch is used as the secondary latch for the L2\* latch. A problem with this optimization technique is choosing which latches can be grouped together. Real designs often cannot completely group all latches together and some dummy latches need to be used. Another problem is that the ATPG tool needs a remodelled netlists for both tests, where the parts that are not tested are removed from the files. [11]

#### 3.1.4 Latches in scan designs

While the LSSD scan style presented in chapter 3.1.3 is usually used in designs containing latches, there are other ways of dealing with latches in scan designs. The simplest solution that comes to mind is to not replace the latches with scannable elements. In that case, the latches need to be initialized into known states, bypassed, or made transparent during the scan test [7]. The disadvantage is that we have now a partial scan or a non-scan design with the decreased testability that comes with that.

The principle of initializing the latches to known states is used in [12], where the latch registers are modelled as combinational gates and preloaded with values before each scan test. This method allows the ability of the latches to hold data to be tested also. Preloading the background data requires adding multiplexers to the data input of the latches and OR gating a force write signal to the clock inputs of the latches. A downside of this method is that the background data needs to be supplied to the scan model by manually modifying the netlist provided to the ATPG tool. This manually modified model needs to be then also verified against the functional model with simulations. Having the same background data for all the latch registers during the test can cause some combinational logic faults to be untestable due to the reconvergence of the background data. A way around this problem is to use different background data for different groups of registers. Another way is to replace some key latches by scannable flip-flops. [12]

A single-latch and single-clock solution is proposed in [13], that uses the pulsed latch principle covered in section 2.1.5.3. A test signal is used to select between the data and scan inputs of the latch. The upper width of the test clock pulse is bounded by the shortest propagation delay of the latch design. [13]

A problem with the single-latch and single-clock solution is that it is not supported by the existing design automation tools.

An asynchronous scan-latch controller solution is proposed in [14], that uses the asynchronous symmetric pulse persistent protocol to control the scan chain made from latches. The asynchronous scan-latch controller is used to control the transparency of the latches in shift mode. The active edge in the scan clock causes the asynchronous scan-latch controller to pulse the clock input of each latch in the scan chain in turn. The last latch in the scan chain is updated first, followed by the rest all the way the first latch in the scan chain. The pulses to the clock

inputs of the latches are timed in a manner that no two latches are transparent at the same time. [14]

A disadvantage with the asynchronous scan latch controller solution is the added design complexity of the controller and the additional clock tree needed from the controller to the latches. This solution is also not supported by the existing design automation tools.

#### 3.2 Logic built-in self-test

Logic built-in self-test (BIST) is a DFT method that incorporates testing features on the CUT itself. Logic structures to generate test patterns and to analyse the output responses are embedded on the designed circuit. [7]

Logic BIST techniques can be divided into two main categories [7].

- Online BIST techniques, where the test functionalities are performed while circuit operates in normal mode, with normal functionality.

- Offline BIST techniques, where the test functionalities are performed in a test mode.

In functional offline BIST techniques, the tests are performed based on the functional specification of the circuitry. In structural offline BIST techniques, the tests are preformed based on the structure of the circuitry instead. The test pattern generation and the output response analysis in a structural offline BIST can be done either with the help of the functional storage elements, an internal BIST, or with separate added logic, an external BIST. [7]

BIST schemes most commonly convert the storage elements of a circuit to scan cells for combinational circuit testing. Some schemes, involving sequential testing by applying test patterns to the inputs of the circuit and analysing the responses at the outputs also exist. [7]

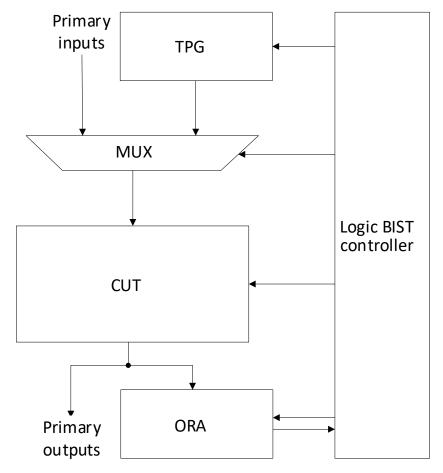

A typical logic BIST, using the structural offline BIST scheme, is shown in Figure 18. It consists of a test pattern generator (TPG) that automatically generates test patterns for the CUT once it is activated. An output response analyser (ORA) is used to automatically compact the output response into a signature. A BIST controller activates the test, compares the ORA signatures against golden signatures and reports a pass or a failure once the BIST operation is complete. [7]

Figure 18. Structure of a typical logic BIST.

The structural offline BIST technique has several advantages compared to the traditional scan techniques. Test costs are reduced as it requires simpler ATE and ATPG, less test time and less tester memory. The tests can be run at functional clock speed, allowing the detection of delay faults. The tests can be run at any time, without the help of an external tester. [7]

There are also several disadvantages compared to traditional scan techniques. There are even more stringent BIST design rules that need to be followed compared to the scan design rules. Since any unknown values that propagate to the ORA in a BIST design will corrupt the signature, following BIST design rules is mandatory for BIST designs. In contrast, breaking many of the scan design rules in a scan design will only result in the loss of fault coverage. Another disadvantage is that the BIST fault coverage is less than that of a scan design, and additional test points might need to be added to increase it to a sufficient level. [7]

#### 3.2.1 Test pattern generation

Several different methods of constructing TPGs exist for generating test patterns for exhaustive, pseudo-exhaustive and pseudo-random testing. [7]

Exhaustive testing achieves maximum fault coverage by applying all possible  $2^n$  input patterns to a circuit consisting of n inputs [7]. Exhaustive testing becomes impractical already for circuits consisting of more than 20 inputs [15].

Pseudo-exhaustive testing aims to reduce test length, while keeping the high fault coverage of exhaustive testing. Pseudo-exhaustive testing aims to exhaustively test a circuit, without applying all possible input patterns by taking advantage of the fact that all the outputs of a circuit do not usually depend on all the inputs. [7]

Pseudo-random testing aims to reduce test length even further by sacrificing fault coverage. In it, a pseudo-random sequence of test patterns is generated with a pseudo-random pattern generator (PRPG). Fault simulation is used to calculate the fault coverage of the pseudo-random test patterns. It is the most used technique for BIST test pattern generation. A downside of pseudo-random testing is that random pattern resistant faults can limit the fault coverage. Test point insertion, mixed-mode BIST, and hybrid BIST techniques can be used to increase the fault coverage of random pattern resistant circuits. [7]

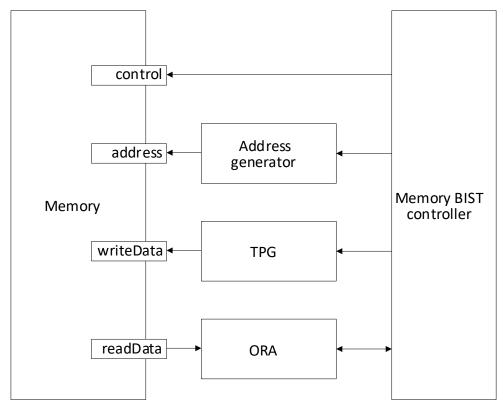

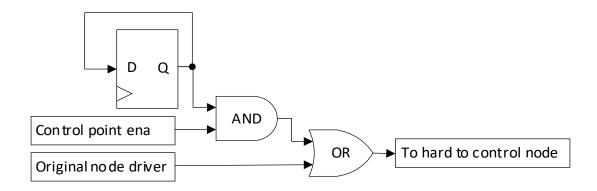

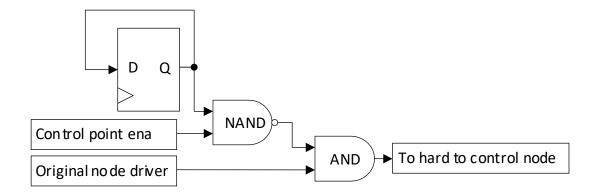

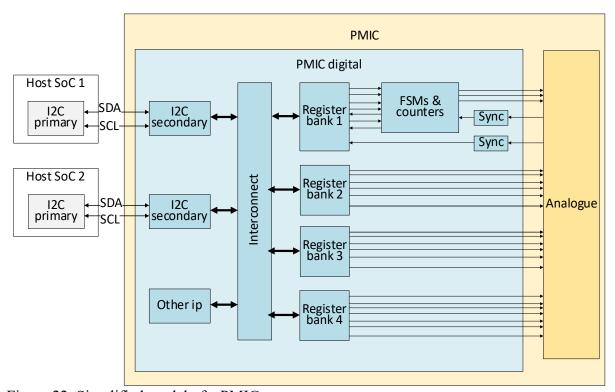

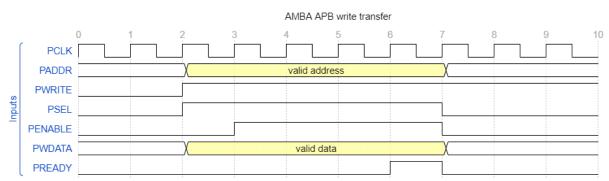

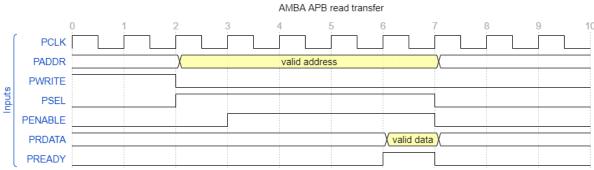

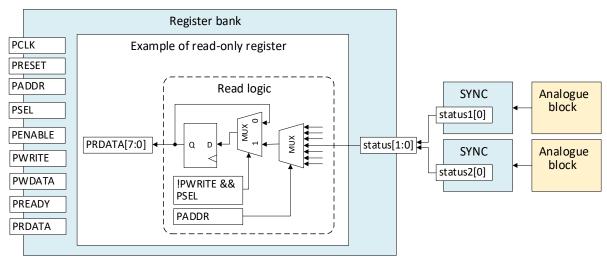

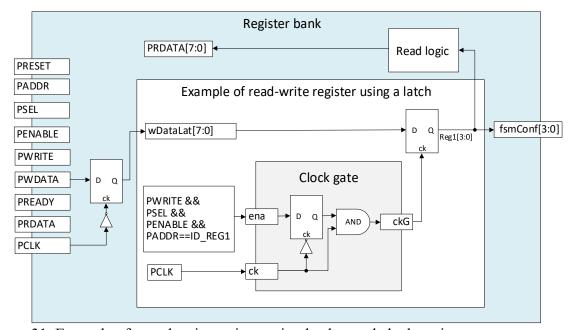

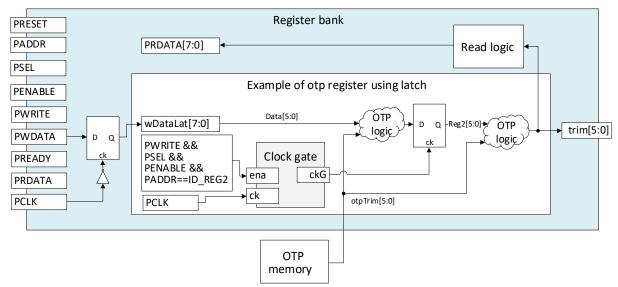

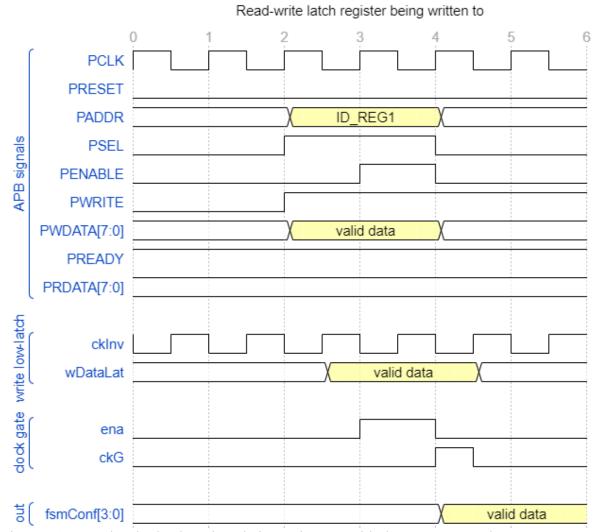

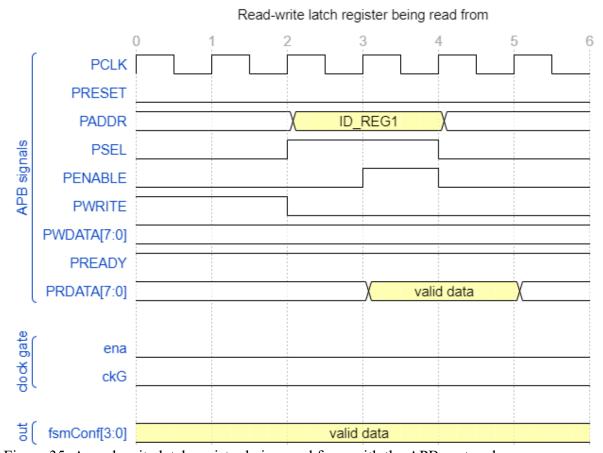

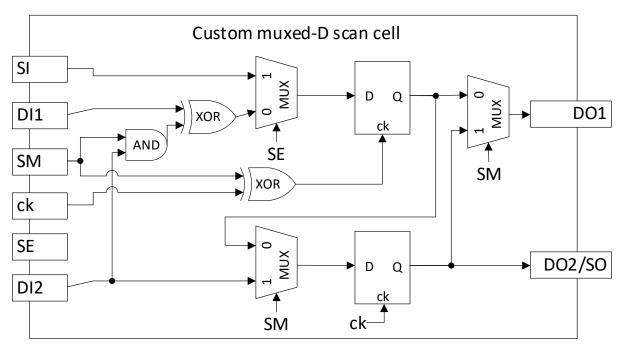

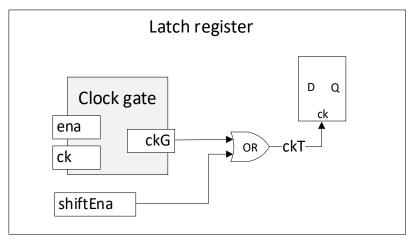

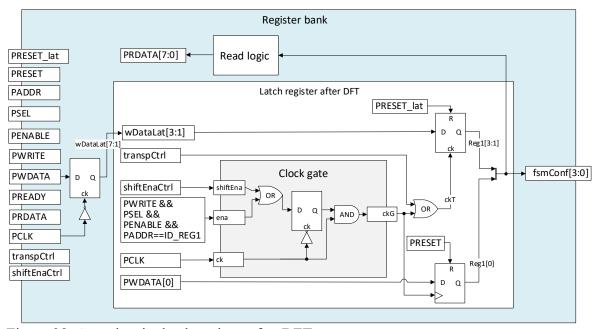

Considering how test patterns are generated in scan designs, generating the test patterns with an ATPG tool comes to mind. Good test patterns can be generated with an ATPG and saved in read only memory (ROM) on the circuit [15]. This method is impractical due to high area overhead of the ROM [15].