Universidade do Minho Escola de Engenharia

Lucas Morais Baptista

# Graphene transistors for radio frequency applications

Dissertação de Mestrado Mestrado Integrado em Engenharia Física Área de Especialização em Dispositivos, Microssistemas e Nanotecnologias

Trabalho efetuado sob a orientação do Professor Doutor Paulo Mateus Mendes e Professor Doutor João Pedro S. H. A. Alpuim

Outubro de 2019

### DECLARAÇÃO

Nome: Endereço eletrónico: Telefone: Bilhete de Identidade/Cartão do Cidadão:

Título da dissertação: Graphene transistors for radio frequency applications.

Orientador/a/es: Professor Doutor Paulo Mateus Mendes Professor Doutor João Pedro S. H. A. Alpuim

Ano de conclusão: 2019 Mestrado Integrado em Engenharia Física

É AUTORIZADA A REPRODUÇÃO INTEGRAL DESTA DISSERTAÇÃO APENAS PARA EFEITOS DE INVESTIGAÇÃO, MEDIANTE DECLARAÇÃO ESCRITA DO INTERESSADO, QUE A TAL SE COMPROMETE.

Universidade do Minho, \_\_\_\_/\_\_\_/

Assinatura:

# Despacho RT - 31 /2019 - Anexo 3 Declaração a incluir na Tese de Doutoramento (ou equivalente) ou no trabalho de Mestrado

### DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Atribuição CC BY https://creativecommons.org/licenses/by/4.0/

Universidade do Minho, \_\_\_\_/\_\_\_\_

Assinatura:

# Despacho RT - 31 /2019 - Anexo 4 Declaração a incluir na Tese de Doutoramento (ou equivalente) ou no trabalho de Mestrado

### STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

Universidade do Minho, \_\_\_\_/\_\_\_/

Assinatura:

# AGRADECIMENTOS

Quero agradecer, em primeiro lugar, aos meus orientadores, Professor Paulo Mendes e Professor Pedro Alpuim, pela oportunidade de trabalho, orientação durante a dissertação e intervenção durante este ano. Para além disso, agradeço também as suas frontalidades e ensinamentos transmitidos ao longo do processo.

Ao projeto de investigação financiado pelos fundos da FCT: PTDC/EEI-TEL/29670/2017 - (POCI-01-0145-FEDER-029670), cofinanciado pelo Fundo Europeu de Desenvolvimento Regional (FEDER) e através de COMPETE 2020.

Agradeço também ao Jerome, Fátima, Chun-Da e Nan Zhang pela ajuda prestada ao longo da dissertação nas áreas de fabrico, caracterização de grafeno, crescimento e transferência de grafeno e síntese dos nano-fios, respetivamente. Pelas suas disponibilidades e ensinamentos transmitidos nas suas respetivas áreas ao qual foram essenciais para o trabalho da dissertação.

Aos meus pais pelo apoio e carinho demonstrados, não só durante a dissertação, mas também ao longo dos anos. Sem eles não seria possível alcançar este objetivo na minha vida.

Aos meus amigos e colegas de laboratório ao qual mantiveram o excelente ambiente de trabalho, as discussões e ajuda nas tarefas.

A todos um especial obrigado por estarem presentes e pelo apoio oferecido.

### **RESUMO**

O grafeno atraiu imensa atenção devido à alta mobilidade dos portadores de carga, tornando um potencial novo material para eletrónica de radio frequência. Transístores fabricados com grafeno, fabricados até à data, possuem frequência de corte intrínsecas de 427 GHz. O fabrico de transístores de grafeno para aplicações de radiofrequência é dificultado devido às tecnologias de fabrico CMOS não poderem ser usadas, no seu estado atual, para este novo material. Neste trabalho, uma deposição física da porta e do óxido da porta foi escolhida de forma a minimizar os danos causados à rede de grafeno e um processo de auto alinhamento para reduzir as resistências de contacto.

De forma a maximizar as figuras de mérito das estruturas pretendidas, foram feitas simulações que correlacionam os parâmetros físicos do dispositivo com as figuras de mérito. Os resultados obtidos dessas simulações mostraram que a elevada discrepância entre as figuras de mérito intrínsecas e extrínsecas resultam do elevado rácio entre as capacitâncias da portadreno e porta-fonte para as capacitâncias parasíticas da porta e do dreno. Um aumento da camada de passivação e redução dos pads resultam na redução significativa do rácio entre os dois. As simulações também mostraram que reduzindo as resistências, capacidades e indutâncias parasitas resulta numa melhoria das figuras de mérito. A redução da largura do canal e aumento do comprimento do canal resulta no aumento das figuras de mérito intrínsecas e consequentemente as extrínsecas.

O grafeno foi crescido por CVD numa folha de cobre, que produz alta qualidade e grandes áreas, e transferido para um substrato isolador. Nano-fios de níquel foram crescidos por deposição eletroquímica usando estruturas de oxido de alumínio anodizado (AAO) com uma camada de semente fina de ouro e uma mistura de NiSO<sub>4</sub>, NiCl<sub>2</sub> e H<sub>3</sub>BO<sub>3</sub>, produziram nano-fios com diâmetros entre 200 e 400 nm. A estrutura foi removida com uma solução de NaOH, expondo os nano-fios.

A cobertura dos nano-fios foi realizada através da oxidação do níquel e deposição de dióxido de silício. Ambas estas estruturas de núcleo-concha foram utilizadas na fabricação dos transístores.

Os nano-fios núcleo-concha foram libertados da camada semente com uma solução de KI e I<sub>2</sub>, e subsequentemente aleatoriamente posicionados em cima do grafeno. Imagens de alta resolução foram obtidas da exata posição dos nano-fios e com a ajuda de marcadores de TitânioTungstênio (TiW), previamente depositados, mascaras para os processos litográficos foram desenhadas, estabelecendo um comprimento do canal em 3 µm. O processo de auto alinhamento foi por fim usado para depositar os contactos do dreno e fonte (Cr/Pd), alinhando-os perfeitamente e reduzindo a resistência de contacto por consequência.

Um processo dieletroforético foi também desenvolvido para posicionar precisamente os nano-fios no substrato e possibilitar a escalabilidade do processo de fabrico.

Por último, caracterização dos dispositivos fabricados foi realizada. Os dispositivos fabricados na primeira iteração mostraram baixo isolamento entre a porta e o canal, sendo esta atribuída ao dielétrico escolhido. Os dispositivos da segunda iteração do processo de fabrico foram impossíveis de caracterizar eletricamente devido à falta de conexão elétrica após a primeira ligação das sondas de medição.

Palavras-chave: grafeno, transistor de efeito de campo, nanofio, fabricação

### ABSTRACT

Graphene has attracted an immense amount of attention due to its high carrier mobility, making it a potentially new material for radio-frequency electronics. Transistors fabricated with graphene have reached intrinsic cut-off frequencies of 300 GHz. The fabrication of graphene RF transistors is challenging as most of the standard CMOS technologies cannot be employed in their current state to this new material. In this work, a physical deposition of the gate and gate oxide was chosen to minimize the damages to the graphene lattice and a self-aligned process to reduce the contact resistance.

In order to maximize the figures of merit of the intended structure, simulations were made correlating the physical parameters to the figures of merit. Results obtained from these simulations showed that the high discrepancy between intrinsic and extrinsic figures of merit resulted from the high ratio between the gate-drain and gate-source capacitances to the parasitic gate and drain parasitic capacitances. An increase in the passivation layer and reduction of the gate and drain pads results in a significantly lower ratio between the two. Simulations also showed that, by minimizing the parasitic resistances, capacitances and inductances results in the increase of both intrinsic and extrinsic figures of merit. Reduction of the channel length and increase of the channel width results in the increase of the intrinsic, and subsequently extrinsic, figures of merit.

Graphene was grown by CVD on a copper foil, which yielded high quality and large area graphene, and transferred onto the insulating substrate. Nickel nanowires were grown by electrochemical deposition using an Anodized Aluminum Oxide (AAO) template with a gold seed layer and a mixture of NiSO<sub>4</sub>, NiCl<sub>2</sub> and H<sub>3</sub>BO<sub>3</sub>, resulting in nanowires with diameters ranging from 200 to 400 nanometers. The template was removed with a solution of NaOH creating free standing nanowires. Coating of the nanowires was performed through the oxidation of nickel and deposition of silicon dioxide. Both of these types of core-shell nanowires were used in the fabrication of the transistors.

The core-shell nanowires were released from the seed layer with a solution of KI and  $I_2$ and subsequently randomly placed on top of the graphene. High resolution images of the nanowires precise position were taken and with the aid of Titanium-Tungsten (TiW) markers previously deposited, masks for a lithographic process were designed, setting the channel width to 3  $\mu$ m. A self-aligned process was lastly employed to deposit the Drain-Source contacts (Cr/Pd), perfectly aligning them and in turn, greatly reducing the access resistance.

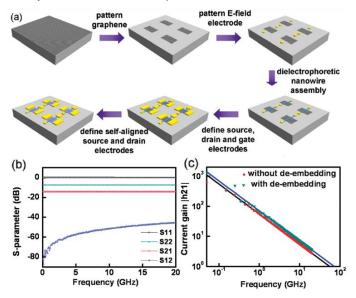

A dielectrophoretic method was also developed to perfectly position the nanowires on the substrate and in turn scale up the device fabrication process.

Lastly, characterization of the fabrication took place. Devices fabricated on the first run of the experiment showed poor isolation between the gate and channel of the devices. This was attributed to the dielectric choice. The second set of fabricated devices were unable to be characterized as connections made onto the devices failed to provide electrical contact after the first placement of the measuring probes.

Keywords: graphene, field-effect transistor, nanowire, fabrication

# TABLE OF CONTENTS

| Agradecimentosiii                                       |  |  |

|---------------------------------------------------------|--|--|

| Resumo                                                  |  |  |

| Abstractvi                                              |  |  |

| Table of Contents   ix                                  |  |  |

| ist of Figuresxii                                       |  |  |

| ist of Tablesxx                                         |  |  |

| ist of Abbreviations and Acronymsxxii                   |  |  |

| Introduction                                            |  |  |

| 1.1 Graphene technology                                 |  |  |

| 1.2 Graphene based radiofrequency devices               |  |  |

| 1.3 Work Motivation                                     |  |  |

| 1.4 Contributions                                       |  |  |

| 1.5 Thesis organization                                 |  |  |

| 2 Graphene based RF devices                             |  |  |

| 2.1 Graphene                                            |  |  |

| 2.1.1 What is graphene?                                 |  |  |

| 2.1.2 Graphene properties and characterization          |  |  |

| 2.1.3 Graphene applications                             |  |  |

| 2.2 Graphene-based RF devices                           |  |  |

| 2.2.1 RF devices                                        |  |  |

| 2.2.2 Graphene-based RF transistors                     |  |  |

| 2.2.3 Figures of merit of graphene-based RF transistors |  |  |

| 2.2.4 Fabrication constraints                           |  |  |

| 2.3 Graphene Synthesis                                  |  |  |

| 2.3.1 Mechanical exfoliation                            |  |  |

| 2.3.2 Thermal decomposition (SiC)                       |  |  |

| 2.3.3 Thermal Chemical Vapor Deposition                 |  |  |

| 2.4 Graphene Transfer methods                           |  |  |

|        | 2.4.1 | Polymer assisted transfer                                                                                        | 20 |

|--------|-------|------------------------------------------------------------------------------------------------------------------|----|

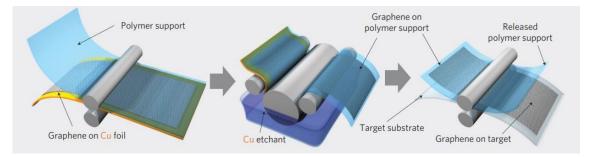

|        | 2.4.2 | Roll-to-roll transfer                                                                                            | 21 |

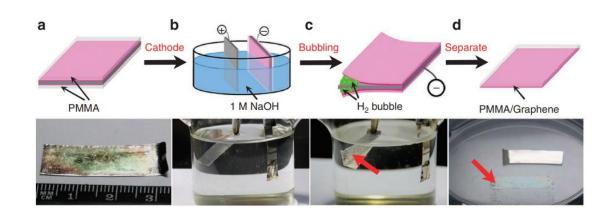

|        | 2.4.3 | Bubbling method                                                                                                  | 21 |

|        | 2.5   | Direct deposition of the gate dielectric onto graphene                                                           | 22 |

|        | 2.5.1 | Physical vapor deposition                                                                                        | 22 |

|        | 2.5.2 | Atomic layer deposition                                                                                          | 23 |

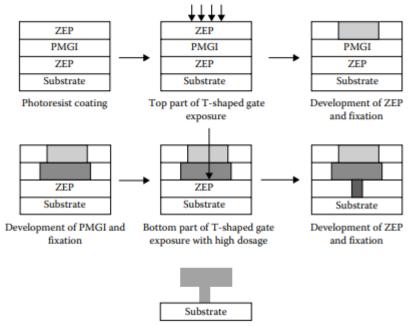

|        | 2.5.3 | T-shaped gate                                                                                                    | 29 |

| 2.6 Ph |       | Physical assembly of nanostructures                                                                              | 31 |

|        | 2.6.1 | Graphene transistor with a self-aligned core-shell nanowire gate                                                 | 32 |

|        | 2.6.2 | Graphene transistors with triangular shaped GaN nanowires                                                        | 35 |

|        | 2.6.3 | Graphene transistors with transferred gate stacks                                                                | 36 |

|        | 2.7   | CMOS back-end-of-the-line approach                                                                               | 37 |

| 3      | Devic | e design and modelling                                                                                           | 43 |

|        | 3.1   | Introduction                                                                                                     | 43 |

|        | 3.2   | Fransistor proposal                                                                                              | 44 |

|        | 3.3   | Fransistor Modelling                                                                                             | 46 |

|        | 3.3.1 | Proposed model                                                                                                   | 46 |

|        | 3.3.2 | Drain current                                                                                                    | 47 |

|        | 3.3.3 | Transconductance                                                                                                 | 49 |

|        | 3.3.4 | Resistances                                                                                                      | 51 |

|        | 3.3.5 | Capacitances                                                                                                     | 51 |

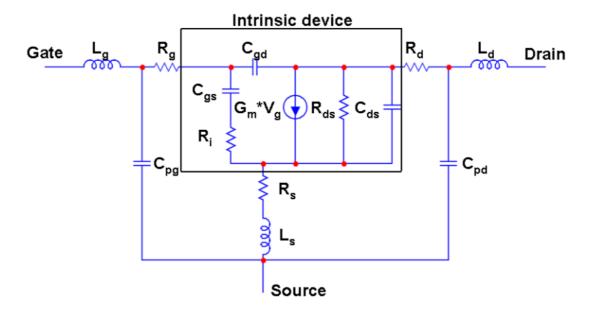

|        | 3.3.6 | Remaining components of the circuit ( <i>Rg</i> , <i>Lg</i> , <i>RD</i> , <i>LD</i> , <i>RS</i> and <i>LS</i> ): | 55 |

| 3.4 Po |       | Performance assessment                                                                                           | 56 |

|        | 3.4.1 | Polarization                                                                                                     | 57 |

|        | 3.4.2 | Figures of Merit                                                                                                 | 58 |

|        | 3.5   | Parametric Analysis                                                                                              | 59 |

|        | 3.5.1 | Channel width (W)                                                                                                | 59 |

|        | 3.5.2 | Channel length (L)                                                                                               | 60 |

|        | 3.5.3 | Gate dielectric thickness ( <i>tox</i> ):                                                                        | 60 |

|   | 3.5.4                                                                                                  | RF pad length (LPad)                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                         |

|---|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 3.5.5                                                                                                  | Thickness of the passivation layer ( <i>tpass</i> )                                                                                                                                                                                                                                                                                                                                                                 | 62                                                                         |

|   | 3.5.6                                                                                                  | Device example                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                         |

|   | 3.6                                                                                                    | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                         |

| 4 | Nano                                                                                                   | owire Synthesis                                                                                                                                                                                                                                                                                                                                                                                                     | 65                                                                         |

|   | 4.1                                                                                                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                                         |

|   | 4.2                                                                                                    | Electrochemical deposition set-up                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                         |

|   | 4.3                                                                                                    | Nickel seed layer                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                                         |

|   | 4.3.1                                                                                                  | Seed Layer deposition                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                         |

|   | 4.3.2                                                                                                  | 2 Template removal                                                                                                                                                                                                                                                                                                                                                                                                  | 70                                                                         |

|   | 4.3.3                                                                                                  | Release attempt: Grind Method                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                         |

|   | 4.4                                                                                                    | Palladium seed layer                                                                                                                                                                                                                                                                                                                                                                                                | 72                                                                         |

|   | 4.5                                                                                                    | Gold seed layer                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                         |

|   | 4.5.1                                                                                                  | Release attempt through sonication bath                                                                                                                                                                                                                                                                                                                                                                             | 73                                                                         |

|   | 4.5.2                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|   | 4.3.2                                                                                                  | Release allempt. Seed layer etch first                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                         |

|   | 4.5.2                                                                                                  | 1 5                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|   |                                                                                                        | 1 5                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                                                                         |

|   | 4.5.3                                                                                                  | Releases attempt: Dissolution of the AAO template first                                                                                                                                                                                                                                                                                                                                                             | 77<br>78                                                                   |

|   | 4.5.3<br>4.6<br>4.7                                                                                    | Releases attempt: Dissolution of the AAO template first                                                                                                                                                                                                                                                                                                                                                             | 77<br>78<br>79                                                             |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap                                                                            | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion                                                                                                                                                                                                                                                                                                                     | 77<br>78<br>79<br>81                                                       |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap                                                                            | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>bhene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .                                                                                                                                                                                                                                | 77<br>78<br>79<br>81<br>81                                                 |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap<br>5.1                                                                     | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>bhene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction                                                                                                                                                                                                                | 77<br>78<br>79<br>81<br>81<br>81                                           |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap<br>5.1<br>5.2                                                              | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>whene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication                                                                                                                                                                           | 77<br>78<br>79<br>81<br>81<br>81<br>83                                     |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap<br>5.1<br>5.2<br>5.3                                                       | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>whene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer                                                                                                                                                      | 77<br>78<br>79<br>81<br>81<br>81<br>83<br>83                               |

| 5 | 4.5.3<br>4.6<br>4.7<br>5.1<br>5.2<br>5.3<br>5.3.1                                                      | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>ohene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer<br>Matrix of optical markers                                                                                                                         | 77<br>78<br>79<br>81<br>81<br>81<br>83<br>83<br>83                         |

| 5 | 4.5.3<br>4.6<br>4.7<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2                                             | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>chene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer<br>Matrix of optical markers<br>Graphene growth and transfer                                                                                         | 77<br>78<br>79<br>81<br>81<br>81<br>83<br>83<br>83<br>85                   |

| 5 | 4.5.3<br>4.6<br>4.7<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3                                    | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>conclusion<br>hene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer<br>Matrix of optical markers<br>Graphene growth and transfer<br>Core-shell nickel/nickel oxide nanowire transfer                        | 77<br>78<br>79<br>81<br>81<br>81<br>83<br>83<br>83<br>85<br>87             |

| 5 | 4.5.3<br>4.6<br>4.7<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.2<br>5.3.3<br>5.3.4                  | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>conclusion<br>phene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer<br>Matrix of optical markers<br>Graphene growth and transfer<br>Core-shell nickel/nickel oxide nanowire transfer<br>Channel Patterning | 77<br>78<br>79<br>81<br>81<br>81<br>83<br>83<br>83<br>83<br>85<br>87<br>88 |

| 5 | 4.5.3<br>4.6<br>4.7<br>Grap<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5 | Releases attempt: Dissolution of the AAO template first<br>Results and Discussion<br>Conclusion<br>conclusion<br>hene Field-effect Transistor with Nickel/Nickel Oxide core-shell nanowire gate .<br>Introduction<br>Nickel oxide shell<br>Fabrication<br>Passivation layer<br>Matrix of optical markers<br>Graphene growth and transfer<br>Core-shell nickel/nickel oxide nanowire transfer<br>Channel Patterning  | 77<br>78<br>79<br>81<br>81<br>83<br>83<br>83<br>83<br>85<br>87<br>88<br>89 |

| 6                         | Graphene Field-effect Transistor with Nickel/Silicon Dioxide core-shell nanowire gate 95 |                                                       |     |

|---------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|

| 6.1 Introduction          |                                                                                          |                                                       | 95  |

| 6.2 Silicon dioxide shell |                                                                                          | 95                                                    |     |

| 6.3 Fabrication           |                                                                                          | 97                                                    |     |

|                           | 6.3.1                                                                                    | 1 Passivation layer                                   | 97  |

|                           | 6.3.2                                                                                    | 2 Matrix of optical markers                           | 97  |

|                           | 6.3.3                                                                                    | 3 Graphene growth and transfer                        | 99  |

|                           | 6.3.4                                                                                    | 4 Core-shell nickel/silicon dioxide nanowire transfer | 99  |

|                           | 6.3.5                                                                                    | 5 Channel Patterning                                  |     |

|                           | 6.3.6                                                                                    | 6 Self-aligned source-drain metal contacts            |     |

|                           | 6.3.7                                                                                    | 7 Core connecting contact                             | 106 |

| l                         | 6.4                                                                                      | Characterization                                      | 107 |

| (                         | 6.5                                                                                      | Conclusions                                           | 107 |

| 7                         | Conc                                                                                     | clusions and future work                              | 109 |

| ,                         | 7.1                                                                                      | Conclusions                                           | 109 |

| ,                         | 7.2                                                                                      | Future Work                                           | 110 |

| Re                        | ference                                                                                  | es                                                    |     |

# LIST OF FIGURES

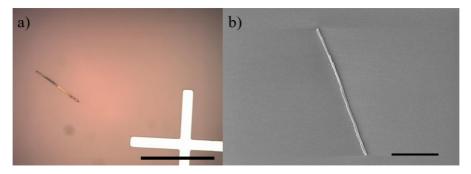

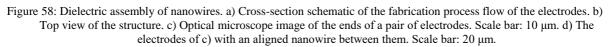

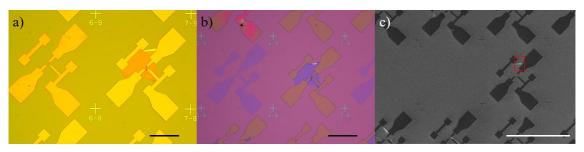

| Figure 1: Optical and corresponding SEM images of the nanowires released from the seed layer.     |  |  |

|---------------------------------------------------------------------------------------------------|--|--|

| a) Scale bar: 90 μm. b) Scale bar: 10 μm                                                          |  |  |

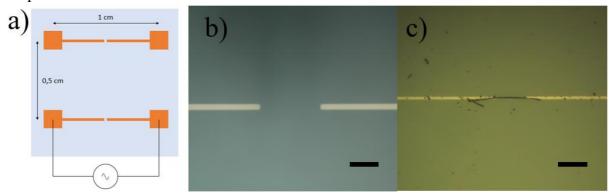

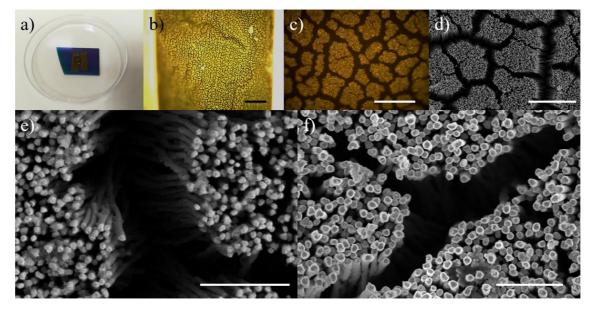

| Figure 2: Dielectric assembly of nanowires. a) Top view schematic of the structure. b) Optical    |  |  |

| microscope image of the ends of a pair of electrodes. Scale bar: 10 $\mu$ m. c) Optical           |  |  |

| microscope images of the electrodes of b) with an aligned nanowire between them. Scale            |  |  |

| bar: 20 μm                                                                                        |  |  |

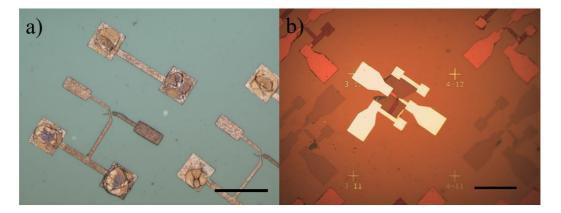

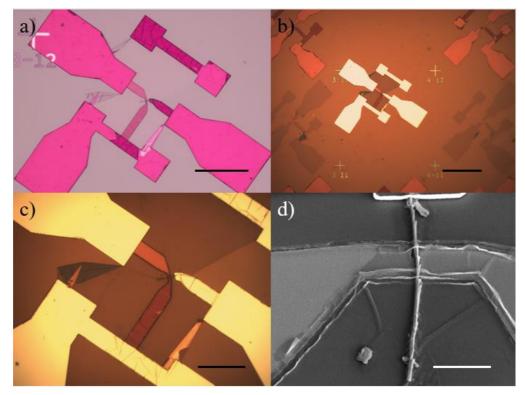

| Figure 3: Resulting transistors of both the fabrication processes. a) Optical image of a graphene |  |  |

| field-effect transistor with nickel/nickel oxide core-shell nanowire gate. Scale bar: 100         |  |  |

| μm. b) Optical image of a graphene field-effect transistor with nickel/silicon dioxide core-      |  |  |

| shell nanowire gate. Scale bar: 200 µm5                                                           |  |  |

| Figure 4: Graphene and its allotropes, fullerenes, carbon nanotubes and graphite, from left to    |  |  |

| right. [7]7                                                                                       |  |  |

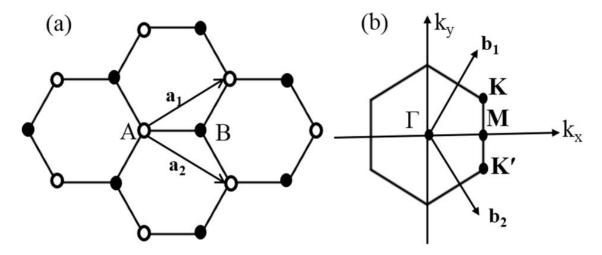

| Figure 5: a) Honeycomb lattice structure of graphene (direct lattice). b) Corresponding Brillouin |  |  |

| zone, showing the high-symmetry points                                                            |  |  |

| Figure 6: Energy bands of graphene obtained from the tight-binding model and zoom around          |  |  |

| the Dirac point at K. Figure retrieved from reference [8]9                                        |  |  |

| Figure 7: Raman spectrum of monolayer graphene with 514.5 nm excitation laser wavelength.         |  |  |

| Figure retrieved from reference [10]10                                                            |  |  |

| Figure 8: Maximum frequency of oscillation fmáx versus cut-off frequency fT of Si RF              |  |  |

| MOSFETs (open circles) and III-V HEMTs (InP HEMTs: full circles, GaAs mHEMTs:                     |  |  |

| half-full circles). The numbers next to the symbols indicate fmáx (first number) and fT           |  |  |

| (second number) in GHz for the best transistors of each type. Figure adapted from                 |  |  |

| reference [18]                                                                                    |  |  |

| Figure 9: Demonstration circuit for a graphene frequency multiplier operating in a gigahertz      |  |  |

| frequency range. Figure retrieved from reference [19]                                             |  |  |

| Figure 10: Graphene-based mixer. a) Circuit diagram of a four-port graphene RF frequency          |  |  |

| mixer. b) Output spectrum of the mixer, between 0 and 10 GHz. Figure adapted from                 |  |  |

| reference [14]14                                                                                  |  |  |

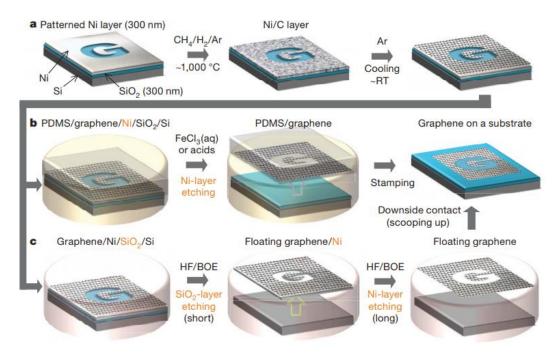

| Figure 11: Synthesis and dry transfer process of a graphene film grown by CVD on top of a Ni      |  |  |

| substrate, a) Synthesis of patterned graphene films on thin nickel layers, b) Etching using       |  |  |

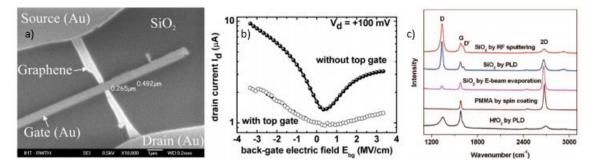

- Figure 14: Field effect device and its I-V curves before and after top gate oxide evaporation. Raman spectroscopy of different types of physical depositions of oxide onto graphene. Figures adapted/ retrieve from references [33] and [34]......23

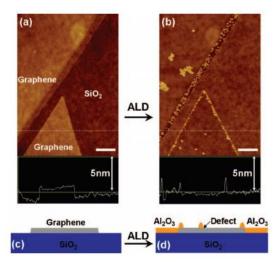

- Figure 15: Experimental results of X. Wang *et al.* a) and b) AFM images of the graphene layer.c) and d) Representations of the AFM images. Figures adapted/retrieved from reference [35].

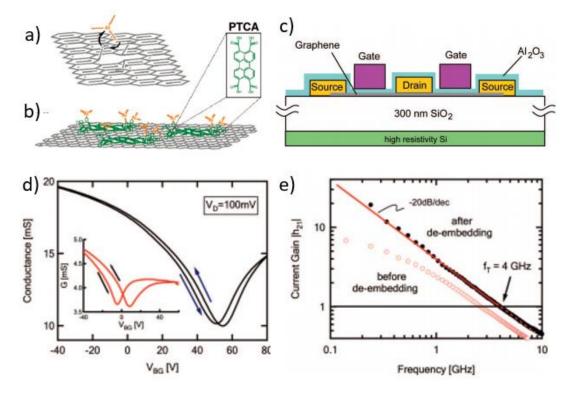

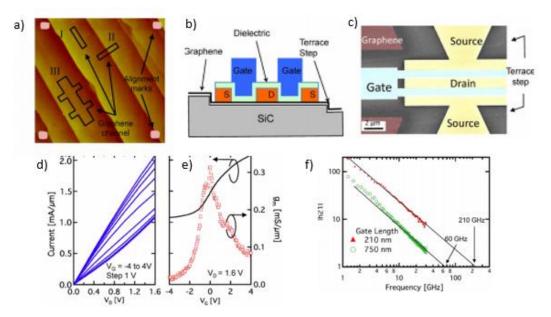

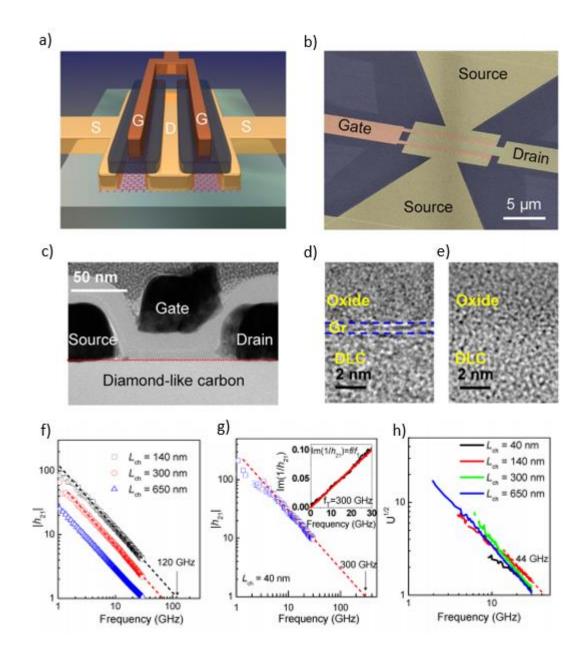

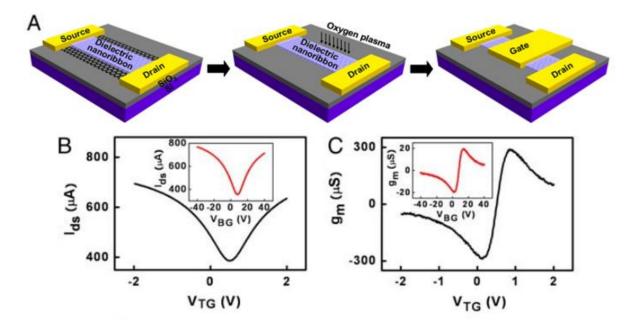

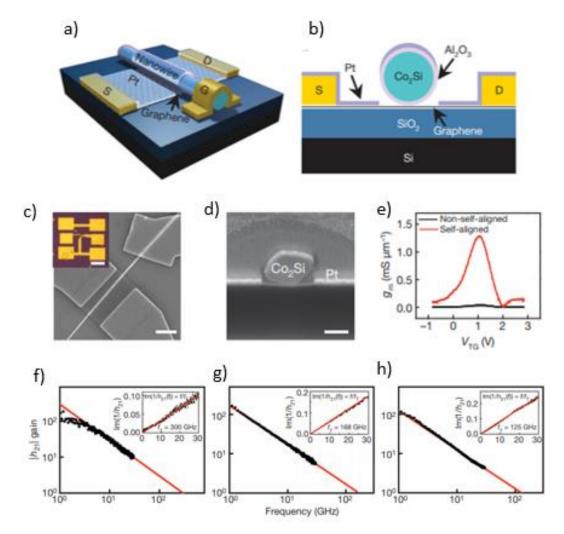

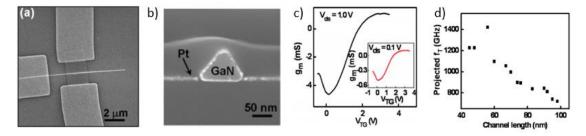

- Figure 23: Graphene transistor with self-aligned core-shell nanowire gate. a) Birds eye view schematic of the device. b) Cross section schematic of the device. c) SEM image of the device. Inset, an optical microscope image of the overall device. e) Transconductance values, before (black) and after (red), the self-aligned process. f), g) and h) Measured small-signal current gain |h21| as a function of frequency for devices with gate length of 144 nm, 182 nm and 210 nm, respectfully. Figures adapted/retrieved from reference [5].

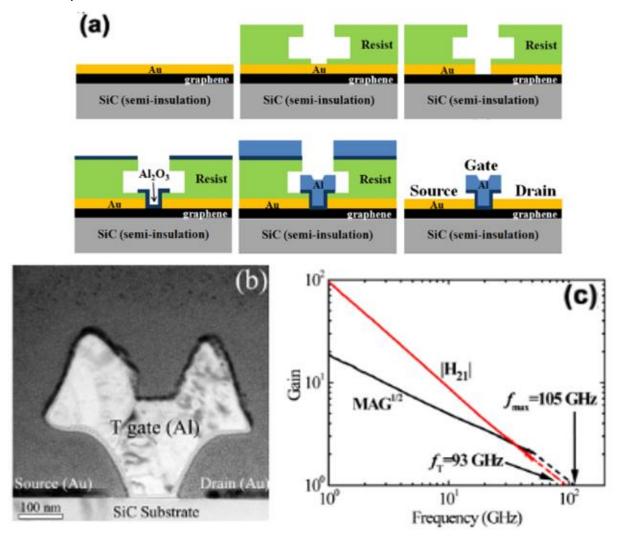

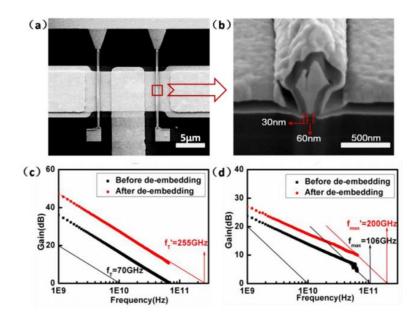

Figure 28: – Buried gate graphene field effect transistor. a) – h) Fabrication schematic of G-FET. i) and j) Cross section SEM images of G-FETs with 200 and 300 nm, respectfully.

k) and l) Measured current gain |h21| of G-FETs i) and j). Figures adapted/retrieved from reference [47].

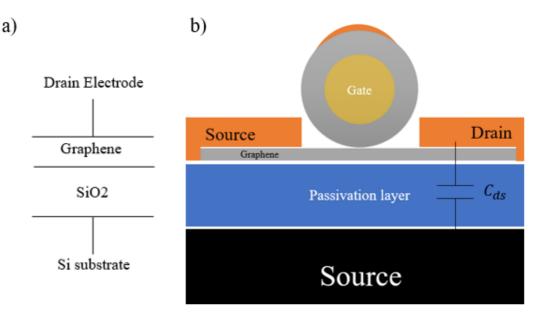

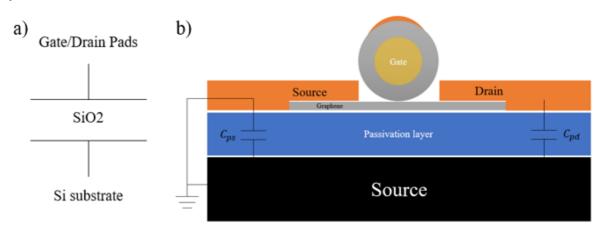

Figure 29: GFET schematic structure a) from top view. b) from cross-section of the channel.

Figure retrieved from reference [50]......47

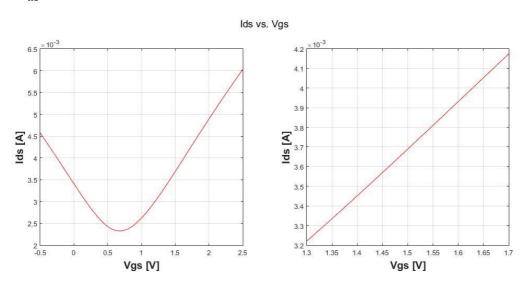

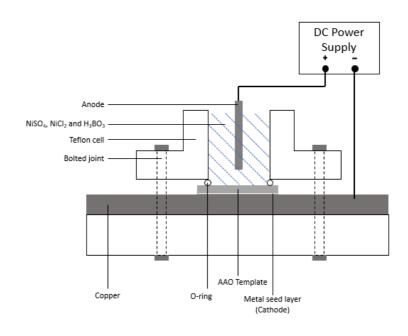

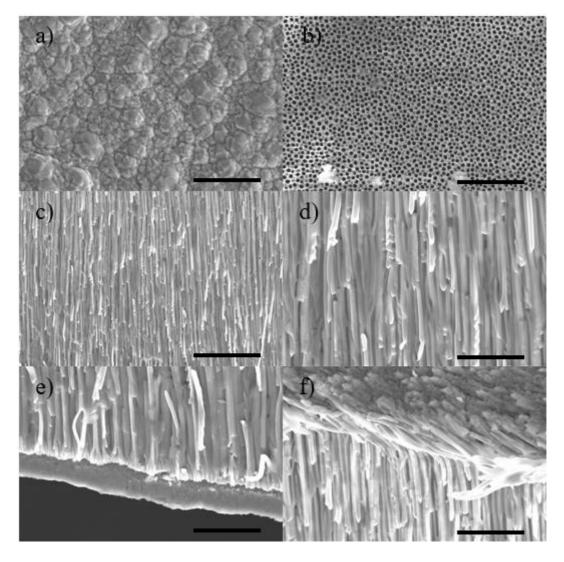

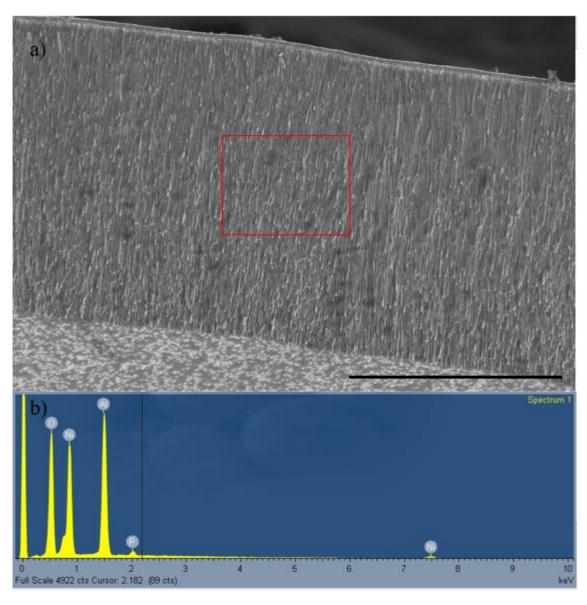

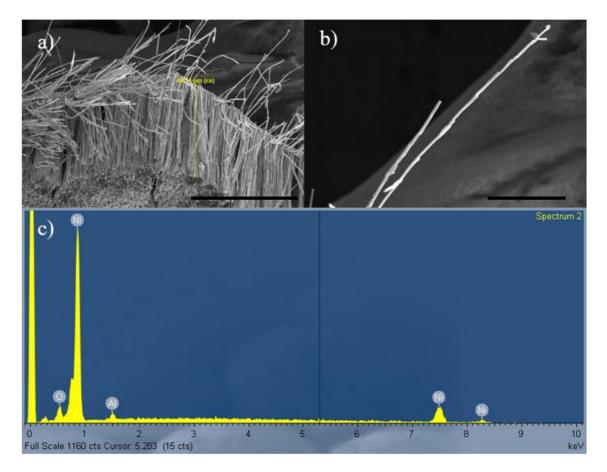

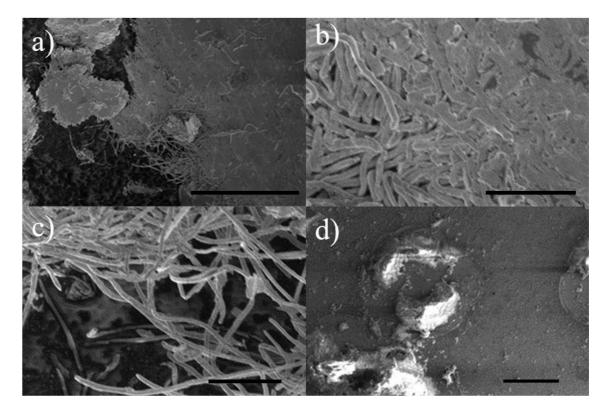

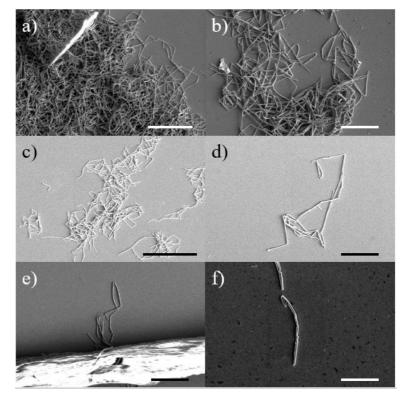

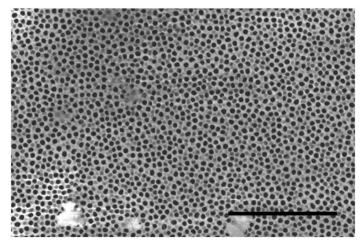

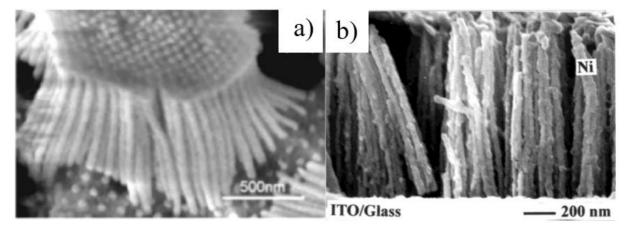

Figure 36: Transfer curve of the modelled GFET with inputted starting parameters and Vds =Figure 37: Detailed schematic of the set-up utilized for the electrochemical deposition of nickel. Figure 38: SEM images of cross and top sections of the AAO template with nickel nanowires grown inside. a) top view of AAO template where the nickel nanowires overgrew the pores. Scale bar: 5 µm. b) top view of AAO template covered by the O-ring during deposition. Scale bar: 5 µm c) middle section of the AAO template. Scale bar: 10 µm. d) close-up image of c). Scale bar: 4 µm. e) cross-section view of the AAO template with the nickel seed layer on the bottom. Scale bar: 4 µm. f) cross-section view of the AAO Figure 39: SEM image and EDX results of the AAO template after deposition. a) cross section of AAO template after deposition. Scale bar: 40 µm. b) EDX results of the red area in a). Figure 40: SEM images and EDX results after the template dissolution. a) cross-section SEM image of the AAO template after dissolution with a measurement from top to bottom of the nanowires which indicates a length of 49 µm. Scale bar: 40 µm. b) close-up SEM image of a single nanowire. Scale bar: 10 µm. c) EDX results of the middle section of the Figure 41:  $1^{st}$  attempt to remove nickel nanowires from nickel seed layer. a) – c) SEM image of the seed layer with the nanowires after mechanical grind. Scale bar: 40 µm,4 µm and 5 µm, respectfully. d) SEM image of the seed layer with the nanowires after 1 hour of ultrasonic bath. Scale bar: 5 µm......72 Figure 42: Palladium seed layer results. a) cross-section view at an unknown angle of the palladium seed layer with the attached wires. Scale bar: 20 µm. b) and c) top view of the palladium seed layer with the nanowires attached. Scale bar: 3 µm and 5 µm, respectfully. d) palladium seed layer with nanowires attached to its back side. Scale bar: 10 µm......73 Figure 43: SEM images showing the results of the ultrasonication bath method. a) and b) 1hour sonication bath. Scale bar: 20 µm and 10 µm, respectfully. c) and d) dilution of a) and b) and 1 more hour of sonication bath. Scale bar: 30 µm and 10 µm, respectfully. f) Dilution of c) and d) and 1 more hour of sonication bath. Scale bar: 10  $\mu$ m and 50  $\mu$ m, respectfully......74

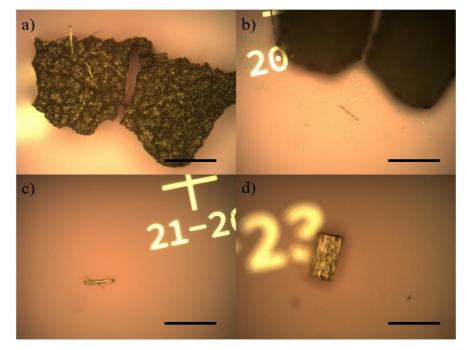

| Figure 44: Optical microscopic images after the etch of gold and subsequent AAO dissolution.       |

|----------------------------------------------------------------------------------------------------|

| a) unetched piece of gold seed layer with clusters of nanowires attached to its surface.           |

| Scale bar: 60 µm. b) different focus of a) showing cluster of nanowires on the substrate           |

| surface. Scale bar: 60 $\mu$ m. c) and d) different sizes of clusters of nanowires deposited on    |

| the surface. Scale bar: 60 $\mu$ m and 30 $\mu$ m, respectfully                                    |

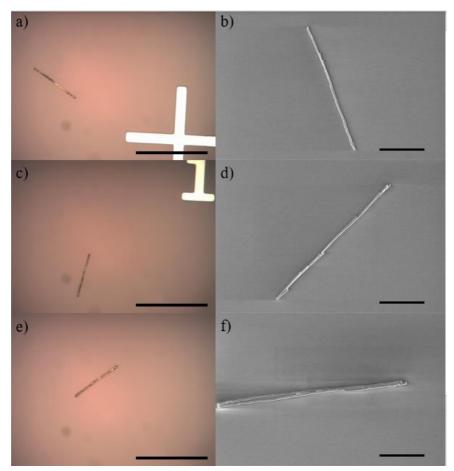

| Figure 45: Optical and corresponding SEM images of 3 random nanowires found in the                 |

| substrate. a), c) and e) Scale bar: 90 $\mu$ m. b), d) and f) Scale bar: 10 $\mu$ m                |

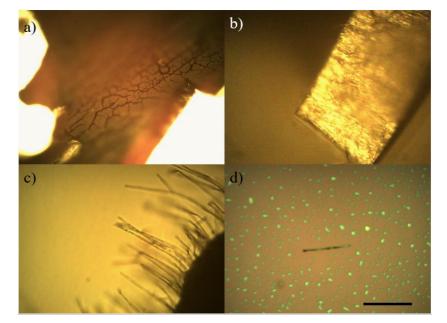

| Figure 46: Optical microscope images of the nanowire oxidation process. a) metal seed layer        |

| with the nanowires after the template dissolution. b) and c) close up images of a). d)             |

| nickel/nickel oxide nanowire after being realised from the seed layer. Scale bar: 30 $\mu$ m.      |

|                                                                                                    |

| Figure 47: SEM image of the templates used. Scale bar: 5 µm                                        |

| Figure 48: Aggregation of nickel nanowires reported in literature. Figures adapted/retrieved       |

| from references [58] and [59], respectfully79                                                      |

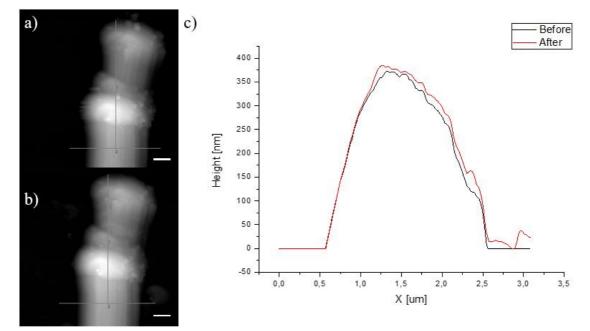

| Figure 49: Nickel oxide thickness characterization. a) AFM image before oxidation. Scale bar:      |

| 0,5 µm. b) AFM image after oxidation. Scale bar: 0,5 µm. c) Comparison of the AFM                  |

| results before and after oxidation                                                                 |

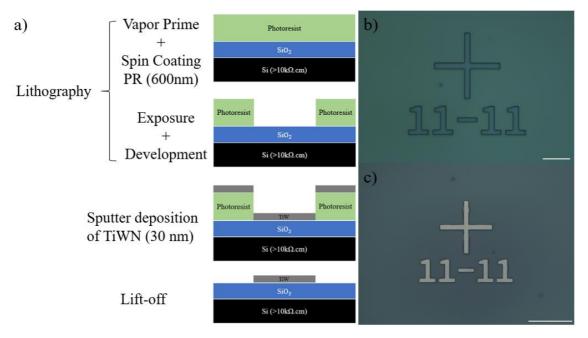

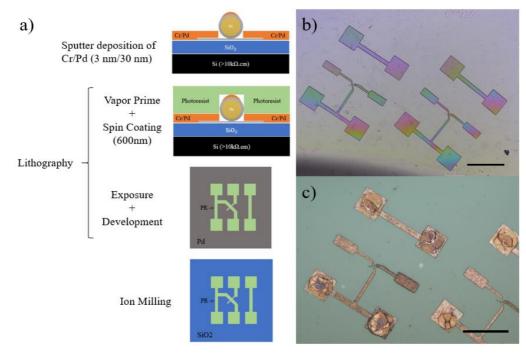

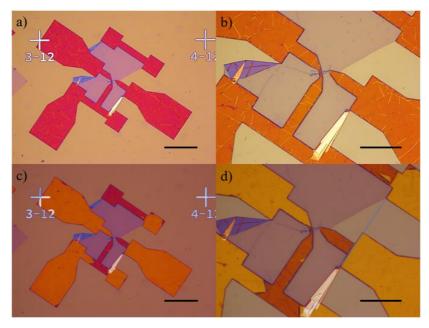

| Figure 50: Optical markers matrix patterning. a) Cross-section schematic of the fabrication        |

| process flow. b) Optical image of the middle marker after development. Scale bar: 25 $\mu$ m.      |

| c) Optical image of the middle marker after lift-off. Scale bar: 50 µm                             |

| Figure 51: Optical images of the substrate after the graphene transfer. a) Top view of the overall |

| substrate. b) and c) optical microscope images of two random areas of the substrate86              |

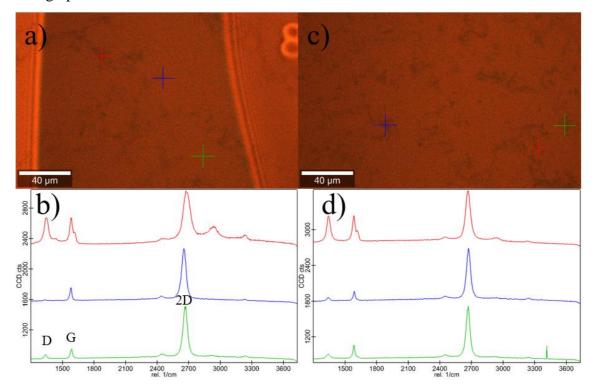

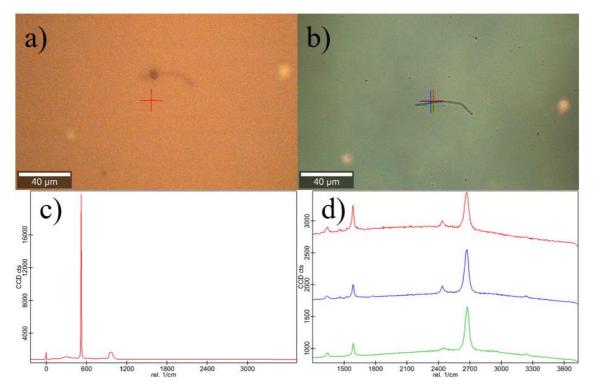

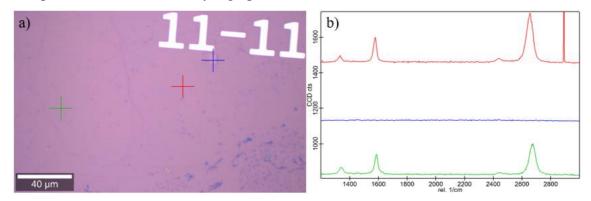

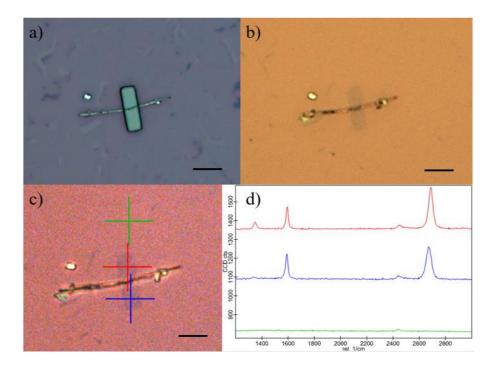

| Figure 52: Raman characterization of the transferred graphene. a) and c) analysed sites. Scale     |

| bar: 40 µm. b) and d) corresponding Raman spectrums of a) and c), respectfully                     |

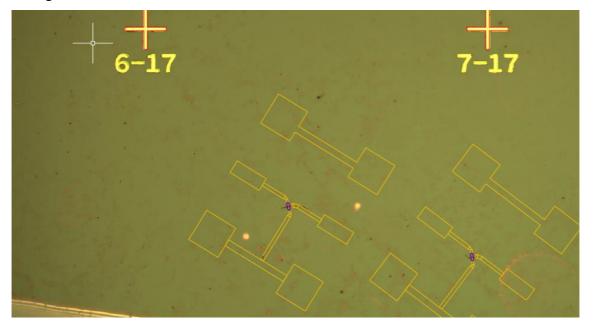

| Figure 53: AutoCAD drawings with the overlaid image of the substrate containing the                |

| nanowires                                                                                          |

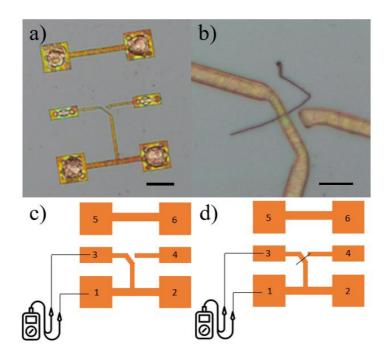

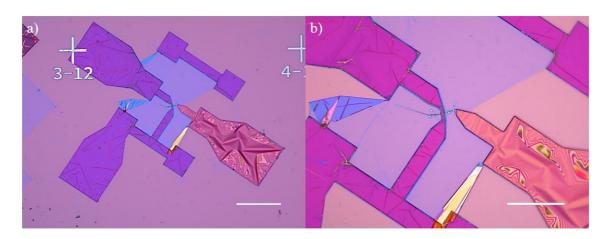

| Figure 54: Channel patterning of the devices. a) Cross-section schematic of the process. b)        |

| Optical microscope image of device 6-16. Scale bar: 10 µm. c) Example of a misaligned              |

| lithography. Scale bar: 24 μm                                                                      |

| Figure 55: Raman characterization a) after oxygen plasma with corresponding spectrum (c) and       |

| b) after acetone bath with corresponding spectrum (d)                                              |

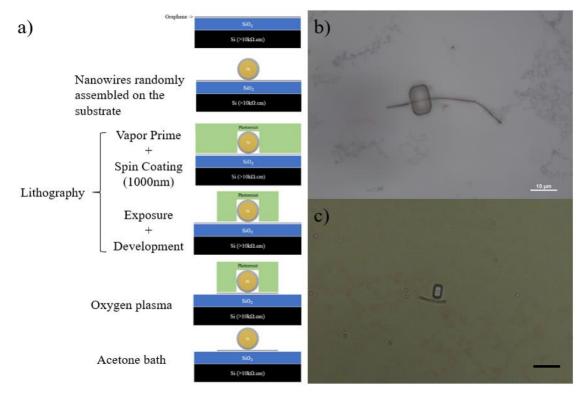

| Figure 56: Self-aligned source drain metal contacts. a) Cross-section/top view schematic of the    |

| metal patterning. b) Optical microscope image of the device 6-16 after the development             |

|                                                                                                    |

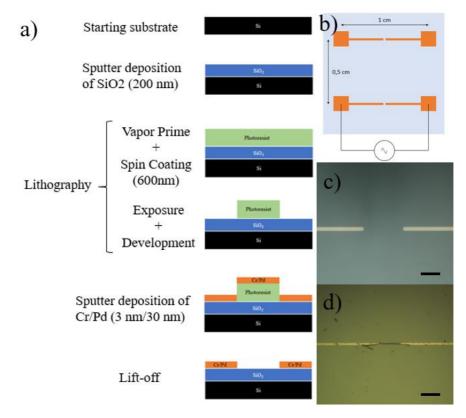

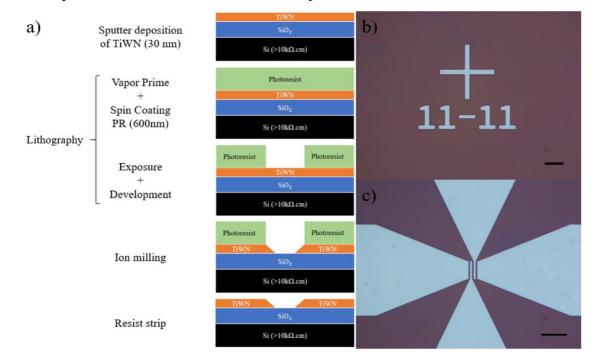

- Figure 59: Dielectric deposition of SiO<sub>2</sub> onto nanowires still attached to the seed layer. a) Optical image of the seed layer duck taped to an SiO<sub>2</sub> substrate before deposition. b) and c) Close-up optical microscope image of a). Scale bar: 120  $\mu$ m and 30  $\mu$ m, respectfully. d) and e) SEM images of the nanowires before SiO<sub>2</sub> deposition. Scale bar: 20  $\mu$ m and 4  $\mu$ m, respectfully. f) SEM image of the nanowires after SiO<sub>2</sub> deposition. Scale bar: 3  $\mu$ m. .... 96

- Figure 60: Patterning of the matrix of optical markers. a) Cross-section schematic of the fabrication process flow. b) Centre optical marker after the resist strip process. Scale bar: 20 μm. c) Graphene resistance measurement device after the process of resist strip. Scale bar: 30 μm.

# LIST OF TABLES

| Table 1: Graphene-based field-effect transistors for radio-frequency applications demonstrated |  |  |

|------------------------------------------------------------------------------------------------|--|--|

| in literature                                                                                  |  |  |

| Table 2: Constant parameters required by the current and transconductance model50              |  |  |

| Table 3: Physical parameters under study with starting values.    57                           |  |  |

| Table 4: Corresponding circuit component values and subsequent figures of merit for the        |  |  |

| starting parameters                                                                            |  |  |

| Table 5: Corresponding circuit component values and subsequent figures of merit for different  |  |  |

| values of channel width59                                                                      |  |  |

| Table 6: Corresponding circuit component values and subsequent figures of merit for different  |  |  |

| values of channel length60                                                                     |  |  |

| Table 7: Corresponding circuit component values and subsequent figures of merit for different  |  |  |

| values of dielectric thickness                                                                 |  |  |

| Table 8: Corresponding circuit component values and subsequent figures of merit for different  |  |  |

| values of pad length61                                                                         |  |  |

| Table 9: Corresponding circuit component values and subsequent figures of merit for different  |  |  |

| values of passivation layer thickness                                                          |  |  |

| Table 10: Corresponding circuit component values and subsequent figures of merit for the best  |  |  |

| values obtained in the simulations prior63                                                     |  |  |

| Table 11: Corresponding circuit component values and subsequent figures of merit for a         |  |  |

| different device example63                                                                     |  |  |

| Table 12: Growth conditions for the nickel seed layers                                         |  |  |

# LIST OF ABBREVIATIONS AND ACRONYMS

| AC    | Alternating Current                       |

|-------|-------------------------------------------|

| AAO   | Anodized Aluminum Oxide                   |

| AFM   | Atomic Force Microscopy                   |

| ALD   | Atomic Layer Deposition                   |

| СМР   | Chemical Mechanical Planarization         |

| CVD   | Chemical Vapor Deposition                 |

| CMOS  | Complementary Metal Oxide Semiconductor   |

| DLC   | Diamond Like Carbon                       |

| DI    | Deionized                                 |

| DC    | Direct Current                            |

| EDX   | Energy Dispersive X-ray                   |

| FET   | Field Effect Transistor                   |

| FIB   | Focused Ion Beam                          |

| GFET  | Graphene Field Effect Transistor          |

| HEMT  | High Electron Mobility Transistor         |

| HOPG  | Highly Oriented Pyrolytic Graphite        |

| INL   | Iberian Nanotechnology Laboratory         |

| ICP   | Inductively Coupled Plasma                |

| IBM   | International Business Machines           |

| IPA   | Isopropyl Alcohol                         |

| LO    | Local Oscillator                          |

| LNA   | Low Noise Amplifier                       |

| MAG   | Maximum Available Gain                    |

| MEMS  | Micro Electro Mechanical Systems          |

| MMIC  | Monolithic Microwave Integrated Circuit   |

| РТСА  | Perylene Tetra Carboxylic Acid            |

| PECVD | Plasma Enhanced Chemical Vapor Deposition |

| PLD   | Physical Layer Deposition                 |

| PVD   | Physical Vapor Deposition                 |

| PDMS  | PolyDiMethylSiloxane                      |

| I     |                                           |

| PMGI | PolyMethylGlutarimide            |

|------|----------------------------------|

| PMMA | PolyMethyl MethAcrylate          |

| RF   | Radio Frequency                  |

| RIE  | Reactive Ion Etching             |

| SEM  | Scanning Electron Microscope     |

| TEM  | Transmission Electron Microscope |

| TMA  | TriMethylAluminum                |

|      |                                  |

### **1 INTRODUCTION**

Throughout the past decades there have been immense advances in the field of electronics which affect our daily lives. These advances can be attributed to the miniaturization of electronic devices, in particular the silicon-based transistors. The number of transistors per chip has been increasing exponentially, reaching the billion mark which in turn means that the physical structure has reached the scale of nanometres. Such advances will eventually come to a halt imposed by the physical limits and to ensure a continued progress of electronic technology, alternative materials or different operating principles are needed.

#### **1.1 Graphene technology**

Graphene was first isolated in 2004 by Geim and Novolesov in 2004 [1]. It has attracted a lot of attention due to its outstanding properties and can be considered as complement to or extension of the existing silicon-based electronics.

Despite the dominant position of silicon, the interest and investment in the research of alternative materials and technologies has been steadily increasing. Device miniaturization has been the enabler of the continuous technological progress we have grown accustomed to and followed the Moore's law. Gordon Moore stated that the size of transistors would decrease and its number on a chip would double every 18 months. This trend followed ever since and today transistors per chip have reached the billion mark. However, miniaturization of devices has reached its limit and technological progress will eventually come to a halt.

To replace the silicon technology, the new materials or processes, have to excel when compared to the dominant technology. Even with superior performance and comparable price alone will not guarantee the adoption of the new technology due to the large investment in CMOS technology. III-V semiconductors are a good example, as they excel in terms of electron mobility, but due to their high cost, they have not made it to mass manufactured consumer electronic devices.

Graphene is a zero-gap semiconductor (i.e., semi-metal) and for this reason, graphene-based field-effect transistors cannot be turned-off. This invalidates graphene to be used as silicon is

today in CMOS logic circuits. On the other hand, the graphene's high carrier mobility, coupled with the large current density of the material, opens up the possibility of RF analogue applications.

Application such as RF communication systems, power control, sensors and actuators include some analogue components or subsystems, where the performance scaling has not been as fast as with digital processing or have not been significantly improved for a while and adoption of new technologies is thus easier. With the shift towards mobile computing, brings interest to different characteristics of materials such as light weight, flexibility and transparency.

#### **1.2 Graphene based radiofrequency devices**

Several devices for radio-frequency applications have been developed throughout the years. These range from passive components, such as capacitors and antennas, to active components, such as field-effect transistors and oscillators.

Graphene antennas were proposed and fabricated in [2]. The radiation efficiency of these antennas is lower, when compared to its metallic counterparts, however the authors claim that graphene-based antennas can be more advantageous due to its wideband properties. The fabricated antennas were measured from 8 to 12 GHz.

CMOS compatible graphene capacitors have been fabricated in [3]. The capacity density obtained was of 2.65 fF/ $\mu$ m<sup>2</sup>, which is 100 times higher than RF MEMS. Through the study of the structure it was seen that, the number of fingers in the capacitor can be altered to increase the capacitance while reducing the graphene resistance. This in turn, allows for a higher Q factor for the devices. The devices fabricated achieved Q factors above 50 for frequencies between 1.1 GHz to 24.8 GHz.

Graphene ring-oscillators have been developed in [4]. Through the use of top-gated fieldeffect transistors, the fabricated devices achieved oscillating frequencies of 1.22 GHz. Subsequently, a graphene mixer was also demonstrated without the need of an external local oscillator.

The previously mentioned RF components are essential for RF communication systems. Through the use of graphene in these devices, gigahertz operating systems are a possibility, with a lower cost of manufacture. However, RF communication systems require high performance from all its components. One of the key components of the RF systems is the transistor, as it is used for the mixers and doublers as well as the LNA and oscillator.

Graphene-based transistors have been fabricated ever since its discovery in 2004. The first transistors fabricated were gated through the substrate and not viable for radio-frequency applications. Several approaches have been developed for the fabrication of graphene transistors operating in the gigahertz or even terahertz band. Fabrication of said devices had to accommodate to the pre-existent and dominant silicon technology. Some of the fabrication processes used for silicon are not compatible with the new material, as it degrades it's lattice, introducing defects and impurities, which lowers the devices performance.

Several approaches were implemented to circumnavigate these problems, and to date, graphene field-effect transistors already reach the terahertz band, in terms of cut-off frequency.

### **1.3 Work Motivation**

The main motivation of this dissertation is to produce a fabrication method of graphenebased field effect transistors for radio-frequency applications, using, as possible, standard and large-scale clean room fabrication technologies. Graphene-based transistors fabricated previously in the research centre were not optimized for radio-frequency applications. Several methods of fabrication from literature were reviewed and based on the available tools, a physical structure was chosen.

In order to better understand how the physical parameters of the chosen structure would influence the figures of merit, modelling of the proposed transistors is required. Several models for these types of devices have been reported in literature, however, these are few and far between. A model that best describes the transistors performance must be first implemented and validated so that it can be used later on for the development of radio-frequency circuits and devices.

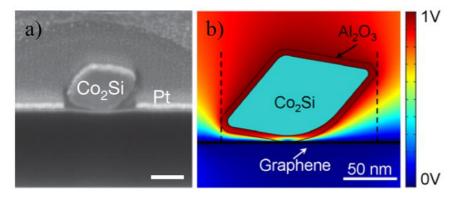

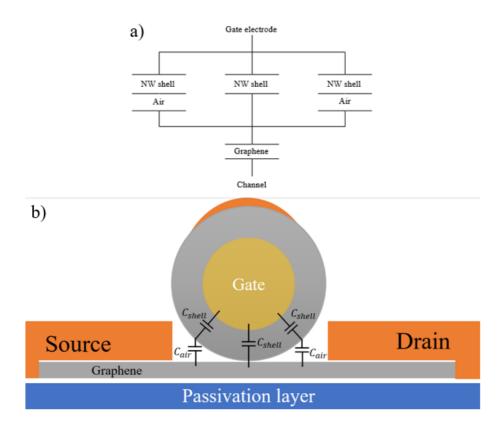

As stated before, the research centre had not fabricated to date, graphene transistors for radio-frequency applications. For this reason, fabrication of graphene field-effect transistors based on the work of [5], will be implemented. This structure requires nanowires to be grown and a dielectric deposited to serve as gate and gate insulator of the device.

In order to synthesise the nanowires, electrochemical deposition of nickel onto AAO templates is the method used. Dielectric shells of nickel oxide and silicon dioxide are both experimented upon to serve as the gate dielectric.

To assess the performance of the fabricated devices and to validate the model developed, characterization of the structures is required through the use of RF probes as well as DC probes.

### **1.4 Contributions**

During the work of this dissertation several contributions were made and will be listed below:

- A radio-frequency model was adapted from literature to match the intended fabrication structure. Performance assessment of the devices based on their physical structures took place and the figures of merit were retrieved for each of the physical layouts.

- Electrochemical growth of nickel nanowires on anodized aluminum oxide templates and subsequent shell deposition of nickel oxide and silicon dioxide was performed. Release and transfer of the synthesized nanowires was also achieved.

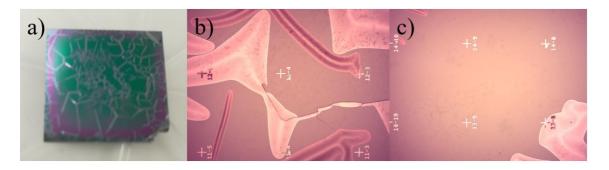

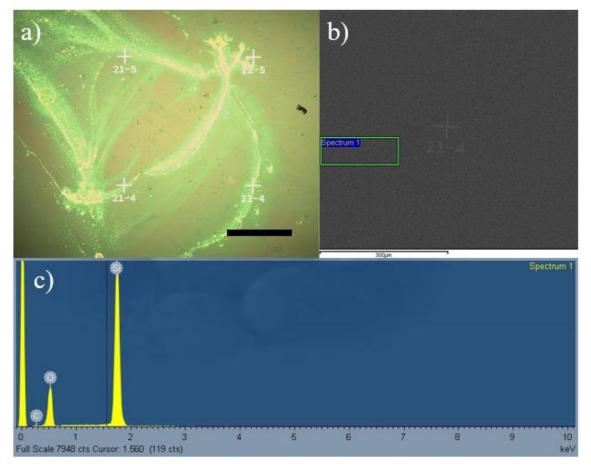

Figure 1: Optical and corresponding SEM images of the nanowires released from the seed layer. a) Scale bar: 90 µm. b) Scale bar: 10 µm.

- A method of precise nanowire placement through a dielectrophoretic process was also performed.

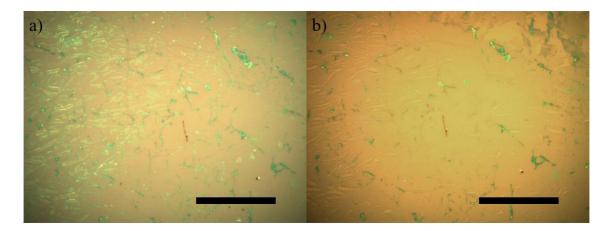

Figure 2: Dielectric assembly of nanowires. a) Top view schematic of the structure. b) Optical microscope image of the ends of a pair of electrodes. Scale bar: 10 µm. c) Optical microscope images of the electrodes of b) with an aligned nanowire between them. Scale bar: 20 µm.

- Fabrication and characterization of two types of graphene field-effect transistors was performed.

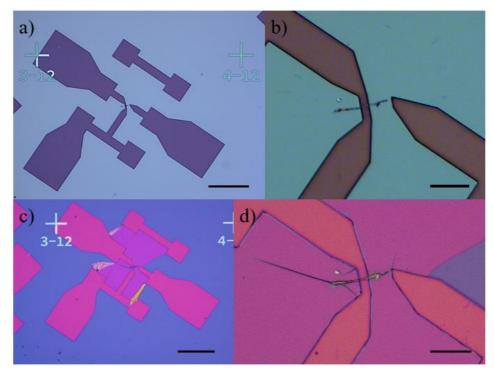

Figure 3: Resulting transistors of both the fabrication processes. a) Optical image of a graphene field-effect transistor with nickel/nickel oxide core-shell nanowire gate. Scale bar: 100 μm. b) Optical image of a graphene field-effect transistor with nickel/silicon dioxide core-shell nanowire gate. Scale bar: 200 μm.

### 1.5 Thesis organization

In the first chapter, a contextualization of graphene and the possibilities it brings when compared to other technologies is introduced alongside the motivation and contributions of this work. The second chapter contains a review of graphene properties and applications for radiofrequency devices. Fabrication constraints and a state-of-the-art of field-effect transistors fabricated for radio-frequency applications is also presented.

The third chapter contains an assessment of the available technologies for the author and a transistor proposal for fabrication of the device. Device modeling is also performed to provide values for the physical layout of the device.

The fourth chapter contains the synthesis process of nickel nanowires electrochemically deposited onto anodized aluminum oxide templates.

The fifth chapter contains the fabrication process of the first graphene field effect transistors based on a core-shell nanowire gate of nickel and nickel oxide.

The sixth chapter contains the fabrication process of the second graphene field effect transistors based on a core-shell nanowire gate of nickel and silicon dioxide.

Finally, the seventh chapter contains the conclusions and future work.

# **2** GRAPHENE BASED RF DEVICES

Graphene has attracted a lot of attention as a possible enabler for future electronics, however fabrication of such devices has encountered several setbacks since CMOS technologies cannot be readily implemented onto this new material. Performance of graphene transistor is inherently linked to its synthesis and the device fabrication process. In this chapter, a small introduction to graphene, its properties and a review of state-of-the-art graphene synthesis and fabrication processes of graphene-based radio-frequency transistors will be presented.

### 2.1 Graphene

#### 2.1.1 What is graphene?

Graphene is a 2D-material that was first isolated by Geim and Novolesov in 2004 [1] and has attracted a lot of attention due to its extraordinary mechanical, electronic and optical properties among others [6]. These properties stem from the double covalent bonds between the carbon atoms sp<sup>2</sup>, well-establishing its monotonical hexagonal shape. Graphene is the basic structural element of other allotropes, including graphite, carbon nanotubes and fullerenes.

Figure 4: Graphene and its allotropes, fullerenes, carbon nanotubes and graphite, from left to right. [7]

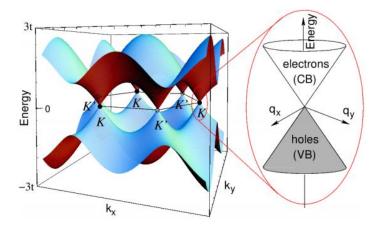

The unitary cell is composed by two carbon atoms, alternating between them in a triangular lattice structure. The honeycomb structure is the overlap of two identical primitive lattices (Figure 5). The distance between each carbon atom in the hexagonal structure is 0.142 nm while in the reciprocal lattice is 0.42 nm.

The point K and K' have the same distance to the point of maximum symmetry ( $\Gamma$ ) and are denominated the Dirac points. These points determine the electronic properties of graphene since there is where the Fermi level is located.

Figure 5: a) Honeycomb lattice structure of graphene (direct lattice). b) Corresponding Brillouin zone, showing the highsymmetry points.

#### 2.1.2 Graphene properties and characterization

Graphene is a zero-bandgap semiconductor, due to its conduction and valence band touching at the Dirac points. Three of the four valence electrons participate in the bond to the next neighbour (covalent bonds) and the fourth pi orbital is perpendicular to the plane. As a consequence, the charge carriers can be described by the Dirac equation. As a semiconductor, the charge carriers present in graphene can be either electrons or holes and the carrier concentration (doping) can be changed depending on the presence of an electric field (gating). The particularity of the graphene density of states is that in the singularities, the valence and conduction bands touch, also known as the Dirac points. The charge carriers in these linear zones form what are known as the Dirac cones where the minimum conductivity is the Dirac point. In the linear zones charge carriers have long uninterrupted paths and velocities of 1/300 the speed of light, which translates into a reduced mass, obeying to the relativistic equation (Dirac equation). Graphene over a dielectric substrate, at room temperature, has always a conductivity at the Dirac points due to the thermally generated electrons and carrier puddles that form in the graphene dielectric substrate.

Figure 6: Energy bands of graphene obtained from the tight-binding model and zoom around the Dirac point at K. Figure retrieved from reference [8]

The covalent bonds of the carbon atoms are isometrically equal translating into a strong resistance to mechanical forces parallel to the plane. In the case of bi-layer graphene the bonds between each graphene layer are established by the Van der Walls forces (weak electrostatic force). For this reason, the mechanical exfoliation of graphene is made possible.

The thermal conductivity of graphene is given by the mobility of phonons in the lattice. Similarly to the electronic conductivity, the thermal conductivity is inversely proportional to the concentration of defects in the lattice. High thermal conductivity of graphene, higher than the exceptional copper, make it an efficient material for heat dissipation applications.

Due to the atom thick structure of graphene, its light transmittance is 97.7 % [8]. Layers added to the graphene monolayer decrease its transmittance by a factor of 2.3 %, with an approximate linear relation. The transmittance of the graphene sheet can provide the number of layers present.

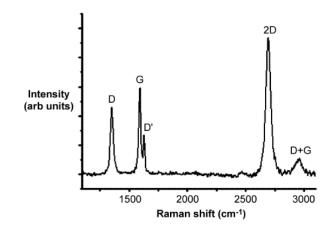

Although graphene is invisible to the naked eye, it can be characterized through the spectrum of inelastic dispersion, that comes from the interaction between phonons, the Raman spectrum (Figure 7). The most intense peaks found in the spectrum are the G peak (around 1600 cm<sup>-1</sup>) which is present in all graphitic materials, the 2D peak (around 2700 cm<sup>-1</sup>) which only

appears on monolayer or few layer graphene films, and the D peak (around 1350 cm<sup>-1</sup>) which correlates with defects on the graphene sheet. The quality of graphene is given by ratio between the G and 2D peaks as the 2D must be more intense than the G. Another form of quality assessment is the intensity of the D peak, which should be as low intensity as possible for high quality graphene sheets.

Figure 7: Raman spectrum of monolayer graphene with 514.5 nm excitation laser wavelength. Figure retrieved from reference [10]

#### 2.1.3 Graphene applications

Fifteen years have passed since graphene was first isolated in 2004 and many research has been devoted to this material, from its synthesis and transfer, to applications that affect our dayto-day lives. Consequently, products that incorporate graphene have started to appear. Graphene properties allow for a variety of applications that range from composites and coatings, energy, sensors, and electronics, among others.

Examples such as shoes where the rubber is mixed with graphene enhancing its durability and elasticity, or the use in storage drivers as a heat dissipators, are products that already have hit the market. However, graphene still holds potential on a variety of different applications.

Graphene can also be used in photonics and optoelectronics through the combination of its optical and electronic properties. In optoelectronic devices, graphene behaves as a transparent

conducting film and is used in a dye-sensitized solar cells[9]. The flexibility of graphene can also enable the production of flexible devices such as light emitting devices[10], and touch screens[11]. Graphene absorption of light over a wide spectrum, from ultraviolet to terahertz, makes it suitable for photodetector devices such as the ultrahigh-bandwidth photodetector based on few-layer graphene reported in [12].

Field-effect transistors[13], integrated circuits[14], capacitors[15], and sensors[16] have also been reported in literature. Due to its high electron mobility and compatibility with silicon technologies, it is believed that graphene can replace the highly used silicon.

Intel cofounder, Gordon Moore, predicted in a published paper in 1965, that the number of transistors in a microchip would double every 18-24 months[17]. This trend followed ever since and became known as the More's law with its main driver being the scaling down of transistors width and length, allowing more transistors per chip while maintaining the same power consumption.

The effects of down scaling have brought the industry to a point where the gate length of a transistors has reached sub-20 nm mark. These devices have increased source drain current leakages due to their proximity. Gate oxide thickness has been reduced as well, which in turn increase the gate current leakages. All of these effects increase the off current of devices and boost their power consumption. To go beyond the scaling limits of silicon, novel devices based on a combination of new materials compatible with the already advanced technology of silicon, such as graphene, will be required. As stated prior, graphene is a semi-metal and graphene-based transistors cannot be turned off. A method of creating a band gap in graphene is to cut it into narrow ribbons with less than tens of nanometres which in turn would allow digital applications for this material. On a simpler approach, graphene analogue/RF devices are a possibility as there is no requirement of turning off the device.

# 2.2 Graphene-based RF devices

Despite its many applications, in this work we will be focused on the use of graphene to support innovative RF devices.

### 2.2.1 RF devices

Several radio-frequency devices have appeared in literature, where graphene is used due to its outstanding properties, mainly electronics. These range from passive components, capacitors and resonators, to active components, frequency multipliers and RF signal mixers.

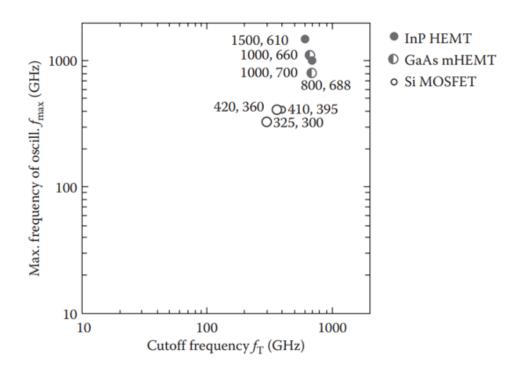

The reason why this material sparked interest in the in the radio-frequency community is due to its high charge carrier mobility (200 000 cm<sup>2</sup>/Vs), which is the highest carrier mobility of any known material. This value, when compared to other semiconductors, has 100 times more mobility than silicon and 10 times more than the state-of-the-art high mobility group III-V semiconductors (InSb), which is an enabler of higher performance values. Figure 8 shows the comparison between Si MOSFETs and the best III-V HEMTs devices in terms of figures of merit for RF transistors.

Figure 8: Maximum frequency of oscillation fmáx versus cut-off frequency fT of Si RF MOSFETs (open circles) and III–V HEMTs (InP HEMTs: full circles, GaAs mHEMTs: half-full circles). The numbers next to the symbols indicate fmáx (first number) and fT (second number) in GHz for the best transistors of each type. Figure adapted from reference [18].

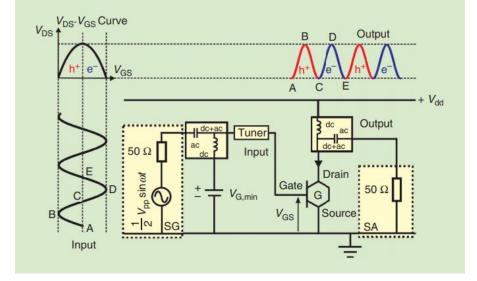

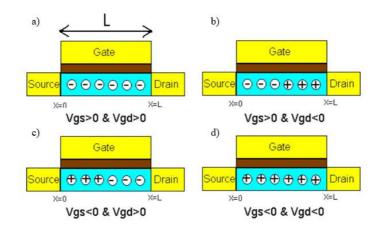

Due to the ambipolar conduction of graphene, non-linear electronics circuits became a possibility[19], which cannot be performed with traditional unipolar devices. In conventional unipolar devices, the majority carrier type in the channel is determined by the doping and cannot be changed after its fabrication. Ambipolar devices can be switched between p- type and n-type conduction by controlling the position of the Fermi level using a gate bias. GFETs biased at its minimum conduction point and superimposing a sinusoidal signal to a dc bias to the gate electrode modulates the carrier type in the channel. Source-drain voltages swing in response to the ac signal applied to the gate and a frequency doubling occurs at the output.

Figure 9: Demonstration circuit for a graphene frequency multiplier operating in a gigahertz frequency range. Figure retrieved from reference [19]

RF mixers are also made possible due to the symmetrical transfer characteristics of the GFETs [14]. The graphene transistor is modulated by two signals, the RF signal and LO signal and the drain source current contains the mixed frequencies. The symmetrical current characteristics of graphene can be expressed as follows:

$$I_D = a_0 + a_1 (V_G - V_{G,min})^2 + a_2 (V_G - V_{G,min})^4 + \cdots$$

(1)

where  $V_{G,min}$  is the gate voltage at the minimum conduction point and a0, a2, a4, . . . are constants. When biased at the minimum conduction of the device, assuming symmetrical transfer characteristics, odd-order intermodulation are supressed, and all the power is coupled to the difference and sum frequencies of even odd terms. Eliminating the odd-order intermodulation products, which are present in unipolar devices, simplifies the circuit.

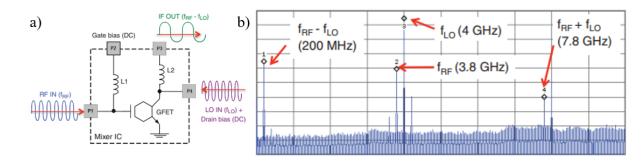

Figure 10: Graphene-based mixer. a) Circuit diagram of a four-port graphene RF frequency mixer. b) Output spectrum of the mixer, between 0 and 10 GHz. Figure adapted from reference [14]

The high carrier mobility and the high current saturation velocity of graphene can potentially allow high operating frequencies as well as low noise devices thus enabling the most attractive analogue applications of GFETs, the low noise amplifier (LNA). Graphene transistor show high current density and excellent electrostatic confinement which increase the conversion efficiency. A graphene Monolithic Microwave Integrated Circuit (MMIC) has been reported in literature [20], working in the Ku band with a small signal power gain of 3.4 dB at 14.3 GHz, and a minimum noise figure of 6.2 dB.

The devices presented previously, all have the same component in common, the transistor.

#### 2.2.2 Graphene-based RF transistors

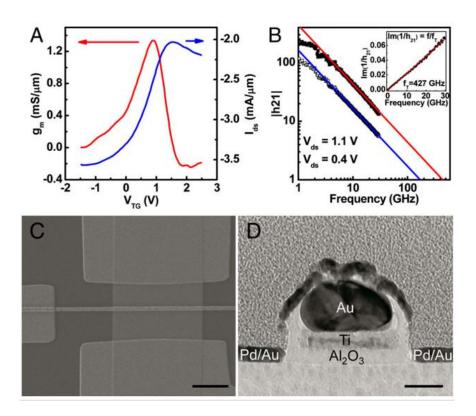

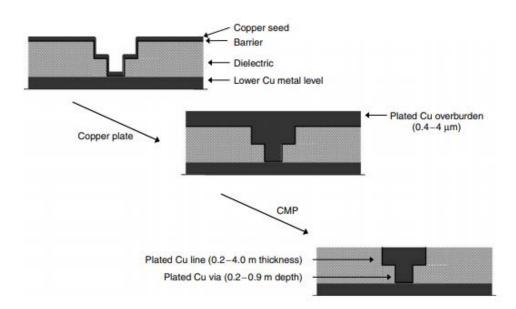

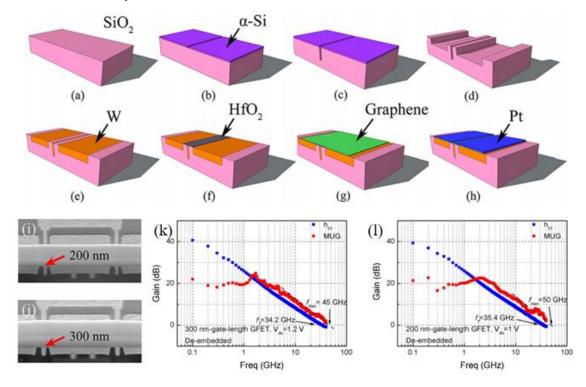

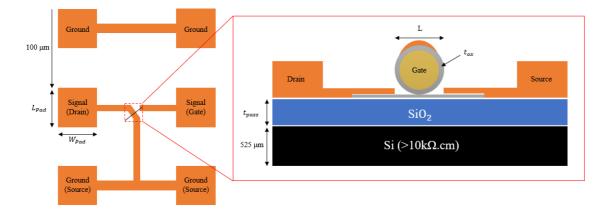

Graphene-based transistors have been developed ever since its first isolation. The devices first fabricated used the back-gate configuration, which is the most commonly used in physics experiments due to its simplicity, but such configuration is not suited for RF applications. A  $300 \text{ nm SiO}_2$  layer on top of the conductive silicon [21], which is used to apply the gate voltage, possesses a low modulation of the channel and large parasitic capacitances.