# Exploiting data locality in cache-coherent NUMA systems

Isaac Sánchez Barrera Barcelona, 2022

Advisors:

Marc Casas Guix Department of Computer Sciences Barcelona Supercomputing Center

Miquel Moretó Planas Department of Computer Architecture Universitat Politècnica de Catalunya Department of Computer Sciences Barcelona Supercomputing Center

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

A mis abuelos, Adela, Alonso, Manuel y Mercedes.

#### **Abstract**

The end of Dennard scaling has caused a stagnation of the clock frequency in computers. To overcome this issue, in the last two decades vendors have been integrating larger numbers of processing elements in the systems, interconnecting many nodes, including multiple chips in the nodes and increasing the number of cores in each chip. The speed of main memory has not evolved at the same rate as processors, it is much slower and there is a need to provide more total bandwidth to the processors, especially with the increase in the number of cores and chips.

Still keeping a shared address space, where all processors can access the whole memory, solutions have come by integrating more memories: by using newer technologies like high-bandwidth memories (HBM) and non-volatile memories (NVM), by giving groups cores (like sockets, for example) faster access to some subset of the DRAM, or by combining many of these solutions. This has caused some heterogeneity in the access speed to main memory, depending on the CPU requesting access to a memory address and the actual physical location of that address, causing non-uniform memory access (NUMA) behaviours. Moreover, many of these systems are cachecoherent (ccNUMA), meaning that changes in the memory done from one CPU must be visible by the other CPUs and transparent for the programmer.

These NUMA behaviours reduce the performance of applications and can pose a challenge to the programmers. To tackle this issue, this thesis proposes solutions, at the software and hardware levels, to improve the data locality in NUMA systems and, therefore, the performance of applications in these computer systems.

The first contribution shows how considering hardware prefetching simultaneously with thread and data placement in NUMA systems can find configurations with better performance than considering these aspects separately. The performance results combined with performance counters are then used to build a performance model to predict, both offline and online, the best configuration for new applications not in the model. The evaluation is done using two different high performance NUMA systems, and the

performance counters collected in one machine are used to predict the best configurations in the other machine.

The second contribution builds on the idea that prefetching can have a strong effect in NUMA systems and proposes a NUMA-aware hardware prefetching scheme. This scheme is generic and can be applied to multiple hardware prefetchers with a low hardware cost but giving very good results. The evaluation is done using a cycle-accurate architectural simulator and provides detailed results of the performance, the data transfer reduction and the energy costs.

Finally, the third and last contribution consists in scheduling algorithms for task-based programming models. These programming models help improve the programmability of applications in parallel systems and also provide useful information to the underlying runtime system. This information is used to build a task dependency graph (TDG), a directed acyclic graph that models the application where the nodes are sequential pieces of code known as tasks and the edges are the data dependencies between the different tasks. The proposed scheduling algorithms use graph partitioning techniques and provide a scheduling for the tasks in the TDG that minimises the data transfers between the different NUMA regions of the system. The results have been evaluated in real ccNUMA systems with multiple NUMA regions.

#### Resum

La fi de la llei de Dennard ha provocat un estancament de la freqüència de rellotge dels computadors. Amb l'objectiu de superar aquest fet, durant les darreres dues dècades els fabricants han integrat més quantitat d'unitats de còmput als sistemes mitjançant la interconnexió de nodes diferents, la inclusió de múltiples xips als nodes i l'increment de nuclis de processador a cada xip. La rapidesa de la memòria principal no ha evolucionat amb el mateix factor que els processadors; és molt més lenta i hi ha la necessitat de proporcionar més ample de banda als processadors, especialment amb l'increment del nombre de nuclis i xips.

Tot mantenint un sistema d'adreçament compartit en el qual tots els processadors poden accedir a la memòria sencera, les solucions han estat al voltant de la integració de més memòries: usant tecnologies modernes com les memòries d'alt ample de banda (high-bandwidth memories, HBM) i memories no volàtils (non-volatile memories, NVM), fent que grups de nuclis (com sòcols sencers) tinguin accés més ràpid a un subconjunt de la DRAM o amb la combinació de solucions. Tot això ha provocat una heterogeneïtat en la velocitat d'accés a la memòria principal, en funció del nucli que sol·licita l'accés a una adreça de memòria en particular i la localització física d'aquesta adreça, fet que provoca uns comportaments no uniformes en l'accés a la memòria (non-uniform memory access, NUMA). A més, molts d'aquests sistemes tenen memòries cau coherents (cache-coherent NUMA, ccNUMA), la qual cosa implica que qualsevol canvi fet a la memòria des d'un nucli d'un processador ha de ser visible pels altres nuclis de manera transparent per als programadors.

Aquests comportaments NUMA redueixen el rendiment de les aplicacions i poden suposar un repte per als programadors. Per abordar el problema en qüestió, a la tesi s'hi proposen solucions, a nivell de programari i maquinari, que milloren la localitat de dades als sistemes NUMA i, en conseqüència, el rendiment de les aplicacions en aquests sistemes informàtics.

La primera contribució mostra que, quan es tenen en compte alhora la precàrrega d'adreces de memòria amb maquinari (*hardware prefetching*) i

les decisions d'ubicació dels fils d'execució i les dades als sistemes NUMA, es poden trobar millors configuracions que quan es condieren ambdós aspectes per separat. Una combinació dels resultats de rendiment i dels comptadors disponibles al sistema s'utilitza per construir un model de rendiment per fer la predicció, tant per avançat com també en temps d'execució, de la millor configuració per aplicacions que no es troben al model. L'avaluació es du a terme mitjançant dos sistemes NUMA d'alt rendiment, i els comptadors mesurats en un sistema s'utilitzen per predir les millors configuracions a l'altre sistema.

La segona contribució es basa en la idea que el *prefetching* pot tenir un efecte considerable als sistemes NUMA i proposa un esquema de precàrrega a nivell de maquinari que té en compte els efectes NUMA. Aquest esquema és genèric i es pot aplicar a diferents algorismes de precàrrega existents amb un cost de maquinari molt baix però amb molt bons resultats. Els resultats s'avaluen amb un simulador arquitectural acurat a nivell de cicle i proporciona resultats detallats del rendiment, la reducció de les comunicacions de dades i els costos energètics.

Per últim, la tercera i darrera contribució consisteix en algorismes de planificació per models de programació basats en tasques. Aquests models simplifiquen la programabilitat de les aplicacions paral·leles i proveeixen informació molt útil al sistema en temps d'execució (*runtime system*) que en controla el funcionament. Aquesta informació s'usa per construir un graf de dependències entre tasques (*task dependency graph*, TDG), un graf dirigit i acíclic que modela l'aplicació i en el qual els nodes són fragments de codi seqüencial, coneguts com a tasques, i els arcs són les dependències de dades entre les diferents tasques. Els algorismes de planificació proposats fan servir tècniques de particionat de grafs i proporcionen una planificació de les tasques del TDG que minimitza la comunicació de dades entre les diferents regions NUMA del sistema. Els resultats han estat avaluats en sistemes ccNUMA reals amb múltiples regions NUMA.

#### Resumen

El final de la ley de Dennard ha provocado un estancamiento de la frecuencia de reloj de los computadores. Con el objetivo de superar este problema, durante las últimas dos décadas los fabricantes han integrado más unidades de cómputo en los sistemas mediante la interconexión de nodos diferentes, la inclusión de múltiples chips en los nodos y el incremento de núcleos de procesador en cada chip. La rapidez de la memoria principal no ha evolucionado con el mismo factor que los procesadores; es mucho más lenta y hay la necesidad de proporcionar más ancho de banda a los procesadores, especialmente con el incremento del número de núcleos y chips.

Aun manteniendo un sistema de direccionamiento compartido en el que todos los procesadores pueden acceder al conjunto de la memoria, las soluciones han oscilado alrededor de la integración de más memorias: usando tecnologías modernas como las memorias de alto ancho de banda (highbandwidth memories, HBM) y memorias no volátiles (non-volatile memories, NVM), haciendo que grupos de núcleos (como zócalos completos) tengan acceso más veloz a un subconjunto de la DRAM, o con la combinación de soluciones. Esto ha provocado una heterogeneidad en la velocidad de acceso a la memoria principal, en función del núcleo que solicita el acceso a una dirección de memoria en particular y la ubicación física de esta dirección, lo que provoca unos comportamientos no uniformes en el acceso a la memoria (non-uniform memory access, NUMA). Además, muchos de estos sistemas tienen memorias caché coherentes (cache-coherent NUMA, ccNUMA), lo que implica que cualquier cambio hecho en la memoria desde un núcleo de un procesador debe ser visible por el resto de procesadores de forma transparente para los programadores.

Estos comportamientos NUMA reducen el rendimiento de las aplicaciones y pueden suponer un reto para los programadores. Para abordar dicho problema, en esta tesis se proponen soluciones, a nivel de *software* y *hardware*, que mejoran la localidad de datos en los sistemas NUMA y, en consecuencia, el rendimiento de las aplicaciones en estos sistemas informáticos.

La primera contribución muestra que, cuando se tienen en cuenta a la vez la precarga de direcciones de memoria mediante *hardware* (o *hardware prefetching*) y las decisiones de la ubicación de los hilos de ejecución y los datos en los sistemas NUMA, se pueden hallar mejores configuraciones que cuando se consideran ambos aspectos por separado. Con una combinación de los resultados de rendimiento y de los contadores disponibles en el sistema se construye un modelo de rendimiento, tanto por avanzado como en en tiempo de ejecución, de la mejor configuración para aplicaciones que no están incluidas en el modelo. La evaluación se realiza en dos sistemas NUMA de alto rendimiento, y los contadores medidos en uno de los sistemas se usan para predecir las mejores configuraciones en el otro sistema.

La segunda contribución se basa en la idea de que el *prefetching* puede tener un efecto considerable en los sistemas NUMA y propone un esquema de precarga a nivel *hardware* que tiene en cuenta los efectos NUMA. Este esquema es genérico y se puede aplicar a diferentes algoritmos de precarga existentes con un coste de *hardware* muy bajo pero que proporciona muy buenos resultados. Dichos resultados se obtienen y evalúan mediante un simulador arquitectural preciso a nivel de ciclo y proporciona resultados detallados del rendimiento, la reducción de las comunicaciones de datos y los costes energéticos.

Finalmente, la tercera y última contribución consiste en algoritmos de planificación para modelos de programación basados en tareas. Estos modelos simplifican la programabilidad de las aplicaciones paralelas y proveen información muy útil al sistema en tiempo de ejecución (*runtime system*) que controla su funcionamiento. Esta información se utiliza para construir un grafo de dependencias entre tareas (*task dependency graph*, TDG), un grafo dirigido y acíclico que modela la aplicación y en el ue los nodos son fragmentos de código secuencial, conocidos como tareas, y los arcos son las dependencias de datos entre las distintas tareas. Los algoritmos de planificación que se proponen usan técnicas e particionado de grafos y proporcionan una planificación de las tareas del TDG que minimiza la comunicación de datos entre las distintas regiones NUMA del sistema. Los resultados se han evaluado en sistemas ccNUMA reales con múltiples regiones NUMA.

# **Acknowledgements**

Aquesta tesi és el resultat de més de cinc anys de feina, amb moments més tranquils i d'altres més durs. Estic content amb tot el que m'ha aportat fer el doctorat: he après moltes coses noves i he fet noves amistats. També puc dir que estic desencantat amb alguns aspectes del món de la recerca, segurament el tenia massa idealitzat i me l'esperava més centrat en fer avançar el coneixement.

Però no m'extendré més amb lamentacions que ara mateix no solucionen res, perquè no hauria de ser l'objectiu d'aquests paràgrafs. No puc més que començar agraint-vos, Miquel i Marc, que m'hàgiu dirigit la tesi. Hi ha hagut moments en els quals m'heu hagut de perseguir (com perquè acabés d'escriure això) o alguna vegada que ha passat al revés, però no ha estat gaire sovint. I també moments de dubtes existencials i de qüestionar-me que el que intentava fer pogués funcionar o servís de res, però que heu pogut salvar gràcies a la vostra experiència i la confiança que m'heu donat.

Molt importants sou tots els de RoMoL i Til·lers 3. En particular, Adrián, no conozco a nadie más dedicado y trabajador que tú, aunque ya te lo he dicho más de una vez. Atrás quedan nuestros ratos de quejarnos de todo, yo creo que con motivo, y espero que estés disfrutando por Cambridge, que debes tener un tiempo más parecido al de tu tierruca que en Barcelona, aunque te falte el mar.

Vladimir, you are a great man (pun intended). Very few people take so much care in what they do as you do, and I think you deserve the best for being such a nice guy. We should do another group Serbian dinner the next time we meet, I enjoyed it a lot the last time we went to that Serbian bar in Barcelona.

Cristóbal, poca relación tuvimos al principio más allá de que alguna vez usaba tu preciado POWER 8 (y luego usamos aquel POWER 9 que sacaron del clúster para poder hacer cosas raras). Pero tu cambio de oficina en el Nexus II cambió las cosas. ¡Te mando fuerzas para que puedas terminar con lo tuyo! Si yo he podido, tú también.

Guillem, Rubén i Víctor, espero que l'experiència del doctorat us vagi molt bé i la resta de la vida també. Juntament amb el Cristóbal, bons moments vam passar dinant al Vèrtex que amb la pandèmia es van convertir en diumenges jugant al pinturillo, petant la xerrada o comentant pel·lícules a cada qual més estrambòtica. Mai us desfareu dels meus acudits. I espero que el gem5 no us deixi amb mal cos.

Obviamente, Constan, parece que no nos podemos deshacer el uno del otro, pero supongo que será una buena señal. Antes nos veíamos más en la oficina, que estábamos sentados delante uno del otro, a ver si en poco tiempo nos volvemos a ver en la oficina (aunque sea solo algún día a la semana), porque eso significará que la pandemia ha mejorado. Así podremos tener también alguna discusión sobre si hacer algo de cierta manera o de otra tiene sentido, que con una pizarra y de cara es mejor que virtualmente.

De ti no me olvido, Calvin, que aunque quizá no te lo parezca, también me has ayudado mucho en estos años de tesis. A ver si un día nos volvemos a ver en la oficina y, por supuesto, a ver si se da otra ocasión para comer con Vladimir y Constan.

Xubin, it was great having you in the office and I'm happy you are still in Barcelona. I think your work is the one that was the clearest exponent of the runtime-aware architectures. I was happy to see you when you visited my home town, and I must say I walked a lot that day!

Paul and Dimitrios, thank you also for everything that I have learnt from both of you, many things I have built upon have started with some basic stuff you provided me. Luc, I hope you are doing great in France (if you're still there). Your tools for conference dates have been really useful, and your base LEX template for the BSC presentations has served me a lot.

Sicong, ens vam conèixer al BSC, vam parlar algun cop i ens vam ajudar en alguna cosa. Ara hem estat treballant uns mesos junts i ha estat un plaer!

Adrià i Lluc, gràcies a vosaltres també perquè, encara que no heu participat directament en la meva tesi, sí que m'heu ajudat, tant amb el gem5 com amb temes més generals de la recerca. Y gracias a ti también, Santi, que aunque hemos coincidido poco tiempo, tu granito de arena me has aportado.

No em vull oblidar de mencionar l'Helena, el Iulian i el César, y tampoco me olvido de ti, Emilio, espero que a tots vosaltres us estigui anant bé allà on sigueu! And finally, I must mention Alex, Asaf, Francesc, Jon, Louis, Max, Robin, Vatistas and Yorgos. I hope I can join you the next time you (probably Robin) organise a group dinner!

Moltes gràcies Josep, Ramon i Sara pels comentaris que em vau fer a la predefensa de la tesi. Em van resultar molt útils i crec que el document ha millorat considerablement gràcies a vosaltres. Em vaig sentir molt còmode en aquella presentació, i això no sempre és fàcil.

Gracias también a ti, Bea, por la confianza para las prácticas de docencia en el DAC. I gràcies també a tots els professors d'IC per haver-me rebut i ajudat aquests anys fent les pràctiques de docència.

Gràcies, Alex, per interessar-te en allò que vaig començar amb el miniAMR i que s'hagués quedat al calaix si no fos per tu. La veritat és que vaig gaudir col·laborant en l'article.

Aprovecho para mandar un abrazo a Helena, Vicente, Mari y el resto de personal del Vèrtex. Muchísimas veces he comido allí durante los años que he estado con el doctorado, salvo este último, y eso es porque la comida, el trato y el precio se lo merecían. No dudo en que volveré a comer allí si estoy por la zona entre semana.

Tack så mycket till alla på UART! (I hope I've written this correctly, I haven't advanced in Swedish as much as I'd have to). Nevertheless, one main contribution of this thesis comes from my research visit there. Mihail, as I've told you more than once, you were a great mentor and I'm happy we still keep in touch. It would have been great to have physical thesis defences, so

that you could visit Barcelona for that occasion, but you are still invited to visit the city any other time. And David, if UART is such a great group it is your fault in great measure! It was very good for me going to Uppsala. And I miss doing Fika with all of you, Anastasia, Chris, Gustav, Hassan, Johan, Kim, Marina, Mehdi, Paul, Per and Ricardo. The mug you gave me is in a privileged place at home.

Marta, mama, papa, es muy típico decir que no habría podido hacer esto sin vuestro apoyo, pero es que es verdad. Sé que en algún momento durante todo el proceso de la tesis no solo he estado desquiciado sino que he sido desquiciante, pero ya se termina y esto es una parte del resultado. Y la cosa es que tampoco habría podido sin mi Ada, mi Otto y mi Frida. Siempre digo que sois muy pesados (Ada, pobrecita, tú ya no), pero especialmente este último par de años se habrían hecho mucho más duros sin vosotros por casa.

Yaya, avi, abuela, abuelo, ya lo digo al principio de esta tesis, pero va por vosotros. Sé la ilusión que os hace incluso si no entendéis nada de lo que hay en el documento. Pero el mismo orgullo que sentís, lo siento yo dedicándoos este trabajo.

Alberto, qué te voy a decir a ti que no sepas ya. Entre que estás lejos y la pandemia, poco nos hemos podido ver (en persona) este último par de años, pero eres seguramente con quien más rato he estado hablando. Se acerca ya el final de nuestro último proyecto en común, con el que hemos aprendido bastante los dos, pero estoy seguro de que vamos a encontrar excusas para hablar y que yo me vaya por los cerros. I com que parlo amb l'Alberto, aprofito i et dic, Laura, que encara no he tastat els paparajotes. Quan sigui tot més normal i us passeu per aquí un altre cop, us dono fulles de llimoner, que els vull tastar!

Guillermo, estos años habrían sido bastante más difíciles sin ti. Ir al teatro no deja de ser una excusa para estar luego hablando de la vida, quejarnos de los políticos, de la sociedad, de lo bueno y lo malo del trabajo... Tenemos que recuperarlo (ahora que está todo un poco más fácil de nuevo) y mantenerlo, porque como se dice, a mí me da la vida.

No acabaré sense esmentar l'ERIE de Recerca i Rastreig amb Gossos de la Creu Roja i la Coral l'Amistat de Premià de Mar. Tots aquests anys formant part del grup dels gossos (juntament amb el meu pare) i aquest últim gairebé any i mig a la coral m'han ajudat a desconnectar de les obligacions. I és totalment necessari per poder aguantar-ho tot.

All this work does not come for free. I have been partially supported by the Spanish Ministry of Education, Culture and Sport under fellowship number FPU15/03612, and by the Spanish Ministry of Science, Innovation and Universities under fellowship number EST18/00799. This thesis has also been supported by the Spanish Government (Severo Ochoa grant SEV2015-0493), by the Spanish Ministry of Science and Innovation (contract TIN2015-65316-P), by the Generalitat de Catalunya (contracts 2017-SGR-1414 and 2017-SGR-1328), by the RoMoL ERC Advanced Grant (grant agreement 321253) and the European HiPEAC Network of Excellence. The Mont-Blanc project has received funding from the EU's H2020 Framework Programme (H2020/2014-2020) under grant agreement numbers 671697 and 779877.

# **Contents**

| 1. | Intro | oductio | n                                                   | 1  |

|----|-------|---------|-----------------------------------------------------|----|

|    | 1.1.  | Thesis  | objectives and contributions                        | 2  |

|    |       | 1.1.1.  | Performance and configuration models for interac-   |    |

|    |       |         | tions between NUMA and hardware prefetchers         | 3  |

|    |       | 1.1.2.  | Hardware prefetching for NUMA systems               | 3  |

|    |       | 1.1.3.  | Task-based applications in NUMA systems             | 4  |

|    | 1.2.  | Thesis  | structure                                           | 4  |

| 2. | Back  | ground  | l and related work                                  | 7  |

|    | 2.1.  | Paralle | el computing, shared memory and NUMA                | 7  |

|    |       | 2.1.1.  | Virtual memory: allowing multiprogramming and       |    |

|    |       |         | larger main memory capacity                         | 9  |

|    | 2.2.  | Cache   | s and the memory hierarchy                          | 10 |

|    |       | 2.2.1.  | Cache coherence and ccNUMA                          | 11 |

|    |       | 2.2.2.  | Hardware prefetching                                | 11 |

|    | 2.3.  | Paralle | el programming in shared-memory systems             | 13 |

|    |       | 2.3.1.  | Task-based programming                              | 15 |

|    |       | 2.3.2.  | Work scheduling and data placement in NUMA systems  | 17 |

|    | 2.4.  | Holisti | c performance optimisation and runtime-aware archi- |    |

|    |       | tecture | es                                                  | 20 |

|    |       | 2.4.1.  | Using models to drive configurations                | 21 |

|    |       | 2.4.2.  | Runtime-aware architectures                         | 22 |

| 3. | Ехре  | eriment | al methodology                                      | 25 |

|    | 3.1.  | Real N  | IUMA systems                                        | 25 |

|    |       | 3.1.1.  | Large ccNUMA systems                                | 26 |

|    | 3.2.  | Simula  | ation of NUMA Systems                               | 27 |

# Contents

|    | 3.3. | Worklo   | oads                                                | 29 |

|----|------|----------|-----------------------------------------------------|----|

|    |      | 3.3.1.   | Fork-join parallel applications                     | 30 |

|    |      | 3.3.2.   | Task-based parallel applications                    | 35 |

| 4. | Perf | ormano   | e and configuration models for interactions between |    |

|    | NUM  | IA and h | nardware prefetchers                                | 39 |

|    | 4.1. | The re   | elevance of NUMA and prefetcher configurations in   |    |

|    |      | perfor   | mance                                               | 40 |

|    | 4.2. | Search   | n space                                             | 43 |

|    |      | 4.2.1.   | NUMA configurations                                 | 43 |

|    |      | 4.2.2.   | Prefetcher configurations                           | 45 |

|    | 4.3. | Chara    | cterisation                                         | 45 |

|    |      | 4.3.1.   | Experimental setup                                  | 46 |

|    |      | 4.3.2.   | Performance opportunities                           | 46 |

|    |      | 4.3.3.   | NUMA+Prefetcher configuration diversity             | 47 |

|    |      | 4.3.4.   | Takeaway                                            | 48 |

|    | 4.4. | Predic   | tion model                                          | 48 |

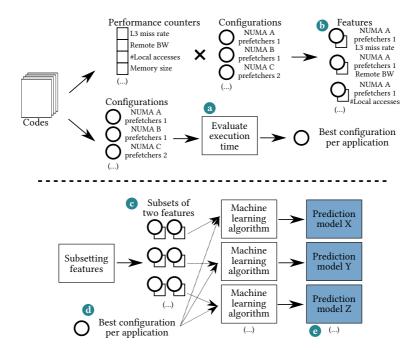

|    |      | 4.4.1.   | Machine learning models                             | 49 |

|    |      | 4.4.2.   | Model generation and inputs                         | 50 |

|    | 4.5. | Predic   | tion results                                        | 53 |

|    |      | 4.5.1.   | Model evaluation                                    | 54 |

|    |      | 4.5.2.   | Comparing machine learning methods                  | 57 |

|    |      | 4.5.3.   | Reaction-based performance counters improve mod-    |    |

|    |      |          | elling                                              | 59 |

|    |      | 4.5.4.   | Takeaway                                            | 60 |

|    | 4.6. | Optim    | ising applications online                           | 61 |

|    |      | 4.6.1.   | Online profiling and optimisation                   | 61 |

|    |      | 4.6.2.   | Whole-application optimisation                      | 62 |

|    |      | 4.6.3.   | Per-region NUMA optimisation                        | 65 |

|    | 4.7. | Summ     | nary                                                | 66 |

| 5. | Hard | lware p  | refetching for NUMA systems                         | 67 |

|    | 5.1. | _        | uction                                              | 67 |

|    | 5.2. |          | ation                                               | 69 |

|    |      | 5.2.1.   | Background on hardware prefetchers                  | 69 |

|    |      | 5.2.2. | Opportunity for NUMA-aware prefetchers 70                  |

|----|------|--------|------------------------------------------------------------|

|    | 5.3. | Propos | sal: NUMA-aware prefetching                                |

|    |      | 5.3.1. | The NUMA-aware stride prefetcher                           |

|    |      | 5.3.2. | Other considerations                                       |

|    | 5.4. | Metho  | dology                                                     |

|    |      | 5.4.1. | Simulation environment                                     |

|    |      | 5.4.2. | Design space exploration                                   |

|    | 5.5. | Result | s and evaluation                                           |

|    |      | 5.5.1. | Design space exploration                                   |

|    |      | 5.5.2. | Performance evaluation 79                                  |

|    |      | 5.5.3. | Comparison with the state of the art 85                    |

|    |      | 5.5.4. | Making other prefetchers aware of NUMA 87                  |

|    |      | 5.5.5. | Cost evaluation                                            |

|    | 5.6. | Summ   | ary                                                        |

| 6. | Task | -based | applications in NUMA systems 91                            |

|    | 6.1. | Graph  | partitioning                                               |

|    |      | 6.1.1. | Graph partitioning algorithms 93                           |

|    | 6.2. | Exploi | ting the task dependency graph to mitigate NUMA effects 95 |

|    |      | 6.2.1. | Dependency easy placement (DEP) 95                         |

|    |      | 6.2.2. | Considerations about applying graph partitioning on        |

|    |      |        | applications' TDGs                                         |

|    |      | 6.2.3. | Runtime informed partitioning (RIP) 97                     |

|    |      | 6.2.4. | Benefits of graph partitioning                             |

|    |      | 6.2.5. | Assumptions of the proposals 102                           |

|    | 6.3. | Experi | mental environment                                         |

|    |      | 6.3.1. | Manual scheduling and graph windows 103                    |

|    | 6.4. | Evalua | tion                                                       |

|    |      | 6.4.1. | SGI Altix UV100                                            |

|    |      | 6.4.2. | Atos Bull bullion S16                                      |

|    |      | 6.4.3. | Reduction of coherence traffic within the bullion S16      |

|    |      |        | Machine                                                    |

|    |      | 6.4.4. | Load imbalance and overhead                                |

|    |      | 6.4.5. | Adding page migration mechanisms 112                       |

|    | 6.5. | Summ   | ary                                                        |

# Contents

| 7.  | Cond   | clusions                                                 | 115 |

|-----|--------|----------------------------------------------------------|-----|

|     | 7.1.   | Goals and contributions                                  | 115 |

|     |        | 7.1.1. Performance and configuration models for interac- |     |

|     |        | tions between NUMA and hardware prefetchers              | 116 |

|     |        | 7.1.2. Hardware prefetching for NUMA systems             | 117 |

|     |        | 7.1.3. Task-based applications in NUMA systems           | 117 |

|     | 7.2.   | Future work                                              | 118 |

|     | 7.3.   | Publications                                             | 120 |

|     | 7.4.   | Financial and technical support                          | 120 |

| Bik | oliogr | aphy                                                     | 123 |

# **List of Tables**

| 3.1. | Common characteristics of the simulated systems                  | 29  |

|------|------------------------------------------------------------------|-----|

| 3.2. | Summary of inputs for fork-join parallel applications            | 34  |

| 3.3. | List of codelets for each fork-join parallel application         | 35  |

| 3.4. | Summary of inputs for task-based parallel applications           | 38  |

| 4.1. | Comparison of speedups between different optimisation            |     |

|      | searches against an optimised default (pages: locality, threads: |     |

|      | scatter, prefetchers: on)                                        | 47  |

| 4.2. | Prediction model parameters. Single/multi-label models use       |     |

|      | the same parameters                                              | 50  |

| 4.3. | Best model parameters for each ML method, including the          |     |

|      | reaction-based performance counters selected as the two          |     |

|      | profile inputs.                                                  | 56  |

| 4.4. | Execution times (billions of cycles) of BT and SP region con-    |     |

|      | flicts and online profiling. The overhead is quickly amortised   |     |

|      | since each region is called hundreds of times                    | 64  |

| 6.1. | Load balance (LB), runtime overheads (OH) and graph par-         |     |

|      | titioning overheads (GP) in the SGI Altix UV100 using three      |     |

|      | sockets (as percentages, %)                                      | 112 |

# **List of Figures**

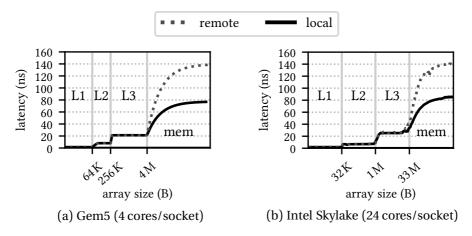

| 3.1.  | Measured memory latencies in milliseconds as we increase        |    |

|-------|-----------------------------------------------------------------|----|

|       | the working set size with LMbench lat_mem_rd                    | 26 |

| 3.2.  | High-level diagram of the simulated gem5 system                 | 27 |

| 3.3.  | Latencies of the memory hierarchy in a simulated environ-       |    |

|       | ment and a real system                                          | 28 |

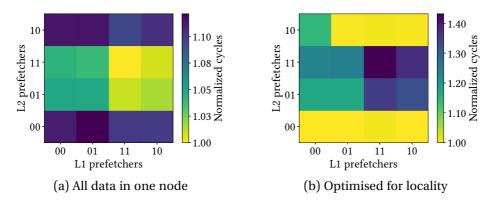

| 4.1.  | Normalised cycles (lighter is faster) for BT using two NUMA     |    |

|       | configurations                                                  | 41 |

| 4.2.  | Normalised speedups (lighter is faster) of parallel regions     |    |

|       | showing complex sensitivities to NUMA+Prefetcher config-        |    |

|       | urations on a Sandy Bridge system                               | 42 |

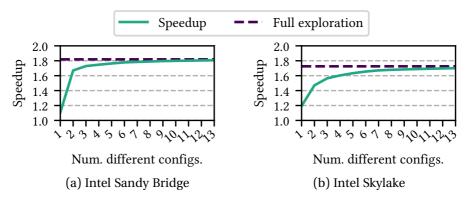

| 4.3.  | Maximum attainable speedup with respect to the number of        |    |

|       | configurations                                                  | 48 |

| 4.4.  | Diagram showing how the model training scheme works             | 51 |

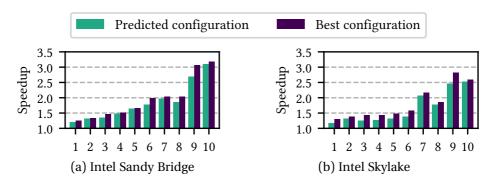

| 4.5.  | 10-fold cross-validation of the predicted results               | 54 |

| 4.6.  | Geometric mean performance gains of the most effective          |    |

|       | prediction model for each Machine Learning methods/_m           |    |

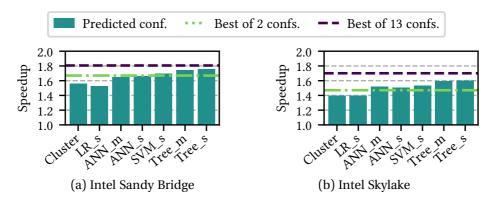

|       | refer to single label/many-labelled training                    | 58 |

| 4.7.  | Single-configuration profiling vs. the best Reaction-based      |    |

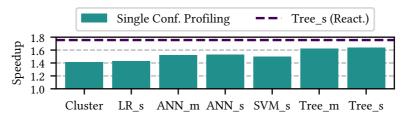

|       | performance counter approach (Tree_s React.)                    | 60 |

| 4.8.  | Online evaluation of different configurations                   | 61 |

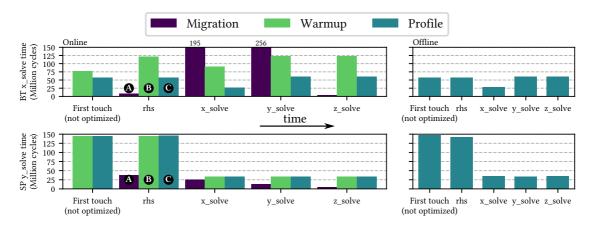

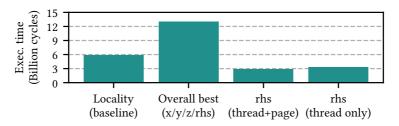

| 4.9.  | Overheads and execution times for online and offline profiling. | 63 |

| 4.10. | Execution cycles for rhs from SP                                | 65 |

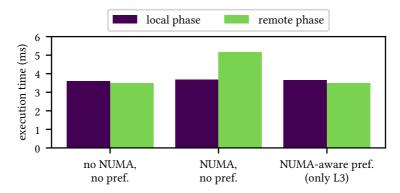

| 5.1.  | Execution times of a microbenchmark with local and remote       |    |

|       | accesses under different configurations                         | 68 |

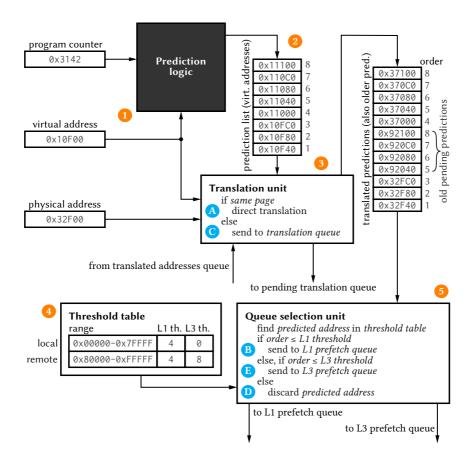

| 5.2.  | Generic diagram of the NUMA-aware prefetching scheme            | 73 |

# List of Figures

| 5.3.  | Sample pseudo-assembly code for explaining the proposal.      |     |

|-------|---------------------------------------------------------------|-----|

|       | On the left, the PC (program counter) is shown                | 74  |

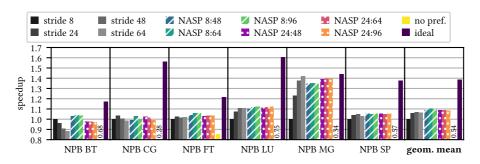

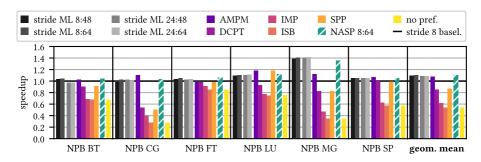

| 5.4.  | Speedups of standard stride prefetcher configurations and     |     |

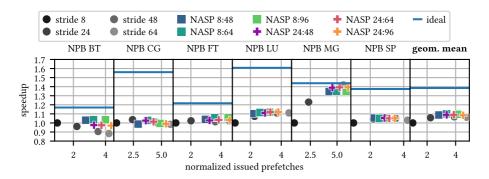

|       | our proposal                                                  | 80  |

| 5.5.  | Speedups vs. total number of issued prefetches (both norm-    |     |

|       | alised to stride 8) at all cache levels                       | 81  |

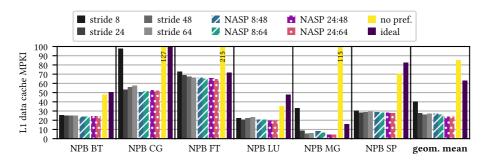

| 5.6.  | Level 1 data cache misses per 1000 instructions               | 82  |

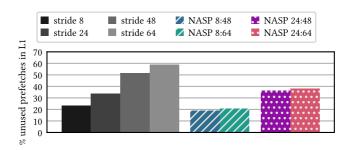

| 5.7.  | Geometric mean of the percentage of unused cache lines        |     |

|       | coming from prefetches in the L1 for different prefetcher     |     |

|       | configurations                                                | 83  |

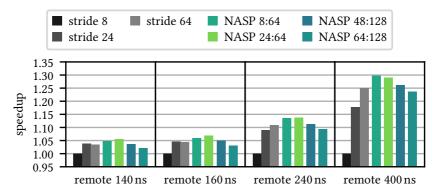

| 5.8.  | Speedups for various 2-socket systems with local latency of   |     |

|       | 80ns and different remote latencies                           | 84  |

| 5.9.  | Comparison of state of the art prefetchers with our proposal. | 85  |

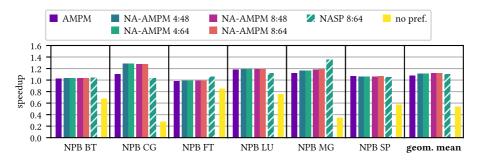

| 5.10. | Extending AMPM prefetcher with NUMA-aware capabilities.       | 87  |

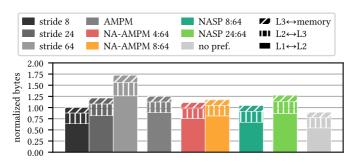

| 5.11. | Average transferred data in the memory hierarchy, includ-     |     |

|       | ing snoop packages, for different prefetcher configurations   |     |

|       | (normalised to stride 8)                                      | 88  |

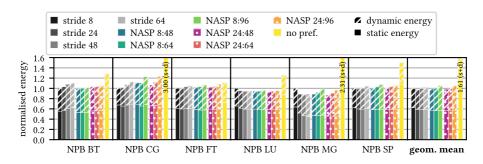

| 5.12. | Normalised energy consumption in the sockets (cores, L1,      |     |

|       | L2 and L3) for the different prefetchers                      | 89  |

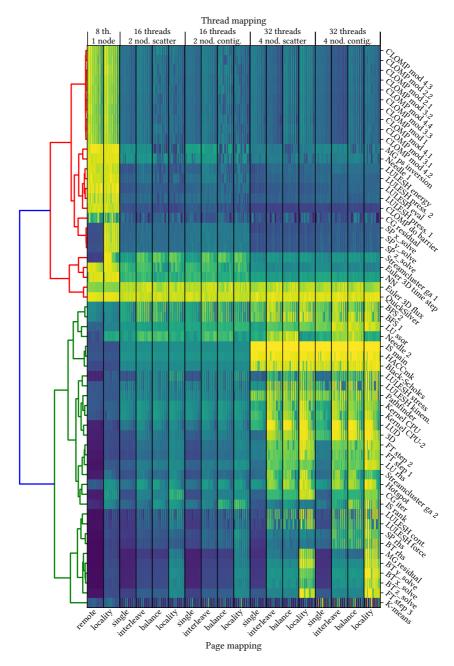

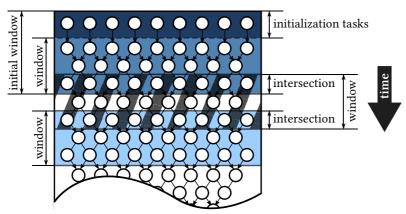

| 6.1.  | Diagram showing how RIP-MW works over time. The most          |     |

|       | relevant parameters for RIP-MW are represented                | 99  |

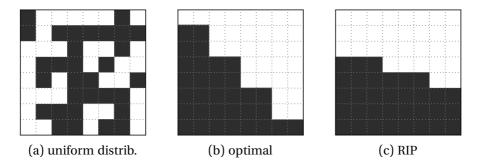

| 6.2.  | Task and data allocations into two sockets (dark and light)   |     |

|       | on the first iteration of Gauss-Seidel (8 $\times$ 8 grid)    | 100 |

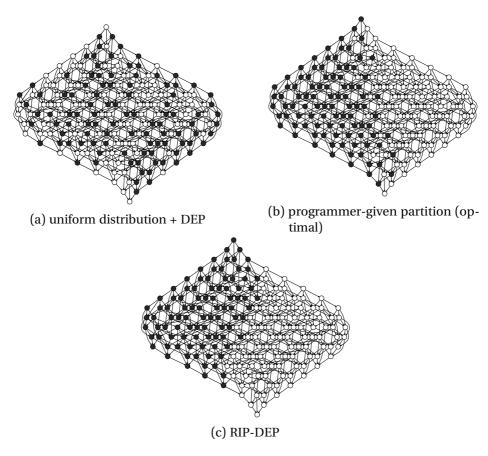

| 6.3.  | Task dependency graph corresponding to three iterations       |     |

|       | of the Gauss-Seidel code comparing a uniform distribution     |     |

|       | placement with locality awareness (DEP) to a programmer-      |     |

|       | given partition and the RIP-DEP technique in a two-socket     |     |

|       | system                                                        | 101 |

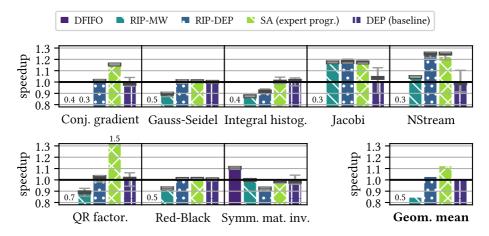

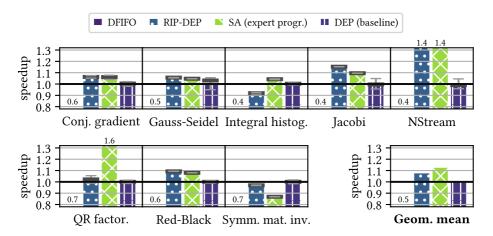

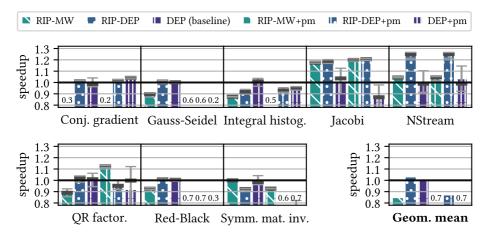

| 6.4.  | Speedup results in the SGI Altix UV100 using 3 sockets, 24    |     |

|       | cores. DFIFO is locality-unaware, SA is manual, the rest are  |     |

|       | automatic methods                                             | 106 |

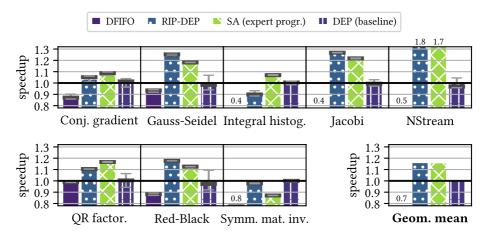

| 6.5.  | Speedup results in the bullion S16 using 4 sockets, 32 cores. |     |

|       | DFIFO is locality-unaware, SA is manual, the rest are auto-   |     |

|       | matic methods                                                 | 107 |

|       |                                                               |     |

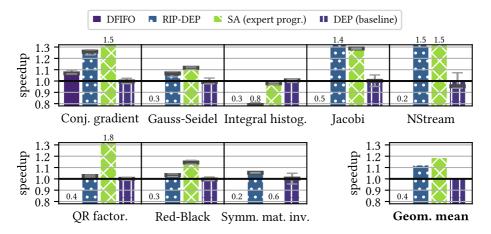

| 6.6. | Speedup results in the bullion S16 using 8 sockets, 32 cores. |

|------|---------------------------------------------------------------|

|      | DFIFO is locality-unaware, SA is manual, the rest are auto-   |

|      | matic methods                                                 |

| 6.7. | Speedup results in the bullion S16 using all 16 sockets, 288  |

|      | cores. DFIFO is locality-unaware, SA is manual, the rest are  |

|      | automatic methods                                             |

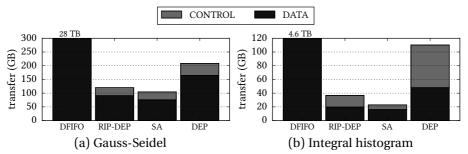

| 6.8. | Coherence traffic to and from the BCS for selected applica-   |

|      | tions using 32 cores in 8 sockets in the bullion S16 110      |

| 6.9. | Speedup results in the SGI Altix UV100 using 3 sockets, 24    |

|      | cores, with page migration mechanisms (marked as $pm$ ) 113   |

# Chapter 1.

# Introduction

The end of Dennard scaling has caused a stagnation of the CPU clock frequency. A solution to keep increasing the peak performance of high performance computing (HPC) systems has been to integrate more and more computing units in the systems, achieved with the interconnection of many nodes (like in supercomputers and clusters), the inclusion of multiple chips in each node and the increase of the number of cores in each chip. This increase in the computing capacity also requires an increase in the memory capacity and bandwidth to be able to feed data to the computing units. However, the speed of memory has not evolved as fast as the speed of processors, causing what is called the *memory wall* [160]. In the case of HPC systems, the increase in memory bandwidth has been achieved by providing local DRAM memories for each processor node with coherent communications between nodes, but also using newer technologies such as non-volatile memories (NVM) or high-bandwidth memories (HBM). These memories increase overall bandwidth, but result in *non-uniform memory* access (NUMA) behaviours: latency and bandwidth depend both on the node accessing the data and the node where the data is stored. In some cases, like in *cache-coherent NUMA* (ccNUMA) systems, there is coherence in the memory hierarchy inside the nodes of the system.

This heterogeneity in memory access time poses many challenges and requires solutions at the various levels of the computer stack. Moreover, it also worsens the programmability in the systems: when programmers have to take into account more and more characteristics of the system where

## Chapter 1. Introduction

the applications are going to be executed to improve the performance, the time for developing and maintaining the applications may increase. This can have an impact in the portability of the code, its complexity and its quality: it is not the same to have all accesses with the same latency or with different latencies. Because of this, one of the trends in the last years has been to develop approaches to abstract the programmer from having to consider the hardware specificities of the underlying systems. Many of the solutions specific for NUMA rely on the OS or runtime system level: automatic page or thread migration by the kernel [43], workload scheduling taking into account the physical location of the data [117, 144, 152] or hybrid solutions [49]. Other more general solutions can be used in systems not showing NUMA effects, like adding hardware structures in the cache hierarchy for prefetching data in advance, known as hardware prefetchers [77, 78].

In this regard, one of the most recent trends to overcome the identified challenges consists in doing a holistic design of the hardware and the runtime system software, that is, designing both simultaneously [150]. One option can be the use of special hardware units that contain information useful for the runtime system, allowing it to make informed decisions or change some hardware configurations and improve the execution performance [28]. This holistic approach with the hardware and the runtime system software can relieve the programmers from having to take the hardware characteristics into account and has been used in many of the recent proposals for improving the performance of software applications in HPC systems.

# 1.1. Thesis objectives and contributions

This thesis has the goal of improving the performance of applications in systems that show NUMA behaviours by improving the data locality of the applications, all in a seamless way for the programmer. In order to reach this goal, we propose various approaches at the runtime software and the hardware level that affect scheduling of the workloads and prefetching of their data.

# 1.1.1. Performance and configuration models for interactions between NUMA and hardware prefetchers

In the first contribution, we study how optimising the NUMA scheduling (the placement of threads and data) or the data hardware prefetcher configurations separately gives results that fall away from the optimal. We present the performance benefits of optimising both for the NUMA scheduling and the data hardware prefetcher configurations in NUMA systems by means of offline modelling and online profiling. To address the large design space, we propose a prediction model that reduces the amount of input information needed and the complexity of the prediction required. We do so by selecting a subset of performance counters and application configurations that provide the richest profile information as inputs, and by limiting the output predictions to a subset of configurations that cover most of the performance.

The proposed model is robust and can choose near-optimal NUMA scheduling and prefetcher configurations for applications from only two profile runs. We further demonstrate how to profile online with low overhead, resulting in a technique that delivers an average of 1.68× performance improvement over a locality-optimised scheduling baseline with all prefetchers enabled.

## 1.1.2. Hardware prefetching for NUMA systems

Extending on the relevance of optimising not just the scheduling of NUMA applications but also the hardware prefetcher configurations, the second contribution proposes a generic hardware prefetching scheme that leverages the NUMA characteristics to enhance system performance. This knowledge is used to prefetch data more aggressively depending on the physical location of the predicted accesses. The extra latency when accessing non-local data is effectively hidden by prefetching this data to the last-level of cache, which has enough capacity to store such data.

This approach is evaluated using gem5, a cycle-accurate architectural simulator, in a modelled multi-socket NUMA system, proposing a simple hardware prefetcher that is aware of NUMA effects. We achieve a 1.30× speedup

#### Chapter 1. Introduction

on average when compared to a standard stride prefetcher. We also get a  $1.10\times$  speedup against the best-performing state-of-the-art prefetcher. Finally, we show that the ideas can be applied to other hardware prefetchers, obtaining a  $1.06\times$  speedup over the NUMA-unaware version.

#### 1.1.3. Task-based applications in NUMA systems

In the last contribution, we propose scheduling techniques at the runtime system level to further mitigate the impact of NUMA effects on parallel applications' performance. We leverage the runtime system metadata obtained when using a task-based programming model, which can model the application in terms of a task dependency graph, where nodes are pieces of serial code and edges are control or data dependencies between them, to efficiently reduce data transfers.

This new approach, based on graph partitioning methods, adds negligible overhead and is able to provide performance improvements up to  $1.52\times$  and average improvements of  $1.12\times$  with respect to the best state-of-the-art approach when deployed on a 288-core shared-memory system. Moreover, using the graph partitioning-based scheduling approach reduces the coherence traffic by  $2.28\times$  on average with respect to the state-of-the-art solutions.

#### 1.2. Thesis structure

The contents of this thesis are organised as follows:

- Chapter 2 presents the background and state-of-the-art in the hardware and software topics upon which this thesis builds.

- Chapter 3 presents the experimental methodology used within the three contributions of this thesis. To evaluate our proposals, we consider both real HPC platforms and a cycle-accurate simulator, as well as representative HPC applications and benchmarks.

- Chapter 4 presents the first contribution of this thesis, which develops performance and configuration models that consider the interaction between NUMA and hardware prefetchers in HPC systems.

- Chapter 5 presents the second contribution of this thesis, which presents a hardware prefetching scheme that alleviates NUMA effects in large HPC systems.

- Chapter 6 presents the third contribution of the thesis, which analyses how a runtime system can be used to reduce coherence traffic in a very large cache coherent NUMA system by leveraging the semantic information available in task-based parallel applications.

- Finally, chapter 7 concludes by summarising the contributions of this thesis, listing the publications resulting from it and considering what future potential research directions it suggests.

# **Chapter 2.**

# **Background and related work**

This chapter presents the previous work related with the topics discussed in the thesis. Section 2.1 introduces parallel and shared-memory systems. Section 2.2 describes caches and the memory hierarchy, together with improvements like hardware prefetching. Section 2.3 presents the options for writing and executing parallel software in shared-memory systems. Finally, section 2.4 gives an overview of holistic approaches to optimising performance in parallel systems and the path towards runtime-aware architectures.

# 2.1. Parallel computing, shared memory and NUMA

One of the early observations in the history of digital computers is that some actions or computations can be executed simultaneously, also called *in parallel*. This can be done at different levels of abstraction. Parallelism starts at the bit level, with computers like the Whirlwind [1], from the 1950s, being among the first to consider numbers as a group of bits (parallel representation) instead of a sequence of bits (serial representation) [2]. This has been standard in computers since then.

Parallelism can also be at the instruction and data levels. Flynn [58] describes a classification of computer architectures considering these levels. *Single instruction, single data* (SISD) architectures are those that allow executing a single instruction on a single data source at a time. Flynn also considers some parallelism in this case when single-CPU computers decode one instruction

## Chapter 2. Background and related work

at a time but the pipeline is segmented in such a way that allows for multiple instructions to be in flight. An example is the IBM System/360 Model 91, from 1964 [68]. Single instruction, multiple data (SIMD) architectures can execute the same instruction for different groups of operands. For such an architecture, one of the first proposals was SOLOMON (in 1962, not built), later superseded by the ILLIAC IV, in 1966, which was the first built computer to support SIMD [139]. Multiple instruction, single data (MISD) architectures are not common, but they refer to architectures that can execute multiple instructions on the same input simultaneously. Finally, multiple instruction, multiple data (MIMD) architectures can execute multiple instructions, each working with their own data, simultaneously. Modern systems with multicore processors are in this group, although such kind of systems have long existed, with the IBM System/360 Model 65, from 1965 [68], being one of the first existing examples.

There is also parallelism at the program level. The architectures that allow this type of parallelism are a particular case of MIMD: they allow executing multiple sequential programs simultaneously, each with their own instructions and data. An evolution is the parallelism at the thread level, which also allows for a single program to divide the execution in various simultaneous threads.

MIMD architectures can be further classified depending on how the memory is interconnected with the CPUs. In a *shared memory* system, the memory has a single address space and all CPUs can access the whole memory (they are also called *multiprocessors*). Such an early example is again the IBM System/360 Model 65. This is in contrast with *distributed memory* systems, in which each CPU has its own private memory, not accessible by the other CPUs (in this case, to share results the CPUs have to explicitly copy the data between them using messages). For example, supercomputers and clusters of computers fall within this category, although each of the components could be considered as a shared memory system as well.

Despite the first multiprocessors with shared memory were built in the mid 1960s, it was not until a couple of decades later when they became more general. However, they could not scale much more due to the contention

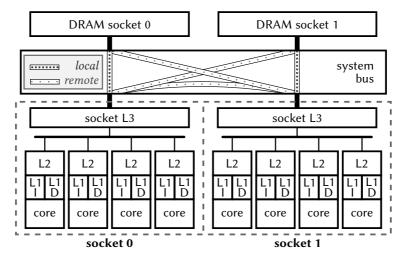

caused by the multiple processors trying to access the same memory resources. This was solved by giving each CPU or group of CPUs its own local memory whilst sharing the address space (allowing all CPUs to access the whole memory), with examples early like the DASH Multiprocessor from Stanford [90] and the SGI Origin [88]. The main effect of this was the unequal access latency to memory depending on the CPU that needed the data and the physical location of that data, with lower latencies for the local accesses. This is the reason why these systems are known as *non-uniform memory access* (NUMA) systems, in contrast with the *uniform memory access* (UMA) systems, as the previous ones became known.

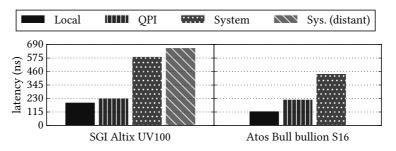

In NUMA systems, the remote accesses to memory can have different latencies as well, making them even more non-uniform. For example, an SGI Altix UV100 [138] system with 12 CPU sockets can have three different remote latencies, apart from the local access latency. To deal with these differences in the latencies, there have been various proposals for programming parallel systems as explained in section 2.3.

# 2.1.1. Virtual memory: allowing multiprogramming and larger main memory capacity

Before main memory became cheaper and with large capacity, there was a need to have an auxiliary memory (with more capacity but much slower) to be able to store the programs and the data [45]. This is without considering the storage of applications that are not executing and their data. Having to manage the main and auxiliary memories from within the applications themselves, moving the instructions and the data from one to the other depending on the needs, lowers the programmability of the systems. Moreover, running multiple applications with overlapping addresses can cause problems, and there would be the need to make sure the compiled applications used different spaces.

A solution to these issues is *virtual memory*. In broad terms, applications use addresses that might overlap with other applications' and there is a translation mechanism, supported by the operating system, to convert these

## Chapter 2. Background and related work

addresses (called virtual) to the real addresses (called physical) [45, 46]. In terms of security, this also has the benefit that untrusted applications cannot know the physical addresses used by trusted applications, and with later advances the operating systems can even protect the pages used by each application or process. Another side effect is that applications can see a larger memory capacity than truly available.

Early developments already decided to use fixed-size pages among other options [46]. In this case, the memory is divided in pages of a specific size (which can depend on the architecture and the operating system) and the map between the virtual addresses and the physical memory is done in a page-by-page basis. This reduces the amount of addresses that have to be translated, needing less storage for the translations compared to translating every single address.

In the case of NUMA systems, this has the benefit of allowing to move the pages to a different physical location without changing the address seen by the application. This also allows for advanced workload scheduling in the system and to develop optimisations that consider the location of the data and the CPUs in charge of doing the computations. This is further detailed in section 2.3 and is one of the characteristics that some proposals studied in this thesis benefit from.

# 2.2. Caches and the memory hierarchy

The different rate at which the speeds of processors and memory have evolved have caused what is known as the *memory wall* [160]. In broad terms, the memory in a system is much slower than the processors, causing a bottleneck. Therefore, by just improving the computation speed of processors the performance of the executed code would hit a limit that would only be improved by making the memory faster. The way this has been done is by creating a hierarchy for the memory: between the main memory and the processors, there are some small capacity memories that act as temporary storage and are faster to access. These memories are known as

*caches* and store the data as lines, with multiple contiguous bytes in a single line (a fixed number that depends on the microarchitecture).

With the idea of caches initially proposed by Wilkes [158] in 1965, the first commercial computer to include a cache was the IBM System/360 Model 85 [68] in 1968. Later developments of caches, still used to date, include the following: using multiple levels of cache, splitting data and instruction caches, predicting addresses before they are used (prefetching) or using advanced replacement policies (what lines to remove from the cache to insert new needed lines) [140].

#### 2.2.1. Cache coherence and ccNUMA

One of the most relevant aspects when using caches is *cache coherence* [137]. Since caches store copies of the data to have faster accesses, there is a risk that the data is not the same between multiple caches or between the cache and the main memory. In some systems this can be solved manually by the software, but many systems include hardware structures that implement *coherence protocols* to make sure that any time a memory address is accessed it is with the most updated contents. A particular case of coherent systems are *cache-coherent NUMA* (ccNUMA) systems. As their name suggests, these are NUMA systems that include hardware structures to keep coherence. In the context of this thesis, all NUMA systems considered in the evaluations are ccNUMA systems.

#### 2.2.2. Hardware prefetching

Prefetching consists in predicting the addresses that are going to be accessed and bringing the corresponding lines in advance to the cache. Prefetchers can be implemented in software or directly in hardware, with more or less complexity in the heuristics used for the prediction. They can also be tailored to prefetching for data or for instructions. Mittal published a survey [106] in 2016 about prefetching in general, though this section will provide a high

#### Chapter 2. Background and related work

level view of hardware data cache prefetching and give some details on more modern hardware prefetching techniques as well.

One of the simplest prefetchers is the *next-k line prefetcher*. When there is a miss, or an access to a prefetched line, this prefetcher would bring the k lines that come after that. This prefetcher, when used with a small buffer to prevent polluting the cache with the prefetches before they are used, is the *stream prefetcher* [78]. An evolution to this is the *stride prefetcher* [39]. In this case, the hardware detects a stride s between accesses to lines and, after access to line s it would prefetch lines s between accesses to lines and, after are more extensions to this, like allowing for different strides within a single memory instruction (PC-correlated prefetchers) or correlating the stride in one instruction with the previous strides to decide which will be the next one (delta-correlated prefetchers). Variations on these two prefetchers are usually implemented in current processor families like Intel's Xeon [153] or IBM's POWER [14].

Some complex applications follow less trivial access patterns and the above prefetching algorithms might not be adequate for these applications. One of the proposals that can serve as a base for many other ideas is the *global history buffer* (GHB) by Nesbit and Smith [107]. The GHB acts as a circular queue to keep the lists of accesses needed to feed the prefetching algorithms to decide the predictions. With this structure, a stride prefetcher can be implemented but also other prefetchers that use Markov chains [77] or other advanced techniques.

#### Modern advanced hardware prefetching

Regarding some recent hardware prefetchers, not included in Mittal's survey [106], Ayers et al. [7] show a methodology for classifying access patterns for prefetching, which allows to use different heuristics depending on the access pattern. This idea might be implemented in some commercial systems, since some hardware vendors have filed patents for similar proposals [64]. Peled, Weiser and Etsion [119] use a neural network for prefetching arbitrary access patterns, allowing for detecting more complex patterns. Still

within machine learning, Hiebel, Brown and Wang [63] use it to fine-tune the parameters of existing hardware prefetchers by using the output of some hardware counters. Ainsworth and Jones [3] propose a programmable prefetcher, which can be seen as an array of small in-order cores that can execute arbitrary prefetching algorithms, but at the cost of requiring a special compiler or extra work for the programmer to manually build these algorithms. Often, prefetchers are designed considering just sequential executions, so Liu, Yu and Huang [95] propose the use of thread-aware prefetching to reduce contention due to shared information.

#### **Prefetchers for NUMA systems**

Disabling all prefetching on NUMA systems can improve performance for irregular access patterns [99]. Moreover, prefetching can also increase the contention and hurt performance [93].

Not many works in the literature have tried to provide hardware prefetchers for NUMA systems. Hardware vendors have registered patents for changing the aggressiveness [65], throttling the prefetchers [70] or using different thresholds [96], all of them depending on the type of memory or the source memory. However, none of these ideas have been properly evaluated. A recent proposal for a NUMA-aware hardware prefetching scheme [135] is further discussed in chapter 5.

The importance of considering NUMA and prefetching simultaneously to improve the performance of parallel applications has already been shown [134], which explained in chapter 4. In general, considering multiple aspects simultaneously is key to optimise the performance of general-purpose parallel systems. This is discussed in more detail in section 2.4.

### 2.3. Parallel programming in shared-memory systems

When using a parallel system, there are multiple computing resources that can be used simultaneously. One widely used option is *multiprogramming*,

#### Chapter 2. Background and related work

which consists in executing different applications at the same time. However, another widely used option are *parallel applications*, which are applications that can use the different CPUs in the system to execute different parts of their code at the same time. Operating systems provide support for executing parallel applications by using *threads*, like POSIX Threads [141] in UNIX-like systems (Linux, BSD, Mac OS...) or Win32 Threads [15] in Windows systems, which are managed using system calls. Some programming languages and frameworks provide wrappers or abstraction layers around these system-provided options to ease code portability between systems.

To write parallel applications using the OS-provided threads or the basic wrappers from languages, programmers need to take into account all aspects from their side: creating and destroying the threads, using locks to prevent race conditions... To make programming easier, there are *application program interfaces* (API) and libraries like OpenMP [113] and Threading Building Blocks (TBB) [131] that implement the *fork-join* model.

In the fork-join model, there is a group of available threads (called a *thread pool*), which can also be created an destroyed, the code has some regions marked as "parallel" (meaning that can be executed by multiple threads) and annotations on the visibility of the variables (whether they are private, specific for each thread, or shared, when all threads use the same address for that variable). Loops can be marked as parallel and their workloads are then divided among all threads. To prevent race conditions, some code fragments can be marked as exclusive and only one thread at a time can execute them.

In the case of OpenMP, widely used in HPC for shared-memory programming, the annotations in the code are done using *compiler directives*. The preprocessor and the compiler then transform these directives into the corresponding API calls to then compile it before executing.

An alternative to these models is using a *message-passing* model such as MPI [146], widely used in clusters and supercomputers with multiple nodes and distributed memory, but also in shared-memory systems. In this case, there are multiple instances of the application running simultaneously, each doing its work and doing an explicit communication of the results to the

other instances by means of a message-passing API. This model is often combined with OpenMP or another model to build very large applications. In the case of NUMA systems, an example of use is having one instance of the application (called MPI rank or process) per NUMA node, using OpenMP inside each NUMA node but communicating the results in the different NUMA nodes with message-passing.

#### 2.3.1. Task-based programming

One of the evolutions of OpenMP is the support for *tasks* since version 3.0, driven by projects like OmpSs. Tasks are pieces of sequential or fork-join parallel code that are executed by a thread or group of threads. With extra additions like the support for *dependencies* since version 4.0 of the standard, tasks can have annotations to indicate the data that is needed to execute them and the data that they output. There is also support for nested task parallelism, in which a task can create subtasks and are executed asynchronously as well.

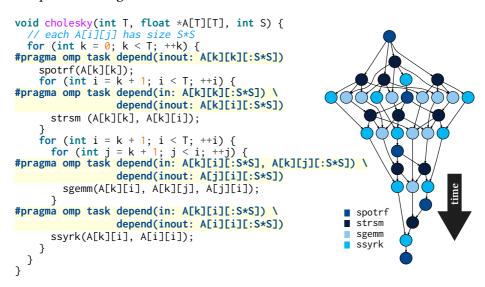

Listing 2.1 shows an example of a task-based parallelisation for a Cholesky matrix decomposition written in C using compiler directives (#pragma) specific for OpenMP. The depend clause is used to indicate the data dependencies, indicating whether each data block is used as input or output and, optionally, its size. The sequential code is split into four task types: spotrf to calculate the Cholesky decomposition of the diagonal blocks, strsm to solve the linear systems that define the below-the-diagonal blocks, and sgemm and ssyrk to do matrix multiply and rank S operations to update the rest of the matrix.

A task-based code with data dependencies can be represented as a *directed acyclic graph* (DAG), as shown in the graph accompanying listing 2.1. In this graph, known as the *task dependency graph* (TDG), nodes represent tasks and edges express dependencies between them. This graph is usually built and maintained by the *runtime system* to orchestrate the parallel execution. Thanks to the automation given by the runtime system, instead of having to explicitly manage the communications between threads and their schedule,

#### Chapter 2. Background and related work

Listing 2.1.: Task-based Cholesky decomposition using OpenMP 4 annotations and its corresponding TDG when T = 5.

the programmer can just express the dependencies and the runtime system will be in charge of managing the execution.

Using task-based programming can improve the programmability of the applications and allow for getting better performance easily. For example, Rico et al. [133] show how using a task-based approach for a mesh refinement application instead of fork-join or message passing in a shared-memory system can substantially improve the performance of the execution, even without advanced scheduling of the tasks.

#### Task scheduling

A key aspect of task-based programming models is the scheduling of the tasks. When using tasks, the programmer is relieved of having to manage how they will be distributed in the system. However, this flexibility can come at the cost of reducing the execution performance if the scheduling is done blindly. One of the simplest methods is assigning the tasks of the graph to a CPU using a *first-in*, *first-out* (FIFO) algorithm: once a task can be executed because all the input dependencies are resolved, it is inserted at the end of

a queue and the runtime system will assign the first task of the queue to any available CPU to execute.

From this basic scheduling technique, there are various advanced proposals derived from it. One simple addition is, instead of using a normal FIFO queue, to include priorities in the tasks and using a priority queue when storing the ready tasks. Built upon this, Chronaki et al. [40] propose the criticality-aware task scheduler (CATS) for heterogeneous systems: the runtime system decorates the tasks with priorities trying to find the critical path for the execution in the TDG, and then uses this information to schedule the tasks in slower or faster CPUs.

#### 2.3.2. Work scheduling and data placement in NUMA systems

In order to mitigate NUMA effects, techniques for migrating threads, memory pages or both already exist [43, 49, 147]. These techniques consist in moving computation near to data or vice versa with the goal of reducing memory access times. One benefit of these approaches is that they are agnostic of the application. However, this comes at the cost of not exploiting any application-specific information to predict the accesses to memory. As such, these proposed OS-level thread or page migration techniques only take action when the application is already suffering from remote memory accesses, which can give suboptimal results in many cases. Oppositely, other approaches transfer the NUMA management responsibility to the programmer [111, 151], exploiting information at the application source code level to carry out NUMA-aware scheduling decisions. The main issues with these approaches are that they may require significant code refactoring and programmer effort to be effective as well as the reduction in portability.

Offline methodologies can allow programmers to decide how to tackle with configurations when executing the applications, by means of some performance counters or execution traces. Diener et al. [50] characterise the communication and memory usage of applications to tune thread and data placement in systems. Beniamine et al. [13] show a tool to create a visualisation of their behaviour and help decide how to fix the performance

#### Chapter 2. Background and related work

issues. Similarly, Trahay et al. [148] present a tool to understand the evolution of memory access patterns. Popov et al. [123] and Popov, Jimborean and Black-Schaffer [125] use the CERE framework to build codelets, which make the evaluation of configurations faster and allow doing a simultaneous exploration of multiple thread and page mappings using offline methods.

Radojković et al. [128, 129] evaluate how different thread placement policies perform, and Durillo et al. [55] evaluate the benefits of using higher or lower parallelism. Diener et al. published a survey [48] with details on both data and thread placement and scheduling in NUMA systems. Many of the evaluated works make use of certain runtime information and hardware counters and are analysed in section 2.4.

#### Task scheduling in NUMA systems

Techniques that take advantage of shared memory systems which integrate different memory devices have been studied for long time. For instance, Yan et al. [162] present the hierarchical place trees (HPT), in which the programmer describes the memory hierarchy as a tree and the tasks are distributed on the tree leaves (where the workers reside) programmatically on the source code of the application. Similarly, Chatterjee et al. [37] show a domain-specific language that allows the programmer to include the locality information using affinity groups for the tasks in a file separated from the application source code, making the approach more portable.

Drebes et al. [53, 54], as well as Virouleau et al. [152] later, present a scheduling technique that can be seen as a NUMA-aware FIFO algorithm. They propose scheduling the tasks initially with a FIFO scheme, or some other technique, but as new tasks become ready, they are scheduled in a CPU that is in the same NUMA node as most of its data dependencies (so that most local access will be local). To prevent starvation of CPUs or load imbalance, they implement a work-stealing approach. This means that a CPU that is idle can execute a task initially assigned to be executed by a CPU in another NUMA node when all CPUs from that node are busy.

Since the application can be modelled as a (directed acyclic) graph, graph algorithms can be applied to the TDG, or to the partial TDG available at a specific point in time during the execution. One example of algorithm is graph partitioning, which has been used statically in message-passing applications since they can be easily represented with an undirected graph [120]. This has been done mostly in two ways: i) dividing a graph where each vertex corresponds to a block of data and the edges represent simultaneous use of data by several processes, and ii) considering a process graph, mainly related to message-passing programming models, where each vertex corresponds to one of the processes and the edges represent communications between them. Our work is the first to dynamically apply graph partitioning to reduce NUMA effects on shared-memory systems, whereas prior proposals partition the graph statically or focus on load balancing distributed memory systems.

One recent development to guide load balancing via graph partitioning techniques in task-based applications is SPAWN by Papin et al. [117]. With SPAWN, the programmer adds geometric information to the task decomposition of the problem (which has the shape of a structured mesh, where edges are not directed, instead of a DAG). This approach assigns the tasks to the CPUs and other processing elements, like GPUs or accelerators, by using a Voronoi tessellation of the mesh. During the execution, the processing elements get an electrical charge value depending on the amount of work they have and the tessellation is thus updated. Afterwards, they move on the task mesh by means of Coulomb's law and the tessellation is updated. This implies the need to have a correspondence between the problem domain and a metric space.

There have been previous results in partitioning directed acyclic graphs using standard partitioners: Tanaka and Tatebe [144] used the multiple-constraint capabilities of METIS (that do the partition in a multidimensional space) to schedule workflows, which are typically more coarse-grained than shared-memory codes. The first use of graph partitioning to directly partition the TDG and use the partition for scheduling the tasks in a NUMA system was presented in 2018 [136]. Chapter 6 has a detailed view of this proposal.

# 2.4. Holistic performance optimisation and runtime-aware architectures

The end of Dennard scaling, with a halt in the frequency increase, derived in the integration of more and more computing units. This has been possible thanks to the reduction of the transistor size as predicted by Moore's law. However, since physical limits exist, the size reduction rate is decreasing and new approaches are needed to obtain better performance from these systems until new electronic technologies (like alternatives to silicon) or computer paradigms (like quantum computers) evolve and can be used successfully.

Using performance metrics and other details available at execution time, as well as some application-specific information, allow making more informed decisions when scheduling and executing applications. In order for these methodologies to be effective, the profiling and metric extraction must have low overhead. Otherwise, the overhead could hinder the optimisation gains.

Wu and Martonosi [159] consider activating or deactivating prefetchers to prevent execution interferences inside applications using some performance counters as a metric. Khan et al. [85] introduce a runtime framework that combines software and hardware prefetching to maximise the throughput of multicore processors by sampling some performance metrics. Chasapis et al. [35] show how the runtime system can be used to model the power differences in processor manufacturing and propose a task-based scheduling algorithm in power-restricted NUMA systems. Jiménez et al. [76] evaluate some prefetching configurations at runtime to build an adaptive prefetching algorithm that automatically selects the best prefetcher configuration. Similarly, Ortega et al. [114, 115] propose using a runtime-level library to modify the hardware configuration knobs (like prefetcher and SMT) at execution time using performance counters. Broquedis et al. [20] and Dashti et al. [43] profile and make optimisation decisions in the scheduling as the application runs.

#### 2.4. Holistic performance optimisation and runtime-aware architectures

Other options that use runtime information from the applications, without using performance counters, allow to speed up the execution of task-based parallel applications. Caheny et al. [24, 26] propose executing with a NUMA-aware runtime to reduce the cache coherence traffic. Brumar et al. [21] use the runtime information about the dependencies to build a memoisation approach to approximate the computations of executions and reduce the execution time. Jaulmes et al. [72–74] evaluate the use of runtime systems in reliability and fault tolerance.

#### 2.4.1. Using models to drive configurations

Performance prediction models use input features to predict the best configuration [89, 157]. Some of the most commonly used features include thread access patterns [47], performance counters [94, 155], static code properties [157], and page, thread or inter-thread communication and sharing [50].

Wang, Davidson and Soffa [155] use integer programming (optimisation using integer variables) to predict bandwidth usage and thread allocation across different degrees of NUMA nodes, while Denoyelle et al. [47] add thread and page mappings. They build performance prediction models and conclude that performance counters and thread access patterns provide similar results as inputs. In both cases, inputs are collected by executing the application. Liao et al. [94] propose a tuning framework that predicts the best prefetching based on performance counters. Hiebel, Brown and Wang [63] extend this prediction to target more fine-grained phases of execution inside applications. Chasapis et al. [36] derive mathematical formulas to predict power consumption due to manufacturing variability and change the scheduling to meet power budgets.

Performance counters and sampled executions can be used to build machine learning models that allow to choose combined configurations of NUMA and prefetchers at execution time for applications not in the model [134]. This also shows that finding a good prefetcher configuration together with an adequate thread and data placement in NUMA systems cannot be done

#### Chapter 2. Background and related work