### POLITECNICO DI MILANO

School of Industrial and Information Engineering Master of Science in Automotive and Industrial Engineering

POLITECNICO MILANO 1863

### ANALYSIS AND OPTIMIZATION OF THE HARDWARE DESIGN OF A SIC MOSFET BASED POWER CONVERTER WITH SIC SCHOTTKY DIODES UTILIZING A SPLIT OUTPUT TOPOLOGY

Supervisor: Prof. Francesco CASTELLI DEZZA

Co-supervisor: Ing. Nicola TOSCANI

Ing. Matteo SPOSITO

Master Thesis dissertation of:

Mikel ACELDEGUI BERNAL

Academic Year 2021-2022

## Abstract

In recent years, the use of power electronic devices for energy conversion with semiconductors such as silicon carbide (SiC) or gallium nitride (GaN) are replacing silicon due to their high thermal conductivity, efficiency, resistance, and the possibility of smaller and thinner designs. For this reason, in order to evaluate the improvement potential of these systems, it is beneficial to realize experimental setups that emulate real operating conditions in order to verify the correct performance of these systems.

In this context and based on the previous work done by Giorgio Ferrara, this thesis focuses on the analysis and identification of improvements of a SiC MOSFET-based power electronic converter with the aim of suggesting and studying different solutions that ensure a highperformance operation that allows its correct implementation in motor traction and gridconnected applications.

During the thesis work, it is carried out an in-depth analysis of the voltage peaks between drain and source originated by the fast switching of the MOSFET to evaluate the use of Snubber capacitors and it is made a new hardware design of the gate driver board using isolated gate drivers to improve the dynamic behaviour in the switching transients of the SiC transistors and provide safety and robustness to the system.

Finally, maintaining the original design of the converter, it implements the split output topology to evaluate possible solutions to the problems of electromagnetic interference (EMI) and the crosstalk effect that occurs with high frequency switching.

# Sommario

Negli ultimi anni, l'uso di dispositivi elettronici di potenza per la conversione dell'energia con semiconduttori come il carburo di silicio (SiC) o il nitruro di gallio (GaN) sta sostituendo il silicio grazie alla sua elevata conducibilità termica, all'efficienza, alla resistenza e alla possibilità di realizzare disegni più piccoli e sottili. Per questo motivo, al fine di valutare il potenziale di miglioramento di questi sistemi, è utile realizzare set-up sperimentali che emulino le condizioni operative reali, in modo da poter eseguire diversi test per verificare il corretto comportamento di questi sistemi.

In tale contesto e a partire dal precedente lavoro effettuato per Giorgio Ferrara, la presente tesi si concentra nell' analisi e nidentificazione di miglioramenti di un convertitore di potenza DC-AC a commutazione, al fine di proporre e studiare diverse soluzioni che garantiscano le elevate prestazioni che assicurano la sua corretta implementazione in applicazioni di trazione a motore e di connessione alla rete.

Durante il lavoro di tesi, si analizza in dettaglio il fenomeno di picchi di tensione tra drain e source causato per la commutazione veloce del MOSFET e si valuta l'utilizzo di condensatori snubber; in più si realizza un nuovo disegno hardware della board di gate driver utilizzando gate driver isolati per migliorare il comportamento dinamico nei transitori di commutazione dei transistor SiC e per fornire sicurezza e robustezza al sistema.

Per finire, mantenendo il disegno originale del convertitore, implementa la topologia di uscita Split Output per valutare possibili soluzioni ai problemi di interferenza elettromagnetica (EMI) e all'effetto diafonia che si produce con la commutazione ad alta frequenza.

## Info

This master thesis has been developed at the Laboratory of Electrical Drives and Power Electronics located at the Department of Mechanical Engineer- ing.

The laboratory is managed by the Electrical Machines, Drives, and Power Electronics Research Group lead by Prof. Francesco Castelli Dezza (<u>francesco.castellidezza@polimi.it</u>)

#### Politecnico di Milano

ELECTRICAL MACHINES, DRIVES, AND POWER ELECTRONICS RESEARCH GROUP Department of Mechanical EngineeringBuilding B23 Campus La Masa (Bovisa)via La Masa 1 20156 Milan, Italy <u>https://www.mecc.polimi.it</u> https://www.polimi.it

The student Mikel Aceldegui BERNAL worked in the new design of the converter, being supervised by Ing. Nicola Toscani (<u>nicola.toscani@polimi.it</u>) and Ing. Matteo Sposito (<u>matteo1.sposito@polimi.it</u>). The thesis contents were studied using the hardware provided by the Electrical Machines, Drives, and Power Electronics Research Group and the university start-up ePEBB<sup>S</sup> Srl which is sponsoring the laboratory materials to this thesis.

Thesis summary:

| Author Name:   | Mikel ACELDEGUI BERNAL                                                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title:         | ANALYSIS AND OPTIMIZATION OF THE HARDWARE<br>DESIGN OF A SIC MOSFET BASED POWER CONVERTER<br>WITH SIC SCHOTTKY DIODES UTILIZING A SPLIT OUTPUT<br>TOPOLOGY |

| Supervisor:    | Prof. Francesco CASTELLI DEZZA                                                                                                                             |

| Co-Supervisor: | Ing. Nicola TOSCANI                                                                                                                                        |

|                | Ing. Matteo SPOSITO                                                                                                                                        |

| Location:          | Department of Mechanical Engineering  |

|--------------------|---------------------------------------|

| Time Duration:     | 9 months                              |

| Language:          | English                               |

| Master of Science: | Automotive and Industrial Engineering |

## CONTENTS

| 1.     | INTRODUCTION                                           |

|--------|--------------------------------------------------------|

| 1.1.   | Problem framing                                        |

| 1.2.   | Main Purpose                                           |

| 2.     | SIC BASED INVERTER WITH SPLIT OUTPUT TOPOLOGY7         |

| 2.1.   | Half-bridge topology limitations7                      |

| 2.2.   | Analysis of the split output converter10               |

| 2.2.1  | Operation of Split Output Converter10                  |

| 2.2.2. | Benefits and drawbacks of the Split Output Converter14 |

| 3.     | ANALYSIS AND OPTIMIZATION OF THE HARDWARE DESIGN 15    |

| 3.1.   | Previous Hardware Design                               |

| 3.2.   | Analysis of the Power Unit17                           |

| 3.2.1  | DC-Link                                                |

| 3.2.2. | Snubber Capacitors                                     |

| 3.2.3  | PSIM Model of the Power Unit                           |

| 3.2.4  | New Proposed PSIM Model of the Power Unit              |

| 3.2.5  | PMDC Simulation with New Model                         |

| 3.3.   | Analysis of the Gate Driver Unit                       |

| 3.3.1  | Hardware design mistakes in the Gate Driver unit       |

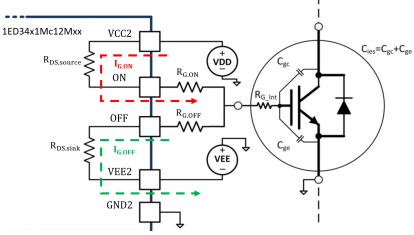

| 3.3.2. | Bootstrap vs Isolated Gate Driver                      |

| 3.3.3  | Selection of New Component to the Gate Driver Unit     |

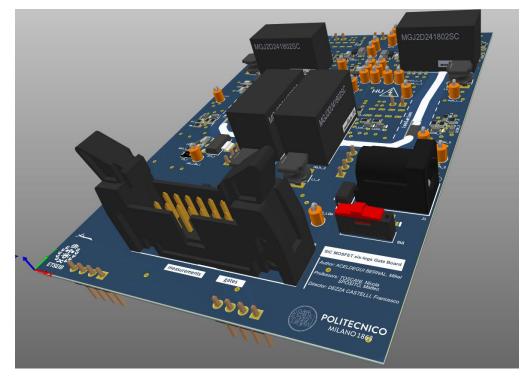

| 4.     | NEW HARDWARE DESIGN OF THE GATE DRIVER BOARD59         |

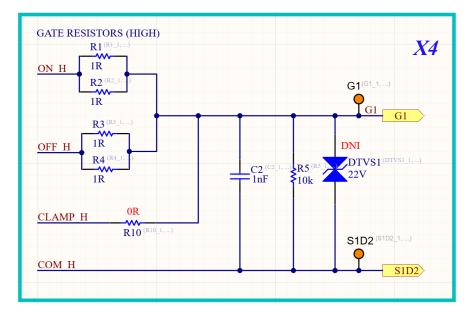

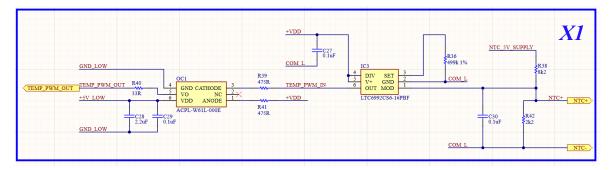

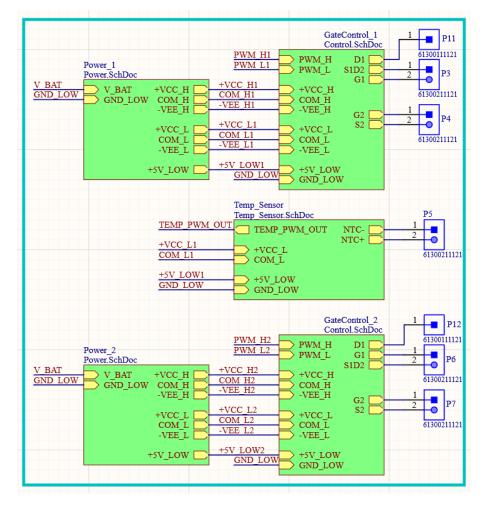

| 4.1.   | Schematics                                             |

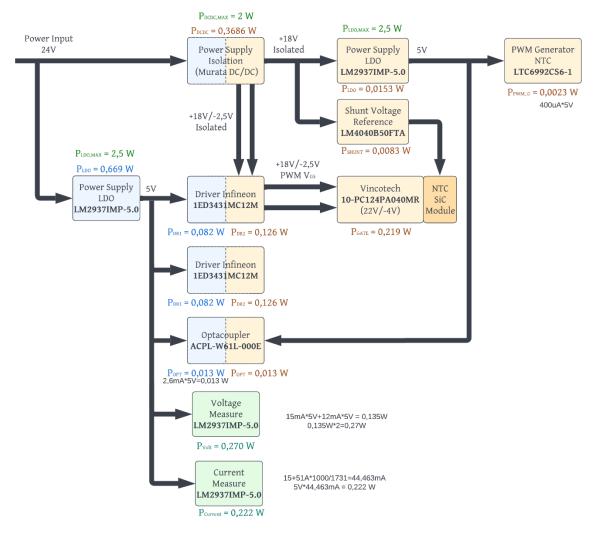

| 4.2.   | Power calculations77                                   |

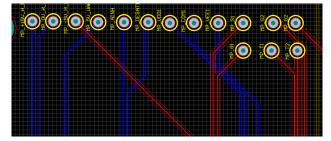

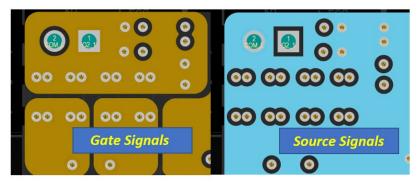

| 4.3.   | PCB Layout Design                                      |

| 4.4.   | Bill Of Materials (BOM)                                |

| 5.   | CONCLUSION                | .91  |

|------|---------------------------|------|

| 5.1. | Total Cost of the Project | . 92 |

| 5.2. | Future Work               | . 93 |

# 1. INTRODUCTION

This section explains the framework of the thesis, explaining the advantages of using silicon carbide semiconductors in comparison to silicon, and the main objectives to be achieved during the development of the project.

### 1.1. Problem framing

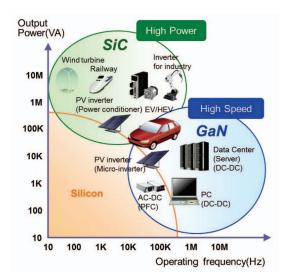

Power electronic devices are replacing silicon semiconductors by wide bandgap semiconductors because of their significantly improved performance. Two typologies of semiconductors are currently used in the industry, Gallium nitrate (GaN) and Silicon Carbide (SiC), both typologies are good choices but the selection of between them depends on the application where they will operate.

Figure 1: Potential applications of GaN and SiC power switching transistors.

The GaN typology is oriented to low power and low voltage applications, while SiC is oriented to high power and high voltage applications. Moreover, the frequency range of GaN devices is much higher due to their high electron mobility compared to SiC, which can reach up to 300 kHz. Currently GaN devices tend to be smaller than SiC, and their manufacturers are improving their performance to meet high power and high voltage applications.

This thesis focuses on the use of silicon carbide power semiconductors and their remarkable improvement in comparison to silicon (Si) based homologues. The SiC type is capable of blocking higher voltages, operating at higher junction temperatures, and obtaining lower switching and conduction losses. In addition, the frequencies achievable by SiC switches sufficiently fulfil the requirements of motor drive or grid-connected applications. On the other hand, given their high-power density and high frequency, they present problems of electromagnetic interference and crosstalk, which must be controlled and treated.

| Properties                                                      | Si      | 4H-SiC    | GaN       |

|-----------------------------------------------------------------|---------|-----------|-----------|

| Crystal Structure                                               | Diamond | Hexagonal | Hexagonal |

| Energy Gap : E <sub>G</sub> (eV)                                | 1.12    | 3.26      | 3.5       |

| Electron Mobility : $\mu_n (cm^2/Vs)$                           | 1400    | 900       | 1250      |

| Hole Mobility : $\mu_{p}$ (cm <sup>2</sup> /Vs)                 | 600     | 100       | 200       |

| Breakdown Field : <i>E</i> <sub>B</sub> (V/cm) X10 <sup>6</sup> | 0.3     | 3         | 3         |

| Thermal Conductivity (W/cm°C)                                   | 1.5     | 4.9       | 1.3       |

| Saturation Drift Velocity : $v_{s}$ (cm/s) X10 <sup>7</sup>     | 1       | 2.7       | 2.7       |

| Relative Dielectric Constamt : $\epsilon_{s}$                   | 11.8    | 9.7       | 9.5       |

Figure 2: Comparison of some electrical and material properties of Si, 4H-SiC and GaN for power device applications.

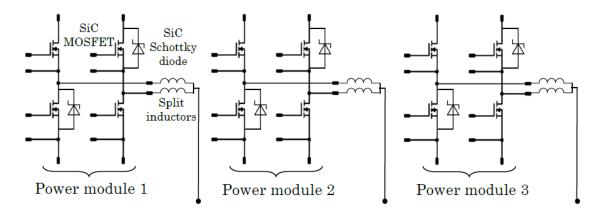

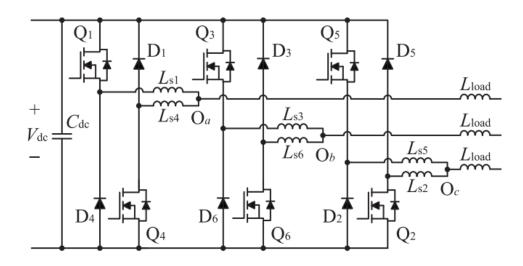

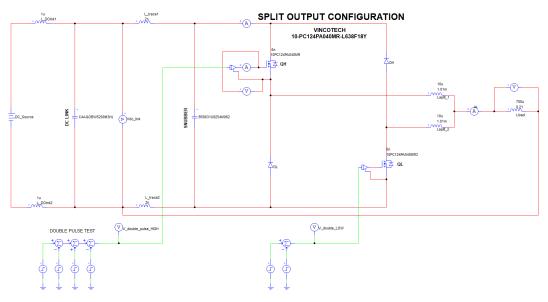

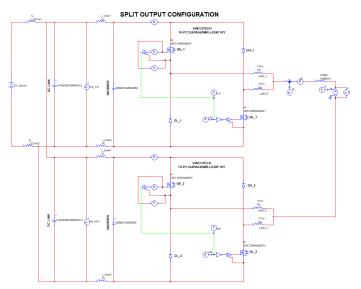

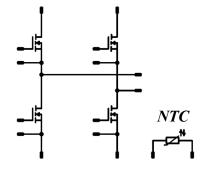

The power converter to be analysed and improved is an experimental six-phase split output inverter that mounts 3 Vincotech modules with SiC MOSFETs and incorporates Schottky SiC diodes in antiparallel. This inverter topology is used to provide the necessary flexibility to test different inverter configurations with and without split output in order to show the improvements and drawbacks when a three-phase load is connected.

Figure 3: Six-phase Split-Output configuration with SiC Schottky diodes in antiparallel.

### **1.2.** Main Purpose

The SiC power inverter with split output mounted in the lab was not operating correctly during the tests realized in the previous thesis project of Giorgio Ferrara. The reasons for this were a bad design of the printed circuit boards which was not designed for high power applications with SiC MOSFETs, a failure on the mechanical assembly between the board connectors and the lack of Snubber capacitors to avoid high voltage peaks which can cause device failures.

In order to improve this behaviour, the analysis and improvement of the inverter is carried out by monitoring the following points during the development of the thesis:

- Analysis and calculations of the inverter's DC bus to verify that it is correctly dimensioned. Proposal to replace the current bus DC with electrolytic capacitors, which reduce the efficiency of the system, with a MKP capacitor bus DC that provides higher performance and also reduces the system's dimensions.

- Study on the integration of Snubber capacitors in order to reduce the voltage peaks between the source-drain terminals of the MOSFETs. Different calculations are performed and the simulation software PSIM is used to validate the results and see the improvements in the inverter performance.

- Comparison between the current converter and the converter with the proposed changes using the tests realized in the previous thesis and the new PSIM simulations.

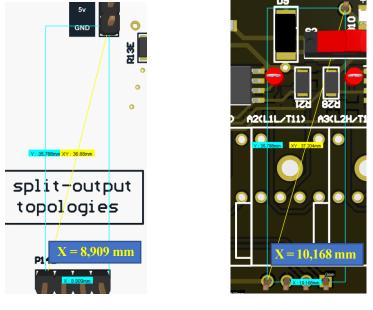

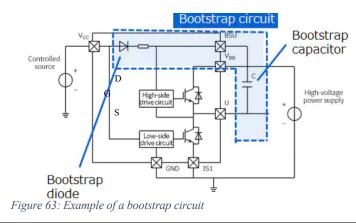

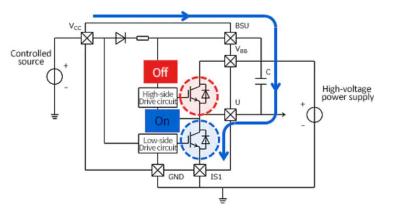

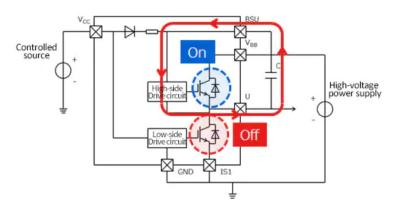

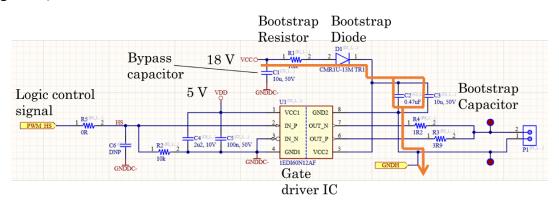

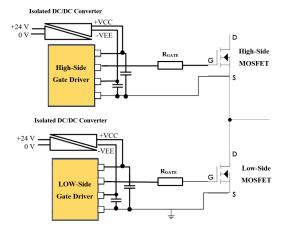

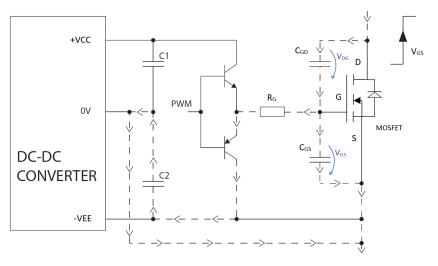

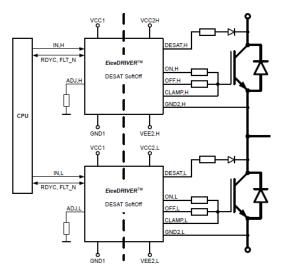

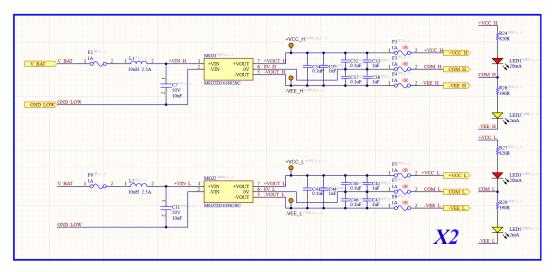

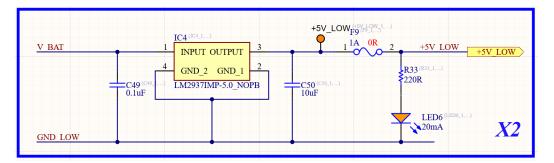

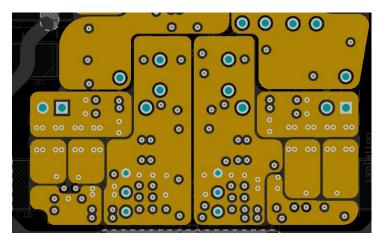

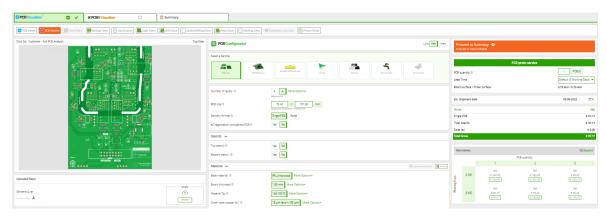

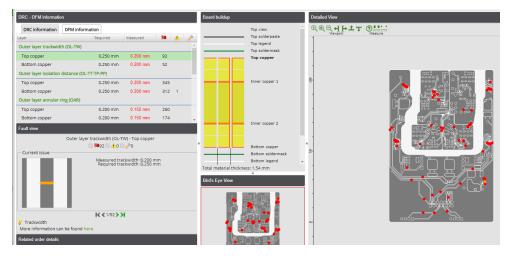

- Redesign of the gate driver board from a 2-layer to a 4-layer board. Bootstrap circuit is replaced by the integration of isolated gate drivers with multiple functionalities to provide protection and including their respective DCDC converters with positive and negative outputs. The traces were redesigned using polygons in order to decrease the parasitic inductances of the traces, avoid high temperatures and reduce electromagnetic interference (EMI) and the crosstalk effect. The position of the connectors was changed to ensure the correct mechanical assembly between the power board and the gate driver board.

- A checking of the new designed board is carried out using Eurocircuit's PCB Checker tool in order to apply changes in the design of the PCB to reduce the level of technology required to manufacture it and also to reduce its cost.

- Analysis of the cost of manufacturing and assembling all the possible changes, including the changes already made and the proposed ones.

# 2. SIC BASED INVERTER WITH SPLIT OUTPUT TOPOLOGY

As previously discussed, silicon carbide (SiC) power devices have great advantages in terms of material properties and are commonly used in power electronic systems to achieve high power density and high efficiency. Because of the low switching and conduction losses of these devices, they can reach frequencies of the order of kHz. These high frequencies can be interesting in applications where it is important to obtain a good wave quality and minimize THD (Total Harmonic Distortion). In other applications, such as renewable energies, where the aim is to minimize converter losses, their use is also very common.

However, SiC MOSFETs have some limitations when used in a standard half-bridge topology at high switching frequencies or when low switching and conduction losses are sought.

### 2.1. Half-bridge topology limitations

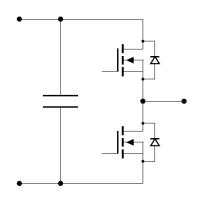

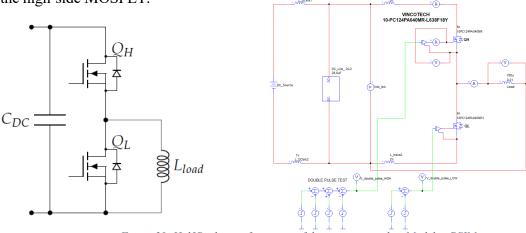

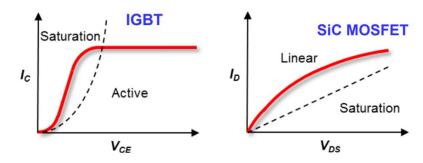

The standard half-bridge configuration is a classic configuration used in many power electronics applications for the realization of DC-DC converters or DC-AC inverters. This configuration is formed from two switches connected in series where, in case of using MOSFET devices, the drain of the low side switch is connected to the source of the high side switch (Figure 4).

Figure 4: Standard half-bridge topology.

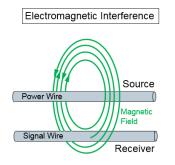

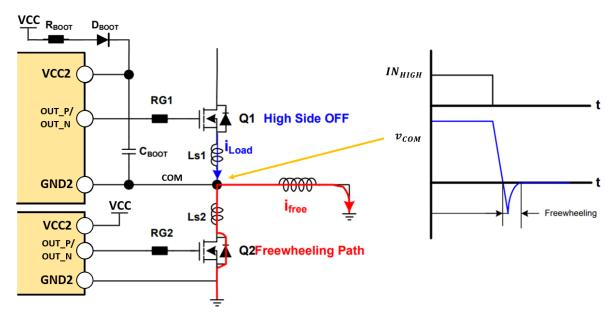

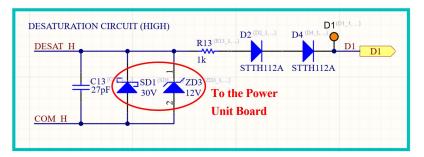

The main limitations of the standard half-bridge topology are switching and conduction losses due to the poor performance of the SiC MOSFET body diode, EMI problems at high frequencies and the crosstalk effect due to the high switching speed (dv/dt).

#### Poor-performing Body Diode

The body diode of SiC MOSFETs produces a high forward voltage drop during conduction and also does not have a very good reverse recovery charge. These poor characteristics result in high losses when using this diode as a freewheeling path: high conduction losses due to the high forward voltage drop and increased switching losses at turn-on caused by the reverse recovery charge.

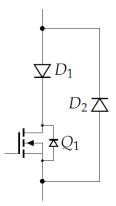

To overcome these losses, the manufacturers of this type of devices suggest the use of external diodes connected in antiparallel with the SiC MOSFET. That is why SiC Schottky diodes, which have superior characteristics than the body diode, have a great relevance in this function. However, this solution of connecting diodes in antiparallel has some drawbacks: the addition of an external diode increases the total junction output capacitance (higher switching losses) and also there is no guarantee that the body diode will not conduct the freewheeling current for example in switching transients due to the effect of some leakage inductance.

A typical application to avoid conduction of the body diode of the SiC MOSFET is shown in Figure 5, where two external diodes are used: A D1 diode connected in series and a D2 diode connected in antiparallel.

Figure 5: Typical solution to avoid the conduction of the MOSFET body by using two external diodes

This presented solution effectively avoids the body diode conduction of the SiC MOSFET, but, due to having more semiconductor devices, it increases the cost, complexity and area of the system.

#### <u>Electromagnetic Interference (EMI)</u>

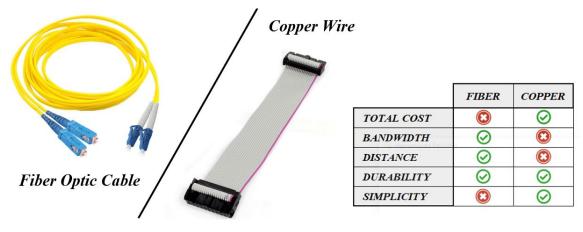

One of the main limitations of SiC MOSFETs devices is the electromagnetic interference (EMI) that is caused due to the high switching speed (dv/dt) of the devices resulting in high frequency currents (di/dt) across the parasitic components of the converter. These high frequency currents produce electromagnetic interference which affects to other devices connected to the converter generating problems and system failures.

#### Crosstalk Effect

The high switching speed of SiC MOSFETs which cause high dv/dt can result in the crosstalk effect. This effect produces the interaction in the turn-on between MOSFETs of the same leg: when one MOSFET turns on, spurious gate voltages can be induced in the other MOSFET causing it to turn on as well. This misfire results in a simultaneous conduction of both switches that leads to a failure of the converter.

In order to avoid the conduction of the MOSFET body diode, decrease EMI and crosstalk problems, the topology of six-phase SiC MOSFET based converter with split output and external SiC Schottky diodes is used.

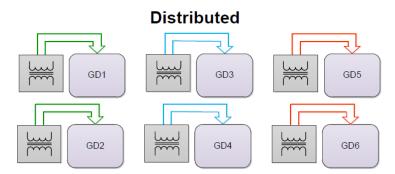

Figure 6: Six-phase split output inverter

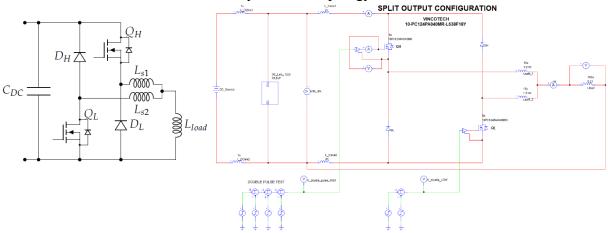

### 2.2. Analysis of the split output converter

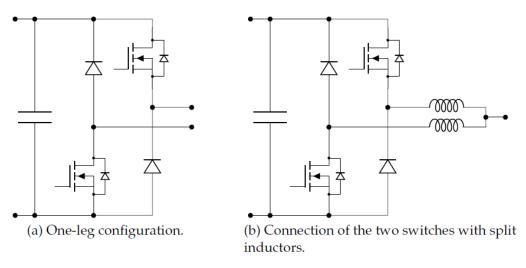

The split output topology for a half-bridge converter is shown in Figure 7.a. Instead of connecting the two MOSFETs directly in series, they are divided into two different legs by adding two diodes which results in two output terminals. On the other hand, Figure 7.b shows how to obtain a single output terminal from two inductors called split inductors connecting the two MOSFETs on the high and low side of the converter.

Figure 7: Half-bridge converter with split output topology

In this topology it is possible to decouple the two MOSFETs by using split inductors and provide a path for the freewheeling current through the external diodes in order to improve the converter performance.

#### 2.2.1. Operation of Split Output Converter

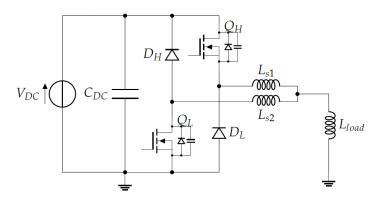

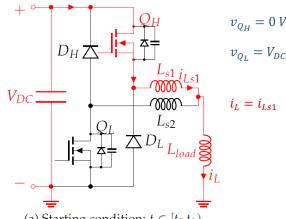

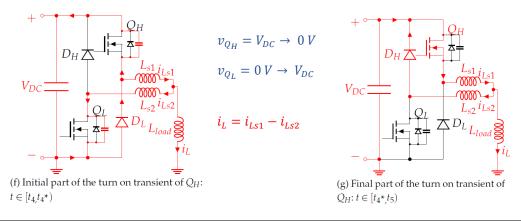

To analyse the operation and the current flow in a half-bridge split output converter, the circuit in Figure 8 is considered. This circuit consists of a high value inductance connected to the output terminal  $L_{load}$ , two split inductors that decouple the MOSFETs  $L_{s1}$ ,  $L_{s2}$ , two ideal external diodes for driving the freewheeling currents  $D_{H}$ ,  $D_{L}$  and the MOSFETs transistors with their respective output capacitances  $Q_{H}$ ,  $Q_{L}$ . Also, the converter is supplied by a constant  $V_{DC}$  voltage source, which is parallel-connected to a DC-link capacitor  $C_{DC}$ .

Figure 8: Half-bridge split output converter with load

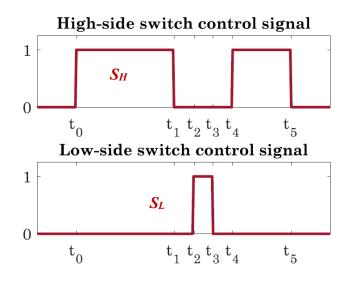

In order to perform the analysis of the different converter states, the control signals  $S_H$  and  $S_L$  that drive the switching of the high side MOSFET ( $Q_H$ ) and low side MOSFET ( $Q_L$ ) are taken into account following the typical form of a double pulse test (DPT), a technique commonly used to validate the transient responses of power converters where is interesting to highlight the current flow in the turn-on and turn-off transitions of the switches, and also during the dead times, when both the transistors are off.

Figure 9: Control signals applied to the SiC MOSFETs (Double Pulse Test, DPT)

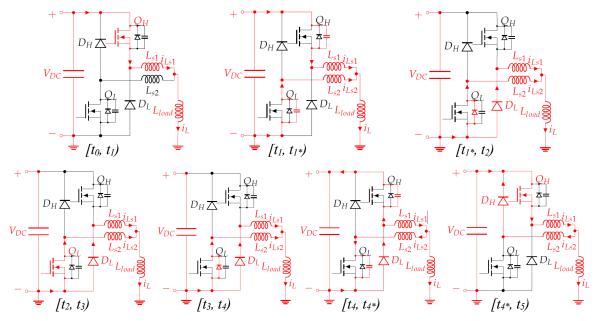

The double pulse test gives seven possible different states shown in the Figure 10, which are analysed in more detail to know the current flow during transients of the converter. During switch-off and switch-on transients of the switches the states are subdivided due to the charging and discharging of the output capacitors of the MOSFETs, these intermediate states are shown with an asterisk \*.

Figure 10: States of a Half-bridge split output converter in a Double Pulse Test (DPT)

#### Initial State [t<sub>0</sub>; t<sub>1</sub>]

The initial state occurs between instants  $t_0$  and  $t_1$ . In this state the upper switch  $Q_H$  is on while the lower switch Q<sub>L</sub> is off blocking the DC-Link voltage. Current flows from the input to the output load through the high side MOSFET and the split inductance  $L_{SI}$ . This current increases linearly until reach the desired output current.

(a) Starting condition:  $t \in [t_0, t_1)$

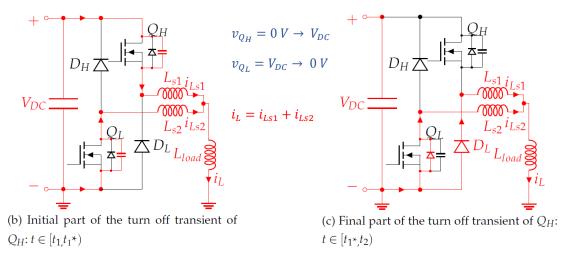

#### Turn off transient of QH [t1; t2]

At instant  $t = t_1$ , the control signal  $S_H$  of the high side MOSFET changes to logic 0 state initiating the turn-off transient of the MOSFET  $Q_H$ . At the beginning of the transient the output capacitance of the MOSFET  $Q_H$  which is initially discharged starts to charge through the split inductance  $L_{SI}$ and the switch voltage goes from 0 V to  $V_{DC}$ . At the same time, the output capacitance of the MOSFET  $Q_L$  which was initially charged begins to discharge through the split inductance  $L_{S2}$ and the switch voltage goes from  $V_{DC}$  to O V. It should be noted that due to the small output capacitances of the MOSFETs, the charge and discharge transients are very fast.

When the processes of charging and discharging of the output capacitances of the MOSFETs are completed, the  $D_L$  diode begins to conduct the  $i_{Ls1}$  current, while the  $i_{Ls2}$  current is commutated to the low-side MOSFET QL body diode.

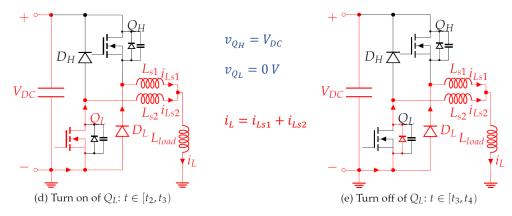

#### Turn on and turn off of OL [t2; t4)

At instant  $t = t_2$ , the control signal of the low side switch  $S_L$  changes to the high logic state 1, so the MOSFET  $Q_L$  starts to conduct with a soft switching of the current  $i_{Ls2}$ .

At instant  $t = t_3$ , the control signal of the low-side switch  $S_L$  changes to logic low state 0, so the MOSFET  $Q_L$  starts to turn off, and a soft-switching of current  $i_{Ls2}$  starts again, which the current returns to flow through the body diode of the MOSFET.

In both states, the output  $i_L$  current decreases linearly due to the application of the 0 voltage at the split inductance terminals.

#### Turn on transient of OH [t3; t4]

In this state the high side switch control signal  $S_H$  at  $t = t_4$  changes to logic 1 state initiating the turn-on transient of the MOSFET  $Q_H$ . The output capacitance of the MOSFET  $Q_H$  which initially had a voltage  $V_{DC}$  begins to discharge, and the switch voltage goes from  $V_{DC}$  to  $\theta V$ . Similarly, the output capacitance of the MOSFET  $Q_L$  which was initially at  $\theta V$  starts to charge by reversing the current iLs2 and the switch voltage goes from  $\theta V_{DC}$ .

When the charge/discharge processes of the output capacitances of the MOSFETs are completed, the  $D_L$  diode stops conducting and a soft switching of the current  $i_{LSI}$  though the MOSFET  $Q_H$  is realized. Otherwise, the diode  $D_H$  starts conducting with a soft switching of the current  $i_{LS2}$  until the energy stored in the split inductance  $L_{S2}$  is dissipated, returning to the initial state in Figure 10.a. If this dissipation does not occur due to the application of another  $S_H$  signal pulse for the MOSFET  $Q_H$  turn-off, the converter starts to operate in the state of Figure 10.b.

#### Ref: SiC\_Inv\_mAB22

#### 2.2.2. Benefits and drawbacks of the Split Output Converter

The development of a new converter with the split output topology implies a series of benefits and drawbacks which are shown below (these benefits and drawbacks are studied in more depth in Giorgio Ferrara's thesis).

#### <u>Benefits:</u>

- © The split output topology provides a path for freewheeling current through the external SiC Schottky diodes, avoiding the conduction of the MOSFET body diode and increasing the efficiency of the converter.

- Decoupling of the high and low side MOSFET switches by the split inductances, mitigating crosstalk effects and allowing the achievement of higher switching frequencies of the converter.

- © Reduced generation of electromagnetic interference (EMI) thanks to the incorporation of split inductances which limit the high-frequency harmonic components of the output.

#### Drawbacks:

- So The split inductors support high current pulses and large voltage drops produced by the switching of the MOSFET  $Q_H$ , furthermore, when the split inductance decreases, the amplitude of the current pulses becomes larger, and the width of the voltage pulses becomes smaller  $\left(v_L = L \cdot \frac{di}{dt}\right)$ . Due to this, large conduction losses are generated in the inductors at high switching frequencies.

- Oue to the decoupling of the MOSFET switches, the synchronous rectification disappears, leading to a negative influence on the converter's conduction losses.

- When the converter operates in continuous conduction mode, the overall efficiency of the converter with split inductors can be lower than without them. This is because the conduction losses generated by the current pulses and voltage peaks in the split inductors can overcome the reduction in switching losses. The loss efficiency is increased at higher switching frequencies.

# 3. ANALYSIS AND OPTIMIZATION OF THE HARDWARE DESIGN

In this section, the previous design of the split output power converter is presented, identifying its possible failures, and proposing new improvement alternatives in order to optimize the converter's performance.

### 3.1. Previous Hardware Design

The previous split output converter was designed to offer flexible operating performance to test the silicon carbide technology for different circuit configurations. The design conditions followed for the inverter hardware design were as follows:

| Maximum DC voltage:  | $V_{DC,máx} = 1000 V$                                                                        |

|----------------------|----------------------------------------------------------------------------------------------|

| Rated DC voltage:    | $V_{DC,N} = 700 V$                                                                           |

| Rated current:       | $I_N = 32 A$                                                                                 |

| Switching frequency: | $f_{sw} > 10 \ kHz \ (max \ 100 \ kHz)$                                                      |

| Flexible topology:   | Allowing for different hardware configurations, including the ones featuring a split output. |

|                      | Rated DC voltage:<br>Rated current:<br>Switching frequency:                                  |

The specifications for voltage and current of the system were chosen based on testing for highperformance DC-AC motor drive and AC-DC grid connection applications.

A maximum switching frequency of 100 kHz was set according to the characteristics of the silicon carbide-based semiconductors and the hardware control system's computational power.

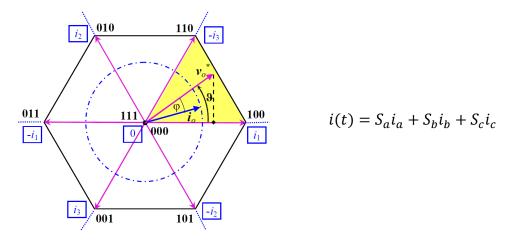

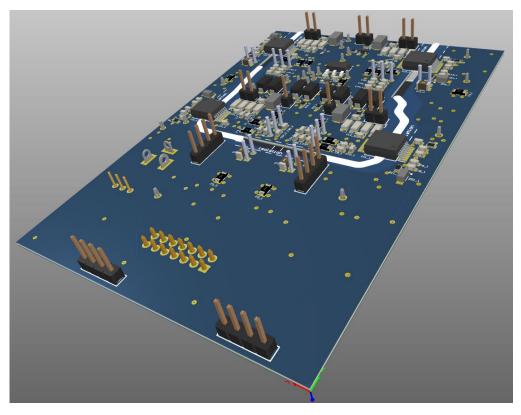

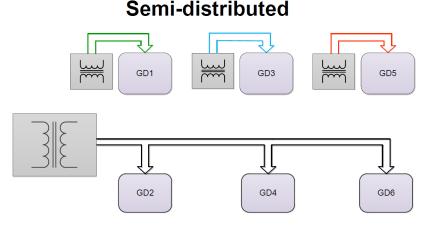

Finally, the flexibility of the converter allows to test it in different load scenarios and also evaluate and compare the possible improvements when using or not using the split output topology. The six-phase SiC MOSFET based converter with split output designed by Giorgio Ferrara is shown in the figure. This system shows three different units:

(1.) The power unit

$\widehat{2}$ .) The gate drive unit

Figure 11: Split Output SiC-Based Power Converter

Additionally, a LauchPad F28069M Piccolo is used to control the inverter, which executes the main switching algorithm of the MOSFETs, monitors all the control signals and acts when it is necessary to ensure that the system is operating properly and safely.

#### <u>Power Unit</u>

The power unit is composed by the DC-link capacitor bank, the three Vincotech MOSFET SiC modules connected by press-fit technology and the different systems for measuring and signal processing of current and voltage.

#### <u>Gate Drive Unit</u>

The gate drive unit is responsible for switching of the different MOSFETs by the PWM signals that it receives from the control unit with optical fiber technology. Also provides the connection for other signals (temperature, current, voltage...) to the control unit and makes the isolation between the low voltage part (control unit) and the high voltage part (power unit).

#### <u>Split Inductor Unit</u>

Consists of the inductors to realize the split output topology, also providing the connections to the power unit.

### **3.2.** Analysis of the Power Unit

In order to make the appropriate improvements in the converter, the first step is to identify the current malfunctions. For this purpose, an exhaustive analysis of the power unit in the previous design is carried out, including the study of new design methods for the converter hardware, which result in different proposals that are verified by the use of calculations and simulations.

The list of the different points that were followed to improve the performance of the power unit of the converter are shown below.

#### DC-Link

- Calculations to verify the correct sizing of the DC-Link capacitance of the inverter.

- Selection of new DC-Link capacitor bank with MKP technology to optimise space, cost, and performance.

#### **Snubber Capacitors**

- Study of the integration of Snubber capacitors together with SiC MOSFET devices in order to reduce the voltage peaks caused by the parasitic inductances of the hardware design and the fast current pulses (di/dt).

- Simulation using PSIM software and comparison between the new proposal hardware with snubber capacitor and the transient response captured in previous tests of the existing inverter.

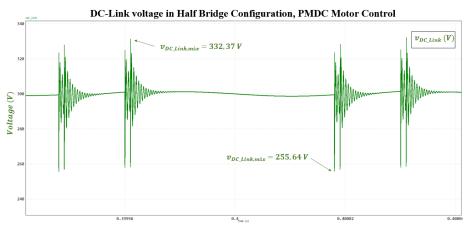

#### **3.2.1.** DC-Link

It is necessary a properly dimensioning of the DC-Link capacitors for the power inverter to comply with the established requirements, trying to ensure that its occupied volume is the minimum possible.

The capacitor bank of the DC-Link mainly performs two functions:

- <u>Provides a low impedance path for high frequency currents.</u> When the frequency goes up, the stray inductances of the battery and cables cause the impedance increase  $(X_L = j\omega L)$ . Inversely, the impedance of the DC-Link capacitor bank decreases according to the equation  $X_C = \frac{1}{j\omega C}$ , so becomes the preferred path for high-frequency AC Ripple Current.

- <u>Stiffen the DC bus.</u> The DC-Link capacitors decouple the effects of parasitic inductance from the DC voltage source to the power bridge. Voltage ripple on the DC bus manifests as ripple in the phase current of the inverter, which is undesirable and must be prevented by having a rigid DC bus. For the dimensioning of the capacitors, it is necessary to specify the maximum permissible voltage ripple on the DC bus.

After describing the functionalities of the DC-Link, the dimensioning is determined based on the analysis of four parameters that it must satisfy.

#### 1. DC Voltage Rating:

The DC voltage rating of the capacitor should be rated based on the average maximum bus voltage multiply by a safety factor of 10%.

$$V_{cap} > V_{DC,N} \cdot 1,1$$

$V_{cap} > 700 V \cdot 1,1 = 770 V$

#### 2. <u>Ripple Current Rating:</u>

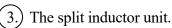

An analytical method for calculating ripple current based on inverters which use Space Vector Modulation (SVM) is used for dimensioning of the DC-Link capacitor bank. The ripple current refers to the AC current that the capacitors must supply to the power bridges and the motor.

The inverter input current i(t) can be expressed by the following three components:

$$i(t) = I_{dc} + \tilde{\iota}(t) + \Delta i(t)$$

Being  $I_{dc}$  the average dc component,  $\tilde{\iota}(t)$  the alternating double fundamental frequency component and  $\Delta i(t)$  the switching frequency component.

In a system with balanced load the component  $\tilde{\iota}(t)$  is zero and the inverter input current only contains of average dc current and high frequency harmonics around the switching frequency and its multiplies.

$$i(t) = I_{dc} + \Delta i(t)$$

Balanced Load

The input current i(t) is the sum of three bridge leg current and is dependent on the inverter switching state. Considering three switching leg states  $S_k = [0,1]$ , k = 1,2,3, the input current of inverter bridge leg can be expressed as:

Figure 12: Space vector diagram of a three-phase inverter output voltage.

The inverter phase currents over the switching period for the worst case correspond to three reference signals with 120° phase shift and whose amplitude is the maximum phase current given in the system specifications ( $I_{ph,max} = I_N = 32 A$ ).

$$i_{a} = I_{ph,max} \cdot \sin(\omega t)$$

$$i_{b} = I_{ph,max} \cdot \sin\left(\omega t - \frac{2}{3}\pi\right)$$

$$i_{c} = I_{ph,max} \cdot \sin\left(\omega t + \frac{2}{3}\pi\right)$$

To calculate the average bus current  $I_{dc}$ , the average value of the input current i(t) in a switching period is calculated.

$$I_{DC} = \frac{1}{T_e} \int_0^{T_e} i(t) \cdot dt$$

By regrouping the above equations, the value of switching frequency input current component is obtained.

$$\Delta i(t) = i(t) - I_{dc} = i(t) - \frac{1}{T_e} \int_0^{T_e} i(t) \cdot dt$$

It is assumed that the battery supplies only DC current and the capacitor must supply all AC current because as the frequency goes up, the impedance of the battery increases while the impedance of the capacitor decreases. This includes the AC components of the fundamental, harmonics and current ripple at the switching frequency. By calculating the RMS component of the AC current, it is possible to obtain the peak current value to be supplied by the capacitor bank of the DC-Link.

$$I_{DC\_link,RMS} = \Delta i_{RMS}(t) = \sqrt{\frac{1}{T_e} \int_0^{T_e} (i(t) - I_{DC})^2 \cdot dt}$$

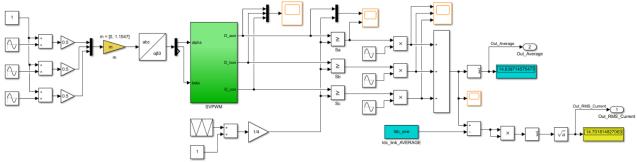

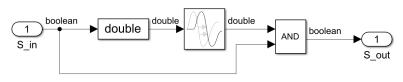

The current required by the capacitor bank due to the use of SVM modulation depends on the phase current, the modulation index, and the power factor. Assuming a unity power factor, the RMS current is plotted for the entire modulation index range [0; 1.1547] using the SIMULINK simulation tool in MATLAB.

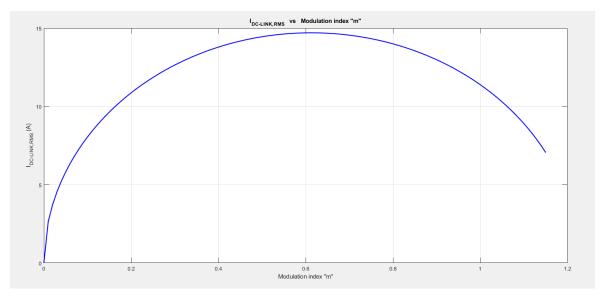

Figure 13: Simulation of the RMS current of the DC-Link in a three-phase inverter with SVM for a PM Motor

After the simulation is completed, the DC-Link capacitor bank has a maximum RMS current to be supplied of 14,7019 A for a modulation index of m = 0,6126.

Figure 14: DC-Link RMS Current vs Index Modulation in a three-phase inverter with SVM for a PM Motor

$I_{DC_{link},RMS}(m = 0,6126) = 14,7019 A$

Another way to calculate the value of the maximum RMS current for PM motors using an approximate but simpler calculation method is to multiply the maximum RMS phase current by a factor of 0,65.

$$I_{DC\_link,RMS}' = 0,65 \cdot I_{ph,RMS} = 0,65 \cdot \frac{32 A}{\sqrt{2}} = 14,7078 A$$

The maximum RMS current of the DC-Link capacitor bank is decisive to ensure the lifetime of the capacitors. The ripple current rating of a capacitor is derived from its temperature and depends on the ESR and thermal resistance. When a capacitor is exposed to high frequency charge and discharge cycles, the conductors heat up, which causes the internal temperature of the capacitor to increase. It is necessary to limit this internal temperature of the capacitor in order to prevent its deterioration, for this reason manufacturers specify the maximum value of the RMS ripple current at an ambient temperature to ensure its proper operation.

For the selection of the capacitor bank in a conservative way, a safety factor of 10% is applied to the ripple current rating.

$I_{cap,RMS} > 1,1 \cdot 14,7019 = 16,172 A$

#### 3. <u>Ripple Voltage Rating:</u>

The DC Link capacitor smooth DC voltage fluctuations and stiffen the DC bus. This is important because any voltage ripple on the DC bus shows up as current ripple in the phase currents, and that leads to torque ripple.

Assuming that the current flowing through the capacitors in a switching period remains constant, the current-voltage relationship of a capacitor over a one switching period is as follows.

$$i_{cap} = C \cdot \frac{d\nu}{dt} \rightarrow i_{cap} = C \cdot \frac{\Delta\nu}{\Delta t} \rightarrow C > \frac{I_{cap,MAX}}{\Delta\nu \cdot f_{sw,min}} = \frac{\sqrt{2} \cdot I_{cap,RMS\_MAX}}{\Delta\nu \cdot f_{sw,min}}$$

The capacitance is inversely proportional to switching frequency. When the switching frequency increase, the capacitance of the DC-Link bus required decreases. Also, the capacitor volume is proportional to the capacitance, so by increasing the switching frequency, higher power densities can be achieved. This is one of the reasons why SiC and GaN-based converters can achieve higher power densities than IGBT-based converters.

For the design of the capacitor bank of the DC-Link ,the maximum allowable voltage ripple assumed is 3% of the maximum voltage of the DC-Link.

$$C > \frac{\sqrt{2} \cdot 16,172 A}{(1000 V \cdot 0,03) \cdot 10 kHz} = 76,236 uF$$

#### 4. <u>Resonant Frequency Rating:</u>

The capacitor has a frequency at which it is self-resonant by the ESL. Beyond this point, the capacitor behaves as an inductor and does not work correctly. To avoid this, the capacitor must have a resonant frequency 2 times higher than the switching frequency. The maximum switching frequency achievable by the inverter is 100 kHz, higher frequencies make the SiC MOSFET less efficient.

$$f_{cap,Res} > 2 \cdot f_{sw} = 2 \cdot 100 \ kHz = 200 \ kHz$$

In summary, the characteristics to be fulfilled by the DC-Link capacitor bank are shown in the following table (Table 1).

| DC-Link capacitor bank Requirements               |                              |  |

|---------------------------------------------------|------------------------------|--|

| DC Voltage                                        | $V_{DC} > 770 \ V$           |  |

| Ripple Current RMS                                | $I_{RMS} > 16,172 \text{ A}$ |  |

| Capacitance                                       | C > 76,236 uF                |  |

| $Resonant \ Frequency \qquad f_{Res} > 200 \ kHz$ |                              |  |

Table 1: DC-Link capacitor bank Requirements

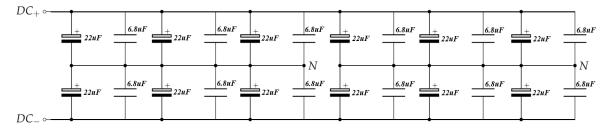

The DC-Link capacitor bus of the laboratory power board consists of two electrolytic capacitors and two ceramic capacitors per leg. The characteristics and connections of the capacitors are shown below.

| Model         | 860241478004                | C4AF7BW4680T3JK             |

|---------------|-----------------------------|-----------------------------|

| Supplier      | Würth Elektronik            | KEMET                       |

| Capacitance   | 22 uF                       | 6.8 uF                      |

| Rated Voltage | 450 V                       | 700 V                       |

| RMS Current   | 0.632 A                     | 18.3 A                      |

| ESR           | $0.7 \ \Omega$              | 2.8 mΩ                      |

| ESL           | 11 nH                       | 10 nH                       |

| fresonance    | -                           | -                           |

| Dielectric    | Polypropylene<br>metallized | Metallized<br>Polypropylene |

| Size          | 25mm x 13 mm<br>(ØD)        | 42 mm x 37 mm x 28<br>mm    |

Table 2: DC-Link capacitors specifications of the laboratory power board design

The two capacitors of each type are connected in series and the two branches are connected by the neutral point N. This configuration results in a total DC-Link capacitance of 86.4 uF

Figure 15: DC-Link capacitor connections from the lab power board design

| $V_{DC\_link} = \min(450 V \cdot 2; 700 V \cdot 2) = 900 V > 770 V$                                                               |                          |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| $I_{RMS,DC\_link} = (0,632 A + 18,3 A) \cdot 6 = 113,592 A > 16,172 A$                                                            |                          |

| $C_{DC_{link}} = \left(\frac{22  uF}{2} + \frac{6.8  uF}{2}\right) \cdot 6 = 86.4  uF > 76,236  uF$                               |                          |

| $Vol_{DC_{link}} = \left(\frac{\pi \cdot 13^2}{4} \cdot 25\right) mm^3 \cdot 12 + (42 \cdot 37 \cdot 28) mm^3 \cdot 12 = 561,964$ | 4 <i>cm</i> <sup>3</sup> |

| $€_{DC_{link}} = 1,73 € \cdot 12 + 7,06 € \cdot 12 = 105,48 €$                                                                    |                          |

The DC-Link capacitor bus meets the system requirements. It is recommended to connect the neutral point "N" of all capacitors in order to avoid voltage unbalance between legs. In addition, the volume occupied by the DC-Link is too high and could be reduced.

The use of film capacitors is highly recommended instead of using electrolytic capacitors due to their higher ripple current capability because of their low ESR and ESL. In addition, the volumetric efficiency is usually much higher when using film capacitors and they have a lifetime of approximately 100,000 hours compared to 10,000 hours for an electrolytic.

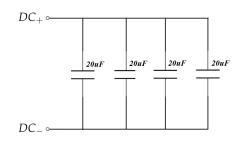

A new proposal of the DC-Link capacitor bus design is made by using only film capacitors in order to meet the system requirements and to optimise the volume and the cost. The capacitors chosen for this design are shown in the Table 3.

| Model            | MKP1848C62090JP4         | C4AQOBW5200M3HJ            |

|------------------|--------------------------|----------------------------|

| Supplier         | Vishay                   | KEMET                      |

| Capacitance      | 20 uF                    | 20 uF                      |

| Rated<br>Voltage | 900 V                    | 900 V                      |

| RMS<br>Current   | 14 A                     | 18.9 A                     |

| ESR              | $5 \mathrm{m}\Omega$     | 4.3 mΩ                     |

| ESL              | 35 nH                    | 13 nH                      |

| fresonance       | 250 kHz                  | -                          |

| Dielectric       | Metallized Polypropylene | Metallized Polypropylene   |

| Size             | 24 mm x 44 mm x 42 mm    | 24 mm x 44 mm x 41,5<br>mm |

Table 3: New proposal DC-Link capacitors specifications for the power board design

The capacitors meet the voltage requirements of the DC-Link, so their connection would be done by interconnecting 4 in parallel to reach a resulting capacitance of 80 uF.

Figure 16: New proposal DC-Link capacitors connections for the power board design

Considering the two capacitor models, it was decided to choose the C4AQOBW5200M3HJ from KEMET, which have better ESR, ESL and RMS peak current performance and are also cheaper in terms of market price.

$V_{DC\_link} = 900 V > 770 V$   $I_{RMS,DC\_link} = 18,9 A \cdot 4 = 75,6 A > 16,172 A$   $C_{DC_{link}} = 20 uF \cdot 4 = 80 uF > 76,236 uF$   $Vol_{DC_{link}} = (24 \cdot 44 \cdot 41,5)mm^3 \cdot 4 = 175,296 cm^3$   $\notin_{DC_{link}} = 6,64 \notin \cdot 4 = 26,56 \notin$

The new DC-Link capacitor bank meets the necessary requirements by achieving a size reduction of 68.80 % and a price reduction of 74.82 % using the MKP technology.

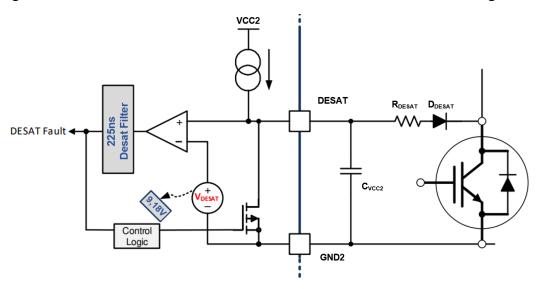

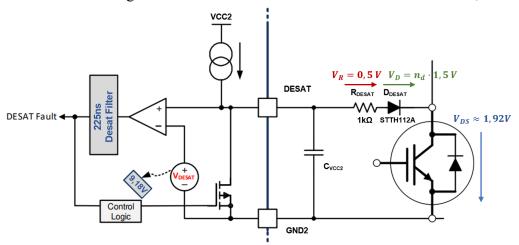

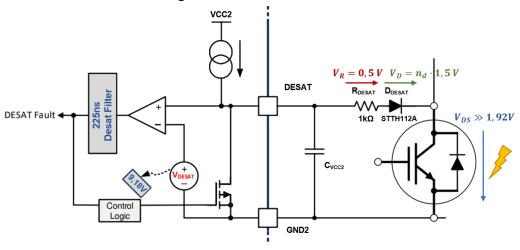

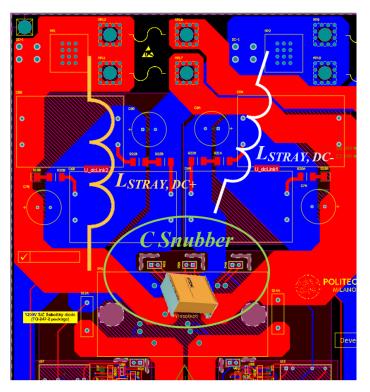

#### 3.2.2. Snubber Capacitors

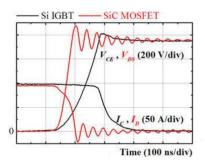

The use of SiC MOSFETs in power applications where fast and efficient switching is required leads to high voltage peaks due to the combination of the high dv/dt and di/dt with the stray inductances of the modules and the surrounding circuit.

Figure 17: Comparison of voltage and current transients during switching of an Si IGBT and a SiC MOSFET

When the MOSFET turns on, current stores energy in the stray inductance of the wire on the PCB layout. This stored energy resonates with the parasitic capacitance of the MOSFET producing a surge current that follows the current ring path illustrated in Figure 18.

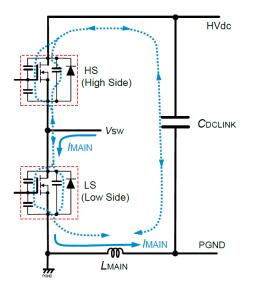

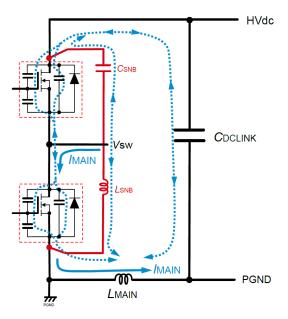

Figure 18: Current path when turn-off surge occurs

In a half-bridge typology when *LS* is turned on, the current  $I_{MAIN}$  flows from  $V_{SW}$  through the stray inductance  $L_{MAIN}$ . When *LS* is turned off,  $I_{MAIN}$  flows through the loop formed by  $L_{MAIN}$ ,  $C_{DCLINK}$  and parasitic capacitance of the *HS* and *LS* switches. During the turn-off of *LS*, a surge voltage occurs at the Drain-Source terminals of *LS* due to the resonance phenomenon between the  $L_{MAIN}$  inductance and parasitic capacitance of the *Coss* MOSFET ( $C_{DS}+C_{DG}$ ).

The maximum voltage  $V_{DS\_SURGE}$  is calculated from the following equation.

$$V_{\text{DS}\_\text{SURGE}} = \frac{V_A * e^{-(a/\omega)[\tan^{-1}(a/\omega) + \Phi]}}{1 + (a/\omega)^2} + V_{\text{HVDC}}$$

Where:

$$V_{A} = \sqrt{V_{HVDC}^{2} + (a/\omega)^{2} * \left(2 * R_{OFF} * I_{MAIN} - V_{HVDC}\right)^{2}}$$

$$\Phi = tan^{-1} \frac{V_{HVDC}}{(a/\omega) * (2 * R_{OFF} * I_{MAIN} - V_{HVDC})}$$

$$a = \frac{1}{2 * R_{OFF} * C_{OSS}}$$

$$\omega_{SURGE} = \frac{1}{\sqrt{L_{MAIN} * C_{OSS}}} * \sqrt{1 - \left(\frac{\sqrt{L_{MAIN}/C_{OSS}}}{2R_{OFF}}\right)^{2}}$$

$\begin{cases} V_{HVDC} = \text{Voltage applied on the DC-Link} \\ I_{MAIN} = \text{RMS current at the output} \\ R_{OFF} = \text{Resistance in the branch when a transistor turns off} \\ C_{oss} = \text{Output parasitic capacitance of the transistor (datasheet).} \\ L_{MAIN} = \text{Stray inductance of the transistor and the branch.} \end{cases}$

Roff is an approximation of the value of the equivalent resistance when the transistor is turned off and Lmain is the sum of the inductances of the DC-Link (Obtained by simulation in 0), the cable that connects the boards, the possible stray inductance of the snubber capacitor and finally, the inductance of the MOSFET itself (oversized in order to have a safety factor).

The calculations for the Vincotech module 10-PC124PA040MR-L638F18Y with a DC-Link bus voltage of 700 V and a maximum current of 32 A give the maximum peak drain-source voltage of the SiC MOSFET.

| Data              |        |  |

|-------------------|--------|--|

| VHVDC             | 700V   |  |

| Coss              | 76 pF  |  |

| L <sub>MAIN</sub> | 16 nH  |  |

| I <sub>MAIN</sub> | 32 A   |  |

| Roff              | 12.5 Ω |  |

$V_{DS\_SURGE} = 805,06 V$

Table 4: Values for the calculation of the peak voltage at the drain-source terminals of the MOSFETs

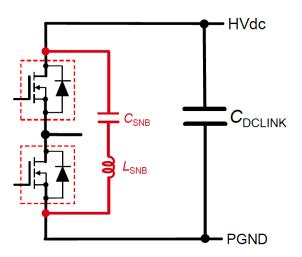

The next step is to introduce a Snubber  $C_{SNB}$  capacitor (Figure 13) to reduce the peak voltage generated by the switching of the MOSFET, which is higher than 800 V and could damage the system. This capacitor has the function of neglecting LMAIN in order to reduce the energy stored in the current ring and consequently decrease the peak voltage generated between the drain and source of the MOSFET.

Figure 19: C Snubber capacitor in a MOSFET leg

The reduction of the peak voltage is due to the fact that  $C_{SNB}$  is placed very close to the switches in order to reduce the inductance involved in the switching path ( $L_{SNB}$ ). The behaviour of the system will be better if the stray inductance is minimised as much as possible. However, this reduction is not always realistic and might make the heat dissipation worse. Instead, placing the snubber capacitor as close as possible to the MOSFET minimize the stray inductance of the circuit. The snubber capacitor  $C_{SNB}$  also absorbs the energy stored by the  $L_{SNB}$  inductance and clamp surge voltage while the MOSFET is turned off. For the calculation of the Snubber capacitor needed to reduce the peak voltage generated in the Drain Source of the MOSFET there are two methods: **<u>passive snubber</u>**, which consists of passive components such as resistor, inductor, capacitor, and diodes; and <u>active snubber</u>, which utilize semiconductor switch.

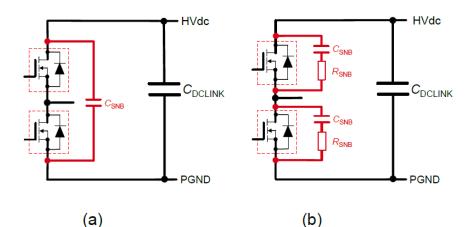

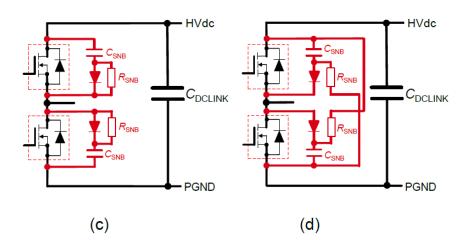

Focusing on passive snubber, four different examples of commonly used Snubber capacitors are shown in the figure.

(a) <u>C snubber</u>, where the capacitor  $C_{SNB}$  is connected in parallel to the MOSFET bridge

(b) <u>*RC snubber*</u>, where the resistor  $R_{SNB}$  and capacitor  $C_{SNB}$  are connected in parallel to each MOSFET

(c) *Discharge RCD snubber*, where a diode is added to RC snubber; and

(d) <u>Non-discharge RCD snubber</u>, where the discharging path is changed from the discharge RCD snubber presented in (c).

*Figure 20: Passive snubber circuits. (a) C snubber, (b) RC snubber, (c) Discharge RCD snubber, (d) Non-discharge RCD snubber*

During the development of the project, it was decided to design the passive snubber C implementation, given its layout simplicity, the reduction in the number of components and because it is more suitable for 2 in 1 module rather than circuit discrete components.

#### C Snubber Design

The C snubber circuit absorbs the energy stored in LMAIN. It is important that the parasitic inductance of the snubber path LSNB has to be smaller than LMAIN. A higher CSNB capacitance of the snubber makes it more efficient because it is not discharged, but it should be noted that the higher the capacitance, the higher the parasitic inductance (ESL) it will present.

Figure 21: C snubber with the IMAIN path

Assuming that all the energy stored in  $L_{MAIN}$  is transferred to the  $C_{SNB}$  capacitance, the following equation is used to select the required electrostatic capacitance of the snubber using the maximum peak voltage  $V_{DC\_SURGE}$ .

$$C_{SNB} > \frac{L_{MAIN} \cdot I_{MAIN}^{2}}{V_{DS\_SURGE}^{2} - V_{HVDC}^{2}}$$

$$C_{SNB} > \frac{16 \, nH \cdot (32 \, A)^{2}}{(805,06 \, V)^{2} - (700 \, V)^{2}} = 0,1036 \, nF$$

For this application, the use of film capacitors has been abandoned in preference to a new generation of ceramic dielectric capacitors, which allow a considerable reduction in volume and weight without losing other features such as rated voltage or low ESL and ESR.

The capacitors selected are B58031U9254M062 from the manufacturer EPCOS / TDK with a CSNB snubber capacitance of 0,25uF. This capacitance is oversized in order to allow the capacitor to withstand the maximum 1000 V of the design conditions and also to allow it conduct higher RMS currents.

| Model            | B58031U9254M062                              |  |  |  |

|------------------|----------------------------------------------|--|--|--|

| Supplier         | EPCOS / TDK                                  |  |  |  |

| Capacitance      | 0,25 uF                                      |  |  |  |

| Rated<br>Voltage | 900 V                                        |  |  |  |

| RMS<br>Current   | 7 A                                          |  |  |  |

| ESR              | 24 mΩ                                        |  |  |  |

| ESL              | 3 nH                                         |  |  |  |

| fresonance       | 9 MHz                                        |  |  |  |

| Dielectric       | Ceramic Lead Lanthanum<br>Zirconate Titanate |  |  |  |

| Size             | 7,14 mm x 7,85 mm x 4 mm                     |  |  |  |

| Price            | 7,30€                                        |  |  |  |

Table 5: C Snubber capacitor specifications

The snubber characteristics meet the system requirements, maintaining a low ESL below LMAIN to decrease the voltage peaks between the Drain-Source terminals of the MOSFETs. The converter will incorporate three snubber capacitors, one for each module, which results in an associated cost of  $21,90 \in$ , that is not a very high value for the improvement in the system performance in terms of durability and reliability.

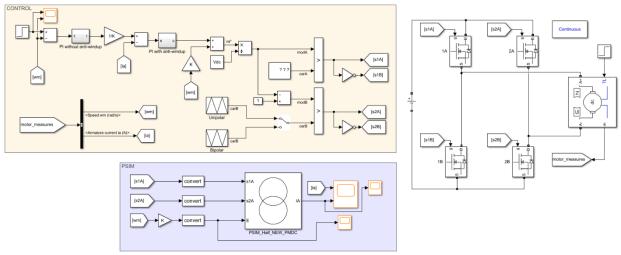

## 3.2.3. PSIM Model of the Power Unit

PSIM is a simulation software that is focused on power electronics. It offers very high simulation speed and at the same time produces high quality simulation results at the system level. Using the PSIM software tool, a simulation model of the laboratory inverter is generated in order to reproduce the behaviour as accurately as possible and to evaluate the improvements from the proposed hardware changes.

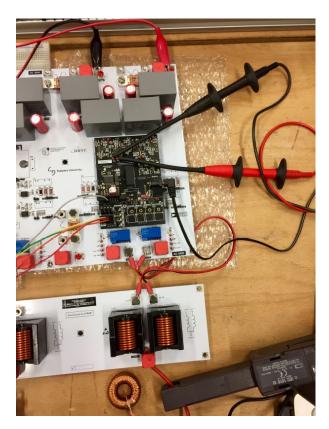

In order to adjust the simulation model to the behaviour in the real conditions, previous tests of the laboratory inverter in different configurations were used. The experimental test setup consisted of the following hardware components:

- Device under test (DUT), which is the power device to be studied, depending on the configuration, it's the lower or upper SiC MOSFET of one leg of the power converter.

- Freewheeling diode, the external SiC Schottky diode that allows the freewheeling current flow, or the internal antiparallel diode of the SiC MOSFET.

- Split Inductors, if required, to study the change in the converter's behaviour

- DC power supply, at a voltage  $V_{DC} = 20V$

- DC-Link, consists of the capacitors assembled on a leg of the designed converter, with a capacitance value  $C_{DC} = 28,8 \ uF$

- Load inductor, a 700 uH inductor with 0.21  $\Omega$  parasitic series resistance

- Gate Driver Circuit, board which is responsible for switching the different MOSFETs according to the signals of the control board

- Control signal generator, a *LaunchPad F28069M Piccolo micro-controller board* is used to generate the control signals with the standard procedure of a *double pulse test (DPT)*

- Oscilloscope, to capture signals of interest.

Figure 22: Test setup used for the Double Pulse Test

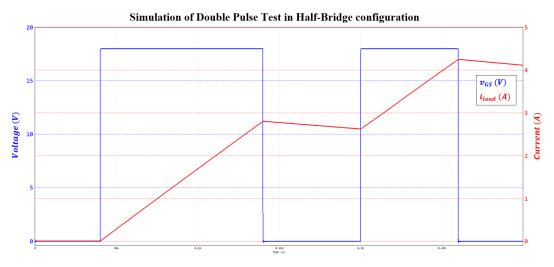

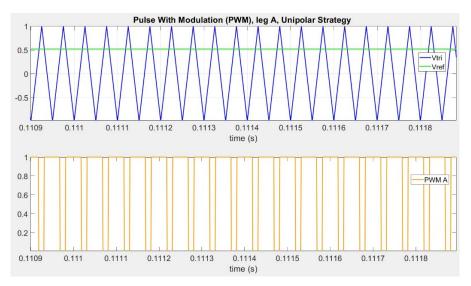

#### **Double Pulse Test**

The test procedure is the same for all experiments done on the inverter hardware of the laboratory using the double pulse test method.

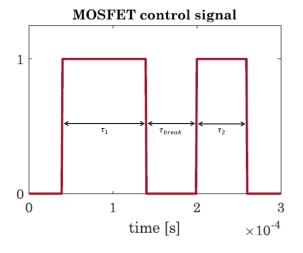

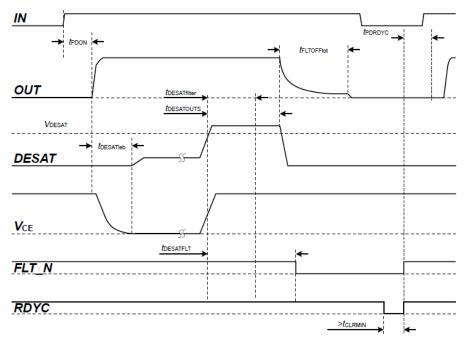

This type of test starts by charging the capacitor bank of the DC-Link to the desired value of 20 V. When this value is reached, the DC-Link is disconnected from the power supply. Furthermore, the control signals of the gates generated by the micro-controller consist of three different periods time periods (**¡Error! No se encuentra el origen de la referencia.**).

Figure 23: Double Pulse Test MOSFET control signal

1. *First Pulse with duration*  $\tau_I$ , defined considering that the voltage overload is governed by the equation

$$v_{load} = L_{load} \cdot \frac{di_{load}}{dt}$$

with initial conditions  $v_{load}(t=0) = V_{dc}$  and  $i_{load}(t=0) = 0$ . Also, it is assumed that the DC-Link voltage during  $\tau_l$  is constant and  $i_{load}(t=\tau_1) = I_{test} = 3A$

$$V_{dc} = L_{load} \cdot \frac{I_{test}}{\tau_1} \rightarrow \tau_1 = L_{load} \cdot \frac{I_{test}}{V_{dc}}$$

$$\tau_1 = 700 \ \mu H \cdot \frac{3 \ A}{20 \ V} \approx \mathbf{100} \ \mu s$$

2. **Pulse break with duration**  $\tau_{break}$ , during this time the switch under test is off, the load is not connected to the DC-Link and the currents flows through the freewheeling diode and the load. The conducting diode has a forward voltage of  $V_F = 1,5 V$  and the current decrease during this period a maximum value of  $\Delta I_{max} = 5\% \cdot I_{test} = 0,15 A$ .

$$\Delta I = \frac{V_F}{L_{load}} \cdot \tau_{break} \rightarrow \tau_{break,max} = \frac{\Delta I_{max} \cdot L_{load}}{V_F}$$

$$\tau_{break,max} = \frac{0.15 \, A \cdot 700 \, \mu}{1.5 \, V} = 70 \, \mu s \, (60 \, \mu s \, limited \, by \, micro)$$

The sampling time of the micro-controller is  $T_s = 1/f_s = 20 \ \mu s$ , as a consequence  $\tau_{break}$  is set to 60  $\mu s$ .

3. Second pulse with duration  $\tau_2$ , this pulse has the role of turning on the switch. During this period, the load is again connected to DC-Link, thus the load current increase. The duration of this pulse has to be selected to remain the current load under acceptable levels. For these reasons,  $\tau_2$  is set to 60  $\mu$ s.

$$\tau_2 = 60 \ \mu s$$

#### **PSIM** schematic

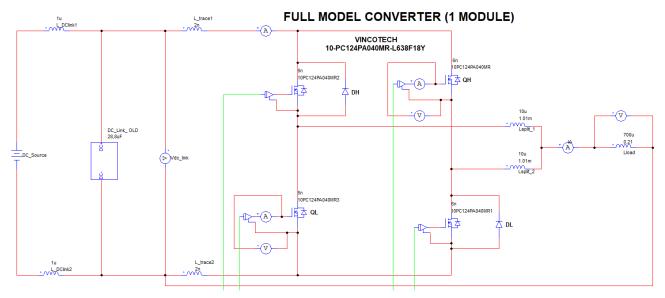

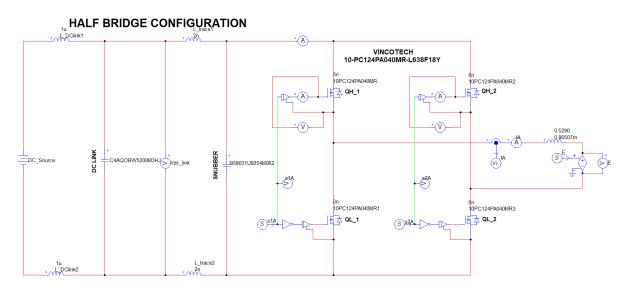

After defining the Double Pulse Test to be used in the simulation of the converter hardware, the schematic design has to be defined in PSIM by introducing the simulation models of the different components in order to emulate the behaviour as accurately as possible. The Figure 24 shows the PSIM schematic of the converter system for a single module in Half-Bridge configuration.

Figure 24: Simulation Model of a single leg of the converter in PSIM

Where the DC-link subcircuit is composed of the following.

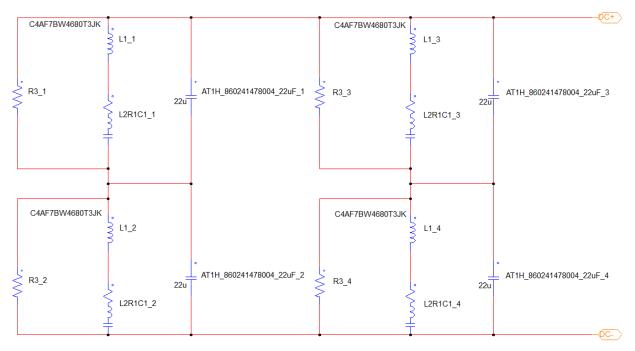

Figure 25: DC-Link Subcircuit of the converter in PSIM

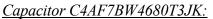

Simulation models of both DC-Link capacitors were made from the manufacturer's information given in the PSPICE files of the components.

Figure 26: C4AF7BW4680T3JK PSPICE parameters and its model in PSIM

#### Capacitor AT1H 860241478004: \* AT1H\_860241478004\_22uF 1 2 "MACROMODEL" SUBCIRCUIT .subckt AT1H\_860241478004\_22uF 1 2 \* Rser 1 3 0.69929 Lser 2 4 1.0635926305E-08 C1 3 4 0.000022 Rpar 3 4 4545454.54545455 .ends AT1H\_860241478004\_22uF PSIM AT1H\_860241478004\_22uF\_1 22u AT1H\_860241478004\_22uF\_1

10.635926305n

Figure 27: AT1H 860241478004 PSPICE parameters and its model in PSIM

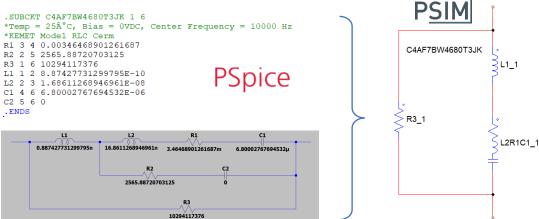

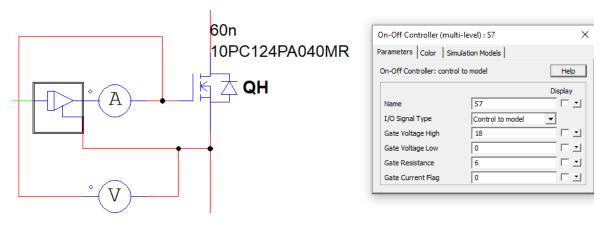

The parameters of the MOSFETs and diodes were set according to their respective datasheet. For the configuration parameters of the SiC MOSFETs and SiC Schottky diodes, level 2 parameters of the PSIM software were used.

| MOSFET: 10PC124PA040N                                                                                                                                                                                                                                                                                          | IR ×        |                       | Diode : DH                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | × |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Parameters Color Simula                                                                                                                                                                                                                                                                                        | tion Models |                       | Parameters Color Simula                                                                                                                                                                                                                       | tion Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| MOSFET (3-state) (Level 2)                                                                                                                                                                                                                                                                                     | Help        |                       | Diode with reverse recovery                                                                                                                                                                                                                   | (Level 2) Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| Name<br>Model Level<br>Vbreakdown (drain-source<br>On Resistance<br>Threshold Voltage VGS(th)<br>Internal Gate Resistance<br>Transconductance<br>Capacitance Cgs<br>Capacitance Cgs<br>Capacitance Cgs<br>Diode Forward Voltage<br>Diode Resistance<br>Parasitic Inductance Ls<br>Current Flag<br>Voltage Flag | 45m 🗆 🔨     | 80n<br>10PC124PA040MR | Name<br>Model Level<br>Forward Voltage<br>Resistance<br>Parasitic Inductance<br>Parallel Capacitance<br>Forward Current<br>Peak Reverse Current<br>Current Slope<br>Reverse Recovery Time<br>Initial Position<br>Current Flag<br>Voltage Flag | Display           DH         Image: Constraint of the second se |   |

Figure 28: PSIM level 2 configuration parameters of the SiC MOSFET and SiC Diode

0.69929

22u

The values of the parasitic inductances were selected by performing successive simulations of the system to adjust the response with the values captured by the oscilloscope of the laboratory converter tests. The values of the DC-Link parasitic inductances were set between the realistic values of 1-5 uH while the SiC MOSFET module between 10-100 nH. In addition, based on the PCB design of the power board, the parasitic inductance was estimated as a function of the length, width, and thickness of the trace, obtaining values of nH. The values used in the simulation are shown in Table 6.

| Stray Inductances                                                                                                                       |                    |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| L <sub>DC_Link</sub> 1 μH (Symmetrical)                                                                                                 |                    |  |  |  |  |

| $L_{trace\_DC\_bus}$                                                                                                                    | 2 nH (Symmetrical) |  |  |  |  |

| Lsic_mosfet 6 nH (per Module)                                                                                                           |                    |  |  |  |  |

| $\mathbf{L}_{\mathbf{MAIN}} = 2 \cdot \mathbf{L}_{\text{trace}_{DC}_{bus}} + 2 \cdot \mathbf{L}_{\text{SiC}_{MOSFET}} = \mathbf{16 nH}$ |                    |  |  |  |  |

Table 6: Stray Inductances of the PSIM model of the converter

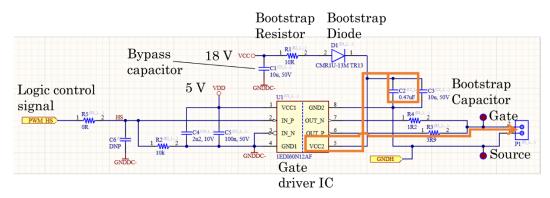

It should be noted that the MOSFET gate circuit is configured according to the converter hardware explained in section 3.3.2. This hardware incorporates the bootstrap technique in the gate switching circuit design and generates PWM switching signals between 0V and 18V with a gate resistance of 6 Ohm.

Figure 29: Bootstrap circuit configuration in PSIM

## PSIM Simulations

When the different elements of the system have been integrated into PSIM and their parameters have been adjusted, the model simulations are carried out and compared with the tests of the real laboratory converter to validate the model.

### Half bridge configuration.

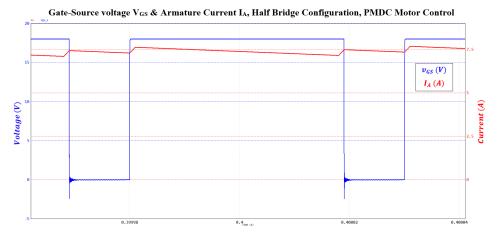

To perform the parameter adjustment, the converter is tested with the Half-bridge configuration. In this configuration, both legs of the SiC MOSFET module are used, connecting the load between both output terminals, and applying the control signal of the double pulse test DPT to the high-side MOSFET.

Figure 30: Half Bridge configuration of the converter and its Model in PSIM

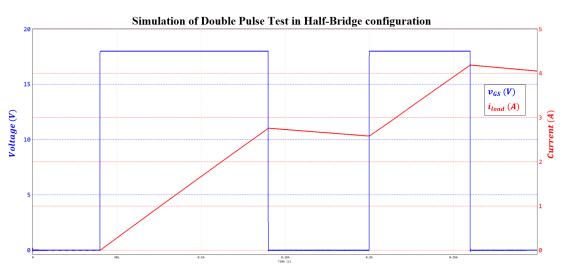

The model is simulated in PSIM for a simulation time of 300  $\mu$ s to obtain firstly the Double Pulse Test graphs. To do this, the voltage applied to the gate-source of the MOSFET and current of the load connected between the output terminal and the DC- are monitored (Figure 31).

Figure 31: Simulation of the Double Pulse Test in Half-Bridge configuration using PSIM

The results are as expected, when the top side MOSFET is closed at  $\tau_1$  the current starts to increase until it reaches a value close to 3A, then with the opening of the MOSFET the current decreases slightly during  $\tau_{break}$  and finally with the new switching of the MOSFET at  $\tau_2$  the current increases again to 4,25A.

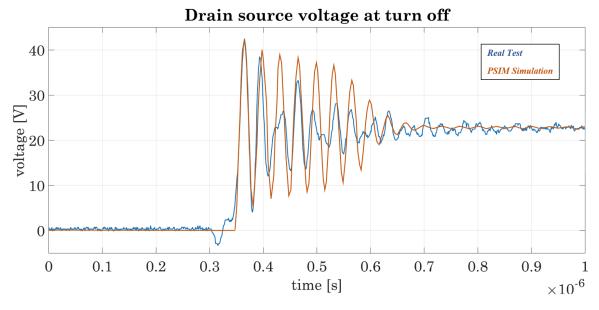

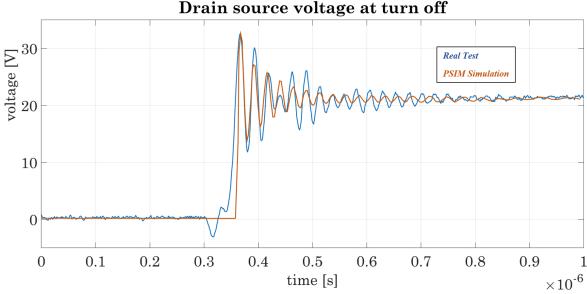

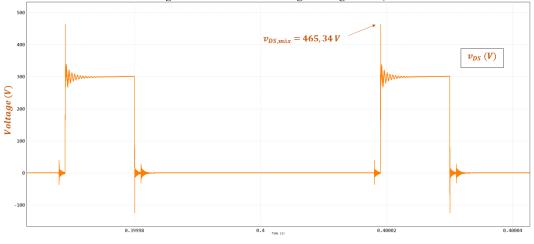

To verify the correct selection of the stray inductances and their effect on the voltage spikes caused by the fast switching of the SiC MOSFETs, the voltage between the drain-source terminals of the high-side MOSFETs in Half Bridge configuration is monitored and compared with the real test of the converter in the laboratory (Figure 32).

Figure 32: Comparison of the Drain-Source voltage at turn-off between real test and PSIM Simulation (Half Bridge)

It is observed that the simulation obtained by PSIM of the drain-source voltage of the MOSFET is very similar to the real behaviour of the system, especially in the maximum peak voltage. This peak voltage has a maximum value of 43 V approximately, which exceeds by far the value of 20 V established in the DC-Link capacitor bank.

#### Split Output configuration.

The next configuration that is simulated from the PSIM model is the split output configuration (Figure 33), that allows to observe if the response obtained is in accordance with the results of the converter tests done in the laboratory with this topology.

Figure 33: Split Output configuration of the converter and its Model in PSIM

In this configuration two inductors 7443763540100 from Wurth Elektronik, with an inductance of 10 µH, are added on both legs of the converter resulting in a single output terminal. The load is connected between this single output terminal and the DC- of the DC-Link bus. The high side MOSFET is selected as the device under test by applying the double pulse test signal and the same simulation period is maintained  $(300 \ \mu s)$ .

Figure 34: Simulation of the Double Pulse Test in Split Output configuration using PSIM

The signals obtained from the double pulse test in the Split output configuration are very similar to the Half bridge configuration. The difference is that the output load is increased by connecting the splitting inductors and therefore the current is slightly lower, reaching a maximum of 4.18V.

Figure 35: Comparison of the Drain-Source voltage at turn-off between real test and PSIM Simulation (Split Output)

The simulation model fits perfectly to the real behaviour of the converter with the split output topology. It can be seen that when the split output configuration is used, the peak voltage generated is reduced to a value of 33V and the turn-off transient of the MOSFET is shortened as it stabilises earlier.

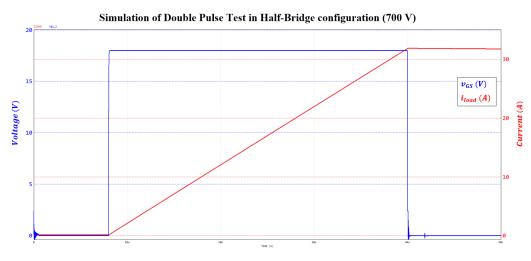

After the simulations in half-bridge and split-output configurations to adjust the parameters of the model, a new simulation is carried out with the most restrictive design conditions, connecting the system to a 700 V power supply, and switching the MOSFET when the load current is 32 A. For this reason, the double pulse test periods are recalculated to obtain the required voltage and current conditions in the simulation.

$$\tau_1 = 700 \ \mu H \cdot \frac{32 \ A}{700 \ V} \approx 32 \ \mu s$$

After the period  $\tau_1$  is over, the high-side MOSFET begins to turn off and the load current with the value of approximately 32 A begins to decrease slowly. No more switching periods are carried out because the discharge slope of the coil current is very small, which would cause the maximum current of the system to be exceeded when the high-side MOSFET is switched on again without waiting enough time.

Figure 36: Simulation of the Double Pulse Test  $(\tau_1)$  in Split Output configuration using PSIM (700V)

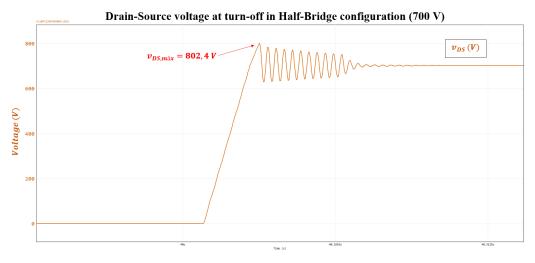

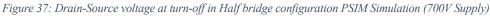

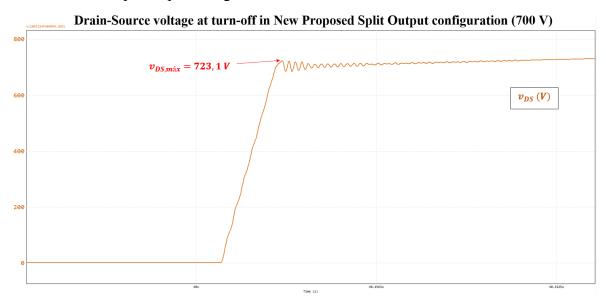

Similarly to the simulation of the converter connected to the 20V power supply, the new simulation is executed with the 700V Half-bridge and Split output configuration monitoring the drain-source voltage of the high-side MOSFET in order to see the maximum peak voltage.

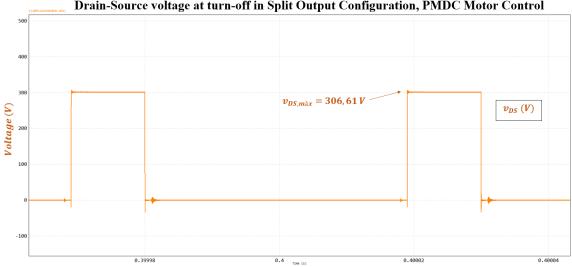

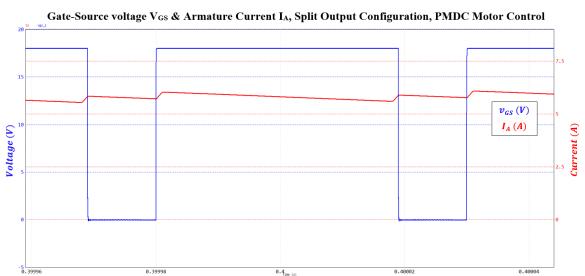

Figure 38: Drain-Source voltage at turn-off in Split output configuration PSIM Simulation (700V Supply)

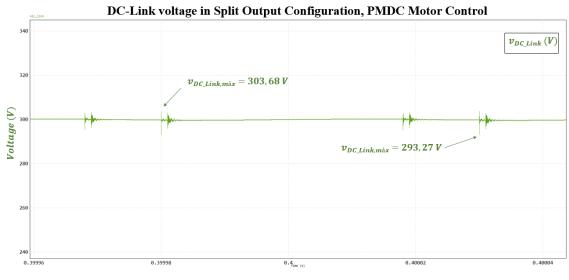

The half bridge and split output configurations produce high peak voltages when the MOSFET turns off. In the half bridge configuration, a voltage between the Drain-Source terminals of 802,4 V is reached, while in the split output it is reduced to 773,2 V due to the advantages of this configuration. These high voltages can cause problems in the converter, leading to failures that compromise the durability and reliability of the system, so it is important to mitigate them.

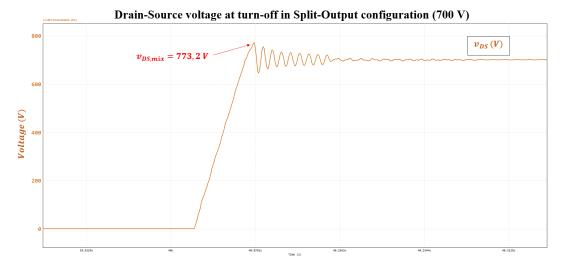

## 3.2.4. New Proposed PSIM Model of the Power Unit

The proposed new model of the power unit (Figure 39) aims to improve the operating performance of the laboratory converter. For this, the new DC-Link capacitor bank proposed in section 3.2.1 is incorporated to minimise the volume occupied with a lower total cost. In addition, this new model also incorporates the snubber capacitors proposed in section 3.2.2 to reduce the peak voltage at the MOSFET Drain-Source terminals when the turn-off occurs.

Figure 39: New Simulation Model of a single leg of the converter with snubber in PSIM

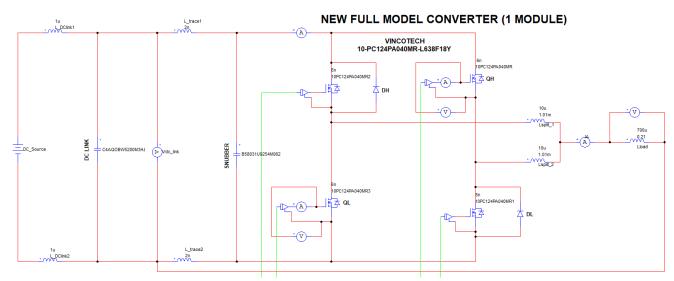

Simulations of the new proposed converter in half bridge and split output configurations are carried out in order to check the improvements in the voltage peaks at the Drain-Source terminals of the MOSFET when the DC-Link is connected to the 700V power source (Design condition).

### > <u>New proposed Half bridge configuration.</u>

The simulated model of the proposed new half bridge configuration is shown in Figure 39. In this model, the old DC-Link is replaced by a single MKP capacitor (*C4AQOBW5200M3HJ*) and also the ceramic snubber capacitor (*B58031U9254M062*) is incorporated.

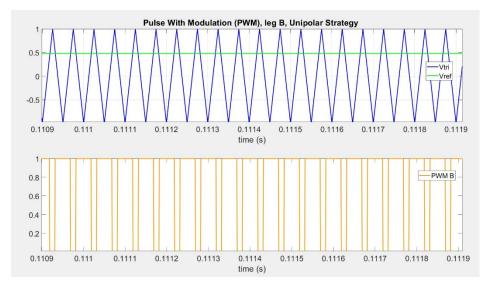

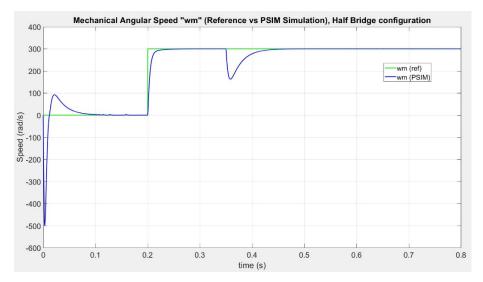

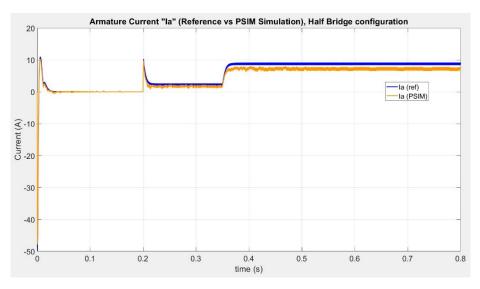

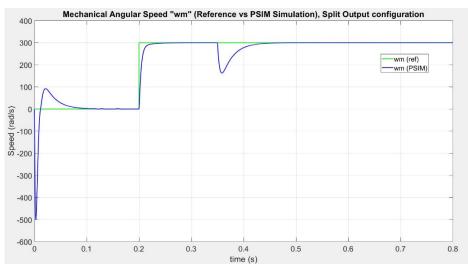

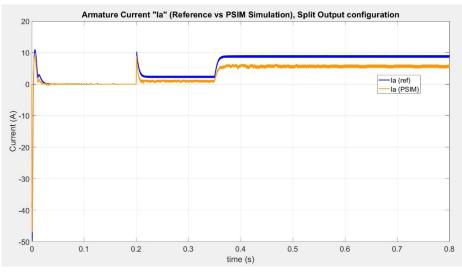

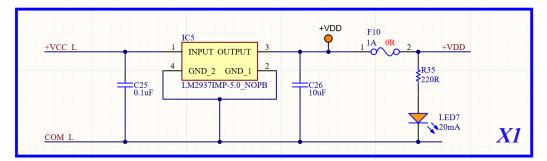

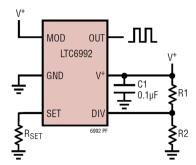

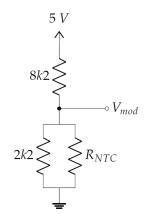

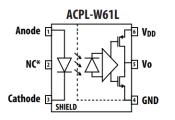

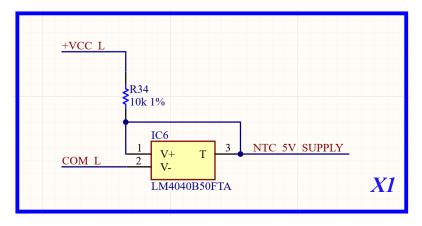

Figure 40: New Proposed Half bridge model in PSIM