# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2014-06

# HIGH PERFORMANCE COMPUTING FOR RECONNAISSANCE APPLICATIONS

Stevens, Christopher J.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/70447

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

# THESIS

# HIGH PERFORMANCE COMPUTING FOR RECONNAISSANCE APPLICATIONS

by

Christopher J. Stevens

June 2014

Thesis Co-Advisors:

Douglas Fouts Weilian Su

Approved for public release; distribution is unlimited

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |                                                                                                                                               | Form Appro                                                              | oved OMB No. 0704-0188                                                                                  |                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |                                                                                                                                               |                                                                         |                                                                                                         |                                                                                                                                                             |

| 1. AGENCY USE ONLY (Leave blank)2. REPORT DATE<br>June 20143. REPORT TYPE AND DATES COVE<br>Master's Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                    |                                                                                                                                               |                                                                         |                                                                                                         |                                                                                                                                                             |

| <ul> <li>4. TITLE AND SUBTITLE<br/>HIGH PERFORMANCE COMPU<br/>APPLICATIONS</li> <li>6. AUTHOR(S) Christopher J. Ster</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vens                                                                                                                               |                                                                                                                                               |                                                                         | 5. FUNDING                                                                                              | NUMBERS                                                                                                                                                     |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    |                                                                                                                                               | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                             |                                                                                                         |                                                                                                                                                             |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |                                                                                                                                               | S(ES)                                                                   | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER                                                       |                                                                                                                                                             |

| <b>11. SUPPLEMENTARY NOTES</b> or position of the Department of |                                                                                                                                    |                                                                                                                                               |                                                                         |                                                                                                         |                                                                                                                                                             |

| <b>12a. DISTRIBUTION / AVAILA</b><br>Approved for public release;distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                                               |                                                                         | 12b. DISTRIB                                                                                            | A BUTION CODE                                                                                                                                               |

| <b>13. ABSTRACT (maximum 200</b><br>Parallel programming is vital<br>market, however, is constantly<br>an open parallel processing la<br>program across multiple archit<br>choice can be made for a give<br>signal processing algorithms a<br>results show that for each algor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | to fully utilize<br>evolving, with<br>nguage, such a<br>ectures. It also<br>en application.<br>across two grap<br>ithm, a specific | new processors and n<br>s OpenCL (Open Co<br>enables a method of<br>In this research, Open<br>phics processing units<br>device can clearly be | ew archit<br>nputing (<br>evaluatio<br>nCL is us<br>and one<br>shown to | ectures getting<br>Language), enso<br>on between mused to evaluate<br>e central proce<br>outperform the | released annually. Using<br>ables the use of a single<br>ltiple devices so the best<br>to the performance of two<br>essing unit. Experimental<br>to others. |

| <b>14. SUBJECT TERMS</b> Fast Fourier transformation (FFT), binary phase-shift keying (BPSK),<br>OpenCL, parallel processing, graphic processing unit (GPU), central processing unit (CPU), field-<br>programmable gate array (FPGA) <b>15. NUMBER OF</b><br>PAGES75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                               |                                                                         | PAGES                                                                                                   |                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |                                                                                                                                               |                                                                         |                                                                                                         | 16. PRICE CODE                                                                                                                                              |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PAGE                                                                                                                               | TION OF THIS                                                                                                                                  | BSTRAC                                                                  | ICATION OF                                                                                              | 20. LIMITATION OF<br>ABSTRACT<br>UU                                                                                                                         |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited

### HIGH PERFORMANCE COMPUTING FOR RECONNAISSANCE APPLICATIONS

Christopher J. Stevens Ensign, United States Navy B.S., United States Naval Academy, 2013

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

### NAVAL POSTGRADUATE SCHOOL June 2014

Author: Christopher J. Stevens

Approved by:

Douglas Fouts Thesis Co-Advisor

Weilian Su Thesis Co-Advisor

Clark Robertson Chair, Department of Electrical and Computer Engineering

## ABSTRACT

Parallel programming is vital to fully utilize the multicore architectures that dominate the processor market. The market, however, is constantly evolving, with new processors and new architectures getting released annually. Using an open parallel processing language, such as OpenCL (Open Computing Language), enables the use of a single program across multiple architectures. It also enables a method of evaluation between multiple devices so the best choice can be made for a given application. In this research, OpenCL is used to evaluate the performance of two signal processing algorithms across two graphics processing units and one central processing unit. Experimental results show that for each algorithm, a specific device can clearly be shown to outperform the others.

# TABLE OF CONTENTS

| I.   | INT | RODUCTION                         | 1  |

|------|-----|-----------------------------------|----|

|      | А.  | PROBLEM STATEMENT                 | 1  |

|      | В.  | PROJECT GOAL                      | 1  |

|      | C.  | MOTIVATION                        | 1  |

|      | D.  | RELATED WORK                      |    |

|      | Е.  | ORGANIZATION OF THESIS            | 3  |

| II.  | PRC | OBLEM DESCRIPTION                 | 5  |

|      | А.  | DIFFERENCES IN COMPUTING DEVICES  |    |

|      |     | 1. Central Processing Units       | 5  |

|      |     | 2. Graphics Processing Units      |    |

|      |     | 3. Field Programmable Gate Arrays |    |

|      | В.  | PARALLEL PROCESSING               | 8  |

|      | C.  | SIGNAL MODULATION                 | 10 |

|      | D.  | FOURIER TRANSFORM                 | 11 |

| III. | RES | SEARCH METHODS                    | 15 |

|      | А.  | OPENCL                            | 15 |

|      | В.  | DEVICES USED                      | 18 |

|      |     | 1. NVIDIA GPUs                    | 19 |

|      |     | a. Tesla K20c                     | 19 |

|      |     | <i>b. GeForce GTX 650</i>         | 20 |

|      |     | 2. Intel Xeon E5-2643             |    |

|      |     | 3. Device Comparison              |    |

|      |     | 4. FPGA                           |    |

|      | C.  | TESTING ALGORITHMS                |    |

|      |     | 1. Binary Phase-Shift Keying      |    |

|      |     | a. Motivation                     |    |

|      |     | b. OpenCL Algorithm               |    |

|      |     | c. Demodulation                   |    |

|      |     | 2. Fast Fourier Transform         |    |

|      |     | a. Motivation                     |    |

|      |     | b. Algorithm                      |    |

| IV.  | EXP | PERIMENTAL RESULTS AND ANALYSIS   |    |

|      | А.  | FFT RESULTS                       |    |

|      |     | 1. Performance: Float Data Type   |    |

|      |     | 2. Performance: Double Data Type  |    |

|      |     | 3. Algorithm Output               |    |

|      | B.  | BPSK PERFORMANCE                  |    |

|      |     | 1. Initial Simulation             |    |

|      |     | 2. Additional Simulations         |    |

|      | C   | 3. Demodulation                   |    |

|      | С.  | COMBINED ALGORITHM PERFORMANCE    | 43 |

| V.   | CON   | ICLUS | SION AND RECOMMENDATIONS      | 47 |

|------|-------|-------|-------------------------------|----|

|      | A.    | FIN   | DINGS AND CONCLUSIONS         |    |

|      | В.    | RE    | COMMENDATIONS FOR FUTURE WORK |    |

|      |       | 1.    | FPGA                          |    |

|      |       | 2.    | Additional Algorithms         |    |

|      |       | 3.    |                               |    |

|      |       | 4.    | Recovery of the FFT Output    |    |

| LIST | OF R  | EFER  | ENCES                         | 51 |

| INIT | IAL D | ISTRI | BUTION LIST                   | 55 |

# LIST OF FIGURES

| Figure 1.  | Single-thread integer performance of CPUs relative to time based on data from the SPEC, after [5]                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.  | Single-threaded floating-point performance of CPUs relative to time based<br>on data from the SPEC, after [5]                                                            |

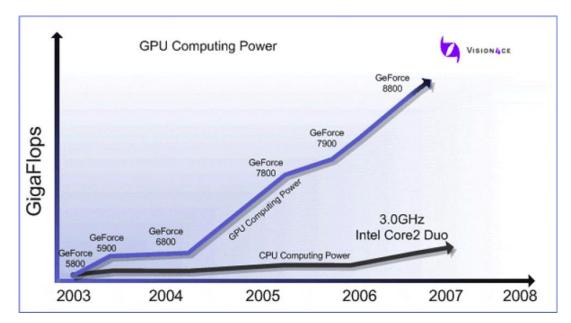

| Figure 3.  | NVIDIA GPU and Intel CPU raw computing power in gigaFLOPS relative to time, from [7]                                                                                     |

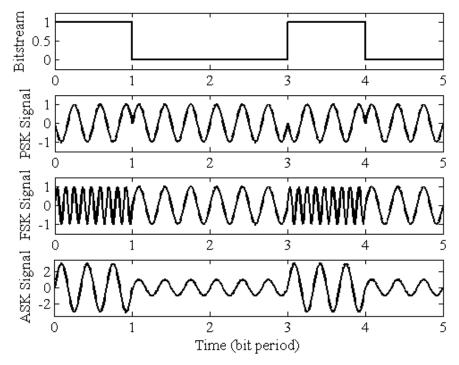

| Figure 4.  | Three binary digital modulation schemes: phase-shift keying, frequency-<br>shift keying, and-amplitude shift keying, as well as the original binary<br>bitstream         |

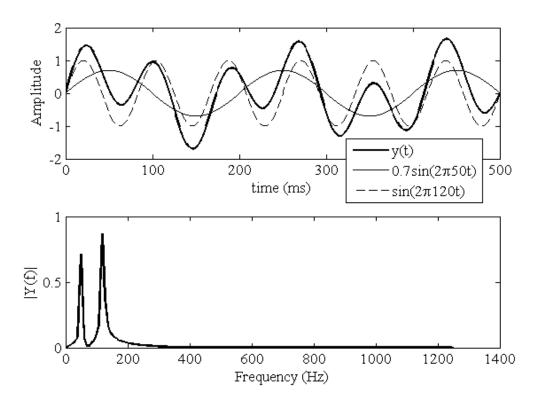

| Figure 5.  | A sinusoidal signal with its two component sinusoids and its Fourier transform                                                                                           |

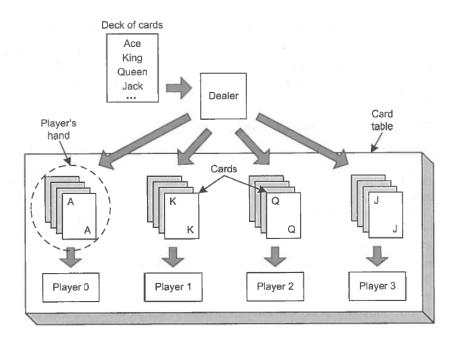

| Figure 6.  | A pictorial representation of a game of cards, from [9, p. 9]16                                                                                                          |

| Figure 7.  | A pictorial representation of kernel distribution among OpenCL-compliant devices, from [9, p. 8]                                                                         |

| Figure 8.  | A visual representation of the deployment of work groups to compute<br>units, from [9, p. 66]                                                                            |

| Figure 9.  | The OpenCL memory model, from [19]18                                                                                                                                     |

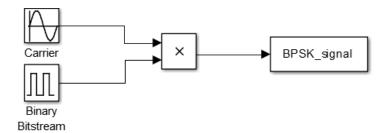

| Figure 10. | A block diagram of a BPSK modulator                                                                                                                                      |

| Figure 11. | An example of a BPSK modulated signal                                                                                                                                    |

| Figure 12. | Runtime results of the FFT algorithm on all three devices using the float data type                                                                                      |

| Figure 13. | Runtime results of the FFT algorithm on the NVIDIA GPUs using the float data type                                                                                        |

| Figure 14. | Runtime results of the FFT algorithm on all three devices using the double data type                                                                                     |

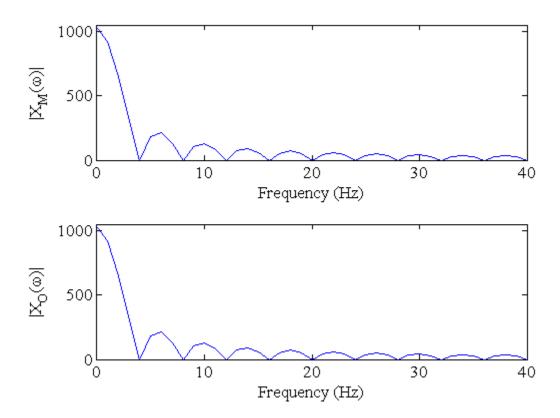

| Figure 15. | Comparison of the FFT output for a signal $rect[n]$ . The output of the                                                                                                  |

|            | MATLAB FFT is shown by $X_{M}(\omega)$ and the output of the OpenCL                                                                                                      |

|            | algorithm is shown by $X_o(\omega)$                                                                                                                                      |

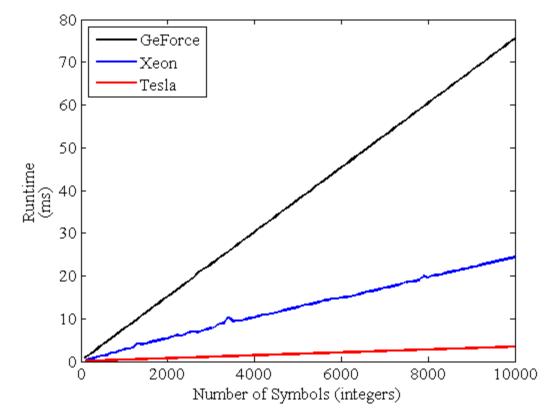

| Figure 16. | Performance results for the BPSK algorithm for all three devices. The number of samples per bit is held constant at 100                                                  |

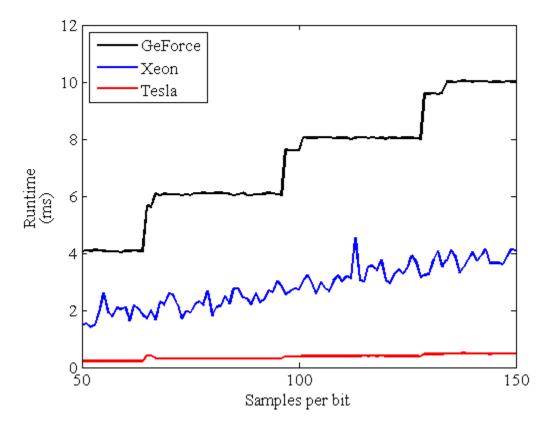

| Figure 17. | Performance results for the BPSK algorithm for the three devices. The number of symbols is held constant at 1000                                                         |

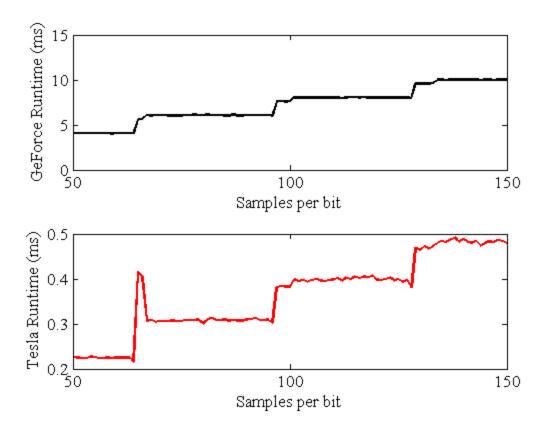

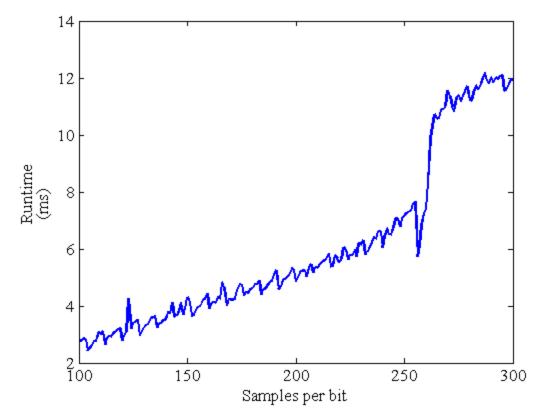

| Figure 18. | Performance results of the BPSK algorithm for the NVIDIA devices with a fixed number of symbols (1000)                                                                   |

| Figure 19. | Performance of the BPSK algorithm on the Xeon to show similarities with<br>the NVIDIA results. A fixed number of symbols (1000) is used                                  |

| Figure 20. | Performance of the BPSK algorithm on all three devices with 16 samples<br>per bit and a variable number of symbols. The plotted performance is the<br>average of 10 runs |

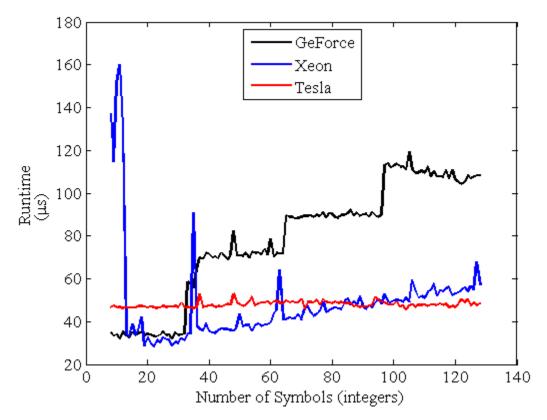

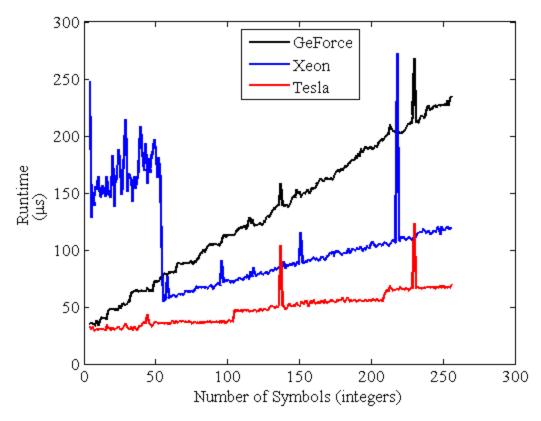

| Figure 21. | Performance of the demodulation kernel on all three devices. The         |

|------------|--------------------------------------------------------------------------|

|            | horizontal axis is the number of integers resultant from the demodulated |

|            | signal40                                                                 |

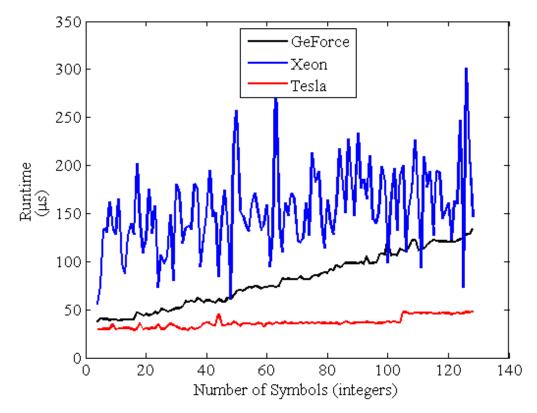

| Figure 22. | Performance of the demodulation kernel on all three devices. The         |

|            | horizontal axis is the number of integers resultant from the demodulated |

|            | signal. The plotted performance is the average of 15 runs                |

| Figure 23. | Performance of the demodulation kernel on all three devices. The         |

|            | horizontal axis is the number of integers resultant from the demodulated |

|            | signal. The plotted performance is the average of 10 runs                |

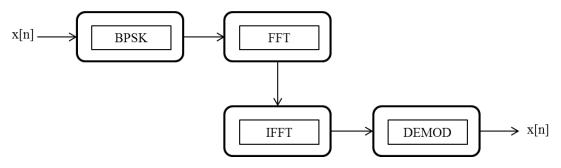

| Figure 24. | Flow of the combined FFT and BPSK algorithms                             |

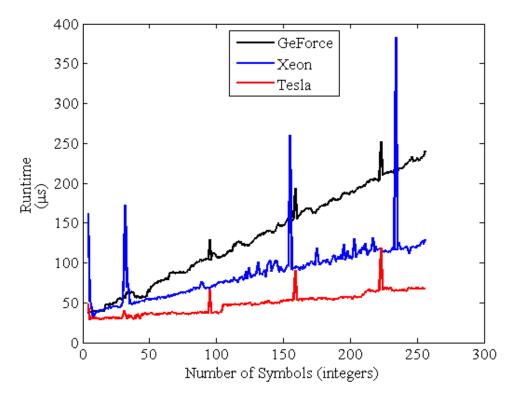

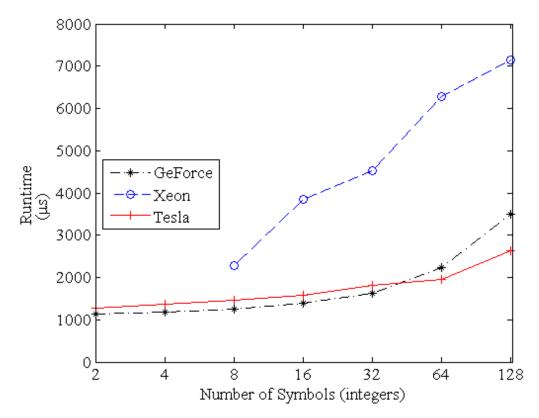

| Figure 25. | Performance of the combined algorithm on all three devices using the     |

| C          | average of 10 runs                                                       |

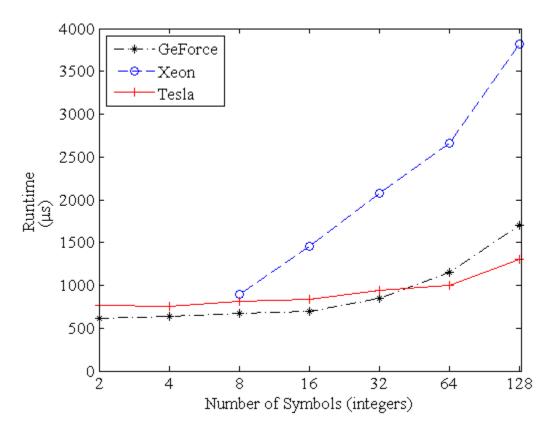

| Figure 26. | Performance of the IFFT and demodulation blocks of the combined          |

| e          | algorithm on all three devices                                           |

|            | 5                                                                        |

# LIST OF TABLES

| Table 1. | Device specifications relevant to the conducted research. Note that the   |     |

|----------|---------------------------------------------------------------------------|-----|

|          | listed memory for the Xeon E5-2643 is actually the system RAM.            | .21 |

| Table 2. | Output of the FFT algorithm for the Tesla showing the possible            |     |

|          | recoverability of the incorrect GPU output                                | .30 |

| Table 3. | A comparison of the signal lengths at which the FFT algorithm breaks      |     |

|          | down on the three devices with the float data type                        | .31 |

| Table 4. | A comparison of the signal lengths at which the FFT algorithm breaks      |     |

|          | down on the three devices with the double data type                       | .32 |

| Table 5. | RMSE values for the FFT algorithm using a signal length of 16384. The     |     |

|          | algorithm does not operate on the GeForce for a length 16384 signal using |     |

|          | the double data type.                                                     | .34 |

|          |                                                                           |     |

# LIST OF ACRONYMS AND ABBREVIATIONS

| ASW    | antisubmarine warfare                                  |

|--------|--------------------------------------------------------|

| BPSK   | binary phase-shift keying                              |

| CONOPS | concept of operations                                  |

| COTS   | commercial off-the-shelf                               |

| CPU    | central processing unit                                |

| CUDA   | Compute Unified Device Architecture                    |

| DFT    | discrete Fourier transform                             |

| DSP    | digital signal processing                              |

| FFT    | fast Fourier transform                                 |

| FLOPS  | floating-point operations per second                   |

| FPGA   | field-programmable gate array                          |

| GPGPU  | general-purpose computing on graphics processing units |

| GPU    | graphics processing unit                               |

| GUI    | graphical user interface                               |

| IFFT   | inverse FFT                                            |

| MIC    | Many Integrated Core                                   |

| OpenCL | Open Computing Language                                |

| RAM    | random access memory                                   |

| RMSE   | root mean square error                                 |

| SDK    | software development kit                               |

| SIGINT | signals intelligence                                   |

| SM     | Streaming Multiprocessor                               |

| SPEC   | Standard Performance Evaluation Corporation            |

|        |                                                        |

#### **EXECUTIVE SUMMARY**

Utilizing the most powerful computing equipment available is vital to processing the increasing amount of data collected by increasingly powerful sensors. The fast processing of collected data and the information required by the systems is vital to enabling the Navy to maintain its lead in control of the seas. Alternatively, utilizing more powerful but less expensive processors allows for a larger number to be utilized, potentially allowing for a wider area of coverage. The multitude of different processors available, and the multitude of architectures used by those processors, makes it difficult to determine what the most powerful computing equipment is for a given application without evaluation.

Current processor architectures are almost entirely multicore. This allows for greater performance but also requires programming methods that are much different from standard, sequential programming. Open Computing Language (OpenCL) is a parallel programming language that contains a library of functions and data structures that serve as an open-source method for using the C language for parallel programming. The OpenCL developers leave the creation of the compiler for the language up to the processor manufacturers. Although this causes some fragmentation in the market, it enables each developer to focus on optimizing the library for their specific device architecture.

Central processing units (CPUs) and graphics processing units (GPUs) are two of the devices present in virtually all modern computing systems. CPUs are the backbone of the majority of computing systems, while GPUs are the devices that enable the visual display of all the information provided by the system. As a result of their prevalence, there is strong competition between manufacturers to create the most powerful and least expensive device. They are, therefore, an important area for consideration as a component in a processing system. In this research, two GPUs and one CPU were evaluated. The CPU tested was the Intel Xeon E5-2643, while the two GPUs were both provided by NVIDIA. The GeForce GTX 650 is a "typical" GPU, while the Tesla K20c is a member of a family of GPUs designed solely for data processing. For this research, two signal processing algorithms were used to evaluate the three processors. The Fourier transform is extremely important to signal processing, allowing for the determination of the frequencies present in the incoming signal. In the processing of acoustic data this is particularly important, as it is one of the few ways to discriminate between underwater targets. The fast Fourier transform (FFT) algorithm is one of the most efficient methods for calculating the Fourier transform on a finite sequence. Modulation is vital to communications as before a signal can be transmitted through any medium it must be modulated. Shift keying functions change a parameter of a carrier sinusoid, depending on the binary symbol to be transmitted. Binary phase-shift keying (BPSK) modulates the phase of the carrier wave using single binary bits as the modulating symbol. An FFT and BPSK algorithm were, therefore, both used to evaluate the three devices. This includes the inverse FFT and a BPSK demodulation algorithm.

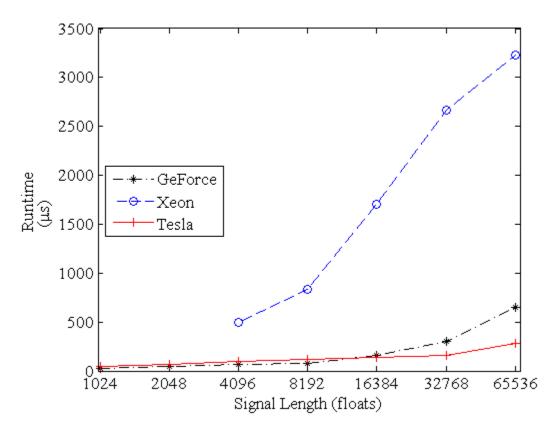

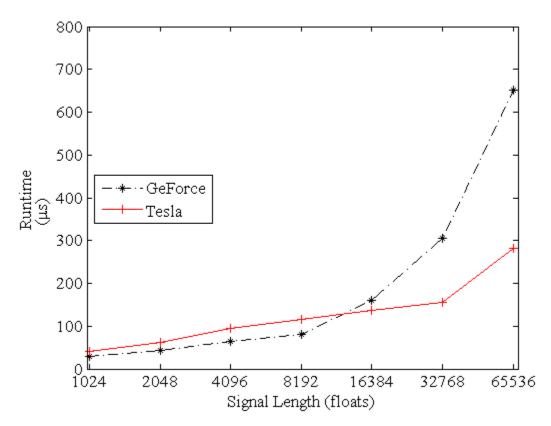

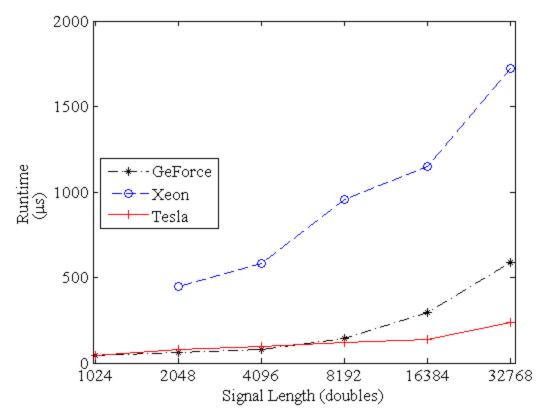

The two test algorithms delivered different results for the performance of the processors. In addition to requiring that an input signal be a power of two, the FFT algorithm did not operate on each of the devices at the test signal lengths. Due to device specifications, the CPU could not perform the algorithm for small signal lengths, while the two GPUs were unable to operate on large signal lengths. For the operable signal lengths, however, the two GPUs vastly outperformed the CPU as expected. The GeForce, for the smaller signal lengths, outperformed the Tesla. This was contrary to the original hypothesis. The IFFT (inverse FFT) algorithm, as it only added a single function to scale the results of the FFT algorithm, performed similarly.

When simulating the BPSK algorithm for a large amount of data, the GeForce performed the slowest of the three devices. The Tesla performed the fastest and required time on the order of milliseconds. With a limited but more realistic set of parameters for the modulation scheme, the GeForce and CPU outperform the Tesla for a brief period. The CPU performance, however, is hurt by its necessity to act as the host of the application, performing computations that the GPUs do not need to perform. The demodulation algorithm performed similarly to the forward modulation.

An additional application was used to evaluate the performance of the devices, a combination of the two algorithms and their inverse. A number of test sequences were

sent through BPSK modulator, the FFT, the IFFT, and the BPSK demodulator. Here the performance closely aligned with the same trend of the performance of the FFT algorithm, with the CPU performing worst and the GeForce outperforming the Tesla when a smaller number of symbols was used.

It is clear from the results that the performance of the devices is strongly affected by the algorithm used. In this case, although the Tesla performance was not the best in every situation, it was consistent. In certain situations, this is more important than occasional higher performance. In addition, cost must sometimes be considered. The Tesla costs \$3,000 while the GeForce costs only \$300. Either way, it is necessary for the specific algorithm that is to be employed get tested.

## I. INTRODUCTION

#### A. PROBLEM STATEMENT

In order to maintain its lead in sea control, it is necessary for the U.S. Navy to utilize the most powerful computing equipment available. Architectural differences in the various processors available, however, make it difficult to determine what the best computing equipment would be for a given application. Also, the ever-evolving technology market can make certain hardware obsolete within 18 months. It is clearly necessary to evaluate the available options prior to hardware selection. Using an open computer language for the testing platform allows for less expensive software development. Utilizing commercial off-the-shelf (COTS) processors as the hardware devices can provide a suitable, relatively inexpensive solution to the problem of the constantly changing market.

#### **B. PROJECT GOAL**

The goal of this research is to determine which of the three provided processors is best suited to perform two specific signal processing algorithms. Ideally, a single device will clearly outperform the others, making for a clear decision. Realistically, of course, this may not be the case.

#### C. MOTIVATION

In warfare, one of the key areas where processing data is important is signals intelligence (SIGINT). Maintaining an advantage in the area of SIGINT is vital to preserving spectral dominance. In the area of SIGINT, it is necessary to process the large amount of data that is received. Although ideally data processing and interpretation are always done as quickly as possible, speed is especially important in warfare. Decrypting a received or intercepted signal could be a matter of life or death.

Acoustics is another area that supplies a large amount of data that is required to be processed. This is increasingly true as sensors continue to become more powerful. The ability of sensors to collect more and more data directly correlates to a need to process more and more data. However, it is unmistakably undesirable for the increase in data to also lead to an increase in the time it takes to process the data. It is essential, therefore, to update the hardware that processes the incoming data at the same time that the sensors collecting the data are upgraded.

In December of 2004, Chief of Naval Operations Admiral Vernon Clark approved the release of a document outlying the general vision of the U.S. Navy's newest concept of operations (CONOPS) for antisubmarine warfare (ASW). Inside the CONOPS, the use of a distributed network of miniaturized sensors is described several times [1]. Utilizing such a network of sensors would improve the understanding that warfighters have of the theater in which they are operating [2]. In order to create this type of network, it would likely be necessary to utilize small, high-performance processors that can do a large amount of the associated data processing necessary prior to that data getting sent to a collector for further analysis.

Finally, it is not just necessary to be able to process more data from external collectors. As technology continues to play an increasingly large role in all areas, it is necessary to improve the level of performance at which that technology operates. Submarines, for example, are now utilizing digital photonics masts in place of more traditional periscopes. This requires a large amount of processing capability.

#### D. RELATED WORK

Many studies have been conducted that have looked at the processing abilities of different computing devices. Due to its cross-platform operability, Open Computing Language (OpenCL) is frequently used for the evaluations. The majority of the studies have found that even though an OpenCL program can be run on any device for which the developer has created a compiler, performance across multiple devices is not necessarily portable. Of course, it could sometimes be unwise to compare the analysis of results from different devices due to differences in architectures, but in certain cases it can be useful. For example, it might be desired to explore how a specific algorithm runs on specific devices.

In certain cases, due to differences in how the different types of processors handle certain computations, performance portability can be abysmal. A study by researchers at the University of Chicago gathered initial results that found the "portable performance of three OpenCL programs is poor, generally achieving a low percentage of peak performance (7.5%–40% of peak GFLOPS and 1.4%–40.8% of peak bandwidth)" [3]. They identified several areas where portable performance could be improved, both in the test algorithms themselves and in the OpenCL compilers. After modifying the test algorithms portable performance was increased "from the current 15% to a potential 67% of the state-of-the-art performance" [3]. Although this wording is slightly vague, it does show that it is possible to improve performance portability. In addition, it must be noted that manually making changes to the test algorithms greatly increases development time—where the ability to compile OpenCL programs on multiple platforms without making changes is what makes the desired, decreased development time possible.

Researchers at China's National University of Defense Technology also identified areas to convert OpenCL programs written specifically for GPUs into programs that would run more efficiently on central processing units (CPUs). However, they found that in doing so the changes they made to the programs were "good for CPU [*sic*], while bad for GPU [*sic*]" [4]. In this case, the researchers manually transformed the OpenCL programs. They are also purportedly working on "developing an automatic transforming tool to implement [their] present work" [4]. Even automatic program transformations, however, make trade-offs for increased performance on one type of device over another and increase development time.

#### E. ORGANIZATION OF THESIS

The rest of this thesis is organized as follows. The problem at hand is discussed in Chapter II; namely, the two algorithms covered as well as the differences that exist between computing devices. A background to parallel processing is also provided in Chapter II. The methods by which the research was carried out are described in Chapter III, covering the OpenCL programming language, the three test devices, and the two algorithms. The findings of the research are discussed in Chapter IV, and the overall conclusions as well as recommendations for future work are provided in Chapter V.

## **II. PROBLEM DESCRIPTION**

#### A. DIFFERENCES IN COMPUTING DEVICES

As mentioned previously, different processing devices use different architectures. These differences are explored in this section.

#### 1. Central Processing Units

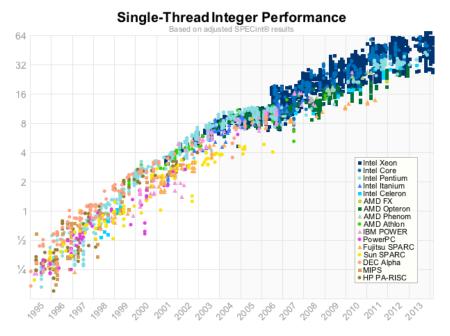

Central processing units have been the core component in many computing systems since their inception. For the computing systems that have them, CPUs are the brain of the system, carrying out the instructions stored in memory. As semiconductor technology has improved and feature size decreased, CPU performance has vastly increased. In order to evaluate the performance of CPUs and other computing devices, the Standard Performance Evaluation Corporation (SPEC) collects and publishes various results of their benchmark programs. Shown in Figure 1 is a graph of the single-thread integer performance of various CPUs covering a period of 18 years, produced using a Python script written by Canadian programmer Jeff Preshing.

Figure 1. Single-thread integer performance of CPUs relative to time based on data from the SPEC, after [5].

5

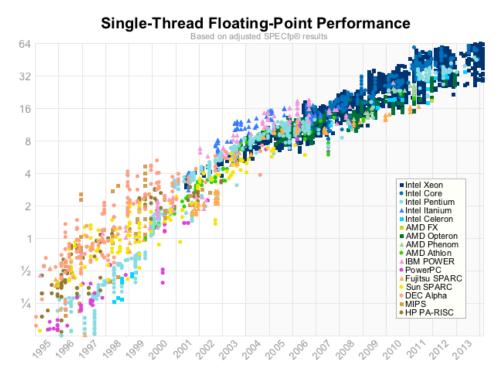

Single-thread performance is used to remove any impact that parallel processing might have, allowing for a better comparison between older and newer CPUs. The results shown in Figure 1 are normalized to the performance of the Sun Ultra Enterprise 2 [6], with the performance of that machine having a value of one. It should be noted that the vertical axis scale is logarithmic. As can be seen, CPU performance increased dramatically for the first 10 years, and although the performance increase appears to have slowed slightly, it has not stopped improving. Single-thread floating-point performance can be seen in Figure 2 and shows much the same results as Figure 1.

Figure 2. Single-threaded floating-point performance of CPUs relative to time based on data from the SPEC, after [5].

#### 2. Graphics Processing Units

As personal computers became more and more commonplace, their operating systems shifted from providing text-based output, such as the Microsoft Disk Operating System, towards graphical user interfaces (GUI). As GUI displays became more complex and required more computationally intensive calculations, GPUs were developed to share the computational load with CPUs. Initially, graphics processors were not separate

devices as is currently the case. Rather, early GPUs were integrated with the computer's motherboard and shared the system random access memory (RAM). Some computer systems today—typically only laptop computers and netbooks that place an importance on size and weight—still use integrated graphics processors. Dedicated GPUs, however, have become increasingly powerful, following much the same trends that early CPUs did. In fact, even as CPU performance increases have slowed, GPU performance still swiftly improves each year [7]. A graph of the performance over time of NVIDIA's GeForce line of processors is shown in Figure 3, measured in gigaFLOPS (where one gigaFLOP is 10<sup>9</sup> floating point operations per second [FLOPS]). The GPU performance is compared to Intel's CPU performance over the same period.

Figure 3. NVIDIA GPU and Intel CPU raw computing power in gigaFLOPS relative to time, from [7].

As GPUs became more powerful, it was realized that their high computational performance could be put to use in areas other than displaying GUIs. Modern GPUs are exclusively multicore devices. As such, they are inherently parallel. This is necessary to be able to handle the processing of thousands of pixels with multiple bits per pixel. Researchers recognized that they are well suited to handle the processing of large amounts of other data. GPUs dedicated to data processing, such as the NVIDIA Tesla

family of processors, have been developed that are in fact only able to operate as data processors—that is, they are unable to display graphics data.

#### **3.** Field Programmable Gate Arrays

Since their invention in the 1980's, field-programmable gate arrays (FPGA) have been used in many areas of computing. As their name suggests, FPGAs are reprogrammable devices that can be used and reused in a vast multitude of situations. FPGAs consist of large numbers of logic blocks that can be reconfigured using a hardware description language to suit the programmer's needs. FPGAs also contain memory blocks of varying sizes. In processing data, one of the key advantages FPGAs maintain over other devices is their low power requirement. Some FPGA power consumption can be on the order of milliwatts [8], whereas certain processors can require over 100 W. This, combined with the ability to optimize FPGA architectures to the specific problem at hand enable them to remain viable even with clock speeds that are typically much lower than other processors.

Programming FPGAs, however, is usually more difficult than writing regular programs. It typically requires an intimate knowledge of a hardware description language such as Verilog. For large applications, this can be extremely tedious and time consuming, greatly adding to the development cost. To aid in FPGA development, however, an FPGA developer, Altera, released a software development kit (SDK) that enables compilation of OpenCL applications on certain devices. Another manufacturer, Nallatech, has developed FPGA-based processors that utilize Altera FPGAs and the Altera OpenCL SDK. On the other hand, Xilinx is working on developing its own OpenCL SDK.

#### **B. PARALLEL PROCESSING**

It has already been shown that as the technology behind the production of computer devices has improved, the raw processing power of computing devices has increased. In order to prevent a plateau in performance, manufacturers began to create processors with multiple cores. The first multicore processor was released in 2001 by IBM [9, p. 5] and was used for multiple applications. Today, virtually all processors

produced have multiple cores. Even certain (relatively) low performance processors used in mobile computers—such as Intel's Atom family of processors—can be purchased that contain two or more cores [10]. On the other end of the spectrum, Intel's Many Integrated Core Architecture (MIC), used by Intel's Xeon Phi coprocessors, can provide powerhungry users with up to 61 cores [11], and each of the processors in the NVIDIA Tesla family of GPUs contains over 2,000 Compute Unified Device Architecture (CUDA) cores per processor [12].

In order to make full use of multicore devices, new programming styles and languages were developed; otherwise, running the programs that were created for singlecore devices could potentially waste the processing power provided by the extra cores. Initial methods of parallel programming were convoluted, particularly when attempting to use GPUs for processing non-graphical data—the programmer had to "trick" the GPU into thinking it was performing graphics rendering tasks. In order to improve upon the programming process, a few months after the November 2006 release of its GeForce 8800 GTX GPU, NVIDIA released a public compiler for its CUDA C language [13]. By taking the C programming language and adding certain keywords, NVIDIA created the "first language specifically designed by a GPU company to facilitate general-purpose computing on GPUs" [13]. Because CUDA C is proprietary, however, it can only be compiled to run on NVIDIA processors. This limits its usefulness.

OpenCL is an open source alternative to NVIDIA's CUDA C. Originally released in 2008, OpenCL was initially developed by Apple and is currently maintained by one of the many working groups of the Khronos Group, a consortium of technology companies that define open standards for a variety of software APIs [14]. The Khronos Group leaves the development of the OpenCL compilers to each individual company, enabling improved performance on individual devices but also creating the potential for fragmentation. NVIDIA was the first company to release its compiler for OpenCL in early 2009, and AMD released its compiler several months later [9, p. 5]. OpenCL version 2.0 was released in 2013 [15]. As each company creates its own compiler, however, not all vendors have updated their compilers, supporting only earlier versions of the language.

## C. SIGNAL MODULATION

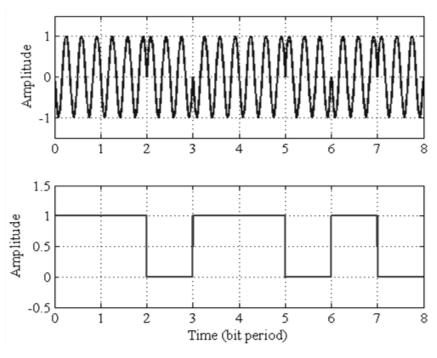

In order to transmit data over long distances, some type of modulation scheme must be used to manipulate some parameter of the analog sinusoidal carrier signal and convey the data. The modulation can itself be either analog or digital, both of which manipulate the carrier sinusoid amplitude, frequency, or phase. Digital modulation schemes use the concept that when conveying digital data there are a limited, discrete number of symbols that can be transmitted. The digital schemes all follow the general equation  $N = 2^n$  where N represents the number of possible symbols that can modulate the carrier wave and n represents the number of bits per symbol. As a result of the limited number of modulation symbols, the variable parameter of the carrier sinusoid also has a limited number of possible values. Signals modulated by an analog method, on the other hand, can theoretically have an infinite number of values. Examples of three binary digital modulation schemes (where the modulation symbols are single bits) are shown in Figure 4.

Figure 4. Three binary digital modulation schemes: phase-shift keying, frequency-shift keying, and-amplitude shift keying, as well as the original binary bitstream.

Once a signal has been modulated, transmitted, and received, it must be demodulated. This is done by matching the value of the carrier sinusoid modulation parameter to its potential values. Whether using analog or digital modulation, this is a fairly straightforward process, particularly when a scheme that modulates either amplitude or frequency is used. If a phase modulation scheme is used, the demodulator must be synchronized with the signal before the demodulation can take place. Otherwise, the interpretation of the transmitted symbols will be incorrect.

#### **D.** FOURIER TRANSFORM

One of the first steps typically done in signal analysis is the determination of the frequencies present in the incoming signal. This is done by taking the Fourier transform of the signal. The Fourier transform is calculated as

$$G(f) = \mathcal{F}\left[g(t)\right] = \int_{-\infty}^{\infty} g(t) e^{-j2\pi f t} dt, \qquad (1)$$

where g(t) is the incoming signal, integrated over time t, and G(f) is the value of the Fourier transform over frequency f. Conversely, the inverse Fourier transform is determined by

$$g(t) = \mathcal{F}^{-1} \Big[ G(f) \Big] = \int_{-\infty}^{\infty} G(f) e^{j2\pi f t} df .$$

<sup>(2)</sup>

Both of these equations can also be represented in terms of angular frequency  $\omega$ , where  $\omega = 2\pi f$ . Substituting this into Equation (1) gives

$$\mathcal{F}\left[g\left(t\right)\right] = \int_{-\infty}^{\infty} g\left(t\right) e^{-j\omega t} dt$$

(3)

When calculating the inverse Fourier transform in terms of  $\omega$ , it is necessary to divide the result by  $2\pi$  due to the relation between  $\omega$  and f.

The importance of the Fourier transform lies in the physical information it gives about the transformed signal. The spectrum given by the Fourier transform indicates the properties of the sinusoids necessary to recreate the signal (the phases and relative amplitudes of the sinusoids) [16, p. 96]. Periodic signals have Fourier spectrums that have discrete frequencies with finite amplitudes. Consider a signal

$$y(t) = 0.7\sin(2\pi 50t) + \sin(2\pi 120t)$$

(4)

where y(t) is comprised of two sinusoids. This signal, along with its single-sided Fourier transform (which has been truncated to more easily show the relevant portion of the spectrum) is shown in Figure 5. The signals here are sampled with a sample rate of 10.0 kHz. Although it is easy to see that the signal y(t) is periodic, it is clear that it is not a single sinusoid. It is also difficult to visually determine what the component sinusoids may be. Taking the Fourier transform easily enables the determination of any and all sinusoids present in the signal. This is, therefore, a very important algorithm for signal processing.

Figure 5. A sinusoidal signal with its two component sinusoids and its Fourier transform.

In order to calculate the Fourier transform of a signal using computers, the discrete Fourier transform (DFT) is used. For a sequence

$$x = x_0, x_1, \cdots, x_{N-1}$$

(5)

having length N, the DFT is

$$X[k] = \sum_{n=0}^{N-1} \omega_N^{kn} x[n]$$

(6)

where

$$\omega_N = e^{-j\frac{2\pi}{N}}.$$

(7)

Calculating the DFT directly, however, is computationally expensive, having complexity of order  $O(n^2)$ . The fast Fourier transform (FFT) algorithm was developed in 1965 as a method to more efficiently calculate the Fourier transform of a discrete sequence and has complexity of only order  $O(n \log n)$  [17]. Although not a new algorithm by any means, the efficiency of the FFT, when combined with the importance of the Fourier transform, has made it one of the most important algorithms developed in the last century [18].

## III. RESEARCH METHODS

#### A. OPENCL

As previously discussed, OpenCL is an open, "royalty-free native, cross-platform, cross-vendor standard" for use in the area of parallel programming on heterogeneous systems [15]. OpenCL is not a completely separate language. Instead, it is primarily a library of functions and data structures that enable programmers to write code using C that runs on any device for which there is a compiler. Utilizing an open computer language and library has several benefits over a proprietary one. First and foremost among these benefits is the ability to run on a vast multitude of systems, preventing a system from remaining in use simply because it is the only workable solution. In addition, because there is generally a large population of users, it is easier to both find bugs in the language and fix those bugs.

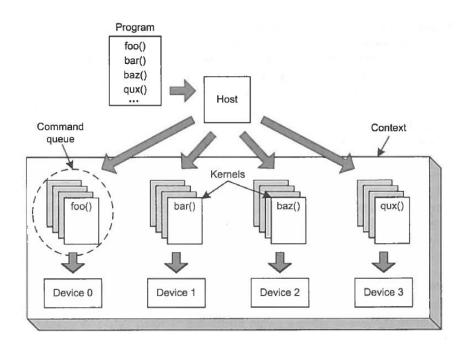

For one knowledgeable in the CUDA C language, the OpenCL programming model appears very similar—many of the differences between the two languages are only differences in terminology. For one without much experience in parallel programming, on the other hand, the OpenCL library is daunting. OpenCL calls any function that is intended to be run on one or more target devices a *kernel*. The list of possible kernels that can be called is known as the *program* [9, p. 7]. When kernels are called they are placed into a *queue*, which is itself a member of the *context*, which keeps track of the queue of the device and any associated data [9, p. 7]. All of these structures are managed by the application *host*. One of the best analogies for the organization of an OpenCL application is one comparing it to a game of cards, which can be seen in Figures 6 and 7.

Figure 6. A pictorial representation of a game of cards, from [9, p. 9]

Figure 7. A pictorial representation of kernel distribution among OpenCLcompliant devices, from [9, p. 8]

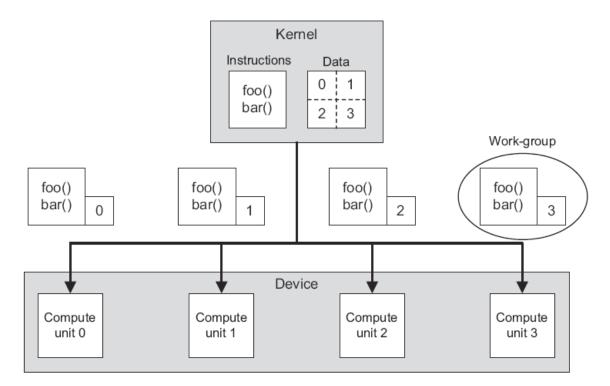

In addition to the organization of the application, an understanding about the break-up of the device is important to the OpenCL programmer. When a kernel is sent to the device, it runs multiple times according to the method by which it is called. Each

instantiation of the kernel runs on the smallest OpenCL processing element, the *work item*. Work items are organized into larger *work groups* [9, p. 65], with potentially thousands of work groups per *compute device*—the applications target device. A final important OpenCL term is the *compute unit*, which is the processing block handling the work group [9, p. 66]. A compute device contains multiple compute units, which can only execute on a single work group at a time [9, p. 66]. This is shown in Figure 8.

Figure 8. A visual representation of the deployment of work groups to compute units, from [9, p. 66].

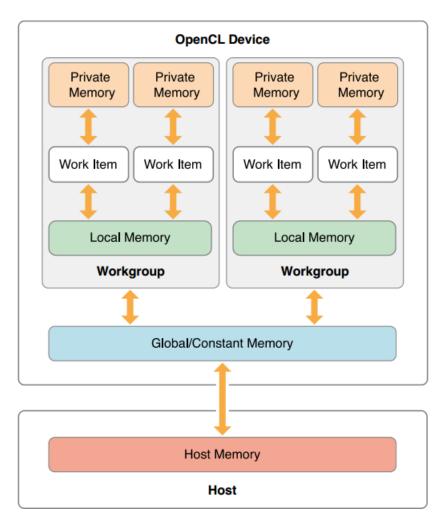

Finally, the OpenCL memory model is extremely important. In OpenCL, memory is classified as one of three types: *global*, *local*, and *private*. Global memory can be accessed by any work item of any work group, whereas local memory can only be accessed by work items of a specific group [9, p. 88]. Finally, private memory can only be accessed by a single work item [9, p. 88]. Global memory exists only in *buffers* that must be created by the host prior to the launch of the kernel. Local memory is normally initialized by the work items after the kernel has been launched, but local memory arrays

must first be defined by the host. Private memory has the smallest size and quickest access times of the three types while global memory is the largest and slowest [9, p. 88]. A pictorial representation of the types of memory is shown in Figure 9.

Figure 9. The OpenCL memory model, from [19].

# **B. DEVICES USED**

For this research project, three different processors were used from two different manufacturers. Two GPUs were used. The Tesla K20c and GeForce GTX 650 were both designed by NVIDIA. The one CPU used, a Xeon E5-2643, was designed by Intel. The

majority of the processor specifications to follow were obtained through OpenCL, while memory bandwidth and power consumption numbers were obtained through product datasheets.

### 1. NVIDIA GPUs

Both the Tesla K20c and GeForce GTX 650 use NVIDIA's latest compute architecture, named Kepler. Designed for maximum performance, the Kepler architecture is built with several features that give it strength in the area of data processing. The Kepler architecture utilizes newly designed "Streaming Multiprocessors (SM)" [20] (NVIDIA's organizational unit for groups of compute cores). These SMs each contain 192 CUDA cores [20]. In addition, the Kepler architecture supports "dynamic parallelism," enabling the "GPU to dynamically spawn new threads by adapting to the data without going back to the host CPU" [20]. Finally, the architecture allows for multiple CPU cores to utilize a single GPU at the same time [20]. Although the last two features were not utilized in the course of this project, both introduce areas for potential further research.

Because both GPUs utilize the same architecture, many of their OpenCL capabilities are the same. At the time this research was conducted, the NVIDIA OpenCL compiler supported the OpenCL standard only up to version 1.1. The GPUs both have maximum work group sizes of 1024 and can use memory addresses up to 32 bits in length. The final relevant capability similar across the two GPUs is the size of their local memory, 49 kB.

### a. Tesla K20c

The Tesla family of GPUs is NVIDIA's current high-performance GPU line designed solely for general-purpose computing on GPUs (GPGPU). In addition to the specifications listed above, the K20c has a clock frequency of 705 MHz, 13 SMs (equivalent to OpenCL compute units) for 2496 CUDA cores [21], and 5 GB of global memory. It also has a memory bandwidth of 208 GB/s [21] and can draw up to 225 W of power.

### b. GeForce GTX 650