# Alma Mater Studiorum - Università di Bologna

#### DOTTORATO DI RICERCA IN

# INGEGNERIA ELETTRONICA, DELLE TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

#### Ciclo XXXIV

Settore Concorsuale di afferenza: 09/E3 Elettronica

Settore Scientifico disciplinare: ING-INF/01

# HIGH PERFORMANCE AND ENERGY-EFFICIENT INSTRUCTION CACHE DESIGN AND OPTIMISATION FOR ULTRA-LOW-POWER MULTI-CORE CLUSTERS

Presentata da: Relatore:

Jie Chen Chiar.mo Prof.

Davide Rossi

Esame finale anno 2021

Thanks to the support of my company GreenWaves Technologies and the help of my professors and my wife.

# High performance and Energy-efficient Instruction Cache Design and Optimization for Ultra-low-power Multi-core clusters

# Jie Chen

Department of Electrical, Electronic and Information Engineering

University of Bologna

A thesis submitted for the degree of

$Doctor\ of\ Philosophy\ in$

Electronics, Telecommunications and Information Technologies Engineering

#### Abstract

High Energy efficiency and high performance are the key regiments for Internet of Things (IoT) end-nodes. Exploiting cluster of multiple programmable processors has recently emerged as a suitable solution to address this challenge. However, one of the main bottlenecks for multi-core architectures is the instruction cache. While private caches fall into data replication and wasting area, fully shared caches lack scalability and form a bottleneck for the operating frequency. Hence we propose a hybrid solution where a larger shared cache (L1.5) is shared by multiple cores connected through a low-latency interconnect to small private caches (L1). However, it is still limited by large capacity miss with a small L1. Thus, we propose a sequential prefetch from L1 to L1.5 to improve the performance with little area overhead. Moreover, we optimized the core instruction fetch stage with non-blocking transfer by adopting a  $4 \times 32$ -bit ring buffer FIFO and adding a pipeline for the conditional branch to cut the critical path for better timing. We present a detailed comparison of different instruction cache architectures' performance and energy efficiency recently proposed for Parallel Ultra-Low-Power clusters. On average, when executing a set of real-life IoT applications, our two-level cache improves the performance by up to 20% and loses 7% energy efficiency with respect to the private cache. Compared to a shared cache system, it improves performance by up to 17\% and keeps the same energy efficiency. In the end, up to 20% timing (maximum frequency) improvement and software control enable the two-level instruction cache with prefetch adapt to various battery-powered usage cases to balance high performance and energy efficiency.

# Contents

| 1 | Intr | roduct | ion                                              | 1  |

|---|------|--------|--------------------------------------------------|----|

|   | 1.1  | Backg  | round                                            | 4  |

|   |      | 1.1.1  | Multi-core architectures                         | 4  |

|   |      | 1.1.2  | Low-power multi-core architecture                | 6  |

|   |      | 1.1.3  | Instruction fetch subsystem                      | 11 |

| 2 | Rel  | ated w | vork                                             | 16 |

|   | 2.1  | Ultra- | low-power instruction memory                     | 16 |

|   | 2.2  | Impro  | wing Instruction Fetch Efficiency                | 23 |

|   | 2.3  | Instru | action Cache Prefetching                         | 24 |

|   | 2.4  | State- | of-the-arts ICache in ULP cluster                | 31 |

|   |      | 2.4.1  | Private Instruction Cache                        | 31 |

|   |      | 2.4.2  | Shared Instruction Cache                         | 33 |

|   |      | 2.4.3  | Multi-ported Instruction Cache                   | 35 |

|   | 2.5  | Thesis | s Outline                                        | 37 |

| 3 | Eva  | luatio | n of state-of-the-art Instruction Caches in PULP | 39 |

|   | 3.1  | Softwa | are and Program paradigm                         | 39 |

|   |      | 3.1.1  | Program methodology                              | 40 |

|   |      | 3.1.2  | Synthetic tests                                  | 42 |

|   |      | 3.1.3  | Benchmarks                                       | 42 |

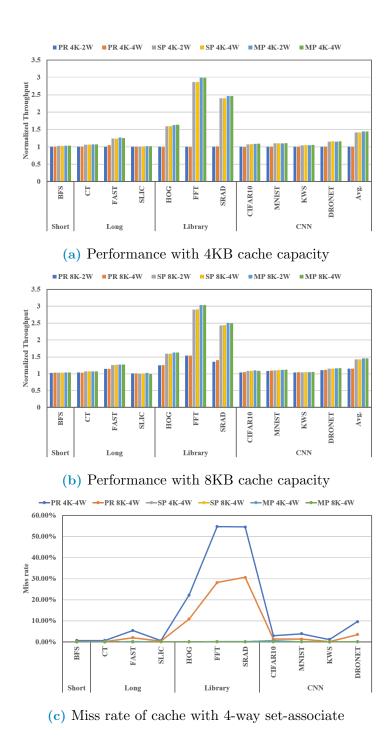

|   | 3.2  | Perfor | rmance Results                                   | 44 |

|   |      | 3.2.1  | The performance of synthetic tests               | 44 |

|   |      | 3.2.2  | The performance for real-life applications       | 47 |

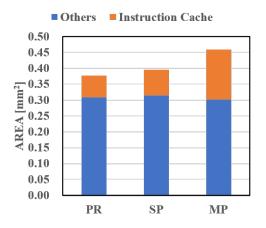

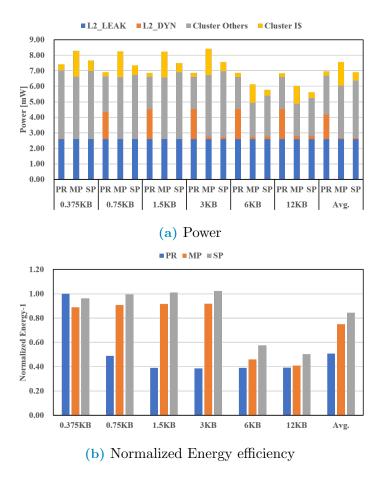

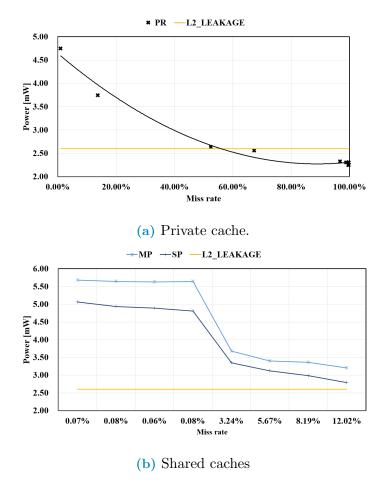

|   | 3.3  | Result | ts of physical implementation                    | 49 |

| Ρι | ublic | ations                                  | 95         |  |  |  |  |

|----|-------|-----------------------------------------|------------|--|--|--|--|

| 7  | Cor   | nclusions                               | 93         |  |  |  |  |

|    | 6.4   | Conclusion                              | 92         |  |  |  |  |

|    |       | 6.3.3 Discussion                        | 91         |  |  |  |  |

|    |       | 6.3.2 Physical Implementation Results   | 86         |  |  |  |  |

|    |       | 6.3.1 Performance Results               | 84         |  |  |  |  |

|    | 6.3   | Evaluation                              | 84         |  |  |  |  |

|    | 6.2   | Architecture                            |            |  |  |  |  |

|    | 6.1   | Overview                                | 79         |  |  |  |  |

| 6  | Cor   | e instruction fetch timing optimization | <b>7</b> 9 |  |  |  |  |

|    | 5.4   | Conclusion                              | 77         |  |  |  |  |

|    |       | 5.3.2 Physical Implementation Results   | 73         |  |  |  |  |

|    |       | 5.3.1 Performance Results               | 72         |  |  |  |  |

|    | 5.3   | Evaluation                              | 72         |  |  |  |  |

|    |       | 5.2.1 Out-of-order interconnect         | 71         |  |  |  |  |

|    | 5.2   | Architecture                            | 68         |  |  |  |  |

|    | 5.1   | Overview                                | 67         |  |  |  |  |

| 5  | Pre   | Prefething in L1 iCache                 |            |  |  |  |  |

|    | 4.4   | Conclusion                              | 65         |  |  |  |  |

|    |       | 4.3.2 Physical Implementation Results   | 61         |  |  |  |  |

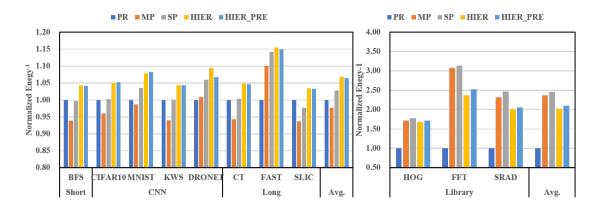

|    |       | 4.3.1 Performance Results               | 60         |  |  |  |  |

|    | 4.3   | Evaluation                              | 59         |  |  |  |  |

|    | 4.2   | Architecture                            | 57         |  |  |  |  |

|    | 4.1   | Overview                                | 56         |  |  |  |  |

| 4  | Two   | o-level instruction cache               | <b>56</b>  |  |  |  |  |

|    | 3.4   | Conclusion                              | 55         |  |  |  |  |

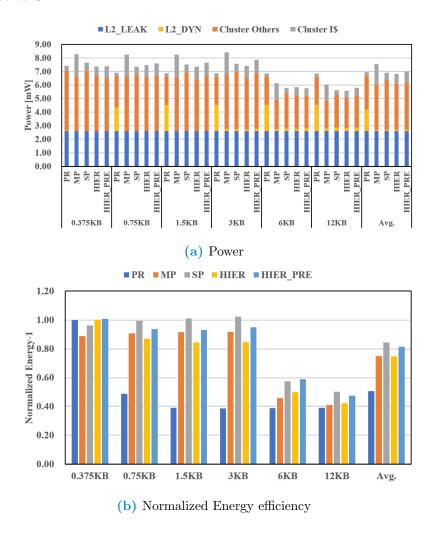

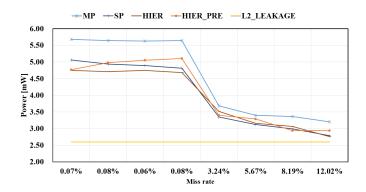

|    |       | 3.3.2 Power results                     | 50         |  |  |  |  |

|    |       | 3.3.1 Area and Timing results           | 49         |  |  |  |  |

Bibliography 96

# Chapter 1

# Introduction

In recent years, with the growing Internet of Things (IoT) markets for smart homes, smart cities remote control and monitoring nodes raising rapidly, the requirement for near-sensor processing devices with high performance and low power is more vigorous, especially when powerful embedded systems and machine learning are involved in this field. The traditional applications, such as thermostats, water meter monitoring, have less necessity for high performance and are often based on the ultra-low-power Micro Controller Unit (MCU) powered by the battery. While for other camera or audio based applications, such as home security, office people counting, voice control, etc, the complex signal processing algorithms require high performance and much larger power. As a result, these devices are always connected to the source, bringing more expense for installation and implementation from the commercial point of view. Thus, to save the power and the implementation fee in commercial practice, designing the high-performance and ultra-low-power IoT signal processing devices with a long battery lifetime becomes our goal.

In general, most of the IoT devices could be divided into three categories, i) the ultra-low-power MCU, receiving and transmitting the data from sensors to the sever with little computing capacity, mainly for controlling and monitoring some specific environments, running with Real-Time Operating System (RTOS); ii) the powerful general embedded multi-core SoC used in real-time camera surveillance powered by the source; iii) Digital Signal Processing (DSP) devices with accelerators, aiming at specific usage cases to save power, such as headphones and earbuds with Audio Noise

Control (ANC). Between the two latter categories, we consider that there could be a usage case that needs high performance and could be powered by the battery. That is a non-real-time usage case with fast response, for example, a smart locker with face recognition powered by the battery. Since the face image detection occurs several times a day, the devices are in sleep most of the time. Thus we concentrate our design on these low-frequency, high-performance usage cases.

To chase this market, the MCUs are apparently not suitable with poor performance. The powerful Linux based embedded multi-core SoCs with various accelerators are capable of fast computation. However, it is difficult for them to control the working power envelope below 10mW and the price including implementation fee. Besides, the specific usage cases limit DSPs' markets. One possible solution to extend the battery lifetime with relatively high performance is using an optimized (simplified) general multi-core platform with specified accelerators to maximize the performance both from instruction-level and thread-level parallelism. Thus, the first version of Parallel Ultra Low Power platform (PULP) is proposed based on Near-Threshold Computing (NTC) [46], which means that it is better to have N × simple cores running at a lower voltage than one core running at nominal voltage. The PULPv1 achieves 60 GOPS/W at 0.5 V in ST Microelectronics UTBB FDSOI 28nm technologies [92].

During the continued optimization of PULPv1, there is one power issue of the instruction Cache (iCache) in multi-core cluster when running OpenMP [78] based applications. The iCache is based on Static Random-Access Memory (SRAM) and consumes more than 50% of the cluster's power. Thus, it is necessary to reduce the iCache's power. Since the cache memory is only a few KB (4KB), in PULPv2, we propose to replace the SRAM with latched-based Standard Cell Memory (SCM) with controlled Placement and Route (P & R) [107]. Thanks to the 2 - 4× less read and write energy compared to the SRAM, the iCache's power occupation in cluster reduces to about 25% and the energy efficiency reaches to 135 GOPS/W [95]. However, even though the private iCache is simple and fast with only one cycle access latency, its relatively small cache capacity and the data duplication degrades the performance and energy efficiency. To increase the cache capacity seen by each core, shared iCaches are proposed to decrease the miss rate [67], the single-port

(SP) iCahce and multi-port (MP) iCache. The former uses low latency (one cycle) interconnect to ensure each core can access all the memory banks. Nevertheless, congestion exists when several cores access the same cache bank, leading to extra power consumption. Besides, the logarithmic interconnect increases the critical path and limits the operating frequency. The latter iCache based on multi-port memories is proposed to tackle the congestion issue. However, the multi-port memories generate large extra area and power. Moreover, it still has limited operating frequency because of large ports congestion in P & R. As a result, the MP iCache is only suitable for small cache capacity with a few KB. In the end, the shared iCaches have worse scalability than the private cache when the number of cores increases.

As mentioned above, continuous performance and power optimization are the key factors in the multi-core PULP cluster to adapt to the battery-powered, low-frequency, high-performance IoT market. The approach proposed in this thesis to match all these requirements is to leverage hierarchy iCache design. Hierarchy iCache uses different levels to solve different above issues. In practice, the upper-level cache L1 is implemented as private, and the lower-level caches are implemented as shared [56]. This design provides high access rates for the high-level caches and low miss rate for the lower-level caches. This ideal was proposed to reduce the speed mismatch between the core and the main memory. In this research, we try to follow this typical design method and adapt it to our ultra-low-power, high-performance design requirement. Besides, hardware prefetching in the L1 cache is explored to improve the performance continuously. Finally, a practical Static Timing Analysis (STA) is performed to help improve the timing in iCache by removing the critical path to balance the high performance and low power in multi-core PULP clusters with good scalability.

In this scenario, it is necessary to launch a detailed comparison for each iCache design in terms of area, performance, power to address the work in this thesis. In order to analyze these characteristics, a based-line Register-Transfer Level (RTL) of PULP cluster with private cache is required to enable the exploration over various real-life IoT applications. Besides, the physical implementation is done for each cluster featuring different iCaches. A specific target of this thesis is to evaluate the iCache architecture's overall influence on the performance and energy for the multi-

core cluster, analyzing the trade-offs between performance, energy and increasing the scalability in the multi-core ultra-low-power platform.

# 1.1 Background

#### 1.1.1 Multi-core architectures

Scaling performance by increasing clock frequency and instruction throughput of single-core have been proven to be not viable anymore due to the power wall and instruction-level parallelism (ILP) wall [40]. Besides, many applications are better suited to thread-level parallelism (TLP) methods, and multiple independent cores are commonly employed to increase a system's overall TLP. A combination of increased available space (due to refined manufacturing processes) and the demand for increased TLP led to the development of multi-core architectures. As a result, the trend changes from pushing a single complex processor to integrating several computing elements into a single integrated circuit die happened decades ago for general-purpose computing, high-performance and also the embedded world (Fig. 1.1).

Figure 1.1: Performance comparison between a single core and multi-core processor [36].

Thanks to the Moore's Law, with a hundred billion transistors now available, even multi-core features with complex cores arise. Intel's Xeon Broadwell, consisting of 3.2 - 7.2 billion transistors, provides up to 22 cores (up from 8 in Xeon Sandy Bridge). Each core has a very aggressively complex 8-issue design (up from 6-issue in Sandy Bridge). AMD EPYC server solution employs a CPU with 4.8 billion

transistors to provide 24 cores with two-way SMP support. Given the multi-core performance-per-area efficiency of small cores and the maximum outright single-threaded performance of large cores, ARM combines the two different cores to create asymmetric architecture. A strategy called "big.LITTLE", using several large cores paired with a few smaller simpler low-power cores, aims to decrease power consumption and prolong battery life instead of maximum multi-core performance for the phone or tablet.

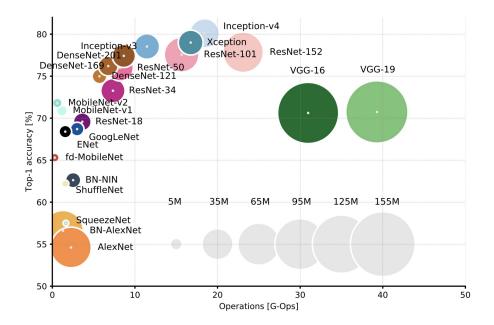

Figure 1.2: Top1 vs. operations, and size parameters. Top-1 one-crop accuracy versus the number of operations required for a single forward pass. The size of the blobs is proportional to the number of network parameters; a legend is reported in the bottom right corner, spanning from  $5 \times 10^6$  to  $155 \times 10^6$  parameters. Both these figures share the same y-axis, and the grey dots highlight the center of the blobs [14].

With the exploration of high-level (coarse-grained) parallelism, multi-core architecture can bring outstanding performance with the same power or get the same performance with less power, or a combination of both. Furthermore, by extending accelerator for specific applications, such as encryption and decryption engine, Graphic Processing Unit (GPU), and video coding engine, a heterogeneous platform can be designed to help unlock the energy efficiency potential, which is kept inaccessible by the burden of the Von Neumann fetch-decode-execute loop. However, the exploration of standard homogeneous multi-core baseline architecture to improve

the performance and energy efficiency never stops. With the trends of exploiting machine learning algorithms for dedicated applications, more and more optimized efficient models are proposed. Some of the top-rated optimized models are shown in Fig. 1.2, from the result of the accuracy versus the number of operations, the most exciting part resides in top-left, which requires less performance ( $\leq 10$  G-Ops) while keeping the high accuracy ( $\geq 75\%$ ). Besides, (Deep Neural Network) DNN relies on massive parallel multiply-and-accumulate (MAC) operations. It is suitable for multi-core low-end inference platforms both from performance and power consumption.

### 1.1.2 Low-power multi-core architecture

Multi-core with a simple core seems to be the best choice for low-power embedded end-nodes devices with relatively high performance, and for the parallelism maximization for intensive data analysis and for neural network inference applications. In the following subsections, two notable related works are described to highlight the low-power and high-performance characteristics of such architecture.

#### 1.1.2.1 STMicroelectronics Platform 2012

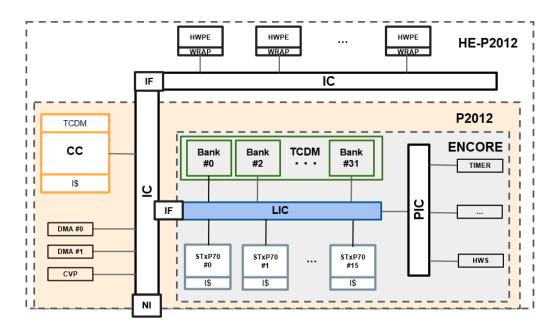

Figure 1.3: A simplified overview of P2012/STHORM cluster architecture.

Platform 2012 (P2012) is a general-purpose many-core accelerator for embedded design by STMicroelectronics composed of tightly-coupled homogeneous clusters [9]. With the design position of easy scalability, friendly implementation in a deep sub-micron process, it is easily programmable and is the basic platform for heterogeneous implementation. Each cluster features up to 16 processors and one control processor with independent instruction streams sharing a multi-banked Level one (L1) data memory, a multi-channel Direct Memory Access (DMA) engine, and specialized hardware for synchronization and scheduling. With the help of standard OpenCL and OpenMP parallel programming to provide the highest level of control on application-to-resource mapping and the addition of dedicated hardware (Intellectual Property) IPs, P2012 achieves extreme small area and energy efficiency by supporting domain-specific acceleration in the cluster level.

In P2012, each cluster, named ENCore, contains up to 16 STxP70-v4 cores sharing an L1 Tightly-Coupled Data Memory (TCDM) of 256 KB, 32 banks. Each core owns a 16 KB instruction cache, and there is no data cache. The asynchronous logarithmic interconnection (LIC) between the cores and the TCDM was designed to allow single-cycle access to the memory banks in case there is no contention [87]. Each cluster is equipped with a Hardware Synchronizer (HWS), which provides low-level services such as semaphores, barriers, as well as event propagation support with internal peripherals, such as Timer. The cluster also has a similarly designed peripheral interconnection used for communication between cores and peripherals (e.g., DMAs), memory outside of the cluster, and a Cluster Controller (CC) containing STxP70 core. As shown at the top, the cluster template can be enhanced with application-specific HardWare Processing Elements (HWPEs) interconnected to the ENCore with LIC to accelerate key functionalities in hardware to form a heterogeneous platform [20]. Compared with the original homogeneous P2012, it achieves up to 123 times speedup on the accelerated code region and saves 2/3 of the energy.

#### 1.1.2.2 Parallel Ultra-Low-Power platform

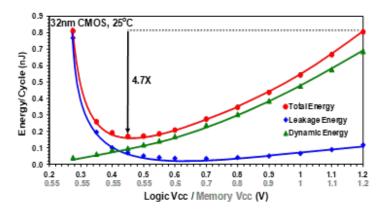

1.1.2.2.1 Near-threshold Computing To explore the high energy-efficient computing platform, Near-threshold Computing (NTC) is proposed. Power consumption is a quadratic function of voltage and is proportional to  $CV^2f$ . As the voltage drops, we get significant power savings at the expense of performance. However, total power is a combination of static or leakage power and dynamic power. NTC's idea is that we need to find the minimum energy point while scaling down system voltage.

Figure 1.4: Measured power, performance and energy characteristics across wide voltage range for an IA-32 processor fabricated in 32nm [46]

In Fig. 1.4, as the voltage is dropped towards the transistor threshold voltage (Vt), the switching power decreases, but at the same time, the leakage current increases. This means that the optimal combination of leakage and switching power has to be found. Reducing the voltage below a certain power threshold increases the leakage faster than switching power decreases, and the performance will also be degraded. The optimum operating point is usually slightly above Vt and is called the near-threshold operating point or minimum energy point. However, NTC brings the promise of an order of magnitude improvement in energy efficiency. The frequency degradation due to aggressive voltage scaling may not be acceptable for high-performance applications for single-core [46]. Thus, to recover the performance degradation, parallel multi-core execution is proposed. Based on NTC, a multi-core platform combines extreme energy efficiency and high performance with parallel computing.

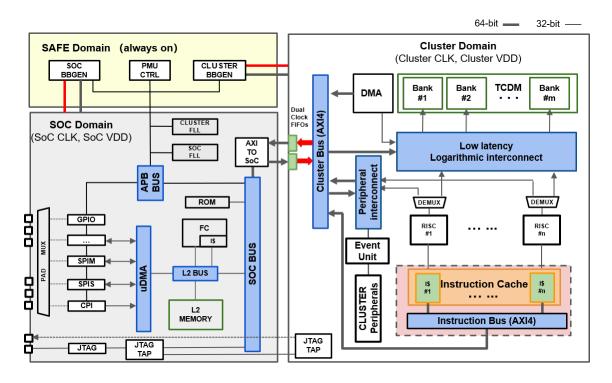

1.1.2.2.2 PULP architecture The Parallel Ultra-Low-Power Processing (PULP) platform is a general-purpose multi-core platform that achieves leading-edge energy efficiency and features widely tunable performance. PULP aims to satisfy the computational demands of IoT applications requiring flexible processing of data streams generated by multiple sensors, such as accelerators, low-resolution cameras, microphone arrays, vital signs monitors and so on. As opposed to single-core MCUs, a parallel ultra-low-power programmable architecture allows meeting the computational requirements of these applications without exceeding the power envelope of a few mW typical of miniaturized, battery-powered systems. Moreover, OpenMP, OpenCL, and OpenVX are supported on PULP, enabling agile application porting, development, performance tuning, and debugging (Fig. 1.5).

Figure 1.5: PULP block diagram [95]

Both the SoC and cluster domain feature with salable voltage and frequency. In the ultra-low-power parallel cluster, a tightly-coupled 1 cycle shared multi-bank L1 data memory is connected with each core through a low latency interconnect. The L1 data memory can be sized from 16KB SRAM to 32KB SRAM + 16KB latch-based Standard Cell Memories (SCM) heterogeneous memory architecture. Concerning SRAM memories, SCMs can achieve a lower density (by a factor of  $\sim 3x$ ), with the

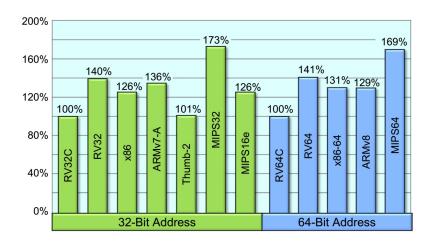

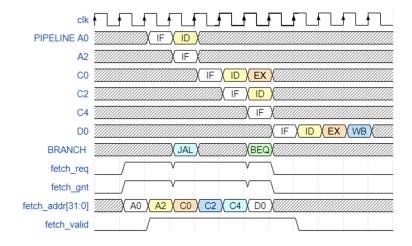

key benefit of providing much smaller energy per access (~4x) [107]. There are N (2 - 16) configurable, simple one-issue cores in the cluster. The cores have a private instruction cache in PULPv1 and PULPv2 or shared instruction cache in PULPv3 connected to the cluster's Advanced eXtensible Interface (AXI) to access Level two (L2) memory in the SoC domain. One cycle hardware synchronization among all the cores to automatically manage idle cores' shutdown and support OpenMP and OpenCL pattern is implemented. Besides, an event unit to trigger idle cores is also employed to help power management. To exchange TCDM data with external L2 memory and peripherals, a lightweight, ultra-low-latency, multi-channel DMA is responsible for providing fast and flexible communication [91]. The DMA uses minimal request buffering and features a direct connection to the TCDM to eliminate the need for internal buffering, which is very expensive in terms of power. Finally, the RISC ISA-based (Reduced Instruction Set Computer - Instruction Set Architecture) core varies from OpenRISC (OR10N) to RISC-V (RI5CY) because of RISC-V compress instruction and easily extendable features (Fig. 1.6).

Figure 1.6: RISC-V Offers Simple, Modular ISA [55]

The cluster domain is responsible for parallel acceleration to improve performance, while the SoC domain is responsible for I/O and system control. A fabric controller (FC) takes control of all SoC by adjusting the (Power Management Unit) PMU and (Frequency Lock Loop) FLL, configuring the peripheral IPs, and cooperating with cluster to be responsible for data movement from peripheral to L2 memory with the help of micro DMA (uDMA). The always-on safe domain helps

aggressively manage idle power with different power modes (deep sleep, sleep, idle and full active mode etc.). In the end, with the help of body-biasing to reduce leakage power, PULPv3 achieves 385 G-Ops/W [94].

#### 1.1.3 Instruction fetch subsystem

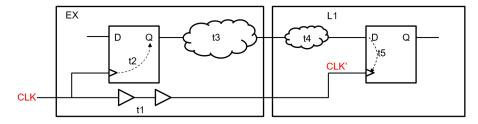

#### 1.1.3.1 Instruction fetch stage in RI5CY

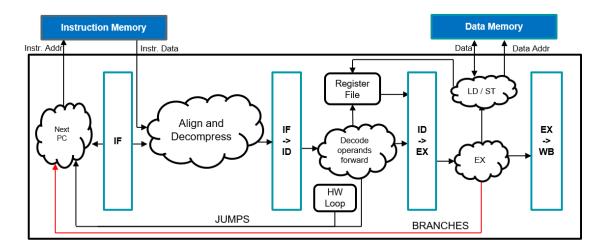

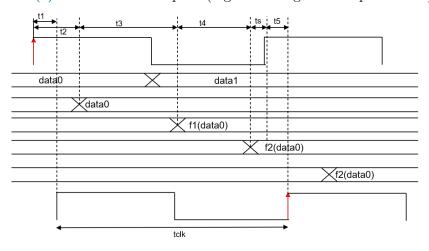

The processing elements in the cluster are based on RI5CY, a small and efficient 32bit, in-order RISC-V core with a 4-stage pipeline that implements the RV32IM[F]C instruction set architecture (Fig. 1.7). The core supports a custom extension to achieve higher code density, performance, and energy efficiency [33] [24]. It started its life as a fork of the OR10N CPU core based on the OpenRISC ISA. By inheriting custom ISA extensions including Hardware Loop (HWLP), bit manipulation, Single Instruction, Multiple Data (SIMD)-like instructions of vector operations, dot production for DSP, its performance speeds up to 9.5 times compared to the standard RV32IMC to 3.19 Coremark/MHz. Compared with OpenRISC ISA, RISC-V's fetch instruction implementation is more complicated. Firstly, since there is no delay slot in RISC-V ISA, the jump loses one cycle, and the next instruction is already being fetched and probably ready in the Instruction Fetch stage (IF). Secondly, there is no set-flag instruction and no branch prediction. As a result, the branch can only be taken after the execution stage (as shown in the red line) to re-target the Program Counter (PC). This combination path from the Execution stage (EX) to the instruction fetch interface outside the core will be on a critical path.

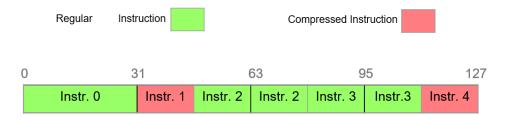

Thirdly, the instruction memory is word-aligned and does not accept misaligned accesses. With the combination of compressed instructions and normal instructions, the cross-word normal instruction needs to be assembled from two words (such as instr.2 and instr.3 in Fig. 1.8), except that if the lower half word is compressed such that there is no need to fetch next ready word. In this way, the core prefetcher needs to buffer at least two words. Therefore with the 32-bit fetch interface, four words are buffered in First In, First Out (FIFO) buffer to meet the consecutive pipeline requirement or four words (one cache line) for optimal performance and deal with

Figure 1.7: RI5CY block diagram

cache misses.

Figure 1.8: Misalignment of compressed instructions

#### 1.1.3.2 Instruction fetch interface to iCache

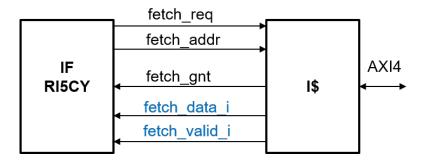

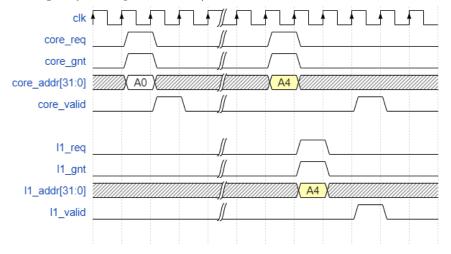

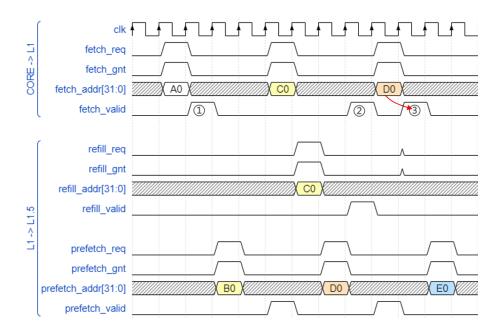

As shown in Fig. 1.9, there are two channels between the IF and iCache - request and response channel. The core sends the fetch request with a target address. If the cache's TAG hits, it responds to the core with valid data in one cycle; if the iCache has a TAG miss, it waits AXI refill for at least 15 cycles before responding to the core.

Since the fetch request depends on the inner combination circuit generated by fetching valid and fetch data to issue the request as soon as possible. As a result, there are two types of long delay paths. One is from the fetch request (fetch\_req) to cache TAG lookup and the fetch\_gnt generated by hardware loopback using handshaking protocol. The other is from fetch\_valid or fetch\_data to fetch\_req. As a result, the critical path degrades the systems maximum frequency and scalability.

Figure 1.9: Instruction fetch interface. I\$ stands for iCache.

#### 1.1.3.3 Instruction cache structure

The L1 iCache connected to the core is used for instruction refill to hide the memory access latency. Its inner structure consists of the memories for instruction's TAG and DATA storage and the cache controller logic to manage the requests and the refills. It can be configurable in its total size, associativity, line size and replacement policy (including FIFO, Least recently used (LRU) or Random). The iCache has two main architectures:

- Private iCache: each core has its private iCache and a separate cache line refill path connected with AXI to the main memory, leading to high contention on external L2 memory. It is used in PULPv1 and PULPv2.

- Shared iCache: there is no difference between the private architecture in the data side except for the reduced contention L2 memory (only one line refill path exists). The shared iCache inner structure compromises a configurable number of banks, a centralized logic to manage requests and fairness mechanism to ensure the cores access to all cache banks. Thus, there are two ways: one is to use crossbar with round-robin scheduling that guarantees fair access to each banks with single port. The other is to use multiple port memories to eliminate the access congestion. Finally, in case of concurrent instruction missed from two or more banks, a simple bus handles line refills in round-robin towards the L2 bus. This structure is used in PULPv3 and Mr Wolf [85].

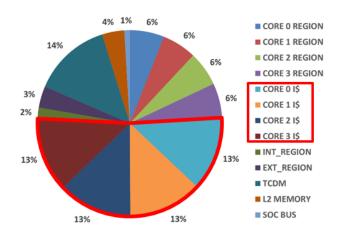

Figure 1.10: PULPv1 cluster power breakdown [92]

#### 1.1.3.4 Instruction cache issue

In the PULPv1 with a private iCache based on SRAM, the iCache takes about 52% of the total cluster power shown in Fig. 1.10. Then, with the limitation of small cache capacity below 8KB, PULPv2 replaces the iCache's SRAM with SCM, reducing the power occupation of iCache to 25% [95]. Even though private cache is small and fast with only one cycle access latency, its relatively small cache capacity degrades the performance in terms of high capacity miss compared with the shared cache. However, the single-port shared cache (SP) suffers from high congestion when accessing the shared banks, especially with parallel programming such as OpenMP. Furthermore, the most critical issue is the scalability of the shared banks. When the core number increases to 8 or 16, the logarithmic interconnect leads to heavy congestion and timing issues. Moreover, due to the four pipelines RI5CY core's unconditional branch, the critical path from the core's EX to iCache worsens the situation.

To solve the single-port shared cache contention issue, on the one hand, we can increase the cache line size to reduce the core fetch frequency. The proposed cache line size can vary from 8 bytes to 32 bytes. On the other hand, a multi-port shared cache (MP) can be used, which keeps each core's read control logic private with n-port shared memory banks. Each private cache controller can access the memory banks simultaneously without contention, and a master controller is responsible for refilling from L2 memory and writing to the shared memory banks. The MP ensures

| Cache type     | Private | Shared      | Shared     | Target |

|----------------|---------|-------------|------------|--------|

|                |         | Single-Port | Multi-port |        |

| Cache capacity | Small   | Large       | Large      | Large  |

| Performance    | Low     | High        | High       | High   |

| Congestion     | No      | Yes         | No         | No     |

| Area           | Small   | Small       | Large      | Small  |

| Timing         | Good    | Bad         | Bad        | Good   |

Table 1.1: The pros and cons of different instruction cache architectures

one cycle hit access latency and shows the best performance while being suitable only for small cache sizes. However, the multi-port memories generate significant area overhead and lead to timing and power issues in P & R. Finally, how to solve this one cycle access from core fetch interface to instruction cache with large cache capacity, high performance, less congestion, small area, and good timing to meet the high-performance and low-power design requirement is the goal in our work (Table 1.1).

# Chapter 2

# Related work

Since the instruction access pattern has strong spatial and temporal locality, the instruction cache is very sensitive to increased access latency. Besides, the iCache's structure is more simple than the data cache with its read-only nature. However, iCache can still consume up to 50% of the overall system energy with the high-performance requirement. Thus, their optimization is a strict requirement for programmable ULP architectures [92]. Nevertheless, high performance means high power and energy, and various hardware architectural techniques for balancing the two factors are proposed [74] [73].

# 2.1 Ultra-low-power instruction memory

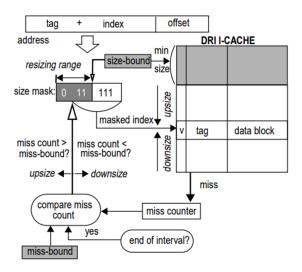

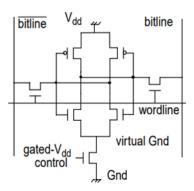

A standard methodology to reduce the energy consumption of the instruction memory in ULP systems is to adopt advanced memory technologies. Powell et al. [81] propose a circuit design named 'gated  $V_{dd}$ ', which adds an extra transistor in the supply voltage path or ground path of the SRAM cell to form a 7T SRAM. It can reduce leakage power by gating the unused sections of a dynamically resizable iCache. In a Dynamically ResIzable instruction-cache (DRI iCache) [113], the key point is to turn off or to gate unused sections in iCache to estimate and adapt to the required iCache size dynamically (Fig. 2.1. The DRI iCache monitors itself in fixed-length sense *interval* with adaptive parameters, measured in a number of dynamic instructions (e.g., one million instructions). A miss counter counts the number of cache misses in each sense interval. At the end of each sense interval,

the cache upsizes/downsizes, depending on whether the miss counter is lower/higher than a preset miss-bound value. A preset size-bound value is set to avoid thrashing. Thus, the 7T SRAM is shown in Fig. 2.2 by adding an extra transistor in the supply voltage path or ground path of the conventional SRAM cell to gate the power supply when the SRAM is unused. The results indicated that a wide NMOS dual-Vt gated-Vd with a charge pump reduces leakage most with minimal impact on cell speed and area.

Figure 2.1: A direct-mapped DRI iCache's anatomy (same for set-associative caches)

[92]

Figure 2.2: SRAM with an NMOS gated-Vdd [92]

Furthermore, the ultra-low-voltage operation of memory cells has become a topic of much interest due to its applications in very low energy computing and communications. As conventional 6T SRAM failed to archive subthreshold operation due

to the effects of  $V_t$  variation [13], researchers have considered different configuration SRAMs for subthreshold operations having single-ended 8T [16] [110] or 10T bit-cells to improve stability. Ickes and al. [44] present a 10 pJ/cycle 32-bit microprocessor SoC with two 4KB custom 8T SRAMs (Fig. 2.3) and a small 1 KB (8 x 128B) instruction cache based on standard cell latches.

Figure 2.3: Zoom of 8T SRAM Architecture [44].

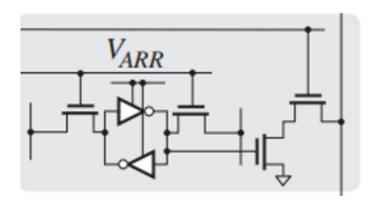

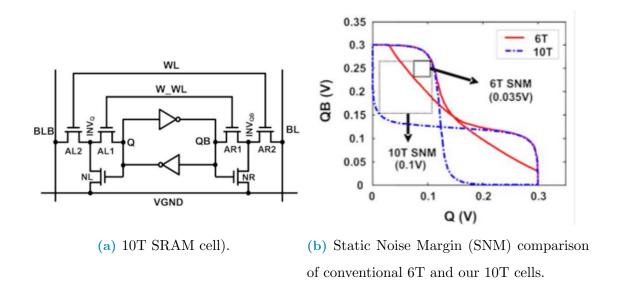

Chang et al. [17] propose a differential 10T bit-cell that effectively separates read and write operations to achieve high cell stability (Fig. 2.4a). In read mode, WL is enabled, and VGND is forced to 0V while remaining disabled. The disabled make data nodes ('Q' and 'QB') decoupled from bitline during the read access. Due to this isolation, the read Static Noise Margin (SNM) of the 10T cell is almost the same as the hold SNM of a conventional 6T cell, the read stability is remarkably improved in this 10T cell (Fig. 2.4b). During write mode, both WL and are enabled to transfer the write data to cell node from bitlines.

By boosting  $V_{WL}$  and  $V_{WwL}$  by 100 mV (at 300 mV) and sharing a common VGND node with several SRAM cells, the 10T SRAM has good write ability and small area overhead. Besides, the leakage power of the proposed 10T bit-cell is close to that of the 6T. Based on the 10T SRAM optimized for sub-threshold operation, Myers et al. [75] introduce a Cortex M0+ based system with two 4KB 10T SRAM to achieve ultra-low power.

Moreover, Magnetic Random Access Memory (MRAM) is a promising emerging memory technology because of its advantages, such as non-volatility, high density, and scalability. In particular, Spin Orbit Torque (SOT) MRAM is gaining interest as it comes along with all the benefits of its predecessor Spin Transfer Torque (STT)

Figure 2.4: Notion of 10T SRAM [17].

MRAM. Especially the split of read and write paths in SOT-MRAM promises faster access times and lower energy consumption than STT-MRAM. Oboril et al. [77] show that a hybrid combination of SRAM for the L1-data cache, SOT-MRAM for the L1 instruction cache and L2 cache can reduce the energy consumption by 60% while the performance increases by 1% compared to an SRAM-only configuration, targeting a 65 nm technology node.

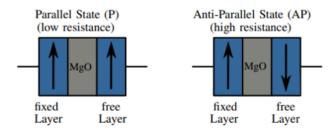

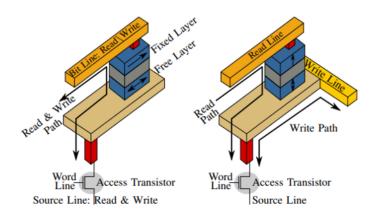

In Spin Orbit Torque memories, the Magnetic Tunnel Junction (MTJ) cell stores the data as a resistance state value. An MTJ device consists of two independent ferromagnetic layers separated by a very thin (a few nm) barrier oxide layer such as magnesium oxide (MgO) (Fig. 2.5). One of the two ferromagnetic layers has a fixed magnetization with a fixed magnetic field. Hence, this layer is known as the fixed or reference layer. In contrast, in the second magnetic layer, called the free layer, the magnetization can be freely rotated based on the current direction flowing through the MTJ device. When the direction of the magnetic field of the free layer is parallel (P) to the fixed layer, the MTJ cell has a low resistance value. Instead, when the magnetization of the free layer is opposite or anti-parallel (AP) to the fixed layer, the MTJ cell has a high resistance value. These high and low resistance values represent logic' 1' and' 0' values.

Figure 2.5: MTJ resistance according to the magnetization of the free layer [77].

This MTJ cell is the core part of a bit-cell in SOT-based memories as well as in STT-MRAM, as shown in Fig. 2.6. However, to eliminate the shortcomings of STT-MRAM, the SOT-MRAM bit-cell has an additional terminal to separate the (unidirectional) read and the (bidirectional) write paths which are perpendicular to each other. The terminals comprise a read line, a write line, a source line and a word line. The word line is used to access the required bit-cell during memory access via the NMOS-based access transistor. The comparison of the features among SRAM, STT-MRAM and SOT-MRAM are shown in Table 2.1. We can see that SOT-MRAM is suitable for cache memory with a smaller area, read latency and energy, especially for read-only instruction cache.

Figure 2.6: Bit-cell for STT-MRAM and SOT-MRAM [77].

|                          | 6T-SRAM | In plane STT-SRAM | SOT-MRAM       |

|--------------------------|---------|-------------------|----------------|

| Data storage             | Latch   | Magnetization     | Magnetization  |

| Non-Volatility           | no      | yes               | yes            |

| $Area [mm^2]$            | 2.78    | 1.63              | 1.80           |

| Read Latency [ns]        | 2.17    | 1.2               | 1.13           |

| Write Latency [ns]       | 2.07    | 11.22             | 1.36           |

| Read access Energy [pJ]  | 587     | 260               | 247            |

| Write access Energy [pJ] | 355     | 2337              | 334            |

| Leakage power [mW]       | 932     | 387               | 354            |

| Process                  | CMOS    | CMOS + STT-MJT    | COMS + SOT-MJT |

| Scalability              | -       | +                 | +              |

| Endurance                | ++      | +                 | +              |

| Radiation immune         | -       | +                 | +              |

| Bit failure Rate         |         | -                 | ?              |

Table 2.1: Comparison of various memory technologies for a 512 KB memory [77].

Then, Garello et al. [32] demonstrate for the first time full-scale integration of top-pinned perpendicular MTJ on 300 mm wafer using CMOS-compatible processes for spin-orbit torque (SOT)-MRAM architectures with 62 nm devices. Kuan and Adegbija [61] show that an energy-efficient, highly adaptable last-level STT-RAM cache (HALLS) can reduce the average energy consumption by 60% in a quad-core system while introducing marginal latency overhead. In order to solve the backward of long write latency and high write energy of STT-MRAM to fit Last-Level Cache (LLC), HALLS allows the LLC's configurations to be dynamically adapted to executing applications cache configuration and retention time requirements. Thus, the STT-MRAM can be a viable option for mitigating the overheads of implementing the STT-RAM in LLC.

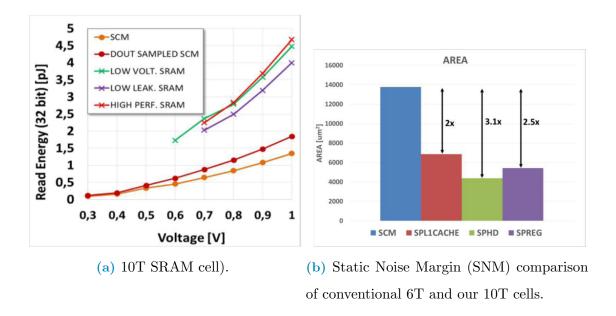

However, the subthreshold SRAM has a limited voltage range and large read energy, STT-MRAM has a slow write speed and high write power, and SOT-MRAM has a large area for high-density memory. Another solution for the small low-level cache is to use latch-based Standard Memory Cells (SCM) because of their design flexibility, ease of implementation, and robust operation at low supply voltages. Te-

Figure 2.7: Notion of SCM [106].

man et al. [106] present a controlled Placement for the synthesis and place and route (P & R) to optimize the distinct and regular structure of an SCM array. Through careful floor planning, the specific structure of these entirely digital blocks can be manipulated in order to optimize their placement and minimize routing congestion and wire length. The proposed architecture for controlled SCMs includes dual-level write clock-gating, latch-based storage, and a NAND/NOR tree for read mux realization. These components are instantiated in RTL and placed during the floorplanning stage of the P & R flow. High-optimized SCM Macro are inserted, leading to a structured, non-congested layout with close to 100% placement utilization and reduced wire length. Based on that, PULPv2 [95] replaces SRAMs with SCMs in the instruction cache and increases the SoC energy efficiency by 38%. SCMs present extremely interesting features for small memory size, low-voltage, and energy-efficient designs, since (i) they can operate with very low voltage, even lower than 10T SRAMs optimized for low voltage [17], and (ii) their energy per access is significantly smaller than SRAMs  $(2-4\times)$  (Fig. 2.7a). Nevertheless, although the controlled placement of standard cells memory array reduces area overhead [107], there is still  $2\times$  the area of the same size SRAMs-based memory (Fig. 2.7b). It is thus clear that since there is a strong motivation to use energy-efficient but lowdensity memories for instruction cache, there is a strong push to maximize the effective capacity of the caches through sharing schemes.

# 2.2 Improving Instruction Fetch Efficiency

Given a specific cache capacity, the miss rate of instruction fetch is a critical factor influencing performance and energy efficiency. Modern processors usually use two-way and four-way set-associative caches to reduce conflict misses. Besides, instruction prefetching is implemented inside or outside the core [100], including branch prediction [115] are effective methods to boost cache performance by reducing compulsory and capacity miss. Support of compressed instructions is also effective in decreasing capacity misses.

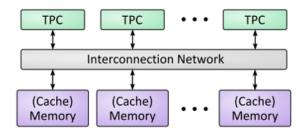

In this direction, we propose a hierarchical instruction cache with a 4-way set-associative design, which also benefits from the RISC-V' C' extension for compressed instructions. Sharing instruction memory is not new and has been mainly exploited in high-end computing platforms such as General Purpose Graphic Processing Units (GP-GPU). In GP-GPUs, all the compute units in each multiprocessor execute their threads in lock-step according to the order of instructions issued by the instruction dispatcher, which is shared among all of them [112].

Figure 2.8: GPU with Thread Processing Cluster (TPCs) and Memory Banks [112].

Besides, all shared-memory multiprocessing architectures supporting OpenMP can benefit from energy reduction by reducing the instruction fetch miss rate with a larger cache capacity. Loi et al. [67] present two multi-banked shared instruction caches to solve the private cache's small capacity issue in PULP. The private cache achieves higher speed due to the simple design, but its performance is limited by the small cache capacity for each core, leading to a high miss rate. Moreover, the parallel program's redundant copies in the system may waste the bandwidth to the

main memory, leading to more power consumption. By combing all the cache banks to share with all cores, the shared cache is proposed to solve the small cache capacity issue, which offers a low miss rate at the cost of minimum hardware area. However, the congestion of accessing the same cache banks may degrade the performance, and hardware complexity generates lower speed. Furthermore, multiple port memory is used inside the cache bank for TAG and DATA to solve the congestion issue. Nevertheless, with increased large hardware area and additional miss penalty, the performance of multi-port shared cache may drop compared with the single-port shared cache. As a result, it is suitable only for cache with a small memory size - a few KB.

# 2.3 Instruction Cache Prefetching

Without introducing a large area/energy penalty and boosting the performance, the importance of latency hiding techniques such as prefetching grows further. Prefetching means prefetching the next N-line to hide the latency of the core. Prefetch on miss and tagged prefetch are proposed by Smith [100]. On a miss, prefetch on miss always fetches the next line as well. It can cut the number of misses for a purely sequential reference stream in half. Tagged prefetch can do even better. In this technique, each block has a tag bit associated with it. When a block is prefetched, its tag bit is set to zero. Each time a block is used, its tag bit is set to one. When a block undergoes a zero to one transition, its successor block is prefetched. If fetching is fast enough, this can reduce the number of misses in a purely sequential reference stream to zero. However, it is unsuitable for non-sequential execution paths caused by jumps, conditional branches, and system calls. Despite these shortcomings, it is still an effective strategy to reduce cache misses by 20-50%.

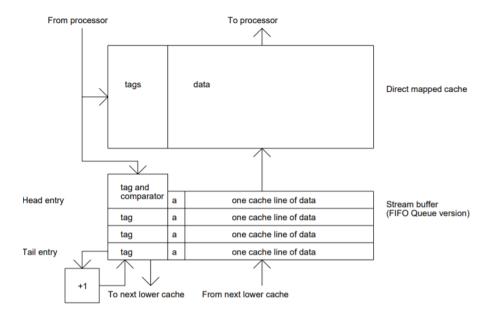

Figure 2.9: Sequential stream buffer design [52].

Unfortunately, the large latencies in the base system can make this impossible. Thus, Jouppi [52] presents a prefetching scheme using stream buffers in Fig. 2.9 to prefetch cache lines starting at a cache miss address. This technique is more effective than previously investigated prefetch techniques using the next lower level in the memory hierarchy when pipelined. On a cache miss, sequential cache blocks are prefetched into a separate FIFO stream buffer until it is filled to avoid L1 cache pollution. Next time, when the L1 cache sees a miss, the first entry of the stream buffer is checked, and, on a hit, a block is brought into the L1 cache. Jouppi also explored using multiple streaming buffers in parallel that can prefetch multiple intertwined reference streams.

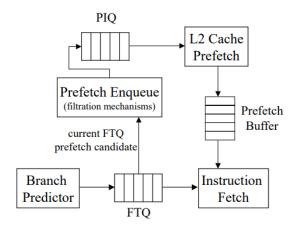

Fetch-directed instruction prefetching (FDP) [88] separates branch predictor and instruction cache, so the branch predictor can run ahead of the instruction cache fetch (Fig. 2.10). The branch predictor produces fetch blocks into a Fetch Target Queue (FTQ), then by using Cache Probe Filtering (CPF) to remove useless prefetch blocks in the FTQ, it sends only useful prefetch addresses to a Prefetch Instruction Queue(PIQ) and the branch predicted fetch blocks could be accurately prefetched and thereby saving bus bandwidth to the L2 cache. This FDP relies on accurate branch predictors and a sufficiently large Branch Target Buffer (BTB) to cover the control flow.

Figure 2.10: Fetch Directed Prefetching Architecture [88].

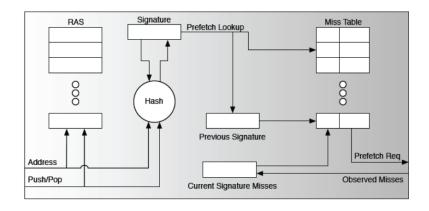

Proactive instruction prefetching (PIF) [26]-[27] is based on the fact that the stream of instruction cache misses is repetitive, and it eliminates the future instruction cache misses directly by tracing these temporally correlated streams. Based on that, RAS-directed instruction prefetching (RDIP) [60] correlates instruction cache misses with the program context captured from the Return Address Stack (RAS). It stores these misses in a *Miss Table* that is looked up using the signatures formed from the contents of the RAS (Fig. 2.11)). They simply XOR the bit-string representing the RAS state to 32-bit signatures. It brings 2% performance improvement compared to PIF with nearly 3X reduction in storage and 1.9X reduction in energy overhead. However, the main shortcoming of the temporal prefetchers is their high storage budget requirements, larger than 60 KB.

Figure 2.11: RAS-directed instruction prefetching architecture [60].

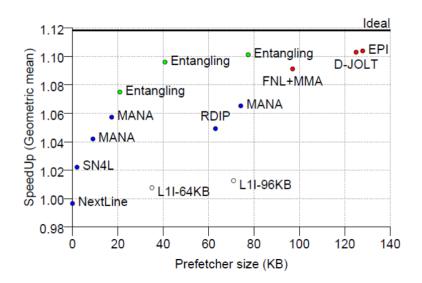

In the IPC-1 [41], numerous hardware instruction prefetchers were published. D-

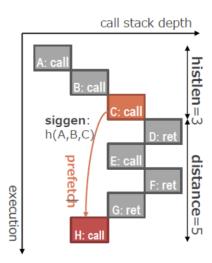

JOLT [104] is a refinement of RDIP. It improves by implementing a new signature generation mechanism that generates the prefetches from a FIFO structure that stores the most recent function return addresses instead of the stack structure used by RDIP. They investigate the characteristics of the RDIP from the following three aspects: Siggen, Histlen and Distance (Fig. 2.12). By increasing the history length of the number of addresses used to generate a signature, D-JOLT can improve the prefetch accuracy while leading to less capacity efficiency. Besides, with a larger time distance of the signature associated with the generated miss address, D-JOLT can improve the prefetch coverage and be in time while losing some accuracy. With these observations, they propose a novel Siggen using a FIFO, which can use the correlations of the last function calls, and a hybrid combination of three prefetchers that consume three miss tables. Finally, D-JOLT consumes a large capacity to achieve high performance. With an 8KB entry miss table, it gives total storage of 125KB [90].

Figure 2.12: Three main characteristics of the RDIP analyzed by D-JOLT. Each block represents a dynamic instruction sequence with a call/return instruction at the end. The Siggen is the algorithm to generate a signature. The histen is the number of addresses used to generate a signature. The Distance indicates how much time has elapsed since the signature associated with the miss address was generated. This figure shows the prefetch block address from the call instruction of C is H, using h(A, B, C) [104].

FNL-MMA combines a Footprint Next Line (FNL) prefetcher and a temporal correlation prefetcher (Multiple Miss Ahead (MMA)) on the I-Shadow cache, which

is a small tag-only cache. FNL is an enhanced next line prefetcher with extra trace recording tables that estimate if a cache line is worth prefetching. MMA selects the look-ahead distance to avoid the late prefetches in the Next Predicted Miss prefetcher (NPM) for non-continuous prefetch blocks. With an 8K entry miss table, it takes total storage of 97KB [90].

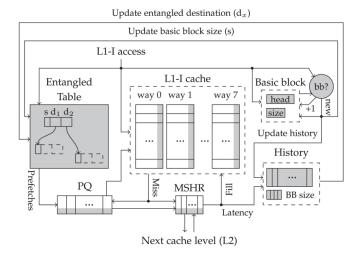

EPI [89] introduced the concept of entangling the cache line to be prefetched (destination) with a source cache line such that the destination would be prefetched when the source cache line is encountered. For an cost-effective EPI [89], only the head (first cache cache) of a basic continuous block for **src** and **dst** is paired. Fig. 2.13 shows the basic implementation of the EIP in the right-top part, a *Basic block* computes the head (first cache line) and size of a dynamic basic block by simply comparing the current address with the head address plus size. Once a new basic block is detected, it is stored in the *Entangled table* (left part of Fig. 2.13).

Figure 2.13: Overview of the Entangling I-prefetcher with hardware extensions shown in gray. The Basic block registers head and size keep track of the current basic block. History is a small circular queue and each entry records basic block information: head, size and timestamp of the first L1I access. Entangled is a cache-like structure and each entry consists in a src-entangled cache line, its basic block size, and a compressed array of dst-entangled cache lines (for the advanced optimization techniques, a confidence counter is associated to each destination). The L1I, PQ and MSHR are extended with information on timing (the timestamp when the request was issued) and on the src-entangled (position of the source in the Entangled table and an access bit indicating if the access stems from a demand access or a prefetch) [90].

To build entangled pairs for timely prefetching, first, it stores the recent history of the basic block heads together with the timestamp of their first access to L1 iCache to a small circular queue called *History buffer*. Second, it calculates the latency of demand L1 iCache miss with the help of start and end timestamps. The start timestamp is held in the miss status holding register (MSHR) with two extra fields: one access bit for demand misses and a pointer to *History buffer*. The access bit is to distinguish a demand miss or prefetch miss to track the latency of the prefetches to compute the actual latency on a late prefetch. The prefetches issued in PQ also have timestamps, and their access bit is set to 0. PQ also exchanges with MSHR when the prefetches miss in iCache. When a late prefetch happens, the corresponding access bit is set to 1. The end timestamp can be obtained with the time of the cache fill. When the access bit in MSHR is set to 1, and the history pointer is valid, it means a src-entangled cache line is found, and then the Entangled-table is updated. If the access bit is 1 and the history pointer is not valid, no src-entangled is searched for. In the end, once there is a hit in the Entangledtable, the current and dst-etangled basic blocks are prefetched. Other optimizations, such as adding confidence, merging spatio-temporal basic blocks and compressing destinations to improve the performance-area trade-off, are added. Typical EIP [89] models highly associative structures (e.g., a +1000-entry history buffer and a 34way Entangled table which gives +8K entries). Its total storage requirements are 127.9KB. However, the size of the cost-effective EPI can reduce to 40KB.

Besides these large metadata prefetch strategies, other types of prefetchers interact with hardware structures, such as the branch predictor (e.g. BTB directed), to gain insights into the program's execution ahead of time. As a result, they require intrusive changes in the processor design. One of such prefetcher is SN4L [4]. It is based on FDP and comprises three predictors: selective next-four-line (SN4L), discontinuity (Dis), and BTB prefetching. SN4L improves next-four-line prefetcher using a usefulness filter. Only previously useful cache lines among the next four will be prefetched. Dis records the 4-bit offset of the branch instruction from the last two demanded instructions upon iCache misses. On iCache accesses, Dis looks up DisTable and generates prefetches if the missing line is found. Otherwise, the BTB will be consulted. Finally, BTB prefetching is employed to reduce BTB misses. BTB

prefetching can be activated when an iCache fill is processed. The predecoder identifies the PC-relative branches and installs those detected branches unconditionally into the BTB array. Because of the nature of the prefetching scheme, the register-relative indirect branches cannot be prefetched by this mechanism. SN4L prefetcher only requires 2.06KB of storage [90]. MANA [5] is a refinement of SN4L-Dis-BTB that uses an 8-bit vector for consecutive prefetchers (previously proposed by PIF [26]]). It offers a good performance-area trade-off, and it is representative of state-of-the-art BTB directed instruction prefetchers. Here is the summary of performance and storage for all kinds of state-of-art iCache prefetch [90]. We can see that FDP based SN4L+Dis+BTB and MANA have a large benefit of good performance-area trade-off without large meta-data.

Figure 2.14: IPC vs mempry requirements [90].

In the end, from the view of industry perspective, Yasuo et al. [45] propose an effective FDP-base frontend design with only 195 bytes of hardware overhead. The authors point out that academic research always uses a less-than-optimal frontend baseline with a small BTB. At the same time, the industrial or commercial solutions always keep accurate branch predictors and large BTB with FDP. To overcome its previous issues, it has two enhancements, taken-only branch target history and post-fetch correction. It outperforms the 1st Instruction Prefetching Championship (IPC-1) winners with a 128KB storage budget.

Nevertheless, for a ULP multi-core cluster with limited instruction cache ca-

pacity, these prefetchers all have the same issue of significant metadata overhead because of extensive address tracking and analysis, which brings much extra area and power. Thus, it is necessary to balance the performance with the cache power. Besides, keeping a large or small BTB for each fetch access for each core in the ULP cluster also brings large dynamic power. In this work, we employ a simple sequential next-line prefetch (4 instructions) to hide the L1 to L1.5 latency without jeopardizing energy efficiency. We expose this feature to allow software-controlled enable/disable of the prefetcher to adapt to application characteristics and trade-off performance and energy efficiency.

## 2.4 State-of-the-arts ICache in ULP cluster

#### 2.4.1 Private Instruction Cache

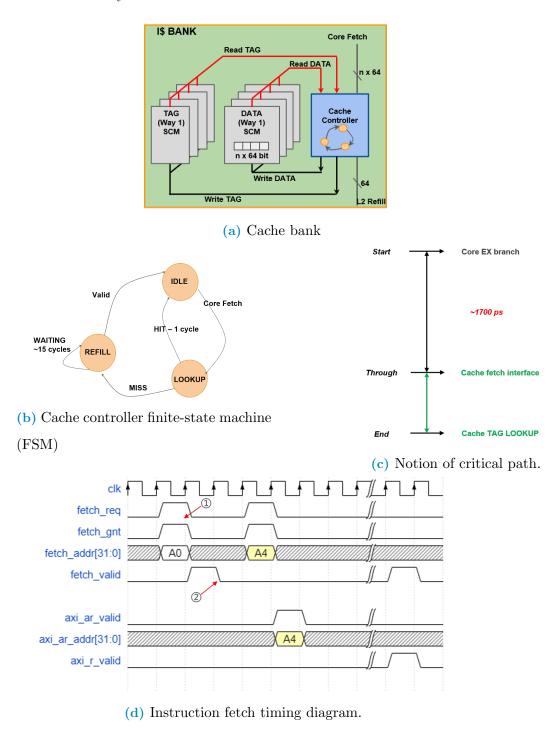

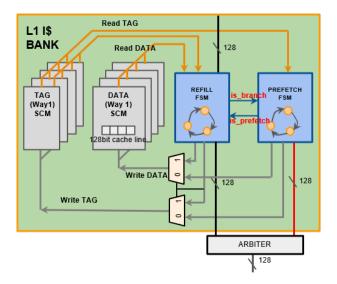

The baseline cluster features private instruction caches (Fig. 1.5). Each private cache bank comprises 3 elements, a TAG, a DATA array implemented using SCMs and a cache controller using a request-grant handshake protocol with a pseudorandom (PRAND) replacement policy. To refill from L2, each cache bank sends the request to the AXI bus independently with AXI interconnect nodes. Fig. 2.15a shows the details of the private cache bank. We can see that the core controller receives the fetch request from the RI5CY core with a cache line size of  $n \times 64$  bits. Here we choose a 128-bit cache line to reduce the core fetch frequency since it is enough for a 32-bit RI5CY core. At the same time, the cache controller will read TAG and DATA to check if the fetch address is inside. If a cache hits, then the data is read back to the core with one cycle. If the cache miss, the controller goes to refill state and waits for AXI bus refill for about 15 cycles. Once controller get the data, it sends to the core (Fig. 2.15b, 2.15d). As a result, when executing parallel applications, each core fetches the same instructions while there is a miss, then all the cores will suffer from a miss and ask for AXI refill with the same instruction for about 15 cycles. This is a waste of AXI bandwidth with redundant refills.

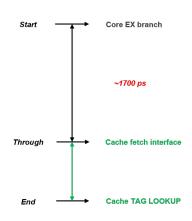

The private cache has one cycle latency when hit and its critical path in the cache controller is from core's  $fetch_req$  to cache bank's tag memory LOOKUP

shown in arrow 1 in Fig. 2.15d). As we mentioned in section 1.1.3.1, it starts from the core's EX stage to determine branches. This path delay is about 1700 ps with the synthesis in GF22FDX technology, which limits the maximum frequency of the core fetch subsystem.

Figure 2.15: Private cache bank subsystem

In conclusion, the private caches are fast (i.e., small critical path) and simple (i.e.,

low-power). Data replication and high miss penalty for large footprint applications are major drawbacks for private instruction cache, which decrease their performance and energy efficiency.

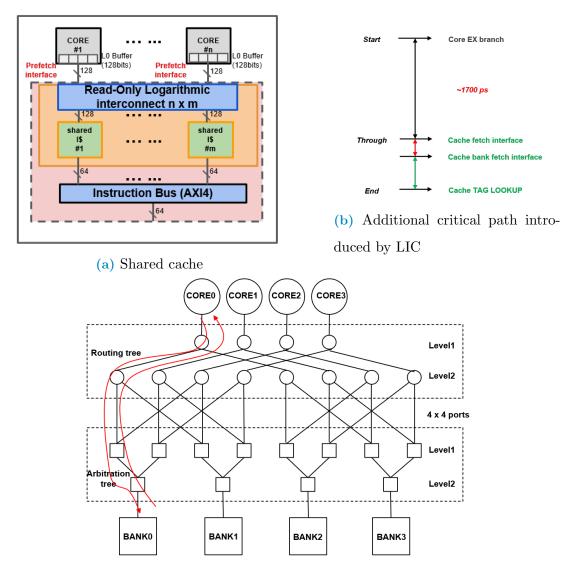

#### 2.4.2 Shared Instruction Cache

Shared instruction cache is shown in Fig. 2.16a. It uses the same cache banks as the private cache Fig. 2.15a, and it sends instruction refill to L2 memory only once when the cores access the same shared banks (AXI bus refill only once). Data replication is avoided since cache banks are shared among the cores, but two or more cores may compete to access the same cache bank. In such a condition, a round-robin arbitration policy ensures that only one core can access the cache bank and keeps the others stalled. As a result, each core has the same probability of accessing the cache bank. To better spread access among multiple banks, a read-only interconnect with n input and m output is employed to ensure fair access to the cache banks.

#### 2.4.2.1 Logarithmic interconnect

The logarithmic interconnect is a parametric, fully combinational Mesh-of-Trees (MoT) interconnection network to support high-performance, single-cycle communication between processors and memories in L1-coupled processor clusters [87]. As shown in Fig. 2.16c, a combinational path is created based on a network of routing primitives (circles blocks) and arbitration primitives (square blocks). The former is used to create independent routing paths (routing trees) from the cores to the arbitration tree and vice-versa. The latter is used to arbitrate concurrent requests (arbitration tree) and route them to the memory banks and vice-versa. The interconnect ensures access to large shared memory for cluster cores. However, it creates more logic delay in the critical path from core's  $fetch\_req$  to memory's tag lookup (shown in red arrow Fig. 2.16c). Therefore, the delay needs to be evaluated in detail. Post-placement & routing results show that the delay of n processors and m memory banks with 32-bit data size  $(n \times m)$ , the delay is expressed by a certain Fan-out of 4 (FO4), which is a measure of time independent of CMOS technologies, the gate delay of a component with a fan-out of 4 [39]. Our target shared instruction cache,

with an  $8 \times 8$  configuration, has 32FO4 (19FO4 from cores to memory and 13Fo4 from memory back to cores), which means that the combinational logic delay for the critical path from core's  $fetch\_req$  to memory's tag lookup will increase 19FO4. This increased delay will push the pressure of the core's fetch timing and reduce the maximum frequency, as shown in Fig. 2.16b. Finally, the maximum performance will decrease with the shared instruction cache.

(c) Mesh of trees 4x4: empty circles represent routing switches and empty squares represent arbitration switches.

Figure 2.16: Single-ported Share Cache subsystem

When one of the core's fetch requests goes to the cache controller of each shared memory bank, if a miss happens, the cache controller asserts the respective refill request and continues accepting incoming fetches from other cores while waiting for the refill response from L2. The shared cache controller can also track more than one pending refill by additional FIFO to track pending misses and restore the correct order from the response coming from the AXI BUS. If incoming fetches ask the same missed address after the L2 refill, they will be served by the TAG and DATA memories instead of refilling in L2. The merge of the same miss refill largely reduces the redundant L2 refill frequency, which is the purpose of shared caches. The shared cache can reduce n times the L2 refill frequency where n is the number of cores, especially in parallel applications.

Consequently, the shared instruction cache benefits from large cache capacity to avoid data replication while minimizing the access cycle (single-cycle-latency) and area overhead. The single-ported shared instruction cache features a read-only low-latency crossbar that uses a round-robin arbitration policy for each core's fetch request. Since one cache bank can serve one refill request each time, it causes congestion when several cores access the same cache bank for parallel applications. Moreover, a long path is present between the instruction fetch stage of the core to the cache banks through the interconnect, which limits the maximum frequency.

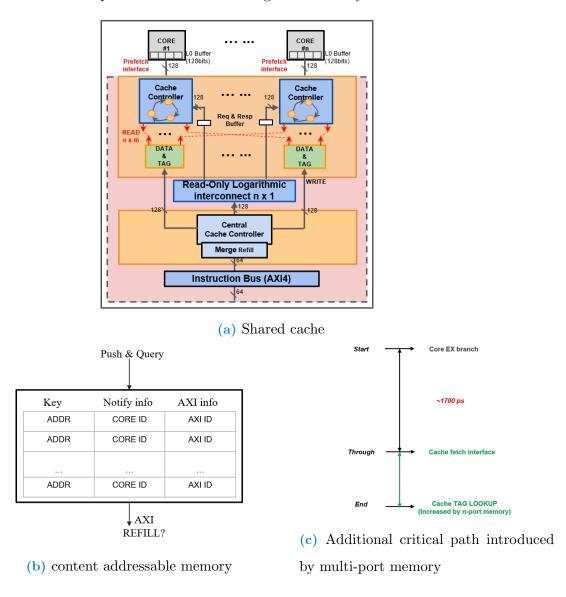

## 2.4.3 Multi-ported Instruction Cache

A new shared instruction cache is proposed to share only TAG and DATA memories while keeping a private cache controller for each core to solve the congestion issue of a single-ported shared cache. This can be realized by using multi-ported SCMs. Fig. 2.17a shows the detailed view of this cache. We can separate the multi-ported shared cache into two parts or two levels. Level 1 is composed of a private cache controller and multi-ported banks. Level 2 has a central cache controller cooperating with a merge refill unit. These two levels are still connected with the same logarithmic interconnect with  $n \times 1$  (n private controllers and one central controller). Finally, a request and response buffer is employed to cut the critical path between levels to reduce the timing pressure of level 1 to level 2.

In the first level, now there can be m memory banks, and each of them is composed of TAG and DATA and a private cache controller. Besides, it has a single write port (written by the central cache controller after a miss) and n read ports, one for each private cache controller (n cores) and used for normal cache access (hit or miss). Each cache controller has a direct and private path (no contention) to read TAG and DATA memories with multi-ported memory banks. Therefore, this cache is similar to the private cache while using different ways to deal with cache misses.

Figure 2.17: Multi-ported Share Cache subsystem

In the second level, different from the private cache, instead of directly sending n refill request to AXI BUS when each cache controller has a miss with the same address, the multi-port cache handles the refills by a dedicated central cache controller, which is in charge of merging the refills with the same address, sending refill to L2 as well as updating the TAG and DATA memories. The refill merge is realized

by a CAM (content addressable memory) like a small cache, all refills to L2 with the same address can be merged into 1 refill by referring CAM. As shown in Fig. 2.17b, the refill address is written into CAM and generates a unique AXI ID (entry ID), and the address will be used as a key. If the same address hits in the CAM, no refill request is generated, and only the CORE ID field is updated, meaning that the cores linked to the hit refill address in the CORE ID field will be notified after the L2 response. If there is a refill address miss, the first empty CAM entry is allocated, and a corresponding refill request is sent to L2.

The multi-ported shared cache may have the best performance with free access to memory banks without contention and minimum L2 refill traffic. However, with the request and response buffer between levels, its miss penalty is two more cycles than the single-ported share cache. This can result in performance decline compared with single-port shared cache in extreme cases: all instructions are missed. Besides, the multi-port memory banks introduce a large area and create wire congestion in place & route of back-end. This also augments the memory read latency, as shown in Fig. 2.17c.

In conclusion, multi-ported shared cache benefits from large cache capacity and avoiding. Nevertheless, even if the heavy congestion for cores' access is avoided, n-ported TAG and DATA memories still have a series of area overhead issues. As a result, it is suitable only for cache sizes up to a few KB.

#### 2.5 Thesis Outline

In this section, we describe the organization of the remainder of the present thesis work.

In chapter 3, we compare different architectures for iCache targeting tightly coupled clusters in detail. The analysis involves private iCaches per core, a shared iCache with single-port memories, as well as a shared iCache with multi-port memories. With synthetic micro-benchmarks and real program workloads, we can figure out an effective iCache architecture configuration to support high performance in a multi-core cluster by varying cache capacity, cache associate, and cache line block size. We summarise the three architectures' characteristics and drawbacks to provide

clear evidence for the next exploration.

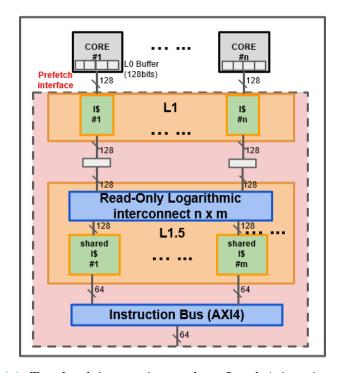

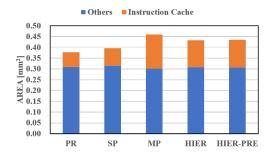

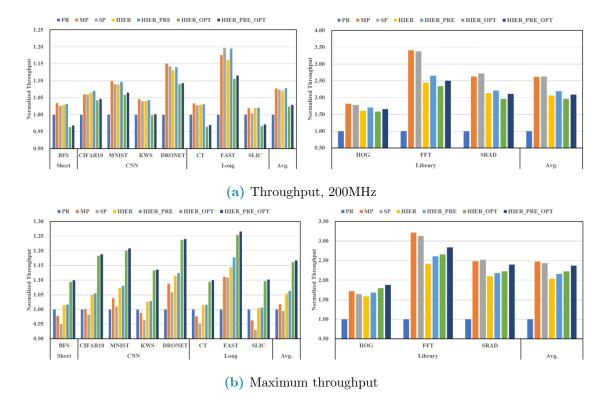

In chapter 4, we propose a two-level iCache to balance a multi-core cluster's performance and energy efficiency, which combines the private iCache for each core as L1 with 1 cycle latency and single-port shared iCache as L1.5 with 2 cycle access latency. It benefits from simple L1 and large cache capacity of shared cache while with a relatively large area. On average, when executing a set of real-life IoT applications, our multi-level cache improves performance and energy efficiency by 10% concerning the private iCache system and improves the energy efficiency by 15% and 7% with a performance loss of only 2% concerning the shared iCache. Besides, the relaxed timing makes two-level iCache an attractive choice for aggressive implementation, with more slack for convergence in physical design.

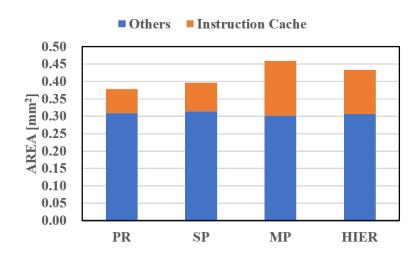

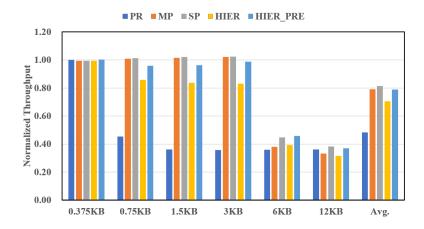

In chapter 5, we exploit adopting sequential prefetch between caches to load as soon as possible the instruction will be used in the future since two-level iCache with limited small L1 cache capacity has the performance drawback compared with shared cache, up to 25% performance drop in some large library based applications. With low power consumption requirements, efficient prefetch should be considered to reduce L1 capacity miss without introducing much power. Thus a dual-port read TAG memory is used for refill and prefetch lookup access in the L1. The result shows that it constantly improves the performance by 7% compared with the no prefetch one. Compared with private cache, it improves the performance by 15% with an energy efficiency loss up to 7%. Compared with shared cache, it almost keeps the same performance and improves energy efficiency by 7%.

In chapter 6, we focus on the timing optimization of the core instruction fetch stage in section 1.1.3.2. It is necessary to analyze and optimize the critical paths in the request and response channels. By removing the critical paths through the implementation of  $4 \times 32$ -bit ring buffer FIFO and one cycle delay of the conditional branch, we achieved a much higher maximum frequency to improve its scalability against shared caches. Finally, we have 20% maximum frequency improvement and up to 17% performance improvement compared to private and shared caches on average.

Finally, we summarize in chapter 7 the main research contributions of the present thesis work and future research direction.

## Chapter 3

## Evaluation of state-of-the-art Instruction Caches in PULP

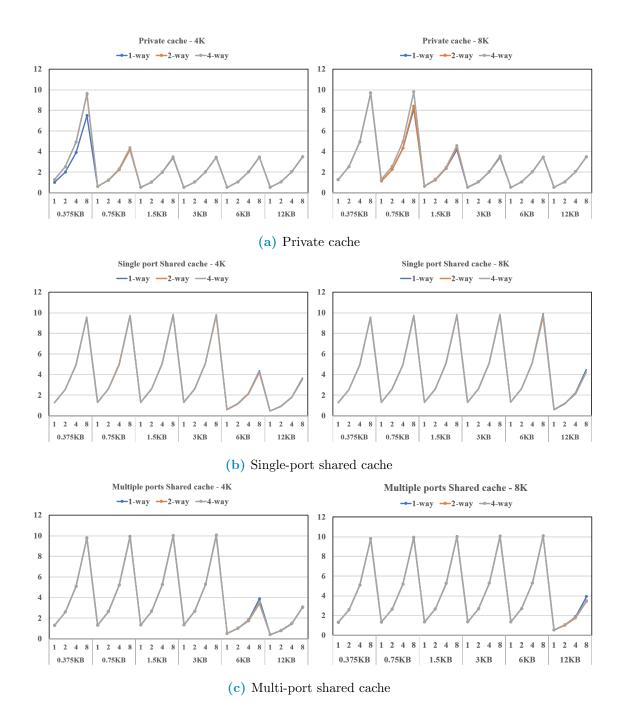

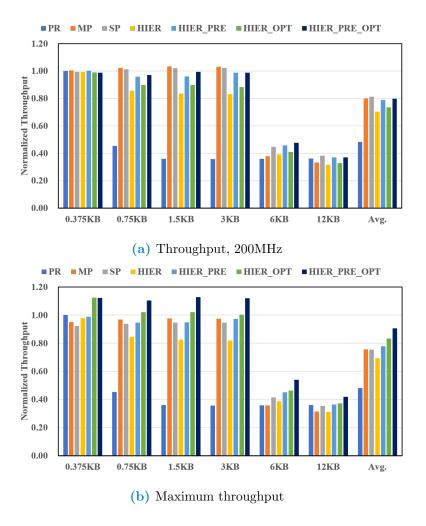

In this chapter, we adapt the three state-of-the-art instruction caches to our target PULP cluster. To give a comprehensive summary of the characteristic of each cache, we run the RTL simulation of the target cluster with the three caches. By varying the configurable parameters in terms of cache size and cache set-associate, we give the best configuration for each iCache for further exploration.

To efficiently analyze and assess the pros and cons of all architecture, we developed a programming environment for efficient data-parallel acceleration based on the OpenMP programming model. This software environment allows us to accurately control the instruction size to create synthetic tests to stress a specific corner case and assess the best and worst operating conditions for the three iCaches. After finding the best corner for each cache, we further validate the caches with real-life applications, including signal processing and CNN kernel-based parallel program with OpenMP.

## 3.1 Software and Program paradigm

To fairly measure the performance and energy efficiency, we fix the PULP cluster with 8 cores and change only the instruction cache (shown in Table 3.1). By varying the cache set-associate and cache size, we can find the best operating configuration for our target ULP cluster. In Table 3.1, the private instruction cache features N

| Mnemonic        | Type    | Hit    | L2      | Description                   | Set-associate |

|-----------------|---------|--------|---------|-------------------------------|---------------|

|                 |         | Cycles | Penalty |                               |               |

| PR              | Private | 1      | 15      | N Bytes I\$ bank x 8 cores    | W-way         |

| SP              | Shared  | ≥1     | 17      | 8 x N Bytes I\$ banks, 1-port | W-way         |

| $\overline{MP}$ | Shared  | 1      | 19      | 2 x M Bytes I\$ banks, 8-port | W-way         |

Table 3.1: Instruction cache architecture configurations

Bytes cache bank for 8 cores, where N can be 512 or 1024, and the same N is used for the single-port shared cache. Therefore, there are two combinations of the total memory of 4KB and 8KB. While for multi-ports shared cache, we choose 2 banks with M Bytes (M can be 2048 or 4096 to have a total of 4KB or 8KB memory) because it has no memory access congestion. Besides, all caches' set-associate W varies among 1-way, 2-way, 4-way. In conclusion, we have six combinations for each cache to make a detailed comparison and find the best combination for the target ULP cluster. Finally, since the PULP has no data cache to avoid redundant data copies with explicit data copy, we use the following multi-core program methodology to activate its computing capacity fully.

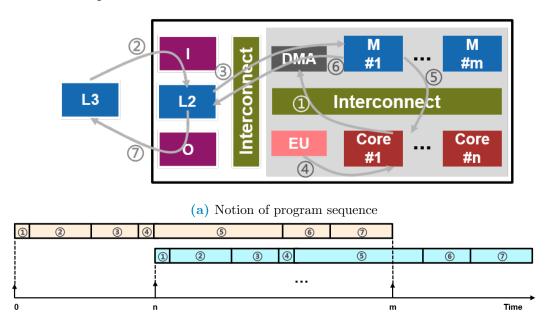

## 3.1.1 Program methodology

Fig. 3.1 shows the basic program sequence with explicit data transfer in PULP. First, the cluster's cores execute the instruction load from L2, and the master core (can be any one of the cores) initiates a DMA transfer to load task data from L2 to cluster's TCDM and go to sleep. Second, if the data size is large and does not fit the L2 size, an external L3 memory device is used to load data to L2 with the help of SoC I/O. Next, the DMA is responsible for transferring the data from L2 to TCDM. Once it's finished, it sends a finished event to the event unit, and the event unit wakes up the cores in step 4. Then, the cores start processing the data in parallel with the help of OpenMP in step 5. In the end, once all the cores finish data processing, the master core asks the DMA to copy the data back to the L2, and I/O copies it back to the L3 in steps 6 and 7 (Fig. 3.1a). The data transfer is in the

pipeline (Fig. 3.1b) with the help of several DMAs while the cores are processing the data to hide the latency of huge memory transfers (shown in step 2, 3) and to maximize the performance.

(b) Data transfer pipeline to hide huge data transfer latency, at least save (m-n) time for the second data processing

Figure 3.1: Program sequence with PULP cluster for parallel acceleration

Thanks to the ultra-low-latency lightweight DMA, it supports multiple outstanding transactions required to hide the huge latency of external memory accesses without a large internal memory for the temporary storage of incoming or outgoing data [91]. Based on the pipelined DMA transfer program mythology, an automatic tool to deploy DNNs on low-cost PULP MCUs with typically less than 1MB of on-chip SRAM memory - DORY is proposed [burrello2020dory]. DORY abstracts tiling as a Constraint Programming (CP) problem: it maximizes L1 memory utilization under the topological constraints imposed by each Deep Neural Network (DNN) layer. Then, it generates ANSI C code to orchestrate off- and on-chip transfers and computation phases. The generated C code helps users to complete the work described in Fig.3.1. Finally, we combine the generated C code with our programs to improve programming efficiency and hide the complex explicit data transfers for DNN applications.

## 3.1.2 Synthetic tests

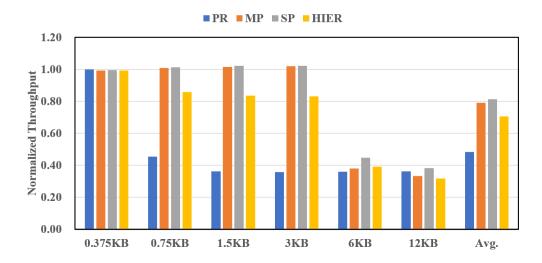

The synthetic tests are simply doing parallel vector multiply for 8092 data. We use Loop unrolling algorithm 1 to control the instruction size of the synthetic tests accurately. The  $BUFFER\_SIZE$  is always fixed to 8192 while STEP changes among 32, 64, 128, 256, 512 and 1024 which represent instruction size for 0.375KB, 0.75KB, 1.5KB, 3KB, 6KB and 12KB respectively. Finally, we run the RTL simulation of the 6 tests, and all the tests have the same number of operations for cluster cores.

```

Algorithm 1 Loop Unrolling

Require: BUFFER\_SIZE = 8192

Require: TOTAL\_CORE = N

Require: STEP = M

start \leftarrow core\_id \times BUFFER\_SIZE \ / \ TOTAL\_CORE

end \leftarrow start + BUFFER\_SIZE \ / \ TOTAL\_CORE

for i = start; i < end; i + = STEP do

c[i] \leftarrow a[i] \times b[i]

c[i] \leftarrow a[i+1] \times b[i+1]

...

c[i+STEP-1] \leftarrow a[i+STEP-1] \times b[i+STEP-1]

end for

```

#### 3.1.3 Benchmarks

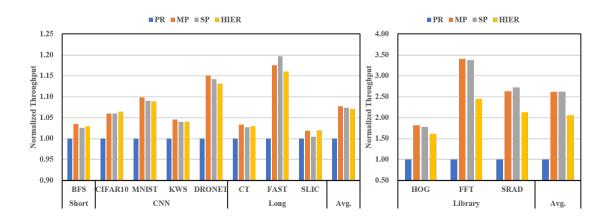

Furthermore, we used a series of benchmarks based on full-fledged optimized OpenMP implementation [69] applications and four CNN applications which make use of the Auto-Tiler library, a CNN library that manages large data transfer between SoC domain and Cluster domain automatically for the embedded system [37] to analyze in-depth the behaviour of each architecture. Each application features a different behaviour in terms of access patterns to the instruction memory subsystem and diversified memory footprints and execution time.

The detailed characteristics of each application are shown in table 3.2, including each code section size in KB and each number of 32-bit instructions in execution. Since cache performance is influenced strongly by code locality and code size, we

| APP                 | Size [KB] | Class                                   | Description                                  |  |

|---------------------|-----------|-----------------------------------------|----------------------------------------------|--|

| BFS                 | 59.2      | Short-Jump                              | Breadth-First Search                         |  |

| $\operatorname{CT}$ | 28.2      | Long-Jump                               | Color Tracking                               |  |

| FAST                | 28.6      | Long-Jump                               | Machine-generated corner detection algorithm |  |

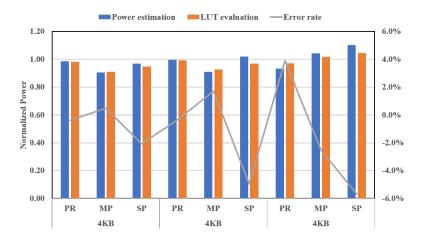

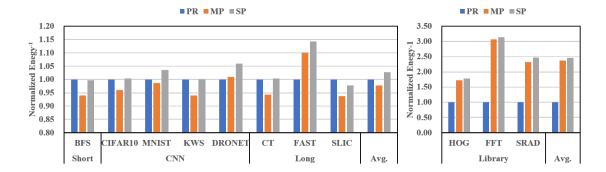

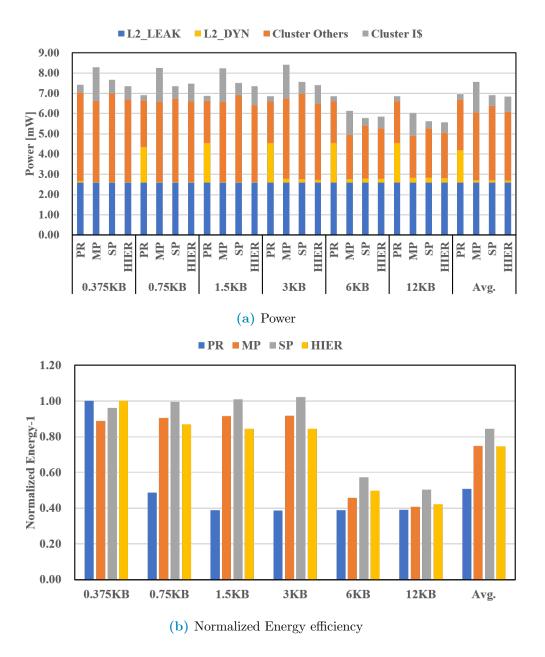

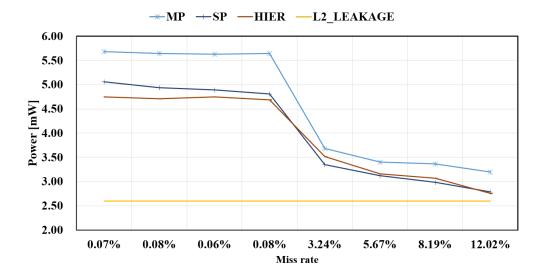

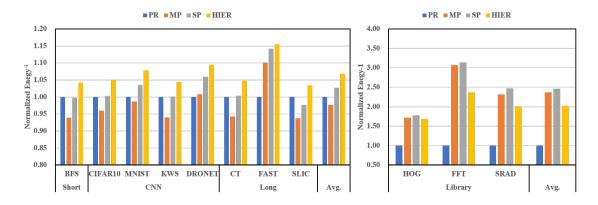

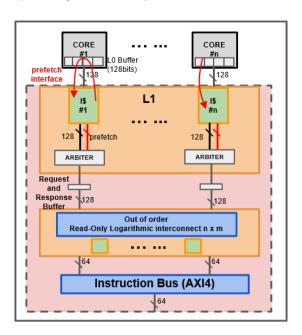

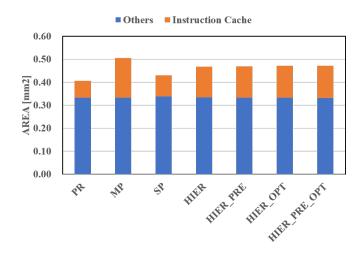

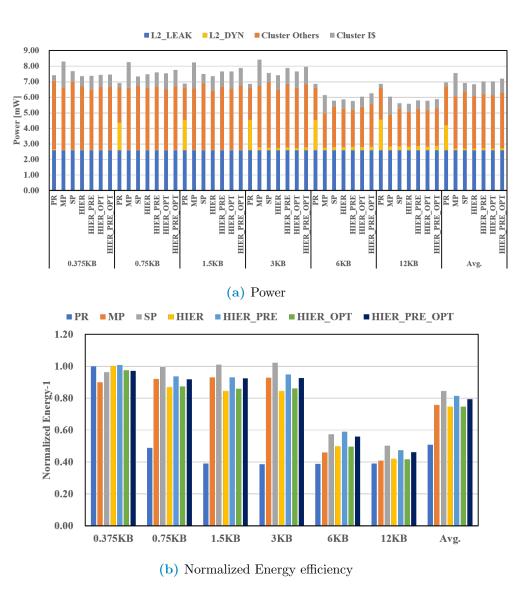

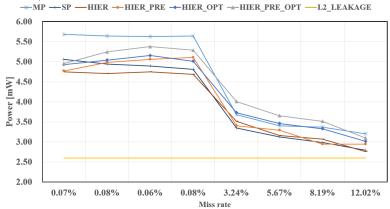

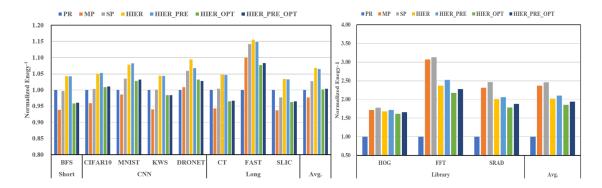

| SLIC                | 26.1      | Long-Jump                               | Simple Linear Iterative Clustering           |  |