### WIRELESS IMPLANTABLE ICs FOR ENERGY-EFFICIENT LONG-TERM AMBULATORY EEG MONITORING

### AL FREEMAN

#### A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

### GRADUATE PROGRAMME IN ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

### YORK UNIVERSITY

### TORONTO, ONTARIO

JUNE 2020

© AL FREEMAN, 2020

## ABSTRACT

This thesis presents the design, development, and experimental characterization of wireless subcutaneous implantable integrated circuits and systems for long-term ambulatory EEG monitoring. Application-, system- and circuit-level requirements for such a device are discussed and a critical review of the state-of-the-art academic and currently available commercial solutions are provided. Two prototypes are presented:

The first prototype presented in Chapter 2 is an 8-channel wireless implantable device with a  $2.5 \times 1.5 \text{ mm}^2$  custom-designed integrated circuit implemented using CMOS 180nm technology at its core. The microchip is fabricated and the measurement results showing its efficacy in EEG signal recording in terms of input-referred noise, voltage gain, signal-to-noise ratio, and power consumption are presented. The chip is implemented together with a BLE 5.0 module on the same platform. Our vision and discussions on biocompatible encapsulation of this system, as well as its integration with a microelectrode array as also provided.

The second prototype, also implemented in CMOS 180nm technology and presented in Chapter 3, employs a novel EEG recording channel architecture that enables long-term implantation of EEG monitoring devices through significant improvement of their energy efficiency. The channel leverages the inherent sparsity of the EEG signals and conducts recording in an activity-dependent adaptive manner. Thanks to the proposed fully dynamic spectral-compressing architecture, the recording channels power consumption is drastically reduced. More importantly, the proposed architecture reduces the required wireless transmission throughput by more than an order of magnitude. Our test results on 10 different patients' pre-recorded human EEG data shows an average of  $12.6 \times$  improvement in the device's energy efficiency.

## DEDICATION

Dedicated to the loving memory of my father Dr. Ali Erfani who inspired me to be a better

person. You will always be missed.

## ACKNOWLEDGEMENT

I wish to express my deepest gratitude to my supervisor Professor Hossein Kassiri for his patience, recommendations and guidance. His intellectual and financial support has been tremendous help during this project and I feel very privileged having worked with him during the course of this program.

I would also like to thank my supervisor committee and defense committee members, Professor Ebrahim Ghafar-Zadeh & Professor Eleftherios Sachlos for reviewing this thesis and providing me with their valuable feedback.

I would like to thank the technical and administrative staff and faculty members of Lassonde School of engineering for their assistance and support.

I wish to acknowledge and thank my colleagues and friends Tayebeh Yousefi, Alireza Dabbaghian, Mansour Taghadosi, Tania Moeinfard and Fatemeh Eshaghi for their continuous help.

My most profound gratitude goes to my beautiful wife Miriam Freeman and my loving son Brayden Freeman who patiently supported me throughout the years. You have been the inspiration for my every effort.

# TABLE OF CONTENTS

| ABSTRACTii                                                                    |

|-------------------------------------------------------------------------------|

| DEDICATIONiii                                                                 |

| ACKNOWLEDGEMENT iv                                                            |

| TABLE OF CONTENTSv                                                            |

| LIST OF TABLES viii                                                           |

| LIST OF FIGURES ix                                                            |

| CHAPTER 1: Introduction and Motivation1                                       |

| 1.1 Motivation and Objective1                                                 |

| 1.2 Design consideration                                                      |

| 1.2.1 Application-level                                                       |

| 1.2.2 System-level                                                            |

| 1.2.3 Circuit-level                                                           |

| 1.3 State-of-the-art7                                                         |

| 1.4 Thesis organization9                                                      |

| CHAPTER 2: A Wireless Subcutaneous Implantable Microsystem for Ambulatory EEG |

| Monitoring 11                                                                 |

| 2.1 System level design and consideration                                     |

| v   P a g e                                                                   |

| 2.1.1 Wireless Data Transmitter                                             |

|-----------------------------------------------------------------------------|

| 2.1.2 Power Management                                                      |

| 2.2 Analog front-end and signal preconditioning                             |

| 2.3 Data conversion using SAR ADC                                           |

| 2.4 Integration and fabrication                                             |

| 2.5 Experimental Measurement Results                                        |

| CHAPTER 3: An Activity-Adaptive Loss-Less-Compressive EEG Recording Channel |

| Architecture                                                                |

| 3.1 Introduction and motivation                                             |

| 3.2 LFP signals Sparsity                                                    |

| 3.3 EEG Recording with Activity-Adaptive Quantization Resolution            |

| 3.4 System-Level Design                                                     |

| 3.5 Design and Implementation of the Recording Front-End                    |

| 3.5.1 System-level Idea 46                                                  |

| 3.5.2 Circuit Implementation                                                |

| 3.6 Activity Monitoring Design and Implementation                           |

| 3.7 Integration and Performance summary                                     |

| CHAPTER 4: CONCLUSIONS AND FUTURE DIRECTIONS                                |

| 4.1 Conclusion                                                              |

| 4.2 Future work                                                             |

| 4.2.1      | Integral transceiver                                               | 69 |

|------------|--------------------------------------------------------------------|----|

| 4.2.2      | Improvements to reference voltage generation                       | 69 |

| 4.2.3      | More optimized digital logic                                       | 69 |

| 4.2.4      | Further in vitro and in vivo experiments                           | 70 |

| 4.2.5      | Encapsulation                                                      | 70 |

| Bibliograp | hy                                                                 | 71 |

| Appendix.  |                                                                    | 78 |

| 5.1 M      | ATLAB code for activity dependent sampling rate adjustment design: | 78 |

## LIST OF TABLES

| Table 1 1: Various brain neural activity monitoring methods compared in terms of their |

|----------------------------------------------------------------------------------------|

| spatio-temporal resolution and spatial coverage2                                       |

| Table 1 2: Recently-reported wireless monitoring headsets for medical-grade EEG        |

| recording                                                                              |

| Table 2 1 : Early design specifications    14                                       | 4 |

|-------------------------------------------------------------------------------------|---|

| Table 2 2 : List of competitive contenders for wireless data telemetry    1         | 6 |

| Table 2 3 : Comparison of the popular off-the-shelf wireless modules                | 7 |

| Table 2 4 : List of components used    1                                            | 8 |

| Table 2 5 : Comparison of various batteries for capacity, discharge rate and size 1 | 9 |

| Table 2 6 : Summary of transistor sizing for AFE    2                               | 2 |

| Table 2 7 : Summary of transistor sizing for ADC's comparator                       | 9 |

| Table 2 8 : Overall specification summary    3                                      | 5 |

| Table 3 1:       | System-level | performance | comparison | between | the | designs | presented | in |

|------------------|--------------|-------------|------------|---------|-----|---------|-----------|----|

| Chapters 2 and 3 |              |             |            |         |     |         |           | 66 |

# LIST OF FIGURES

|        | Figure 1 1 : A typical EEG recording session in a medical facility 2                         |

|--------|----------------------------------------------------------------------------------------------|

|        | Figure 1 2 : Top-level block diagram and envisage implantation of the proposed subdermal     |

| implan | t 4                                                                                          |

|        | Figure 1 3 : Commercial examples of wearable EEG recording devices                           |

|        |                                                                                              |

|        | Figure 2 1 : Placement of the proposed EEG recording system                                  |

|        | Figure 2 2 : Top-level block diagram of the presented device                                 |

|        | Figure 2 3 : Illustration of the envisioned final prototype                                  |

|        | Figure 2 4 : Block diagram of the prototype board 16                                         |

|        | Figure 2 5 : The PCB prototype board 18                                                      |

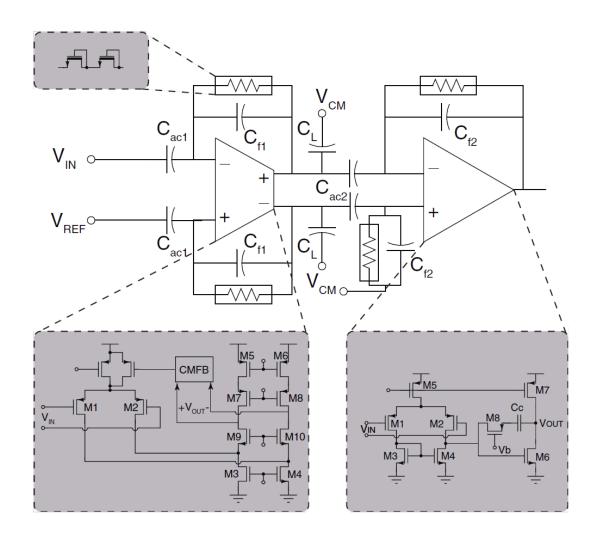

|        | Figure 26: Circuit view of the analog front-end including fully differential folded cascaded |

| OTA    |                                                                                              |

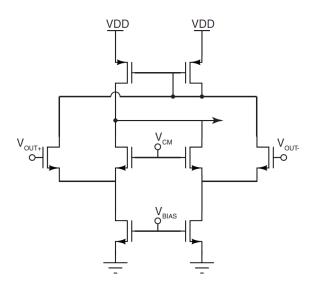

|        | Figure 2 7 : Circuit view of the common mode feedback                                        |

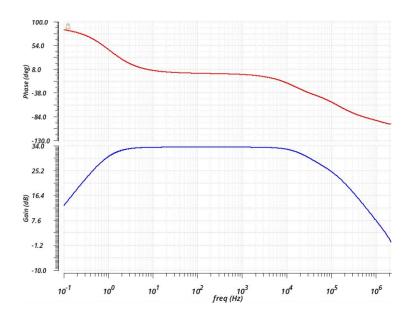

|        | Figure 2 8 : Gain and phase plot for first stage folded cascaded OTA 24                      |

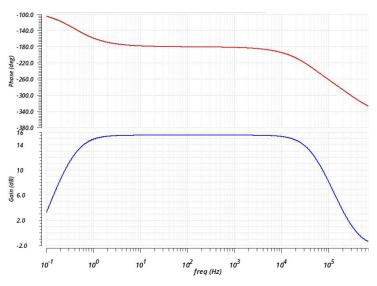

|        | Figure 2 9 : Gain and phase plot for second stage OpAmp 24                                   |

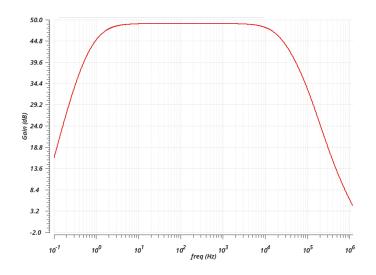

|        | Figure 2 10 : Gain bandwidth plot for overall gain stages 25                                 |

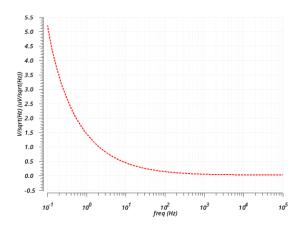

|        | Figure 2 11 : Input referred noise for the analog front end 25                               |

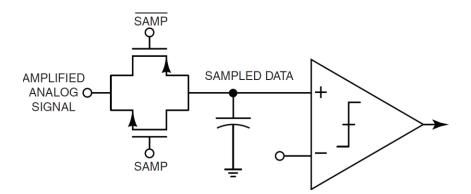

|        | Figure 2 12 : Sample and hold circuit                                                        |

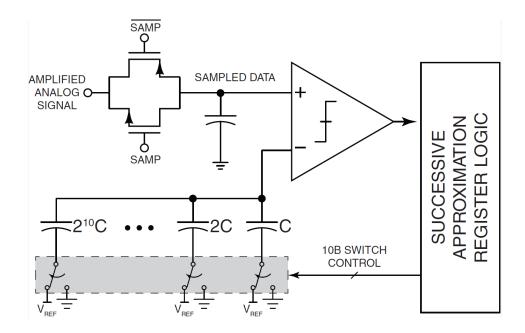

|        | Figure 2 13 : Capacitive DAC with binary weighted capacitors                                 |

|        | Figure 2 14 : Strong Arm Comparator                                                          |

|        | Figure 2 15 : Transient analysis of the SAR ADC 30                                           |

| Figure 2 16 - 8:1 Mux used for data serialization                             | 31 |

|-------------------------------------------------------------------------------|----|

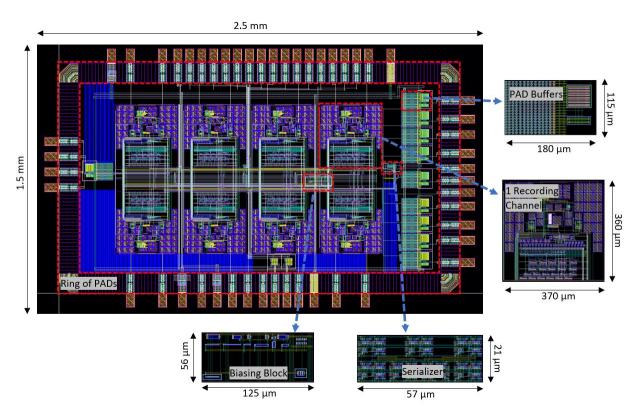

| Figure 2 17 : Layout of the EEG recording channel (0.36 x 0.38 mm)            | 31 |

| Figure 2 18 : Full chip layout of 8 channel EEG recorder                      | 32 |

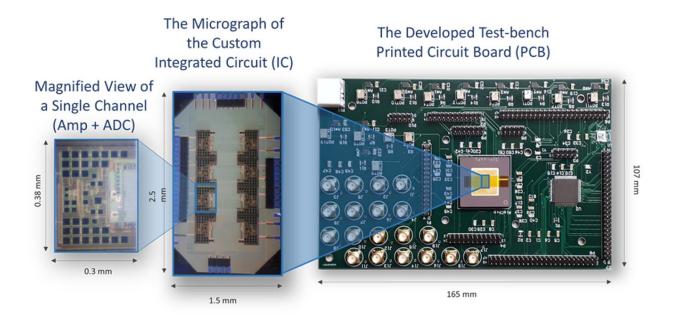

| Figure 2 19 : Magnified view of the fabricated chip along with test-bench PCB | 33 |

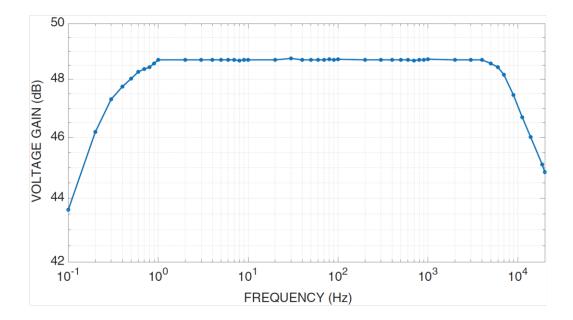

| Figure 2 20 : Measured gain – bandwidth graph post fabrication                | 34 |

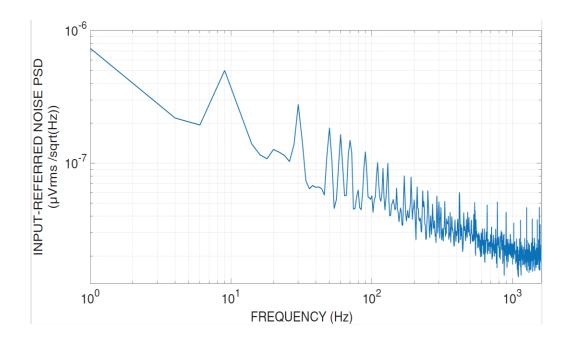

| Figure 2 21 : Measured input referred noise                                   | 35 |

| Figure 3 1 : Diagram showing phases of an action potential over time [25]                     | . 38 |

|-----------------------------------------------------------------------------------------------|------|

| Figure 3 2 : LFP EEG recording from CHB-MIT scalp EEG database [27]                           | . 39 |

| Figure 3 3 : Block level diagram                                                              | . 43 |

| Figure 3 4 : LFP EEG recording with an event (A) and idle period (B) marked                   | . 44 |

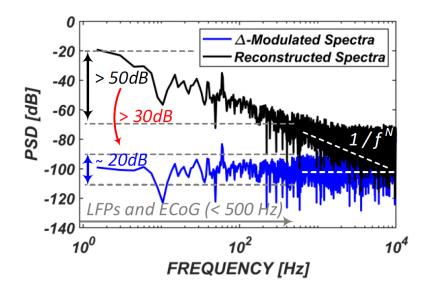

| Figure 3 5: Spectra comparison of $\Delta$ -modulated and $\Sigma$ -demodulated neural signal | . 46 |

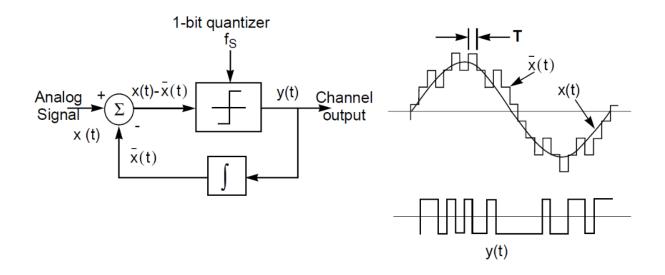

| Figure 3 6 : Delta modulation principle [39].                                                 | . 47 |

| Figure 3 7 : Block diagram of the proposed differential-difference $\Delta$ -modulated ADC    | . 48 |

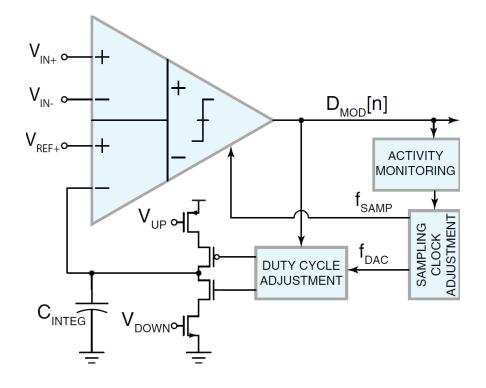

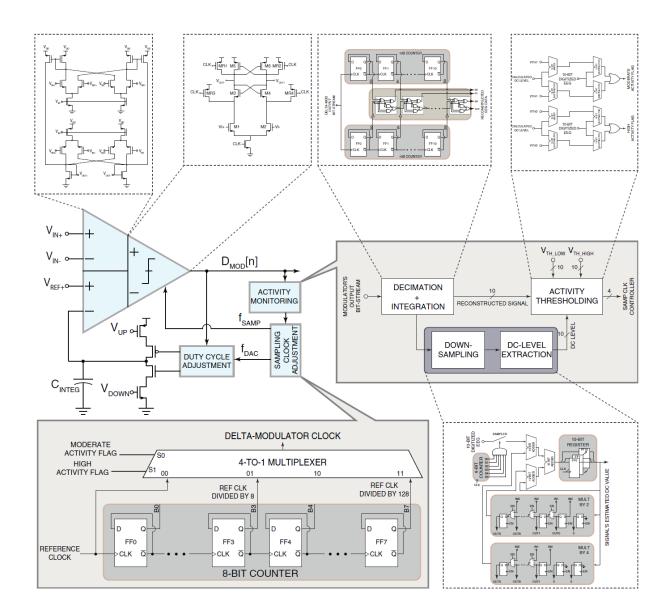

| Figure 3 8 : Feedback architecture of the proposed design                                     | . 49 |

| Figure 3 9 : Circuit diagram of differential difference amplifier                             | . 51 |

| Figure 3 10 : Frequency response of the differential difference amplifier                     | . 53 |

| Figure 3 11 : Input referred noise of differential difference amplifier                       | . 53 |

| Figure 3 12: Digital back-end block diagram                                                   | . 54 |

| Figure 3 13 : Plot of sampling rate adjustment algorithm                                      | . 56 |

| Figure 3 14 : Circuit diagram of amplitude reconstruction block                               | . 57 |

| Figure 3 15 : Transient analysis for amplitude reconstruction block                           | . 58 |

| Figure 3 16 : Simplified circuit diagram of DC extraction block                               | . 59 |

| Figure 3 17 : Transient analysis of DC extraction block                             | 60 |

|-------------------------------------------------------------------------------------|----|

| Figure 3 18: Threshold level detection circuit                                      | 61 |

| Figure 3 19: Circuit diagram of sample clock generator                              | 61 |

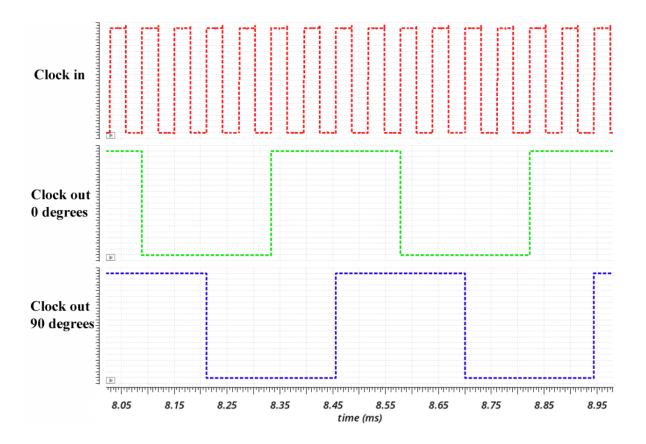

| Figure 3 20 : Transient analysis for clock generator                                | 62 |

| Figure 3 21: Integrated blocks diagram                                              | 63 |

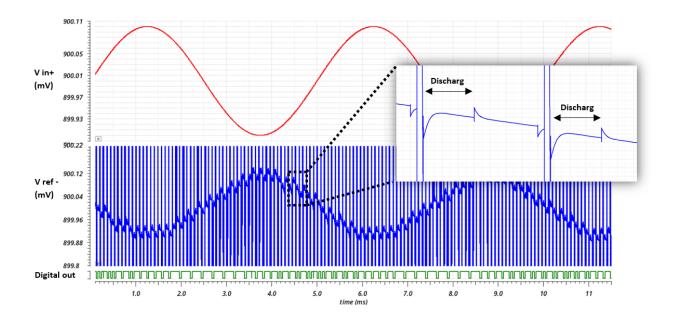

| Figure 3 22 : Synthetization of V ref (–) in response to input sin wave at V in (+) | 64 |

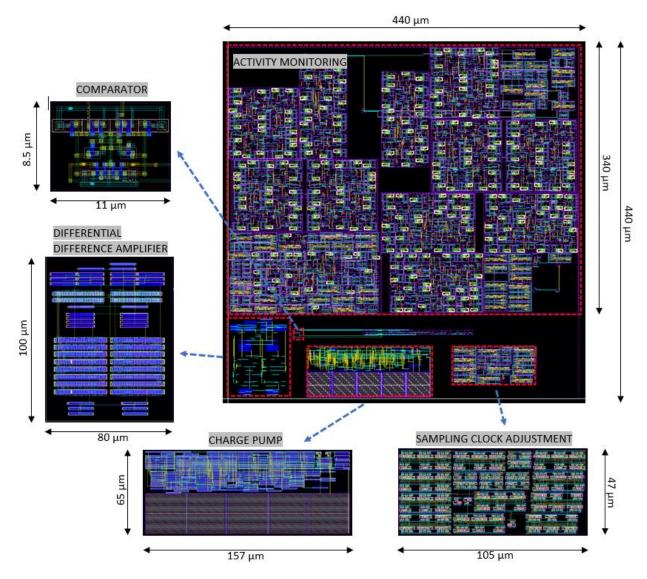

| Figure 3 23 : Layout view of Activity-Adaptive EEG Recording channel                | 66 |

## CHAPTER 1:

## Introduction and Motivation

### 1.1 Motivation and Objective

The ever-increasing demand for understanding human brain functions and dysfunctions requires methods and tools for monitoring brain activity, analyzing the acquired data, and in some cases, providing the proper feedback to stop/prevent an undesired neurological event. Unlike signal processing and neuro-modulation that are only required in diagnostic/treatment applications, brain neuro-monitoring is the essential first step toward any research on the brain. Depending on the required spatial and temporal resolution as well as the level of tolerated invasiveness, various brain imaging/monitoring technologies are available. Table 1 1, summarizes and compares different brain imaging/monitoring methods in terms of their spatial and temporal resolution, spatial coverage and invasiveness.

| Technology  | Spatial<br>Resolution<br>(mm) | Spatial<br>Coverage      | Temporal<br>resolution<br>(s) |

|-------------|-------------------------------|--------------------------|-------------------------------|

| MRI         | 0.5-100                       | $0.5 \text{ cm}^2 <$     | 500<                          |

| PET         | 5-100                         | $50 \text{ cm}^2 <$      | 10<                           |

| fMRI        | 2-100                         | $20 \text{ cm}^2 <$      | 0.5<                          |

| MEG         | 5-100                         | $50 \text{ cm}^2 <$      | 0.05<                         |

| EEG         | 10-100                        | $100 \text{ cm}^2 <$     | 0.05<                         |

| ECoG        | 1-50                          | $1-500 \text{ cm}^2$     | 0.005 <                       |

| Depth EEG   | 0.1-0.5                       | $0.001-0.2 \text{ cm}^2$ | 0.0005<                       |

| Patch Clamp | 0.01-0.03                     | 1-20 neurons             | 0.0001 <                      |

Table 1 1: Various brain neural activity monitoring methods compared in terms of their spatiotemporal resolution and spatial coverage.

Electroencephalography (EEG) is a standard test to acquire information about the metabolic and electric status of the brain. It is widely used for both the diagnostics and the monitoring of the state of human cognitive system, and provides brain activity recordings with high temporal and moderate-to-high spatial resolution. It is typically done in a hospital environment where the patient is tethered to a benchtop recording system and their neuro-electrical activity is sensed using several scalp electrodes (Figure 1 1), all placed based on a standard convention [1]. The test requires a trained technician to prepare the patient and the recording system, conduct the test, and perform post-test data collection and translation. As such, it is only practical for short periods (e.g., <1-2 hours).

Figure 1 1 : A typical EEG recording session in a medical facility

However, many applications demand long-term continuous monitoring of the brain activity to obtain a deeper insight into the root cause of particular neurological disorders. For example, prior to a brain resection surgery in epileptic patients, a long-term monitoring needs to be done in order to precisely localize the source of very-infrequently-occurring seizures. Long-term EEG monitoring is also used for monitoring vigilance level [2], sleep stages [3], and indices of impending severe hypoglycaemia [4] [5]. This became the motivation for development of a wireless medical device solution that can perform all the required tests while the patients go about their normal routines and daily activities and to eliminate the need for long term hospitalizations.

For most cases, intra-cranial EEG implants (i.e., deeply implanted in the brain), are too invasive to be acceptable. Therefore, over the past decade, several surface EEG recording systems in the forms of headsets, headbands, etc. have been introduced, and some of them are commercialized. The most important common issues with all of these solutions are (1) none of them are subtle enough to be used by the patient constantly during their daily routine without being obtrusive, and especially not comfortable enough to be worn during sleep at night; (2) all of them suffer from constant instability of recording electrode due to many reasons (e.g., talking, chewing, frowning, blinking, etc.), which cause recording artifacts that are orders of magnitude larger that the EEG signals. Therefore, the recording quality in terms of signal-to-noise ratio is typically not sufficient to be a reliable source for clinical applications.

Motivated by this, in this project, we studied the feasibility and challenges of the design and implementation of a minimally-invasive subcutaneous wireless implantable device, which (a) is not as invasive as deep-brain implants, (b) provides an unobtrusive continuous long-term EEG monitoring, and (c) its recording quality is not affected by motion-induced artifacts.

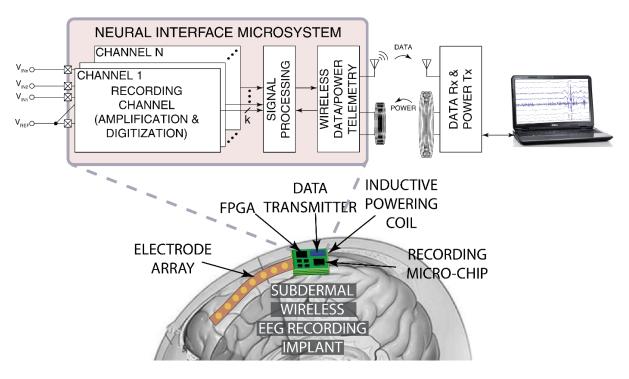

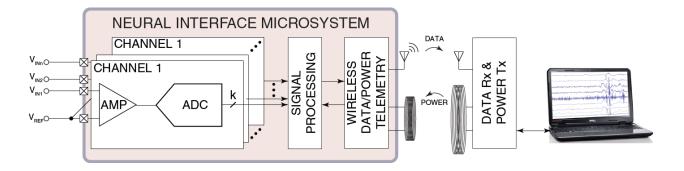

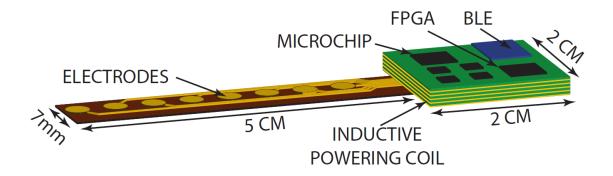

Figure 1 2 depict the high-level block diagram and envisaged implantation of the proposed solution. As shown, the device is comprised of an electronic backend connected to a flexible electrode array. The backend module will host a microchip that is responsible for multi-channel low-noise signal amplification and analog-to-digital conversion. Additionally, discrete components will be used to enable wireless data communication and embedded signal processing.

An inductive coil will be wound at the outer edges of the backend module for wireless power reception.

Two prototypes will be reported; first one presenting the design, development, and experimental characterization of an 8-channel custom-designed implementation of a neural recording microchip as well as a miniaturized platform for wireless communication and programmable neural signal processing. Next we will present a novel architecture for loss-less compressive activity-dependent neural data acquisition designed to improve the energy efficiency of the EEG recording device by more than an order of magnitude.

Figure 1 2 : Top-level block diagram and envisage implantation of the proposed subdermal implant.

### 1.2 Design consideration

### 1.2.1 Application-level

From the application-level point of view, the most important criterion is to minimize the solution's invasiveness. This involves both minimizing the device's weight and form factor, as well as its biocompatibility. Ideally, the device implantation surgery should be carried out by making a small incision on the scalp skin. The weight and size of the implant should be kept at a level that it is unobtrusive or minimally-obtrusive for the patient. Electrode array's material must be selected to be bio-compatible to prevent any damage to the neighboring tissue, and the electronic backend must be encapsulated using a bio-compatible material such as parylene-c or similar. Additionally, the device, particularly the electrode array, must be made using flexible material to accommodate various patients scalp size and curvature. Since this subcutaneous-EEG micro-system is considered as an outpatient care solution, the device must be designed to operate automatically with no need for patient's involvement. For the same reason, it is ideal for the device to be remotely controllable/configurable by the physician/technician.

### 1.2.2 System-level

From the system-level point of view, a sufficient number of recording channels must be integrated onto the device to capture the brain neural activity with a reasonable spatial resolution. Multi-channel recording is also required for multi-variate algorithms that use signals from different locations on the brain to perform seizure detection. In addition, to add diagnostic capability to the solution, the device should be equipped with a signal-processing unit that could be programmed with cross-patient or patient-specific diagnostic algorithms, depending on the application. Wireless communication is also an unavoidable feature that needs to be included in the system. Wireless

link specifications such as the link throughput and being uni- or bi-directional are decided based on (a) the application and the size of data that needs to be transmitted/received in real time, and (b) whether or not certain aspects of the system needs to be reconfigured wirelessly.

Perhaps, the most important system-level aspect of such an implantable device is the energy delivery. Envisaged to be fully unobtrusive, there can't be any external module to be mounted outside of the scalp. Therefore, continuous wireless powering of the device, which requires an external energy transmitter is not an option, and a battery is unavoidable. However, a battery that can last for several months is orders of magnitude larger (in terms of volume) to be implanted under the skin. Therefore, a hybrid approach where a small rechargeable battery that lasts ~1 day along with overnight wireless charging is ideal.

As it is discussed in details in [6], embedding signal processing on the device results in a significant reduction in decision-making latency and removes the need for a power-hungry high-throughput data transmitter that otherwise would be required to communicate raw EEG signals. However, it has the disadvantage of limited available computational power, which could lead to sacrificing the computation accuracy. Generally, a significant portion of signal processing (e.g., data compression, feature extraction and seizure detection) is conducted on an embedded processor, and only the signal processing results are communicated wirelessly. All of the system-level modules (i.e., recording channels, signal processing, and wireless transceiver) must be connected to each other using the least number of wires possible to realize a minimal form factor for the device. From a system-level point of view, this means using serializers/deserializers at the interface point of these modules to time-multiplex multi-bit data that is being communicated. Furthermore, to ensure that the solution is fully self-contained, all the necessary DC bias voltages and clock waveforms required for the operation of the integrated analog and digital circuits must

be generated using on-device components such as digital-to-analog converters (DACs), voltage regulators, and crystal oscillators.

#### 1.2.3 Circuit-level

From the circuit-level perspective, each recording channel should be able to amplify and digitize surface EEG signals with a typical amplitude range of  $10\mu$ V to a few mV and frequency content of up to 500Hz. The sensing front-end circuit must have (a) a differential architecture, (b) an input-referred noise that does not add substantially (i.e., more than 10%) to the noise that already exists at the recording electrodes ( $10\mu$ Vrms) [7], (c) input impedance that is orders of magnitude larger than the electrode-tissue interface impedance, (d) a reasonably high voltage gain, and (e) a mechanism for rejecting large (up to 100s of mVs) DC offset between the recording and reference electrodes. The input signal dynamic range demands a minimum ADC resolution of 8 bits.

In addition to the above design specifications that are roughly the same for implantable EEG recording front ends, a subcutaneous EEG-recording device has an important requirement that is mainly attributed to their large size where signals could travel a few centimeters between different modules. This makes the signals prone to various types of noise and interference from the environment and from neighbor components on the device. As such, the recording circuit should be able to strongly attenuate any noise or interference that is common between the recording and reference electrodes.

#### 1.3 State-of-the-art

To date, there hasn't been any report of a subdermal implant for long-term EEG monitoring. However, since many of the application, system, and circuit-level design

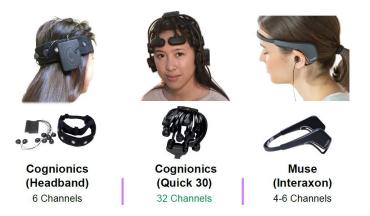

considerations are similar to wearable wireless ambulatory EEG devices, reviewing these works could provide useful intuition in design of the proposed subdermal implant. Table 1.2 summarizes some of the recently reported academic and commercial wireless monitoring headsets that aim to provide medical-grade EEG signals. Looking at these devices, it seems that the designs are either performance-oriented at the cost of sacrificing some of the application-level concerns (e.g., ease of use, comfort, lightweight, quick setup time, etc.), or user-oriented at the cost of reducing the system-level capabilities (Figure 1 3).

Figure 1 3 : Commercial examples of wearable EEG recording devices.

For example, the device presented in [8] meets the channel count, noise, bandwidth, and wireless connectivity requirements. The device is also designed to be adjustable to different scalp shapes and sizes. However, the weight and bulkiness of the device limits its usage to in-lab tests and inappropriate for ambulatory EEG recording. Also the device does not feature a mechanism for removing artifacts due to the physical motions of the patient, which could significantly degrade the recording quality. An example of the other end of spectrum is the Muse headband [9]. While this solution features a small form factor and lightweight, it only has 4 recording channels and uses passive electrodes for recording and integrates all the active circuitry on one side of the device, causing significant susceptibility to different types of noise and interference sources. Overall, none

of these devices is ideal to be used as a quickly-mountable medically-relevant ambulatory EEG monitoring and analysis headset for the applications described in the previous section.

| Specification           | [14]    | [18]    | [17]   | [17]   | [15]   |

|-------------------------|---------|---------|--------|--------|--------|

| # of channels           | 8       | 5       | 6      | 30     | 4      |

| Signal Processing       | Yes     | Yes     | Yes    | Yes    | No     |

| BW (Hz)                 | 0.5-100 | 0.5-100 | <262   | <262   | N/R    |

| Wireless Tech           | BT 2.1  | BT 2.1  | BT 4.0 | BT 4.0 | BT 2.1 |

| Motion Artifact removal | Digital | Digital | No     | No     | No     |

| Weight (grams)          | 200     | N/R     | 110    | 610    | 61     |

Table 1 2: Recently-reported wireless monitoring headsets for medical-grade EEG recording.

A number of commercially-available closed-loop implantable neural interface microsystems have been reported to enable some of the aforementioned functions. They are mostly designed for a very specific application and their primary use is for deep brain stimulation and recording, hence, lack the spatial coverage that is required for many applications [10].

### 1.4 Thesis organization

Chapter 2 presents the design, implementation, and experimental validation of an 8-channel custom-designed EEG microchip implemented in TSMC 180nm CMOS technology. It also reports a details analysis on the system-level design challenges of the subdermal implantable device, with a particular focus on its energy breakdown and bottlenecks. The chapter also presents design, and experimental validation of a miniaturized prototype that hosts a bidirectional wireless data communication module as well as a programmable computing module for neural signal processing.

Chapter 3 presents the design and simulation results of a novel channel architecture that targets significant improvement of system-level energy efficiency of the implantable device. The proposed design benefits from a fully-dynamic architecture and performs loss-less compression of the recorded EEG signals as it is performing the amplification and digitization. The compression of the signal is done in a fashion that EEG signal epochs with higher level of activity are recorded

with higher quantization resolution, and the idle periods (which are >90% of the time during an EEG recording) are recording with a low resolution. We have shown that this method leads to orders of magnitude energy efficiency improvement, particularly for cases that EEG recording is performed for a specific application, such as a neurological event (e.g. an epilepsy seizure) detection.

Chapter 4 concludes the thesis and discusses possible future directions for this research work.

## CHAPTER 2:

## A Wireless Subcutaneous Implantable

## Microsystem for Ambulatory EEG Monitoring

As discussed in the introduction, a subdermal implantable device seems to be an optimal solution for long-term ambulatory EEG monitoring. On one hand, it is not as invasive as a cortical or sub-cortical implanted device, and on the other hand is not prone to motion artifacts and interference like surface EEG devices.

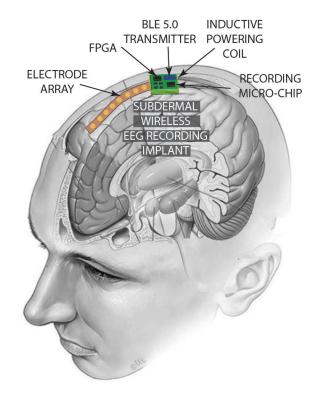

Figure 2 1 shows the envisaged implantation of the subdermal device. As shown, eight recording electrodes are implemented on an organic substrate in the form of a narrow strip, which is connected at the tail to a mini-PCB that hosts the active electronics. The organic electrode array is custom-designed and supplied by our industry partner in this project, Panaxium Inc. As will be described in this chapter, the mini-PCB is envisioned to host blocks for neuro-physiological recording, wireless data transmission, and wireless energy reception, management, and storage.

The implanted device will operate fully automatic and records, digitizes, and wirelessly transmits the EEG activities to an external computer (hand-held or desktop) in real time, with no need for external manual control. Since this solution is planned to be used for long-term applications, it is desired for the patient's comfort and psychological health that there will be no external modules attached to the body. Meanwhile, a battery that can last several months will be too large to be implanted. Therefore, we decided to use a rechargeable battery that lasts ~24-48 hours, giving the patient the option to only need to recharge at night. The direct correlation between the battery size (which is by far the largest component in this device) and its storage capacity further emphasizes on the importance of energy-efficient design for the recording and wireless communication blocks.

In the remaining of this chapter, we will describe the first prototype designed and developed in this project. First, the system-level design, considerations, and analysis are presented. Next the design of a custom-made 8-channel neuro-recording device is presented, followed by the characterization measurement results for the chip. The chapter ends with the measurement results for the wireless communication module, validating its performance.

### 2.1 System level design and consideration

During the course of this research, we worked closely with industry experts and our partner Panaxium to properly define system level criteria and metrics to capture the EEG signal successfully from the organic electrode array. Additionally, the required voltage amplification gain, input referred noise, input impedance, CMRR, PSRR, and the effective resolution of the digitized data have been defined to meet the requirements for effective high-quality neural recording. This has to be accomplished while the power consumption and physical size of the device are minimized.

A typical implanted neural recorder consists of an array of analog recording frontend channels that are responsible for low noise amplification and preconditioning (e.g., filtering) of biomedical signals, data converters to digitize the acquired data, and wireless data telemetry unit. Depending on the application, a digital signal processing block might also be included in the system. This block allows for pre-processing of the raw-recorded data before transmission. This way, only the processing results, which could be the detection of a certain neurological event will need to be transmitted instead of the raw recordings. The signal processing module could also relax the transmission throughput requirement by applying data compression algorithms on the raw recorded signals.

Figure 2 2, shows the top-level block diagram of the presented device. As shown, the microsystem includes 8 recording channels, each equipped with a low-power low-noise amplifier, a 10-bit analog to digital converter, and a parallel-to-serial converter that facilitates the data transition to the wireless transceiver. All channels are integrated into a single recording microchip and will be mounted on the front side of a miniaturized PCB board. BLE transceiver and the FPGA controller along with the battery will also be placed on the PCB board, while the electrode array

is connected to the PCB from one side. For biocompatibility, all electronics will be encapsulated with approved materials. Figure 2 3 shows the envisaged final prototype.

Figure 2 2 : Top-level block diagram of the presented device.

Figure 2 3 : Illustration of the envisioned final prototype.

| Parameter                   | Target                               |

|-----------------------------|--------------------------------------|

| Voltage gain                | > 200 V/V                            |

| Bandwidth                   | 1 Hz to 5 kHz                        |

| DC offset removal           | $\pm 100 mV$                         |

| Integ. Input referred noise | <10 µVrms                            |

| CMRR                        | > 60dB                               |

| Power                       | $< 10 \ \mu A \ \times \ \text{VDD}$ |

Table 2 1 : Early design specifications

### 2.1.1 Wireless Data Transmitter

As shown in Figure 2 1, the transmission of the data is enabled by a standalone and offthe-shelf Bluetooth Low Energy (BLE) chip which is controlled by the onboard FPGA controller. In addition to competitively high transmission data-rate, BLE offers highly standardized communication protocol that widens the application of this microsystem and can be paired with widely available electronics such as cell phones or any other sophisticated biomedical monitoring systems. [11]

Perhaps, the most important reason for adopting the Bluetooth technology in this project is their energy efficiency. The importance of energy efficiency of all active electronic blocks in the solution's overall size and feasibility was described earlier. However, it must be emphasized that the wireless communication module is by far the most important block in terms of power consumption. To help putting this in perspective, it should be noted that a typical commercially available neural recorder has a power consumption in the order of  $100\mu$ W [12], a typical wireless data transmitter that is specifically designed for low-power biomedical applications has an average of 10 mW of power dissipation in continues transmission mode. It can be deduced that overall battery life of an implantable EEG recorder is overwhelmingly limited to the efficiency of the data telemetry.

Motivated by this, an extensive research was conducted to identify the most suitable transceiver solution for this application (please see table 2 1). Based on our survey summarized below, we decided to use the Nordic Semi microchip, mainly due to its optimal performance in terms of power consumption and maximum data-rate.

| Manufacturer<br>Model No. | data<br>throughput | Nominal power<br>for 0dB output | Package size   | Additional consideration |

|---------------------------|--------------------|---------------------------------|----------------|--------------------------|

|                           |                    | power                           |                |                          |

| Nordic semi               | 2 Mbps             | 9.7 mA @ 1.8V                   | 5.00 x 5.00 mm | Built in MCU             |

| nRF8002 series            |                    |                                 | 32 pins        | BLE enabled              |

| TI                        | 2 Mbps             | 6.1 mA @ 3V                     | 7.00 x 7.00 mm | Built in MCU             |

| CC2640R2F                 | -                  |                                 | 48 pins        | BLE enabled              |

| TI                        | 500 kbps           | 16.8 mA @ 1.8V                  | 4.15 x 4.15 mm | SPI interface            |

| CC1101                    | _                  |                                 | 20 pins        | 2FSK                     |

| Microsemi                 | 256 kbps           | 5.3 mA @ 2 V                    | 7.00 x 7.00mm  | SPI interface            |

| ZL70103                   |                    |                                 | 48 pins        | 2FSK                     |

Table 2 2 : List of competitive contenders for wireless data telemetry

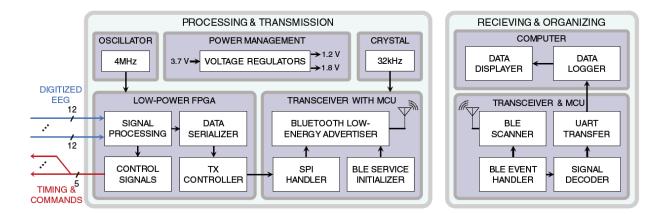

Figure 2 4 depicts a simplified block diagram of the prototype board that has been designed to validate the system-level performance of the presented solution, with a particular interest in the wireless transmission module and the way it is interfaced with the wireless receiving stationary module. As shown, the digitized EEG signals are first fed to the signal processing module for initial decoding and processing. The output of this block could be used to further optimize the data acquisitions (e.g., channel omission, sampling rate variation, etc.) as well as serialized and fed to the on-board wireless transceiver microcontroller unit using a serial peripheral interface (SPI) protocol. The microcontroller receives and organizes the raw data from the FPGA and prepares it for transmission.

Figure 24: Block diagram of the prototype board

In this work, we have used the Rigado BMD-350 module that uses the Nordic microchip introduced above (Table 2 1). The module integrates both the transmitter Bluetooth chip and its planar antenna. Table 2 2 compares this transceiver module with the most popular wireless module for medical applications used in the literature. On the receiver side, a development board from Rigado is used to receive and decoded the data and send it to the USB port of a bench-top computer using a universal asynchronous receiver-transmitter interface.

Comparison of the off-the-shelf available Bluetooth microchips/modules for medical sensory applications.

| Transceiver              | NINA-B112               | BL652                   | ZL70103               | CC2640R2F             | BMD-350     |

|--------------------------|-------------------------|-------------------------|-----------------------|-----------------------|-------------|

|                          | [32]                    | [33]                    | [34]                  | [35]                  | [36]        |

| Energy Efficiency (nJ/b) | 9-19                    | 9-19                    | 15-19                 | 11-23                 | 12-25       |

| $I_{DC}$ at 0dBm (mA)    | 5.3                     | 5.3                     | 5.3                   | 6.1                   | 7.1         |

| VDD (V)                  | 1.7-3.6                 | 1.7-3.6                 | 2.8-3.5               | 1.8-3.6               | 1.7-3.6     |

| Duplex                   | N/R                     | Full                    | Half                  | Full                  | Full        |

| Physical Size $(mm^3)$   | $14 \times 10 \times 4$ | $14 \times 10 \times 2$ | $6 \times 5 \times 2$ | $7 \times 7 \times 2$ | 8.7×6.4×1.5 |

| Antenna                  | Internal                | Internal                | External              | External              | Internal    |

| Max DR (Mbps)            | 1                       | 1                       | 0.8                   | 1                     | 2           |

Table 2 3 : Comparison of the popular off-the-shelf wireless modules

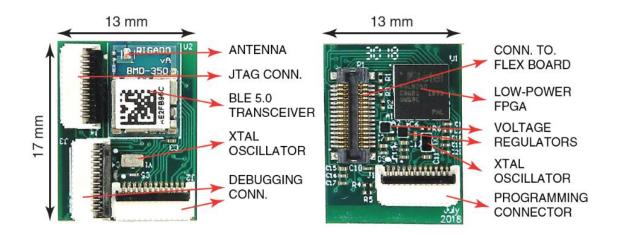

Figure 2 5, shows the top and bottom view of a 13mm×17mm PCB implementation of the presented backend module. The board is populated with the low-power Microsemi FPGA as the main processor, making the device capable of hosting small-to-medium-size (in terms of computational expense) neural signal processing algorithms, a Bluetooth low energy (BLE) 5.0 transceiver module with a built-in antenna for wireless communication (Rigado BMD350 built based on the nRF52832 SoC from Nordic Semiconductor).

Figure 2 5 : The PCB prototype board

Figure 2 5, also shows other components on the backend PCB including voltage regulators, connectors, crystal oscillators and peripheral passive components to ensure that the board can operate as a self-contained module and only requires a 3.7V supply voltage. The full list of components used in this implementation is provided in Table 2 3.

| Component          | Company           | Model              |  |

|--------------------|-------------------|--------------------|--|

| D 1                |                   |                    |  |

| Regulator-3.3      | Analog device     | ADP121-ACBZ33R7    |  |

| Regulator-1.2      | Analog device     | ADP121-ACBZ12R7    |  |

| Adj Regulator      | Linear Technology | LT3020EMS8xPBF     |  |

| BLE Tx             | Rigado Inc        | BMD-350-A-R        |  |

| FPGA               | Microsemi         | AGLN250V2-CSG81    |  |

| XTAL 32kHZ         | ECS Inc           | ECS327-6-12-C-TR   |  |

| Oscillator 4MHz    | SiTime            | 8021AI-J4-XXS-4.0E |  |

| Vertical Connector | Panasonic         | AXT430124          |  |

| Vertical Connector | Panasonic         | AXT430324          |  |

| FFC Connector      | Molex             | 5034801200         |  |

Table 24: List of components used

### 2.1.2 Power Management

Similar to the wireless module, we carried out research to identify optimal battery that can power this system. Ideal batteries should be compact and capable of max discharge rate of greater than 11 mA (~10mA for BLE chip in addition to the estimated 1mA for the EEG recoding chip). More importantly, we needed to ensure that the battery has the sufficient capacity to last at least 12 hours before recharging. Based on the above, DTP301120 polymer Li-ion rechargeable battery, which can support nearly 4 hours of continuous data transmission at max data rate is the most attractive choice for this application. We decided to sacrifice the battery lifetime to avoid increasing the solution size beyond the budget set for us by our collaborators. Later in Chapter 3, we will show that how we leveraged the sparsity of EEG signals to achieve an order of magnitude longer battery cycles with the same battery.

| Model #                | Capacity        | Max Discharg<br>rate | e size             |

|------------------------|-----------------|----------------------|--------------------|

| DTP301120              | 40 mAh (3.7V)   | 40mA                 | 11.5 x 22 x 3.2 mm |

| 031015                 | 16 mAh (3.7V)   | 48 mA                | 10 x 15 x 3 mm     |

| Bottoncell:MS920SE     | 11 mAh (3 V)    | 0.8 mA               | 9.5 mm x 2.1 mm    |

| Bottoncell:MS621FE     | 5.5 mAh (3 V)   | 0.25 mA              | 6.8 mm x 2.1 mm    |

| Eagle Picher - D-00020 | 50 mAh (3.65 V) | 25 mA                | 18x12x4.5 mm       |

| Wyon - W102            | 18 mAh (3.7 V)  | 36 mA                | 10x6.5x4 mm        |

Table 25: Comparison of various batteries for capacity, discharge rate and size

### 2.2 Analog front-end and signal preconditioning

Accuracy of EEG monitoring system heavily relies on the performance of its Analog frontend and mainly low noise amplifier. While the number of recording channels are specified by the spatial resolution required by the application, the electrical performance requirement for each channel is relatively similar for all neuro-physiological recording circuits. The circuit should have sufficient frequency bandwidth, that is 500Hz if designed for local field potential (LFP) recording, and 5 kHz if designed for recording action potentials (APs). The voltage gain must be large enough to amplify the smallest neural activity (~10uV) sufficiently so that a low-power ADC is able to digitize it with the required resolution. On the other hand, the gain should not be so large that a strong neural signal (e.g., 1mV amplitude) saturate the amplifier.

The recording circuit architecture must be differential to enable the use of a reference electrode for removing common-mode signals and interference. To ensure maximum common-mode rejection and minimal loss of signal at the electrode interface, the front-end circuit must have the highest possible input impedance. Additionally, the input-referred noise must be minimized to obtain the highest possible signal to noise ratio. This includes both thermal and flicker noise that are generated by the circuit and referred to the input. Another challenge in the design of neural amplifiers is removing a DC offset voltage at the input that is generated due to chemical reactions between brain cells and microelectrodes, and can saturate the amplifier. As it has been mentioned before, all of the above must be done while maintaining the area and power consumption within the budget specified by the application or the desired battery life-cycle.

To make the chip capable of both LFP and AP recording (the AP recording is for future applications), we decided to design the amplifier capable of capturing EEG signal within the frequency spectrum of 1 - 5 KHz and amplitude ranging from  $10\mu$ V to 5mV while eliminating any possible DC offset that may be caused by electrochemical activities at the recording site. [13]

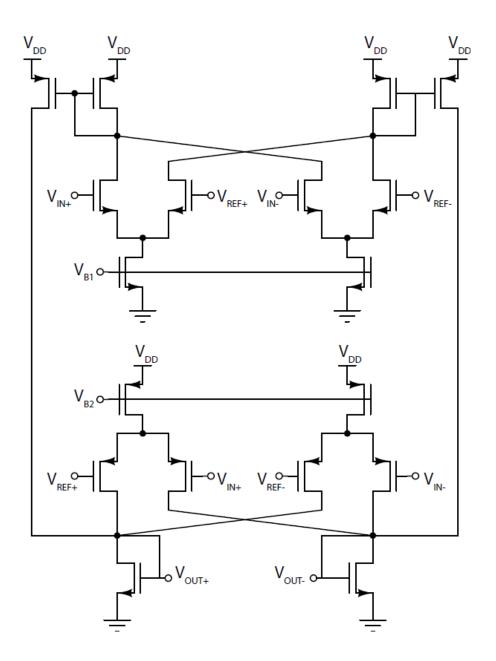

To maximize CMRR, fully differential folded cascaded OTA, shown in Figure 2 6, topology was chosen for the first amplification stage with large PMOS devices at the input to minimize the flicker noise. [14] It's worth mentioning that choosing large PMOS devices also

facilitates lowering the overdrive voltage for these devices when biasing them in subthreshold region of operation. It's well known that transconductance "gm" of MOS transistors is inversely proportional to their overdrive voltage and putting input devices in subthreshold region for the same drain current (i.e., same power consumption) will help maximizing their transconductance.

$$gm = \frac{2I_D}{V_{ov}}$$

To remove the DC offset, input transistors are AC coupled to the organic electrodes using two on - chip metal-insulator-metal (MIM) capacitors. The voltage gain of this stage is set by the ratio of C1/C2. C2 was set to 300 fF, which is the minimum possible MIM cap that could be implemented in this technology. Accordingly, to C1 was set to 15pF to realize a voltage gain of 50 V/V. C2 also influences the amplifier's bandwidth. The low-frequency high-pass pole of the amplifier is set by  $1/(R_2C_2)$ . Given the small value of C2, to achieve a high-pass pole of 1Hz,  $R_2$ needs to be greater than  $1G\Omega$ . Implementing such a large resistance on the chip as a passive component is not feasible due to its area that will be orders of magnitude larger than the entire active circuit. Instead, we decided to use pseudo-resistors that are implemented using diodeconnected long thick-oxide NMOS transistors, as shown in Figure 2 6. A common-mode feedback (CMFB) circuit, depicted in Figure 2 7, is used to set the DC output of the amplifier and ensures a DC level of V<sub>CM</sub>=0.9V at all times.

Figure 26: Circuit view of the analog front-end including fully differential folded cascaded OTA

| Device                | Width (µm) | Length (µm) | Multiplier |

|-----------------------|------------|-------------|------------|

| First stage : M1, M2  | 2          | 1.5         | 25         |

| First stage : M3, M4  | 2          | 15          | 1          |

| First stage : M5, M6  | 4          | 10          | 1          |

| First stage : M7, M8  | 1          | 2           | 1          |

| First stage : M9, M10 | 1          | 1           | 1          |

| 2nd stage : M1, M2    | 2          | 5           | 1          |

| 2nd stage : M3, M4    | 1          | 10          | 1          |

| 2nd stage : M5        | 1.6        | 3           | 1          |

| 2nd stage : M6        | 1          | 10          | 1          |

| 2nd stage : M7        | 2          | 3.5         | 1          |

| 2nd stage : M8        | 0.9        | 3.5         | 1          |

Table 2 6 : Summary of transistor sizing for AFE

As shown in Figure 2 6, a second stage of amplification is added to the recording channel to increase the overall voltage gain. Similar to the first stage, a capacitively-coupled negative feedback amplifier topology is used. Since the input referred noise of the second stage is significantly attenuated by the first-stage gain, its noise performance requirement is much more relaxed. As depicted, for this stage, we used a two-stage OPAMP.

Figure 27: Circuit view of the common mode feedback

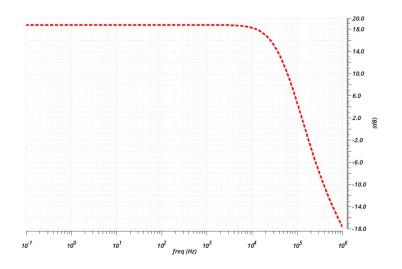

Figures 2 8 and 2 9, show the gain-bandwidth simulation results for the first and second stage amplifiers. The first stage, which uses a fully differential folded cascade OTA, has a closed-loop gain of 33.5dB, for the 1Hz to 24 kHz bandwidth. The circuit's stability is also verified and it shows a phase margin of 60 degrees.

Figure 28: Gain and phase plot for first stage folded cascaded OTA

The second gain stage, employing a low power and wide swing OpAmp , has a closed loop gain of 15.5 dB , and was also stable with a phase margin of 50 degrees as shown in figure 2 9, The 3dB bandwidth for this stage was 0.4 Hz to 45 KHz.

Figure 29: Gain and phase plot for second stage OpAmp

Overall, both amplification stages have a combined gain of 49 dB with overall bandwidth of 1 Hz to 20 KHz. Figure 2 10, shows the simulation results for the voltage gain and bandwidth of the two-stage amplifier, which both meet/exceed our initial targets.

Figure 2 10 : Gain bandwidth plot for overall gain stages

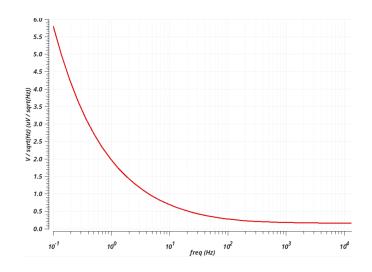

The input - referred noise of the analog front end is simulated and plotted in figure 2 11. The high frequency noise floor is at 46nV/sqrt(Hz) and the integrated input referred noise from 1Hz to 5 KHz was calculated at approximately 6  $\mu$ V RMS. It's worth noting that as shown in figure below flicker noise 1/f becomes the dominant source of noise for frequencies below 100Hz as expected.

Figure 2 11 : Input referred noise for the analog front end

We should also mention that the input impedance is maximized as the amplifier's inputs are connected to the gates of PMOS devices with fA leakage current, leading to a super-G $\Omega$  input impedance. Such a high Z<sub>in</sub> along with the fully differential architecture of the amplifier guarantees

a high CMRR. Simulation results were conclusive that the designed analog front-end met the system level requirements and criteria and are ready to be passed on to the data converter.

#### 2.3 Data conversion using SAR ADC

As mentioned earlier, the EEG data needs to be digitized and serialized before wireless transmission. Considering the EEG's low-frequency signal content and to minimize the power consumption, the successive approximation register (SAR) topology was selected for the ADC. The ADC should be designed with a dynamic range that covers the entire magnitude range of the EEG signals, when amplified by the two-stage amplifier. Given the voltage gain of 240 V/V, and the desired ranged of 10uV - 5mV at the amplifier's input, the ADC's input dynamic range should be equal to 2.4mV - 1.2V. Accordingly, the required ADC resolution is calculated as:

required quantization levels

$$=$$

$\frac{1.2V}{2.4mV} = 600$

requied ADC resolution  $= log_2^{600} = 9.23$

Considering minimum required resolution of 9.23 bits and accounting for non-idealities in practical ADCs such as quantization errors and mismatches caused by parasitic, a resolution of 10 bits was chosen for this design.

SAR ADCs convert sampled values from a continuous analog waveform into digital quantized values through a binary search process where each sampled value is compared against a sequentially-approximated voltage level. The digital output bits, from MSB to LSB, are set based on the result of the consecutive comparisons. The reference voltage level for the next comparison is also set based on the result of the previous comparison. After n repetitions are done, where n is the ADC's number of bits, the conversion is completed. Number of bits don't affect the data

conversion flow however higher number of bits will lengthen the binary search, hence, make the ADC slower.

The first stage, that is, the track and hold (see Figure 2 12), was implemented using a transmission gate with analog signal at input and a capacitor as the storage that will be charged to the sample level and will retain this voltage as SAR comparison commences. Schematic view of the sample and hold circuit is displayed below. (For simplicity, connection to other terminals of the comparator are not marked.)

Figure 212: Sample and hold circuit

Sampled level needs to be compared to all possible quantization levels which will be generated by a capacitive DAC. A 10-bit binary-weighted capacitive DAC is employed in this design to generate the required 1024 voltage levels. All capacitors have a common terminal connected to the comparator which is also the output of the DAC and their other terminal is individually controlled (charged / discharged) by SAR logic, and thus any possible voltage level within the target resolution can be synthesized. A simplified view of the implemented capacitive DAC is illustrated below.

Figure 2 13 : Capacitive DAC with binary weighted capacitors

The successive approximation starts with setting the most significant bit (MSB) to 1. Then this value is sent to the DAC which generates the corresponding analog value. If comparator determines that sampled value is greater than DAC output, the bit is left as 1 and we move on to the next bit.

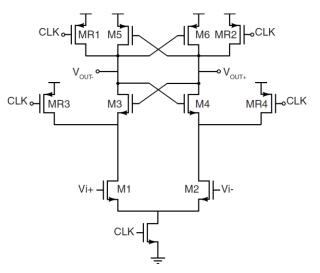

The comparator used in this project was designed based on the "strong arm" architecture. The circuit, shown in Figure 2 14, has a fully-dynamic power consumption, benefits from a preamplifier stage to minimize the kick-back noise, and uses all-node-reset method to achieve a minimal hysteresis. Once the "clk" has fallen to 0, the output node of the comparator is charged to 1. In this mode, all the other nodes in the circuit are also reset to VDD/GND to ensure no residual charge is left in the parasitic capacitors before the comparison starts. This will ensure minimal offset and hysteresis for the comparator. Once the "clk" is raised to 1, the input differential pair, as well as the cross-coupled positive feedback loop are enabled and the two outputs slew away from each other to VDD and GND, indicating the comparison result as a 1 or a 0. [15]

Figure 2 14 : Strong Arm Comparator

| Device                                                  | Width (nm) | Length (nm) | Multiplier |

|---------------------------------------------------------|------------|-------------|------------|

| MR1, MR2, MR3, NR4                                      | 420        | 250         | 4          |

| M1, M2                                                  | 420        | 250         | 1          |

| M3, M4, M5, M6                                          | 420        | 250         | 1          |

| Tail NMOS CLK                                           | 420        | 250         | 2          |

| T-11-27 Commence of the side of the ADC's second to the |            |             |            |

Table 27: Summary of transistor sizing for ADC's comparator

In this design, the comparator output could be fed to a shift register to generate a parallel output after 10 clock cycles, or could be directly used as the serial output. If used as a serial output, it should be noted that the data is valid for certain clock cycles, and invalid for the others. Therefore, timing information of the SAR ADC must be sent along its serial output bits to the block that will use them (e.g. a signal processing block, or a wireless transmitter). We should mention that since the BLE transceiver requires single-ended data, the other terminal of the comparator was connected to a dummy load so not to introduce mismatches in the design.

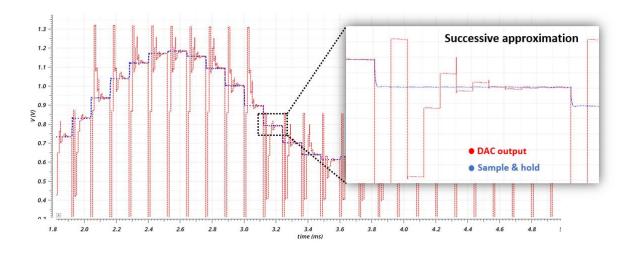

Figure 2 15 : Transient analysis of the SAR ADC

Figure 2 15 shows an example transient simulation results of the SAR ADC's output in response to a sinusoidal input. The blue trace represents the sampled and hold value of the 500-Hz sinusoidal wave and the red trace is the output of the SAR DAC which tracks the sampled value successfully. Based on the post layout simulation results, the effective number of bits (ENOB) was calculated as,

$$ENOB = \frac{SNR - 1.76}{6.02} = 7.85$$

Bit

Effective number of bits is directly related to the parasitic mismatch in the SAR ADC's capacitive DAC, choosing larger capacitors will significantly improve ENOB at the cost of higher power consumption and larger area.

#### 2.4 Integration and fabrication

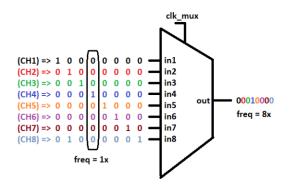

Once front-end and Data converter blocks were successfully verified to meet the system level criteria, they were integrated to form a single recording channel depicted in Figure 2 2. Eight recoding channels were implemented and their serial outputs were fed to a multiplexer that interfaces with the BLE chip for wireless data telemetry. The parallel to serial converter was comprised of an 8-to-1 multiplexer which is controlled by a "clk" with 8 times the frequency of the generated data. Once transmitted, the bit stream will be deserialized inside a microcontroller unit to reconstruct each channel's data.

Figure 2 16 - 8:1 Mux used for data serialization

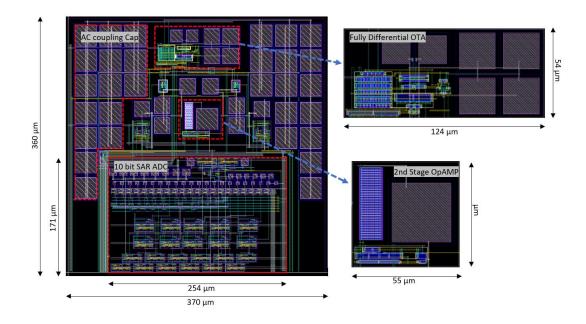

Figure 2 17, shows the layout of the described recording channel with major blocks annotated. As shown, each channel includes a 10 bit SAR ADC, a fully differential OTA and an OpAMP for additional gain which all together take an area of less than 0.14 mm<sup>2</sup>.

Figure 2 17 : Layout of the EEG recording channel (0.36 x 0.38 mm)

Figure 2 18, shows the full layout of the chip with all 8 recording channels, the parallel-toserial data converter, as well as additional blocks for testability, signal buffering, and ESD protection.

Figure 2 18 : Full chip layout of 8 channel EEG recorder

# 2.5 Experimental Measurement Results

The microchip was fabricated in TSMC 0.18  $\mu$ m technology through CMC microsystems services. Following fabrication, the chip was packaged (PGA-68) and was tested using a development test-bench PCB, which was custom-designed and fabricated for this project as shown in figure 2 19.

Figure 2 19 : Magnified view of the fabricated chip along with test-bench PCB

To measure the gain and bandwidth of the analog front end, sinusoidal function generator with capability of generating differential source was connected to the input of subthreshold OTA (using BNC connector for robustness) with differential peak to peak amplitude of 2mV, then frequency of the input wave was swept from 0.1 Hz to 40 KHz and the output amplitude after the single ended OpAmp was probed and measured. Result of this measurement is plotted in Figure 2 20, Gain of 48.8 dB was recorded which was very close to the post layout simulation results of 49dB. However, 3dB bandwidth deviated from the expectation by 5 KHz and was recorded at approximately 15 KHz. It was observed during the design stage that bandwidth is sensitive to the variation of reference current and also post fabrication parasitic and PVT variations could also contribute to the mismatch between bandwidth expectation and measurements. Nevertheless, our system level requirement bandwidth of 5 KHz is clearly achieved and the chip performance won't be affected by the aforesaid variation.

Figure 2 20 : Measured gain - bandwidth graph post fabrication

Input referred noise was measured by shorting inputs of the input amplifier to the ground and measuring the noise magnitude at the output, the measured noise is then divided by the overall front end's gain to evaluate the input refereed noise. The results of this measurement are plotted in figure 2 20. At lower frequencies, the measured noise was higher than the simulation results i.e. at 8Hz, measurement:  $1\mu V/\sqrt{Hz}$  vs. simulation:  $0.5 \mu V/\sqrt{Hz}$ , however the gap between measured and simulated results reduces at higher frequencies i.e. at 110Hz, measurement:  $128 \text{ nV}/\sqrt{Hz}$  vs. simulation:  $136 \text{ nV}/\sqrt{Hz}$ . Noise measurement can be significantly affected by environmental elements such as Electromagnetic interference (EMI), and also process corner variation will contribute to any mismatches between simulated and measurement results.

Figure 2 21 : Measured input referred noise

Table 2.7 summarizes the overall specification of fabricated chip at both channel-level and the chip-level. Measurement results confirm that the chip meets the expectations for high-quality neural recording. Nonetheless as discussed in section 2.3, this was an engineering design decision to priorities lower power consumption and smaller chip area over higher ENOB for SAR ADC.

| Overall specification summary                    |                         |  |

|--------------------------------------------------|-------------------------|--|

| ASIC area                                        | $3.75 mm^2$             |  |

| Technology                                       | TSMC 0.18 μm            |  |

| Analog front end power consumption (per channel) | 3.7μA RMS               |  |

| ADC power consumption (per channel)              | 14.4μ <i>A</i> RMS      |  |

| Gain                                             | 48.8 dB                 |  |

| Bandwidth                                        | 15 KHz                  |  |

| Int. input referred noise                        | 6 μV RMS (1 Hz – 5 KHz) |  |

| ADC resolution                                   | 10 bit                  |  |

| ADC ENOB                                         | 7.85 bit                |  |

| # of channels                                    | 8 Channels              |  |

Table 2 8 : Overall specification summary

# CHAPTER 3:

# An Activity-Adaptive Loss-Less-Compressive EEG Recording Channel Architecture

#### 3.1 Introduction and motivation

As discussed in the previous chapter, wireless data transmission is responsible for the majority (i.e., >80%) of the implantable device overall power consumption. Despite adopting one of the most energy efficient wireless technologies (i.e., BLE 5.0), our calculations show that the implantable device presented in chapter 2 can only last ~4-5 hours of continuous operation without the need for a battery recharge. It was also discussed that for practical reasons, a minimum of 12 hours of operation (ideally, >24 hours) is required for ambulatory long-term EEG recording devices. It should also be considered that the system presented in the previous chapter has only 8 recording channels. Similar to surface EEG, carrying out a clinical-grade recording with sufficient spatial resolution and coverage, more electrodes needs to be added to the system, hence, more number of recording channels. This means more EEG data is acquired at any moment, which demands higher communication data-rate, further reducing the battery life.

The above further emphasizes on the vital role of data transmission energy efficiency in overall success of the brain-implantable device. Reviewing the literature, we noticed that due to the wide availability of far-field radio transmitters and a myriad of different infrastructures (e.g., Bluetooth Low Energy, Wi-Fi, etc.), these transmitters can be employed conveniently, and are expected to exhibit robust operation [16]. However, even the best low-power radios consume >1 nJ/b [17] [18], which is an order of magnitude larger than what we require for a sub-dermal EEG.

As an alternative to far-field radios, impulse radio ultra-wideband (IR-UWB) transmission has been proposed and employed in a few recent reported devices. UWB radios do not require to generate a carrier signal and generally use a very wide band of frequencies (3.1-10.6GHz) and yield high data-rates with a few tens of pJ/b energy efficiency [19] [20]. However their high peak transmission power requires a large high-capacity battery for operation. They also need the receiver to be at a cm-scale distance (e.g., on skin), making them less practical for our application of interest. The same issue is valid about the near-field backscattering transmitters that are highly energy efficient, but require the external module (i.e., the interrogator) to be placed on the skin [21] [22] [23].

Considering the above discussion, it seems that while the more energy-efficient technologies such as UWB and near-field backscattering might be an attractive solution for implantable devices with in-lab or short-term applications, far-field radios are the only practical option for a long-term ambulatory applications, where the patient's comfort and normal day-to-day life is of greater priority. This motivates for devising strategies that allow for using the far-field transmitters, without sacrificing the battery life.

In the rest of this chapter, we will first introduce our proposed idea for lossless EEG data compression, and later, describe the circuit implementation, characterization, and integration.

## 3.2 LFP signals Sparsity

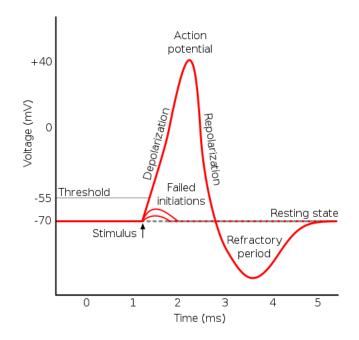

In defining the characteristics of EEG signal for long term monitoring applications, it's essential to review and distinguish between two different classes of bio potentials. "Action potential" is the result of individual cell's depolarization which in turn ripples through adjacent cells (Figure 3 1). Action potentials are the fundamental means to cell-to-cell communication. [24] By nature, action potentials are very unique to individual cells and recording them requires invasive direct access to the cell with use of fine, needle-shaped probes that are inserted into the brain.

Figure 3 1 : Diagram showing phases of an action potential over time [25] On the other hand, local field potentials (LFPs) are extracellular signals that could be defined as the spatially-averaged sum of action potentials of a cluster of cells in a region of interest.

LFPs are monitored by placing electrodes in the vicinity of a group of neurons and as the name implies, the field created by the cells in that spatial radius will be visible to the neurological recorder. Since direct access to individual cells are not required, this method is significantly less invasive in compare to recording action potentials, making it more appropriate for long-term ambulatory EEG recording [26].

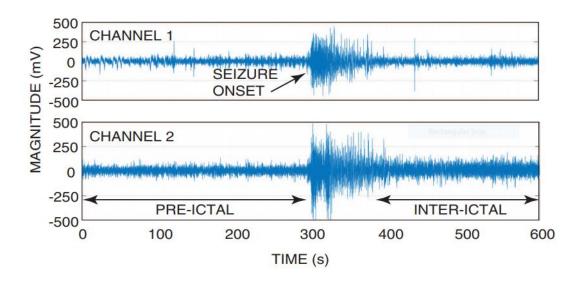

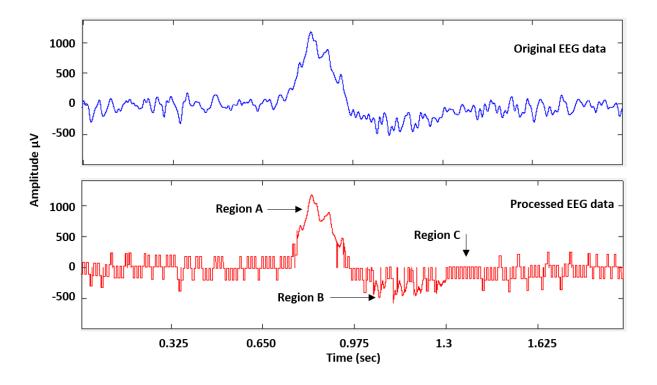

Figure 3 2 : LFP EEG recording from CHB-MIT scalp EEG database [27]

As illustrated in Figure 3 2, LFP EEG activities of the brain are represented with large transient spikes in amplitude of the local potential field which are sparse in time domain. [28] As mentioned earlier sampling sparse signals at a continuously high frequency are not efficient and will lead into significant overhead for the transmitter. By properly defining the sampling windows and adjusting the sampling rate accordingly it's possible to drastically reduce the data generation and extend the implantable device's battery life. It's also worth noting that since Nyquist condition is met for each sampling window, this technique is theoretically loss less and the sampled data can be completely reconstructed once transmitted.

#### 3.3 EEG Recording with Activity-Adaptive Quantization Resolution

Generally, recording of sensory signals, including biomedical signals, starts with lownoise signal amplification, followed by signal conditioning stages such as spectral filtering and noise reduction, and ends with the digitization of the data before being ready for processing on- or off-chip [29]. Considering the unpredictable and non-periodic nature of the LFP EEG signals ,the recording process is required to be done continuously to ensure high temporal resolution. However, depending on the level of signal's activity (i.e., transient dynamic range) the required sampling rate to fully capture the signal's dynamics might vary. Of course, adopting a variable sampling rate should be done without violating the Nyquist rate. A crucial principle in sampling any continuoustime signal is the Shannon-Nyquist sampling theorem which states, "A band-limited signal with bandwidth X can be perfectly reconstructed if it's sampled with a frequency 2X" [30].

One way to deal with this is to leverage the fact that the Nyquist rate varies for different intervals in an EEG recording. Therefore, it'd be possible to acquire signals with a variable sampling rate (i.e. non-uniform sampling), which results in an adaptive temporal resolution that it is correlated with the signal "level of activity". Adopting a non-uniform sampling approach means that the maximum sampling rate (hence, data rate) is only used for a fraction of time, which for the typically-sparse EEG signals would be a very small fraction. Consequently, it results in a significant reduction in the required data transmission throughput.

While the advantages of this idea are clear, it has a fundamental issue that constrains its efficacy in practice. Due to the unpredictability of the EEG signals, the sampling rate variations must be done based on the signal's average level of activity for the past x number of samples. Therefore, the quantized data must be fed to an activity monitoring block that decided to increase/decrease the sampling rate. The problem happens when a sudden activity such as a seizure

starts right after a low-activity period. In this situation, due to the recent past low activity, the circuit is sampling at a low rate. Since the activity monitoring block is using an averaged metric, it is very likely for the circuit to take a long time to understand that it must increase the sampling rate. Hence, a time-sensitive sudden short neurological event might be completely missed or the detected very late.

This motivates for a recording technique that adjusts the quantization resolution rather than the sampling frequency. Using this method, the signal is always sampled at the Nyquist rate, but the resolution of the digital output is adaptive to the signals level of activity. While the idea is simple and elegant, it's effective and efficient implementation could be quite challenging with two fundamental problems.

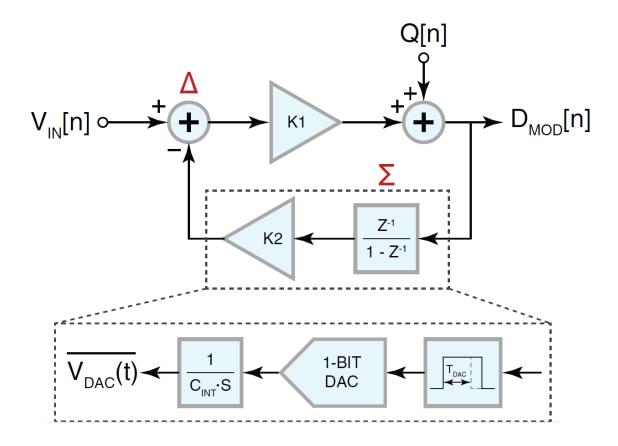

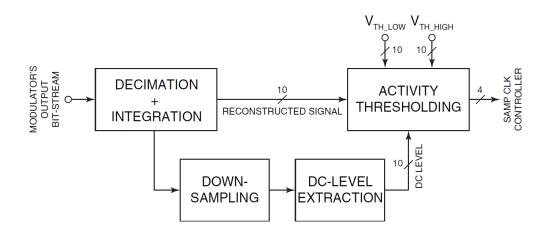

The first problem is that generally, nyquist-rate ADCs are designed for a certain resolution that is set by the application. For example, for a SAR ADC, the capacitor bank sizing, the sampling stage precision, the comparator dynamic settling error, and many more parameters are set based on the required quantization resolution. This means that a SAR ADC with a variable resolution will still have to meet the area and power requirements that are determined by the maximum resolution. This means that the benefits of an adaptive resolution ADC will only be limited to the wireless transmission data-rate and the recording channels power consumption will still be more or less the same. The second issue is related to the fact that the sequential operation of these ADCs are generally designed for a set resolution, and a variable resolution could cause serious complexity in terms of post-ADC data handling. Such irregular data handling requires complex digital timing controllers with substantial dynamic power consumption, which is against the initial goal of energy efficiency. Driven by the above discussion, in this work, we propose to use an oversampling spectralshaping amplifying ADC that (a) has a variable adaptive resolution that can be adjusted with a simple clock frequency variation, and does not require post-ADC data re-synchronization, (b) integrated a dynamic amplification stage inside itself, making the amplifier's power consumption adaptive as well, (c) leverages single-bit activity monitoring computation, which significantly reduces the dynamic power consumption of this module.

#### 3.4 System-Level Design

It is expected that by employing the described activity-adaptive variable data rate recording strategy, the wireless transmission throughput, hence, the power consumption reduces significantly. This will bring the power consumption of this block to the same level as the array of recording channels. Therefore, it is crucial to ensure that the recording channels' power consumption is also scaling down proportional to the activity slow down. This demands for a recording channel architecture with a power consumption that is dominantly dynamic. Therefore, an increase/decrease in the clock frequency, not only changes the oversampling ratio of the quantizer (hence, its resolution), but also directly varies the power consumption of the recording front-end.

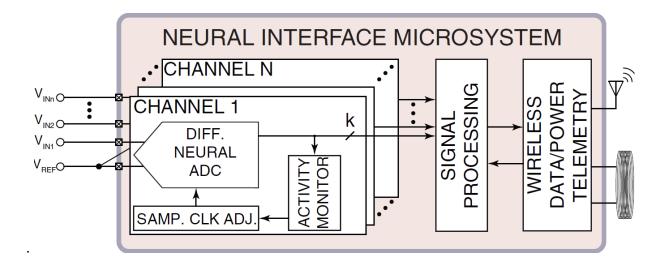

Conventionally, the EEG recording front-ends are designed based on an amplifier+ADC architecture, such as the circuit described in Chapter 2. However, in recent year, a new generation of fully-dynamic neural ADCs have been reported where amplification and digitization are both done in a single stage [31] [32]. Adopting this type of front-ends makes the recording channel's power consumption proportionate to the required sampling rate, hence, adaptive to the signal's activity. The top-level block level diagram of the proposed system is shown in Figure 3 3.

Figure 3 3 : Block level diagram

As shown, the EEG signals are fed to an array of differential fully-dynamic neural ADCs, which are responsible for low-noise amplification and quantization. The digital output of the recording channels are fed to an activity monitoring block where the required quantization resolution is calculated and fed back to the front-end neural ADC to make its performance adaptive to the EEG level of activity. The output of the recording channels together with the resolution information are fed to the wireless transmission block.

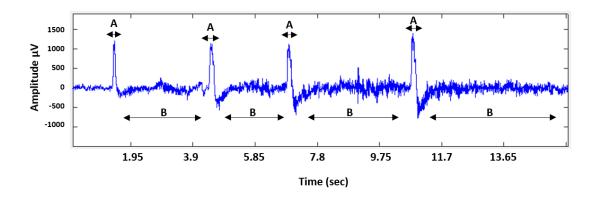

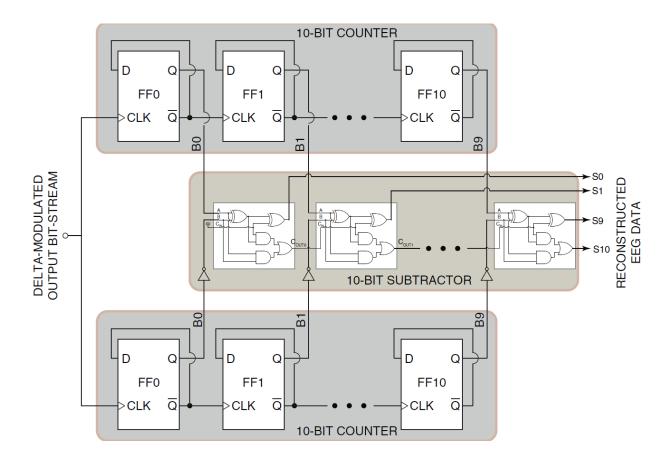

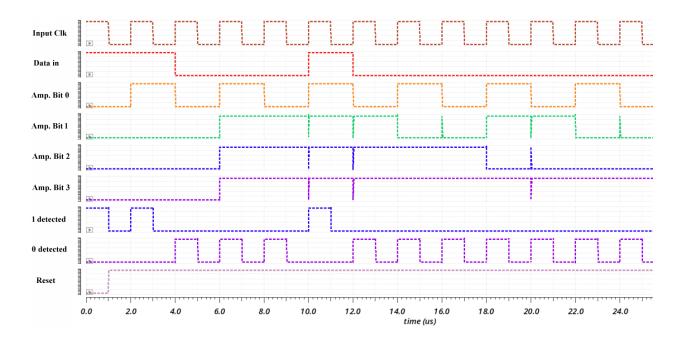

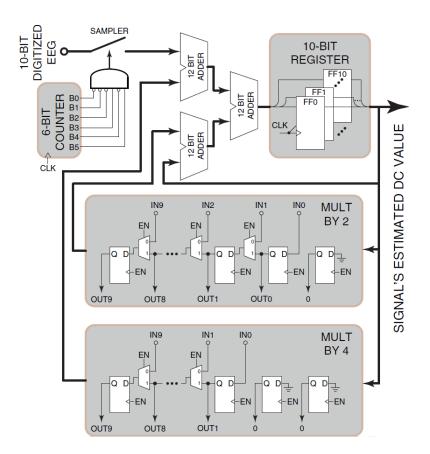

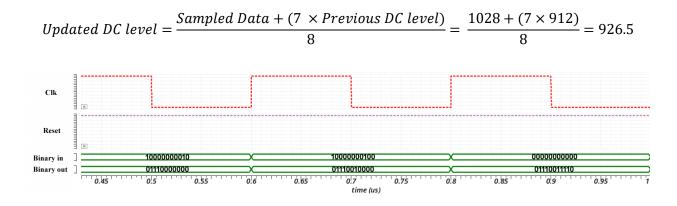

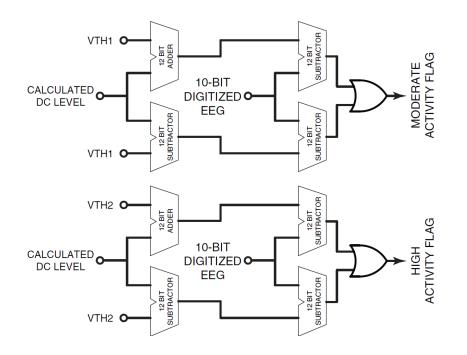

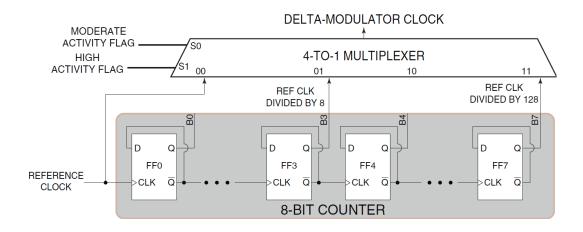

Since determining the level of EEG signal's activity is a major factor in the performance and efficacy of the proposed system, the activity-level evaluation criteria must be clearly defined. Based on the various EEG-based neurological event detection systems reported in the literature (e.g., [33] [34] [35]), it is commonly accepted that sudden bursts in LFP signals beyond the noise floor can be counted as events (in this text LFP "event" and LFP "activity" are used interchangeably). Accordingly, any period with no event is defined as idle period.