# ENERGY EFFICIENT ENCODING METHODS FOR CHIP-TO-CHIP COMMUNICATION

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF SCIENCE AND ENGINEERING

2022

Eleni Maragkoudaki

Department of Computer Science

# **Contents**

| List of Acronyms |        |                                             | 10 |

|------------------|--------|---------------------------------------------|----|

| Abstract         |        |                                             |    |

| D                | eclara | tion                                        | 16 |

| C                | opyrią | ght                                         | 17 |

| A                | cknov  | vledgements                                 | 18 |

| 1                | Intr   | oduction                                    | 19 |

|                  | 1.1    | Trends of Modern Integrated Circuits        | 19 |

|                  | 1.2    | Power Consumption of Data Communication     | 20 |

|                  | 1.3    | Contributions and Publications              | 23 |

|                  | 1.4    | Thesis Organisation                         | 25 |

| 2                | Pow    | er of Die-to-Die Communication              | 27 |

|                  | 2.1    | Low-Swing Signalling                        | 28 |

|                  | 2.2    | Increasing Physical Proximity               | 30 |

|                  |        | 2.2.1 Three-Dimensional Integration         | 30 |

|                  |        | 2.2.2 2.5-Dimensional Integration           | 31 |

|                  | 2.3    | Signal Encoding for Parallel Transmission   | 32 |

|                  |        | 2.3.1 Static Encoding Schemes               | 33 |

|                  |        | 2.3.2 Adaptive Encoding Schemes             | 35 |

|                  | 2.4    | Signal Encoding for Serial Transmission     | 53 |

|                  |        | 2.4.1 Source Synchronous Serial Interfaces  | 53 |

|                  |        | 2.4.2 Source Asynchronous Serial Interfaces | 55 |

|                  | 2.5    | Summary                                     | 58 |

| 3 | Low | -Swing   | Signalling for 2.5-D Technologies              | 59  |

|---|-----|----------|------------------------------------------------|-----|

|   | 3.1 | Interpo  | ser Technologies and Modeling                  | 60  |

|   | 3.2 | Simula   | tion Setup                                     | 63  |

|   |     | 3.2.1    | Low-Swing Transceiver                          | 63  |

|   |     | 3.2.2    | Test Circuit                                   | 64  |

|   | 3.3 | Energy   | Improvement and Limitations                    | 65  |

|   |     | 3.3.1    | Critical Length for Minimum Wire Pitch         | 66  |

|   |     | 3.3.2    | Energy Efficiency for Different Wire Densities | 68  |

|   | 3.4 | Summa    | ary                                            | 71  |

| 4 | Ada | ptive En | ncoding for Parallel Interfaces                | 73  |

|   | 4.1 | Encodi   | ng Algorithm                                   | 75  |

|   | 4.2 | Algorit  | thmic Performance Evaluation                   | 76  |

|   |     | 4.2.1    | State-of-the-Art Techniques                    | 77  |

|   |     | 4.2.2    | Savings in Switching Activity                  | 79  |

|   | 4.3 | Circuit  | Architecture                                   | 82  |

|   |     | 4.3.1    | Encoder                                        | 82  |

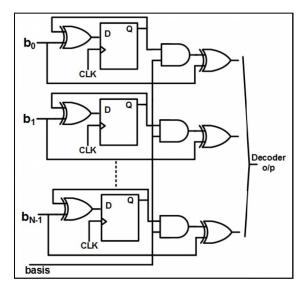

|   |     | 4.3.2    | Decoder                                        | 85  |

|   | 4.4 | Simula   | tion Setup                                     | 86  |

|   | 4.5 | Results  | 8                                              | 88  |

|   |     | 4.5.1    | Circuit Implementation and Overheads           | 88  |

|   |     | 4.5.2    | Power Savings of AWR                           | 92  |

|   |     | 4.5.3    | Comparison with State-of-the-art               | 94  |

|   |     | 4.5.4    | Resilience of AWR to process variations        | 98  |

|   | 4.6 | Summa    | ary                                            | 100 |

| 5 | Ada | ptive En | ncoding for Serial Interfaces                  | 102 |

|   | 5.1 | Encodi   | ng Algorithm                                   | 103 |

|   | 5.2 | Energy   | vs Reliability Trade-off                       | 105 |

|   | 5.3 | Circuit  | Architecture                                   | 107 |

|   |     | 5.3.1    | STTE Encoder                                   | 108 |

|   |     | 5.3.2    | STTE Decoder                                   | 111 |

|   | 5.4 | Energy   | r-efficiency Results                           | 112 |

|   |     | 5.4.1    | Evaluation Methodology                         | 112 |

|   |     | 5.4.2    | Power and Timing Overheads                     | 113 |

|   |     | 5.4.3    | Energy Savings                                 | 115 |

|    | 5.5    | Link Integrity Results                   | 117 |

|----|--------|------------------------------------------|-----|

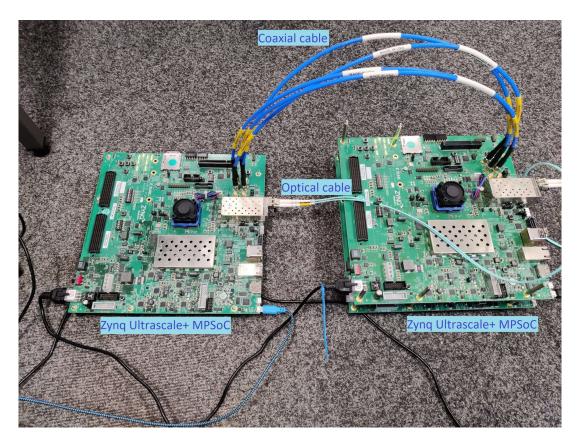

|    |        | 5.5.1 Experimental setup                 | 117 |

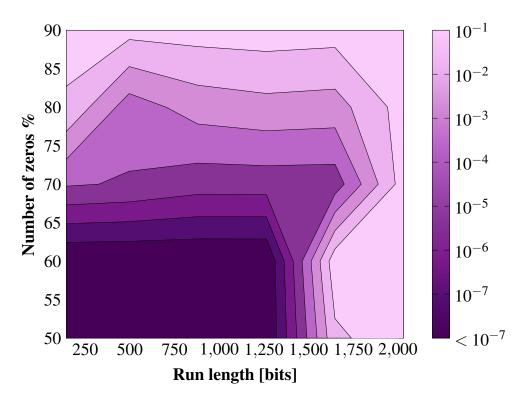

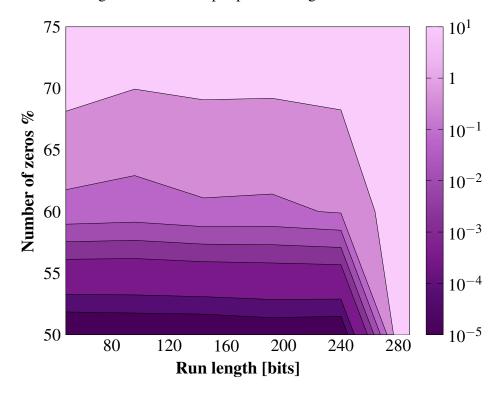

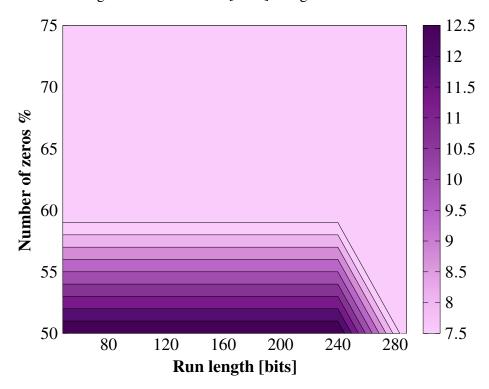

|    |        | 5.5.2 Link Integrity and Performance     | 119 |

|    | 5.6    | Summary                                  | 125 |

| 6  | Con    | clusions and Future Work                 | 128 |

|    | 6.1    | Summary                                  | 128 |

|    | 6.2    | Future Work                              | 132 |

| Bi | bliogr | aphy                                     | 134 |

| A  | Sim    | ulation of AWR and STTE Encoder Circuits | 146 |

|    | A.1    | Analog Simulation                        | 146 |

|    | A.2    | Mixed-Signal Simulation                  | 153 |

Word Count: 33456

# **List of Tables**

| 2.1 | Classification of adaptive encoding techniques for parallel intercon-           |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | nects based on their characteristics                                            | 36  |

| 2.2 | Characteristics of adaptive encoding techniques for parallel intercon-          |     |

|     | nects                                                                           | 52  |

| 3.1 | Interconnect parameters including the minimum width $(W)$ , space $(S)$ ,       |     |

|     | and thickness $(T_W)$ of the wires, the interlayer dielectric thickness $(T_D)$ |     |

|     | and dielectric constant of the passivation layer                                | 61  |

| 3.2 | <i>RLC</i> elements of microbumps and package                                   | 61  |

| 3.3 | Electrical characteristics of wires for minimum pitch                           | 63  |

| 3.4 | Critical length for different interposer technologies                           | 68  |

| 4.1 | Parameters of the investigated encoding techniques. The parameters              |     |

|     | are selected such that each technique yields the highest decrease in            |     |

|     | switching activity                                                              | 79  |

| 4.2 | Characteristics of data streams                                                 | 80  |

| 4.3 | Decrease in both self and relative switching activity for the different         |     |

|     | encoding schemes for diverse data streams                                       | 81  |

| 4.5 | Electrical characteristics of wires                                             | 88  |

| 4.6 | Power consumption of encoder and decoder circuits in mW                         | 89  |

| 4.7 | Timing overheads of encoding techniques. The critical path delay is             |     |

|     | listed in ns and the latency in clock cycles. The bus width is $M=64$           |     |

|     | bits unless stated otherwise and $N$ is the window size                         | 90  |

| 4.8 | Detailed analysis of power consumption using the LFRic and the Im-              |     |

|     | age benchmarks.                                                                 | 98  |

| 4.9 | Process corner analysis results using the LFRic benchmark                       | 99  |

| 5.1 | Power overhead in mW of the STTE encoder and decoder circuits op-               |     |

|     | erating at 250 MHz                                                              | 114 |

| 5.2 | Timing overheads of the STTE encoder and decoder circuits operating |     |

|-----|---------------------------------------------------------------------|-----|

|     | at 250 MHz                                                          | 114 |

| 5.3 | Percentage of 0's. DC balance is achieved for $\sim$ 50%            | 123 |

| 5.4 | Maximum run length in bits                                          | 123 |

| 5.5 | Errors per packet using a coaxial cable                             | 124 |

| 5.6 | Link data rate in Gb/s using a coaxial cable                        | 125 |

| 5.7 | Errors per packet using an optical cable                            | 125 |

| 5.8 | Link data rate in Gb/s using an optical cable                       | 126 |

# **List of Figures**

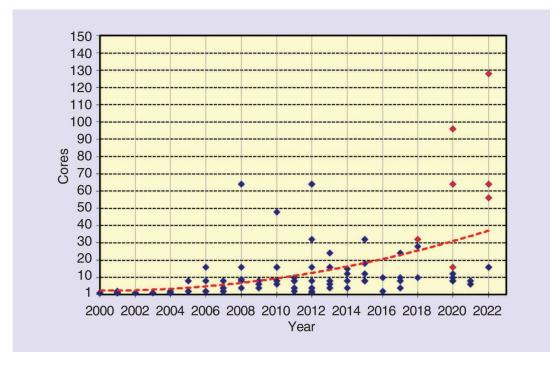

| 1.1                                                                  | Number of cores over the years. The red diamonds denote multichip           |    |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|----|

|                                                                      | modules [2]                                                                 | 20 |

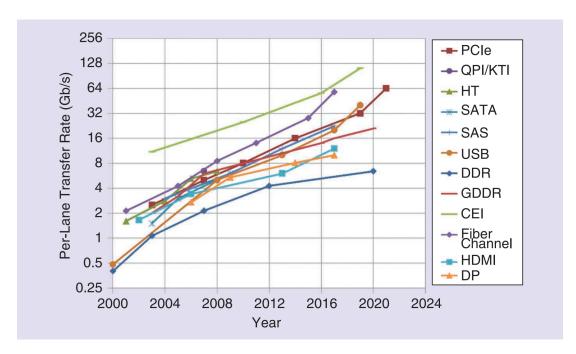

| 1.2                                                                  | Data rate per lane of various I/O standards over the years [2]              | 21 |

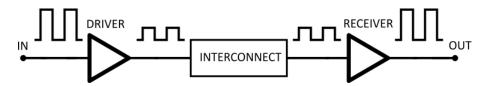

| 2.1                                                                  | Low-swing signalling implementation                                         | 29 |

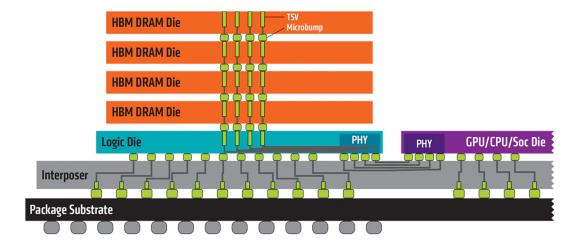

| 2.2                                                                  | Schematic of AMD's High Bandwidth Memory [11]                               | 31 |

| 2.3                                                                  | Basic structural diagram for signal encoding                                | 33 |

| 2.4                                                                  | Circuit implementation of the BI encoder [46]                               | 37 |

| 2.5                                                                  | Circuit diagram of the APBI technique [60]                                  | 39 |

| 2.6                                                                  | Circuit diagram of the Mask Computation block [60]                          | 40 |

| 2.7                                                                  | Redundancy added by the ABE technique [72]                                  | 43 |

| 2.8                                                                  | Block diagram of the ABE encoder [72]                                       | 43 |

| 2.9                                                                  | Block diagram of the decision block of the ABE encoder [72]                 | 44 |

| 2.10                                                                 | Circuit diagram of the the ABE decoder [72]                                 | 44 |

| 2.11                                                                 | Simplified bus model [77]                                                   | 50 |

| 2.12                                                                 | Pseudo Open Drain interface [85]                                            | 51 |

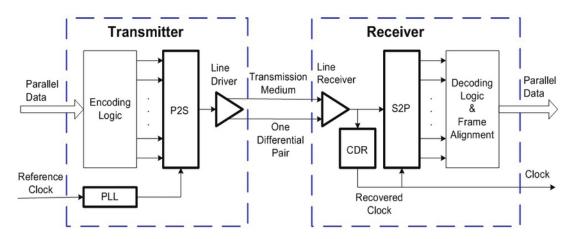

| 2.13                                                                 | A generic architecture of SerDes devices [112]                              | 56 |

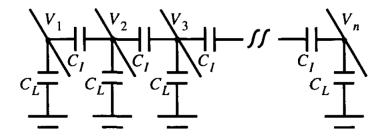

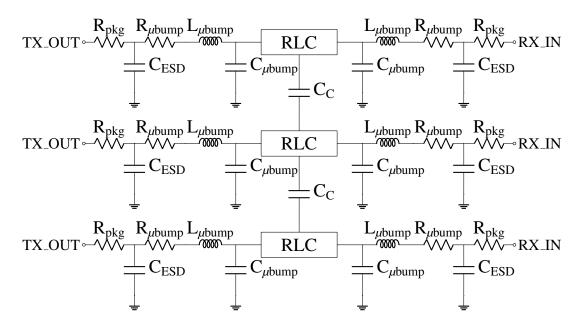

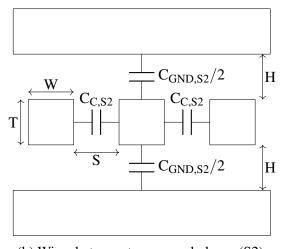

| 3.1                                                                  | Electrical model of three interconnect lines for an interposer technology.  | 61 |

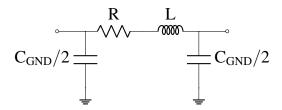

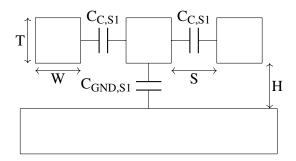

| 3.2                                                                  | A $\pi$ -type segment                                                       | 62 |

| 3.3                                                                  | Cross-sectional view of typical interconnect structures, where (a) one      |    |

|                                                                      | ground plane is present and (b) interconnects are flanked by two ground     |    |

|                                                                      | planes                                                                      | 62 |

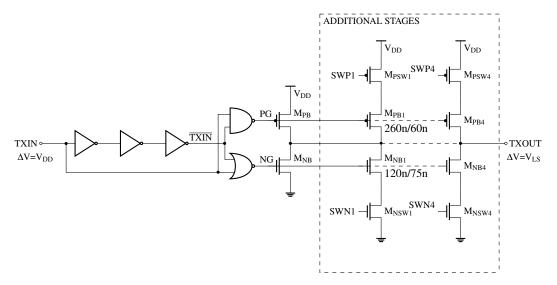

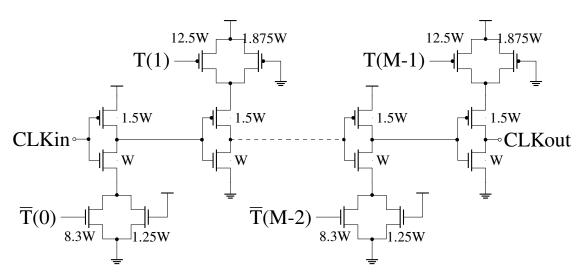

| 3.4                                                                  | Transmitter schematic diagram                                               | 64 |

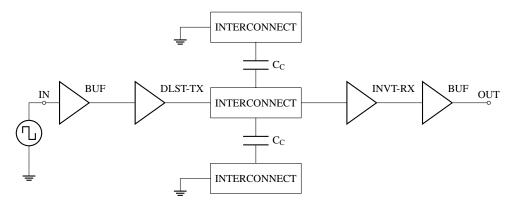

| 3.5                                                                  | Transceiver test circuit                                                    | 65 |

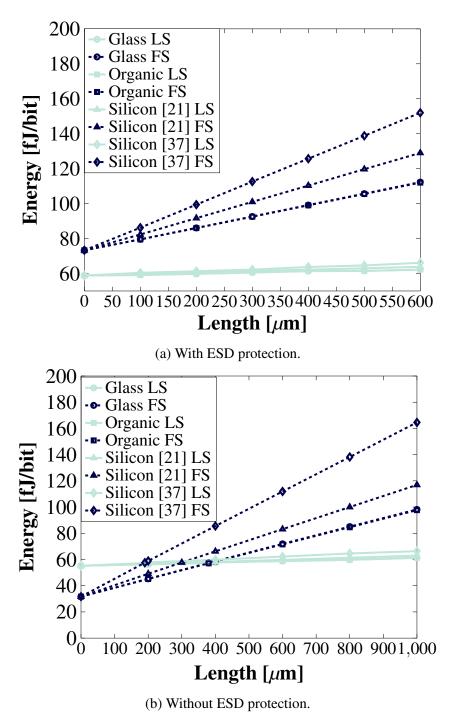

| 3.6 Energy vs interconnect length for different interposer technolog |                                                                             |    |

|                                                                      | where (a) the ESD capacitance is $C_{ESD} = 50$ fF and (b) the $C_{ESD}$ is |    |

|                                                                      | not considered                                                              | 67 |

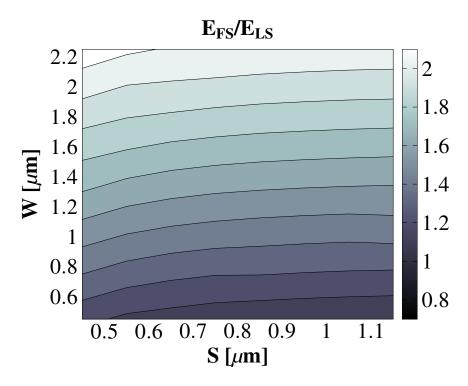

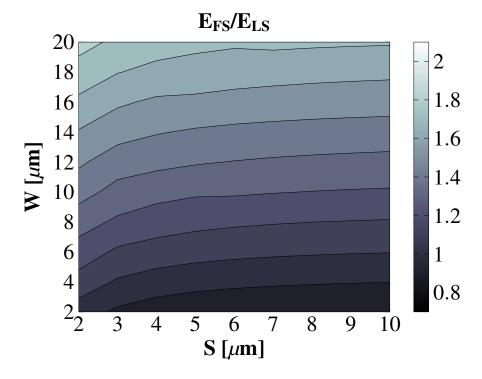

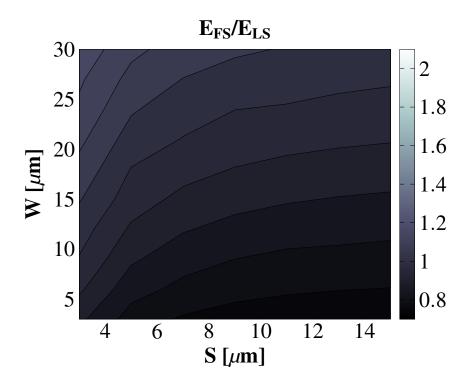

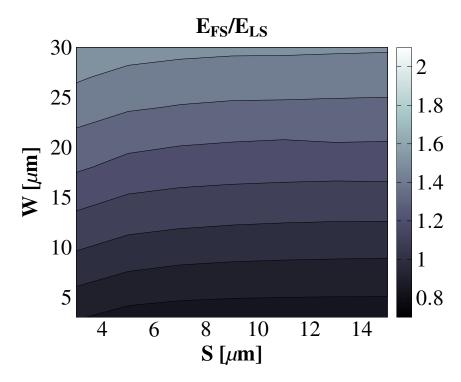

| 3.7  | Energy efficiency for the silicon interposer with wire parameters de-      |     |

|------|----------------------------------------------------------------------------|-----|

|      | scribed in [37]                                                            | 69  |

| 3.8  | Energy efficiency for the silicon interposer described in [21]             | 69  |

| 3.9  | Energy efficiency for the glass interposer                                 | 70  |

| 3.10 | Energy efficiency for the organic interposer                               | 70  |

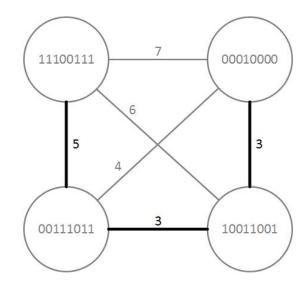

| 4.1  | Examples of routes that reduce bit transitions                             | 77  |

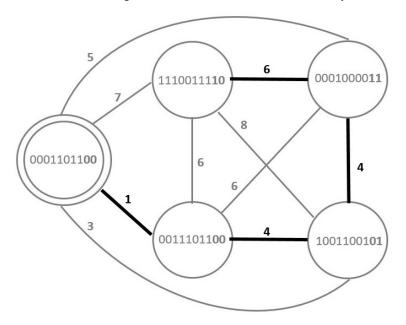

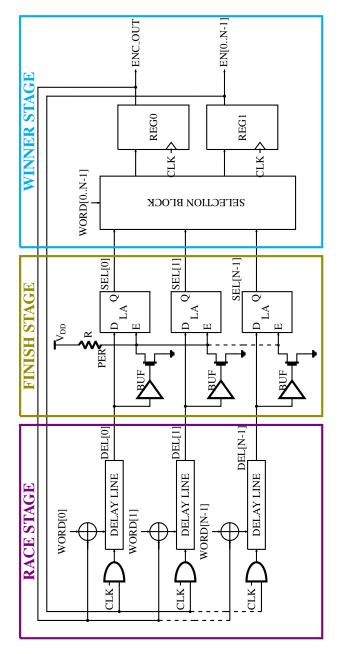

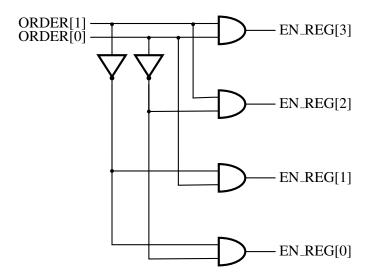

| 4.2  | Encoder circuit                                                            | 83  |

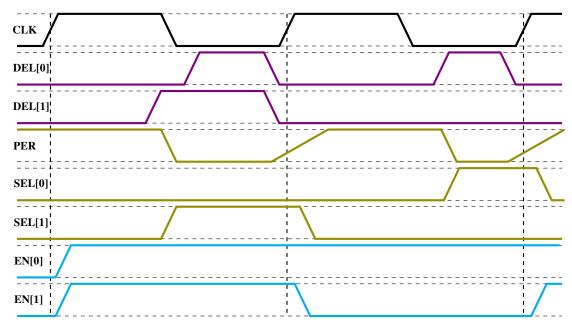

| 4.3  | Timing diagram of the encoder circuit                                      | 85  |

| 4.4  | Delay line circuit                                                         | 85  |

| 4.5  | Decoder circuit                                                            | 86  |

| 4.6  | Electrical model for an interposer-based interconnect                      | 87  |

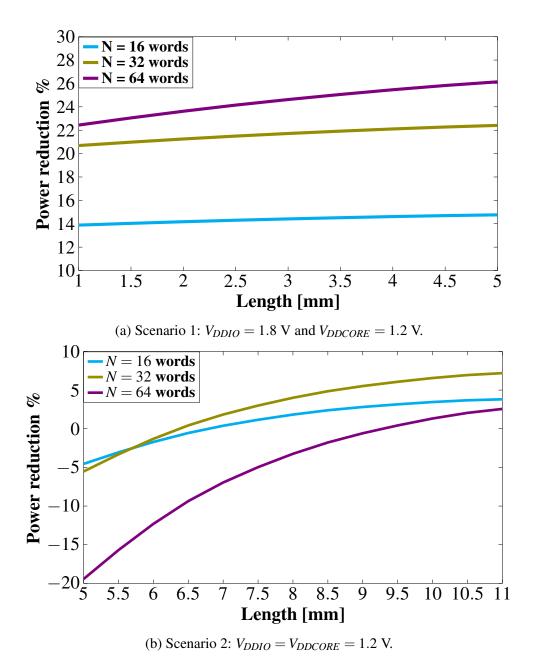

| 4.7  | Decrease in power for $M = 64$ bits and different number of reordered      |     |

|      | words, $N$                                                                 | 94  |

| 4.8  | Decrease in power for fixed number of reordered words $N=32$ and           |     |

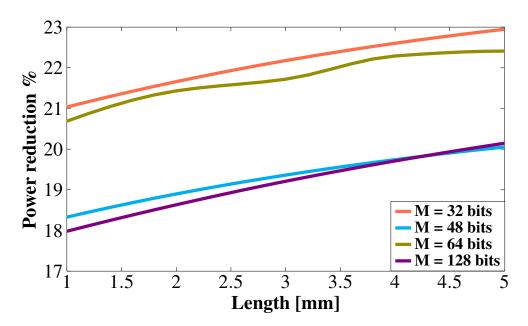

|      | different bus widths $M.~V_{DDIO}=1.8~V$ , and $V_{DDCORE}=1.2~V$          | 95  |

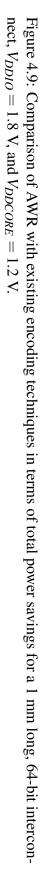

| 4.9  | Comparison of AWR with existing encoding techniques in terms of            |     |

|      | total power savings for a 1 mm long, 64-bit interconnect, $V_{DDIO} = 1.8$ |     |

|      | V, and $V_{DDCORE} = 1.2 \text{ V}. \dots$                                 | 96  |

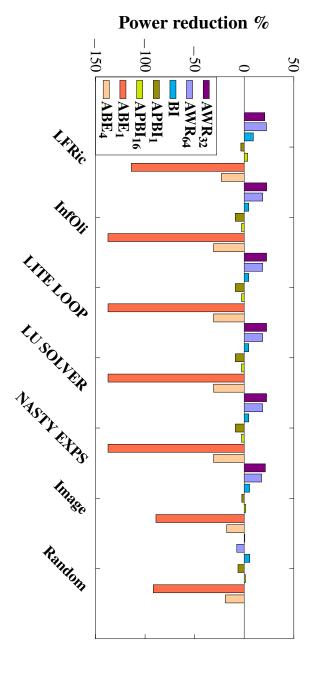

| 5.1  | Reduction in the number of transitions compared to a scrambled data        |     |

|      | stream as a function of the step size $S$                                  | 106 |

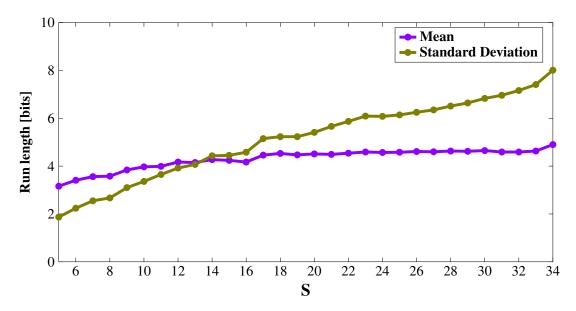

| 5.2  | The mean run length (i.e. number of consecutive bits without a transi-     |     |

|      | tion) and the standard deviation in relation to the step size $S$          | 107 |

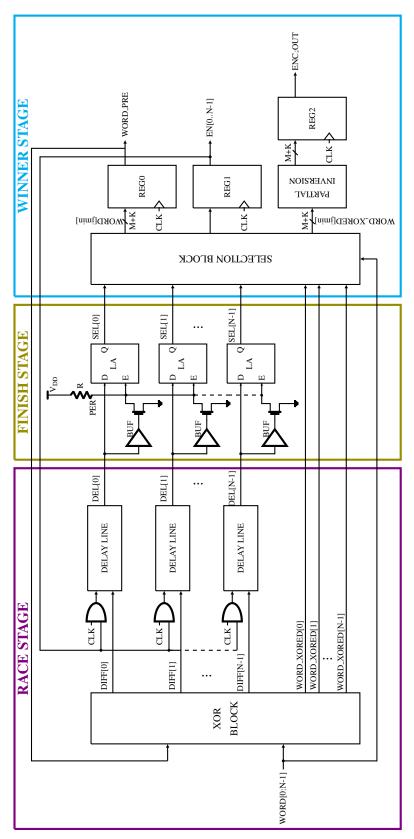

| 5.3  | Encoder circuit of STTE                                                    | 109 |

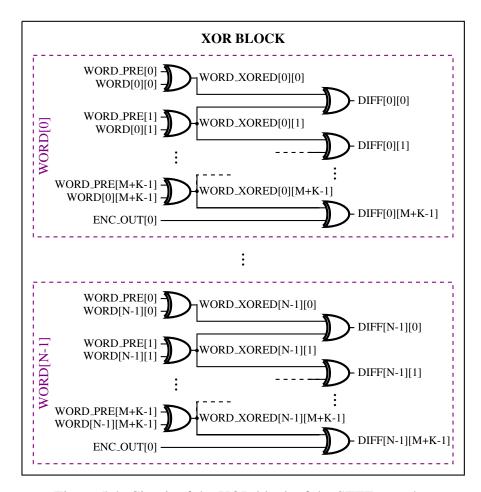

| 5.4  | Circuit of the XOR block of the STTE encoder                               | 110 |

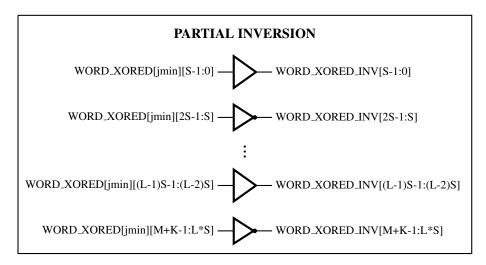

| 5.5  | Circuit of the Partial Inversion block of the STTE technique               | 111 |

| 5.6  | Circuit of the STTE decoder                                                | 112 |

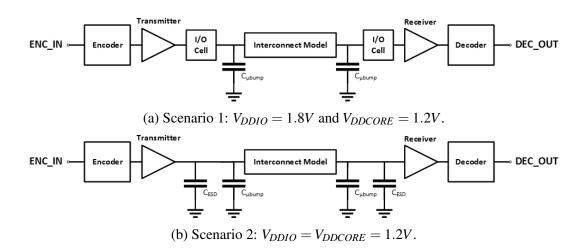

| 5.7  | Test circuit of an interposer-based interconnect                           | 113 |

| 5.8  | Energy savings for $N = 16$ reordered data words                           | 116 |

| 5.9  | Energy savings for $N = 32$ reordered data words                           | 116 |

| 5.10 | Experimental setup                                                         | 118 |

| 5.11 | Errors per packet using a coaxial cable                                    | 120 |

| 5.12 | Errors per packet using an optical cable                                   | 120 |

| 5.13 | Data rate [Gb/s] using a coaxial cable                                     | 122 |

| 5.14 | Data rate [Gb/s] using an optical cable.                                   | 122 |

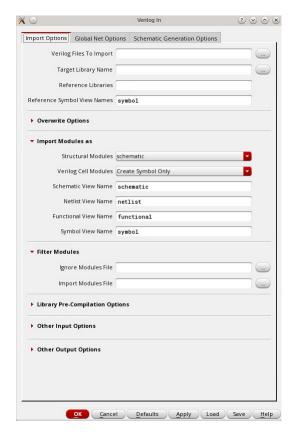

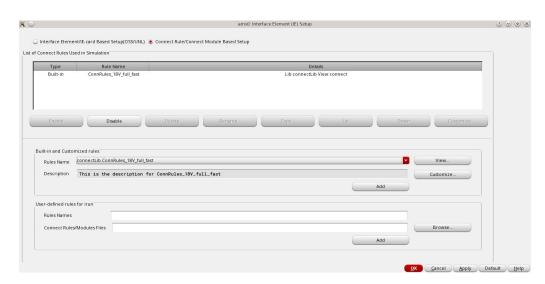

| <b>A.</b> 1 | Verilog In form.                                   | 149 |

|-------------|----------------------------------------------------|-----|

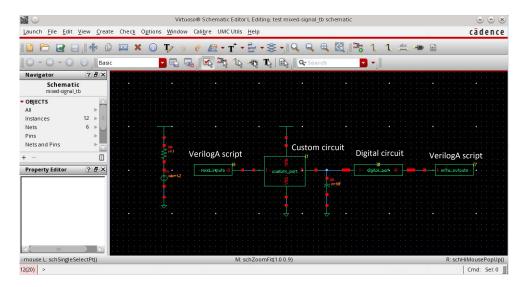

| A.2         | Schematic view of the mixed-signal test circuit    | 155 |

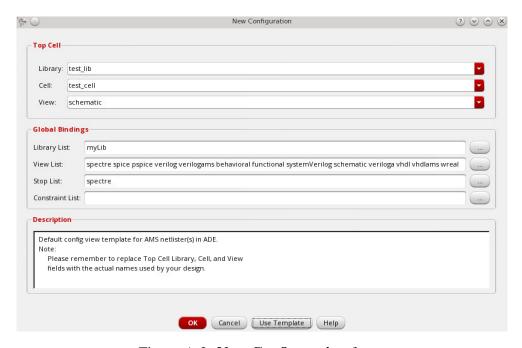

| A.3         | New Configuration form                             | 156 |

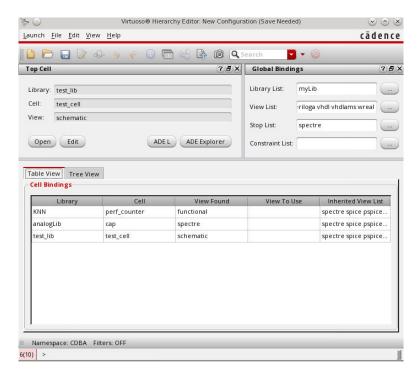

| A.4         | Virtuoso® Hierarchy Editor: New Configuration form | 157 |

| A.5         | Selecting connect rules                            | 158 |

| A.6         | Customising the supply voltage of connect rules    | 158 |

# **List of Acronyms**

**3-D** Three-Dimensional

2.5-D 2.5-Dimensional

I/O Input/Output

**ICs** Integrated Circuits

ICT Information and Communication Technologies

**PCIe** Peripheral Component Interconnect Express

VLSI Very Large Scale Integration

**EM** Electromagnetic

**FPGA** Field Programmable Gate Array

**SNR** Signal to Noise Ratio

**EMI** Electromagnetic Interference

TSVs Through Silicon Vias

**HBM** High Bandwidth Memory

**DRAM** Dynamic Random Access Memory

V-NAND Vertical-NAND

**CAD** Computer Aided Design

**GPU** Graphic Processing Unit

**RDLs** Redistribution Layers

**BEOL** Back-End-of-Line

EMIB Embedded Multidie Interconnect Bridge

**ISI** Intersymbol Interference

**BI** Bus Invert

**DDR4** Double-Data-Rate fourth generation

**PBI** Partial Bus Invert

**APBI** Adaptive Partial Bus Invert

TTA Total Transition Accumulator

WC Window Counter

MUC Mask Update Counter

**SINV** Shift Invert

BS Bus Shifting

**ABE** Adaptive Bus Encoding

FV Frequent Value

**CAM** Content Addressable Memory

**ADES** Adaptive Dictionary Encoding Scheme

**MSBs** Most Significant Bits

MTF Move-To-Front

**DESC** Data Exchange using Synchronized Counters

ATE Adaptive Time-based Encoding

**STFL** Slow Transition Fast Level

**BEAM** Bus Encoding based on instruction-set-Aware Memories

POD Pseudo Open Drain

**GDDR5** Graphics Double Data Rate 5

**DBI** Data Bus Inversion

MiL More is Less

**BD** Bitwise-Difference

**CAFO** Cost-Aware Flip Optimization

**PCM** Phase Change Memory

STT-RAM Spin-Transfer Torque Random Access Memory

**I**<sup>2</sup>**C** Ifrijf

SPI Serial Peripheral Interface

**SILENT** Serialized Low-Energy Transmission

**TIC** Transition Inversion Coding

ADE Approximate Differential Encoding

LSBs Least Significant Bits

VDBS Value-Deviation-Bounded Serial

**AXSERBUS** Approximate Serial Bus

**SerDes** Serialiser/Deserialiser

**USB** Universal Serial Bus

CDR Clock Data Recovery

PRBS Pseudorandom Bit Sequence

LFSR Linear Feedback Shift Register

PCB Printed Circuit Board

**TPV** Through Package Via

ESD Electrostatic Discharge

ABF Ajinomoto Build-up Film

**DLST-TX** Dynamic Low Swing Tunable Transmitter

**IVT-RX** Inverter-based Tunable Receiver

LS Low Swing

FS Full Swing

AWR Adaptive Word Reordering

NN Nearest Neighbour

**DMA** Direct Memory Access

**LPDDR3** Low-Power Double Data Rate 3

**TSP** Travelling Salesman Problem

TT Typical/Typical

**STTE** Serial Tuned Transition Encoding

CRC Cyclic Redundancy Check

MPSoC Multiprocessor System on Chip

SS Spiral Strip

**PHY** Physical Layer

**HDL** Hardware Description Language

SAIF Switching Activity Interchange Format

**CPUs** Central Processing Units

LLC Last Level Cache

Advanced eXtensible Interface AXI

## **Abstract**

# ENERGY EFFICIENT ENCODING METHODS FOR CHIP-TO-CHIP COMMUNICATION Eleni Maragkoudaki A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy, 2022

As traditional scaling slows down, the number of cores and the amount of memory per system increase to satisfy the performance demand. This drive for more parallelism increases data movement requirements rapidly. However, as technology scales the energy dissipated in data communication scales at a much slower pace compared to computation energy. Therefore, new methods to reduce the energy of data transmission are explored in this thesis.

Three different techniques that decrease the dynamic power of interconnects are discussed: low-swing signalling, 3-D and 2.5-D integration technologies that reduce the interconnect length, and signal encoding. An investigation of the energy benefits and limitations of low-swing signalling when applied to interposer technologies is provided, where different interposer materials are considered. Although the potential energy savings are high, low-swing signalling is susceptible to noise or induces high area penalty. Therefore, this thesis focuses on signal encoding, which reduces the bit transitions of the transmitted data to save power.

Two encoding schemes are proposed, named Adaptive Word Reordering (AWR) and Serial Tuned Transition Encoding (STTE), for parallel and serial interfaces, respectively. AWR achieves a high decrease in transitions and a novel custom circuit implementation is provided to constrain the overhead in power. The power savings of AWR reach up to 23% for a 1 mm interposer-based interconnect without affecting the communication bandwidth. Alternatively, STTE is designed for source asynchronous

serial interfaces, where the receiver recovers the clock from the incoming data. STTE regulates the number of transitions such that the clock can be reliably recovered while the communication energy is lowered. STTE provides at least 25% decrease in energy for a 1 mm interposer-based interconnect compared to scrambling, which is typically used in these interfaces. The ability to maintain clock recovery and, thus, link integrity is evaluated experimentally using both an electrical and an optical link that interconnect two FPGA devices.

# **Declaration**

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?

DocID=24420), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.library.manchester.ac.uk/about/regulations/) and in The University's policy on presentation of Theses

## Acknowledgements

First and foremost, I would like to thank my main supervisor Dr. Vasilis F. Pavlidis for his guidance throughout my PhD. He consistently provided advice and motivated me to develop and research my own ideas. His constructive criticism, his experience in research, and his knowledge on integrated circuits helped me become a better researcher.

A big thank you to Przemyslaw Mroszcz and Nguyen Dao for the technical support at different stages of my PhD. Their technical advice truly helped me overcome many challenges. I would also like to thank Will Toms for the fruitful discussions and collaboration.

Furthermore, I am thankful to Dr. Jim Garside, Dr. Dirk Koch, and my cosupervisor Dr. Christoforos Moutafis for their valuable advice and discussions about my research at the first and second year examinations as well as throughout my PhD. I would also like to thank all my colleagues from the APT group and especially Minmin Jiang for creating a pleasant and productive working environment. I am grateful to the European Commission and Pr. Mikel Luján for providing the funding for my research through the EuroEXA project.

Additionally, I would like to express my gratitude to my friends Danae, Rigina, Katerina, Eleni, Christos, Mary, Markos, Ioanna, and Thanos for their support and understanding and for making this journey enjoyable. I am also thankful to Joe for his support during the writing of this thesis.

Last but not least, I am deeply grateful to my family for supporting me and especially my mother, Popi, for believing in me and inspiring me to forge my own path. I dedicate this thesis to her.

# Chapter 1

## Introduction

### 1.1 Trends of Modern Integrated Circuits

Traditional transistor scaling has been slowing down due to manufacturing challenges including process variations, mask cost, and difficulty in shrinking the gate length [1]. Alternative routes are explored by the semiconductor industry to satisfy the emerging performance demand of data-intensive applications, such as machine learning. The clock frequency has plateaued and replaced by increasing the number of processing cores per system as well as memory to provide the required performance [2].

The integration of multiple dies in a single package has also facilitated the increase in core count and functional density as depicted in Figure 1.1. Advanced packaging technologies, such as wire bonding, three-dimensional (3-D) and 2.5-dimensional (2.5-D) integration, are utilised to interconnect multiple dies in close physical proximity, thus, reducing form factor [6]. This increase in processing cores and memory and the drive for more parallelism has led to an increasing demand of data movement and communication bandwidth.

Data bandwidth has been increasing rapidly in various systems from smartphones to supercomputers. This trend is illustrated in Figure 1.2, where the data rate per lane of a wide range of input/output (I/O) standards is depicted for the past 22 years. This exponential growth in data bandwidth poses significant challenges in terms of signal integrity and especially power consumption.

Constraining the energy demand of Integrated Circuits (ICs) is more important than ever. The Information and Communication Technologies (ICT) sector is responsible for a large part of the global electricity demand. Around 2% of the global carbon emissions is attributed to the ICT sector [3]. Due to the widespread use of ICs, from

Figure 1.1: Number of cores over the years. The red diamonds denote multichip modules [2].

personal digital devices and sensors to data centers, low-power circuit design has to become even more sophisticated to support sustainability. Low-power circuit design is, also, essential for battery-operated devices, such as smartphones. These devices require significant performance and high communication bandwidth. Hence, increasing energy efficiency is required to extend battery longevity.

## 1.2 Power Consumption of Data Communication

A large part of the energy of ICs is dissipated in data communication. The energy dissipated in data transmission is estimated between 18% and 40% of the total system energy for scientific applications and could further increase in upcoming exascale systems [43]. Alternatively, in smartphone devices, the energy spent on moving data across the memory hierarchy is 34.6%, on average, and reaches 41% for realistic web browsing [45]. Consequently, data transmission becomes the bottleneck in satisfying power constraints of ICs.

An imbalance between computation and communication energy has emerged with

Figure 1.2: Data rate per lane of various I/O standards over the years [2].

technology scaling. The energy of data movement scales at a much slower pace compared to computation energy [44], [42]. For instance, the energy of a load instruction that requires transmitting data off-chip is estimated 115× higher than the energy of an add operation in smartphone devices [45]. The reason is that wires and I/O pins scale gradually, therefore, interconnect capacitance scales at a slower pace compared to gate capacitance [4]. Thus, a larger amount of power is dissipated for charging and discharging interconnect capacitance. Hence, due to the increasing demand of communication bandwidth as shown in Fig. 1.2, the power of inter-die communication becomes a key challenge of modern ICs.

The static power of ICs becomes more prominent with technology scaling as the gate capacitance decreases. However, the interconnect capacitance does not scale as much [4], therefore, the dynamic power dissipated in charging and discharging the interconnect capacitance is a major contributor of the total power consumption. Hence, in this thesis, the reduction of the dynamic power consumption of off-die communication is explored. Nevertheless, the developed low-power techniques are evaluated in terms of the total power as results include both static and dynamic power throughout the thesis.

Different techniques that decrease power are discussed: low voltage swing transmission, advanced packaging technologies, and signal encoding methods. Low-swing

signalling reduces the voltage range of transmitted signals. Although the potential power improvement is significantly high (4× decrease in power over full swing communication [30]), low-swing signalling is susceptible to noise or induces high area overhead, such as double number of I/O pins and wires [25]. 3-D and 2.5-D are advanced integration technologies that support the integration of multiple dice and decrease form factor [6]. These technologies effectively reduce the interconnect length and, thus, capacitance, however, introduce manufacturing challenges or suffer from high cost.

Alternatively, signal encoding methods decrease the switching activity, *i.e.* bit transitions, of the transmitted signals [5]. Therefore, the frequency of charging and discharging the interconnect load is reduced and, thus, power is saved. An encoder and a decoder logic is added to the transmitter and the receiver, respectively, to reduce bit transitions and retrieve the original data. In this way, a low amount of on-chip computation power is exchanged for a decrease in I/O power. With technology scaling, the effectiveness of signal encoding is expected to increase, as I/O power scales disproportionately to computing power. Hence, the impact of the overhead due to encoding and decoding decreases for smaller process nodes.

The focus of this thesis is particularly on signal encoding. This work is of interest to digital and mixed-signal IC designers of data encodings for off-die communication. Two types of data transmission are targeted. The first type is wide parallel links implemented on advanced packaging technologies that support high wire density, such as interposers and Embedded Multidie Interconnect Bridge (EMIB) [96]–[97]. The second type of communication is high-speed, source asynchronous, Serialiser/Deserialiser (SerDes) interfaces. An encoding technique is proposed that can be integrated in the physical layer of a SerDes protocol, where voltage-mode drivers are utilised with one-to-one mapping between digital signals and transmitted symbols, such as Stub Series Terminated Logic (SSTL) [116].

Encoding schemes tailored to parallel buses reduce bit transitions between consecutive data words. A variety of encoding schemes have been proposed for parallel interconnects [46], [48], [51]-[81], [85]-[91]. The majority of the techniques exploit specific characteristics of the data stream to reduce transitions, such as data locality or the sequential nature of instruction addresses. These techniques are effective only for specific applications. On the contrary, general purpose encoding schemes either provide a moderate reduction in bit transitions or exhibit substantial encoding/decoding overhead. Thus, the latter allow savings only for long interconnects with large loads.

In serial communication, the target of encoding schemes is the decrease of transitions within data words. Existing low-power encoding techniques [104]-[110] are only suitable for source synchronous interconnects, despite the omnipresence of high-speed, source asynchronous serial interfaces, such as Ethernet and Peripheral Component Interconnect Express (PCIe) [111]. In source asynchronous interfaces, the receiver extracts the clock signal from the incoming data stream, instead of relying on an external clock signal. Consequently, the transmitted data must exhibit frequent bit transitions to facilitate clock recovery [101], [111]. Therefore, the minimisation of bit transitions in this type of interconnects obstructs clock recovery and degrades link integrity.

#### 1.3 Contributions and Publications

A large part of the material in this thesis has been published. The contributions and publications are the following:

- E. Maragkoudaki, P. Mroszczyk, and V. F. Pavlidis, "Energy Efficiency of Low Swing Signaling for Emerging Interposer Technologies," Proceedings of the IEEE/ACM Conference on Nanoscale Architectures, pp. 124–130, July 2018. The effectiveness of low-swing signalling on 2.5-D integration scenarios is investigated. The energy consumed by a low swing scheme is, therefore, compared with a full swing solution. An electrical model of an interposer-based interconnect is developed to quantify the energy improvement as well as the limitations of low-swing signalling. Specifically, the critical length of the interconnect, above which the low swing solution starts to pay off is determined. Three different interposer materials are investigated: silicon, glass, and organic. The low swing solution provides higher energy savings and achieves the shortest critical length for silicon interposers, which have the highest wire capacitance. Furthermore, the effect of typical interconnect parameters such as width and spacing on the energy efficiency of low swing communication is, also, evaluated. In this way, useful rules of thumb are provided regarding the use of low swing communication mechanisms for 2.5-D integrated systems.

- E. Maragkoudaki, P. Mroszczyk, and V. F. Pavlidis, "Adaptive Word Reordering for Low-Power Inter-Chip Communication," *Proceedings of the Conference on Design, Automation and Test in Europe*, pp. 980–983, March 2019.

A general purpose encoding technique named Adaptive Word Reordering is proposed to reduce the power consumption of parallel interfaces by changing the order of data. This new scheme reduces bit transitions up to 48% for diverse data types without affecting the communication throughput. A novel encoder circuit is proposed, which exploits the time domain for complex computations of Hamming distances, to decrease the power overhead of encoding. AWR achieves significant power savings, up to  $\sim 23\%$  for 1 mm interposer-based interconnects. The proposed scheme outperforms state-of-the-art encoding techniques in terms of reduction in transitions.

- E. Maragkoudaki and V. F. Pavlidis, "Energy-Efficient Time-Based Adaptive Encoding for Off-Chip Communication," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 28, No. 12, pp. 2551–2562, Dec. 2020.

In this publication, the effectiveness and limitations of the proposed encoding technique are further investigated. A comparison with state-of-the-art techniques in terms of savings in power as well as delay and latency overheads for diverse benchmark applications is provided. The power of the encoding and decoding circuits for each technique is also included, thus, an accurate estimation of the efficiency of each technique is provided. Furthermore, the power benefits of using the time domain for the complex computations are quantified. Additionally, the resilience of the proposed encoder and decoder circuits under process variations is explored. The trade-offs between accuracy, power, and timing are discussed.

- M. Jiang, E. Maragkoudaki, and V. F. Pavlidis, "Mitigating EM Side-Channel Attacks with Dynamic Delay Insertion and Data Bus Inversion," *Proceedings of the IEEE International Symposium on Circuits and Systems*, May 2022.

In this work, a technique is proposed to mitigate security vulnerabilities in cryptographic circuits. These circuits are susceptible to electromagnetic (EM) sidechannel attacks, which detect EM emissions to extract sensitive data. The proposed technique reduces the correlation between processed data and electromagnetic emissions by dynamically inserting a short delay (up to 110 ps) to signals based on the Hamming Distance of consecutive data. My contribution to this work is the implementation of the circuit of the proposed dynamic delay insertion scheme. This work is not presented in the thesis as the scope is beyond my PhD.

- E. Maragkoudaki, W. Toms, and V. F. Pavlidis, "Energy-Efficient Encoding for

25

High-Speed Serial Interfaces," *IEEE Transactions on Very Large Scale Integra*tion (VLSI) Systems, Submitted.

An encoding technique for high-speed, source asynchronous serial interfaces is proposed that reduces energy while maintains link integrity. Typically in these interfaces, techniques that insert bit transitions, such as scrambling, are employed to facilitate clock recovery. On the contrary, this scheme regulates the frequency of transitions such that the receiver can recover the clock from the transmitted data, while the number of transitions is reduced compared to scrambling and, hence, energy is saved. The proposed technique is investigated in terms of both energy-efficiency as well as maintaining link integrity to avoid data errors. The energy savings are estimated for a 1 mm interposer-based interconnect, whilst the link integrity is experimentally evaluated using both an electrical and an optical link that interconnect two Field Programmable Gate Array (FPGA) boards.

## 1.4 Thesis Organisation

The rest of this thesis is organised as follows. In Chapter 2, the techniques for decreasing the dynamic power consumption of off-die interconnects are presented. Particularly, three methods are discussed, low-swing signalling, 3-D and 2.5-D integration that reduce the length of off-die links, and signal encoding. The latter is the main focus of this thesis, therefore, a review of existing encoding methods for both parallel and serial links is provided. Techniques for parallel buses are classified to static and adaptive, while serial interfaces are divided into source synchronous and asynchronous and encoding schemes for both categories are reviewed. The strengths and limitations of all techniques are highlighted.

In Chapter 3, the energy improvement and limitations of low-swing signalling are investigated for interposer-based interconnects. The energy efficiency of a low-swing scheme is estimated for different interposer materials, interconnect lengths, and wire densities.

A general purpose encoding scheme for parallel interfaces is proposed in Chapter 4 that reduces bit transitions for diverse data types. The circuit implementations of the encoder and the decoder are presented. The effectiveness of the technique is investigated in terms of power for an interposed-based link where the power overhead of encoding and decoding is also considered. The limitations and timing overheads of

this technique are discussed.

Existing low-power encoding techniques for serial interconnects are only applicable to source synchronous interfaces. Therefore, an encoding technique for source asynchronous serial links is presented in Chapter 5. The energy savings are estimated for an interposer-based interconnect, while the link integrity is experimentally evaluated for both an electrical and an optical interconnect. The trade-offs between energy, link integrity, and throughput are discussed.

A summary of the thesis is provided in Chapter 6 and conclusions are drawn. Directions for future research topics are also presented.

## Chapter 2

## **Power of Die-to-Die Communication**

As technology scales, data movement becomes increasingly the bottleneck in satisfying the power constraints of modern processors. The ever growing compute density, enabled by parallelism, in combination with the non-decreasing system size has led to an excessive demand for data movement through long interconnects [42]. The energy cost for transferring data across the memory hierarchy is estimated between 18% and 40% of the total system energy for scientific applications and is expected to further increase in upcoming exascale systems [43]. In addition, the energy of transferring data does not scale as fast as the energy for computation [44]. For instance, the energy consumed for off-chip communication is estimated 115× higher than that of an add operation in smart phone devices [45]. Thus, the power reduction of inter-die communication is a key challenge for modern integrated systems.

The static power of ICs becomes more significant compared to dynamic power as technology scales since the capacitive load of gates shrinks. However, this trend does not apply to communication power. The reason is that wires and, thus, the interconnect capacitance do not scale as fast [4]. Consequently, to increase the energy efficiency of off-die communication, the dynamic power consumption has to be restricted, which is given by:

$$P = aC_L V_{DD}^2 f, (2.1)$$

where a is the average switching activity,  $C_L$  is the load capacitance,  $V_{DD}$  is the supply voltage, and f is the operating frequency. Hence, the decrease of any of these factors is required to limit the dynamic power consumption.

There is a plethora of techniques for reducing the power demand of off-die communication, such as data-centric architectures that reduce the number of memory accesses and data movement, reduction of the voltage level, packaging technologies that

decrease the distance between dies, and signal encoding schemes that decrease the switching activity factor. In this thesis, the focus is on the reduction of the energy cost of data transfers, therefore, techniques that decrease the factors of Equation 2.1 are discussed in this chapter.

One way to reduce the dynamic power dissipation is to decrease frequency by employing frequency throttling. This technique is useful to restrict power to control temperature and prevent overheating. However, this method is not effective in decreasing the energy demand [42]. Therefore, this mechanism is not investigated in this work.

Techniques that target the rest of the parameters are discussed in the following sections. Particularly, low-swing signalling schemes that reduce the voltage range of the signals transmitted over the wires are described in Section 2.1. In Section 2.2, emerging packaging technologies are presented that contribute in increasing the physical proximity of dies and, thus, reducing the capacitive load of the wirelines. The benefits as well as the limitations of low-swing signalling and packaging technologies are highlighted.

Another category of power reduction techniques, called signal encoding, decrease the average switching activity of the transmitted data. Low-power signal encoding is the main focus of this thesis, which can be categorised to encoding for parallel and serial interfaces. The characteristics of the two types of interfaces are described and a thorough review of the state-of-the-art encoding techniques is provided in Sections 2.3 and 2.4 for parallel and serial communication, respectively.

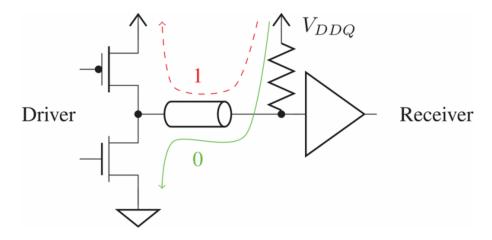

## 2.1 Low-Swing Signalling

Power exhibits a quadratic relationship with voltage, thus, one of the most effective ways to reduce the dynamic power consumption of signal transmission is to decrease the voltage range. The implementation of low-swing signalling is illustrated in Fig. 2.1. The driver converts the signal from full-swing to low-swing. The signal is transferred over the interconnect in a lower voltage range, while the receiver at the other end of the link fully restores the voltage swing.

A number of low-swing schemes have been proposed in the literature. The majority of these schemes rely on additional power supply or reference voltage and multiple threshold voltage devices for the voltage level conversion [25], [26]. Although the dual power rail schemes exhibit high signal to noise ratio (SNR), they suffer from high area and delay penalties [26]. Furthermore, the complexity of the physical design

Figure 2.1: Low-swing signalling implementation.

is increased by the additional power supply and the technology node portability is confined due to the requirement of multi-threshold devices [28].

Alternatively, single supply, low-swing schemes address the drawbacks of the dual power rail. A set of single supply techniques exploit the threshold voltage of transistors to limit the voltage swing [27]–[29]. The energy efficiency of these techniques is limited since the energy savings depend on the threshold voltage of transistors, which is not that low compared to the supply voltage, especially for modern, scaled-down technologies. The last group of single supply schemes achieve the desired level of voltage by restraining the charging and discharging time of the load capacitance [30]–[33]. These circuits exhibit low voltage swing and low circuit complexity, therefore, high power savings. However, these schemes exhibit low SNR and are susceptible to crosstalk noise as well as process and environmental variability [25]. An additional restriction of these schemes is that the capacitive load must be known at design time, which is not always feasible, especially for off-die interconnects.

To enhance noise immunity of signal transmission, differential signalling has been widely employed. Two complementary signals are transmitted on a pair of wires to indicate the state of the transferred information. The receiver calculates the voltage difference of the pair of complementary signals instead of the difference between the data signal and the ground as in single-ended transmission. Differential signalling is highly resistive to crosstalk and electromagnetic interference (EMI) compared to single-ended transmission. The reason is that external noise similarly affects both wires, thus, is cancelled out [34]. Because of the noise-resilient nature of differential signalling, a further reduction in the signal swing can be achieved compared to single-ended signalling [25].

Although the potential power reduction is high by employing low-swing signalling reaching up to  $4 \times [30]$ , there are some important considerations. The major concern is reliability as single-ended, low-swing signalling is susceptible to noise. On the contrary, techniques that offer improved noise immunity have important limitations. Dual power rail methods depend on additional supply voltage for the voltage conversion,

which induces a large area penalty and increases the physical design complexity. Differential signalling requires the double number of wires and I/O pins, which is an important limitation from both an area and a power perspective especially, as the number of I/Os does not scale as fast with technology evolution.

## 2.2 Increasing Physical Proximity

Technology scaling has increased computational density, but, at the same time, has increased data movement over longer interconnects. Accessing memory is one of the primary bottlenecks in terms of both power and performance [6]. The cost of data movement can be alleviated by placing memory modules closer to processing elements, thus, increasing the physical proximity. A primary way to improve physical proximity and, therefore, decrease the interconnect length is 3-D and 2.5-D integration, described in subsections 2.2.1 and 2.2.2, respectively.

#### 2.2.1 Three-Dimensional Integration

In 3-D integration, the third dimension is exploited by stacking multiple dice, which are vertically interconnected. There are various ways of interconnecting the different tiers, such as wire bonding or inductive links, however, the most common approach is the utilisation of Through Silicon Vias (TSVs) [7]. An example of 3-D integration is depicted in Fig. 2.2, where memory dies are vertically stacked and interconnected using TSVs and microbumps ( $\mu$ bumps).

3-D integration offers significant benefits in terms of performance, size, and heterogeneity. The primary advantage of 3-D integration is the drastic decrease in interconnect length, enabled by vertically stacking dice [8]. Shorter wire length leads to a decrease in delay and power dissipation since the capacitive load is lower. Another important benefit of 3-D ICs is the ability to combine heterogeneous tiers with disparate fabrication processes, such as sensors, analog and digital processors, and memories, in a single low form factor package. In this way, the system footprint is reduced compared to planar approaches [9]. Health monitoring, military, security, and environmental monitoring are just a few areas that can benefit from this heterogeneous integration paradigm. Finally, TSVs provide high connectivity density, thus, increased data bandwidth and performance.

Figure 2.2: Schematic of AMD's High Bandwidth Memory [11].

The benefits and versatility of 3-D integration using TSVs has led to the commercialisation of this technology. Examples of commercial 3-D systems are High Bandwidth Memory (HBM) [10], [11], where dynamic random-access memory (DRAM) dies are vertically stacked and interconnected with TSVs and  $\mu$ bumps as depicted in Fig. 2.2, Hybrid Memory Cube [12], where four DRAM dice and one logic die are vertically stacked using TSVs in a single package, and Samsung's Solid State Drives using vertical-NAND (V-NAND) technology [13].

Despite the commercial success of 3-D systems, there are important challenges that restrict the applicability of this technology. Thermal issues are of major concern, as the high volumetric density of devices increases the power density and, thus, temperature [6]. Additionally, manufacturing complexities, testing for wafer level integration, design of global interconnects, and the development of efficient Computer Aided Design (CAD) tools for placement and routing are some of the challenges of 3-D integration [6]. These issues have limited the usage of 3-D integration mainly in memory systems.

## 2.2.2 2.5-Dimensional Integration

2.5-D integration is an alternative solution that resolves the manufacturing and thermal issues of 3-D ICs [14], whilst provides fine pitch interconnections. 2.5-D integration introduces a new substrate layer, named interposer, which interconnects the dice and the package substrate layer. An interposer is used in AMD's HBM to link the processing unit with the logic die of the memory stack and the package substrate as illustrated

in Fig. 2.2. Other examples of commercial products employing interposer technologies are Xilinx Virtex-7 FPGA [15] and NVIDIA Tesla P100 Graphic Processing Unit (GPU) accelerator [16].

Interposers utilise  $\mu$ bumps and Redistribution Layers (RDLs) to interconnect the hosted dice. RDLs are horizontal metal layers similar to Back-End-of-Line (BEOL) interconnects, therefore, exhibit low pitch. Interposers provide high integration density and smaller form factor compared to traditional packaging technologies, as the size of interconnects, vias, and bumps is decreased. Therefore, higher bandwidth and lower power consumption are achieved [38].

The electrical characteristics of interposer-based interconnects are affected by the material of the interposer substrate. Silicon is the most widespread material used for interposers among the semiconductor fabrication processes, offering fine metal routing [17]. However, silicon substrate suffers from high cost and high insertion loss due to high conductivity [17]. Organic materials are a useful alternative that have been used for IC packaging. However, organic substrates require large pads, therefore, they are unsuitable for interconnecting high I/O density dice [18]. Finally, glass is a promising solution as exhibiting good electrical properties, such as low insertion loss and high resistivity, [19] and the cost per I/O is lower compared to silicon. Glass interposers also pose challenges, including cost of via formation and inferior thermal characteristics compared to silicon [19].

## 2.3 Signal Encoding for Parallel Transmission

Although 3-D and 2.5-D technologies increase the physical proximity of the interconnected dies, the high power of interconnects remains a major problem. Therefore, alternative low-power techniques are employed as well. An effective method to decrease the dynamic power is to reduce the switching activity, *a* of Equation 2.1. This aim can be effectively implemented through signal encoding. An encoder circuit is added to the transmitter to reduce bit transitions and a decoder is included at the receiver to restore the data as illustrated in Fig. 2.3 for a single bus lane. Signal encoding techniques have been developed for both parallel and serial data communication. The focus of this section is on parallel communication, while encoding for serial interfaces is discussed in Section 2.4.

Parallel transmission is the most straightforward way of transferring data between

dies as each bit of data is transmitted simultaneously on a separate bus lane. In addition, parallel communication is source synchronous, *i.e.* a clock signal is transmitted along with data that is utilised by the receiver to sample the incoming data. Hence, parallel transmission provides better design simplicity over serial transmission, since no added circuitry is required for serialisation/deserialisation or clock recovery. Wide parallel links are especially preferred in advanced packaging technologies such as 2.5-D and 3-D integration and EMIB [96]–[97], where higher wire densities are supported compared to Printed Circuit Board (PCB) interconnects.

Encoding techniques tailored to parallel interfaces reduce the power dissipation of data transmission by decreasing the bit transitions between consecutively transmitted data words. This aim is accomplished without affecting noise resilience and without inducing any manufacturing challenges. In addition, encoding schemes become more beneficial with the scaling of technology. By employing signal encoding, a significant portion of the power dissipated in interconnects can be saved at the expense of a low increase in on-chip power for encoding and decoding. As technology scales, the power dissipated for computation decreases faster compared to the interconnect power [44]. Consequently, the impact of the added power for encoding and decoding on the overall savings in power diminishes.

Although some techniques aim at latency reduction [50], the vast majority of encoding methods target primarily to decrease power. The focus of this thesis is on the latter objective. Encoding schemes can be classified to either static or adaptive. Static schemes exploit the statistical properties of data streams, considered known at design time, and are discussed in subsection 2.3.1. Alternatively, adaptive schemes assume that there is no prior knowledge of these properties, observe data at runtime, and apply the appropriate encoding. These methods are described in subsection 2.3.2.

#### 2.3.1 Static Encoding Schemes

The main requirement of static schemes is that the statistical properties of the transmitted data must be known at design time. An analysis of these properties is conducted before static schemes are developed. In this way, static schemes usually exhibit lower

Figure 2.3: Basic structural diagram for signal encoding.

overheads compared to adaptive. Static techniques that decrease bit transitions of both address buses and data buses have been proposed.

The transmitted signals in address buses tend to be sequential as both data and instructions are usually stored in consecutive memory addresses. This attribute is exploited by some encoding techniques to reduce the number of transitions. Bit transitions in this type of buses can be reduced by encoding addresses with Gray code [51]. Gray code ensures a single bit transition between consecutive addresses. To code is another encoding technique that is based on the observation that addresses are usually incremental with a fixed stride, in which case the content of the bus is not altered and an extra bit signal, named INC, is set [52]. In this way, To ensures that no transition occurs for consecutive addresses. Both Gray code and To code decrease bit transitions only for consecutive addresses and are ineffective when the frequency of sequential addresses is low such as in case of frequent branch instructions.

The Beach Solution is an encoding technique that aims to address this problem [54]. This technique relies on the assumption that even non-sequential addresses are frequently correlated. A prior analysis of the address stream produced by one or more executions of a program is required to group the bus lines in clusters. For each cluster an appropriate encoding function is generated. However, this technique is application oriented since a program has to be executed at least once to generate the address stream to analyse. Therefore, this scheme is not suitable for general purpose processors where different applications can run concurrently.

In the case of data buses or multiplexed address and data buses, the transmitted data words are not sequential, therefore, the previous techniques are rather not effective. A technique that is appropriate for these types of buses is probability-based mapping [55]. The data words with high probability of occurrence are mapped to code words with low Hamming weight, *i.e.* low number of 1's, to decrease the overall transitions. An analysis of the data stream at design time is required to obtain these statistical properties. This idea is implemented using reversible circuits in [56], where only part of the statistics of the data stream is given. Another technique that assigns limited-weight codes, *i.e.* codes with low Hamming weight, is proposed in [57]. The assignment of codes is determined based not only on the frequency of occurrence of each memory trace but, also, on the frequency with which each trace is followed by another trace. By exploiting the information regarding the sequence of traces, a further reduction in bit transitions is achieved. A prior analysis of the memory traces of the system is required for the design of the code assignment.

In [53], an encoding technique is proposed for multiplexed buses, which combines T0 coding [52] and Bus Invert (BI) [46]. BI is an adaptive encoding scheme suitable for data buses and is further discussed in the next subsection. The method applies the T0 code in case of consecutive addresses, otherwise BI is employed. The power savings of this technique are limited if the addresses are not consecutive and, additionally, the circuit overhead of the technique is higher as two different techniques are combined. An algorithm that generates low activity codes based on a detailed statistical characterisation of the data stream is proposed in [58]. Particularly, the probability distribution of all pairs of successive values of data words is required to assign a code to each pair. The optimal code can be generated for buses with limited width as the complexity of the encoding and decoding increases rapidly with the number of bus lines. Hence, this technique is more effective for narrow buses and requires a detailed analysis of the data stream statics.

#### 2.3.2 Adaptive Encoding Schemes

Adaptive techniques do not require a *a priori* knowledge of the statistical properties of data, therefore, address the limitations of static methods. Specifically, static schemes rely on the statistics of the transmitted data stream for the design of the encoding mechanism. Therefore, these statistics must be known at design time, which is not always feasible. In addition, the power savings diminish if the statistical properties vary temporally. Alternatively, adaptive techniques observe data during runtime to apply the appropriate encoding. Hence, these techniques are more versatile and can be applied to a wide range of interconnects.

A plethora of adaptive techniques for parallel interfaces have been proposed. These encoding schemes are categorised, based on their characteristics, in Table 2.1. General purpose techniques can be applied to a wide range of parallel buses and are effective for all types of data. On the contrary, there are encoding techniques that exploit the correlation of the transmitted data to achieve a higher reduction in bit transitions. However, these techniques are ineffective for uncorrelated data. In time-based techniques, data are represented as delays in the time domain to reduce transitions.

Techniques aiming to balance performance and power use the energy delay product as an optimisation metric. Techniques based on value prediction add two identical predictors to the encoder and the decoder and whenever the prediction is successful, no data are transmitted over the bus, thus, power is saved. Coupling-based techniques are designed for interconnects with high coupling capacitance between adjacent wires.

| Categories                                         | Techniques                         |

|----------------------------------------------------|------------------------------------|

| General purpose                                    | [46], [60], [61], [62], [72], [48] |

| Exploiting data correlation                        | [65], [67], [66], [63], [64]       |

| Time-based                                         | [68], [69]                         |

| Balancing performance and energy                   | [70], [71], [73]                   |

| Value prediction                                   | [74], [75], [76]                   |

| Coupling-based                                     | [77]–[81]                          |

| Tailored to interfaces with asymmetric termination | [71], [85]–[91]                    |

Table 2.1: Classification of adaptive encoding techniques for parallel interconnects based on their characteristics.

Therefore, these techniques focus on reducing the power dissipated in charging and discharging the coupling capacitance. Finally, techniques tailored to interconnects with asymmetric termination reduce power by decreasing the direct current flowing due to the termination resistor of these links.

#### **General Purpose Techniques**

BI is one of the early encoding schemes for decreasing bit transitions [46]. BI works as follows. In each clock cycle, BI calculates the Hamming distance, *i.e.* the number of bits that two data words differ, of the current data word and the word transmitted in the previous clock cycle. If the Hamming distance is higher than M/2, where M is the bus width, then the data word is inverted before transmission, otherwise it remains unaltered. One redundant bus line is used to inform the decoder whether the data word is inverted or not. Hence, the decoder conditionally inverts the input data depending on the value of the redundant bus line.

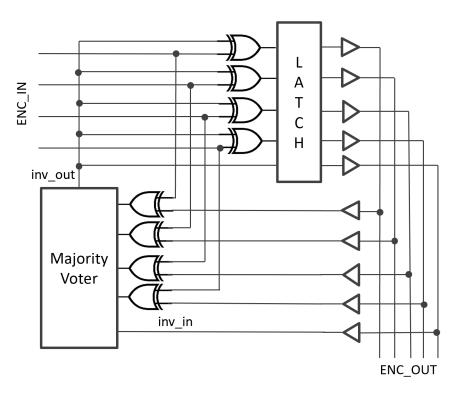

A possible circuit implementation of the technique is depicted in Fig. 2.4 for a 4-bit bus. The bits of the two words are compared using 4 XOR gates, while the majority voter calculates the Hamming distance and decides whether to invert the data word or not. If the data word is inverted then *inv\_out* is set. The remaining 4 XOR gates are used to invert the data word. The implementation of the decoder is simple, as *M* XOR gates are required for the conditional inversion of the data word.

This technique remains popular and is adopted in commercial bus interfaces such

Figure 2.4: Circuit implementation of the BI encoder [46].

as in HBM [10] because of its simple circuit implementation, and low overhead ( $\sim$ 1 mW in a 65 nm technology, operating at 400 MHz). The benefits of using BI are investigated in [47]. When BI is applied to double-data-rate fourth generation (DDR4) memory, the I/O power as well as the power-supply noise decrease. Despite its commercial success, BI provides limited savings in transitions compared to more elaborate techniques, especially in cases where data are highly correlated, such as image data, where BI exhibits 4.42% reduction in transitions for a 32-bit bus [60]. This behaviour is, also, verified in Chapter 4 of the thesis, where BI exhibits a mere 6.04% reduction in transitions for the transmission of image data over a 64-bit bus.

Some techniques are based on BI and aim at enhancing the reduction in bit transitions by inverting only a part of the data word. In [59], the Partial Bus Invert (PBI) method is proposed, where a subgroup of bus lines is composed. Only the bits of the bus lines in the subgroup are considered for inversion according to BI. The subgroup is formed based on the transition probabilities and the transition correlations among the bus lines. PBI has both static and adaptive features as these statistics must be known at design time, however, the decision about inverting the subgroup of bus lines is taken at runtime. Nevertheless, PBI is not effective when the statistics of the data stream are not known in advance.

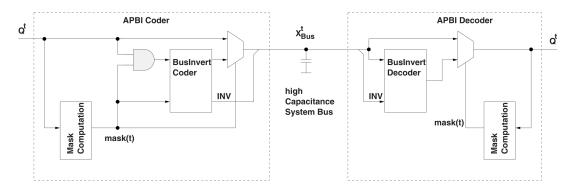

Adaptive Partial Bus Invert (APBI) is an extension of PBI that is fully adaptive and, thus, addresses the restriction of PBI [60]. The data stream is observed during runtime and the subgroup of encoded bus lines is changed periodically. Specifically, APBI observes the data stream for a window of a fixed number of words and forms a subgroup with the bus lines with the highest number of transitions, called mask. BI is then applied only to the bus lines in the mask and one extra bit (*INV*) is used to inform the decoder about inversion.

APBI encoding is defined as follows:

$$X_{Bus}^{t} = \{X_{d}^{t}, INV\} = \begin{cases} \{Q^{t}, 0\}, & \text{if } W(X_{Diff}^{t}) \leq \frac{W(mask(t)) + 1)}{2} \\ \{Q^{t} \oplus mask(t), 1\}, & \text{otherwise}, \end{cases}$$

(2.2)

where  $X^t_{Bus}$  is the encoded data word including the redundant bit, INV, that is transmitted over the bus at time t.  $Q^t$  is the original data word unencoded and W(x) is the Hamming weight, *i.e.* the number of 1's of a binary vector. The mask at time t is equal to  $mask(t) = \{m_0^t, m_1^t, ..., m_{n-1}^t\}$ , where  $m_i^t \in \{0, 1\}$  and n is the bus width. If  $m_i^t = 1$ , then, the  $i^{th}$  bus line is included in the mask at time t, thus, in the subgroup of bus lines where BI is applied.  $X^t_{Diff}$  is defined as:

$$X_{Diff}^{t} = (X_{Bus}^{t-1} \oplus \{Q^{t}, 0\}) \cdot mask(t), \tag{2.3}$$

where  $X_{Bus}^{t-1}$  is the encoded data word transmitted over the bus at time t-1. The decoder conditionally inverts the bus lines of the mask depending on the value of the redundant bit INV. Hence, the decoder restores the original word as follows:

$$Q^{t} = \begin{cases} \{X_{d}^{t}\}, & \text{if } INV = 0\\ \{X_{d}^{t} \oplus mask(t)\}, & \text{if } INV = 1. \end{cases}$$

(2.4)

To determine which bus lines are in the mask, the number of bit transitions of each bus line, as well as the total number of transitions across the bus have to be calculated over a specified window of *N* data words. The mask is, therefore, calculated as follows:

$$m_i^t = \begin{cases} 1, & \text{if } \alpha_i \ge \alpha_{tot}/n \\ 0, & \text{if } \alpha_i < \alpha_{tot}/n. \end{cases}$$

(2.5)

where  $\alpha_i$  is the number of transitions of the  $i^{th}$  bus line and  $\alpha_{tot}$  is the total number of

transitions of the bus over a specified window of N words. Hence, if the number of transitions of a bus line is higher than the average, then, the bus line is included in the mask.

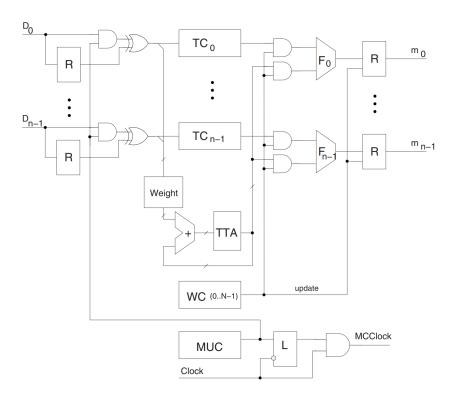

The mask information is not transmitted to the decoder, instead the calculation of the number of transitions per bus line is performed by the decoder over the same window of words to define the mask. The circuit diagram of APBI is illustrated in Fig. 2.5. The Bus Invert Coder can be implemented according to Fig. 2.4 and the Decoder with a number of XOR gates as in BI. The implementation of the Mask Computation block is depicted in Fig. 2.6. The current data word  $(D_0, ..., D_{n-1})$  is XOR-ed with the previous word to detect if a transition occurs in each bus line. The previous word is stored in registers denoted as R in the diagram. The outputs of the XOR gates are fed to the enable inputs of n counters  $(TC_0,...,TC_{n-1})$ , which count the number of transitions of each bus line. In addition, the total number of transitions of the bus has to be computed. Therefore, the Weight block calculates the number of 1's of the XOR outputs in each cycle and the output of Weight is fed to Total Transition Accumulator (TTA), where the total number of transitions over N cycles is calculated.

The mask is computed in the  $F_0,...,F_{n-1}$  blocks according to Equation 2.5. To simplify the division operation of Equation 2.5, the bus width is restricted only to values that are a power of 2. Thus, the division can be replaced by a shift operation. The output of the F blocks is the resulting mask and is stored in registers, R. The computation of the mask in F is only performed at the end of each window, therefore, a Window Counter (WC) is used that produces an update signal that is fed to the F blocks and the final registers.

The power dissipated in the encoder and decoder circuits of APBI can be reduced by disabling the mask computation for some windows. Hence, instead of calculating a

Figure 2.5: Circuit diagram of the APBI technique [60].

Figure 2.6: Circuit diagram of the Mask Computation block [60].

new mask in every window, the mask can be updated every  $k^{th}$  window. Consequently, the mask computation is disabled for windows 1 to k-1. This function is implemented in the Mask Update Counter (MUC) and the clock gate circuit, composed of a latch (L) and an AND gate, that generates the MCClock clock signal. The output of the MUC block is only high during the  $k^{th}$  window, thus, the mask is computed only during this window.

APBI is particularly effective and outperforms BI in terms of reduction in transitions for highly correlated data streams, such as image files [60]. However, this technique suffers from high circuit overhead as the calculation of the mask must be performed twice, both in the encoder and the decoder, especially when the mask computation takes place in every window. Alternatively, when the mask update interval is increased, the reduction in transitions decreases, thus, restricting the power savings. Furthermore, in cases where the bus lines are not correlated, the simple BI technique is more efficient, as shown in Chapter 4.

The effectiveness of bus inversion diminishes for large bus widths [62], therefore, alternative methods are explored. Shift Invert (SINV) coding selects between shifting and inverting data words to further decrease the number of transitions compared to BI

[61]. Specifically, SINV, first, evaluates the number of transitions of transmitting the data word in the original form, inverted, left-shifted, and right-shifted. Then, the data word is transmitted in the form that leads to the lowest number of transitions. Two additional bus lines are required to indicate the form of the transmitted data such that the decoder can retrieve the original data.

Although this technique further reduces transitions compared to BI, the required hardware complexity is higher as more computations of Hamming distances are required. The circuit overhead of the technique is not estimated, therefore, the effectiveness of the technique in decreasing power cannot be properly evaluated. Finally, the effectiveness of SINV in reducing transitions is only evaluated for random data, however, data are correlated in many applications.

Bus shifting (BS) rotates the data word to be transmitted by a number of bits to minimise transitions and uses spatial redundancy to send this number to the decoder [62]. To determine the optimal number of rotations, the Hamming distance for all possible rotations of each data word is calculated. The number of rotations with the lowest Hamming distance is then selected. This scheme is only tested for uniformly distributed random data, where the probability of transition of each bus line is 0.5.

BS is most effective for random data when the bus width is 32 or 64 bits. However, in this case 32 or 64, respectively, calculations of Hamming distances per clock cycle are required, which increase the hardware complexity. Alternatively, for narrow buses the reduction in transitions is limited due to the redundant bus lines. For example, 2 redundant bus lines are required when the bus width is 4 bits, which diminish significantly the transition savings [62]. Furthermore, a circuit implementation of this scheme is not provided, therefore, the power overhead of the encoding mechanism can not be assessed. Hence, the power savings of the technique can not be fairly estimated. In addition, the performance of BS in reducing bit transitions is only evaluated for random data and not for real types of data, which often are correlated.

Adaptive Bus Encoding (ABE) is another technique that encodes only the highly correlated bus lines [72]. This technique observes the data characteristics over a window of a fixed number of words to select a bus line as a basis line and form a cluster with the bus lines that exhibit high correlation with the basis line. The lines in the cluster are finally XOR-ed with the basis to achieve a high reduction in bit transitions.

The pseudocode of the ABE technique is shown in Algorithm 1, where N is the number of bus lines. To determine the optimal basis line and cluster, each bus line is considered as basis and the number of transitions of every other line XOR-ed with

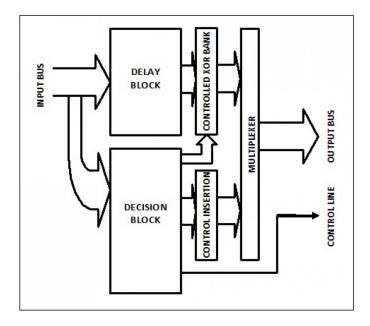

the basis is calculated. For every basis line, a cluster is formed with the bus lines that exhibit less transitions when XOR-ed with the basis line. Subsequently, the clustered lines are XOR-ed with the basis line and the savings in transitions are calculated. The bus line that leads to the maximum savings is selected as basis. This process is repeated for each observation window. The basis and cluster information are transmitted using a redundant bus line and an additional clock cycle at the beginning of the window, respectively, as depicted in Fig. 2.7. The observation window comprises 16 words, the bus lines are denoted as  $b_0 - b_{15}$  and clock cycles as  $t_{14} - t_{23}$ .

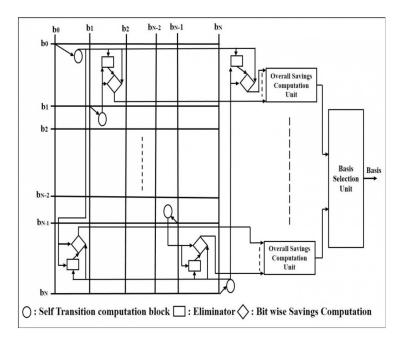

A high level circuit diagram of the encoder is depicted in Fig. 2.8. The encoder comprises a decision block, which determines the basis line and the cluster, a delay element, a block of XOR gates used to XOR the clustered lines with the basis line and a multiplexer is used to insert the temporal redundancy, *i.e.* the cluster information. The decision block is structured as a  $N \times N$  array, as illustrated in Fig. 2.9. In each row (*i*) the corresponding bus line ( $b_i$ ) is considered as basis. The number of transitions of the  $b_i$  are calculated in the self transition computation block, while in the bit wise savings computation block the number of savings in transitions contributed by every bus line  $b_j$  ( $j \neq i$ ) when XOR-ed with the basis line  $b_i$  are calculated and the presence of  $b_j$  in the cluster is decided.

The overall savings computation unit calculates the total number of savings in transitions for each  $b_i$ . In the basis selection unit, the basis and the cluster that exhibit the highest savings are selected. The role of the eliminator block is to restrict the power dissipated in the encoder. Therefore, this block removes the bus lines with a low number of transitions from consideration as basis line, since the probability of being selected as basis is low. The circuit implementations of the individual blocks of Fig. 2.9

## **Algorithm 1** Pseudocode of the ABE technique.

- 1: Find total number of transitions in all the bit lines  $s_{ini}$

- 2: **for**  $i \leftarrow 0$  to N-1 **do**

- 3: Choose  $i^{th}$  line as basis

- 4: **for**  $j \leftarrow 0$  to N-1,  $j \neq i$  **do**

- 5: Put  $j^{th}$  line in cluster if  $j^{th}$  line has more transitions than  $j^{th}$  line XOR-ed with basis line

- 6: XOR all the clustered lines with the basis line

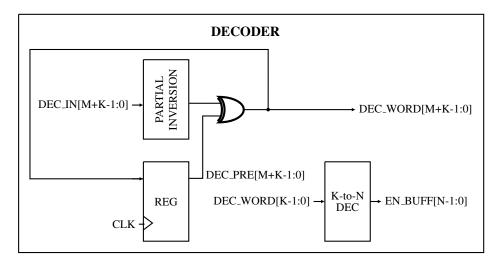

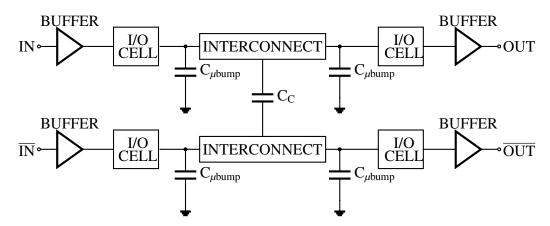

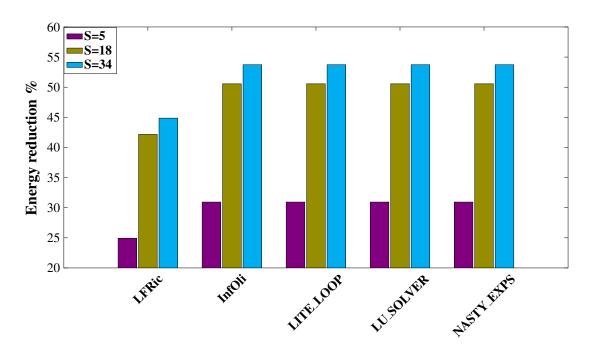

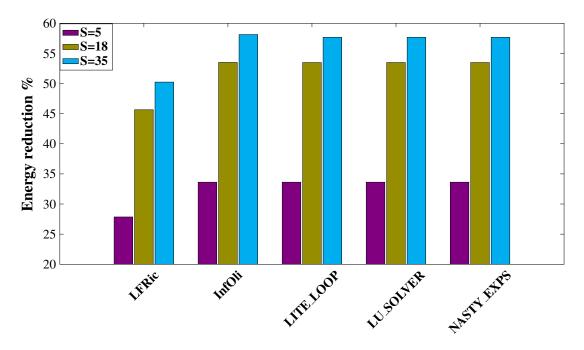

- 7: Find number  $(s_i)$  of transitions in this modified set