# PARALLELISATION OF NEURAL PROCESSING ON NEUROMORPHIC HARDWARE

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF SCIENCE AND ENGINEERING

2022

Luca Peres

Department of Computer Science

## Contents

| A | bstra | act                                   | 17 |

|---|-------|---------------------------------------|----|

| D | eclar | ation                                 | 19 |

| C | opyri | $_{ m ight}$                          | 21 |

| A | ckno  | wledgements                           | 23 |

| 1 | Intr  | roduction                             | 25 |

|   | 1.1   | Motivation                            | 25 |

|   | 1.2   | Research Questions                    | 26 |

|   | 1.3   | Contributions                         | 26 |

|   | 1.4   | Publications                          | 27 |

|   |       | 1.4.1 External Coverage               | 28 |

|   | 1.5   | Thesis Structure                      | 28 |

|   |       | 1.5.1 Chapter 2                       | 29 |

|   |       | 1.5.2 Chapter 3                       | 29 |

|   |       | 1.5.3 Chapter 4                       | 29 |

|   |       | 1.5.4 Chapter 5                       | 30 |

|   |       | 1.5.5 Chapter 6                       | 30 |

|   | 1.6   | Summary                               | 30 |

| 2 | Neı   | ıral Modelling and Dedicated Hardware | 31 |

|   | 2.1   | Introduction                          | 31 |

|   | 2.2   | Neurons and Neural Networks           | 32 |

|   |       | 2.2.1 Point Neuron Models             | 34 |

|   |       | 2.2.2 Synaptic Plasticity             | 36 |

|   |       | 2.2.3 Multicompartment Neuron Models  | 38 |

|   | 2.3 | Neura                          | l Network Simulators                          |

|---|-----|--------------------------------|-----------------------------------------------|

|   |     | 2.3.1                          | Software Simulators                           |

|   |     | 2.3.2                          | Hardware Simulators                           |

|   | 2.4 | Neuro                          | morphic Hardware                              |

|   |     | 2.4.1                          | Analog Neuromorphic Systems                   |

|   |     | 2.4.2                          | Digital Neuromorphic Systems                  |

|   | 2.5 | The S                          | piNNaker System                               |

|   |     | 2.5.1                          | Hardware Overview                             |

|   |     | 2.5.2                          | Software Overview                             |

|   | 2.6 | Neura                          | l Modelling and Simulations on SpiNNaker      |

|   |     | 2.6.1                          | Network Partitioning                          |

|   |     | 2.6.2                          | Routing Tables and Communications             |

|   |     | 2.6.3                          | Synaptic Matrices                             |

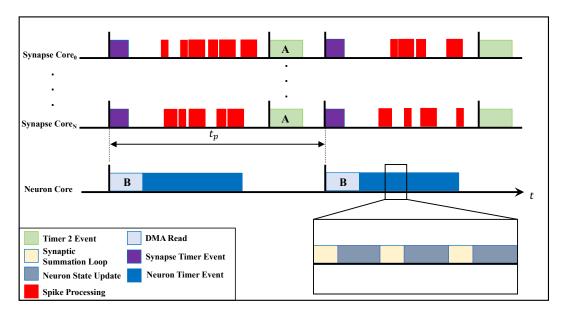

|   |     | 2.6.4                          | Simulation Flow                               |

|   |     | 2.6.5                          | Synaptic Update                               |

|   | 2.7 | Summ                           | ary                                           |

| 3 | Rea | $\operatorname{l-Tim}\epsilon$ | e Simulations of SNNs 71                      |

|   | 3.1 | Introd                         | uction                                        |

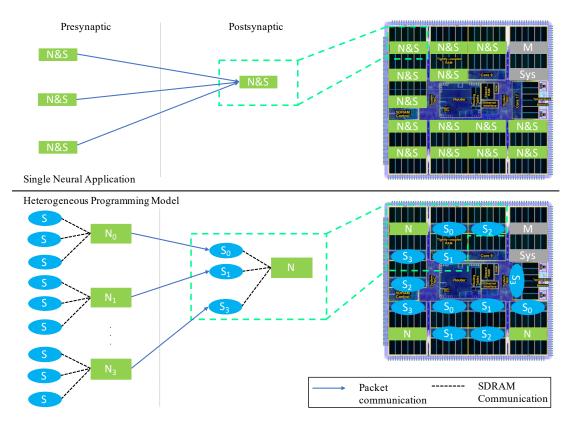

|   | 3.2 | The H                          | eterogeneous Programming Model                |

|   |     | 3.2.1                          | The Synapse-Centric Mapping                   |

|   |     | 3.2.2                          | Model Adaptations                             |

|   |     | 3.2.3                          | Model Benchmarking                            |

|   | 3.3 | Real-T                         | Time Simulation of the Cortical Microcircuit  |

|   |     | 3.3.1                          | The Cortical Microcircuit Network             |

|   |     | 3.3.2                          | Challenges and Previous Works                 |

|   |     | 3.3.3                          | Real-Time Simulation                          |

|   | 3.4 | Result                         | s                                             |

|   |     | 3.4.1                          | Simulation Accuracy                           |

|   |     | 3.4.2                          | Machine Allocation and Energy Consumption 107 |

|   | 3.5 | Discus                         | sion                                          |

|   | 3.6 | Summ                           | ary                                           |

| 4 | On- | line Le                        | earning on SpiNNaker 113                      |

|   | 4.1 |                                | uction                                        |

|   | 4.2 | The U                          | rbanczik-Senn Neuron Model                    |

|   |     | 4.2.1  | SpiNNaker Implementation                                    | 117 |

|---|-----|--------|-------------------------------------------------------------|-----|

|   |     | 4.2.2  | The Plasticity Framework                                    | 118 |

|   | 4.3 | The T  | hree-Compartment Pyramidal Model                            | 119 |

|   |     | 4.3.1  | SpiNNaker Implementation                                    | 120 |

|   |     | 4.3.2  | The Plasticity Framework                                    | 121 |

|   | 4.4 | Error  | Backpropagation approximation                               | 121 |

|   |     | 4.4.1  | Dendritic Microcircuits                                     | 122 |

|   | 4.5 | Applie | eation of the Heterogeneous Partitioning                    | 124 |

|   |     | 4.5.1  | Microcircuit Network for MNIST                              | 124 |

|   |     | 4.5.2  | Placements and Constraints                                  | 125 |

|   |     | 4.5.3  | Synaptic Matrices in Local Memory                           | 127 |

|   |     | 4.5.4  | A Plasticity Framework for the Heterogeneous Model          | 128 |

|   |     | 4.5.5  | Rate Live Injector                                          | 132 |

|   | 4.6 | Result | s                                                           | 135 |

|   |     | 4.6.1  | Correctness of the US Learning Rule                         | 135 |

|   |     | 4.6.2  | Correctness of the Dendritic Microcircuits Learning         | 137 |

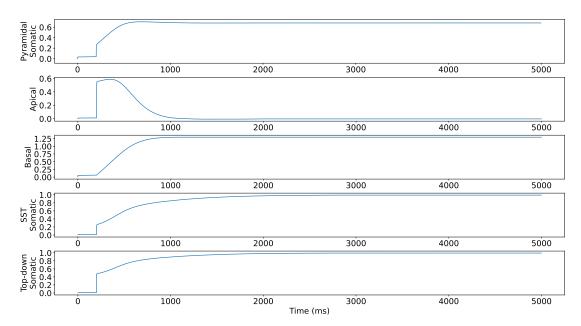

|   |     | 4.6.3  | Dendritic Microcircuit and Self-Predicting State Simulation | 139 |

|   |     | 4.6.4  | Nonlinear Regression Task                                   | 140 |

|   |     | 4.6.5  | The MNIST Challenge                                         | 141 |

|   | 4.7 | Discus | ssion                                                       | 142 |

|   | 4.8 | Summ   | ary                                                         | 142 |

| 5 | Mul | ti-Tar | get Partitioning                                            | 145 |

|   | 5.1 | Introd | uction                                                      | 145 |

|   | 5.2 | Why N  | Multi-Target Synapse Cores?                                 | 146 |

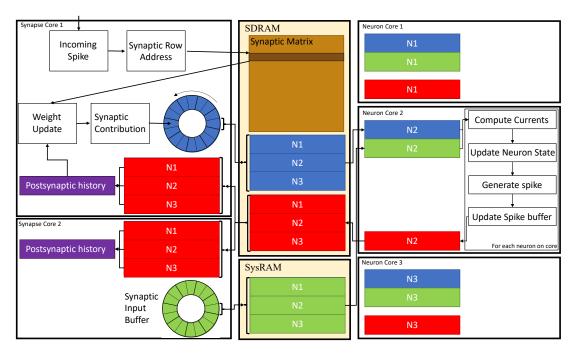

|   | 5.3 | Multi- | Target Synapse Cores Implementation                         | 149 |

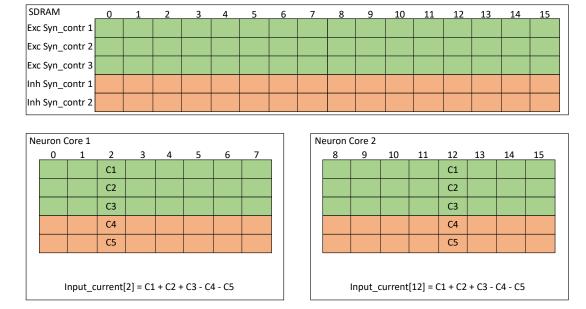

|   |     | 5.3.1  | Memory Usage                                                | 150 |

|   |     | 5.3.2  | Dual Memory Use                                             | 151 |

|   |     | 5.3.3  | Cores Interaction                                           | 151 |

|   |     | 5.3.4  | Synaptic Plasticity                                         | 155 |

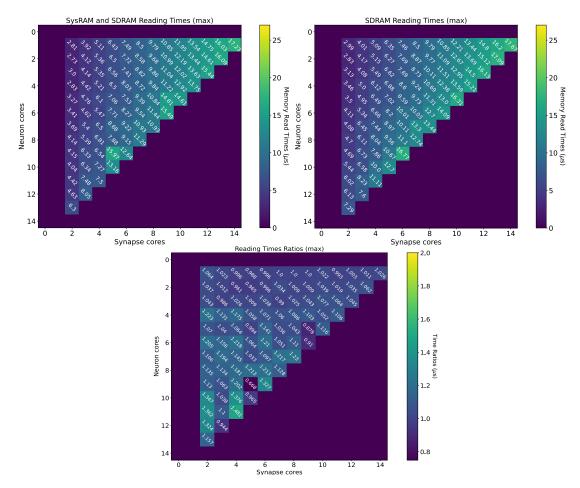

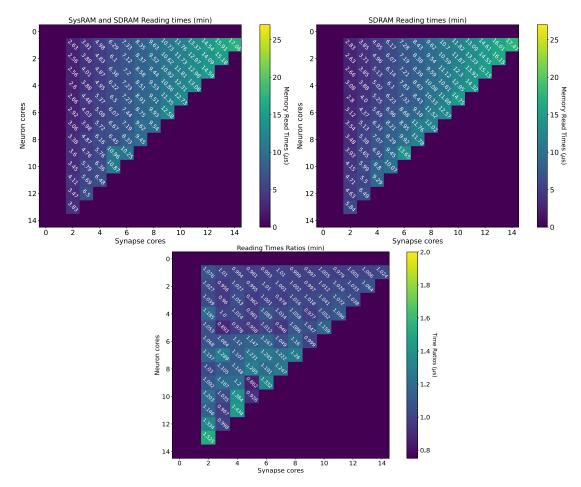

|   | 5.4 | Result | s                                                           | 157 |

|   |     | 5.4.1  | Memory Benchmarking                                         | 157 |

|   |     | 5.4.2  | Peak Throughput Performance                                 | 167 |

|   |     | 5.4.3  | Sparsity Efficiency                                         | 186 |

|   | 5.5 | Discus | ssion                                                       | 189 |

|   | 5.6 | Summ   | ary                                                         | 191 |

| 6 Conclusions |       |        |                                 |     |

|---------------|-------|--------|---------------------------------|-----|

|               | 6.1   | Future | e Work                          | 194 |

|               |       | 6.1.1  | Further Models Extensions       | 195 |

|               |       | 6.1.2  | Future Neuromorphic Generations | 196 |

|               | 6.2   | Overal | ll Summary                      | 196 |

| Bi            | bliog | raphy  |                                 | 199 |

Word Count: 43361

## List of Tables

| 2.1 | Spin1API priority levels                                     | 56  |

|-----|--------------------------------------------------------------|-----|

| 3.1 | Priority levels for the <i>Synapse</i> cores events          | 84  |

| 3.2 | Cortical Microcircuit Parameters                             | 96  |

| 3.3 | Cortical Microcircuit Energy Measurements                    | 110 |

| 4.1 | Synaptic processing time                                     | 126 |

| 5.1 | Presynaptic firing neurons for the peak processing benchmark | 170 |

## List of Figures

| 1.1  | Thesis Structure                                              | 28 |

|------|---------------------------------------------------------------|----|

| 2.1  | Generations of Neural Networks                                | 33 |

| 2.2  | Block diagram of a SpiNNaker Chip                             | 48 |

| 2.3  | Layout of a SpiNNaker Chip                                    | 49 |

| 2.4  | The SpiNNaker system                                          | 52 |

| 2.5  | The SpiNNaker software toolchain                              | 53 |

| 2.6  | The SpiNNaker board side software                             | 55 |

| 2.7  | SpiNNaker event-driven programming framework                  | 57 |

| 2.8  | SNN partitioning on SpiNNaker                                 | 58 |

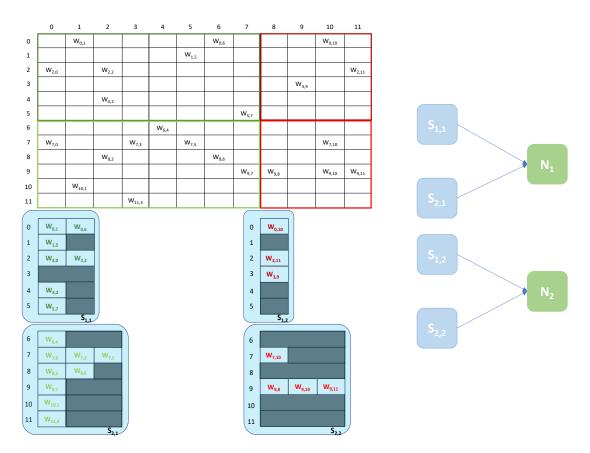

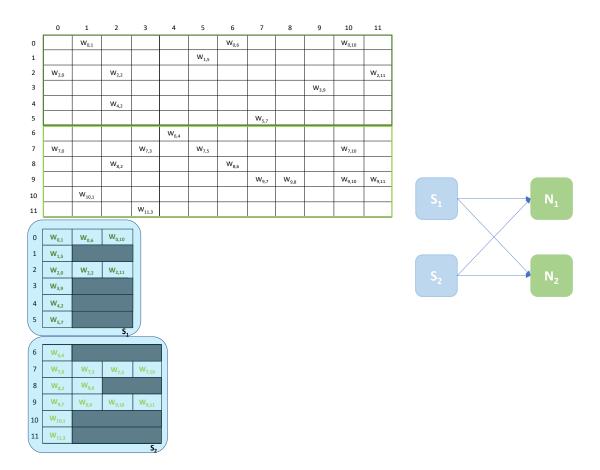

| 2.9  | Synaptic matrix structure and partitioning                    | 60 |

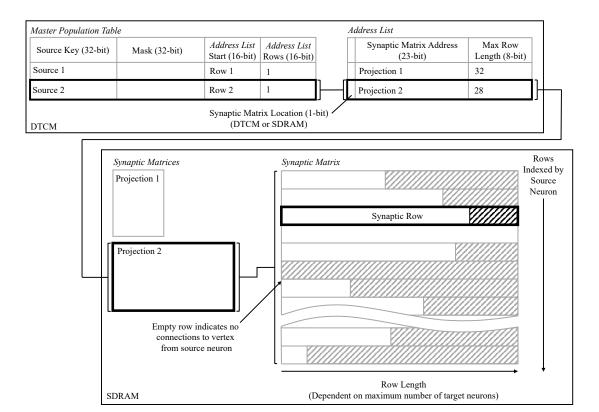

| 2.10 | Master Population Table and Address List interaction          | 62 |

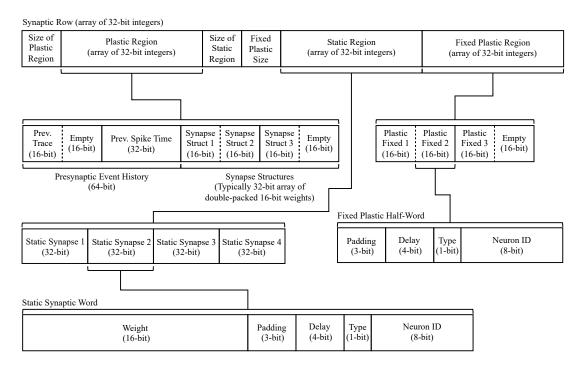

| 2.11 | Synaptic row structure                                        | 63 |

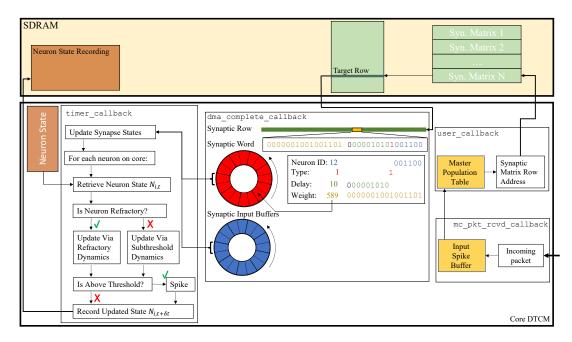

| 2.12 | SNN simulation flow                                           | 65 |

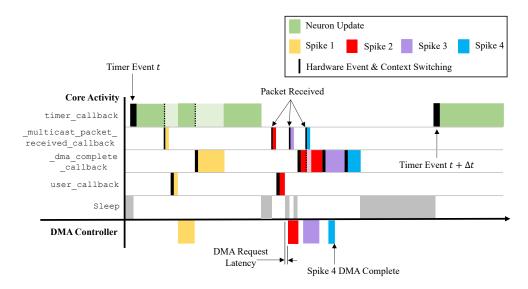

| 2.13 | Callbacks interaction                                         | 67 |

| 3.1  | Synaptic matrix partitioning under the Heterogeneous Program- |    |

|      | ming model                                                    | 75 |

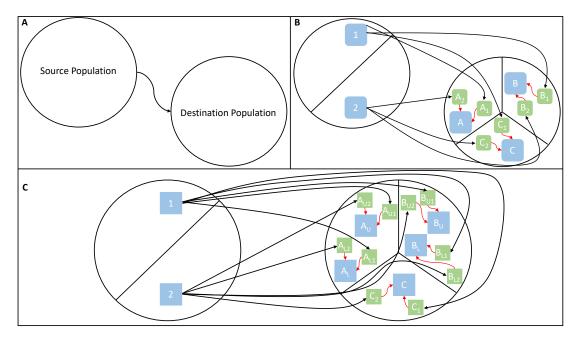

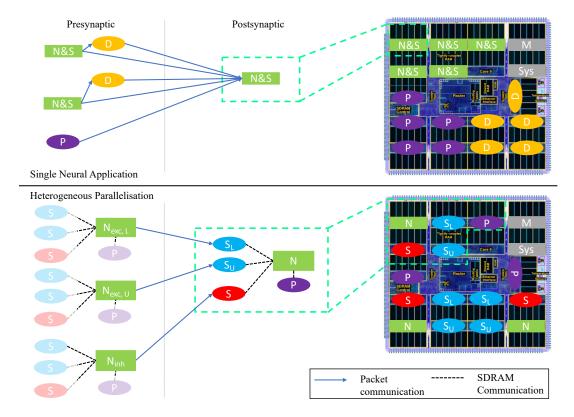

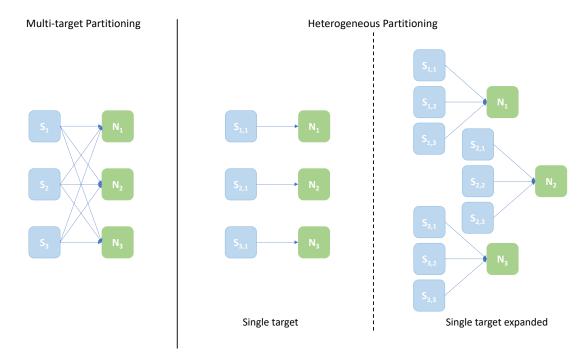

| 3.2  | Heterogeneous Programming Model partitioning                  | 78 |

| 3.3  | Heterogeneous Programming Model placement                     | 80 |

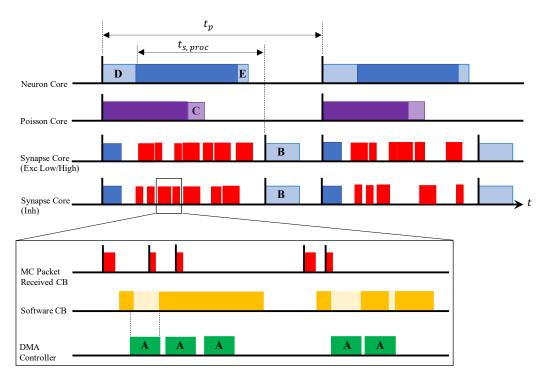

| 3.4  | Heterogeneous Programming model scheduling                    | 83 |

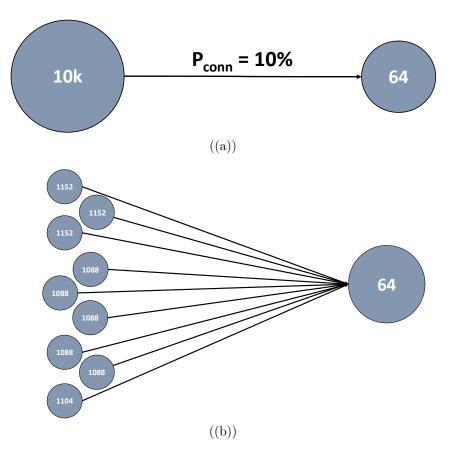

| 3.5  | Heterogeneous Programming Model Test Network                  | 86 |

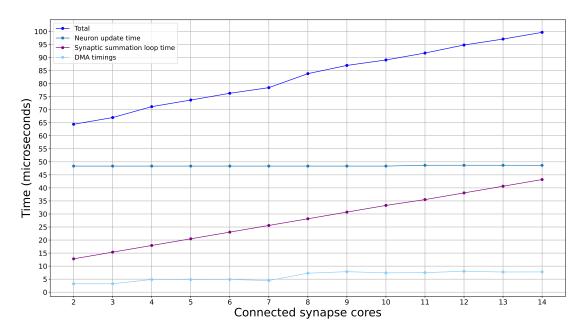

| 3.6  | The Neuron core Performance                                   | 88 |

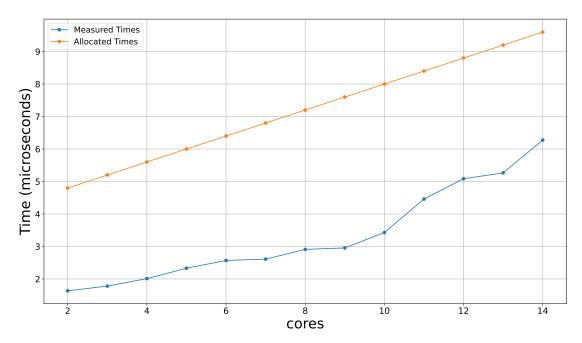

| 3.7  | DMA write latency                                             | 91 |

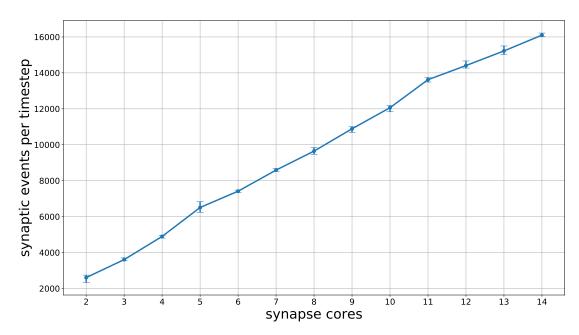

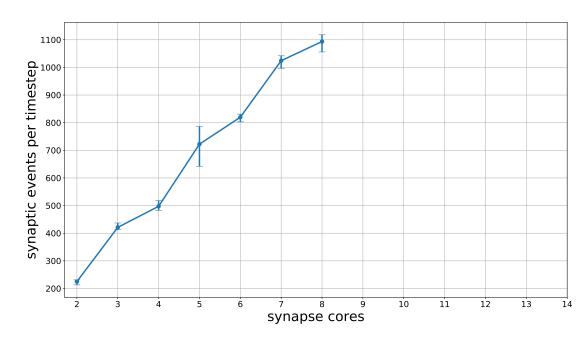

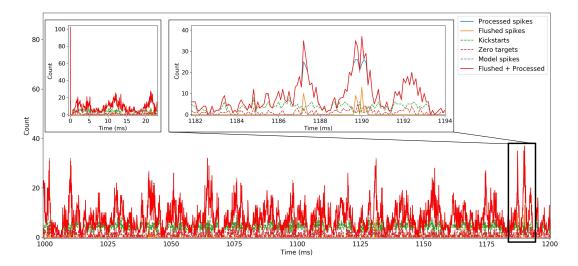

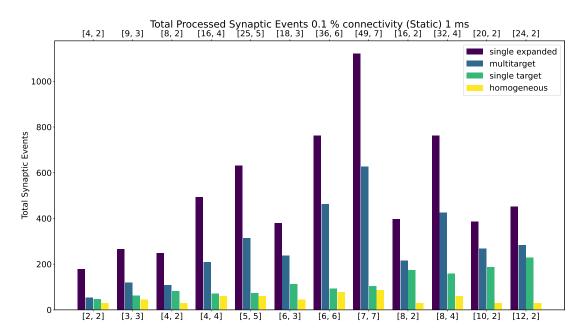

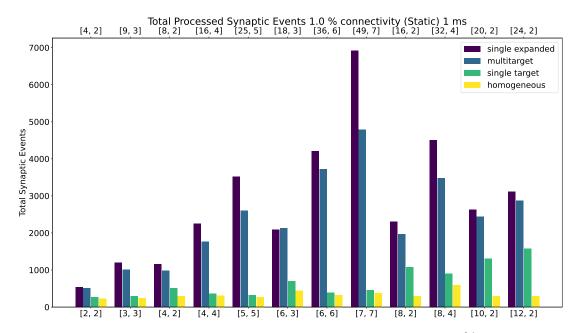

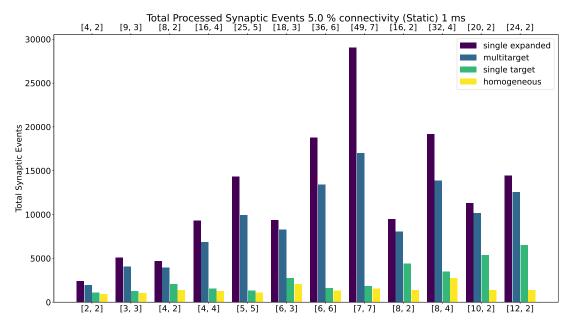

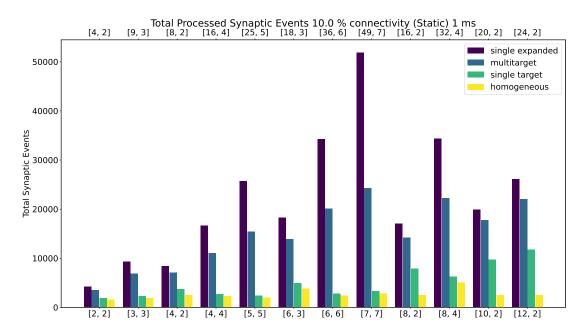

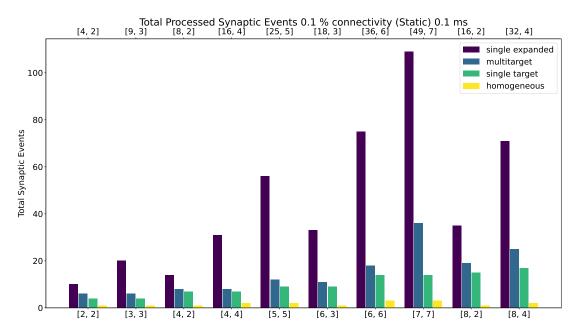

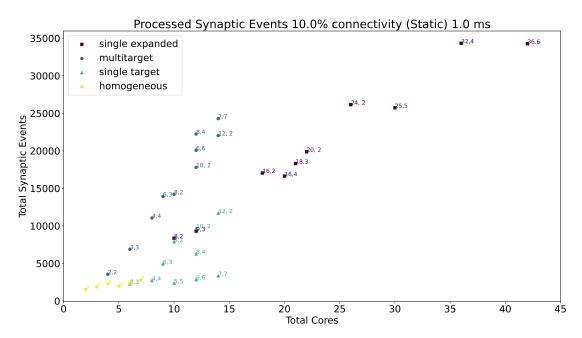

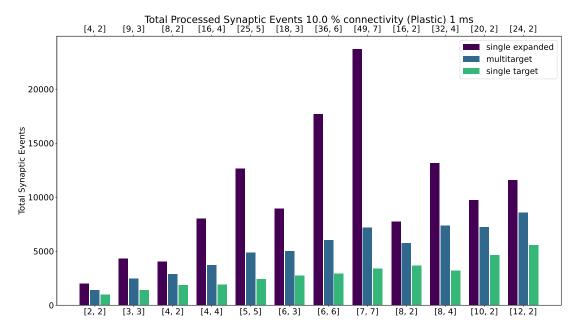

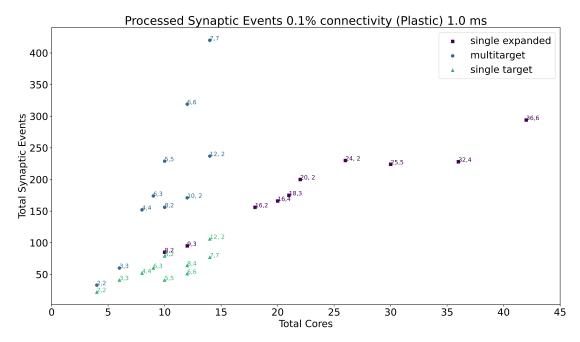

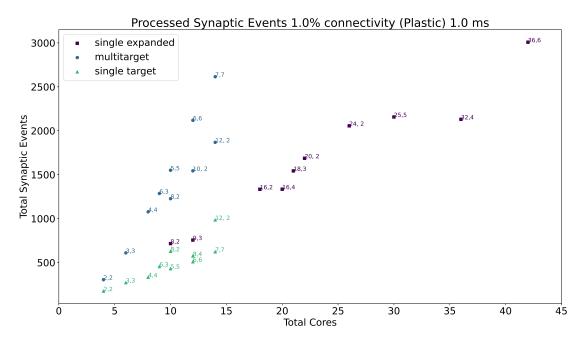

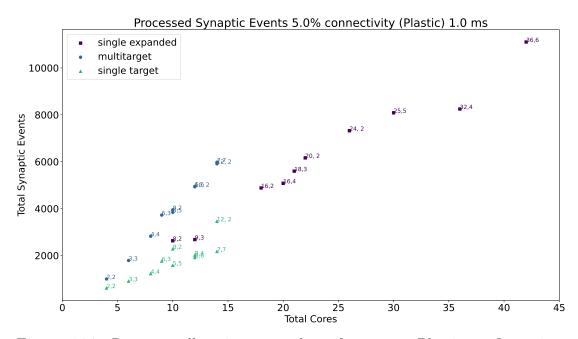

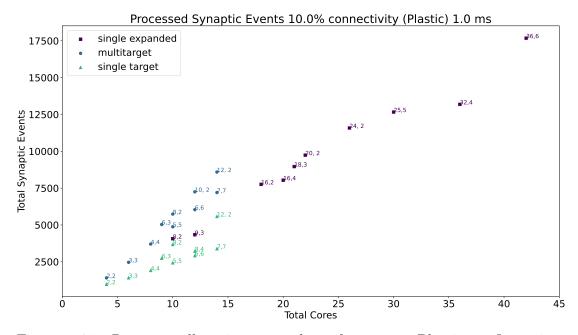

| 3.8  | Processed Synaptic Events 1 ms Timestep                       | 92 |

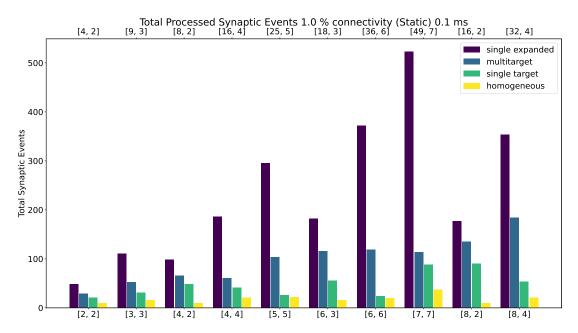

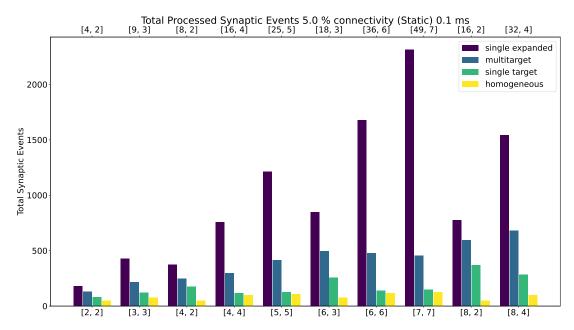

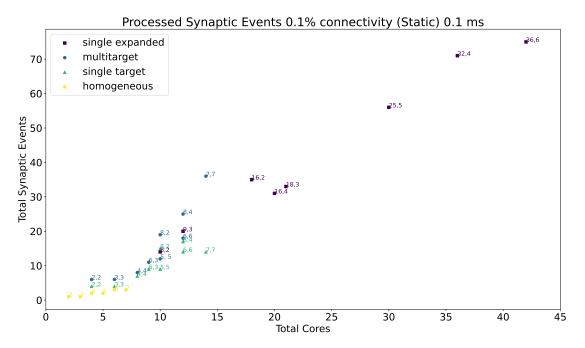

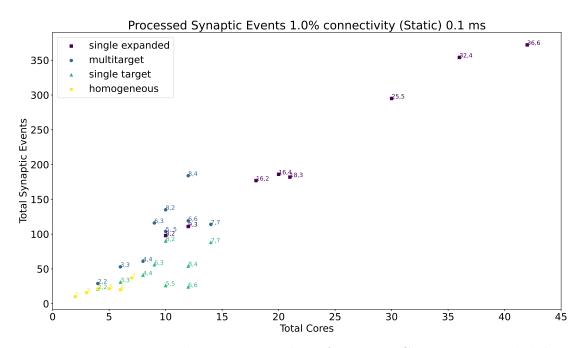

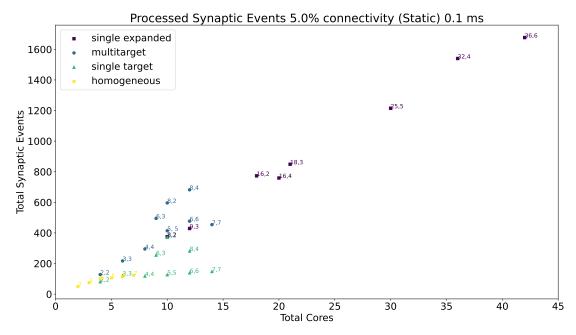

| 3.9  | Processed Synaptic Events 0.1 ms Timestep                     | 93 |

|      | Trocessed Synaptic Events of this Thiestep                    | 00 |

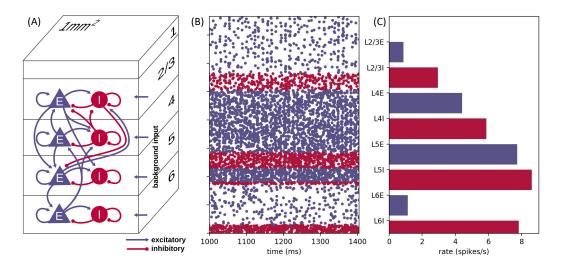

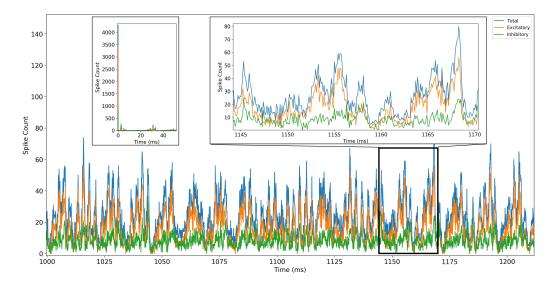

| 3.10 | · · · · · · · · · · · · · · · · · · ·                         | 95 |

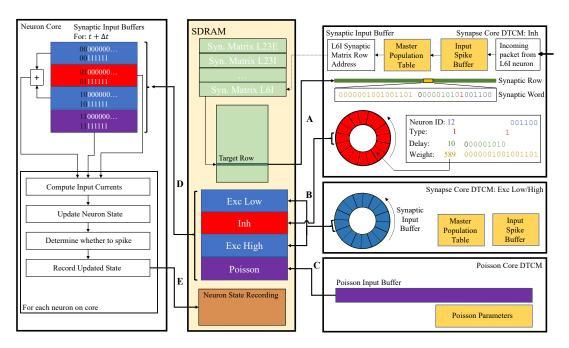

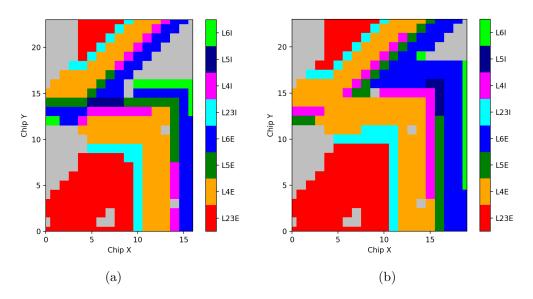

| 3.12 | Application Cores mapping for the Cortical Microcircuit Model . 1    | 101 |

|------|----------------------------------------------------------------------|-----|

| 3.13 | Callback interactions for the real-time execution of the Cortical    |     |

|      | Microcircuit                                                         | 103 |

| 3.14 | Memory use and data structures for the Cortical Microcircuit Model 1 | 04  |

| 3.15 | Synapse core Profiling Cortical Microcircuit                         | 106 |

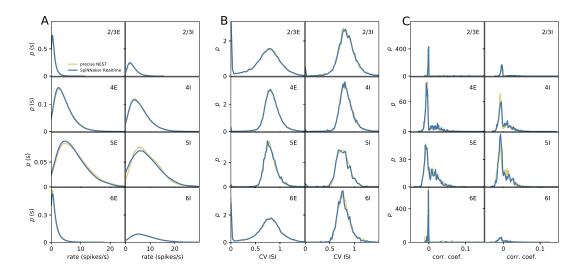

| 3.16 | Cortical Microcircuit comparison between NEST and SpiNNaker . $$ 1   | 108 |

| 3.17 | Cortical Microcircuit Placements on SpiNNaker                        | 109 |

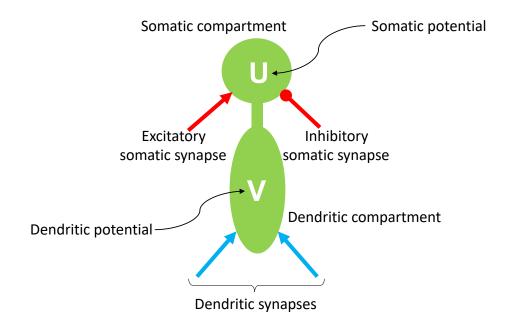

| 4.1  | The Urbanczik-Senn neuron model                                      | l15 |

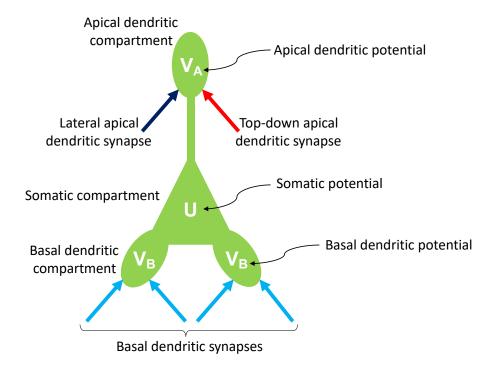

| 4.2  | The 3-compartment pyramidal neuron model                             | 119 |

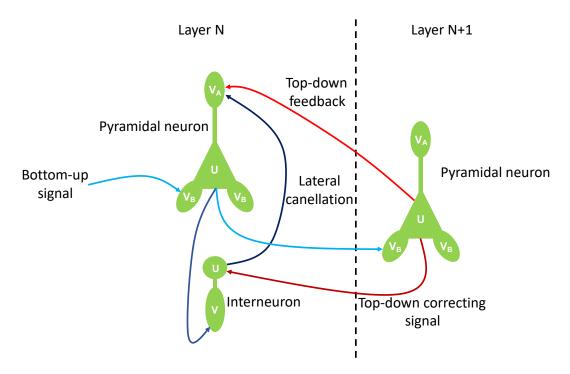

| 4.3  | Schematic of the Self-predicting learning mechanism                  | 122 |

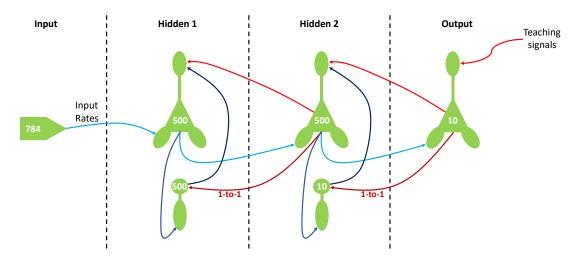

| 4.4  | Topology of the MNIST microcircuit                                   | 124 |

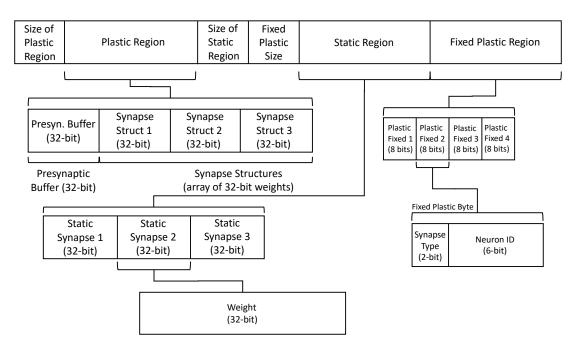

| 4.5  | Updated DTCM synaptic row structure                                  | 128 |

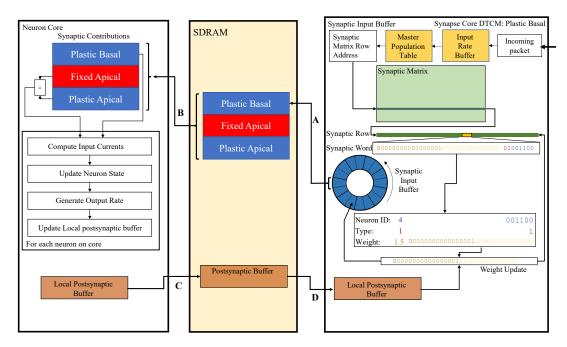

| 4.6  | Memory usage and data structures for the pyramidal model $$ 1        | 129 |

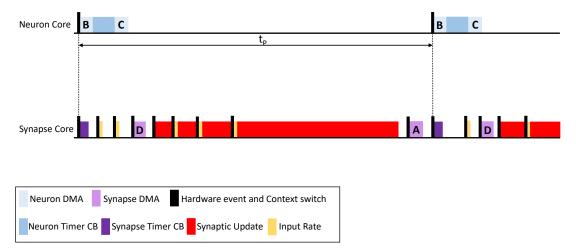

| 4.7  | Callbacks interaction for the pyramidal model                        | 131 |

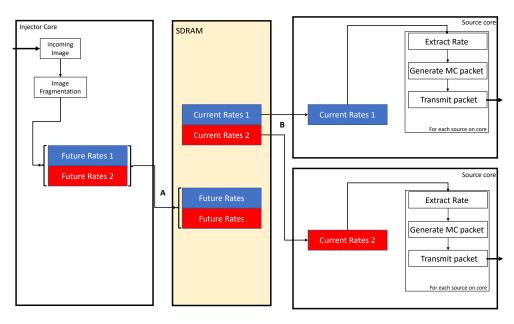

| 4.8  | Memory Usage for the Rate Live Injector                              | 133 |

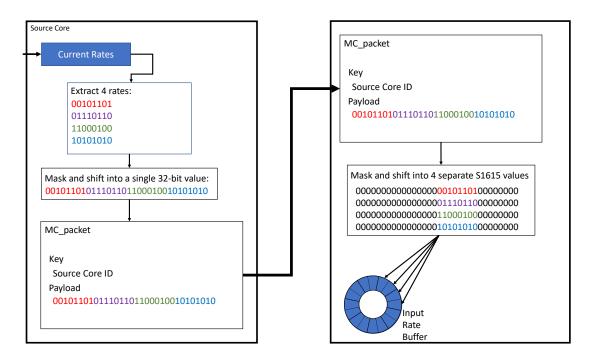

| 4.9  | Packet compression mechanism                                         | 135 |

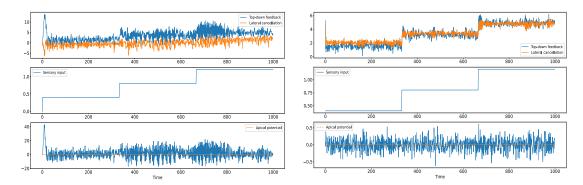

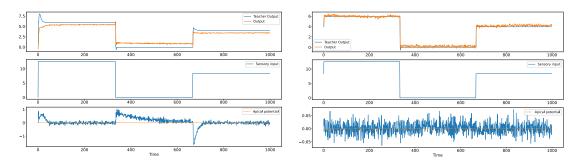

| 4.10 | Urbanczik-Senn plasticity experiment                                 | 136 |

| 4.11 | Dendritic Microcircuit learning rule on SpiNNaker                    | 138 |

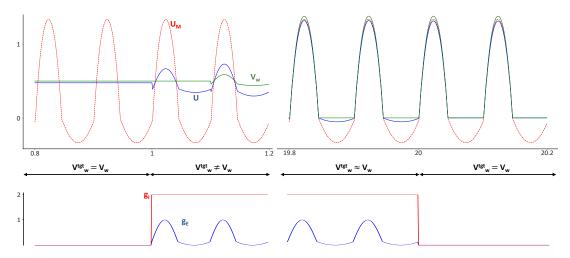

| 4.12 | Self predicting state simulation on SpiNNaker                        | 139 |

| 4.13 | Nonlinear regression task on SpiNNaker                               | 141 |

| 5.1  | Synaptic matrix partitioning under the Multi-Target approach 1       | 147 |

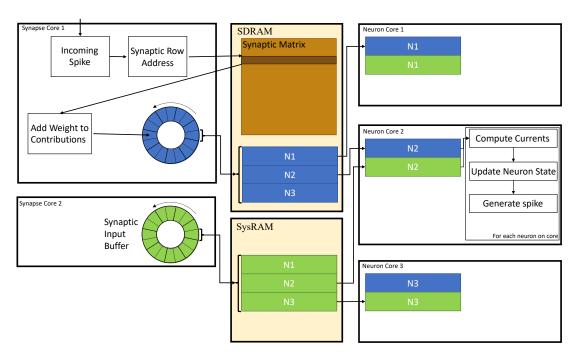

| 5.2  | Memory usage and data structures for the static Multi-Target par-    |     |

|      | titioning                                                            | 152 |

| 5.3  | Multi-target Synaptic Contribution Summation                         | 155 |

| 5.4  | Memory usage and data structures for the plastic Multi-Target        |     |

|      | partitioning                                                         | 156 |

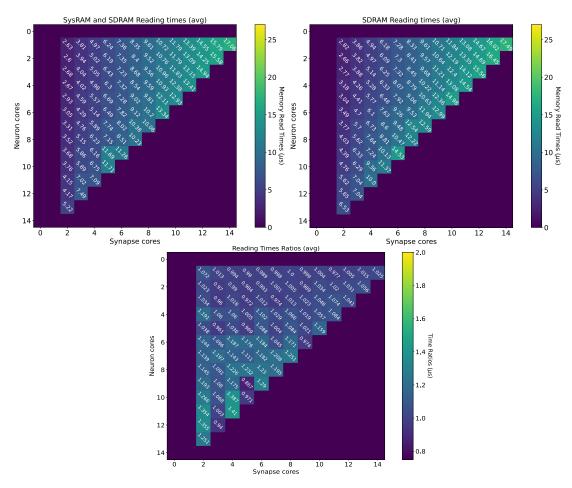

| 5.5  | Max time Reading Memory Benchmarking                                 | 159 |

| 5.6  | Min time Reading Memory Benchmarking                                 | 161 |

| 5.7  | Average time Reading Memory Benchmarking                             | 162 |

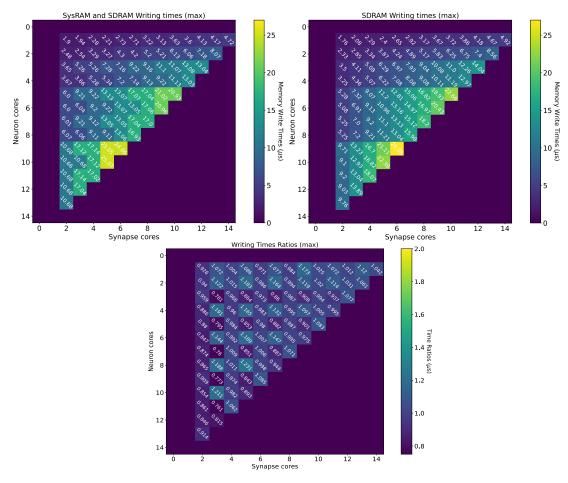

| 5.8  | Max time Writing Memory Benchmarking                                 | 64  |

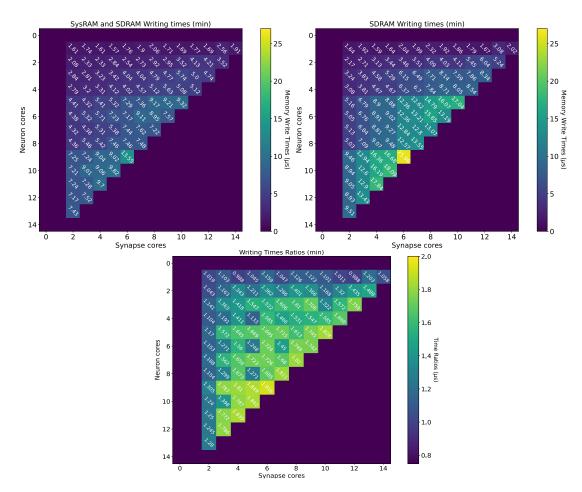

| 5.9  | Min time Writing Memory Benchmarking                                 | 165 |

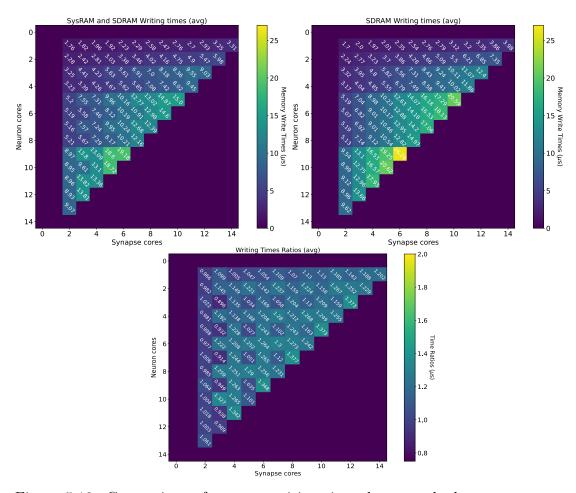

| 5.10 | Average time Writing Memory Benchmarking                             | 166 |

| 5.11 | Cores arrangement for the Multi-target peak processing experiment 1  | .68 |

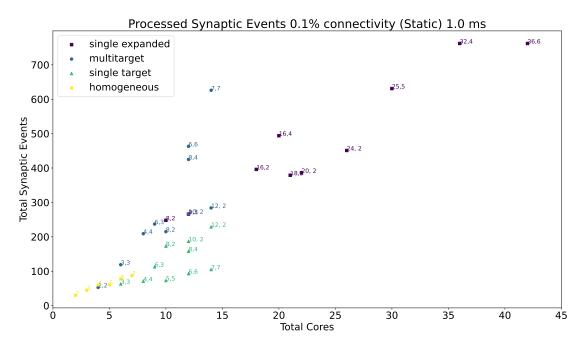

| 5.12 | Peak Processing Experiment Static 0.1%, 1 ms timesteps               | 72  |

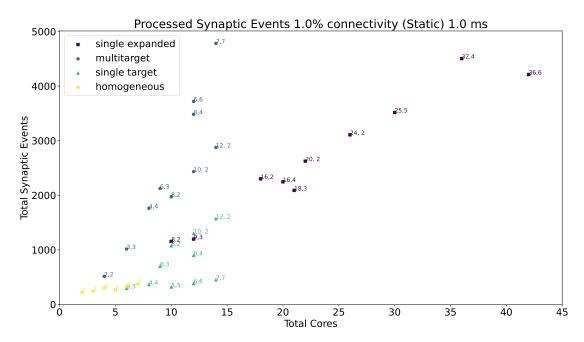

| 5.13 | Peak Processing Experiment Static 1%, 1 ms timesteps                                            | 173 |

|------|-------------------------------------------------------------------------------------------------|-----|

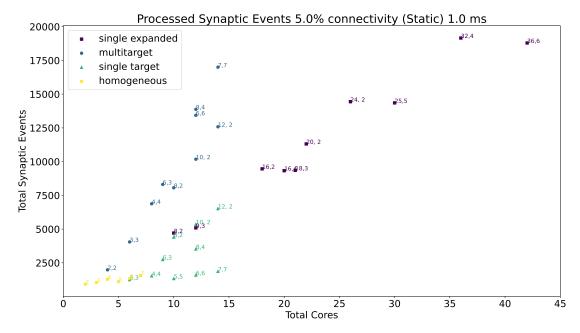

| 5.14 | Peak Processing Experiment Static 5%, 1 ms timesteps                                            | 173 |

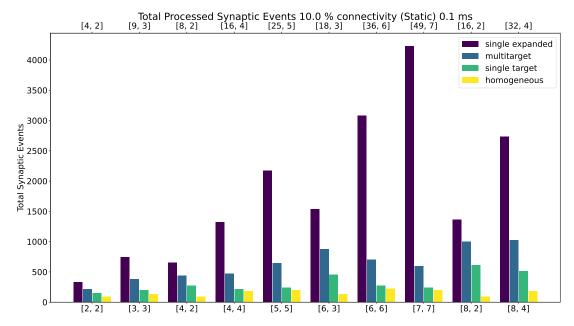

| 5.15 | Peak Processing Experiment Static 10%, 1 ms timesteps $\dots$                                   | 174 |

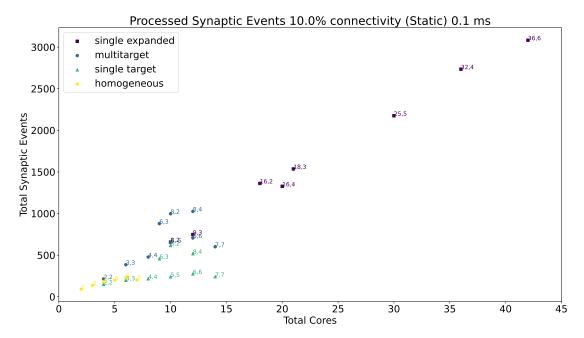

| 5.16 | Peak Processing Experiment Static 0.1%, 0.1 ms timesteps                                        | 175 |

| 5.17 | Peak Processing Experiment Static $1\%$ , $0.1$ ms timesteps                                    | 176 |

| 5.18 | Peak Processing Experiment Static 5%, 0.1 ms timesteps                                          | 177 |

| 5.19 | Peak Processing Experiment Static 10%, 0.1 ms timesteps $$                                      | 177 |

| 5.20 | Resource allocation vs peak performance 0.1%, 1 ms time<br>steps $$                             | 178 |

| 5.21 | Resource allocation vs peak performance 1%, 1 ms time<br>steps $$ . $$ .                        | 179 |

| 5.22 | Resource allocation vs peak performance 5%, 1 ms time<br>steps                                  | 179 |

| 5.23 | Resource allocation vs peak performance $10\%,1$ ms timesteps                                   | 180 |

| 5.24 | Resource allocation vs peak performance 0.1%, 0.1 ms time<br>steps $% \left( 0.1\right) =0.1$ . | 180 |

| 5.25 | Resource allocation vs peak performance $1\%,0.1~\mathrm{ms}$ timesteps                         | 181 |

| 5.26 | Resource allocation vs peak performance $5\%,0.1~\mathrm{ms}$ timesteps                         | 181 |

| 5.27 | Resource allocation vs peak performance $10\%,0.1$ ms timesteps .                               | 182 |

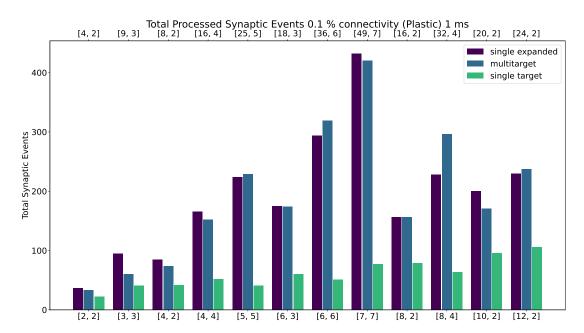

| 5.28 | Peak Processing Experiment Plastic 0.1%                                                         | 183 |

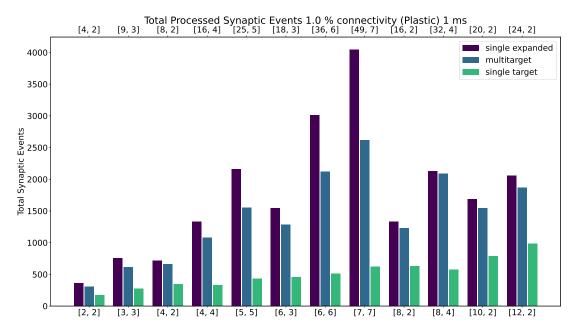

| 5.29 | Peak Processing Experiment Plastic 1%                                                           | 184 |

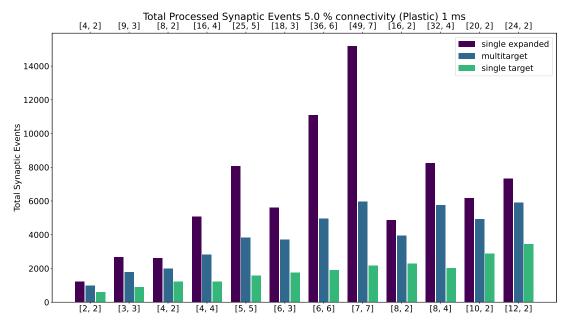

| 5.30 | Peak Processing Experiment Plastic 5%                                                           | 184 |

| 5.31 | Peak Processing Experiment Plastic $10\%$                                                       | 185 |

| 5.32 | Resource allocation vs peak performance plastic $0.1\%$                                         | 185 |

| 5.33 | Resource allocation vs peak performance plastic $1\%$                                           | 186 |

| 5.34 | Resource allocation vs peak performance plastic $5\%$                                           | 187 |

| 5.35 | Resource allocation vs peak performance plastic $10\%$                                          | 187 |

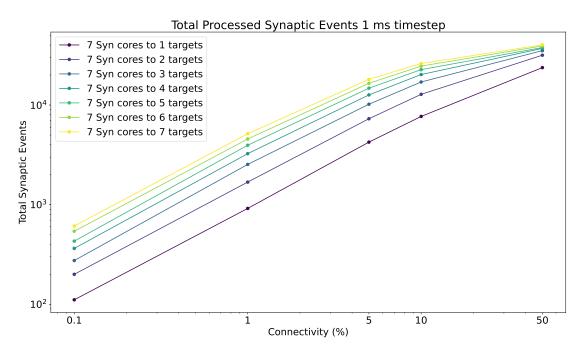

| 5.36 | Sparsity Experiment 1 ms                                                                        | 188 |

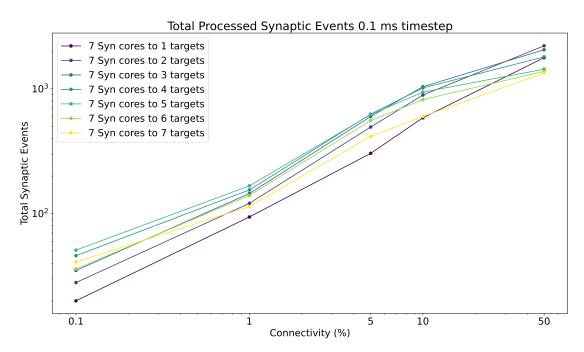

| 5.37 | Sparsity Experiment 0.1 ms                                                                      | 189 |

## Glossary

**AER** Address Event Representation. 46, 59

AI Artificial Intelligence. 33

ANN Artificial Neural Network. 32, 124

**API** Application Programming Interface. 41, 42, 54, 55, 68, 73, 76, 100, 153

ARM Advanced RISC Machine. 47, 48, 56, 196

ASIC Application Specific Integrated Circuit. 39, 43

CNN Convolutional Neural Network. 43

CPU Central Processing Unit. 40, 41, 43

**DDR** Double Data Rate. 151

**DMA** Direct Memory Access. 49, 66, 76, 82, 83, 88–90, 92, 102, 127, 128, 130, 153, 158

**DNN** Deep Neural Network. 43

**DTCM** Data Tightly-Coupled Memory. 49, 61, 65, 69, 74, 101, 128

FIQ Fast Interrupt Queue. 55

FPGA Field Programmable Gate Array. 42, 51, 111, 141

FPU Floating Point Unit. 117

GALS Globally Asynchronous Locally Synchronous. 47

**GPU** Graphic Processing Unit. 42, 43, 98, 99, 108, 110, 111, 188

**HBP** Human Brain Project. 28

**HPC** High-Performance Computing. 40, 41, 98, 99, 108, 110, 111

**IoT** Internet of Things. 197

IRQ Interrupt ReQuest. 55

**ISR** Interrupt Service Routine. 55

ITCM Instruction Tightly-Coupled Memory. 49, 54

LIF Leaky Integrate-and-Fire. 36, 95, 158, 169

LSB Least Significant Bit. 64, 104

LTD Long Term Depression. 37

LTP Long Term Potentiation. 37

ML Machine Learning. 32

MLP Multi Layer Perceptron. 32

MNIST Modified National Institute of Standards and Technology database. 124, 125, 128, 132, 134, 135, 141, 194

MPI Message Passing Interface. 41, 42

MSB Most Significant Bit. 104

**NEST** NEural Simulation Tool. 40, 42, 111

$\mathbf{NoC}$  Network-on-Chip. 47, 151, 196

RNN Recurrent Neural Network. 34

ROLLS Reconfigurable On-Line Learning Spiking Neuromorphic Processor. 45

**SARK** SpiNNaker Application Runtime Kernel. 54

SC&MP SpiNNaker Control Monitor Program. 54

- **SDRAM** Synchronous Dynamic Random Access Memory. 48, 49, 53, 54, 61, 63, 64, 66, 69, 73, 82, 83, 90, 91, 102, 128, 130, 132, 147, 150, 151, 153, 154, 156–158, 160, 163, 166, 167, 183, 196

- **SNN** Spiking Neural Network. 25, 27–30, 33, 34, 36, 39–41, 43, 47, 51, 54, 56, 59, 61, 64, 70–72, 74, 77, 85, 97, 98, 110, 111, 113, 117, 125, 127, 142, 145, 146, 148, 155, 157, 158, 160, 167, 169, 171, 174, 175, 189, 191, 193, 194, 196, 197

- **SpiNNaker** Spiking Neural Network Architecture. 26, 29, 30, 32, 47, 48, 50, 51, 53–57, 59, 61, 64, 69–74, 76, 77, 79, 84, 85, 90, 91, 93, 98–102, 104, 107–111, 113, 114, 117, 118, 120, 124–126, 128, 131, 132, 134–137, 139, 141, 142, 146, 149–153, 157, 160, 162, 169–171, 176, 190, 193, 194, 196

STDP Spike-Timing Dependent Plasticity. 37, 42, 45–47, 118

UDP User Datagram Protocol. 53

US Urbanczik-Senn. 117, 119–122, 137

#### Abstract

#### Parallelisation of Neural Processing on Neuromorphic Hardware Luca Peres

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy, 2022

Learning and development in biological brains typically happen over long timescales, making experimental exploration at the level of individual neurons challenging. Computer simulations of Spiking Neural Network (SNN) models offer a potential route to investigate these phenomena. Accelerating large-scale brain simulations on conventional hardware however is a challenge. Researchers therefore need efficient simulation tools and platforms to complete these tasks in real- or sub real time, to enable exploration of features such as long-term learning and neural pathologies over meaningful periods. Neuromorphic engineering aims to provide suitable platforms for such tasks by building architectures whose structures emulate the mammalian brain and therefore to reduce the time and energy impact that Neural Networks simulations have on standard computing platforms. In order to perform real-time simulations of biologically representative Spiking Neural Networks however, digital Neuromorphic platforms need innovative programming paradigms to best exploit their hardware features. This research explores parallelisation strategies for neural applications to address real-time simulations of SNNs, including on-line learning strategies, with the aim of maximising the throughput of neural operations.

This work employs the many-core SpiNNaker digital Neuromorphic hardware as a research platform, and proposes strategies that enabled the world's first

real-time simulation of the Cortical Microcircuit model, a benchmark SNN describing the behaviour of the mammalian cortex, achieving performance  $20\times$  better than previously published results. The parallelisation strategies are then extended and generalised to on-line learning applications, involving the use of multicompartmental neuron models for classification and regression tasks. Finally, new partitioning strategies affecting the placement of neural components on Neuromorphic hardware are presented. These strategies make more efficient use of the available hardware features, effectively reducing the required resources and providing additional flexibility in order to handle sparser SNNs simulations. Through this final development, up to  $9\times$  higher throughput of neural operations is demonstrated, together with improved handling of biologically-representative sparse connectivity patterns.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=487), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

A PhD is a long journey which sets new challenges every day. In this journey I have been extremely lucky to find the best guidance possible. First of all I would like to thank Professor Steve Furber for his supervision throughout these three years and for believing in me even during the most challenging phases.

I am extremely thankful to my co-supervisor Dr. Oliver Rhodes for his invaluable guidance, not only for my professional development, but also for being the best mentor I could ask for on the personal side. I wouldn't have made it this far without him.

I would like to thank the EPSRC and The University of Manchester for funding my PhD and investing in my education.

A big acknowledgment goes to the SpiNNaker team for providing all the necessary support with the platforms and tools. Particularly I would like to thank Andrew Rowley, Luis Plana, Andrew Gait, Christian Brenninkmeijer and Donal Fellows. An important thank goes to my fellow PhD studens who helped me through this long journey always cheering me up when I needed it: Adam Perrett, Edward Jones, Sara Summerton and Mollie Ward. A special acknowledgment goes to Mark Kynigos for our very helpful coffee breaks during which we pushed each other to keep up writing.

Finally, I would like to thank my friends and family for all the patience and support 1000 miles away and for always being so available I felt they were here with me: Alessandro Zanotto, Marco Caporaso and Fulvia Barolo.

## Chapter 1

### Introduction

#### 1.1 Motivation

Networks of neurons allow the brain to perform tasks such as learning, inference and motor control reliably and with limited energy consumption [HH11]. However, simulating such tasks is non-trivial, as long-range connectivity and sparse temporal signals, typical of biologically-representative Spiking Neural Networks (SNNs), make traditional communication mechanisms inefficient [FMCR19].

Conventional computer hardware is therefore not suited to perform such tasks, as the communication cost dominates performance, scaling nonlinearly with neural network size, slowing down simulations and increasing the energy consumption of the underlying simulator [vARS<sup>+</sup>18, IEPD17]. Alternatives have been proposed to address these challenges, including Neuromorphic engineering [TMC<sup>+</sup>18], an emerging field which aims at building machines by taking inspiration from the mammalian brain. Various platforms and technologies [CDLB+22] have been developed with the ultimate goal of performing real-time simulations of complex biologically-representative Spiking Neural Networks (SNNs). These aim at better understanding the biological mechanisms which regulate activities such as learning, memory and cognitive tasks on the one side and at finding alternative architectures in order to overcome the end of Moore's law [Moo06] on the other [SKP<sup>+</sup>22]. Neuromorphic systems approach SNN simulations from a different perspective, compared to conventional hardware [ILBH+11], by being power efficient and architecturally similar to neural networks. They furthermore provide great scalability capabilities, overcoming the communication bottleneck of conventional hardware. Although looking promising, these architectures still struggle to achieve the needed performance on more complex simulations. The reasons can often be found in sub-optimal exploitation of the hardware resources and in the lack of targeted programming models for these unique architectures [vARS+18]. These machines are therefore far from their potential, as demonstrated by cases such as SpiNNaker, where no biologically-plausible network has been simulated employing the full one-million core machine to date.

This work aims to address these issues by researching programming paradigms based on parallelisation of neural processing on digital Neuromorphic hardware, in order to bridge the gap in communication between the neuroscientific community and computer architects. The target of this research is therefore to optimise neural network simulations, by performing a more efficient use of the available hardware resources, and highlight the weaknesses of such systems, in order to inform the design of the next generation of Neuromorphic hardware.

#### 1.2 Research Questions

The main hypotheses constituting the foundation of this work are presented here in the form of research questions:

- 1. How can the process of mapping biologically-representative SNNs be optimised on Neuromorphic Hardware?

- 2. What are the challenges of implementing on-line learning algorithms in real time on Neuromorphic hardware?

- 3. How can the brain's sparse connectivity and activity be modelled efficiently on Neuromorphic hardware?

#### 1.3 Contributions

The research presented in this manuscript addresses the questions formulated in Section 1.2. The contributions provided by this work are here summarised:

1. The Cortical Microcircuit network [PD12], commonly regarded as benchmark in the neuroscience field, was used as a vehicle to explore neural models and connectivity patterns, typical of biologically-representative SNNs. Detailed profiling and optimisations are here presented, together with the first

real-time Neuromorphic simulation of the SNN, constituting a  $20 \times$  speedup compared to previously published results. This contribution is addressed in detail in Chapter 3.

- 2. Challenges and limitations related to the implementation of on-line learning algorithms in real time on Neuromorphic hardware are explored, further improving the developed software framework to include multicompartmental neural modelling and rate-based densely-connected SNNs. This contribution is addressed in Chapter 4.

- 3. Brains' levels of connectivity, fan-in and neuron density, are explored, providing a new efficient SNN placement methodology for digital Neuromorphic hardware, which enables efficient simulations of biologically-representative sparsity levels. This approach achieved a reduction in required hardware resources and up to 9× neural operations throughput compared to previous methodologies. This contribution is addressed in detail in Chapter 5.

#### 1.4 Publications

Most of the work presented in this thesis has been submitted for publication and is available in various forms:

#### • Journal Articles

- Oliver Rhodes, Luca Peres, Andrew G. D. Rowley, Andrew Gait, Luis A. Plana, Christian Brenninkmeijer, and Steve B. Furber. Real-time cortical simulation on neuromorphic hardware. Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences, 378, Dec 2019 this article summarises the work presented in Chapter 3.

- Luca Peres and Oliver Rhodes. Parallelization of Neural Processing on Neuromorphic Hardware. Frontiers in Neuroscience, 16, May 2022

this article constitutes the work presented in Chapter 5.

#### Posters

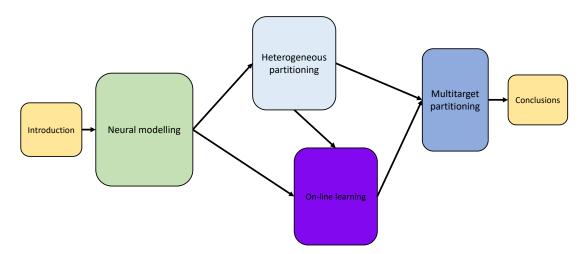

Figure 1.1: Thesis Structure. Each box corresponds to a chapter, while the arrows indicate the relations between chapters.

Luca Peres, Oliver Rhodes (2020) "Real-time cortical simulation on SpiNNaker". figshare. Poster. https://doi.org/10.6084/m9. figshare.17086667.v1 [PR20]

#### 1.4.1 External Coverage

The published work described in Chapter 3 received coverage from the general press and was addressed in the 12th October 2019 issue of the New Scientist [Gen19] magazine. The same work was cited among the biggest achievements during the introductory keynote at the Human Brain Project (HBP) Summit in Athens in February 2020.

#### 1.5 Thesis Structure

This thesis is composed of 6 chapters in total. Its structure is shown in Figure 1.1. Each box indicates a topic which maps to a specific chapter in this manuscript and the arrows indicate the relations between them.

This chapter describes the motivations and the research questions addressed in this work. Chapter 2 (Neural Modelling) provides an overview of the field and the necessary background to understand this work. Chapter 3 (Heterogeneous partitioning) describes a parallelisation approach to improve SNN simulations on Neuromorphic hardware. Chapter 4 (On-line learning) expands this approach to biologically-plausible learning strategies. Chapter 5 (Multi-target

partitioning) combines the previous developments and presents an evolved parallelisation method, achieving optimal performance and including additional edge cases. Chapter 6 (Conclusions) summarises the research and discusses potential future work.

#### 1.5.1 Chapter 2

Chapter 2 serves as a background on Spiking Neural Networks and neural modelling, providing the reader with the information necessary to understand the work. The initial focus is on the evolution of neural networks over the years, with emphasis on Spiking Neural Networks, spiking neuron models and plasticity rules. An overview of simulation platforms is also provided, showing the available options on the market. Neuromorphic hardware is addressed in more detail and chosen as target hardware for this research. Finally, a detailed descritpion of the SpiNNaker Neuromorphic platform is provided as the main platform used for this work.

#### 1.5.2 Chapter 3

Chapter 3 addresses the first research question, and presents the development and application of a parallelisation strategy, namely the Heterogeneous Programming model, on digital Neuromorphic hardware. This programming model targets real-time simulations of biologically-representative SNNs, and achieved the first real-time simulation [RPR<sup>+</sup>19] of the Cortical Microcircuit network [PD12], a well-known benchmark in the field of computational neuroscience. To date, this represents the only complete Neuromorphic simulation of the network.

#### 1.5.3 Chapter 4

Chapter 4 addresses the second research question, and expands the approach presented in Chapter 3 by applying it to a different context, targeting on-line learning [LDBK20] challenges. Multicompartmental neuron models from the literature are presented and simulated on SpiNNaker and the novel parallelisation strategy is adapted to a rate-based context. Performance of this new implementation is then tested in real-time supervised learning problems.

#### 1.5.4 Chapter 5

Chapter 5 addresses the third research question and builds on the knowledge acquired from Chapters 3 and 4 to build an optimised framework which can adapt to support simulations of various ranges of SNNs: from extremely sparse connectivity patterns to denser networks, including support for biological learning mechanisms defined by plasticity rules. This method shows unprecedented throughput of neural operations and a reduction in the required hardware resources for a given simulation [PR22].

#### 1.5.5 Chapter 6

Chapter 6 presents the conclusions of the thesis, summarising the research outcomes and providing insights for potential future work.

#### 1.6 Summary

This thesis focuses on the development of parallelisation techniques to achieve real-time simulations of biologically-representative Spiking Neural Networks on Neuromorphic hardware. This is achieved by performing a more efficient use of the available hardware resources. First, the context is provided through a description of the relevant fields and the available tools. An implementation of a parallelisation technique is then provided for the SpiNNaker Neuromorphic platform, together with its extensions to different contexts and forms. Finally the results are presented together with considerations about future work.

## Chapter 2

## Neural Modelling and Dedicated Hardware

#### 2.1 Introduction

The human brain is a complex system able to perform learning tasks efficiently with extremely low energy cost [LC20]. However, replicating such behaviour on conventional computer hardware is challenging, due to a lack of complete understanding of brain functioning and to inadequate simulation architectures. Both the neuroscientific and computer science communities are investing considerable effort in achieving full brain simulations, on the one side by providing biologically-representative models and on the other side by building dedicated hardware to simulate such models efficiently. This chapter presents an introduction to biologically-inspired neural network simulation and to the available platforms on the market to perform this task. This constitutes the background necessary to introduce the research presented in this thesis. Section 2.2 presents a description of neural networks and their structure, with focus on biologicallyinspired networks. A description of spiking neuron models and biological learning mechanisms - such as synaptic plasticity - is provided, concluding with an introduction to neural compartments and multicompartment neuron models. Section 2.3 describes the tools and techniques used to simulate neural networks, both from hardware and software perspectives, providing evaluation of the advantages and tradeoffs of every solution. Section 2.4 presents a more detailed description of Neuromorphic platforms as dedicated hardware simulators which mimic the structure of the brain. Section 2.5 contains a detailed description of the

SpiNNaker Neuromorphic system, the chosen platform for this research, together with hardware and software features, and how neurons and neural networks are simulated on it.

#### 2.2 Neurons and Neural Networks

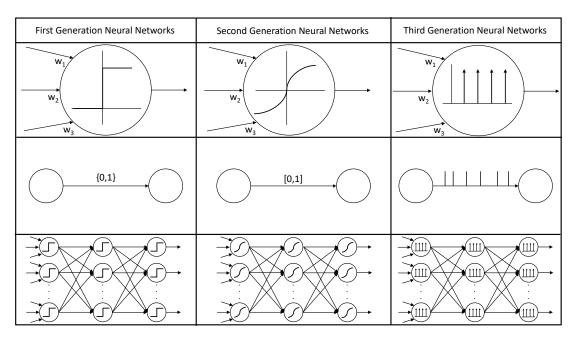

Neural networks are circuits of neurons, which take inspiration from biology. The term takes its roots in the attempt to find mathematical representations of information processing in biological systems [Bis06]. Neural networks are gaining popularity in the field of Computer Science, thanks to the reduction in computational power consumption and advances in parallel computing paradigms, together with a larger presence of high quality databases and training sets [GBC16]. The most popular type of neural network is called Artificial Neural Networks (ANNs), which in general are circuits of artificial neurons. ANNs are a broad class employed in several Machine Learning (ML) tasks and commonly used by commercial applications in fields such as pattern recognition and inference. The basic building blocks of neural networks are neurons, which can be modeled following different abstraction levels from the biological neurons, according to the type of application. Multiple generations of neural networks have been proposed to date and they change according to the implemented type of neuron and connectivity. Figure 2.1 shows the evolution of neural networks through generations. The first row represents the neuron models employed by each generation, the second row shows how neurons interact with each other and the third row shows networks of neurons.

The first generation (shown in the first column in Figure 2.1), evolving from the first developed artificial neuron model (the McCulloch-Pitts neuron [MP43]), employed a computational model called the Perceptron [Ros58]. This sums together the input weights  $(w_1, w_2 \text{ and } w_3 \text{ in Figure 2.1 top left})$  and then performs a threshold step function on the result of the sum. The output assumes binary values only. Multilayer combinations of these units generate networks called Multilayer Perceptrons (MLP) [Maa97].

The second generation (middle column in Figure 2.1) makes use of artificial neurons employing continuous nonlinear activation functions (such as the sigmoid function [Mey01]) to transform the inputs and generate real-valued outputs. This, from a biological interpretation of neural networks, corresponds to a

Figure 2.1: Neural networks generations. Each column shows a generation of neural networks, including Multilayer Perceptrons (left column), ANNs (central columns) and SNNs (right column). The first row contains the type of neuron employed by each generation, the second row the communication model and the third row the network structure.

representation of the current firing rate of a biological neuron [Maa97]. The activation function is applied, similarly to the first generation of neural networks, to a weighted versionsum of the inputs. Second generation neural networks support learning algorithms based on gradient descent, such as Error Backpropagation [RHW86, Maa97]. This generation is currently the most popular in the Artificial Intelligence (AI) field, being the basis of Deep Learning algorithms [GBC16].

Finally, the third generation (third column in Figure 2.1) is referred to as Spiking Neural Networks (SNN). This type of network takes inspiration from real neurons, by using the exact timing of spikes to encode information. This means that neurons do not output mean firing rates, as for the previous generations, but emit spikes at precise times and these times are used to encode information. Spikes (or action potentials) are commonly modelled as events at a precise time, therefore their mathematical representation is the Dirac delta function [Mey01]. SNNs present clear advantages over previous generations, including low power consumption and the capability of processing real-time temporal data. However the development of efficient learning algorithms for them is still at an early stage,

therefore they have not yet fully replaced the previous generations of neural networks [LDC<sup>+</sup>20].

The simplest model of neural network is called feedforward and it is commonly used to approximate a chosen function. The goal for the network is to learn the values of some parameters to find the best approximation of the desired function. This type of network has the information flowing in one direction only (there is no feedback) and the neurons are organised in layers. Therefore at a higher abstraction level, each layer performs a task, and the whole network an algorithm. The most common representation is through a DAG (Directed Acyclic Graph), the first layer is called input layer, the last is the output layer and all the middle layers are called hidden layers [GBC16]. The introduction of feedback connections defines a more complex class of neural network called Recurrent Neural Networks (RNNs), which are employed for more complex tasks involving sequential data processing, such as language translation, natural language processing (NLP) and speech recognition. This type of neural network employs feedback connections to create a form of "memory" of the previous inputs which persists in the network's internal state, influencing the outputs. Additional details about RNNs are left as reference [Gra12].

This work focuses on algorithms and platforms related to SNNs simulations, aiming to provide design methodologies to inform the design of future dedicated hardware and algorithms. The following sections contain descriptions of SNNs and hardware platforms employed to simulate them.

#### 2.2.1 Point Neuron Models

Biological neurons have been modeled through the years at different levels of abstraction, from simple Integrate-and-Fire models [GK02] to the ion channel modeling proposed by Hodgkin and Huxley [HH52]. The common aspect is the spiking nature of these models. Rate-based models, indeed, commonly encode the information through the firing rate of the neurons; spiking models, on the other hand, exploit the timings of the spikes to encode spatial and temporal information. Spikes are typically represented as Dirac delta functions, and the set of emitted spikes is represented by a train of delta functions. Networks of spiking neurons therefore communicate through this pulse-based mechanism, each connection is represented through a strength, commonly called weight and the

inputs come in the form of synaptic currents, where the synapses allow connection between neurons. When two neurons are connected, the source neuron is called presynaptic, while the destination is denominated postsynaptic. A neuron takes its inputs from other presynaptic neurons on tree-like structures called dendrites and the junction between a presynaptic and a postsynaptic neuron is called synapse. The synapses allow the transmission of neurotransmitters between the two neurons. The core part of a neuron is called soma, or cell body, and it is the nucleus of the neuron. In the soma all the input currents are collected. The soma connects to the axon (a projection used to transmit information to other neurons) through a cone-shaped section called axon hillock. This is the generation site for action potentials, which are then propagated through the axon to reach the dendrites of the target neurons (the schematic of spiking neurons is shown in Figure 2.1 right).

Each spike contributes to postsynaptic neurons according to the weight of the connection, and connections can be either excitatory, when they contribute to a postsynaptic spike, or inhibitory, when they are opposed to postsynaptic spiking activity. Learning in SNNs happens through a mechanism called synaptic plasticity, which leads to weight modifications (more details about synaptic plasticity are presented in Section 2.2.2) under specific conditions.

The most basic representation of spiking neurons is given by the Leaky Integrateand-Fire (LIF) model [GK02]. This model represents the neurons as simple electrical RC circuits, having a resistor (R) in parallel with a capacitor (C), driven by a current ( $I_{syn}(t)$ ). The membrane voltage is measured as output voltage and evolves with time according to Equation 2.1, where R is the cell membrane resistance and  $\tau_m$  represents the time constant (and is equal to the product between R and C).

$$\tau_m \frac{dV}{dt} = -(V - V_{rest}) + RI_{syn}(t) \tag{2.1}$$

$$\tau_{syn} \frac{dI_{syn}}{dt} = -I_{syn}(t) + \sum_{j} \delta(t - t_{j})$$

(2.2)

$V_{rest}$  is the resting potential and is the value the membrane voltage converges to when no synaptic input current  $(I_{syn})$  is injected. The model acts in a way that when the membrane voltage reaches a threshold value, it emits a spike and then V is set to the resting potential level for an interval of time called the refractory

period, during which the neuron cannot emit any spike. The current injected into the neuron through its synapses is modeled by Equation 2.2. This is determined by the incoming spikes (represented by the sum of  $\delta$  functions, which include the weight contribution for each activated synapse j) and it is exponentially-shaped.

Another popular point neuron representation is given by the Izhikevich model [Izh03], whose creator claims it to be as biologically-plausible as the Hodgkin-Huxley [HH52] model, but with a complexity comparable to the LIF model [Izh03, Izh04]. The Izhikevich model dynamics are modeled by the two-dimensional system of equations shown in Equation 2.3.

$$\frac{dV}{dt} = 0.04V^{2} + 5V + 140 - U + I(t),

\frac{dU}{dt} = a(bV - U)$$

(2.3)

V and U are dimensionless variables representing membrane potential and a membrane recovery variable of the neurons respectively. I(t) the synaptic current. a and b are dimensionless parameters used to tune the model dynamics and can be configured to modify the neuron spiking behaviour according to simulation conditions [Izh03].

Despite their simplicity compared to biological neurons, point neuron models represent a powerful way to model biologically-plausible SNNs and are nowadays employed in large networks used as benchmarks by the neuroscientific community, such as the Cortical Microcircuit model [PD12], or the more complex multi-area model [SBS<sup>+</sup>18], or even for cerebellar representations [BMC<sup>+</sup>21, CMM<sup>+</sup>19].

#### 2.2.2 Synaptic Plasticity

The process that governs synaptic modification is termed synaptic plasticity and it is believed to be the main learning mechanism in biology, as well as the substrate of memory. Synaptic plasticity is also the main learning mechanism employed in SNNs. Most of the plasticity models originate from Hebb's description of synaptic changes [Heb49], which states that if a neuron's firing activity results in modifications of a connected postsynaptic neuron's firing activity, then some metabolic change happens in one or both the cells which causes the synaptic efficacy to increase. Therefore, correlations in pre- and postsynaptic firing activity drive synaptic modifications. Hebb's theory however does not take into account

the fine temporal structure between pre- and postsynaptic spikes, stressing more on causation, rather than correlation. The discovery of this aspect led to the formulation of modern plasticity rules, in the form of Spike-Timing-Dependent Plasticity (STDP) [MGS12]. Differently from what Hebb thought, according to the temporal dynamics, both increases and decreases can be observed in synapses. These two phenomena are termed Long-Term Potentiation (LTP) and Long-Term Depression (LTD) respectively. An important feature of these rules is that only variables locally available at the synapses can be involved in the synaptic weight update. This means that effects caused by pre- and postsynaptic spikes, alone or in conjunction, and membrane voltage changes are the only parameters that can be taken into account when modeling synaptic plasticity [MDG08]. Several STDP rules have been formulated, which vary according to the neuron models and system type [AN00, BP01]. The most common STDP rule, as well as the simplest, is the pair-based formulation [MDG08]. According to this formulation, when a presynaptic neuron fires and, shortly after, a postsynaptic action potential is generated, then the involved synapse is potentiated, therefore the weight increases. If the opposite situation happens, i.e. a postsynaptic action potential is followed shortly after by a presynaptic spike, the synapse is depressed [BP98]. Therefore, a change in weight, according to pair-based STDP rules, depends on the temporal difference between pairs of pre- and postsynaptic spikes.

$$\Delta w^{+} = F_{+}(w)e^{-\frac{|\Delta t|}{\tau_{+}}} \quad if \ \Delta t > 0$$

$$\Delta w^{-} = -F_{-}(w)e^{-\frac{|\Delta t|}{\tau_{-}}} \quad if \ \Delta t \le 0$$

(2.4)

Equation 2.4 shows the amount of weight modification according to the time difference between a single pair of spikes  $\Delta t = t_j - t_i$ .  $F_+$  and  $F_-$  indicate functions expressing the dependence of the update on the current weight, and  $\tau_+$  and  $\tau_-$  are time constants controlling the time windows over which synaptic modification can happen. A common way to simulate this rule is through a history trace of the spiking activity. This trace can be modeled through exponential decay (this is equivalent to a low-pass filter of the input spike train, therefore the function increases every time a spike arrives and then slowly decreases over time).

$$\frac{ds_i}{dt} = -\frac{s_i}{\tau_s} + \sum_{t_i} \delta(t - t_i) \tag{2.5}$$

The history trace evolution over time is shown in Equation 2.5, where  $s_i$  represents the trace for the synapse i,  $\tau_s$  is the time constant for the synapse and the sum indicates the spike train. By keeping both a pre- and postsynaptic history trace, it is possible to separate the two contributions. Therefore the weight update can be modeled as the sum of two main contributions: a decrease induced by the arrival of a presynaptic spike, which is proportional to the momentary value of the postsynaptic trace, and an increase caused by the generation of a postsynaptic action potential, which is proportional to the presynaptic trace [MDG08].

$$\frac{dw_{ij}}{dt} = -F_{-}(w_{ij})s_{i}(t)\delta(t - t_{j}) + F_{+}(w_{ij})s_{j}(t)\delta(t - t_{i})$$

(2.6)

Equation 2.6 shows the weight update relation for a synapse between a presynaptic neuron j and a postsynaptic neuron i, through an all-to-all pairing scheme.

The choice of the function F(w) indicates the update dependence on the weight [BP98]. The case in which there is no dependence is called additive, and it is the simplest representation. In this formulation, the function F(w) is replaced by a constant, which controls the maximum weight update [MDG08]. Other common weight dependence rules are multiplicative, where the weight update is proportional to the weight itself [RLS01], and power law, where the update is proportional to a power of the weight [MAD07]. Extensions to the pair-based rule have been provided to achieve more accurate results, however these are beyond the scope of this thesis and therefore are available as references [MDG08, PG06, Izh07, AE05].

## 2.2.3 Multicompartment Neuron Models

Section 2.2.1 addressed Spiking neurons in the form of point models. Point neuron models however, represent a simplification of real neurons, by assuming that the membrane potential is constant across the entire cell membrane of the neuron. This theory neglects the nature of dendrites as complex structures, simplifying them to wires carrying signals to the soma of the neuron. This limitation becomes evident in Pyramidal neurons, a type of neuron largely present in the cerebral cortex of most mammals, birds, fish and reptiles [Spr08]. Pyramidal neurons present dendritic trees which can be divided into two main categories: basal and apical dendrites, descending from the base and the apex of the soma respectively [Spr08]. The structure of these dendrites varies, and inputs can have different

effects according to where they are received, which means that different dendritic domains have different integration properties for the inputs [Spr08]. This property does not only apply to different domains, but is also position-dependent: the farther the synapses are from the soma, the lower is their influence on the action potential generation [HM03]. Neurons commonly take advantage of this property to perform complex integrative processing [Spr08]. Multi-compartmental models try to take into account these phenomena by modeling neurons as collections of smaller independent compartments within which the membrane voltage is constant. Compartments are then connected together by passive conductance [HM03]. Different models present different numbers of compartments, ranging from the simplest, which condense the soma, axon and basal dendrites into a single somatic compartment and model the apical dendrites as a separate compartment [HM03], up to 100s of different dendritic compartments [SMKS00, SS01].

Multi-compartment modeling represents a tradeoff between efficiency and accuracy, since these types of models are more complex to simulate and therefore require more computational power, but are closer to biology than point models. A big benefit of multicompartment modeling, however, is given by the chance to build biologically-plausible learning rules, overcoming the limitations posed by point neuron models, therefore reducing the gap between Deep learning applications and biology [GLR17a].

# 2.3 Neural Network Simulators

The models and rules described in the previous sections need adequate tools to be simulated, and simulation is the key for further understanding and model development. Simulating neural networks is a complex task, which requires handling high parallelism and reliability. Scalability of systems is another important feature, since complex tasks require large network representations.

Different approaches are nowadays available for SNN simulation and they fall into different categories, presenting different advantages and drawbacks. The two main categories are: Hardware simulators and Software simulators. Hardware simulators are commonly ASICs (Application Specific Integrated Circuits) specifically designed with the aim of simulating neural networks. These tend to be very efficient, but often come with low flexibility, since the number of models

or rules that can be implemented might be constrained by the hardware implementation of the simulator. Software simulators are tools designed to run on HPC (High Performance Computing) platforms. These typically come with a higher flexibility, however the performance is limited by the underlying hardware and its communication mechanisms, which can represent a major bottleneck.

#### 2.3.1 Software Simulators

Software simulators are software tools commonly designed to run on CPU-based systems, which come with high flexibility, but performance constrained by the hardware they are executed on. Neurons are described as sets of Ordinary Differential Equations (ODEs) implementing the mathematical properties of the chosen model. Because of their flexibility it is generally straightforward to add new neuron models, and it is possible to simulate networks of arbitrary sizes. The implemented algorithms can follow either a clock-driven approach, or an event-driven approach or a hybrid one. A clock-driven approach consists of a discretisation of the simulation time into equally long intervals, called timesteps. These events are used to mark the advance of time and represent the points during the simulation where neural states are updated. This allows continuous time models to be discretised, and provided the timestep resolution is high enough, allows modelling of neuron state updates via exponential integration, calculating the dynamics timestep by timestep. The most commonly used resolutions, in accordance with biological times, are therefore 1 ms or 0.1 ms. A major drawback of these simulators, however, is that all the spikes arriving within a timestep are considered simultaneous in that timestep, reducing the maximum precision for the state update to the timestep resolution. The event-driven approach, on the other hand, performs the state update only when a spike is received. This property allows the temporal nature of SNNs to be precisely mimicked, by implementing synaptic and status changes when signals are received, instead of discretising them over a longer timestep. However, biologically-plausible SNNs present fan-ins so large that it becomes impractical to use this approach in many simulators [MMG<sup>+</sup>05]. The hybrid solution, which is the one preferred by most of the established simulators, employs a time-driven simulation for the neuron state update, and an event-driven approach for the synapses. Examples of the use of this approach are given by NEST [GD07], BRIAN [GB08] and NEURON [CH06].

An important requirement for software simulators is to perform real-time simulations. A software simulator is defined real-time when the simulation time matches the wall-clock time, therefore the time taken to perform the simulation corresponds to the biological time for the network. For biologically-representative complex SNNs this condition might become hard to meet, due to the high number of neurons and connections and the tight timing constraints. For this reason, some platforms perform soft real-time simulations, in which some timesteps are allowed to overrun, and then they recover in future timer periods where the computational load is reduced, yielding real-time performance on average. However this violates hard real-time requirements, which mandate that every timestep completes within the corresponding amount of wall-clock time (i.e. each 0.1 ms of biological time is completed in 0.1 ms). Where real-time performance is not possible, an operation called slowdown can be performed. This results in increasing the length of each timestep by a multiplicative factor (or slowdown factor). Therefore each timestep will have a longer duration compared to biological realtime, giving the resources enough time to perform all the necessary updates.

#### 2.3.1.1 MPI and OpenMP

Software simulation is commonly performed on CPU-based supercomputers, as detailed in section 2.3.1. Supercomputers and HPC platforms typically consist of a large number of compute nodes connected by fast interconnect. Each of these nodes can contain a number of CPUs containing multiple cores. The memory system can be distributed or shared. In order to offer coding support to programmers, two main standards have been developed, which are exploited by many software simulators. These two standards are called OpenMP and MPI.

OpenMP is an API which provides directives for parallel programming in shared memory systems. Its aim is to provide a model for parallel programming which is portable across shared memory architectures. The standard allows multiple threads of execution to perform tasks defined implicitly or explicitly by OpenMP directives and provides a relaxed memory consistency mechanism, where the memory view of a thread can be modified without reflecting to memory until a flush operation is performed [Boa08].

MPI is a paradigm commonly used for multiprocess programming on distributed memory machines [For09]. This standard is based on a message-passing communication system. Similarly to OpenMP, the main idea is to guarantee

portability, by defining a standard. This API allows communication mechanisms between different processes to be improved and provides abstraction for developers.

The two standards can be combined together in brain-scale network simulations [IEPD17, JIH<sup>+</sup>18] to improve the exploitation of computer capabilities, employing both thread-based parallelism and process-based parallelism.

#### 2.3.1.2 NEST

NEST (NEural Simulation Tool) [GD07] is an open source software tool, developed and maintained by the NEST initiative under the GNU General Public License. It has been designed to simulate large-scale networks of point neuron models or neurons with a small number of compartments. Simulations are controlled through a built-in scripting language or a Python module called PyNEST [JIH+18]. Networks are modeled as sets of nodes and connections, where nodes can be neurons, devices or sub-networks. Connections are defined by sending node, receiving node, weight and delay, and communications are event-based. Models of synaptic plasticity can be implemented in the form of STDP, and high level functions to create connectivity schemes are provided. In order to optimise the use of resources, NEST supports hybrid parallelisation, therefore MPI is employed for inter-node communication, where each node is assigned to one MPI process and events are communicated between processes by collective MPI functions, and inside each MPI process multi-threading is supported through OpenMP, making better use of the available memory.

#### 2.3.2 Hardware Simulators

Hardware simulators are dedicated circuits and platforms designed with the purpose of simulating neural networks. They commonly come with high performance, but limited flexibility compared to their software counterparts, as the hardware implementation of the neuron models limits the variety that can be simulated. The hardware simulators can be analog, digital or mixed-signal. The time scale can be continuous, discrete or abstract, and the simulators can be real-time, accelerated or non real-time [Dav12]. There are several classes of hardware simulator, which span from FPGAs, Graphic Processing Unit (GPU), hardware accelerators, to Neuromorphic platforms.

#### 2.3.2.1 FPGAs

FPGAs (Field Programmable Gate Arrays) are an alternative to ASICs for hardware simulations. These systems allow the implementation of the desired logic function by programming them. However FPGAs are a viable choice only for small networks sizes, as the fabric process is much larger compared to ASICs [KR07] and the number of neurons that can be implemented is limited [RHTF03]. Due to their clock speeds, which are commonly around hundreds of MHz, it is possible to perform sub-realtime simulations of point neuron models and it is possible to connect multiple FPGAs together [MFM<sup>+</sup>12]. Scalability issues typical of these platforms [MMG<sup>+</sup>07] seem to have been overcome with the latest developments, however programmability still requires expertise in hardware design, reducing the accessibility of these platforms [NCA<sup>+</sup>20].

#### 2.3.2.2 GPUs

GPUs (Graphics Processing Units) are nowadays well established neural network simulators. Through their high parallelism they provide a good framework for this type of application. The GeNN library [YTN16, KN21] allows code to be generated efficiently to accelerate SNN simulations on NVIDIA GPUs and demonstrated remarkable performance in simulating biologically-representative SNNs [KN18, KKN21]. Despite the rapid advances in technology, which continuously provide new more powerful platforms addressing issues such as sparsity (e.g. the Ampere architecture [NVI]), scalability still represents a limitation when simulating SNNs on GPUs. Multi-GPU simulations are problematic, as connections between separate GPUs still represent a bottleneck, being constrained by a single communication channel which therefore limits the performance.

#### 2.3.2.3 Hardware Accelerators

The final subcategory of hardware simulators is identified by hardware accelerators. These are platforms commercially available from industry which aim to facilitate DNN and CNN algorithms [CBM<sup>+</sup>20]. Companies such as Intel (through the Xeon series) and Apple (though the Bionic series of CPUs) are investing in building new architectures commonly targetting inference and pattern recognition, and specific libraries are being developed to accelerate AI applications on these platforms. A detailed analysis of these platforms is, however, beyond the

scope of this thesis, due to the heterogeneity of these technologies. Additional details are available as reference [CBM<sup>+</sup>20].

# 2.4 Neuromorphic Hardware

Neuromorphic Engineering is a field pioneered by Carver Mead in the 1980s, which approaches neural network simulations from a different perspective [Mea90, Mea89. The original idea was, instead of employing standard computing systems, to implement a platform which was architecturally similar to the brain structure. Mead noticed that MOS transistors show very similar behaviours compared to ion channels, therefore he suggested to implement hardware simulators through the use of low-power sub-threshold analog circuits, instead of using digital computing systems, showing a reduction in power consumption up to 4 orders of magnitude [Mea90]. This was the first step towards a new field which is nowadays gaining more popularity, and several platforms, both in the digital and analog domains, have been developed [TMC<sup>+</sup>18, Fur16]. All these platforms share the basic idea of non conventional computing (they are often referred to as non Von Neumann, since their design deviates from the standard centralised approach commonly used in computing platforms), where, instead of a single central and powerful computational unit, a distributed approach is preferred, having small units acting like the neurons in the brain. The memory hierarchy is revised as well to be distributed and as close as possible to the computational units, to mimic the behaviour of synapses. The connectivity between computational nodes is enhanced, such that the units are allowed to form multiple connections as happens in the brain.

Analog and digital platforms present quite different architectures and approaches, where the first are generally more performance oriented, at the expense of lower flexibility, while the second allow more customisation and freedom in neural modelling.

Neuromorphic Engineering has two main objectives: first to better understand the computational properties of neural systems, by providing an electronic implementation of them, second to provide new alternatives to standard computing paradigms, to compensate for the end of Moore's law [Moo06].

### 2.4.1 Analog Neuromorphic Systems

Analog Neuromorphic platforms are the closest to Mead's idea. Neurons and synapses are implemented by physical circuits. This provides a very high efficiency in terms of simulation times, often guaranteeing sub-realtime performance, however this comes at the expense of flexibility. The physical implementation of the neural circuitry sets a limit on the number of neurons and on the variety of models that can be implemented. Well-known analog Neuromorphic platforms include BrainScaleS [SKMM17] and ROLLS [QMC+15].

#### 2.4.1.1 BrainScaleS

BrainScaleS was developed at the University of Heidelberg and is based on the direct implementation of the neuron model equations in electronic circuits. The electrical parameters that can be read out represent the model variables. The system can run 10<sup>4</sup> times faster than biological real-time and the implemented neuron model is the Adaptive Exponential Integrate-and-Fire Model [BG05]. The neuron and all its synapses are implemented as a continuous-time analog circuit. Simulations including more than a few hundreds of neurons require a multichip implementation, which is achieved through wafer-scale integration [SFM08], a postprocessing wafer technique which allows chips manufactured on the same wafer to be interconnected without separating them. 128k synapses and 512 membrane circuits are grouped into ANNCOREs (Analog Neural Network CORE) and they can form neurons with up to 16k synapses each [SFM08, SKMM17]. Synaptic plasticity is available through a digital general purpose processor, implementing programmable STDP rules and connected to the synapse memory array [FSG<sup>+</sup>17, FFS<sup>+</sup>13].

At the moment of writing, a second generation of the BrainScaleS platform is under development, called BrainScaleS-2. This aims to provide a flexible tool for the machine learning and computational neuroscience communities, targeting scalability and bio-inspired learning rules [PBC<sup>+</sup>22].

#### 2.4.1.2 ROLLS

The Reconfigurable On-Line Learning Spiking Neuromorphic processor (ROLLS) is composed of a configurable array of synapse and neuron circuits producing biologically realistic response properties and behaviours [QMC<sup>+</sup>15]. Neurons are

represented as silicon circuits as a row in an array of 256 elements and they physically implement the Adaptive Exponential Integrate-and-Fire model. Synapse circuits are two blocks of the array of 256 × 256, the first modeling long-term plasticity mechanisms and the second short-term plasticity. Through a synapse de-multiplexer it is possible to choose how many rows of plastic synapses to connect to the neurons [QMC<sup>+</sup>15, CSBI14]. Communication happens through the Address Event Representation (AER) packet format [Mea89] and the system supports STDP. SNNs are defined through custom software called PyNCS [SNSI14].

### 2.4.2 Digital Neuromorphic Systems

Digital Neuromorphic platforms commonly make use of components available on the market such as low-power processors, combining these with custom digital circuits to build a different type of architecture with enhanced connectivity and optimised for neural network simulations. Their structure guarantees a much higher programmability compared to the analog platforms, which results in more flexibility in the number and types of neurons that can be simulated. However digital circuits cannot often reach the performance of the analog implementation.

Some examples of digital Neuromorphic platforms are Intel Loihi [DSL<sup>+</sup>18], IBM TrueNorth [ASC<sup>+</sup>15] and SpiNNaker [FLP<sup>+</sup>13]. The first two platforms are briefly presented below, SpiNNaker is addressed in the next section in more detail, as it is the main platform used in this work.

#### 2.4.2.1 TrueNorth

TrueNorth is a digital Neuromorphic chip developed by IBM, with the aim of delivering a very dense, energy-efficient platform capable of supporting a range of cognitive applications [ASC $^+$ 15, MAAI $^+$ 14]. This platform makes use of custom digital neurosynaptic cores, each implementing 256 neurons receiving 256 synapses each. A TrueNorth chip contains 4096 neurosynaptic cores which operate asynchronously. A 256  $\times$  256 cross-bar connects source and destination neurons, implementing individually configurable point-to-point routes. 16 chips are connected to form larger boards, reaching a total of 16 million neurons and 4 billion synapses. Boards can be interconnected to provide higher scalability [Fur16].

#### 2.4.2.2 Loihi

Loihi is Intel's contribution to the Neuromorphic field. It is a fully digital chip containing 128 digital Neuromorphic processors and 3 embedded x86 cores organised in a NoC, implemented as a two-dimensional mesh which allows asynchronous communication in the form of packetised messages [DSL+18]. The Neuromorphic cores implement the neural state update and handle the synapses in an event-driven manner, computing all the state updates in-memory. The general purpose cores, on the other hand, are used as service cores, loading the SNN configurations on the Neuromorphic cores, pre- or post-processing the input and output data and supervising the packet routing [LWC+18b]. Each Neuromorphic core can implement up to 1024 spiking neural units, or compartments, which are grouped into sets of trees building neurons. The state update is time-multiplexed and pipelined. Loihi supports synaptic plasticity in the form of STDP and the equations are stored as microcode in a memory block local to the Neuromorphic cores as part of a learning block [DSL+18, LWC+18b, LWC+18a].

SNNs are described in Python through a LoihiAPI library and a dedicated software toolchain maps the network onto the Loihi system [LWC<sup>+</sup>18b, LWC<sup>+</sup>18a]. To provide scalability Loihi comes in different configurations, ranging from a 2-chip USB device (called Kapoho Bay), to a system composed of 24 32-chip boards (for a total of 768 chips), called Pohoiki Beach [FOF<sup>+</sup>20].

A Python software framework called Lava [Int21] has been released to provide support to neuro-inspired applications and a second generation of the Loihi Neuromorphic platform is under development at the moment of writing [OFR<sup>+</sup>21].

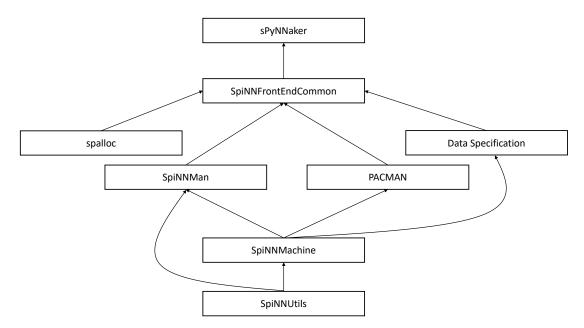

# 2.5 The SpiNNaker System

This section provides details on the SpiNNaker Neuromorphic system [FGTP14], which is the main platform chosen for the work performed for this thesis. The system is described both from hardware and software perspectives. SpiNNaker is an acronym for Spiking Neural Network architecture [FLP+13, FGTP14]. It has been developed at the University of Manchester in the School of Computer Science by Prof. Steve Furber and his group. The system is a many-core GALS (Globally Asynchronous Locally Synchronous) system, composed of  $\approx 1$  million general purpose ARM cores and its aim is to perform real-time simulations of biologically-inspired SNNs.

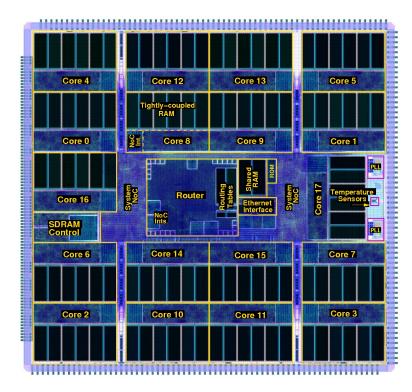

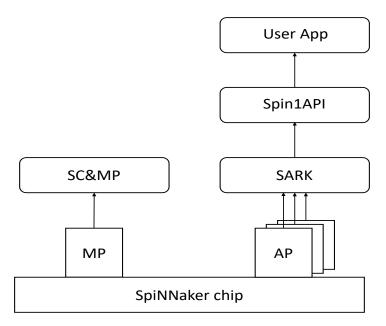

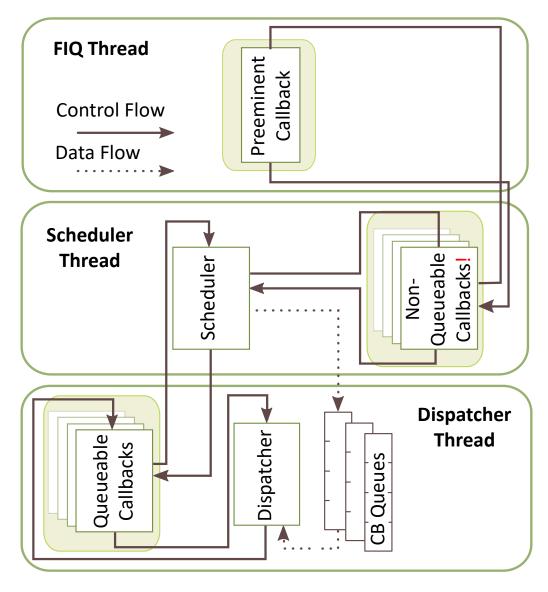

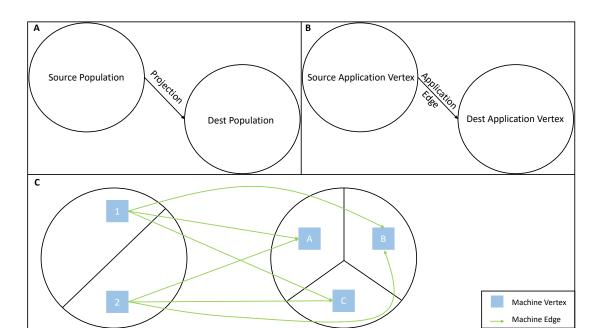

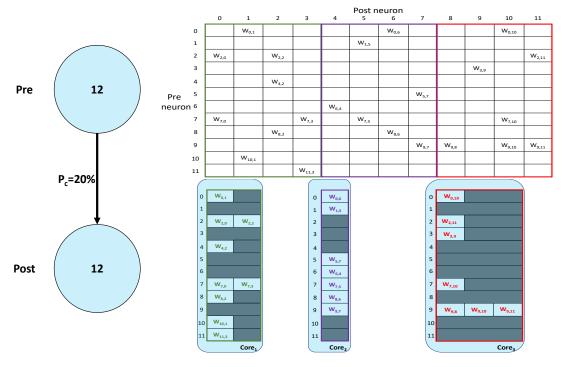

Figure 2.2: Block diagram of a SpiNNaker Chip

#### 2.5.1 Hardware Overview

From a hardware perspective, the main building block of the SpiNNaker system is the SpiNNaker chip. Each chip contains 18 ARM968 cores, 128 MB of shared SDRAM memory, and a custom router allowing direct communication with 6 neighbouring chips. Among the 18 cores, 16 are assigned as Application processors and are used for simulation purposes, 1 is the Monitor Processor and has the role of supervising the other cores' behaviour and 1 is for fault tolerance purposes. A schematic of a SpiNNaker chip is shown in Figure 2.2, while Figure 2.3 shows the layout. SpiNNaker chips are arranged on boards, which can be accessed externally through an Ethernet interface.

#### 2.5.1.1 The ARM968 Processor

The computational units employed by the SpiNNaker system are general purpose ARM968 processors. They feature the ARM9TDMI architecture, supporting the instruction set of the ARMv5TE architecture, an AHB bus interface and the

Figure 2.3: Layout of a SpiNNaker Chip

Thumb instruction set [ARM06]. The cores run at 200 MHz clock frequency and feature two local memories: a 32 KB ITCM (Instruction Tightly Coupled Memory) and a 64 KB DTCM (Data Tightly Coupled Memory). The first is used to store the instructions to be executed during a simulation, and the second for the data. Each core has direct access to its private memories and can access the shared SDRAM memory either via a core-specific DMA controller, or through bridge access. Each processor node has access to 2 independent counters, which can be used to trigger interrupts for real-time dynamics.

#### 2.5.1.2 The Shared Memory

Each chip is connected to a 128 MB shared SDRAM. The access to it is through a single channel and the cores are distributed in a tree-based structure for getting access. A single core has access to the memory at a time, therefore when multiple requests are issued simultaneously the memory channel is contended. This results in different access times for different cores. The access tree consists of a binary tree having an arbiter at each junction and cores placed at the leaves. For every junction, the first core requesting a DMA transfer has the bus granted by the

arbiter, the other cores get queued. This means that branches with multiple cores trying to access memory will experience longer access times [PPG<sup>+</sup>13]. In addition to the off-chip SDRAM memory, the SpiNNaker chips have an integrated 32 KB System RAM shared between the cores and a Boot ROM used during bootstrap.

#### 2.5.1.3 The Routing System