# ADVANCED POWER CONVERTERS FOR RAILWAY TRACTION SYSTEMS

by

IVAN KRASTEV

A thesis submitted to the

University of Birmingham

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electronic, Electrical, and Systems Engineering

School of Engineering

University of Birmingham

March 2018

## UNIVERSITY<sup>OF</sup> BIRMINGHAM

## **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

# <u>ABSTRACT</u>

This thesis presents a new traction drive suitable for fuel-cell powered light rail vehicles based on a multilevel cascade converter with full-bridge cells. The converter provides dc-ac power conversion in a single stage, while compensating for the variation of fuel cell terminal voltage with load power. The proposed converter can replace the conventional combination of dc-dc converter, as it benefits from having a multilevel ac voltage waveform and much smaller power inductors, compared to conventional solutions.

The converter numerical and analytical models are derived showing that the converter can be modelled as a cascaded boost converter and 3-phase inverter. The design methodology for the energy storage capacitors and power inductors is presented, showing that inductance is reduced at a quadratic rate with the addition of more submodules, while total converter capacitance remains constant. A simulation of a full-scale traction drive in a fuel cell tram demonstrates that the proposed converter is a viable solution for light rail applications.

The concept of a boost modular cascaded converter is fully validated through a bespoke laboratory prototype driving a small induction machine. The experimental inverter achieves operation from standstill, with full motor torque, to field weakening with constant power, boosting a 50V dc supply to 200V peak line-to-line voltage.

# **ACKNOWLEDGMENTS**

This project was a big part of my life for several years, and when I started, I really had no idea what I was getting into. In the beginning everything was nice and relaxed but, much quicker than I like to admit, the PhD poured over into my personal life. In all that time my partner Andriana stood by me, listened to me complaining about stuff blowing up and was extremely understanding when I'd spend the whole weekend fixing said stuff. She kept me clean, fed, and most of all - sane. Adi, I truly could not have done this without you.

I would also like to thank my loving parents for their support and for being so understanding – I hope I didn't worry them too much when I was locked away for days in the basement lab. They also provided priceless advice when it was time to go back to the real world and find a job and helped me prepare for interviews and negotiations.

The most fun side of the project was technical – designing and building converters, modelling and doing some embedded coding. Solving my technical problems was made easy by the wonderful people at the Birmingham Centre for Railway Research and Education (BCRRE), whom I would like to thank: Pietro Tricoli, my supervisor, was always available for a technical chat, he let me bounce so many ideas off him (most of them not very clever), and always had something helpful to say; Dr Stuart Hillmansen got me to build a hydrogen loco which is how I learned most of the engineering I know; Prof Felix Schmitt who always lent a helping hand in the right moment; Paul Weston and Louis Saade were of great help when I started writing code and were invaluable when I had to build two dozens of PCBs in the space of two months; Prof Clive Roberts for funding some power electronics shenanigans; and Adnan Zentani, for all the cutting, drilling and machining!

I would also like to thank Nadeen Taylor, for being *the best* administrator that knows everything and everyone and is always ready to help out!

Also, a big thanks to all my friends from BCRRE- Heather, Rana, Rob, Krish, Rory, Louis, Paul, and Rhys. Hanging out, playing board games and watching bad B-movies – those were lots of fun times and great memories!

Lastly, I would like to express my gratitude to the Engineering and Physical Sciences Research Council for funding this project, and ©Mitsubishi Electric Corporation for providing IGBT modules.

# **TABLE OF CONTENTS**

| List of abbreviations                                                        | xii      |

|------------------------------------------------------------------------------|----------|

| Chapter 1. Introduction                                                      | 1        |

| 1.1. Problem statement                                                       | 3        |

| 1.2. Research objectives                                                     | 5        |

| 1.3. Publications                                                            | 6        |

| 1.4. Thesis outline                                                          | 7        |

| Chapter 2. Review of boost converters and inverter drives for electric tract | ion 9    |

| 2.1. Discussion of requirements and metrics                                  | 9        |

| 2.2. 3-phase inverters                                                       | 12       |

| 2.2.1. 2-Level inverters                                                     | 13       |

| 2.2.2. Multi-level inverters                                                 | 18       |

| 2.3. Boost converter topologies                                              | 28       |

| 2.3.1. Single inductor boost converter (SIBC)                                | 28       |

| 2.3.2. Interleaved boost converter with separate inductors (IBC)             | 30       |

| 2.3.3. Interleaved boost converter with coupled inductor (IBCCI)             | 32       |

| 2.3.4. Interleaved multi-phase boost converter with coupled in               | ıductors |

| (IMPBCI) 33                                                                  |          |

| 2.3.5. Flying capacitor boost converter (FCBC)                               | 35       |

| 2.3.6. Three-level boost converter (TLBC)                                    | 36       |

| 2.3.7. Isolated converters (IsoC)                                            | 38       |

| 2.4.    | Sin  | gle stage buck-boost inverters                              | 40 |

|---------|------|-------------------------------------------------------------|----|

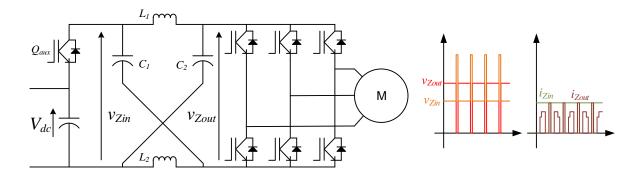

| 2.4     | .1.  | Voltage fed Z-source inverter (VFZSI)                       | 41 |

| 2.4     | .2.  | Voltage-fed quasi Z-source inverter (QZSI)                  | 43 |

| 2.4     | .3.  | Current-fed quasi Z-source inverter (CFQZSI)                | 44 |

| 2.5.    | Pro  | oposed converter: Boost Multilevel Cascaded Inverter (BMCI) | 46 |

| 2.6.    | Su   | mmary                                                       | 49 |

| Chapter | · 3. | Modelling of Boost Multilevel Cascaded Inverters            | 53 |

| 3.1.    | Pri  | nciple of operation                                         | 53 |

| 3.2.    | Ма   | thematical modelling                                        | 59 |

| 3.3.    | Av   | erage-time model                                            | 64 |

| 3.3     | .1.  | Large signal model                                          | 72 |

| 3.3     | .2.  | Small signal model                                          | 73 |

| 3.4.    | Su   | mmary                                                       | 76 |

| Chapter | 4.   | Modulation and control system of BMCIs                      | 77 |

| 4.1.    | Мс   | dulation                                                    | 77 |

| 4.1     | .1.  | Staircase modulation                                        | 77 |

| 4.1     | .2.  | Pulse-width modulation (PWM)                                | 80 |

| 4.1     | .3.  | Space-vector modulation                                     | 85 |

| 4.2.    | Co   | nverter control                                             | 86 |

| 4.2     | .1.  | Sub-module capacitor voltage balancing                      | 86 |

| 4.2.2.     | Average leg sub-module voltage control                                 | 91   |

|------------|------------------------------------------------------------------------|------|

| 4.2.3.     | 3-phase motor control                                                  | 102  |

| 4.2.4.     | Injected balancing power for low frequency compensation                | 111  |

| 4.2.5.     | Converter control systems                                              | 112  |

| 4.3. Su    | mmary                                                                  | 115  |

| Chapter 5. | General design for an <i>n</i> -module BMCI and experimental converter | r117 |

| 5.1. Ge    | neral converter design                                                 | 117  |

| 5.1.1.     | Choice of number of sub-modules n and inverter waveform levels         | 119  |

| 5.1.2.     | Inductance design                                                      | 127  |

| 5.1.3.     | Capacitor design                                                       | 139  |

| 5.2. Ele   | ectronics design of prototype converter                                | 145  |

| 5.2.1.     | Design of converter sub-module                                         | 146  |

| 5.2.2.     | Current sensor card design                                             | 152  |

| 5.2.3.     | Routing card design                                                    | 153  |

| 5.2.4.     | Master controller                                                      | 154  |

| 5.3. Su    | mmary                                                                  | 154  |

| Chapter 6. | Simulation of a BMCI for a hydrogen tram                               | 157  |

| 6.1. Sir   | nulation setup                                                         | 157  |

| 6.1.1.     | Vehicle model                                                          | 158  |

| 6.1.2.     | Fuel cell stack model                                                  | 161  |

| 6.1.3.     | BMCI model                                                             | 164  |

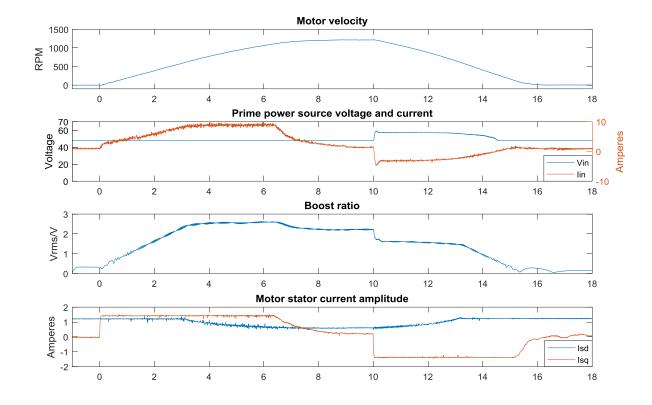

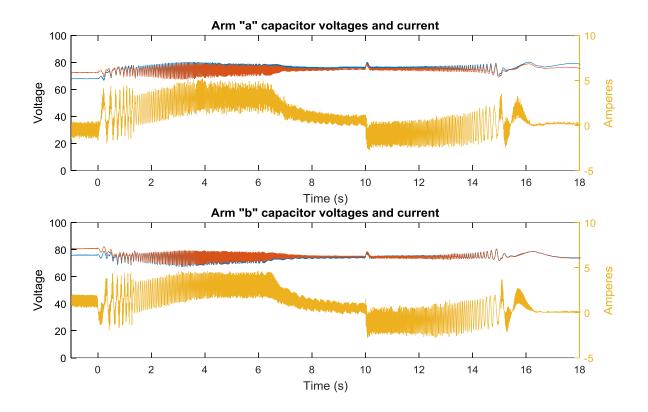

| 6.2. B     | MCI drive                                                   | 165 |

|------------|-------------------------------------------------------------|-----|

| 6.2.1.     | Overall performance                                         | 166 |

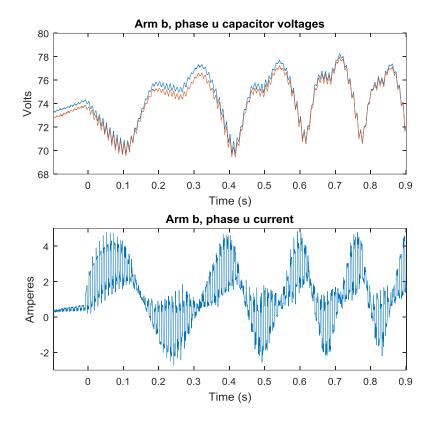

| 6.2.2.     | Operation at low-speeds                                     | 168 |

| 6.2.3.     | Constant torque region                                      | 171 |

| 6.2.4.     | Constant power region                                       | 172 |

| 6.2.5.     | Regenerative braking                                        | 174 |

| 6.3. Co    | omparative study                                            | 176 |

| 6.3.1.     | Switch apparent power requirement                           | 177 |

| 6.3.2.     | Comparison of total capacitor energy                        | 179 |

| 6.3.3.     | Comparison of total inductor energy and inductor losses     | 182 |

| 6.3.4.     | Inductor specific resistance ( $\Omega/J$ )                 | 185 |

| 6.3.5.     | Converter design values, efficiency, and THD                | 186 |

| 6.4. Sı    | ımmary                                                      | 195 |

| Chapter 7. | Experimental validation                                     | 198 |

| 7.1. 0     | pen loop control with passive load                          | 200 |

| 7.1.1.     | Initial validation of the basic operations of the converter | 200 |

| 7.1.2.     | Maximum boost characteristics                               | 206 |

| 7.2. 0     | peration of internal controllers                            | 211 |

| 7.2.1.     | Sub-module balancing controller                             | 211 |

| 7.2.2.     | Arm balancing controller                                    | 212 |

| 7.2.3.     | Average leg capacitor voltage regulator                     | 213 |

| 7.2.4.     | Low-frequency operations                                       | 214 |

|------------|----------------------------------------------------------------|-----|

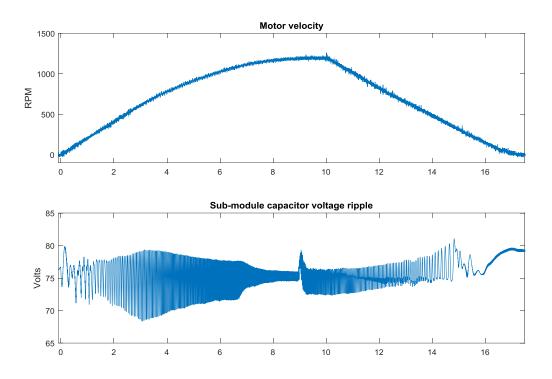

| 7.3. Ex    | periments with converter driving a simulated traction load     | 216 |

| 7.3.1.     | Traction cycle test                                            | 217 |

| 7.4. Su    | mmary                                                          | 226 |

| Chapter 8. | Conclusion and future possibilities                            | 228 |

| 8.1. Co    | onclusions                                                     | 229 |

| 8.1.1.     | Suitability of BMCI as a boost traction inverter               | 229 |

| 8.1.2.     | Predictions of the BMCI large signal model                     | 229 |

| 8.1.3.     | Impact on the dc-side voltage on the modulation index          | 230 |

| 8.1.4.     | Link between passive elements and motor parameters             | 230 |

| 8.1.5.     | Influence on inductance and output THD                         | 231 |

| 8.2. Fu    | ture work                                                      | 231 |

| 8.2.1.     | BMCI for permanent magnet drives                               | 231 |

| 8.2.2.     | Capacitor voltage ripple reduction                             | 231 |

| 8.2.3.     | Trade-off between dc current ripple and ac voltage THD         | 232 |

| 8.2.4.     | Optimum carrier modulation to reduce the leg inductance        | 232 |

| 8.2.5.     | BMCI power density                                             | 232 |

| 8.2.6.     | BMCI efficiency and device power dissipation                   | 233 |

| 8.2.7.     | Effects of ddc,x on device utilisation and ac voltage waveform | 233 |

| 8.2.8.     | BMCI used as DC-traction power supply                          | 233 |

| 8.2.9.     | Hybrid traction drive using embedded energy storage            | 234 |

| Bibliography |                          | .236 |

|--------------|--------------------------|------|

| Appendix A.  | BMCI Design              | .249 |

| Appendix B.  | Control system design    | .251 |

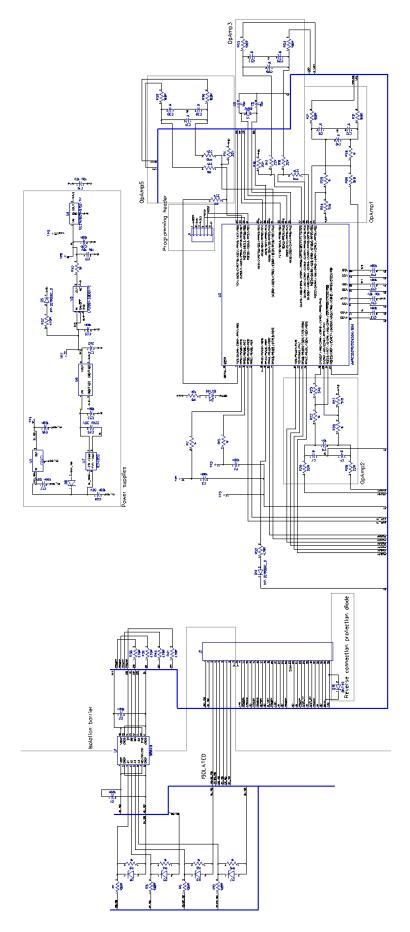

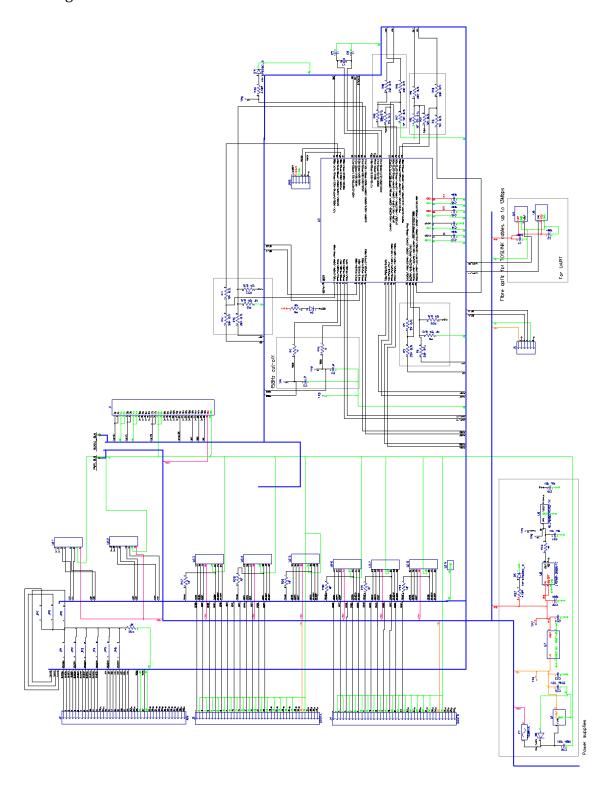

| Appendix C.  | Converter PCB schematics | .257 |

# **LIST OF FIGURES**

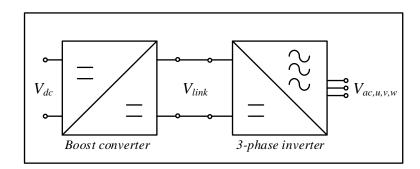

|     | Figure 2-1 Diagram of a 2-stage conversion process - dc-dc and dc-ac,          | with   |

|-----|--------------------------------------------------------------------------------|--------|

| int | termediate voltage V <sub>link</sub>                                           | 9      |

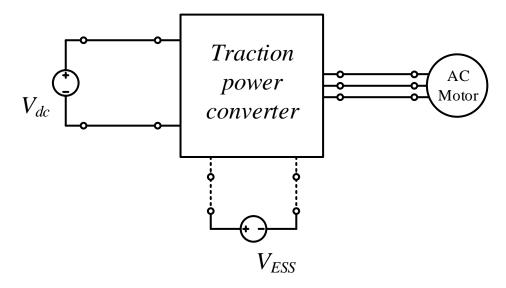

|     | Figure 2-2 Basic diagram of a traction converter with optional energy storage  | 10     |

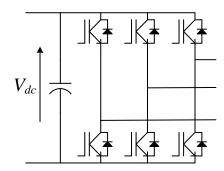

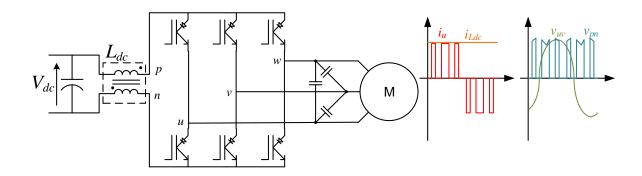

|     | Figure 2-3 2-level voltage source inverter                                     | 13     |

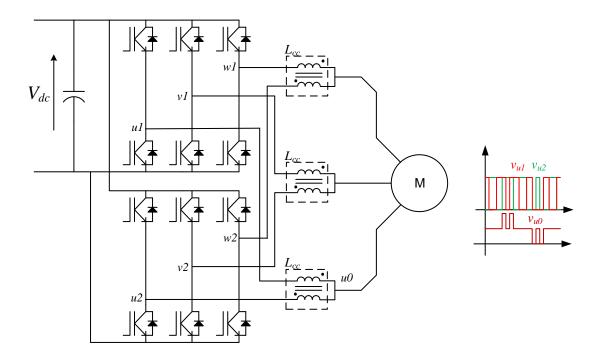

|     | Figure 2-4 Interleaved VSI with coupled inductors                              | 15     |

|     | Figure 2-5 Current source inverter drive                                       | 17     |

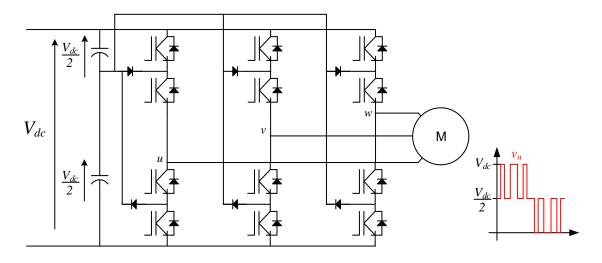

|     | Figure 2-6 3-level NPC inverter                                                | 19     |

|     | Figure 2-7 4-level NPC inverter                                                | 20     |

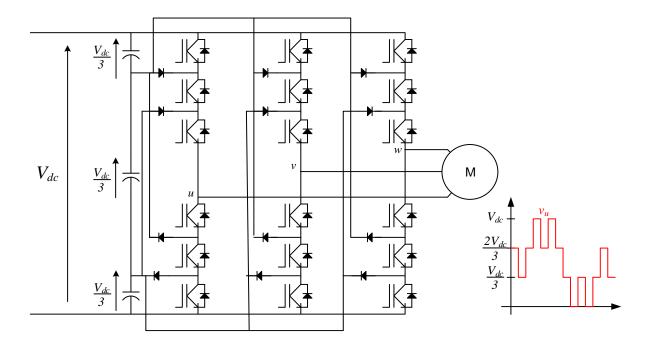

|     | Figure 2-8 3-level FC inverter                                                 | 22     |

|     | Figure 2-9 4-level FC inverter                                                 | 23     |

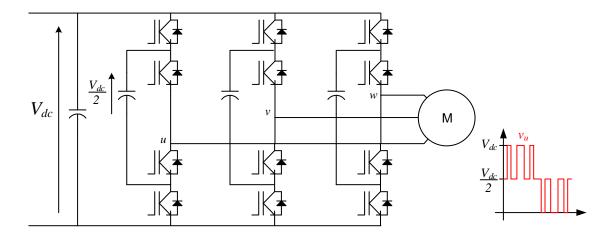

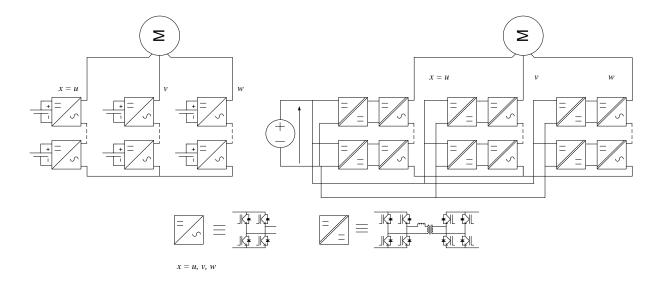

|     | Figure 2-10 Cascaded H-bridge inverters with separate isolated power sources ( | [left) |

| an  | nd single dc power source (right)                                              | 25     |

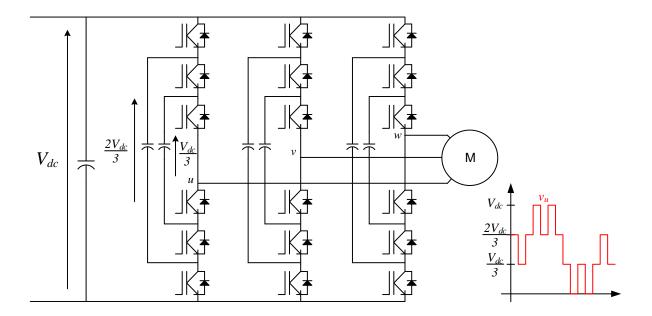

|     | Figure 2-11 Multilevel Cascaded Converter with half-bridge cells               | 27     |

|     | Figure 2-12 Single inductor boost converter                                    | 29     |

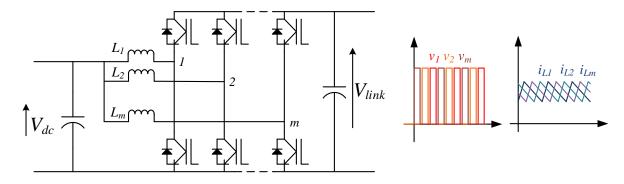

|     | Figure 2-13 Multi-leg interleaved boost converter                              | 30     |

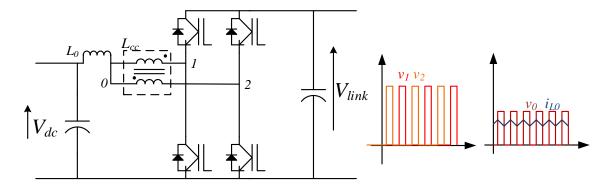

|     | Figure 2-14 2-phase interleaved converter with close-coupled inductor          | 32     |

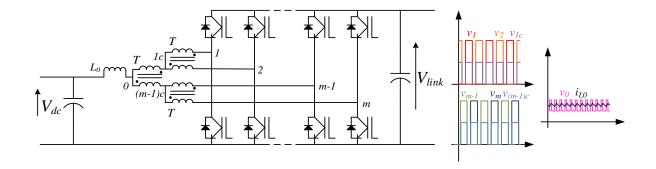

|     | Figure 2-15 Multi-phase Interleaved converter with cascaded coupled inductors. | 34     |

|     | Figure 2-16 Flying capacitor boost converter                                   | 35     |

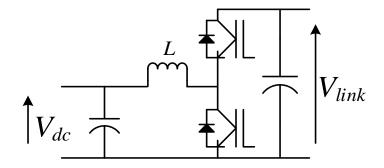

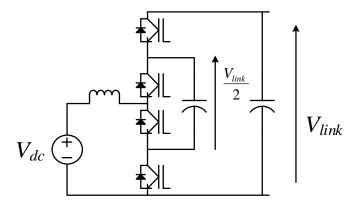

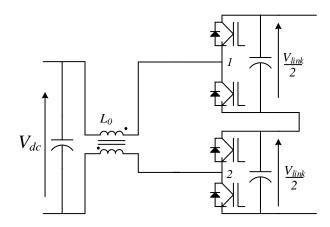

|     | Figure 2-17 TLBC circuit diagram                                               | 36     |

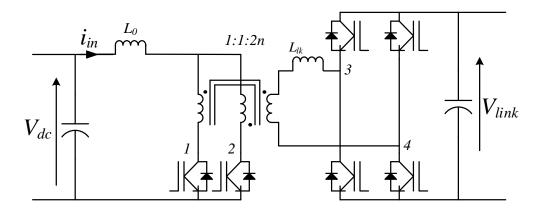

|     | Figure 2-18 Current fed isolated converter                                     | 38     |

|     | Figure 2-19 Inductor fed dual active-bridge converter                          | 39     |

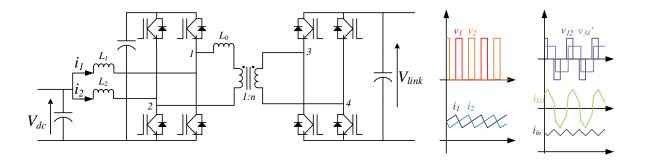

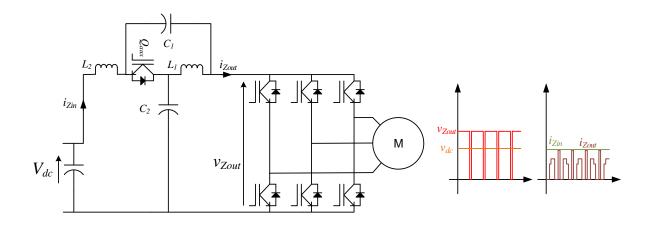

|     | Figure 2-20 Voltage fed Z-source inverter                                      | 41     |

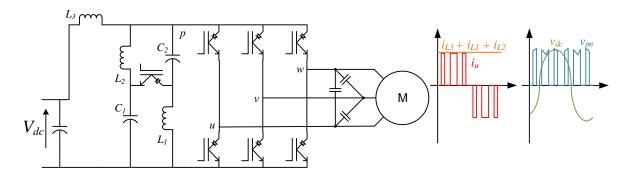

|     | Figure 2-21 Voltage fed QZSI                                                   | 43     |

| Figure 2-22 Current-fed quasi Z-source inverter                                         | 44        |

|-----------------------------------------------------------------------------------------|-----------|

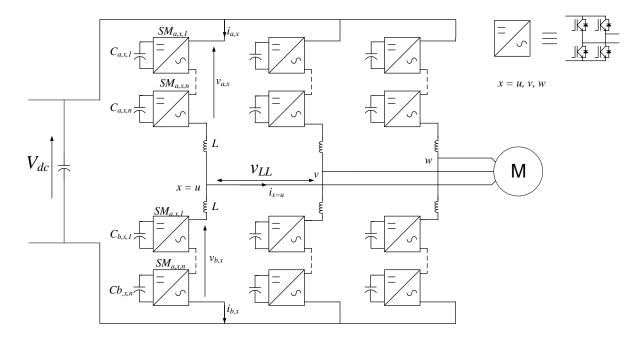

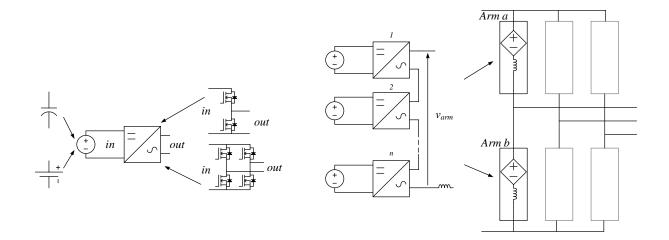

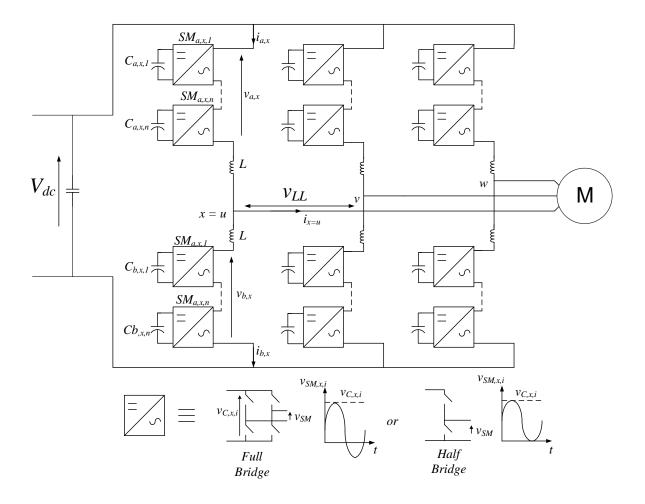

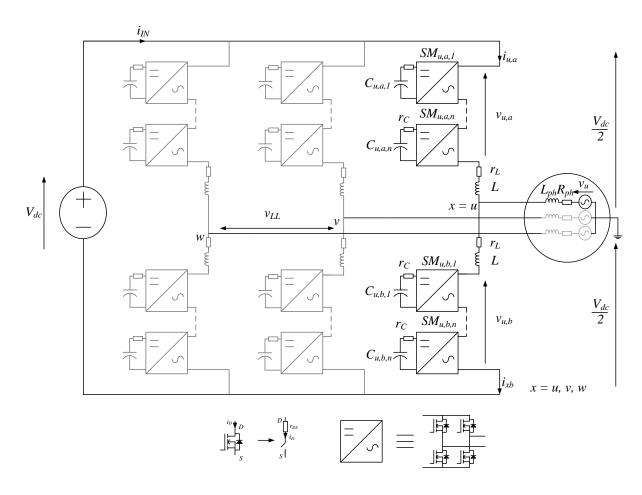

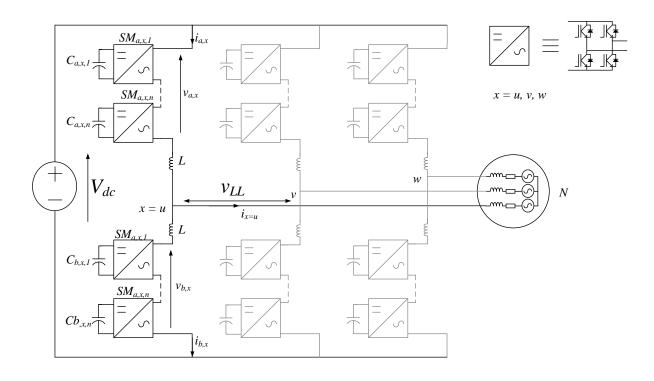

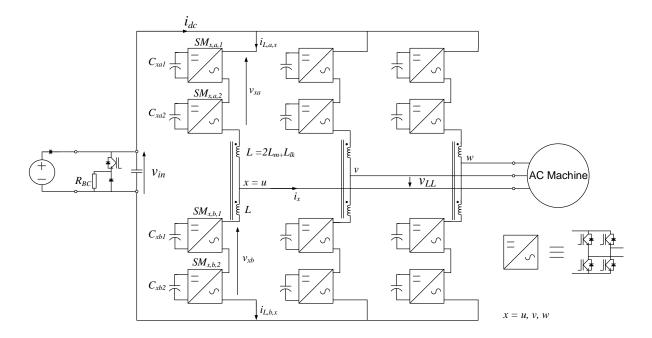

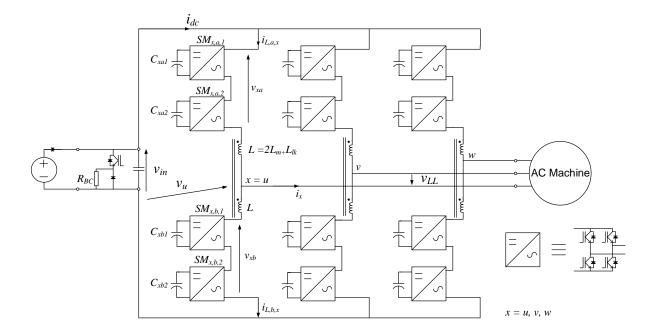

| Figure 2-23 Proposed boost modular cascaded inverter                                    | 46        |

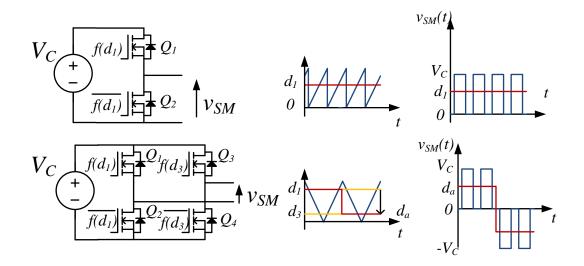

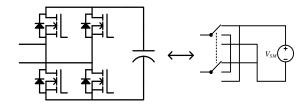

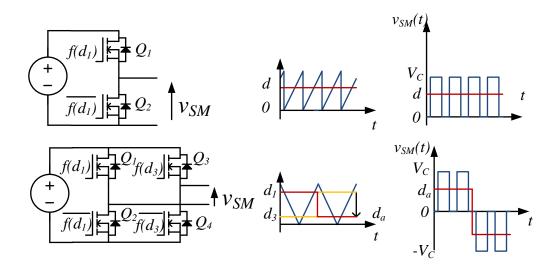

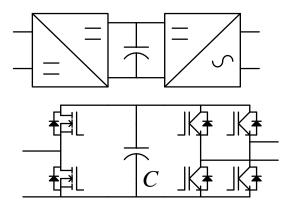

| Figure 3-1 Half-bridge and Full-bridge sub-modules with their respective mo             | dulation  |

| and output waveforms                                                                    | 52        |

| Figure 3-2 MCC building blocks                                                          | 53        |

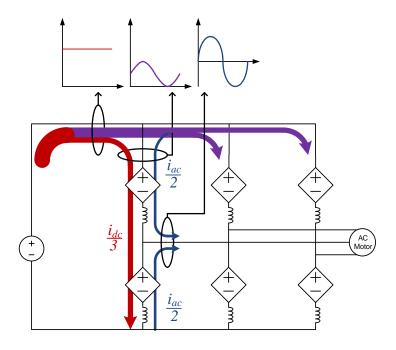

| Figure 3-3 Schematic diagram for the current flow in MCCs                               | 54        |

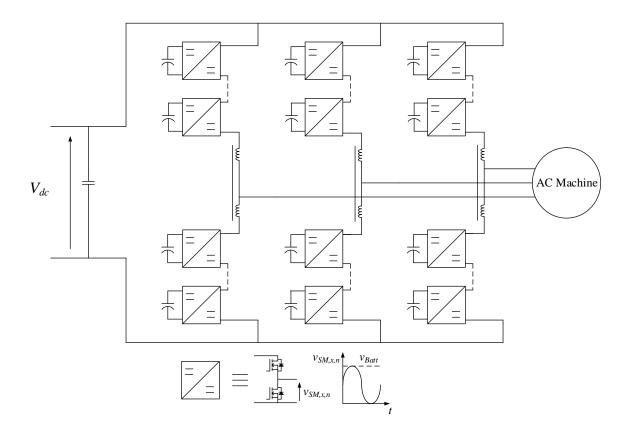

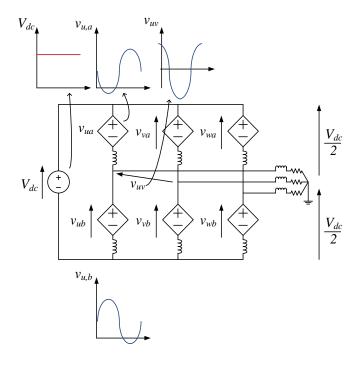

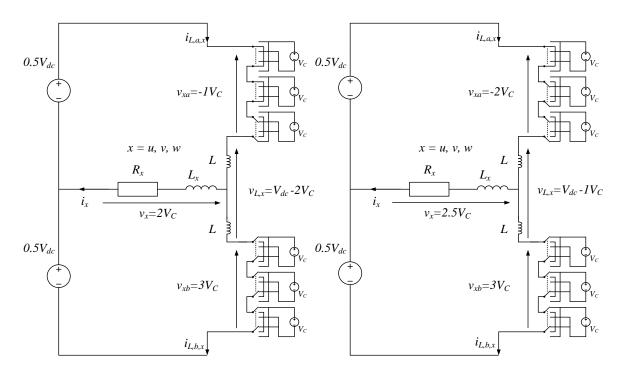

| Figure 3-4 Boost function of the FB MCC                                                 | 56        |

| Figure 3-5 Structure of a general MCC and difference between full and half bri          | dge sub-  |

| modules, with typical mean sub-module output voltages                                   | 57        |

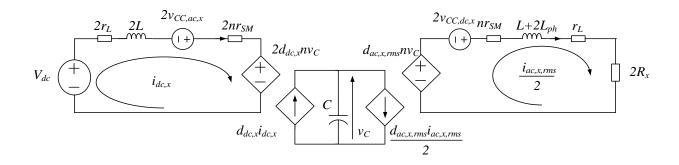

| Figure 3-6 BMCI model including parasitic resistances                                   | 58        |

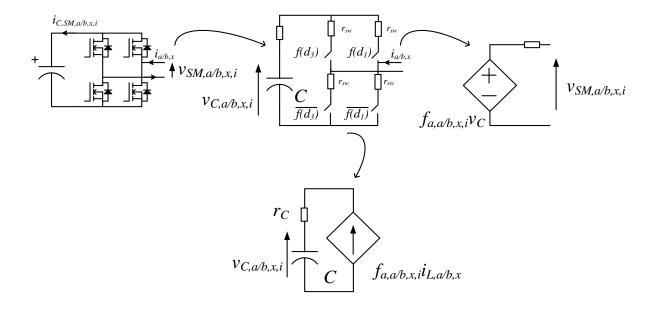

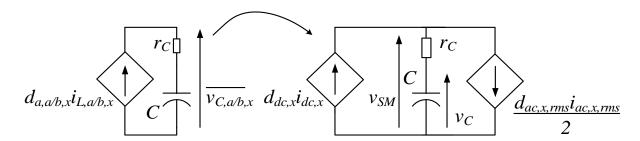

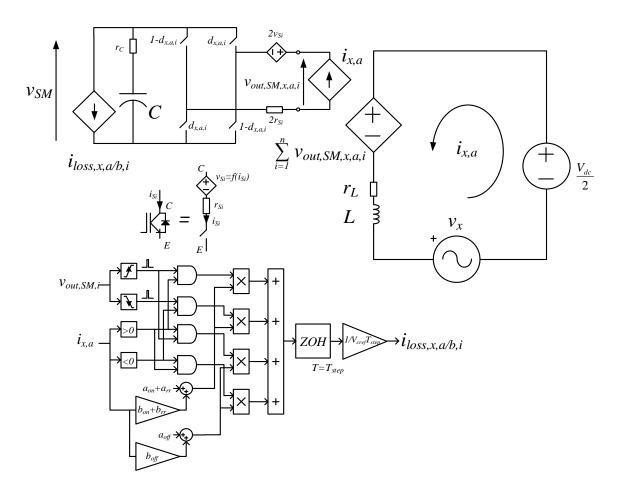

| Figure 3-7 Generic sub-module and equivalent circuits used for modelling                | 59        |

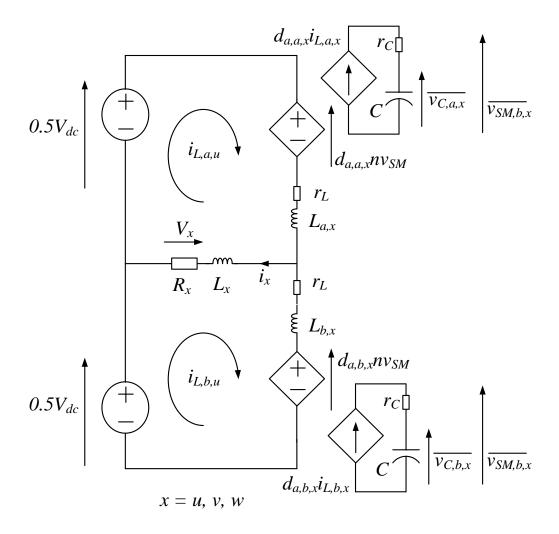

| Figure 3-8 Equivalent circuit of an MCC leg                                             | 63        |

| Figure 3-9 Equivalent circuit of a converter sub-module                                 | 67        |

| Figure 3-10 Equivalent circuit of the BMCI averaged-time model                          | 69        |

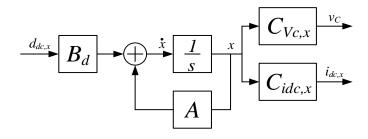

| Figure 3-11 Average-time model block diagram with capacitor voltage and                 | l dc-side |

| current outputs                                                                         | 73        |

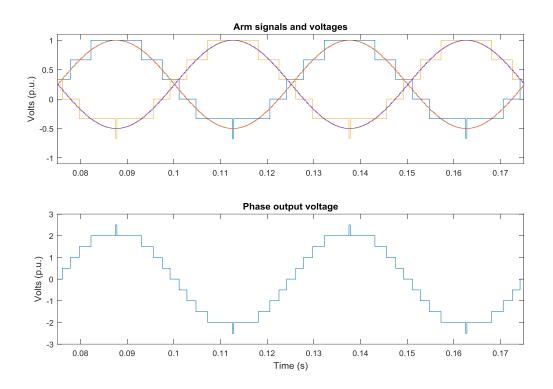

| Figure 4-1 Staircase modulation for a BMCI with 3 sub-modules and $d_{\text{dc}}$ =0.25 | 76        |

| Figure 4-2 Equivalent switch circuit of a sub-module with a full-bridge of tra          | ansistors |

|                                                                                         | 77        |

| Figure 4-3 BMCI switching states for a single leg for two neighbouring volta            | ige steps |

|                                                                                         | 77        |

| Figure 4-4 Half-bridge and full-bridge modules, their PWM modulation sign               | nals, and |

| output voltages                                                                         | 78        |

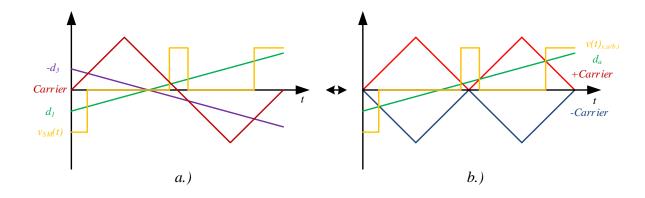

| Figure 4-5 Two modulation schemes that produce the same output voltage                  | 79        |

| Figure 4-6 Modulation and carrier signals, with resultant arm voltages                  | 80        |

|                                                                                         |           |

| Figure 4-7 Phase shifted carrier and equivalent APOD carriers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Figure 4-8 PD modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                      |

| Figure 4-9 POD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                      |

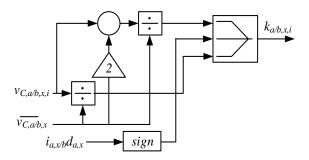

| Figure 4-10 Feedforward balancing controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                      |

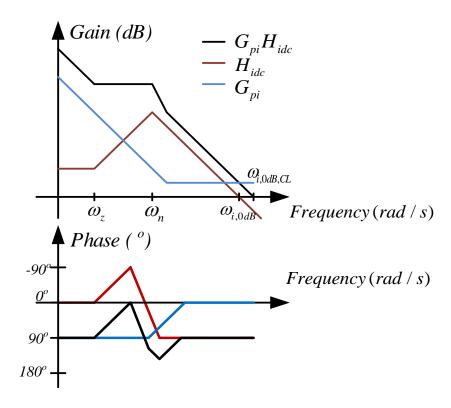

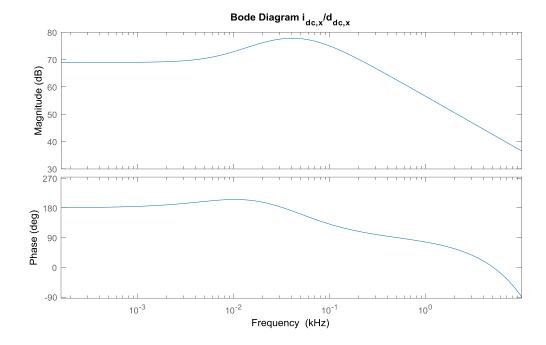

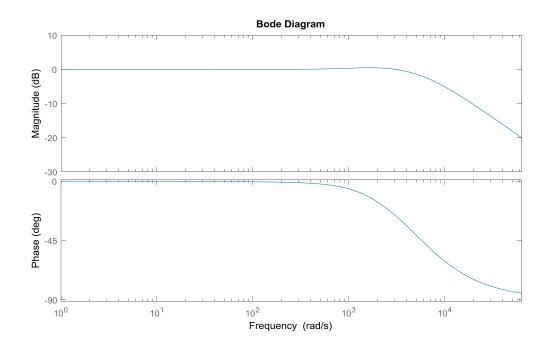

| Figure 4-11 Simplified bode plot of current transfer function, controller, and | ombined                 |

| model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 94                      |

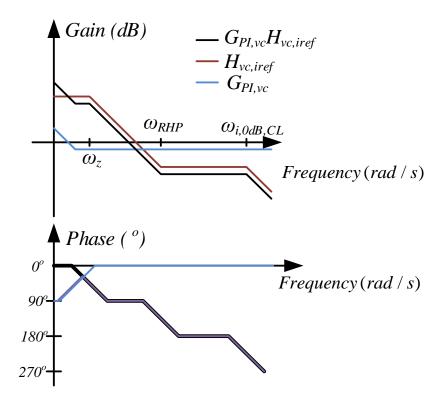

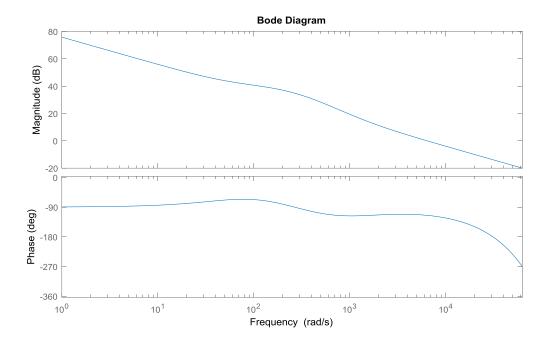

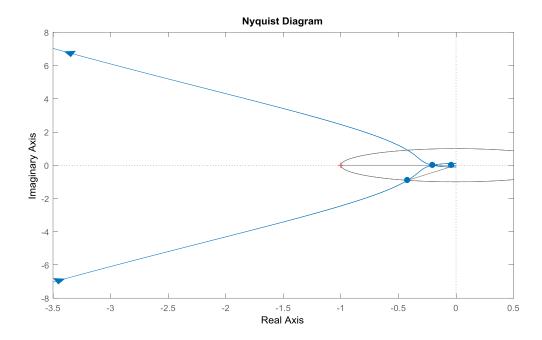

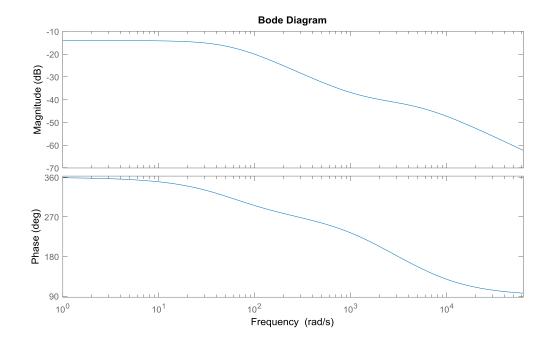

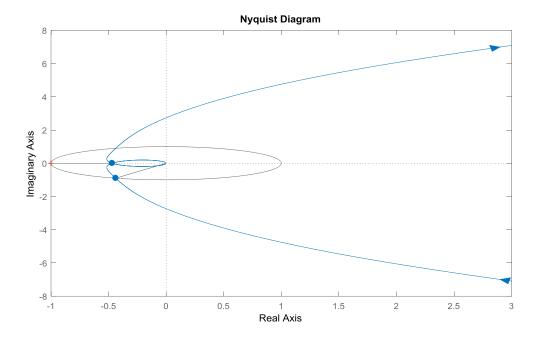

| Figure 4-12 Simplified bode plot of voltage closed loop, open loop, and comp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | pensator                |

| transfer functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98                      |

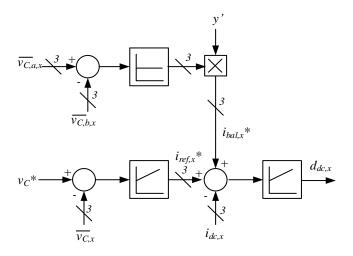

| Figure 4-13 Leg sub-module voltage controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                     |

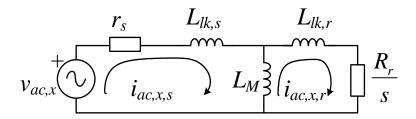

| Figure 4-14 Induction machine per phase equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101                     |

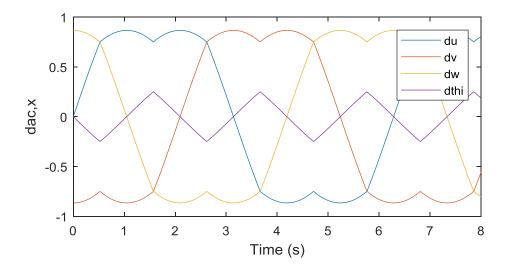

| Figure 4-15 Third harmonic injection modulation waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107                     |

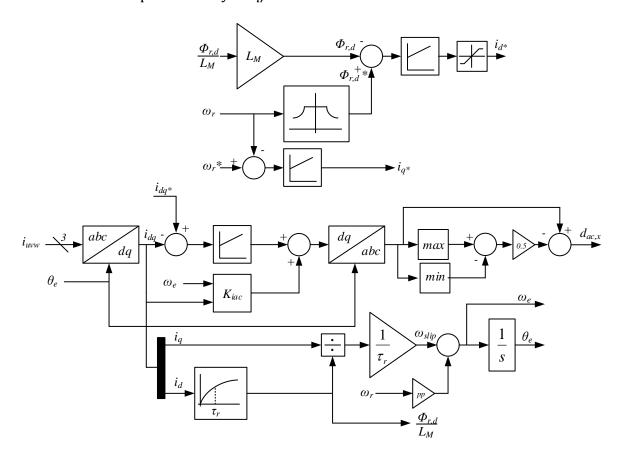

| Figure 4-16 Control system of induction motor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 108                     |

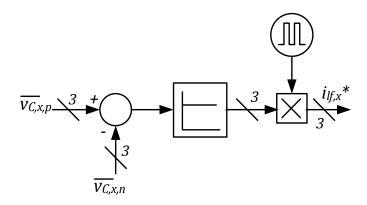

| Figure 4-17 Diagram of low-frequency arm balancing compensator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110                     |

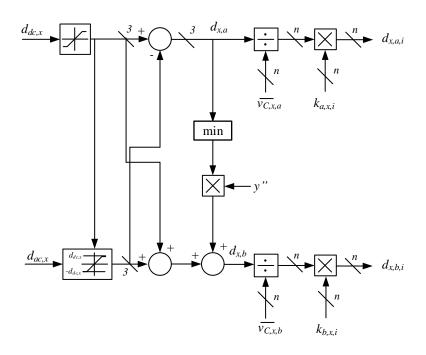

| Figure 4-18 Converter arm control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111                     |

| Figure 4-19 Effect of arm duty cycle saturation (above) on filtered arm voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (below)                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112                     |

| Figure 5-1 Basic BMCI structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116                     |

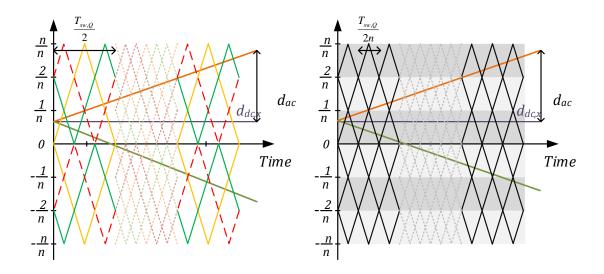

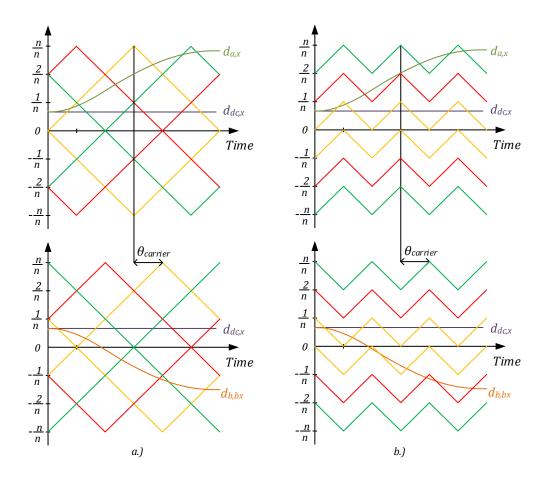

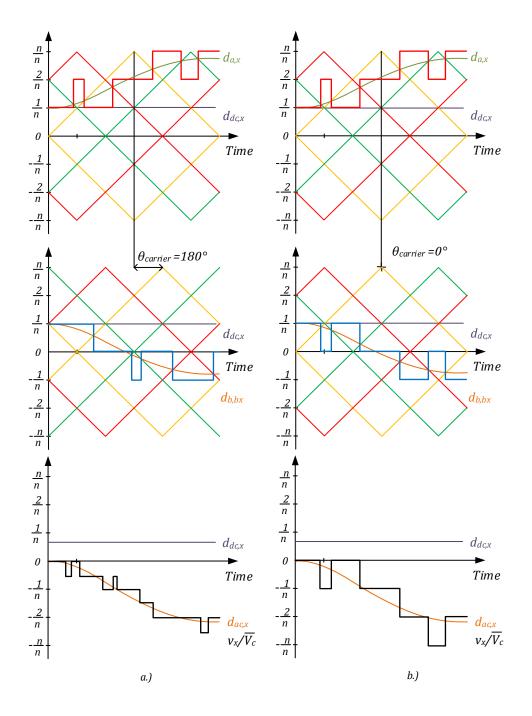

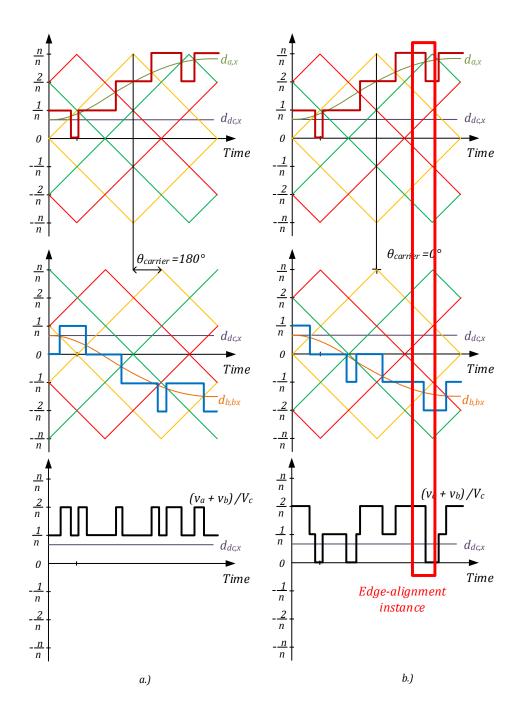

| Figure 5-2 Modulation for top and bottom converter arms, Phase shifted ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rrier a.),              |

| and Phase disposition carrier b.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 119                     |

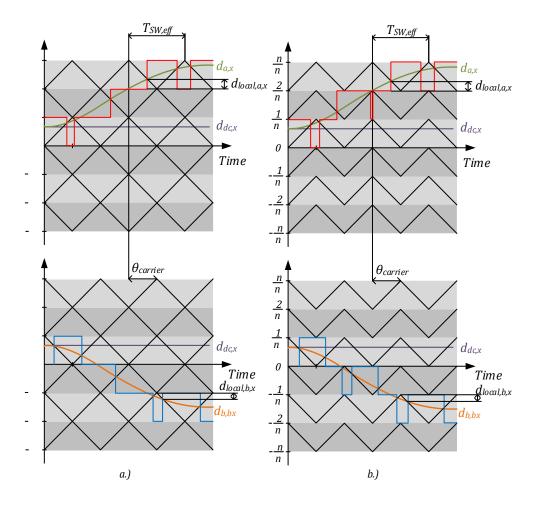

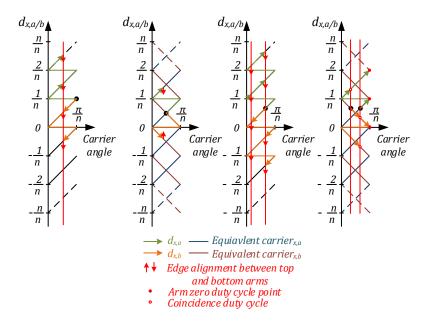

| Figure 5-3 PWM modulation using APOD carriers a.) and PDC carriers b.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120                     |

| Figure 5-4 Pulsed waveforms of arm and phase voltages, with carrier phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e shift of              |

| 180° a.) and 0° b.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121                     |

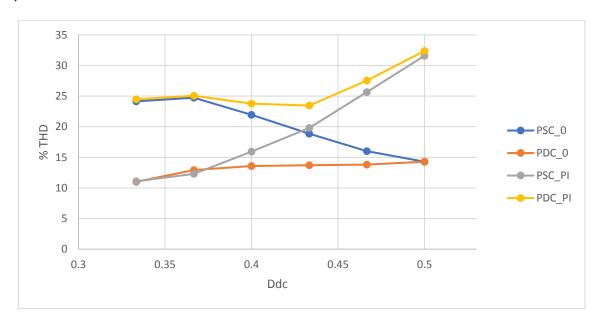

| Figure 5-5 Arm and phase voltage waveforms with $0.5/n < d_{dc,x} < 1/n$ , and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\vartheta_{carrier} =$ |

| 180° a.) or $\theta_{\text{carrier}} = 0^{\circ}$ b.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123                     |

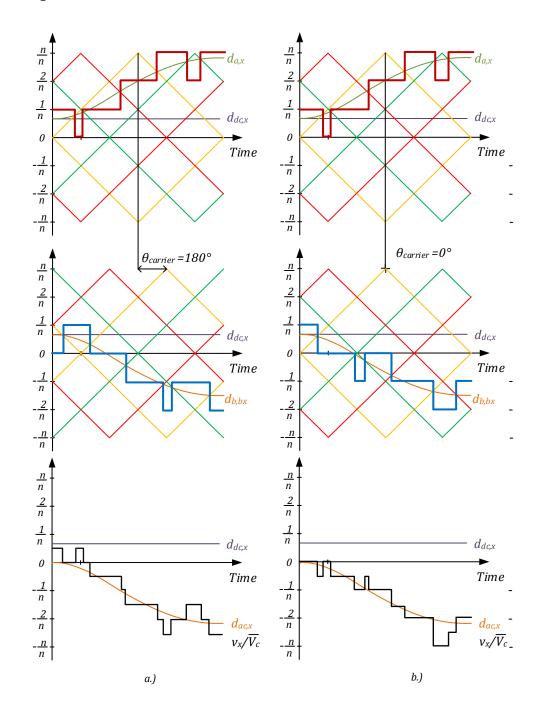

| Figure 5-6 THD results at maximum modulation index, for PSC, $\vartheta_{carrier}$ = 0°, PDC, $\vartheta_{carrier}$ = |

|-----------------------------------------------------------------------------------------------------------------------|

| 0°, PSC, θ <sub>carrier</sub> = 180°, PDC, θ <sub>carrier</sub> = 180°                                                |

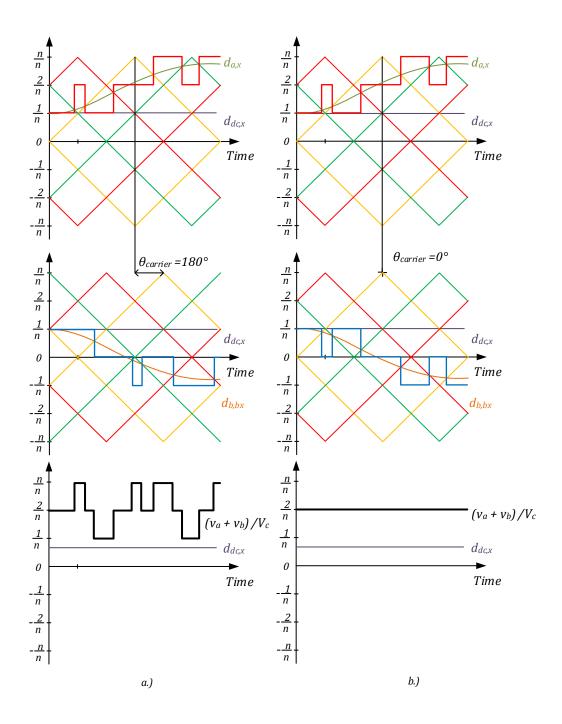

| Figure 5-7 Instantaneous arm voltages and resultant sum for $\theta_{carrier}$ = 180° a.) and                         |

| $\vartheta_{\text{carrier}} = 0^{\circ} \text{ b.}$                                                                   |

| Figure 5-8 Arm and dc voltage waveforms with $0.5/n < d_{dc,x} < 1/n$ , and $\vartheta_{carrier} = 180^\circ$         |

| a.) or $\vartheta_{carrier} = 0^{\circ}$ b.)                                                                          |

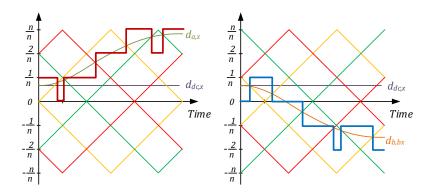

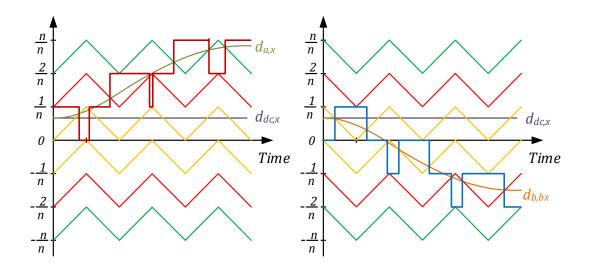

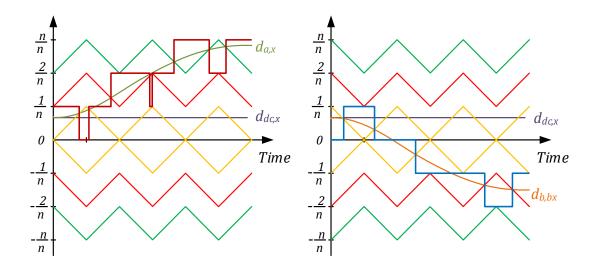

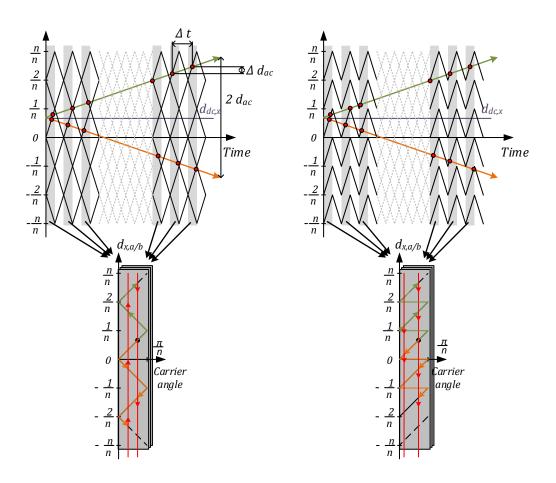

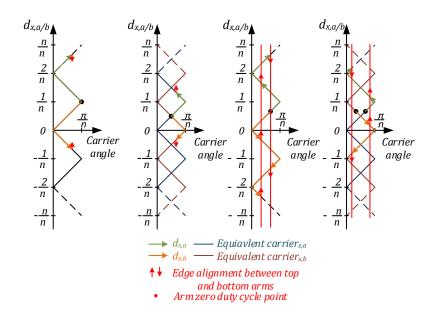

| Figure 5-9 Construction of arm duty cycle trajectory for APOD (left) and PCD(right)                                   |

| modulation129                                                                                                         |

| Figure 5-10 Duty cycle trajectories for PSC and APOD modulation130                                                    |

| Figure 5-11 Duty cycle trajectories for PDC modulation131                                                             |

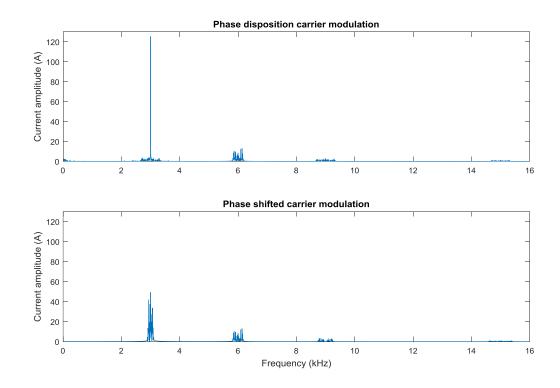

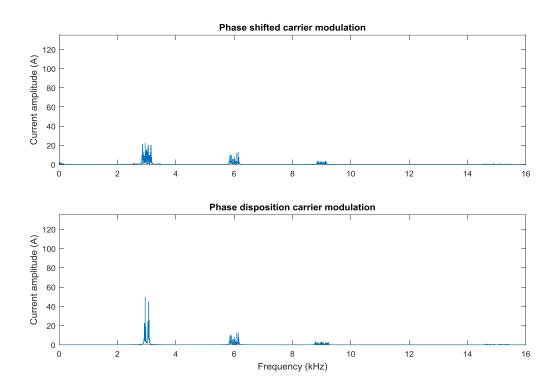

| Figure 5-12 Circulating current spectrum for PSC and PDC modulation, $\vartheta_{carrier} = 0^{\circ}133$             |

| Figure 5-13 Circulating current spectrum for PSC and PDC modulation, $\vartheta_{carrier}$ = 180°                     |

| 134                                                                                                                   |

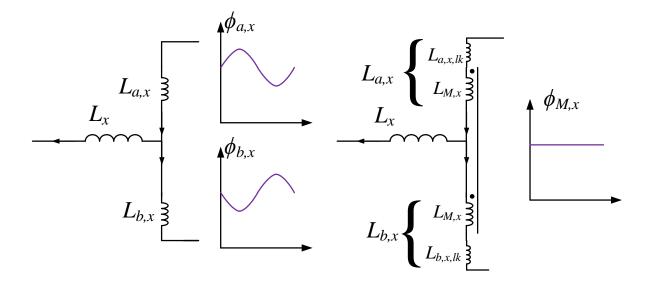

| Figure 5-14 Circuit and core flux for two separate leg inductors (left) and a single                                  |

| centre-tapped inductor (right)136                                                                                     |

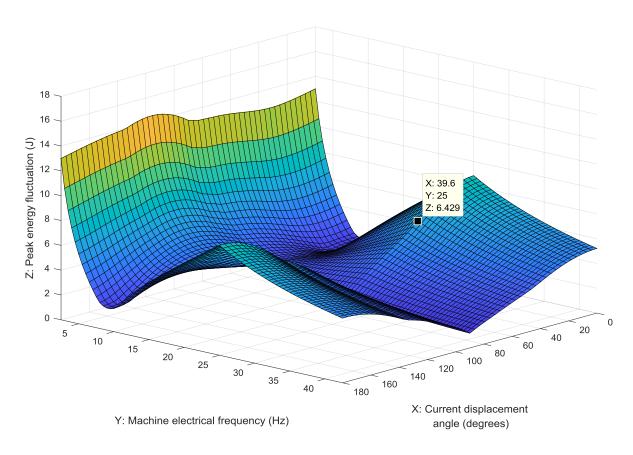

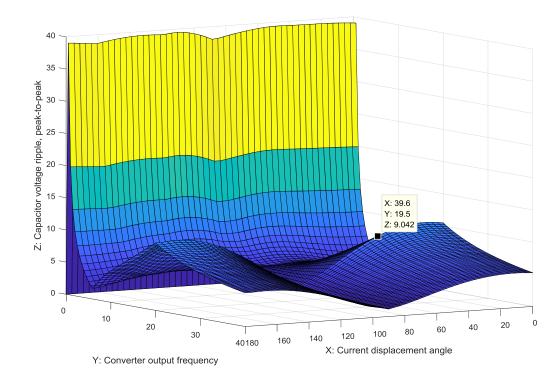

| Figure 5-15 Sub-module arm energy fluctuation for experimental prototype converter                                    |

| with value at the converter's operating point142                                                                      |

| Figure 5-16 High level diagram of prototype converter143                                                              |

| Figure 5-17 Prototype sub-module high-level diagram145                                                                |

| Figure 5-18 Single converter sub-module showing power PCB with IGBT power                                             |

| module and control card with microcontroller. The MOSFET leg is not mounted on the                                    |

| PCB                                                                                                                   |

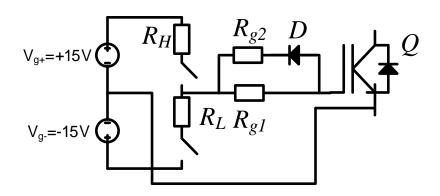

| Figure 5-19 Equivalent circuit of IGBT gate driver147                                                                 |

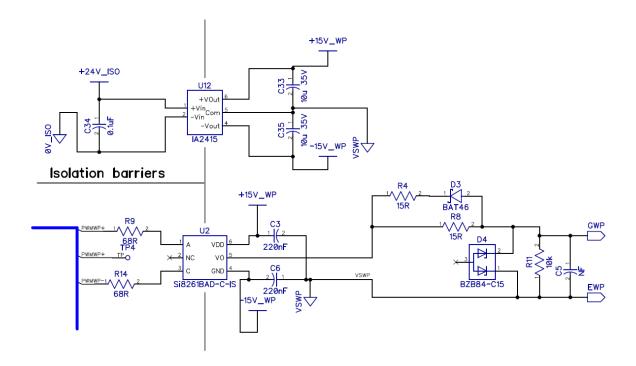

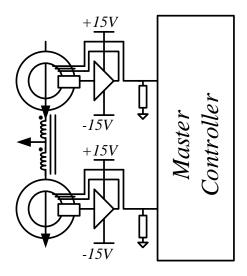

| Figure 5-20 Isolated bipolar gate driver with separately isolated power supply148                                     |

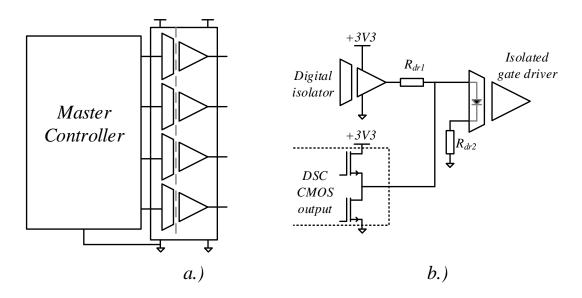

| Figure 5-21 Digital isolators a.) and drive of gate driver input b.)149                                               |

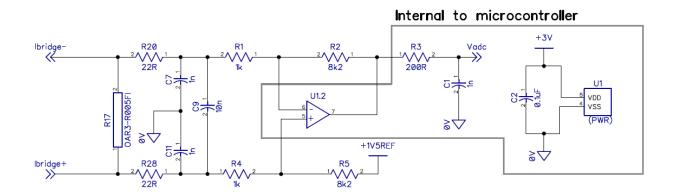

| Figure 5-22 Difference amplifier circuit with current sensing resistor R17     | 150       |

|--------------------------------------------------------------------------------|-----------|

| Figure 5-23 Current sensor design and placement with leg inductor              | 151       |

| Figure 5-24 Connections between the power stages and the controller.           | Dashed    |

| connections are virtual                                                        | 152       |

| Figure 6-1 A Midland Metro Urbos tram (source: Railwaygazette.com)             | 156       |

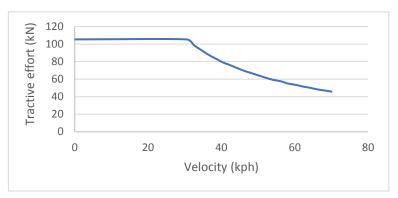

| Figure 6-2 Urbos 3 tram tractive effort chart                                  | 156       |

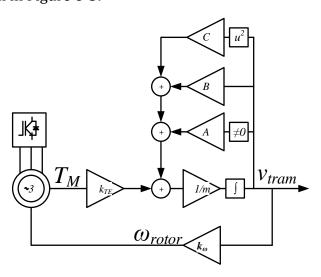

| Figure 6-3 Tram mechanical model                                               | 158       |

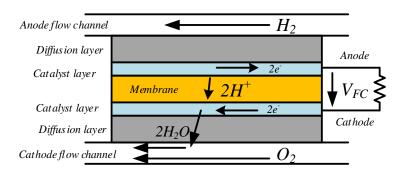

| Figure 6-4 Basic structure of a PEM fuel cell                                  | 159       |

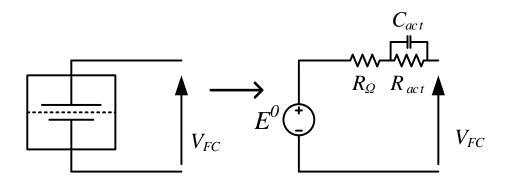

| Figure 6-5 Simplified equivalent circuit model of a fuel cell stack            | 160       |

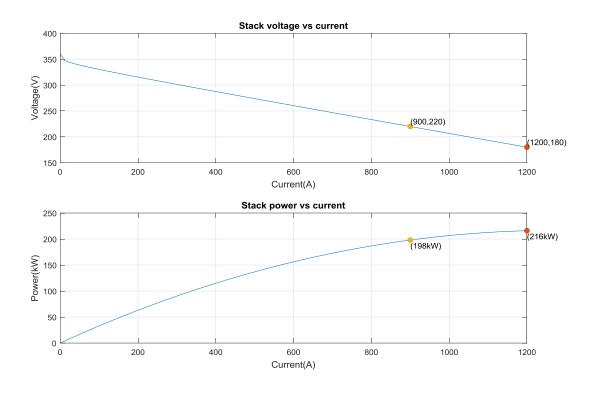

| Figure 6-6 Simulated fuel cell stack voltage-current characteristics           | 162       |

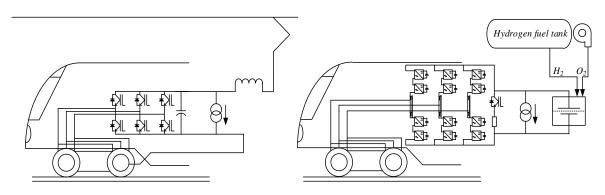

| Figure 6-7 Conventional motor drive (left) and proposed BMCI fuel cell drive   | e (right) |

|                                                                                | 162       |

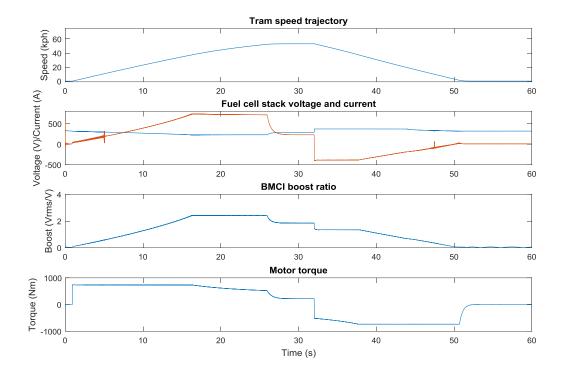

| Figure 6-8 Tram acceleration - cruising - braking cycle                        | 164       |

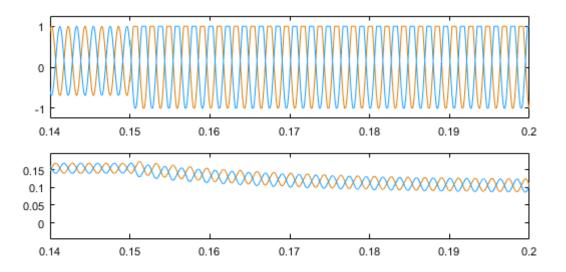

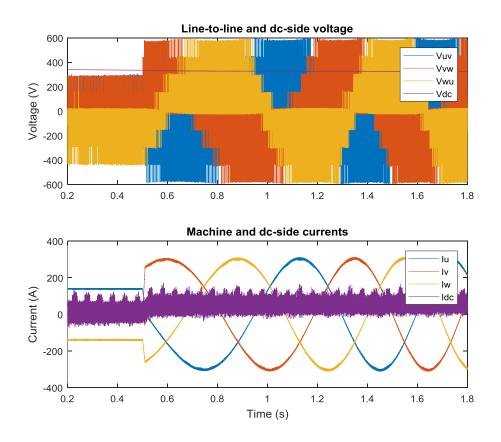

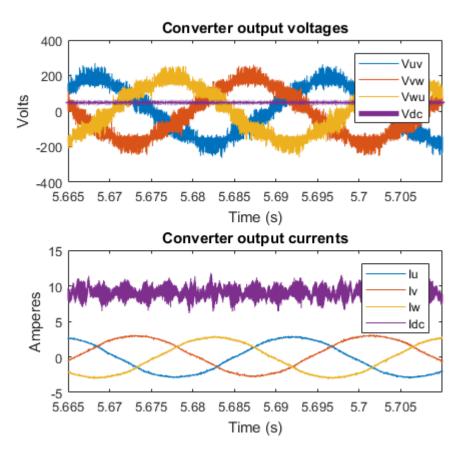

| Figure 6-9 Feedback values for the BMCI during a traction cycle                | 165       |

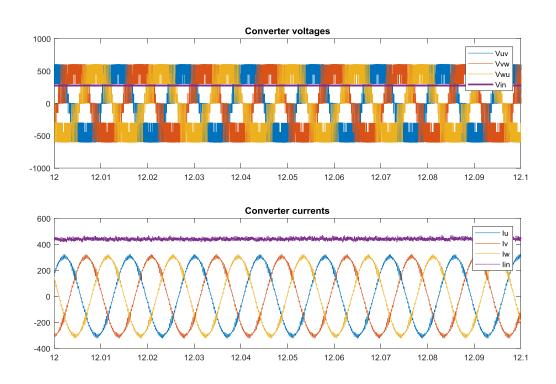

| Figure 6-10 Converter voltages and currents at start of acceleration show      | ing low   |

| distortion machine current                                                     | 166       |

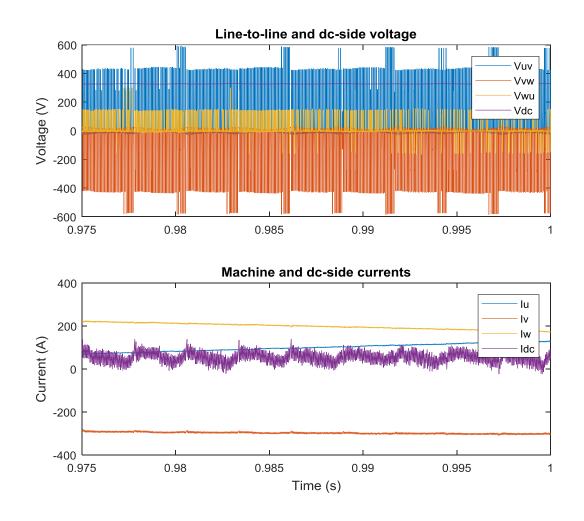

| Figure 6-11 Zoomed in capture at t=0.975s, showing dc current ripple caused    | d by the  |

| low-frequency arm-balancing currents; motor currents only show small spikes f  | rom the   |

| arm voltage step switching                                                     | 167       |

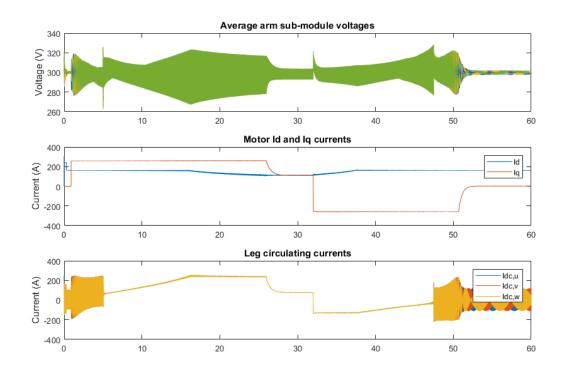

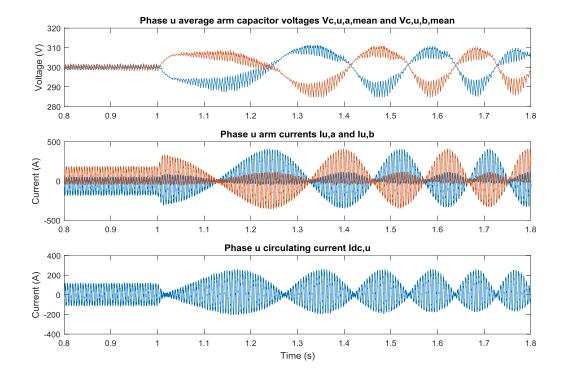

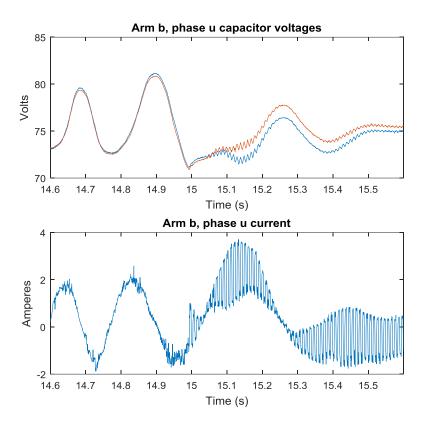

| Figure 6-12 Arm capacitor voltage, arm currents, and circulating current       | at low    |

| machine frequency                                                              | 168       |

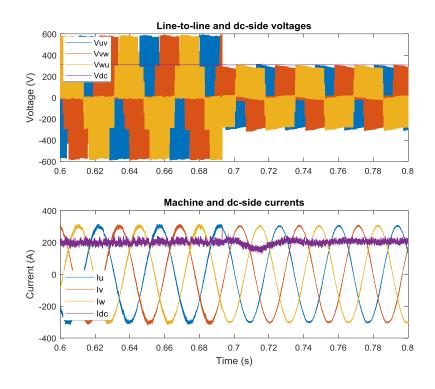

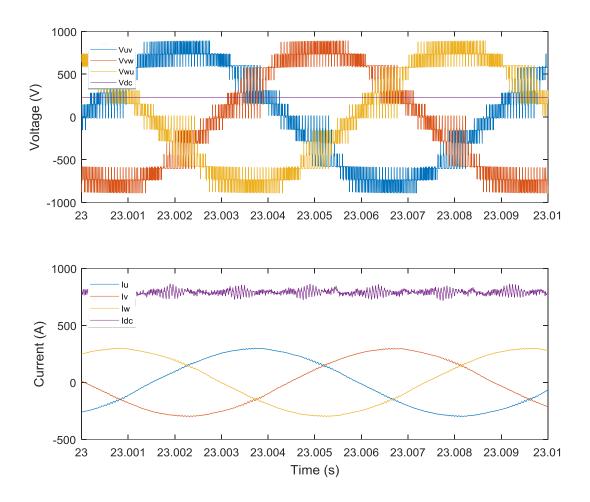

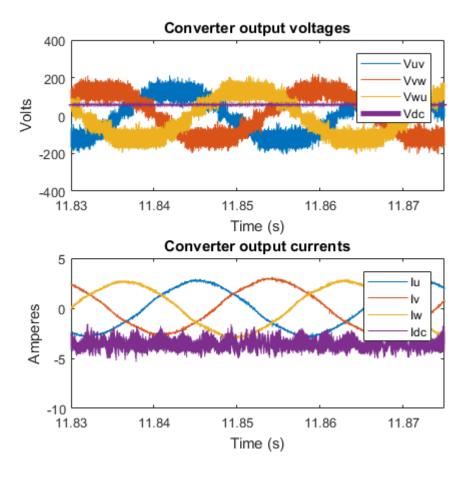

| Figure 6-13 Converter in the constant torque region, with ac-side voltage buck | k 169     |

| Figure 6-14 BMCI under ac-side voltage boost operation                         | 170       |

| Figure 6-15 BMCI terminal voltages and currents at constant output power       | 171       |

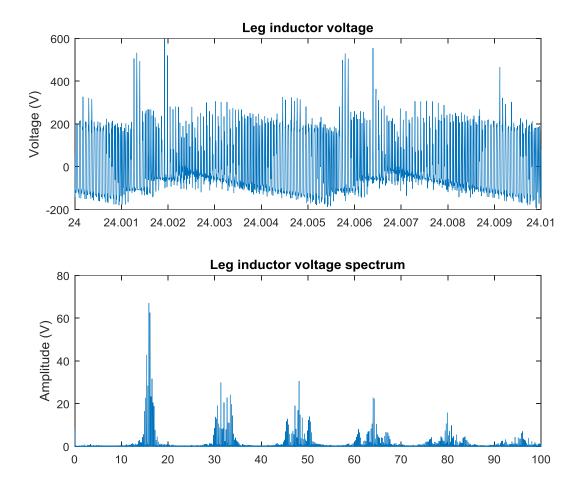

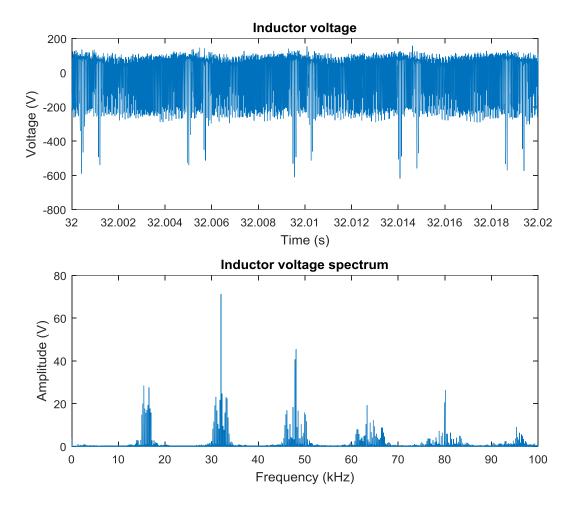

| Figure 6-16 Leg inductor voltage and its frequency spectrum during vehicle                   |

|----------------------------------------------------------------------------------------------|

| acceleration; peak component is at the arm switching frequency172                            |

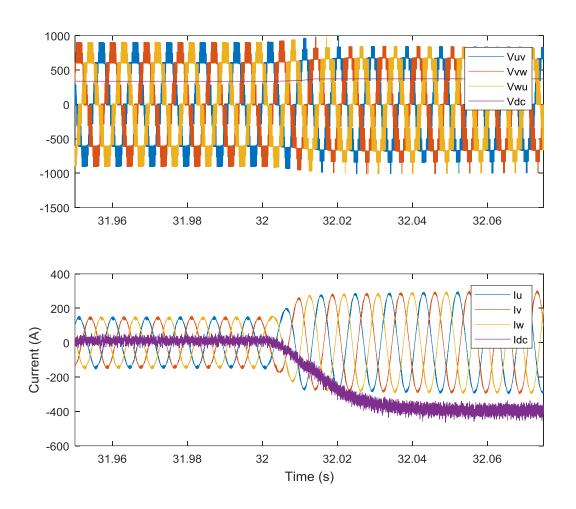

| Figure 6-17 Converter currents and voltage at start of braking; ac-side voltage              |

| waveform changes as converter is regenerating power and dc duty-cycle steady-state           |

| value is different173                                                                        |

| Figure 6-18 Phase leg voltage and its FFT spectrum during vehicle braking174                 |

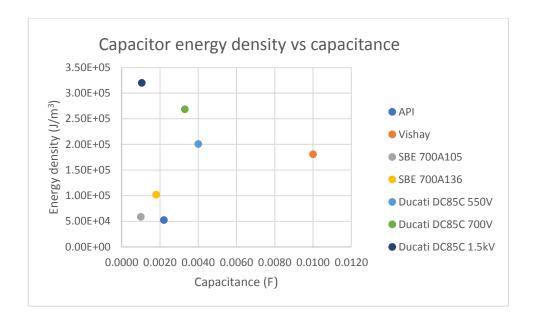

| Figure 6-19 Capacitor energy density survey178                                               |

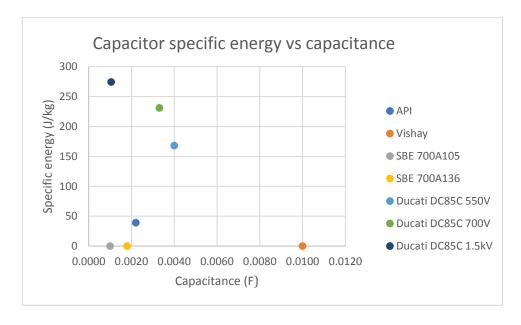

| Figure 6-20 Capacitor specific energy survey178                                              |

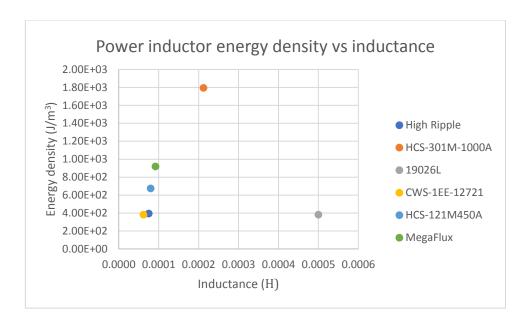

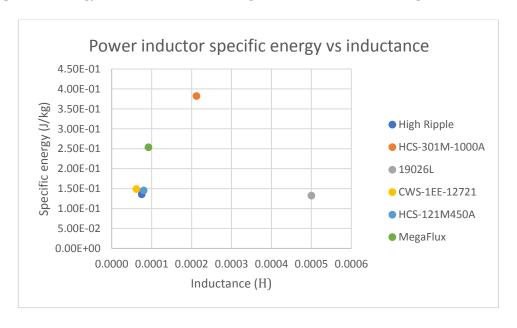

| Figure 6-21 Inductor energy density survey182                                                |

| Figure 6-22 Inductor specific energy survey182                                               |

| Figure 6-23 Specific resistance as a function of inductance184                               |

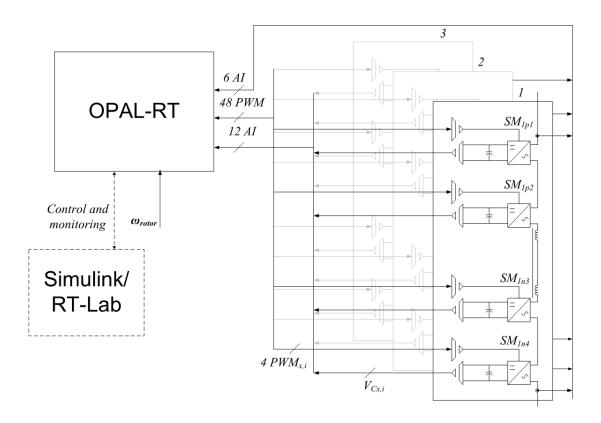

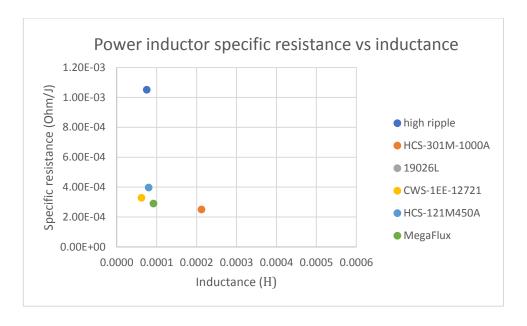

| Figure 6-24 Converter efficiency measurement setup184                                        |

| Figure 6-25 Simulated BMCI186                                                                |

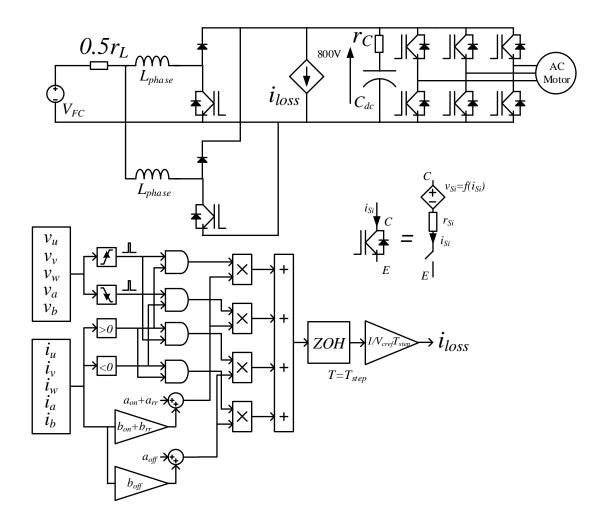

| Figure 6-26 Lossy BMCI model for a top arm with IGBT switches187                             |

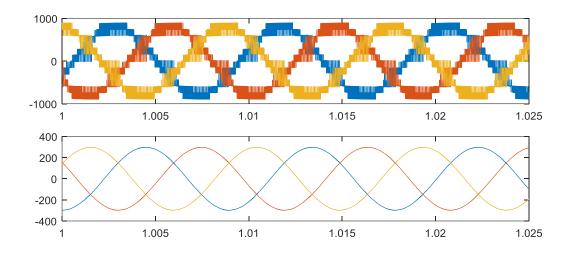

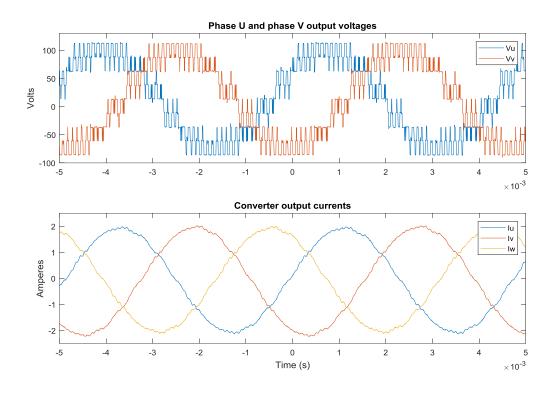

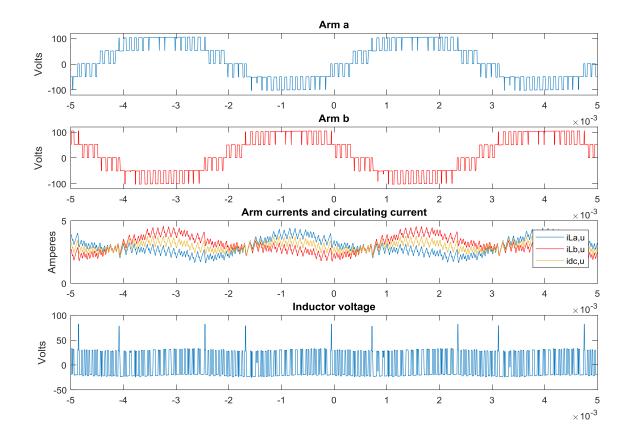

| Figure 6-27 BMCI phase-to-phase voltages and line currents189                                |

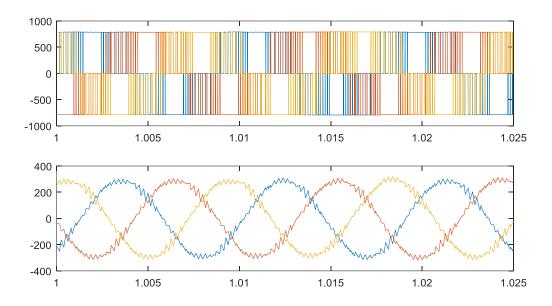

| Figure 6-28 BVSI model including conduction and switching losses192                          |

| Figure 6-29 BVSI phase-to-phase voltages and line currents193                                |

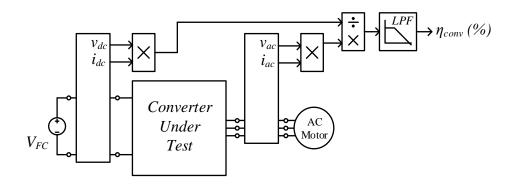

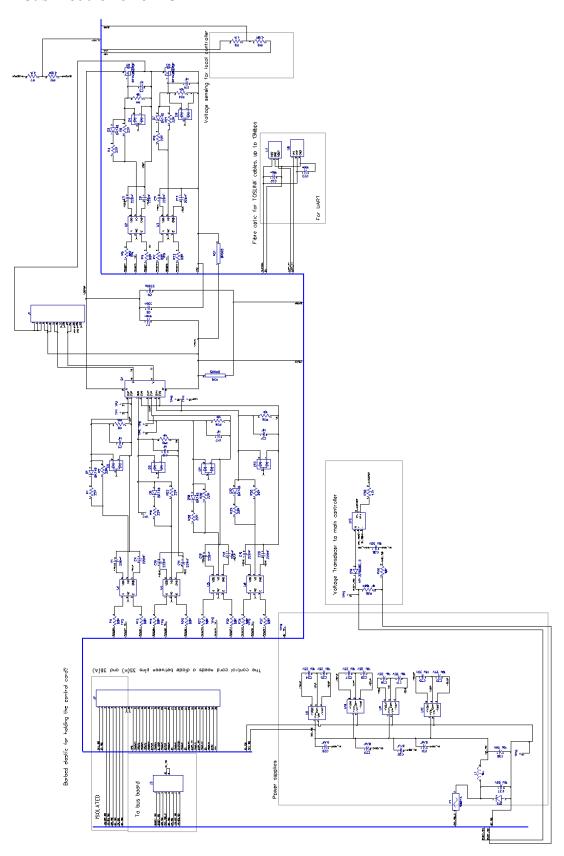

| Figure 7-1 Schematic of prototype BMCI196                                                    |

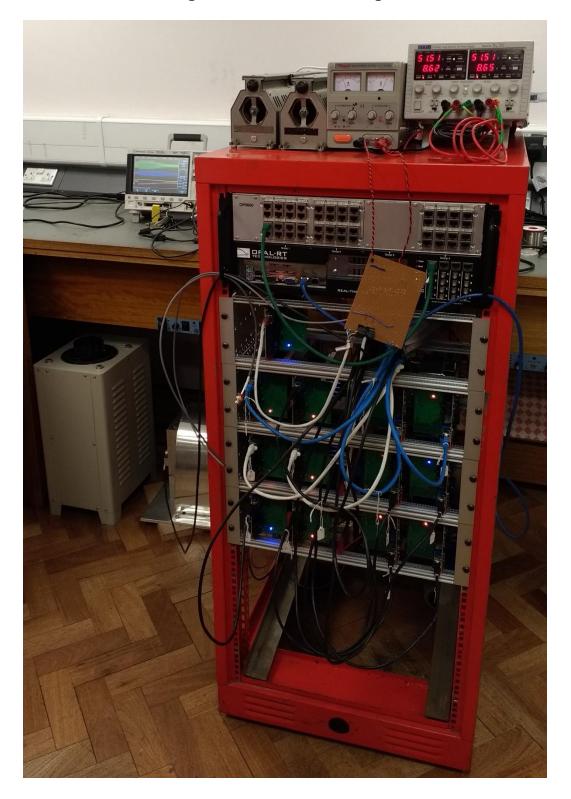

| Figure 7-2 Final setup of the converter prototype with a variac load, induction motor        |

| load, and dc power supply197                                                                 |

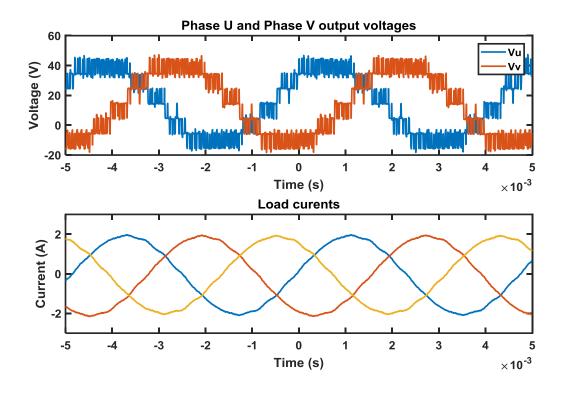

| Figure 7-3 Converter phase voltages, referenced to power supply 0V, and output               |

| currents199                                                                                  |

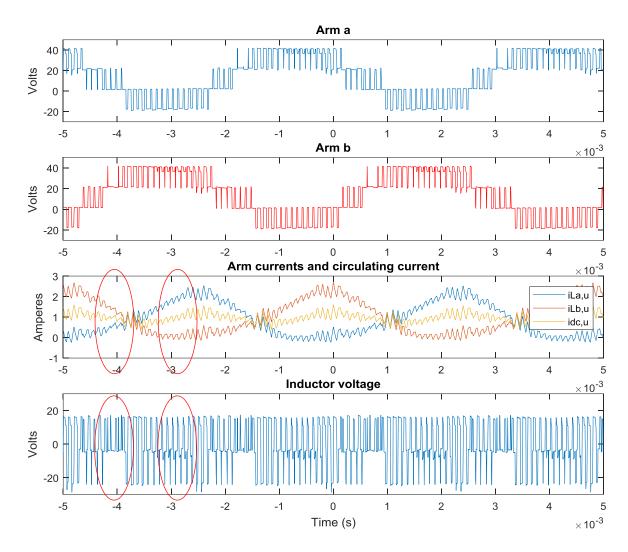

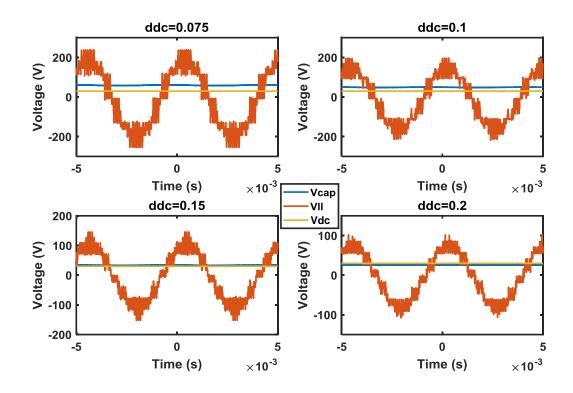

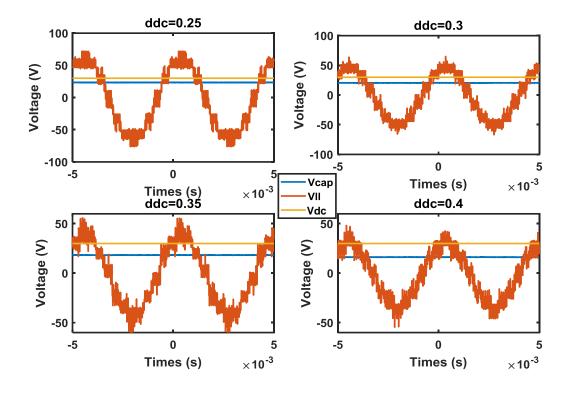

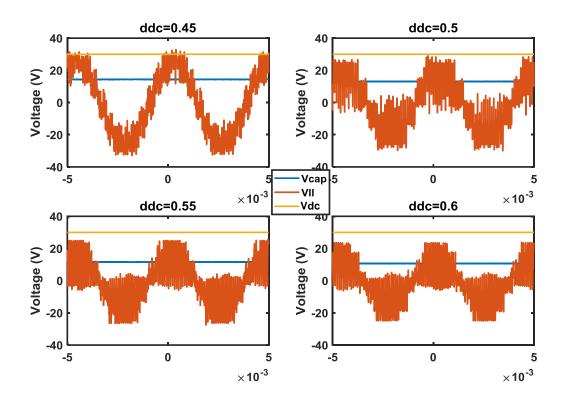

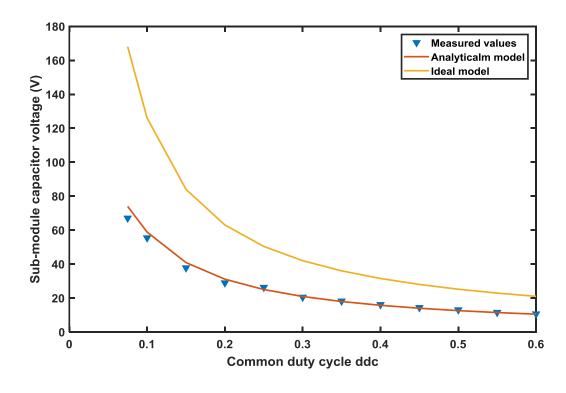

| Figure 7-4 Arm voltages and currents at $d_{\text{dc}}$ =0.3, with maximum current ripple200 |

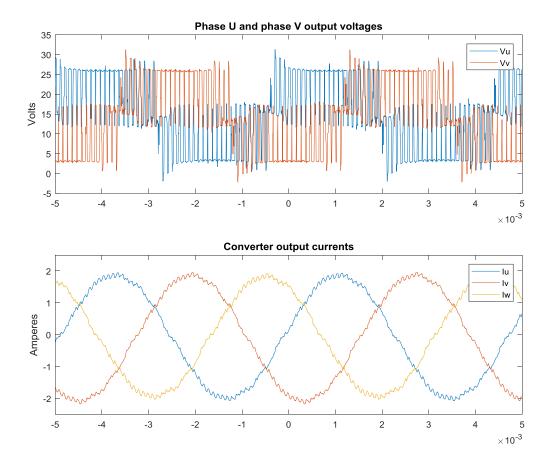

| Figure 7-5 Converter phase voltages, referenced to power supply 0V, and output               |

| currents, at d <sub>dc</sub> =0.5201                                                         |

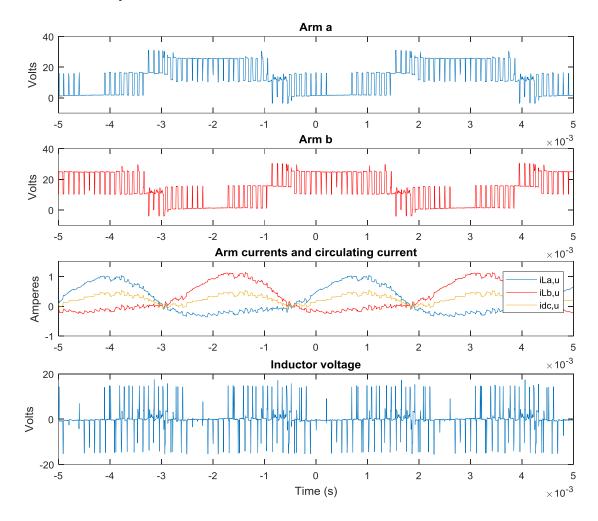

| Figure 7-6 Arm voltages and currents for d <sub>dc</sub> =0.5                          | 202       |

|----------------------------------------------------------------------------------------|-----------|

| Figure 7-7 Converter phase voltages, referenced to power supply 0V, and                | l output  |

| currents, at d <sub>dc</sub> =0.1                                                      | 203       |

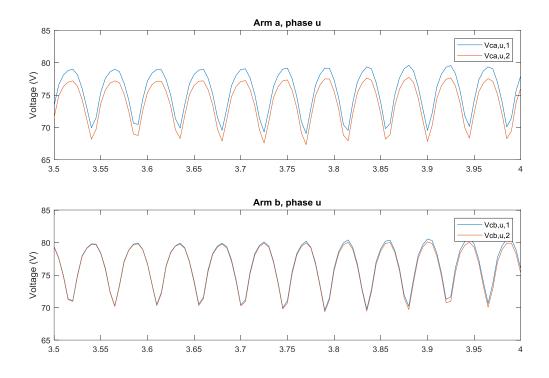

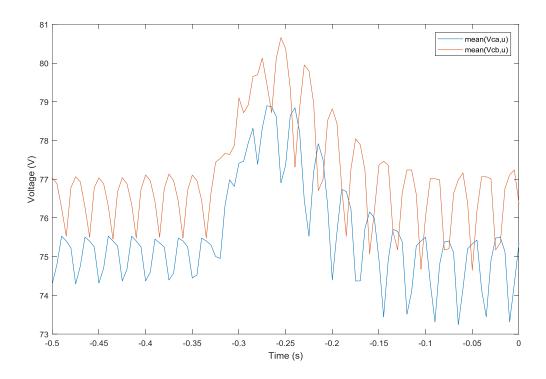

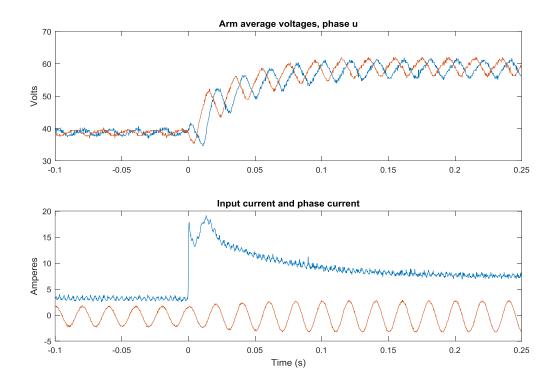

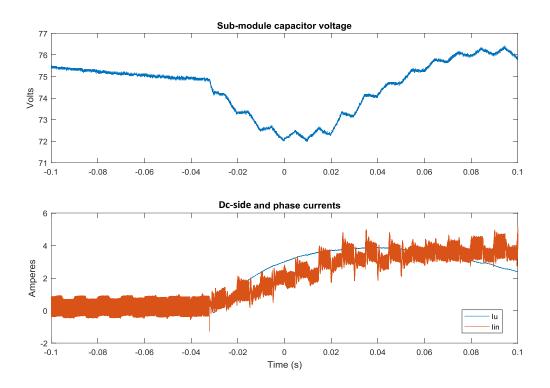

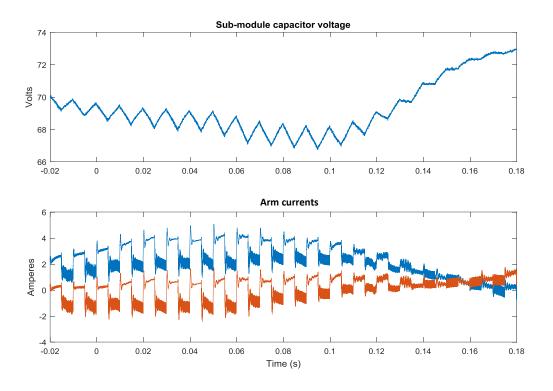

| Figure 7-8 Arm voltages and currents for ddc=0.1                                       | 204       |