# UCC Library and UCC researchers have made this item openly available. Please let us know how this has helped you. Thanks!

| Title                          | The characterization and passivation of fixed oxide charges and interface states in the Al2O3/InGaAs MOS system                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)                      | Hurley, Paul K.; O'Connor, Éamon; Djara, Vladimir; Monaghan, Scott;<br>Povey, Ian M.; Long, Rathnait D.; Sheehan, Brendan; Lin, Jun;<br>McIntyre, Paul C.; Brennan, Barry; Wallace, Robert M.; Pemble, Martyn<br>E.; Cherkaoui, Karim                                                                                                                                                                                                                                                     |

| Publication date               | 2013-09-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Original citation              | <ul> <li>Hurley, P. K., O'Connor, É., Djara, V., Monaghan, S., Povey, I. M.,</li> <li>Long, R. D., Sheehan, B., Lin, J., McIntyre, P. C., Brennan, B., Wallace,</li> <li>R. M., Pemble, M. E. and Cherkaoui, K. (2013) 'The characterization and passivation of fixed oxide charges and interface states in the</li> <li>Al2O3/InGaAs MOS system', IEEE Transactions on Device and</li> <li>Materials Reliability, 13(4), pp. 429-443. doi:</li> <li>10.1109/TDMR.2013.2282216</li> </ul> |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Link to publisher's<br>version | http://dx.doi.org/10.1109/TDMR.2013.2282216<br>Access to the full text of the published version may require a<br>subscription.                                                                                                                                                                                                                                                                                                                                                            |

| Rights                         | © 2013, IEEE. Personal use of this material is permitted. Permission<br>from IEEE must be obtained for all other uses, in any current or<br>future media, including reprinting/republishing this material for<br>advertising or promotional purposes, creating new collective works,<br>for resale or redistribution to servers or lists, or reuse of any<br>copyrighted component of this work in other works.                                                                           |

| Item downloaded<br>from        | http://hdl.handle.net/10468/13492                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Downloaded on 2022-08-26T12:36:48Z

Coláiste na hOllscoile Corcaigh

# The characterisation and passivation of fixed oxide charges and interface states in the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS system

P.K. Hurley<sup>1</sup>, E. O'Connor<sup>1</sup>, R. D. Long<sup>1,2</sup>, P. C. McIntyre<sup>2</sup>, B. Brennan<sup>3</sup>, R. M. Wallace<sup>3</sup>, V. Djara<sup>1</sup>, S. Monaghan<sup>1</sup>, B. Sheehan<sup>1</sup>, J. Lin<sup>1</sup>, I. M. Povey<sup>1</sup>, M. E. Pemble<sup>1</sup> and K. Cherkaoui<sup>1</sup>.

<sup>1</sup> Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland

<sup>2</sup> Department of Material Science and Engineering, Stanford University, Stanford, California 94305, USA

<sup>3</sup> The University of Texas at Dallas, Richardson, TX, 75080, USA

Corresponding Author: Dr Paul K Hurley, Tel: + 353 21 4904080, Fax: +353-21-490-4058, Email: paul.hurley@tyndall.ie

Keywords: High-k, InGaAs, fixed oxide charges, interface state density, CV analysis, characterisation, passivation.

#### Abstract

In this paper we present and overview of experimental results examining charged defect components in the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor (MOS) system. For the analysis of fixed oxide charge and interface state density an approach is described where the flat band voltage for *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures is used to separate and quantify the contributions of fixed oxide charge and interface state density. Based on an Al<sub>2</sub>O<sub>3</sub> thickness series (2nm to 20nm) for the *n* and *p* type In<sub>0.53</sub>Ga<sub>0.47</sub>As layers, the analysis reveals a positive fixed charge density (~9x10<sup>18</sup> cm<sup>-3</sup>) distributed throughout the Al<sub>2</sub>O<sub>3</sub> and a negative sheet charge density (-8x10<sup>12</sup>cm<sup>-2</sup>) located near the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. The interface density of the fixed oxide charge components is significantly reduced by forming gas (5% H<sub>2</sub>/95% N<sub>2</sub> ambient at 350°C for 30 min) annealing. The interface state distribution obtained from multi-frequency capacitance-voltage and conductance-voltage measurements on either MOS structures or MOSFETs indicates a peak density located around the In<sub>0.53</sub>Ga<sub>0.47</sub>As mid-gap

energy, with a sharp increase in the interface state density towards the valance band and evidence of interface state aligned with the  $In_{0.53}Ga_{0.47}As$  conduction band. The integrated density obtained from multi-frequency capacitance-voltage and conductance-voltage analysis is in good agreement with the approach of comparing the flat band voltages in *n* and *p* type  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOS structures. Finally, the paper reviews recent work based on an optimisation of the  $In_{0.53}Ga_{0.47}As$  surface preparation using (NH<sub>4</sub>)<sub>2</sub>S, combined with minimising the transfer time to the atomic layer deposition reactor for the  $Al_2O_3$ , which indicates interface state reduction and genuine surface inversion for both *n* and *p* type  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOS structures.

#### 1. Introduction

The last fifty years have witnessed dramatic developments in computing power, information storage and digital communication technologies. A significant driving force behind these developments has been the on-going miniaturisation of metal oxide semiconductor field effect transistors (MOSFETs), which represent the fundamental switching elements of integrated circuits. The scaling of MOSFETs minimum device dimensions from values of around 10  $\mu$ m in the early 1970's to values of around 65 nm in 2006 was performed to increase transistor density and switching speed and was achieved without any significant changes to the fundamental device concept or the basic SiO<sub>2</sub> and Si materials which constituted the device.

As the minimum dimensions of MOSFETs were reduced to values below around 50nm, transistor miniaturisation no longer remained as the single driving force behind the development of integrated circuits. In the recent technology generations there has been a concerted research effort to incorporated new materials into the device structure to reduce the power dissipation associated with individual MOSFETs and consequently to reduce the overall power dissipation associated with integrated circuits. The power dissipation of *n* and *p* channel MOSFETs in a Complementary MOS (CMOS) configuration is comprised of both static and dynamic components. A significant reduction in static power dissipation was achieved with the incorporation of an HfO<sub>2</sub> based high dielectric constant (high-*k*) material into the gate stack of MOSFETs to reduce gate current leakage at the 45nm technology node [1]. The dynamic power dissipation is proportional to the square of the supply voltage (V<sub>dd</sub>), and as a consequence the use of semiconductor materials or device architectures which allow V<sub>dd</sub> reduction are also being

investigated to reduce the dynamic power dissipation in CMOS inverters. One approach to reduce  $V_{dd}$  without reducing the drive current and the associated switching speed is through the use of high mobility materials, such as Ge and III-V compound semiconductors, to form the active channel region of the MOSFETs. A range of alternative semiconductors have been studied which exhibit high hole mobility (Ge [2], GaSb [3], InGaSb [4]) and high electron mobility (InGaAs [5-8], InAs [9], InSb [10]).

There are a range of challenges associated with the realisation of high channel mobility materials, which include: the understanding, control and passivation of electrically active defects at the interface between the high-*k* dielectric layer and the III-V or Ge surface, fixed oxide charges within the high-*k* oxide and traps within the oxide (border traps); the reduction of the overall source and drain contact resistance in III-V semiconductors; the integration of the high mobility materials onto a 300mm silicon platform; the control of the band to band tunnelling leakage in reduced band gap semiconductors (Ge=0.66eV, In<sub>0.53</sub>Ga<sub>0.47</sub>As =0.75eV); and finding a suitable *p* channel device when using III-V materials for both the *p* and *n* channel MOSFET.

Considering the issue of the gate stack formation, the search to find suitable dielectrics and processes to form stable III-V MOS structures with acceptable levels of electrically active interface states is not a new pursuit, with publications on GaAs MOSFETs dating back to the mid-1960's [11]. Early work focussed on chemical, thermal, or anodic oxidation of the III-V surface (GaAs), as well as sputter deposition methods [12-14]. More recent work has focussed on the use of atomic layer deposition (ALD) for the formation of high-*k* oxides on III-V surfaces [15]. In the case of MOS systems formed on GaAs [16] and on In<sub>x</sub>Ga<sub>1-x</sub>As (x: 0.3 to 0.15) [17] surfaces the capacitance-voltage (C-V) response is generally dominated by a high level of dispersion of the capacitance with frequency consistent with a high (>10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup>) density of interface states (D<sub>it</sub>) at the high-*k*/In<sub>x</sub>Ga<sub>1-x</sub>As (x: 0, 0.15, 0.3) interface. Analysis of the C-V response at a reduced temperature of 77K [18] confirms that the Fermi level is strongly pinned at high-*k*/GaAs and high-*k*/In<sub>x</sub>Ga<sub>1-x</sub>As (x: 0.15 to 0.3) interface. A significant reduction of D<sub>it</sub> and a genuine demonstration of surface inversion at the high-*k*/GaAs interface can be achieved through the use of gallium sub oxide (Ga<sub>2</sub>O) deposition onto an oxide free GaAs surface using an ultra-high vacuum environment [19, 20]. Similar results can also be achieved using silicon

interlayers inserted between the GaAs surface and the oxide layer [21, 22]. However, these results demonstrating genuine surface accumulation and inversion have not been replicated to date using ALD to form the high-k gate oxide on GaAs.

When moving to MOS systems formed on  $In_{0.53}Ga_{0.47}As$  surfaces, (which is a lattice matched indium concentration to InP), a range of publications demonstrate modulation of the surface Fermi level with the gate voltage and genuine surface accumulation in MOS capacitors formed on *n*-type  $In_{0.53}Ga_{0.47}As$  [17, 23-25]. However, the multi-frequency C-V response of the  $In_{0.53}Ga_{0.47}As$  MOS capacitors for a range of ambient temperatures still indicates the influence of an interface defect response, and interface state densities around the  $In_{0.53}Ga_{0.47}As$  mid-gap energy are typically reported to be in the range mid- $10^{12}$  to  $2x10^{13}$ cm<sup>-2</sup>eV<sup>-1</sup> [26-29]. Analysis of C-V response of  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOS structures also indicates the presence of fixed positive oxide charges [30, 31] within the oxide layer. In addition to fixed oxide charge and interface states, dispersion in the C-V response of  $In_{0.53}Ga_{0.47}As$  MOS for samples biased in accumulation has been attributed to the effect and defects located within the oxide near the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface (sometimes referred to as border traps [32]), which can communicate with the conduction and valence bands of the In<sub>0.53</sub>Ga<sub>0.47</sub>As by a tunnelling process [33, 34].

As charges in the bulk of the oxide and interface states affect MOSFET performance, stability and long term reliability, it is important to characterize and understand the various defect components. The objective of this paper is to provide an overview of charged defect quantification in the  $In_{0.53}Ga_{0.47}As$  MOS system. The paper will firstly review a method to separate fixed oxide charges and interface states based on the determination of the flat band capacitance for *n* and *p* type  $In_{0.53}Ga_{0.47}As$  MOS structures. Following this section, the paper will provide a summary of the interface state density distribution across the energy gap as determined from the analysis of MOS capacitors and MOSFETs. Finally, the paper will cover approaches which have been studied to reduce the interface state density in  $In_{0.53}Ga_{0.47}As$  MOS system, and demonstrate that following an optimized  $In_{0.53}Ga_{0.47}As$  surface preparation interface state densities can be reduced to a level which results in a C-V response consistent with genuine surface inversion for both *n* and *p* type  $In_{0.53}Ga_{0.47}As$  MOS structures. The paper will focus on the case of the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system, as experimental results [23, 24], supported by theoretical calculations [35] indicate that Al<sub>2</sub>O<sub>3</sub> reduces the concentration of electrically active states at the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. Moreover, the process of forming Al<sub>2</sub>O<sub>3</sub> on the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface using trimethylaluminum (TMA) [Al(CH<sub>3</sub>)<sub>3</sub>] and H<sub>2</sub>O results in a reduction of the native oxides on the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface [15] through a process of ligand exchange [36]. As a consequence, the use of Al<sub>2</sub>O<sub>3</sub> deposited by ALD is representative of the best interfacial properties reported to date for the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system. While Al<sub>2</sub>O<sub>3</sub> exhibits a relatively low *k* value (8 to 8.6), the equivalent oxide thickness (E<sub>OT</sub>) of the gate stack can be reduced by utilizing a bi-layer oxide approach where the Al<sub>2</sub>O<sub>3</sub> is used as an interfacial control layer and an oxide with a higher *k* value (e.g., HfO<sub>2</sub>) is subsequently deposited to achieve a scaled E<sub>OT</sub> [37, 38].

#### 2. Experimental Sample Details

The experimental results and analysis presented in this paper are based on both Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors and *n*-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSETs. For the case of the MOS capacitor samples  $In_{0.53}Ga_{0.47}As$  epitaxial layers of  $2\mu m$  in thickness were grown by metal organic vapour phase epitaxy (MOVPE) on InP (100) substrates. For the case of the ntype samples the In<sub>0.53</sub>Ga<sub>0.47</sub>As layers were doped with sulphur to ~  $4x10^{17}$ cm<sup>-3</sup> on heavily *n*doped (S at  $\sim 2 \times 10^{18} \text{ cm}^{-3}$ ) InP substrates. For the corresponding p type samples the In<sub>0.53</sub>Ga<sub>0.47</sub>As layers were doped with zinc to ~  $4x10^{17}$ cm<sup>-3</sup> on heavily *p*-doped (Zn at ~ $2x10^{18}$ cm<sup>-3</sup>) InP substrates. Experimental results are reported for samples with and without chemical treatments of the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface prior to the atomic layer deposition of the Al<sub>2</sub>O<sub>3</sub> layer. For the samples with chemical treatment prior to oxide deposition, the In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces were initially degreased by sequentially rinsing for 1 min each in acetone, methanol, and isopropanol. Before the  $Al_2O_3$  deposition, the samples were immersed in  $(NH_4)_2S$  solutions (10% in deionized H<sub>2</sub>O) for 20 min at room temperature (~295K). The 10% (NH<sub>4</sub>)<sub>2</sub>S surface preparation approach for 20 minutes and room temperature was found to be the optimum to suppress the formation of In<sub>0.53</sub>Ga<sub>0.47</sub>As native oxides and to reduce the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface state density [39, 40]. The optimum of 10% (NH<sub>4</sub>)<sub>2</sub>S was subsequently confirmed to yield improvements in fully fabricated planar and 3D In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs [41]. Following the 10% (NH<sub>4</sub>)<sub>2</sub>S surface preparation the samples were introduced to the atomic layer deposition (ALD) chamber. Results are presented where the transfer time from the aqueous (NH<sub>4</sub>)<sub>2</sub>S solution to the ALD chamber varied between 3 and 30 minutes. The Al<sub>2</sub>O<sub>3</sub> dielectric was deposited by ALD at temperatures in the range 270 to 300°C using TMA and H<sub>2</sub>O. The TMA pulse was the first pulse in the ALD process. A range of Al<sub>2</sub>O<sub>3</sub> thickness values from 5 nm to 20 nm were fabricated. Results are presented for samples with Ni(60nm)/Au(40nm) metal gates formed by electron beam evaporation and a lift-off process [24, 39], and for samples with a Pt gate (75nm) formed by electron beam evaporation through a shadow mask [31].

For the analysis based on surface-channel MOSFETs, the devices were fabricated on a 2-µmthick Zn-doped ( $4 \times 10^{17}$  /cm<sup>3</sup>) *p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As layer grown on *p*+ InP (100) wafer by metalorganic vapor phase epitaxy (MOVPE). The In<sub>0.53</sub>Ga<sub>0.47</sub>As surface passivation prior to gate oxide deposition was an immersion in 10% (NH<sub>4</sub>)<sub>2</sub>S at room temperature for 20 min (transfer time < 5 minutes). A 10-nm-thick Al<sub>2</sub>O<sub>3</sub> gate oxide film was formed by ALD using alternating pulses of TMA and H<sub>2</sub>O precursors at 250°C. The source and drain (S/D) regions were selectively implanted with a Si dose of  $1 \times 10^{14}$  cm<sup>-2</sup> at 80 keV and  $1 \times 10^{14}$  cm<sup>-2</sup> at 30 keV. Implant activation was achieved by rapid thermal anneal (RTA) at 600°C for 15 s in a N<sub>2</sub> atmosphere [42]. A 200-nm-thick Pd gate was defined by electron beam evaporation and lift-off. Non-self-aligned ohmic contacts were defined by selective wet etching of the Al<sub>2</sub>O<sub>3</sub> in dilute HF and electron beam evaporation of an Au (14 nm)/Ge (14 nm)/Au (14 nm)/Ni (11 nm)/Au (200 nm) metal stack. It is noted that MOS capacitors were also included in the MOSFET fabrication process flow. Further details can be found in [43].

The C-V and conductance-voltage (G-V) measurements were recorded using either an HP4284A, CV enabled B1500, or an E4980 Agilent LCR meter. The measurements, from -50°C to 25°C, were performed on-wafer in a microchamber probe station (Cascade Microtech, model Summit 12971B) in a dry air, dark environment (dew point < -65°C).

### 3. Charge Separation and Quantification at the Flat Band Voltage (V<sub>fb</sub>)

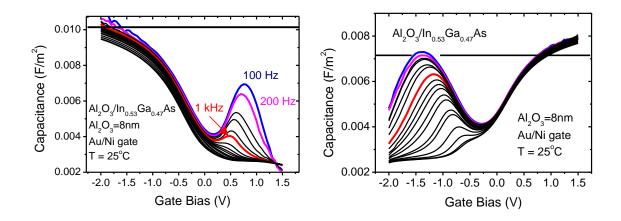

The results in Figures 1 (a) and 1 (b) provide representative multi-frequency C-V responses (100 Hz to100 kHz) for Au/Ni/Al<sub>2</sub>O<sub>3</sub>(8nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors for *p*-type and *n*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As layers, respectively. The samples received a 10% (NH<sub>4</sub>)<sub>2</sub>S surface preparation for

20 minutes and room temperature, with a 7 minute transfer time to the ALD system. The C-V responses demonstrate a range of features which are generally representative of  $In_{0.53}Ga_{0.47}As$  MOS structures. Considering the case of the *n*-type  $In_{0.53}Ga_{0.47}As$  MOS structure as shown in Figure 1 (b). In the nominally accumulated region of the C-V (V > 0.5 V) the sample exhibits a relatively low level of frequency dispersion (1.0 % per decade). The black horizontal line represents the theoretical maximum low frequency capacitance calculated using a Poisson-Schrodinger C-V simulation based on the  $In_{0.53}Ga_{0.47}As \Gamma$  Valley only [44]. Upon cooling the sample down to 77K the capacitance (V > 0.5 V) exhibits very little change (for example see [18]), and this observation is consistent with genuine surface accumulation of electrons at the Al<sub>2</sub>O<sub>3</sub>(8nm)/*n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As interface as opposed to capacitance dominated by an interface defect response. It is noted that the measured capacitance exceeds the theoretical maximum low frequency capacitance, which will be discussed further in section 4.

In the gate voltage region from -0.5V to -2 V the C-V exhibits a frequency dependent distortion, where the capacitance moves through a peak value and subsequently decreases with increasing negative gate voltage. This observation is typical of *n*-type  $In_{0.53}Ga_{0.47}As$  MOS structures and has been observed for a range of oxides, including: Al<sub>2</sub>O<sub>3</sub> [45], SiO<sub>2</sub> [46], HfO<sub>2</sub> [17], LaAlO<sub>3</sub> [47], Si<sub>3</sub>N<sub>4</sub> [48] and SrTaO<sub>6</sub> [49]. This type of C-V response is characteristic of an interface state distribution which exhibits a peak density at a specific energy level in the  $In_{0.53}Ga_{0.47}As$  band gap [50], and is discussed further in section 4 of the paper. It is noted that when higher D<sub>it</sub> levels are present and/or thicker oxides are used, the effect is to stretch out the D<sub>it</sub> response along the gate voltage axis, and a clear peak in the C-V may not be observed in this case [51].

The C-V behaviour of the MOS structure is influenced by fixed oxide charges, interface states and defects within the oxide (border traps). The conventional approach to determine the interface state density and the fixed oxide charge density is to determine the two quantities separately from multi-frequency C-V and G-V responses and the flat band voltage (V<sub>fb</sub>) respectively. In this section we will review an approach reported in [31], where the fixed oxide charge and the integrated interface state density across the energy gap (in units [cm<sup>-2</sup>]) can be separated and quantified based on the experimental flat band voltage for *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS structures.

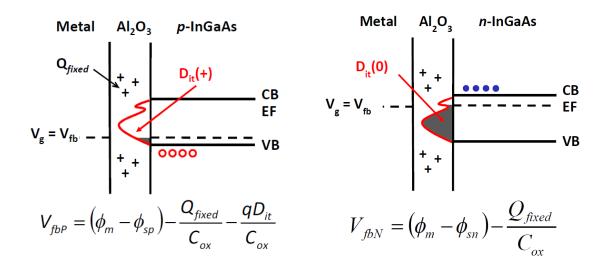

The concept behind the approach is illustrated in Figures 2 (a) and 2 (b), where the flat band condition is represented on a schematic energy band diagram for p and n type  $In_{0.53}Ga_{0.47}As$ structures respectively. For the sake of illustration, it is assumed in Figure 2 that the interface states are donor (0/+) type. Considering first the fixed oxide charge (Q<sub>fixed</sub>) component, it is reasonable to assume that the fixed oxide charge density and distribution in the high-k layer (Al<sub>2</sub>O<sub>3</sub> in this case), will not depend on the dopant type of the InGaAs, as the dopant concentration of  $4 \times 10^{17}$  cm<sup>-3</sup> represents one dopant atom for approximately every  $10^5$  In, Ga or As substrate atoms. The charge associated with the interface state density at the flat band condition, however, will depend on the nature and density of the interface states. The position of the Fermi level  $(E_F)$  at the flat band condition relative to the conduction band edge  $(E_C)$  or valence band edge ( $E_V$ ) is set by the semiconductor doping concentration. For In<sub>0.53</sub>Ga<sub>0.47</sub>As with a doping concentration of  $4 \times 10^{17}$  cm<sup>-3</sup>, as presented in this work, the Fermi level (E<sub>F</sub>) at flat band condition is close to the band edges, with  $E_C-E_F \sim 0.04$  eV and  $E_F-E_V \sim 0.04$  eV for the n and p type  $In_{0.53}Ga_{0.47}As$ , respectively. Consequently, the Fermi level position at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface, at the flat band voltage (V<sub>fb</sub>), in n and p doped In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures  $(4x10^{17} \text{ cm}^{-3})$ , spans the majority of the  $In_{0.53}Ga_{0.47}As$  energy gap. Consequently, the interface states are primarily unoccupied for a *p*-type substrate and primarily occupied for the *n*-type substrate. The corresponding equations for the flat band voltages are shown in Figures 2(a) and 2(b).

This provides an approach to quantify and separate the fixed oxide charge and interface state density contributions. From the equations for the respective flat band voltages for the p (V<sub>fbp</sub>) and n (V<sub>fbn</sub>) samples, as shown in Figures 2 (a) and 2 (b), by subtraction of V<sub>fbn</sub> and V<sub>fbp</sub>, the fixed oxide charge term and the metal work function in contact with the oxide are eliminated, and the resulting equation is below,

$$V_{fbN} - V_{fbP} = \left(\phi_{sp} - \phi_{sn}\right) + \frac{qD_{it}}{C_{ox}}$$

(1)

Consequently, the magnitude of the difference between  $V_{fbn}$  and  $V_{fbp}$  represents the magnitude of  $D_{it}$  integrated across the energy gap in units of  $[cm^{-2}]$ . The sign of  $(V_{fbN} - V_{fbP}) - (\phi_{sp} - \phi_{sn})$ indicates if the interface states are net donor or net acceptor type. Once  $D_{it}$  is evaluated it can be substituted back into the individual equation for  $V_{fbp}$  and  $V_{fbn}$  in Figures 2(a) and 2(b). Alternatively, if a value for the work function of the metal on the oxide is known or assumed, the total charge density at the flat band voltage ( $Q_{fixed} + qD_{it}$ ) can be determined in each case and the difference in the calculated values yields the interface state density ( $qD_{it}$ ).

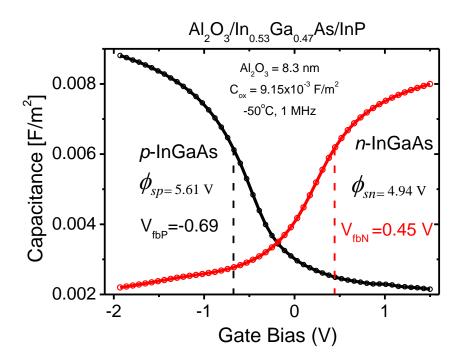

For this approach, it is necessary to perform the electrical measurements under conditions which minimise the capacitance contribution of the interface states ( $C_{it}$ ) and/or border traps ( $C_{bt}$ ) to the overall measured capacitance, allowing a determination of the flat band capacitance and corresponding flat band voltage. In order to approximate to the true high frequency response, measurements were performed at a temperature of -50°C and an *ac* signal frequency of 1 MHz. Under such measurement conditions, interface traps are manifest primarily as a stretch out of the depletion part of the C-V characteristic along the gate voltage axis. The temperature of -50°C and the frequency of 1 MHz were selected for practical reasons. The temperature of -50°C represents the lowest temperature available for the probe station used. Frequencies higher than 1 MHz can be affected by series resistance contributions.

Figure 3 illustrates the C-V response at -50°C and 1 MHz of *n* and *p* type Au/Ni/Al<sub>2</sub>O<sub>3</sub>(8nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors. These are the same samples for which the multiple frequency C-V results were presented in Figure 1. Based on the doping concentration (4x10<sup>17</sup>cm<sup>-3</sup>), the Al<sub>2</sub>O<sub>3</sub> thickness of 7.8 nm (from transmission electron microscopy), a dielectric constant of 8.6 for the Al<sub>2</sub>O<sub>3</sub> [43], the flat band capacitance is determined as 0.006 F/m<sup>2</sup> and the corresponding V<sub>fbn</sub> and V<sub>fbp</sub> values are shown in Figure 3. The values of  $\phi_{sn}$  and  $\phi_{sp}$  are set by the In<sub>0.53</sub>Ga<sub>0.47</sub>As electron affinity (4.9eV) and the In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentrations and are also shown in Figure 3. Using equation (1) the integrated interface state density across the In<sub>0.53</sub>Ga<sub>0.47</sub>As energy gap is  $2.7x10^{12}$  cm<sup>-2</sup>. The sign of  $(V_{fbN} - V_{fbP}) - (\phi_{sp} - \phi_{sn})$  is positive, which indicates the interface states are net donor type, in agreement with Brammertz et al. [52] and Varghese et al. [53]<sup>1</sup>. Based on an assumed value for the 5eV for the Ni work function of in the Au/Ni gate stack, the fixed oxide charge density can be determined and is ~3x10<sup>12</sup> cm<sup>-2</sup>. For the single oxide thickness value presented in Figure 3, it is not possible to determine if the fixed charge is located in a plane or distributed throughout the

<sup>&</sup>lt;sup>1</sup> It is noted that it is possible for both donor and acceptor states to exist within the energy gap at the oxide/InGaAs interface, and in this case, the technique yields the density of donors minus the density of acceptors and not the magnitude of the donor plus acceptor concentrations. That is, the method determines the net charge associated with the  $D_{it}$  in the energy gap, and not the net density.

oxide layer. In addition, it is possible that both positive and negative fixed oxide charge exist in the oxide layer. For this analysis it is necessary to examine an  $Al_2O_3$  thickness series, which is considered next.

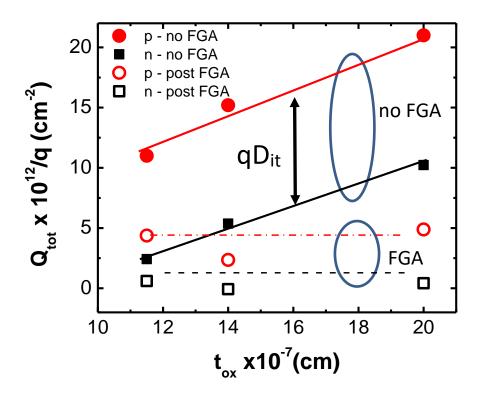

Figure 4 shows the results obtained from an Al<sub>2</sub>O<sub>3</sub> thickness series experiment. The samples are Pt gate Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors over *n* and *p* type (4x10<sup>17</sup> cm<sup>-3</sup>) In<sub>0.53</sub>Ga<sub>0.47</sub>As. The In<sub>0.53</sub>Ga<sub>0.47</sub>As surface received no surface preparation prior to the ALD alumina process. The thickness series included samples with no annealing following the oxide deposition and metal gate formation (referred to as "no FGA"), and a corresponding series with a forming gas anneal (FGA) in a 5% H<sub>2</sub>/95% N<sub>2</sub> ambient at 350°C for 30 min. From the flat band voltage determined at -50°C and 1 MHz, the total charge (Q tot) was determined based on an assumed Pt work function of 5.4eV [54]. For more details see [31]. Q<sub>tot</sub> represents the sum of the fixed oxide charge (Q<sub>fixed</sub>) and the *charged* interface state component at the flat band condition, and is the equivalent charge density (in units [cm<sup>-2</sup>]) located at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. The results are presented for Al<sub>2</sub>O<sub>3</sub> thickness values from 11nm to 20nm, for samples with and without FGA.

The Figure contains a number of significant features relating to the charge components in the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure. Firstly, the total charge Q<sub>tot</sub> at V<sub>fb</sub> for both the *n* and the *p* type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures prior to FGA is positive and increase linearly with the Al<sub>2</sub>O<sub>3</sub> thickness, indicating that the fixed oxide charge in the Al<sub>2</sub>O<sub>3</sub> is distributed uniformly throughout the oxide layer. From the slope of Q<sub>tot</sub> versus the Al<sub>2</sub>O<sub>3</sub> thickness (t<sub>ox</sub>), for either the *n* or *p* type MOS samples, the volume density of positive charge is ~ 7x10<sup>18</sup> cm<sup>-3</sup> to 1.1x10<sup>19</sup> cm<sup>-3</sup>. Secondly, the magnitude of Q<sub>tot</sub> is higher for the *p* than the *n* type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures by a constant amount. This corresponds to the value of D<sub>it</sub> integrated across the In<sub>0.53</sub>Ga<sub>0.47</sub>As energy gap and has a density of 1.1x10<sup>13</sup> cm<sup>-2</sup>. The magnitude of Q<sub>tot</sub> is higher for *p* than *n* type In<sub>0.53</sub>Ga<sub>0.47</sub>As, again indicating that the net D<sub>it</sub> across the energy gap is donor type, in agreement with the results in Figure 3 and [52, 53]. The integrated D<sub>it</sub> in Figure 4 (pre FGA) is higher than the value obtained for the samples in Figure 3 (2.7x10<sup>12</sup> cm<sup>-2</sup>). The samples in Figure 3, however, experienced an (NH<sub>4</sub>)<sub>2</sub>S surface preparation (10% in deionized H<sub>2</sub>O) for 20 min at room temperature, prior to the ALD oxide deposition, confirming the efficacy of the (NH<sub>4</sub>)<sub>2</sub>S

observation from Figure 4 relates to the total charge density extrapolated to zero Al<sub>2</sub>O<sub>3</sub> thickness for the pre-FGA samples. As discussed previously, the interface defects within the energy gap are donor type, as a consequence for an *n* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor at V<sub>fb</sub> the interface defects are occupied and neutral, and the charge at V<sub>fb</sub> is only influenced by the fixed oxide charge component. If the Al<sub>2</sub>O<sub>3</sub> layer contained only uniformly distributed positive charges, then the extrapolated Q<sub>tot</sub> for this sample should intercept the origin in Figure 4. However, extrapolation of this curve yields a value of -7.6x10<sup>12</sup> cm<sup>-2</sup>, indicating a negative fixed oxide charge component present at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. Hence, Q<sub>tot</sub> is comprised of a positive charge density on the oxide Q<sub>ox</sub> and a negative sheet charge at the interface (Q<sub>int</sub>). Finally, from Figure 4, the fixed oxide charge components (both positive and negative) in the Al<sub>2</sub>O<sub>3</sub> are both significantly reduced by the forming gas annealing process.

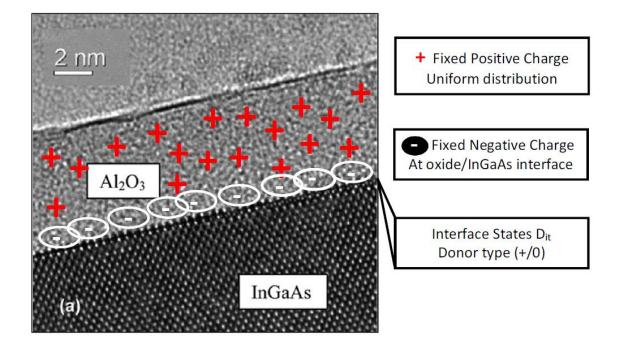

Based on the results presented in Figure 4, the picture which emerges for the charge type and distribution for the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  is illustrated in the TEM image in Figure 5. The distribution of positive charge throughout the  $Al_2O_3$  and the negative charge located close to the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface is in agreement with the analysis in [30]. The same charge distribution in the oxide was also obtained for the  $Al_2O_3/GaSb$  MOS system [55]. The density of the positive and negative charge are reduced significantly following forming gas annealing 5%  $H_2/95\%$  N<sub>2</sub> ambient at 350°C for 30 min, and the results are summarized in Table 1<sup>2</sup>.

proposed that the bulk positive fixed charge can be attributed to aluminium dangling bonds and the negative fixed charge near the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface to oxygen dangling bonds in the  $Al_2O_3$  layer [30]. The observation that the positive and negative charge densities can be significantly reduced following a FGA is consistent with this observation as atomic hydrogen resulting from the forming gas anneal process is known to passivate dangling bond centres, with

<sup>&</sup>lt;sup>2</sup> The interface state density is also reduced by the FGA. However, for the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface in the full MOSFET process, which experienced a 600°C for 15 s in a N<sub>2</sub> to activate the source and drain silicon doping implantation, the FGA has no influence on the interface state density [71]. As a consequence, the reduction in D<sub>it</sub> recorded in Table 1 is most probably a result of a structural rearrangement of the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface due to the temperature of the FGA process (350°C), which is higher than the  $Al_2O_3$  growth temperature (270°C), and not a result of hydrogen passivation of interface states.

the Pt gate electrode assisting in the dissociation of molecular hydrogen into atomic hydrogen [56].

#### 4. The D<sub>it</sub> Energy Distribution at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As Interface

The technique of charge separation at the flat band voltage, as described in section 3, provides the integrated density of the defects across the band gap and identifies if the defects are primarily donor or acceptor type. However, the technique does not contain information relating to the energy distribution of the interface defects. The energy distribution can be contained from analysis of the multi-frequency C-V or G-V responses, using the well-established high-low frequency C-V method [57], the Terman Method [58] or via conductance analysis [59].

To provide insight into the D<sub>it</sub> distribution which can yield the C-V behavior exhibited by the In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS samples in Figures 1 (a) and 1 (b) it is instructive to consider the multifrequency C-V responses reported for Si(100)/SiO<sub>2</sub> and Si(100)/SiO<sub>x</sub>/high-*k* MOS structures where a high density of silicon dangling bonds (P<sub>bo</sub> and P<sub>b1</sub>) are present at the Si(100)/SiO<sub>2</sub> interface. The silicon dangling bonds (P<sub>bo</sub> and P<sub>b1</sub>) are amphoteric defects and have specific peak energies in the silicon band gap, which are reported to be around 0.3eV and 0.85eV above  $E_V$  in silicon based on electrical [60-65] and biased electron spin resonance methods [66]. These defects are electrically active following the dissociation of hydrogen from the dangling bonds. This can be achieved by vacuum annealing (T> 700°C) [62], a rapid pull from an oxidation furnace [60] or through a process of rapid thermal annealing (RTA) in a N<sub>2</sub> ambient [63], where the cooling from the maximum RTA temperature is too rapid to allow passivation during the cooling process. Analysis of the high-*k*/Si MOS system by electron spin resonance [67, 68] and C-V analysis [69, 70] indicates that the dominant interface defects are also P<sub>b</sub> centres, as the interface region between the silicon and the high-*k* film (either intentionally or via the high-*k* growth process) is an SiO<sub>x</sub> layer.

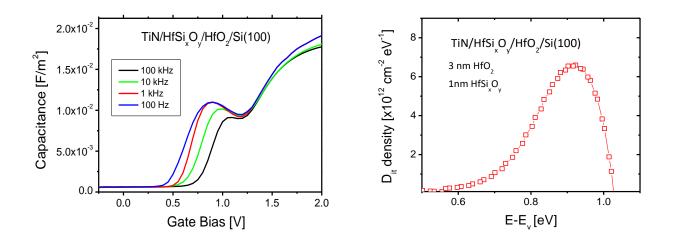

An example C-V response is shown for a TiN/HfSi<sub>x</sub>O<sub>y</sub>HfO<sub>2</sub>/SiO<sub>x</sub>/Si(100) MOS capacitor in Figure 6 (a) [69], where the sample experienced no final forming gas annealing and unpassivated  $P_b$  centres are present. The corresponding interface state profile in the upper gap region is shown in Figure 6 (b). There are clear similarities between the C-V response of  $P_b$

centres in the TiN/HfSi<sub>x</sub>O<sub>y</sub>/HfO<sub>2</sub>/SiO<sub>x</sub>/Si(100) MOS structures in Figure 6 (a), and interface defect response for the Al<sub>2</sub>O<sub>3</sub>(8nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitor in Figure 1 (b). Both indicate a frequency-dependent C-V distortion, with the capacitance moving through a peak and subsequently reducing. In addition, the peak capacitance occurs at a bias closer to the accumulation region with increasing ac signal frequency. The C-V response, in both cases, is consistent with an interface state density which has a peak density at a specific energy in the band gap. This is also supported by first principles C-V simulations by Masson et al [50]. The similarities between C-V response for the TiN/HfSi<sub>x</sub>O<sub>y</sub>/HfO<sub>2</sub>/SiO<sub>x</sub>/Si(100) and the Al<sub>2</sub>O<sub>3</sub>(8nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors, provides a platform for interpreting the typical InGaAs C-V responses, and also strong evidence that the D<sub>it</sub> at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As exhibits a peak density at a specific energy in the In<sub>0.53</sub>Ga<sub>0.47</sub>As energy gap.

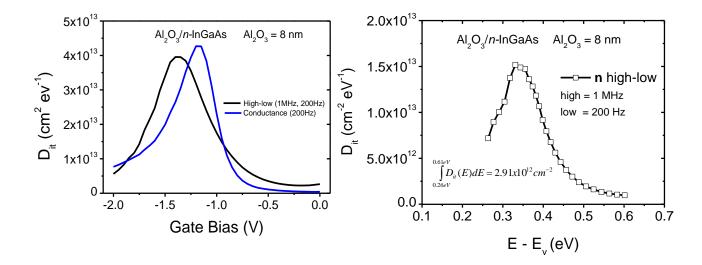

Figure 7 (a) presents the interface state density versus gate voltage obtained for the high-low C-V approach (high=1MHz and low=200Hz) and the conductance approach (200Hz) for the Al<sub>2</sub>O<sub>3</sub>(8nm)/*n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitor shown in Figure 1 (b). The equivalent parallel conductance,  $G_p$ , was converted to a peak interface state density using the assumption of zero deviation in surface potential band bending. It is observed that the conductance and the high-low approach are in reasonable agreement. For more details see [39]. Translating the gate voltage to the energy position was achieved by assuming that the 1 MHz C-V represents a true high frequency response, and the resulting D<sub>it</sub> distribution is shown in Figure 7 (b). The interface state distribution exhibits a peak density of  $1.5 \times 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> at 0.35eV above the valence band edge. The interface density in units of [cm<sup>-2</sup>] is obtained through the integral of the curve. The integrated density from 0.26eV to 0.61eV yields a value of  $2.9 \times 10^{12}$  cm<sup>-2</sup>. The approach of using V<sub>fbn</sub> and V<sub>fbp</sub>, as shown in Figure 3, on the same sample set, yielded  $2.7 \times 10^{12}$  cm<sup>-2</sup> demonstrating the consistency of the two separate approaches for the calculation of the integrated interface state density.

An alternative approach to profile the energy distribution of interface states for the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOS system based on analysis of the full gate capacitance of the surface *n*-channel  $In_{0.53}Ga_{0.47}As$  MOS transistors has recently been reported [71]. In this approach, the experimental capacitance, recorded at -50°C and 1 MHz to approximate a high frequency response, is compared to the theoretical C-V response to evaluate the interface state distribution

across the  $In_{0.53}Ga_{0.47}As$  energy gap. This approach has the advantage of profiling the interface state density distribution using a single device structure. The resulting interface state distribution is shown in Figure 8.

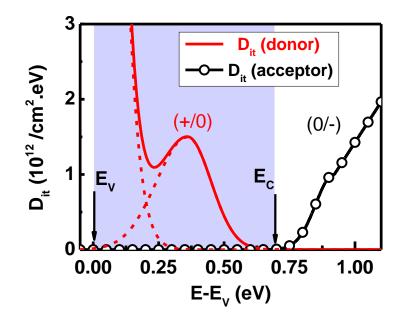

In agreement with the C-V and G-V analysis in Figure 7 (b), the analysis of the full MOSFET gate capacitance reveals a peak  $D_{it}$  density around the mid gap energy ( $E_v$ + 0.36eV). The observation of a peak density near the In<sub>0.53</sub>Ga<sub>0.47</sub>As mid-gap energy has also been reported in other works, for different high-k oxides, including: LaAlO<sub>3</sub> [72], SrTa<sub>2</sub>O<sub>6</sub> [49] and an Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bi-layer [26]. The density and energy at the peak are compared in table 2. The similarity in the energy associated with the peak  $D_{it}$  for the different high-k oxides suggest that the interfacial defects are related to the  $In_{0.53}Ga_{0.47}As$  surface and not to the oxide layer. This indicates options such as dangling bonds or dimers of As, Ga or In and anti-site defects, such as the AsGa anti-site. The energy at the peak density and charge transition type (donor) are consistent with As<sub>Ga</sub> anti-site defects based on hybrid density functional calculations of point defects in III–V compounds [73]. It is noted, however, that not all groups report a peak in the interface state density within the band gap, and a number of publications indicate a monotonic increase in the interface state density from the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band to the In<sub>0.53</sub>Ga<sub>0.47</sub>As valence band edge [52, 74, 75]. The determination of the precise energy distribution of D<sub>it</sub>, and in particular whether or not a peak density occurs within the energy gap, is an area where further research is needed in the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS field.

From Figure 8, it is also observed that the interface state density is low around the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band edge, and increases sharply into the conduction band. Including a D<sub>it</sub> component at energies > E<sub>c</sub> is required as the experimental values of capacitance exceed the predicted maximum theoretical values when the Fermi level enters the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band. The interface states aligned with the conduction band are acceptor like, and the results in Figure 8 are in agreement with other publications [74, 76]. The observation of interface states aligned with the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band is also consistent with C-V measurements on GaAs MOS and In<sub>x</sub>Ga<sub>1-x</sub>As MOS capacitors (x≤0.3). For *n*-GaAs MOS [16] and *n*-In<sub>x</sub>Ga<sub>1-x</sub>As MOS capacitors (x≤0.3) [17, 18] the C-V response is not consistent with genuine surface accumulation, and analysis indicatives a high density of acceptor like interface states in the upper region of the energy gap. The *n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS samples do exhibit genuine surface

accumulation of electrons. The energy gap reduction from GaAs to  $In_{0.53}Ga_{0.47}As$  is primarily due to a reduction in the energy of the conduction band minima (i.e., an increase in electron affinity). In this case, the interface defects which prevent surface accumulation in *n*-In<sub>x</sub>Ga<sub>1-x</sub>As MOS capacitors (x≤0.3) are located in the conduction band for In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures. Consequently, the C-V observations and analysis for *n*-In<sub>x</sub>Ga<sub>1-x</sub>As MOS capacitors (x≤0.3) are consistent with the inferred presence of interface states with energies aligned with the conduction band for the case of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures.

Finally, it is noted that there is also a sharp increase in  $D_{it}$  towards the valence band edge, which is in agreement with most publications on the interface state density in the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As system [52, 74, 75]. Based on the experimental approach used in this work, it is not possible to discriminate between the contributions of border traps or interface states for  $D_{it}$  close to the valence band or for  $D_{it}$  aligned with the conduction band.

#### 5. Reduction of D<sub>it</sub> and Surface Inversion for In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS devices

A wide range of techniques have been explored to reduce or passivate electrically active interface states at the oxide/  $In_{0.53}Ga_{0.47}As$  interface. The techniques reported have included; the deposition of Ga sub-oxides on an As de-capped  $In_{0.53}Ga_{0.47}As$  surface [77], nitridation of the  $In_{0.53}Ga_{0.47}As$  surface [46], the use of As capping layers desorbed in the ALD reactor [78], the use of undoped InP capping layers [5], and the use of thin ALD oxide interface control layers [37].

The use of inorganic sulphides has been established as an approach to improve the electronic properties of III-V surfaces, and (NH<sub>4</sub>)<sub>2</sub>S has been reported to improve surface recombination velocity for GaAs [79]. The approach has been extended to the chemical preparation of In<sub>0.53</sub>Ga<sub>0.47</sub>As surface prior to oxide deposition and studies have been performed to identify the optimum conditions for (NH<sub>4</sub>)<sub>2</sub>S surface preparation [39, 40]. Based on analysis using atomic force microscopy, x-ray photoelectron spectroscopy and C-V analysis, the optimum was found to be 10% (NH<sub>4</sub>)<sub>2</sub>S, at room temperature for 20 minutes. The exposure time between the removal from the (NH<sub>4</sub>)<sub>2</sub>S, solution and entry to the ALD system has been established to be a factor which influences the resulting D<sub>it</sub> values [24].

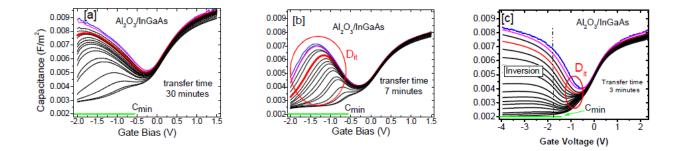

The C-V results (20 Hz to 100 kHz) shown in Figures 9 (a-c) illustrate the influence of the air exposure time between the optimum (NH<sub>4</sub>)<sub>2</sub>S surface preparation and entry of the sample into the ALD reactor for 8 nm Al<sub>2</sub>O<sub>3</sub> deposition on *n*-InGaAs surfaces. The transfer times shown are 30 minutes, 7 minutes and 3 minutes. The three multi-frequency C-V responses illustrate the progressive reduction of the interface state concentration with the reduction of the transfer time from 30 minutes to 3 minutes. In Figure 9 (a), which is typical of C-V responses for an n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure, the full interface state response is outside the gate bias window on the measurement. The capacitance corresponding to the expected theoretical minimum capacitance ( $C_{min}$ ) based on the doping concentration of  $4x10^{17}$  cm<sup>-3</sup> is also marked on the figure. The minimum experimental capacitance at 100 kHz does not reach the theoretical minimum indicating the surface is not inverted within the gate bias range examined. Figure 9 (b) is for the reduced exposure time of 7 minutes. In this case, the interface defect feature in depletion (highlighted by a red oval) is reduced in magnitude, and the experimental capacitance is closer to the theoretical minimum. Both of these observations are consistent with a reduction in the interface state concentration. Figure 9 (c), is for the case of a 3 minutes transfer time. The interface state response is significantly reduced in this case and the capacitance value at high frequency reaches the expected theoretical minimum value. While not clearly evident in the C-V response, the interface state defect response is still present in the range -0.5 to -1 V (highlighted by the red oval). The interface states in this region are still evident in the conductance response [24]. However, the interface state density concentration is clearly reduced significantly for this sample, and in the gate bias range < -2 V, the capacitance for a given *ac* signal frequency acquires an almost constant value with applied gate voltage. The constant capacitance in this region increases with decreasing frequency up to the maximum value set by the oxide capacitance. This is the characteristic *ac* response of an MOS system in inversion [80]. Detailed analysis of the capacitance and conductance of this sample with ac signal frequency and temperature confirms surface inversion for both n and p doped Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures [24]. This characteristic behaviour of surface inversion has also been reported for Al<sub>2</sub>O<sub>3</sub>/n- In<sub>0.53</sub>Ga<sub>0.47</sub>As [23] and Al<sub>2</sub>O<sub>3</sub>/p- In<sub>0.53</sub>Ga<sub>0.47</sub>As [81] MOS capacitors, and for HfO<sub>2</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As [25].

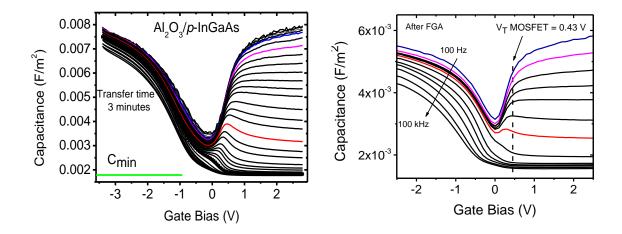

The C-V response for the corresponding Al<sub>2</sub>O<sub>3</sub>/*p*- In<sub>0.53</sub>Ga<sub>0.47</sub>As /*p*+InP MOS capacitor with the optimised (NH<sub>4</sub>)<sub>2</sub>S surface preparation and the 3 minutes transfer time is shown in Figure 10 (a). Again, the characteristic inversion behaviour is evident for  $V_g > 1$  V, and analysis of the frequency and temperature dependence in the bias region  $V_g>1$  V is consistent with surface inversion [24]. The minimum experimental capacitance at 1 MHz is in agreement with the theoretical value based on the Zn doping concentration (4x10<sup>17</sup> cm<sup>-3</sup>). Analysis of the conductance around the region of the peak interface state density response ( $V_g \sim -0.6$  V) yields a mid-gap D<sub>it</sub> in the range 6 to 9x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>. The significant reduction in the mid-gap D<sub>it</sub>, when compared to the results in Figure 7 (b) and Figure 8, allows the Fermi level to be moved through the energy gap at the Al<sub>2</sub>O<sub>3</sub>/ In<sub>0.53</sub>Ga<sub>0.47</sub>As interface within the applied bias range, resulting in the observed inversion behaviour for both the *n* and *p* type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures.

Significantly, further support that the *ac* capacitance behaviour in Figures 10 (a) ( $V_g > 1V$ ) and 9 (c) (Vg < -2 V), represent genuine surface inversion can be obtained from the Al<sub>2</sub>O<sub>3</sub>/*p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors formed in a full surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs process [42]. The availability of the full MOSFET allows an accurate determination of the threshold voltage, which can be identified on the neighbouring Al<sub>2</sub>O<sub>3</sub>/*p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor. An example is presented in Figure 10 (b) for the C-V response from 100 Hz to 100 kHz of an Al<sub>2</sub>O<sub>3</sub> (10nm)/*p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As/*p*+InP capacitor formed in a full In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET process described in section 2 of the paper. The threshold voltage (V<sub>T</sub>) of the neighbouring MOSFET was 0.43 V and is identified on the Figure (dotted line). The V<sub>T</sub> of the MOSFET relates to the condition of strong inversion at the Al<sub>2</sub>O<sub>3</sub>/*p*-In<sub>0.53</sub>Ga<sub>0.47</sub>As interface, and consequently the multi-frequency C-V behaviour for V<sub>g</sub> > 0.43 V in Figure 10 (b) corresponds to the C-V response of an inverted surface. This provides further support that the *ac* C-V response as shown in Figure 10 (a) does correspond to the condition of surface inversion.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup> It is noted that the "shoulder" in the capacitance at intermediate frequencies in the region corresponding to strong inversion (~ 0.5 V in Figure 10(a) and ~ 0.3 V in Figure 10 (b)) is not due to an interface state response. This behaviour is also evident in the simulated ideal multi-frequency C-V with no interface states, fixed charge or border traps. This is beyond the scope of this work and will be covered in a future publication.

#### 6. Conclusions

The performance, stability and long term reliability of InGaAs MOSFETs will be affected by fixed oxide charges in the gate oxide and interface defects, so it is important to characterize and understand the various charged defect components within the InGaAs MOS system, and to explore ways to intrinsically remove or passivate the defect sites. In this work we have presented an overview of capacitance-voltage and conductance-voltage based analysis of fixed oxide charges and interface states in the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor (MOS) system, where the Al<sub>2</sub>O<sub>3</sub> layer is deposited by atomic layer deposition.

Based on an analysis of the flat band voltage obtained from the high frequency (-50°C, 1 MHz) CV responses of *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures, an approach has been described to determine the density of interface states (D<sub>it</sub>) integrated across the In<sub>0.53</sub>Ga<sub>0.47</sub>As energy and the total fixed charge in the oxide. Using this technique for an Al<sub>2</sub>O<sub>3</sub> thickness series (2nm to 20nm), for samples with no initial In<sub>0.53</sub>Ga<sub>0.47</sub>As surface preparation and no forming gas annealing, the analysis indicates a fixed positive oxide charge distributed through the Al<sub>2</sub>O<sub>3</sub> layer (~8x10<sup>19</sup> cm<sup>-3</sup>) and a negative sheet charge (~ -8x10<sup>12</sup> cm<sup>-2</sup>) located near the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. This charge distribution has been obtained for different ALD systems and for Al<sub>2</sub>O<sub>3</sub>/GaSb structures by other groups, indicating the charge density and distribution is related uniquely to the Al<sub>2</sub>O<sub>3</sub> layer. The interface state density integrated across the energy gap (E<sub>v</sub>+0.04eV to Ev+ 0.67eV) for samples prior to forming gas annealing (5% H<sub>2</sub>/95% N<sub>2</sub> ambient at 350°C for 30 min) is ~ 1x10<sup>13</sup> cm<sup>-2</sup> donor type defects (+/0). Following forming gas annealing the positive and negative oxide charge density is reduced significantly, consistent with the fixed charges being related to dangling bonds type defects in the Al<sub>2</sub>O<sub>3</sub>.

The interface state distribution determined from Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures and surface channel Al<sub>2</sub>O<sub>3</sub> gate In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs, yields a peak interface state density centred at 0.36 eV above the In<sub>0.53</sub>Ga<sub>0.47</sub>As valence band edge, with a density ~  $1.5 \times 10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> for samples where the surface preparation and transfer time to the ALD system are not optimised. The interface state density increases sharply towards the valence band edge. The interface state density exhibits a minimum value near the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band edge, and then increases sharply into the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band, where the defects aligned with the conduction band are acceptor-like (0/-). Following an optimisation of the In<sub>0.53</sub>Ga<sub>0.47</sub>As

surface preparation in  $(NH_4)_2S$  and minimising the transfer time to the ALD reactor, the mid gap interface state density is reduced to around 6-9x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>, and the multi-frequency C-V and G-V responses are consistent with genuine surface inversion for both *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures.

## Acknowledgements

The authors acknowledge the financial support of science foundation Ireland through the following projects (09/IN.1/I2633, 08/US/I1546 and 07/SRC/I1172).

#### References

[1] K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi,G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, K. Zawadzki,"*Tech. Dig. - Int. Electron Devices Meet.* 247, (2007)

[2] Choong Hyun Lee, Tomonori Nishimura, Kosuke Nagashio, Koji Kita and Akira Toriumi, *IEEE Elec. Dev. Letters* 58, 1295 (2011)

[3] A. Ali, H. S. Madan, A. P. Kirk, D. A. Zhao, D. A. Mourey, M. K. Hudait, R. M. Wallace, T. N. Jackson, B. R. Bennett, J. B. Boos, and S. Datta, *Appl. Phys. Lett.*, 97, 143502 (2010)

[4] Kuniharu Takei, Morten Madsen, Hui Fang, Rehan Kapadia, Steven Chuang, Ha Sul Kim, Chin-Hung Liu, E. Plis, Junghyo Nah, Sanjay Krishna, Yu-Lun Chueh, Jing Guo, and Ali Javey, *Nano Lett.* 12, 2060–2066 (2012)

[5] M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros,

W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and Robert Chau *Tech. Dig. - Int. Electron Devices Meet.* 319, (2009)

[6] Steven J. Bentley, Martin Holland, Xu Li, Gary W. Paterson, Haiping Zhou, Olesya, Ignatova, Douglas Macintyre, Stephen Thoms, Asen Asenov, Byungha Shin, Jaesoo Ahn, Paul C. McIntyre and Iain G. Thayne, *IEEE Electron Device Letters*, 32 (4). pp. 494-496 (2011)

[7] Masafumi Yokoyama, Ryo Iida, Sanghyeon Kim, Noriyuki Taoka, Yuji Urabe, Hideki Takagi, Tetsuji Yasuda, Hisashi Yamada, Noboru Fukuhara, Masahiko Hata, Masakazu Sugiyama, Yoshiaki Nakano, Mitsuru Takenaka, and Shinichi Takagi, *IEEE Elec. Dev. Lett.*, VOL. 32, 1281 (2011)

[8] Mengwei Si, Jiangjiang J. Gu, Xinwei Wang, Jiayi Shao, Xuefei Li, Michael J. Manfra, Roy G. Gordon, and Peide D. Ye, *Appl. Phys. Lett.* 102, 093505 (2013)

[9] Anil W. Dey, Claes Thelander, Erik Lind, Kimberly A. Dick, B. Mattias Borg, Magnus Borgström, Peter Nilsson, and Lars-Erik Wernersson, *IEEE Electron Device Letters*, 33, 791 (2012)

[10] Robert Chau, Justin Brask, Suman Datta, Gilbert Dewey, Mark Doczy, Brian Doyle, Jack Kavalieros, Ben Jin, Matthew Metz, Amlan Majumdar, and Marko Radosavljevic, *Microelectronic Engineering* 80, 1-6, (2005)

[11] H. Becke, R, Hall, J. White, Solid State Electronics, 8 (10), 813 (1965)

[12] Physics and Chemistry of III-V Compound Semiconductor Interfaces, edited by C. Wilmsen, (Plenum, New York, 1985).

[13] H.H. Wieder, "Dielectric/semiconductor interfaces", *J. Vac. Sci. Technol.* B11, 1331 (1993); and references therein.

[14] W.F. Croydon, E.H.C. Parker, *Dielectric Films on Gallium Arsenide* (Gordon and Breach, Scientific Publishers: New York, 1981)

[15] Robert M. Wallace, Paul C. McIntyre, Jiyoung Kim, and Yoshio Nishi, *MRS Bulletin*, 34, 493 (2009)

[16] G. Brammertz, H. C. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns, J. Electrochem. Soc. 155, H945 (2008)

[17] É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble,

G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, *Appl. Phys. Lett.* 94, 102902 (2009)

[18] P.K. Hurley, É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K.Cherkaoui, J. MacHale, A.J. Quinn, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev,, A. M. Sonnet, R. V. Galatage, M. N. Jivani, E. M. Vogel, R. M. Wallace and M. E. Pemble, *ECS Transactions*, 25 (6) 113-127 (2009)

[19] A. Callegari, P.D. Hoh, D.A. Buchanan and D. Lacey, Appl. Phys. Lett., 54, 332 (1989)

[20] M. Passlack, M.Hong and J.P. Mannaertz, Appl. Phys. Lett., 68, 1099 (1996)

[21] C. L. Hinkle, M. Milojevic, B. Brennan, A. M. Sonnet, F. S. Aguirre-Tostado, G. J. Hughes, E. M. Vogel, and R. M. Wallace, *Appl. Phys. Lett.*, 94, 162101 (2009)

[22] M. El Kazzi, L. Czornomaz, D. J. Webb, C. Rossel, D. Caimi, H. Siegwart, J. Fompeyrine, and C. Marchiori, *Appl. Phys. Lett.*, 99, 052102 (2011)

[23] H. D. Trinh, E. Y. Chang, P. W. Wu, Y. Y. Wong, C. T. Chang, Y. F. Hsieh, C. C. Yu, H. Q. Nguyen, Y. C. Lin, K. L. Lin, and M. K. Hudait, *Appl. Phys. Lett.* 97, 042903 (2010).

[24] É. O'Connor, S. Monaghan, K. Cherkaoui, I. M. Povey, and P. K. Hurley, *Appl. Phys Lett* 99, 212901 (2011)

[25] T. D. Lin Y. H. Chang C. A. Lin, M. L. Huang, W. C. Lee J. Kwo and M. Hong, *Appl. Phys. Lett*, 100, 172110 (2012)

[26] L. K. Chu, C. Merckling, A. Alian, J. Dekoster, J. Kwo, M. Hong, M. Caymax, and M. Heyns, " *Appl. Phys. Lett.*, 99, 042908 (2011)

[27] G. Brammertz, H. C. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W. E. Wang, M. Caymax, M. Meuris, and M. Heyns, *J. Electrochem. Soc.* 155, H945 (2008)

[28] Yoontae Hwang, Roman Engel-Herbert, Nicholas G. Rudawski, and Susanne Stemmer, *Appl. Phys. Lett.* 96, 102910 (2010)

[29] Roman Engel-Herbert, Yoontae Hwang, and Susanne Stemmer, *Journal of Applied Physics*, 108, 124101 (2010)

[30] B. Shin, J.R. Weber, R.D. Long, P. K. Hurley, C.G. Van de Walle, G. Chris, P. C. McIntyre, *Appl. Phys. Lett.* 96, 152908 (2010)

[31] R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, *Journal of The Electrochemical Society*, 158 (5) G103-G107 (2011)

[32] D. M. Fleetwood, IEEE Trans. on Nuclear Science, 39, 269 (1992)

[33] Guy Brammertz, Alireza Alian, Dennis Han-Chung Lin, Marc Meuris, Matty Caymax, and W.-E. Wang, *IEEE Trans. on Elec. Dev.*, 58, 3890 (2011)

[34] Yu Yuan, Bo Yu, Jaesoo Ahn, Paul C. McIntyre, Peter M. Asbeck, Mark J. W. Rodwell, and Yuan Taur, *IEEE Trans. On Elec. Dev*, 59, 2100, (2012)

[35] J. Robertson and L. Lin Appl. Phys. Lett. 99, 222906 (2011).

[36] S. Klejna and S. D. Elliott, J. Phys. Chem. C 116, 643-654 (2012).

[37] A. O'Mahony, S. Monaghan G. Provenzano, I.M. Povey, M.G. Nolan, E. O'Connor, K. Cherkaoui,

S.B. Newcomb, F. Crupi, P. K. Hurley and M.E. Pemble, Appl. Phys. Lett. 97, 052904 (2010)

[38] R. Suzuki, N. Taoka, M. Yokoyama, S. Lee, S. H. Kim, T. Hoshii, T. Yasuda, W. Jevasuwan, T. Maeda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, *Appl. Phys. Lett.* 100, 132906 (2012)

[39] É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, *Journal of Applied Physics*, 109, 024101 (2011)

[40] B. Brennan, M. Milojevic, C. L. Hinkle, F. S. Aguirre-Tostado, G. Hughes, and R. M. Wallace Appl. Surf. Sci. 257 (9), 4082, (2011)

[41] J. J. Gu, A. T. Neal, and P. D. Ye, J. Appl. Phys., 99, 152113 (2011)

[42] V Djara, K Cherkaoui, S B Newcomb, K Thomas, E Pelucchi, D O'Connell, L Floyd, V Dimastrodonato, L O Mereni and P K Hurley, *Semicond. Sci. Technol.* 27 082001 (2012)

[43] V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. M. Povey, D. O'Connell, M. E.Pemble, and P. K. Hurley, *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 1084 - 1090, (2012).

[44] T.P. O'Regan, P.K. Hurley, B. Soree, M.V. Fischetti, Appl. Phys. Lett. 96, 213514 (2010)

[45] Eun Ji Kim, Lingquan Wang, Peter M. Asbeck, Krishna C. Saraswat, and Paul C. McIntyre, *Appl. Phys. Lett.* 96, 012906 (2010)

[46] T. Hoshii, M. Yokoyama, H. Yamada, M. Hata, T. Yasuda, M. Takenaka, and S. Takagi, *Appl. Phys. Lett.* 97, 132102 (2010)

[47] N. Goel, P. Majhi, W. Tsai, M. Warusawithana, D. G. Schlom, M. B. Santos, J. S. Harris and Y. Nishi, *Appl. Phys. Lett.* 91, 093509 (2007)

[48] Igor Krylov, Arkady Gavrilov, Dan Ritter, and Moshe Eizenberg, *Appl. Phys. Lett.* 99, 203504(2011)

[49] Zhang P.F., Nagle R.E., Deepak N., Povey I.M., Gomeniuk Y.Y., O'Connor E., Petkov N., Schmidt M., O'Regan T.P., Cherkaoui K., Pemble M.E., Hurley P.K., Whatmore R.W. *Microelectronic Engineering*, 88, 7, 1054-1057 (2011)

- [50] P. Masson, J. L. Autran, M. Houssa, X. Garros and C. Leroux, *Appl. Phys. Lett.*, 81 (18), 3392 (2002).

- [51] E. O'Connor, Djara V., Monaghan S., Hurley P.K., Cherkaoui K. *ECS Transactions*, 35, 3 415-430 (2011)

- [52] G. Brammertz, H.C. Lin, K. Martens, A. Alian, C. Merckling, J. Penaud, D. Kohen, W.-E Wang, S. Sioncke, A. Delabie, M. Meuris, M. Caymax, M. Heyns, *ECS Transactions*, 19 (5) 375-386 (2009)

[53] D. Varghese, Y. Xuan, Y. Q. Wu, T. Shen, P. D. Ye, and M. A. Alam, *Tech. Dig. - Int. Electron Devices Meet. p. 379* (2008)

- [54] Y.-C. Yeo, T.-J. King and C. Hu, J. Appl. Phys., 92, 7266 (2002).

- [55] Aneesh Nainani, Toshifumi Irisawa, Ze Yuan, Brian R. Bennett, J. Brad Boos, Yoshio Nishi, and Krishna C. Saraswat,, *IEEE Trans on Elec Dev.* 58, 3407 (2011)

- [56] Scholten, J. J. F.; Pijpers, A. P.; Hustings, A. M. L. Catal. Rev-Sci. Eng. 1985, 27, 151-206.

- [57] R. Castagne and A. Vapaille, Surface Sci., 28, 557 (1971)

- [58] E. H. Nicollian and J. R. Brews, MOS Physics and Technology, Wiley, New York, 1982, p. 325.

- [59] E. H. Nicollian and A. Goetzberger, Bell Syst. Tech. J. 46, 1055 (1967).

- [60] E. H. Poindexter, G. J. Gerardi, M. Rueckel, and P. J. Caplan, J. Appl. Phys. 56, 2844 (1984)

- [61] M. J. Uren, J. H. Stathis, and E. Cartier, J. Appl. Phys. 80, 3915 (1996)

- [62] M. J. Uren, K. M. Brunson, J. H. Stathis, and E. Cartier, Microelectron. Eng. 36, 219 (1997)

- [63] BJ O'Sullivan, PK Hurley, C Leveugle C, JH Das, Journal of Applied Physics, 89, 7, (2001), p3811.

- [64] P.K.Hurley, B.J.O'Sullivan, F.N. Cubaynes, P.A. Stolk, F.P. Widdershoven and J.H.Das, *Journal of the Electrochemical Society*, 149, pp. 194-197 (2002)

- [65] N.H. Thoan, K. Keunen, V.V. Afanas'ev and A. Stesmans, J. Appl. Phys, 109, 013710 (2011)

- [66] G. J. Gerardi, E. H. Poindexter, M. E. Rueckel, and P. J. Caplan, Appl. Phys. Lett. 49, 348 (1986).

- [67] A. Stesmans and V.V. Afanas'ev, Appl. Phys. Lett., 80, 1957 (2002).

- [68] Y.G. Fedorenko L. Truong, V.V. Afanas'ev, and A. Stesmans, *Applied Physics Letters*, 84, 4771 (2004).

- [69] P.K. Hurley, K. Cherkaoui, S. McDonnell, G. Hughes and A.W. Groenland, *Microelectronics Reliability*, 47, (2007), 1195-1201

- [70] P.K. Hurley, K. Cherkaoui, E. O'Connor, M.C. Lemme, H. D.B. Gottlob, M. Schmidt, S. Hall, Y. Lu, O. Buiu, B. Raeissi, J. Piscator, O. Engstrom and S.B. Newcomb, Journal of the Electrochemical Society, 155 (2) G13-G20 (2008)

- [71] V. Djara, T.P. O'Regan, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I.M. Povey, D. O'Connell, M.E. Pemble, P.K. Hurley, *Microelectronic Engineering* 109 182–188 (2013)

- [72] Ali, A.; Madan, H.; Koveshnikov, S.; Oktyabrsky, S.; Kambhampati, R.; Heeg, T.; Schlom, D.; Datta, S. *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 742-748, Apr. 2010.

- [73] H-P Komsa and A. Pasquarello Microelectronic Engineering 88 (2011) 1436–1439

- [74] G. Brammertz, H.C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, *Appl Phys Lett.*, 95, 202109 (2009)

- [75] Han-Ping Chen, Yu Yuan, Bo Yu, Jaesoo Ahn, Paul C. McIntyre, Peter M. Asbeck, Mark J. W. Rodwell, and Yuan Taur, *IEEE Transactions on Electron Devices*, 59, No. 9, 2383 (2012)

- [76] N. Taoka, M. Yokoyama, S.H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda,

- T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M.Takenaka and S.Takagi, *Proceedings of the IEEE International Electron Devices Meeting IEDM*, p. 610 (2011)

- [77] M. Milojevic, R. Contreras-Guerrero, E. O'Connor, B. Brennan, P. K. Hurley, J. Kim, C. L. Hinkle and R. M. Wallace, *Appl. Phys. Lett.*, 99, 042904 (2011)

- [78] E.J. Kim, E. Chagarov, J. Cagnon, Y. Yuan, A.C. Kummel, P.M. Asbeck, S. Stemmer, K.C. Saraswat, and P.C. McIntyre, *J. Appl. Phys.* 106, 124508-1-8 (2009).

- [79] E. Yablonovitch, Bhat R, Harbison JP, Logan RA. Appl. Phys. Lett., 51, 439 (1987)

- [80] E. H. Nicollian and J. R. Brews, MOS Physics and Technology, Wiley, New York, 1982, p.145.

- [81] H. C. Lin, W-E. Wang, G. Brammertz, M. Meuris, and M. Heyns, *Microelectron. Eng.* 86, 1554 (2009).

| Figure 1 (a) Room temperature multi-                                                        | Figure 1 (b) Room temperature multi-                                |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| frequency C-V (100 Hz to 100 kHz) for an                                                    | frequency C-V (100 Hz to 100 kHz) for the                           |

| Au/Ni/8nmAl <sub>2</sub> O <sub>3</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As/InP MOS | corresponding Au/Ni/8nmAl <sub>2</sub> O <sub>3</sub> /p-           |

| structure. The $In_{0.53}Ga_{0.47}As$ surface                                               | In <sub>0.53</sub> Ga <sub>0.47</sub> As/InP MOS structure. Surface |

| experienced a 10% (NH <sub>4</sub> ) <sub>2</sub> S surface                                 | preparation and transfer time as in Figure 1                        |

| preparation approach for 20 minutes and room                                                | (b). The black horizontal line represents the                       |

| temperature. The transfer time from the                                                     | theoretical maximum low frequency                                   |

| (NH <sub>4</sub> ) <sub>2</sub> S to the ALD reactor was 7 minutes.                         | capacitance calculated using a Poisson-                             |

| The black horizontal line represents the                                                    | Schrodinger C-V simulation based on the                             |

| theoretical maximum low frequency                                                           | In <sub>0.53</sub> Ga <sub>0.47</sub> As Γ Valley only.             |

| capacitance calculated using a Poisson-                                                     |                                                                     |

| Schrodinger C-V simulation based on the                                                     |                                                                     |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As $\Gamma$ Valley only.                              |                                                                     |

|                                                                                             |                                                                     |

Figure 2 (a) Schematic representation of the energy band diagram for the Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure at the flat band condition. The interface states are assumed donor type, and are predominantly unoccupied, and positively charged. The corresponding flat band voltage (V<sub>fbP</sub>) for the structure is shown below the Figure, where  $\phi_{\rm m}$ is the work function of the metal gate,  $\phi_{sp}$  is the work function of the *p*- type  $In_{0.53}Ga_{0.47}As$ , [cm<sup>-3</sup>] is the positive fixed charge Q fixed in the  $Al_2O_3$ ,  $C_{ox}$  is the oxide density capacitance per unit area [F/m<sup>2</sup>] and D<sub>it</sub> is the interface state distribution.

Figure 2 (b) Schematic representation of the energy band diagram for the Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure at the flat band condition. The interface states are assumed donor type, and are predominantly occupied, and neutral. The corresponding flat band voltage (V<sub>fbN</sub>) for the structure is shown below the Figure.  $\phi_{sn}$  is the work function of the *n*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As, and all other terms are as defined in Figure 2(a).

Figure 3. The C-V responses for the *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure recorded at 1 MHz and -50°C to approximate to a high frequency C-V response (Note: these are the same sample as in Figures 2 (a) and 2 (b)). The flat band voltages for the *n* and *p* type Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures are shown in the figure. The difference in the flat band voltages relates to the integrated D<sub>it</sub> across the In<sub>0.53</sub>Ga<sub>0.47</sub>As energy gap, as indicated in equation (1), and yields a value of  $2.7 \times 10^{12}$  cm<sup>-2</sup>.

Figure 4. The total charge density as a function of  $Al_2O_3$  thickness (11 nm to 20nm) determined for the flat band voltages of the *n* and *p* type Pt/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure recorded at 1 MHz and -50°C. The results are shown prior to the 350°C for 30 min. FGA (filled symbols) and post FGA (open symbols) for the *p*-type (red) and *n*-type (black) In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS samples. The difference between the total charge for the *p* and *n* type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS is the integrated D<sub>it</sub>, and the results indicate net donor type interface states.

Figure 5. Transmission electron micrograph image of an  $Al_2O_3/In_{0.53}Ga_{0.47}As$  structure illustrating the picture which emerges from the C-V analysis for fixed oxide charges and interface states.

| Charge<br>Component | Q <sub>ox/q</sub><br>(cm <sup>⁻³</sup> ) | Q <sub>int/q</sub><br>(cm <sup>-2</sup> ) | D <sub>it</sub><br>(cm <sup>-2</sup> ) |

|---------------------|------------------------------------------|-------------------------------------------|----------------------------------------|

| Pre FGA             | 9 x10 <sup>18</sup>                      | -8x10 <sup>12</sup>                       | 1x10 <sup>13</sup>                     |

| Post FGA            | <4x10 <sup>18</sup>                      | -7x10 <sup>11</sup>                       | 5x10 <sup>12</sup>                     |

Table 1. The values of the positive oxide charge  $(Q_{ox})$  distributed through the Al<sub>2</sub>O<sub>3</sub>, the negative fixed charge near the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface  $(Q_{int})$ , and the interface state density  $(D_{it})$  before and after the forming gas annealing process. Note: The Q<sub>fixed</sub> in Figure 2 is comprised of the two terms Q<sub>ox</sub> and Q<sub>int</sub>. The term Q<sub>tot</sub> in Figure 4 is the sum of Q<sub>fixed</sub> and qD<sub>it</sub>.

| Figure 6 (a) Example multi-frequency (100Hz                                                  | Figure 6 (b) The corresponding interface state  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------|

| to 100 KHz) C-V response obtained for a                                                      | density profile determined in the upper half of |

| (100)Si/SiO <sub>x</sub> /HfO <sub>2</sub> /HfSi <sub>x</sub> O <sub>y</sub> /TiN gate stack | the silicon energy gap. The energy (E) is with  |

| over n-type silicon. HfO <sub>2</sub> films by MOCVD.                                        | respect to the highest energy in the valence    |

| Measurements at 22°C [69]. The samples                                                       | band, E <sub>v</sub> .                          |

| experienced no final forming gas anneal, and                                                 |                                                 |

| have non-passivated silicon dangling bond                                                    |                                                 |