Administrative unit: University of Padova

Department: Department of Information Engineering (DEI)

PhD Program: Research in Science and information Technology

Batch: XXXI

### Characterization and Study of Reliability Aspects in GaN High Electron Mobility Transistors

PhD Program Coordinator: Prof. Andrea NevianiSupervisor: Ch.mo Prof. Gaudenzio MeneghessoCo-Supervisor: Ch.mo Prof. Matteo Meneghini

PhD candidate: Alaleh Tajalli

Sede Amministrativa: Università degli Studi di Padova

Dipartimento: Dipartimento di Ingegneria dell'Informazione (DEI)

CORSO DI DOTTORATO DI RICERCA: Ricerca in Scienza e Tecnologia dell'Informazione

Ciclo: XXXI

## Caratterizzazione e studio degli aspetti di affidabilità nei HEMT in GaN

Coordinatore: Prof. Andrea Neviani Supervisore: Ch.mo Prof. Gaudenzio Meneghesso Co-Supervisore: Ch.mo Prof. Matteo Meneghini

Dottoranda: Alaleh Tajalli

To my beloved mother, Maryam, and beloved father, Hossein ...

# Acknowledgements

I would like to express my gratitude to several people without whom this work would not have been accomplished. First, I would like to express my sincere graduate to my kind supervisor Prof. Gaudenzio Meneghesso, for trusting in me and giving me the opportunity to be part of microelectronic Lab. My extended thanks go to both Prof. Gaudenzio Meneghesso and Prof. Enrico Zanoni for providing me with the most favorable work conditions during my Ph.D.

Special thanks go to Prof. Matteo Meneghini for being such a supportive and motivating supervisor, for his guidance and support throughout the period of this dissertation as well as continuous review of my work. I have been extremely lucky to have such a committed co-supervisor who cared so much about me and my work.

I would also like to express my gratitude to the rest of the thesis jury committee, Dr Peter Moens and Dr Farid Medjdoub, for reviewing my thesis. Moreover, I am also thankful to Dr Peter Moens for his expert opinions and many great discussions that we had over the experimental results. My extended thanks go to Dr Farid Medjdoub for providing me with the opportunity of working under his supervision at IEMN Laboratory for a period of 5 months.

My special thanks go to Armin, Paris and Ayrin for their support and making the life in abroad easier despite being away from my home town.

Special thanks go to Isabella Rossetto and Davide Bisi for their support and help regarding any questions and problems in the measurements. I am also thankful to Alessandro Barbato for his help and for the Italian translation of the abstract of this thesis.

Moreover, I would like to thank Saeed for his kind help and support during the course of this thesis. I thank also all my former and current colleagues at microelectronic Lab, Fabiana Rampazzo, Stefano Dalcanale, Carlo De Santi, Eleonora Canato, Maria Ruzzarin, Matteo Borga, Desiree Monti, Matteo Buffolo, Nikola Renso, Marco Barbato for their friendship and for creating a very nice atmosphere and wonderful time for me during the last 3 years in Padova.

Finally, I would like to express my sincere gratitude to my parents, Maryam and Hossein to whom I own my life, my brothers Armin and Ali, my sister, Azin, and my niblings Sina, Adrina and Ayrin for their unconditional love and for supporting me throughout my life.

Padova, 20 September 2018

A. Tajalli

## Abstract

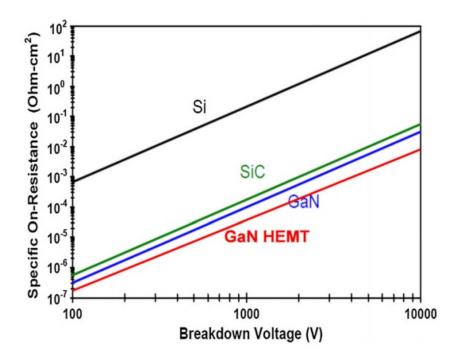

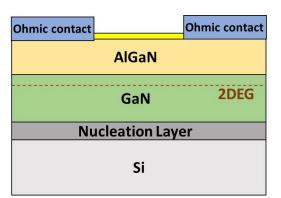

GaN-based high electron mobility transistors (HEMTs) have excellent performance for power applications. Indeed, characteristics such as the high breakdown electric filed (3.3 MV/cm), the low ON-Resistance ( $R_{ON}$ ) and the good thermal dissipation make the GaN-based diode and transistor a good potential for high frequency and power applications. The other outstanding feature of GaN-based HEMTs is the high electron mobility (> 1200 cm<sup>2</sup>/v.s) of the 2-dimensional electron gas (2DEG), formed at the interface between AlGaN and GaN, which leads to a low channel resistance and a high current density.

This thesis presents an overview of the most relevant trapping and degradation mechanisms that limit the performance and lifetime of GaN-based transistors for power electronics applications. To that end, pulsed I-V and drain current transient measurements are employed in order to investigate the trapping effects.

The degradations of AlGaN/GaN MIS-HEMTs submitted to the gate step-stress experiments are investigated in the first part of this thesis. The results, that are obtained by a combined electrical and optical characterization over the different voltages, are discussed in chapter 2 which indicate the existence of a field- and hot-electron induced phenomena as the AlGaN/GaN MIS-HEMTs degradation mechanism.

A specific discussion is devoted to investigate the proton irradiation effect on the dynamic-Ron in HEMTs and is presented in chapter 3. It is shown that the proton irradiation is an effective and controllable method to reduce the dynamic-Ron in AlGaN/GaN HEMTs. Indeed, it is shown that samples that are submitted to a proton irradiation at high fluences ( $1.5 \times 10^{14}$  cm<sup>-2</sup>, 3 MeV) exhibit a complete suppression of dynamic-Ron (complete voltage range,  $150^{\circ}$ C). This chapter further continuous to describe the voltage and temperature-dependent pulsed I-V characteristics of 650 V-rated transistors. It also points out the physical origin of dynamic R<sub>ON</sub> in these devices.

Furthermore, owing to the positive and stable threshold voltage, the low on-resistance and the high breakdown field, the p-GaN gate GaN-based transistors are commonly accepted as promising devices for application in power converters. To that end, chapter 4 deals with the mechanisms that limit the dynamic performance and the reliability of normally-off GaN-based transistors. This chapter proposed the suppression of threshold voltage instability by a suitable passivation on the p-GaN sidewall. The improved reliability of device highlights that hole trapping mostly takes place on the sidewalls.

Finally, in chapter 5, a low leakage current and a state-of-the-art vertical breakdown voltage of above 1400 V a carbon-free GaN-on-Si device are demonstrated. These characteristics are achieved thanks to a thick and excellent crystal quality of GaN buffer. Indeed, low trapping effects are observed all the way to 1200 V with a low dependency of the substrate bias on the current density. The first demonstration of trap-free at such high voltage with this material system, could paves the way for 1200 V applications with GaN-on-Si resulting in a lower Ron and thus higher efficiency as compared to SiC and Si devices.

## Abstract

I transistor ad alta mobilità in nitruro di Gallio (GaN–HEMT) hanno eccellenti proprietà per applicazioni di potenza. Infatti, caratteristiche come l'alto campo elettrico di rottura (3.3 MV/cm), la bassa resistenza di canale ( $R_{ON}$ ) e la buona dissipazione termica hanno reso i diodi e i transistor in GaN degli ottimi candidati per applicazioni ad alta frequenza e potenza. Un'altra eccezionale caratteristica dei transistor HEMT è l'alta mobilità (> 1200 cm<sup>2</sup>/v.s) del gas bidimensionale (2DEG) che viene a formarsi all'interfaccia tra l'AlGaN e il GaN, che porta ad alte densità di correnti e a basse resistenza di canale.

Questa tesi presenta un panoramica dei principali meccanismi di intrappolamento di carica e di degrado che limitano le prestazioni e l'affidabilità di dispositivi GaN HEMT per applicazioni di elettronica di potenza. Per investigare i meccanismi di intrappolamento di carica sono state usate misure di transienti di corrente e misure I-V impulsate.

Inoltre nella prima parte della tesi è stato analizzato il degrado di GaN MIS HEMT sottoposti a step-stress al gate. I risultati (discussi nel capitolo 2), ottenuti da caratterizzazioni sia ottiche sia elettriche a diverse tensioni, indicano l'esistenza di meccanismi di degrado attivati dal campo elettrico e da elettroni caldi.

Nel capitolo 3 viene presentata una discussione specifica che analizza gli effetti dell'irraggiamento con protoni sulla resistenza di canale di GaN HEMT. Viene mostrato che l'irraggiamento da protoni è un metodo efficace e controllabile per ridurre il fenomeno dell'incremento della resistenza di canale nei GaN HEMT. Infatti viene mostrato che i campioni che sono sottoposti a irraggiamento con protoni ad alta fluenza ( $1.5 \times 10^{14}$  cm<sup>-2</sup>, 3 MeV) mostrano una soppressione completa del fenomeno della resistenza dinamica (nell'intero intervallo di tensione a 150°C). Questo capitolo continua a descrivere la dipendenza delle caratteristiche impulsate di transitor in GaN a 650 V dalla tensione e dalla temperatura. Inoltre viene sottolineata l'origine fisica del fenomeno della resistenza dinamica presente sui dispositivi.

A causa della tensione di soglia positiva e stabile, della bassa resistenza di canale e dell'alto campo elettrico di rottura gli HEMT con gate in p-GaN sono dei dispositivi promettenti per applicazioni di potenza. Il capitolo 4 tratta i meccanismi che limitano le prestazioni dinamiche e l'affidabilità di transistor GaN HEMT con soglia positiva. Questo capitolo mostra come sia possibile sopprimere totalmente l'instabilità della tensione di soglia aggiungendo uno strato di passivazione sullo strato di p-GaN. Il mi-glioramento dell'affidabilità del dispositivo sottolinea come avvenga intrappolamento di lacune sullo strato di p-GaN e questo viene limitato grazie alla passivazione.

Infine nel capitolo 5 viene presentato un dispositivo verticale in GaN cresciuto su Silicio capace di sostenere 1400 V e a bassa perdita di corrente. Queste caratteristiche sono ottenute grazie alla possibilità di crescere un strato buffer in GaN molto sottile e di eccellente qualità cristallografica. Infatti sono stati osservati bassi effetti di intrappolamento di carica fino a 1200 V con una bassa dipendenza dalla polarizzazione del substrato sulla densità di corrente. La prima dimostrazione di un dispositivo cresciuto con questi materiali senza intrappolamento di carica può aprire la strada ad applicazioni a 1200 V realizzate con dispositivi in GaN sfruttando la minore resistenza di canale e quindi la miglior efficienza rispetto a dispositivi in carburo di silicio (SiC) e silicio (Si).

# Contents

| knov                          | wledge                                                                                          | ments                                                                                                                                                                                                                                                      | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract (English/Italian) vi |                                                                                                 |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| st of f                       | figures                                                                                         |                                                                                                                                                                                                                                                            | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| stof                          | tables                                                                                          |                                                                                                                                                                                                                                                            | xxii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| st of                         | publica                                                                                         | ations                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Gall                          | lium N                                                                                          | itride Material and Device Properties                                                                                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.1                           | Galliu                                                                                          | m Nitride (GaN)                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                               | 1.1.1                                                                                           | Electrical properties                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                               | 1.1.2                                                                                           | Piezoelectric properties                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2                           | GaN I                                                                                           | High Electron Mobility Transistors                                                                                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3                           | The st                                                                                          | ubstrate                                                                                                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.4                           | Metal                                                                                           | contacts                                                                                                                                                                                                                                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.5                           | Trapp                                                                                           | ing effects                                                                                                                                                                                                                                                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 1.5.1                                                                                           | Current collapse                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 1.5.2                                                                                           | Drain Current Transient Spectroscopy                                                                                                                                                                                                                       | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.6                           | GaN I                                                                                           | HEMT Reliability                                                                                                                                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fiel                          | d and H                                                                                         | Hot Electron-Induced Degradation in GaN-based power MIS-HEM                                                                                                                                                                                                | ITs 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1                           | Recen                                                                                           | it advancements in GaN technology                                                                                                                                                                                                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2                           | Exper                                                                                           | imental details                                                                                                                                                                                                                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 2.2.1                                                                                           | Electroluminescence analysis                                                                                                                                                                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 2.2.2                                                                                           | Degradation mechanism Step Stress                                                                                                                                                                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | 2.2.3                                                                                           | Field-dependent degradation of devices stressed at low $\mathrm{V}_{\mathrm{DS}}$                                                                                                                                                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | ostra<br>st of :<br>st of :<br>st of :<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>Fiel<br>2.1 | ostract (Eng<br>st of figures<br>st of tables<br>st of publica<br>Gallium Ni<br>1.1 Galliu<br>1.1 Galliu<br>1.1.1<br>1.1.2<br>1.2 GaN H<br>1.3 The su<br>1.4 Metal<br>1.5 Trapp<br>1.5.1<br>1.5.2<br>1.6 GaN H<br>2.1 Recen<br>2.2 Exper<br>2.2.1<br>2.2.2 | st of figures         st of tables         st of publications         Gallium Nitride Material and Device Properties         1.1 Gallium Nitride (GaN)         1.1.1 Electrical properties         1.1.2 Piezoelectric properties         1.1.2 Piezoelectric properties         1.2 GaN High Electron Mobility Transistors         1.3 The substrate         1.4 Metal contacts         1.5.1 Current collapse         1.5.2 Drain Current Transient Spectroscopy         1.6 GaN HEMT Reliability         Field and Hot Electron-Induced Degradation in GaN-based power MIS-HEM         2.1 Recent advancements in GaN technology         2.2 Experimental details         2.2.1 Electroluminescence analysis         2.2.2 Degradation mechanism Step Stress |

#### Contents

|   |      | 2.2.4   | Hot-electron degradation of devices stressed at high $V^{}_{\rm DS}$ $~$ | 37  |

|---|------|---------|--------------------------------------------------------------------------|-----|

|   | 2.3  | Robus   | stness analysis                                                          | 43  |

|   | 2.4  | Step S  | Stress and Recovery                                                      | 44  |

|   | 2.5  | Concl   | usions                                                                   | 46  |

| 3 | Pro  | ton-Irr | adiation Effects on AlGaN/GaN HEMTs                                      | 48  |

|   | 3.1  | Exper   | imental details                                                          | 49  |

|   | 3.2  | Exper   | imental results Proton Irradiation up to $10^{13}$ p/cm <sup>2</sup>     | 53  |

|   |      | 3.2.1   | Electrical characterization                                              | 53  |

|   |      | 3.2.2   | Optical characterization                                                 | 63  |

|   | 3.3  | Total   | Suppression of Dynamic-Ron in AlGaN/GaNHEMTs Through Pro-                |     |

|   |      | ton Ir  | radiation                                                                | 64  |

|   |      | 3.3.1   | Electrical characterization                                              | 66  |

|   |      | 3.3.2   | Substrate ramp                                                           | 70  |

|   |      | 3.3.3   | Hard switching                                                           | 78  |

|   |      | 3.3.4   | Optical characterization                                                 | 78  |

|   |      | 3.3.5   | Capacitance characterization                                             | 80  |

|   |      | 3.3.6   | On-resistance on power bars devices                                      | 81  |

|   | 3.4  | Concl   | usion                                                                    | 85  |

| 4 | Reli | ability | of Normally-Off GaN HEMTs with p-Type Gate                               | 87  |

|   | 4.1  | Origir  | n of Leakage Current of p-Gate AlGaN/GaN HEMTs                           | 90  |

|   |      | 4.1.1   | Device and stress procedure description                                  | 90  |

|   |      | 4.1.2   | Reverse and forward gate bias                                            | 92  |

|   |      | 4.1.3   | Forward gate bias                                                        | 93  |

|   | 4.2  | Impa    | ct of sidewall etching on the dynamic performance of GaN-on-Si           |     |

|   |      | E-mo    | de transistors                                                           | 96  |

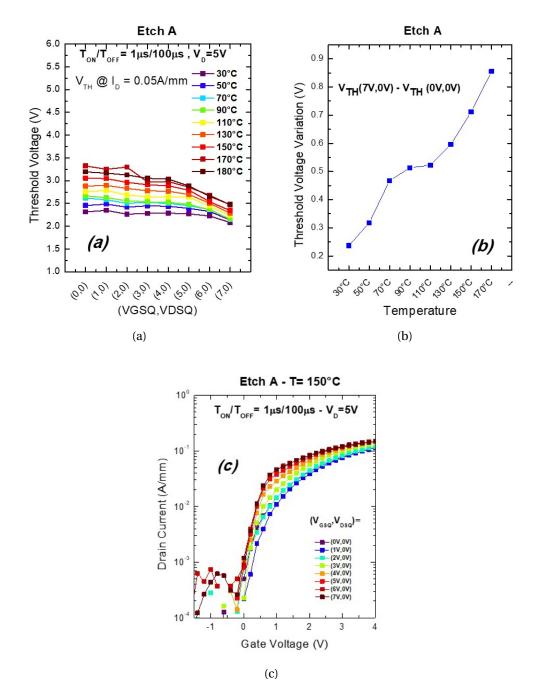

|   |      | 4.2.1   | Preliminary DC characterization                                          | 98  |

|   |      | 4.2.2   | Pulsed characterization of reference devices                             | 102 |

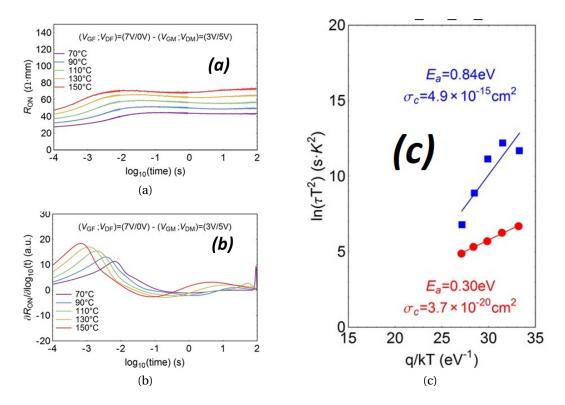

|   |      | 4.2.3   | Transient characterization of reference devices                          | 104 |

|   |      | 4.2.4   | Temperature dependent characterization of reference devices .            | 105 |

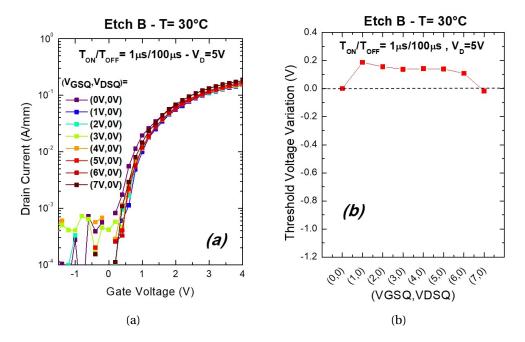

|   |      | 4.2.5   | Characterization of devices with improved p-GaN sidewall $\ . \ .$       | 105 |

|   |      | 4.2.6   | Step stress experiments                                                  | 107 |

|   | 4.3  | Concl   | usions                                                                   | 112 |

#### Contents

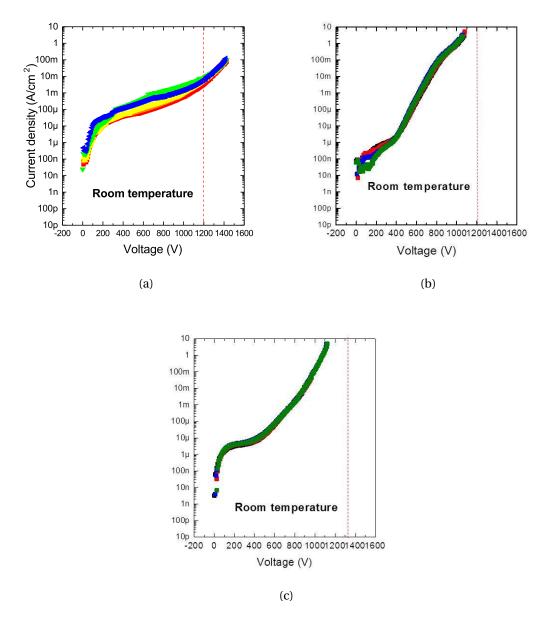

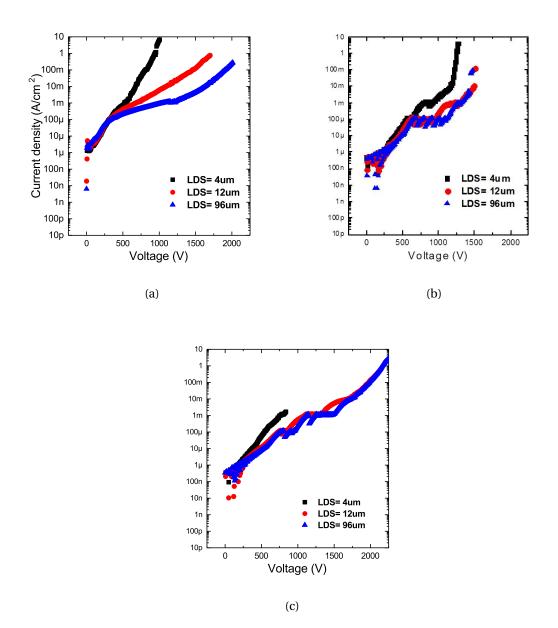

| 5  | GaN          | -on-silicon material system for 1200 V applications | 113 |  |  |

|----|--------------|-----------------------------------------------------|-----|--|--|

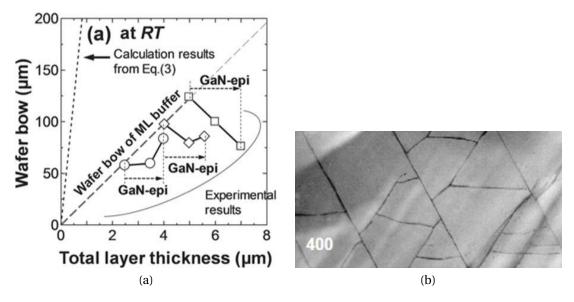

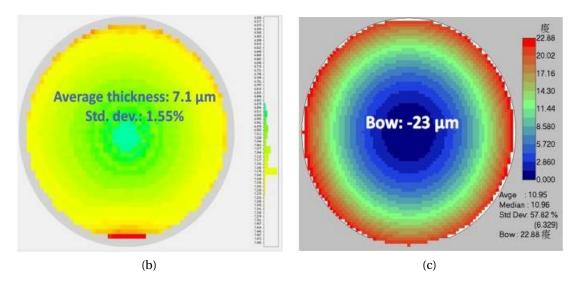

|    | 5.1          | Device structure                                    | 115 |  |  |

|    | 5.2          | DC characterization                                 | 116 |  |  |

|    | 5.3          | Vertical, Lateral breakdown                         | 117 |  |  |

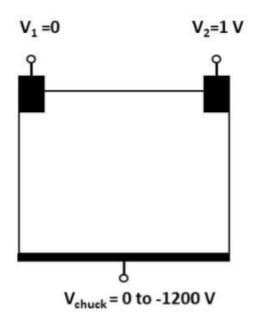

|    | 5.4          | Substrate ramp                                      | 120 |  |  |

|    | 5.5          | Conclusion                                          | 124 |  |  |

| 6  | Con          | clusions                                            | 125 |  |  |

| Bi | Bibliography |                                                     |     |  |  |

# List of Figures

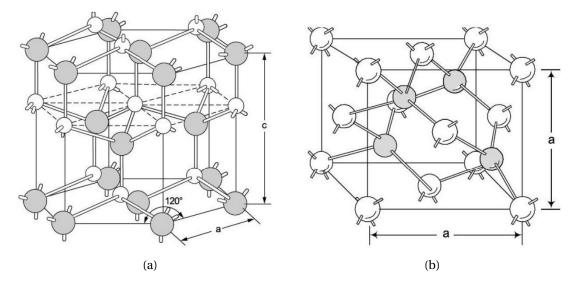

| 1.1  | (a) Visualization of wurtzite and (b) zincblende structures                      | 6  |

|------|----------------------------------------------------------------------------------|----|

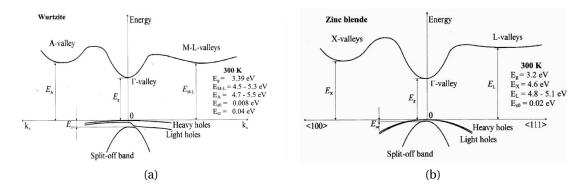

| 1.2  | Wurtzite and zincblende band diagrams in the first Brillouin zone                | 7  |

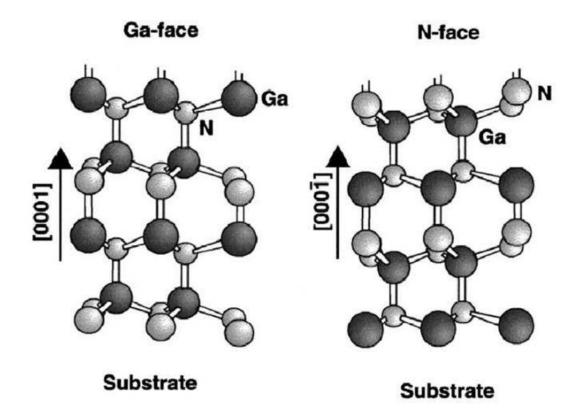

| 1.3  | Schematic drawing of the crystal structure of wurtzite Ga-face and N-            |    |

|      | face GaN layer                                                                   | 9  |

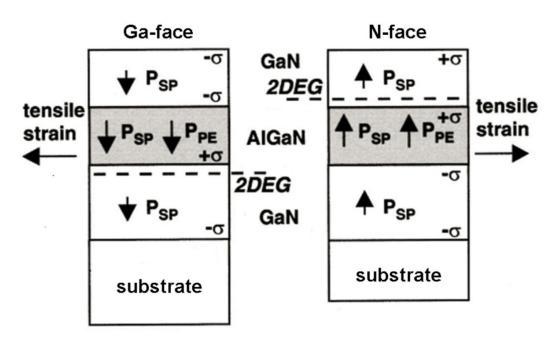

| 1.4  | Spontaneous piezoelectric polarization vectors in Ga-face and N-face             |    |

|      | topologies                                                                       | 10 |

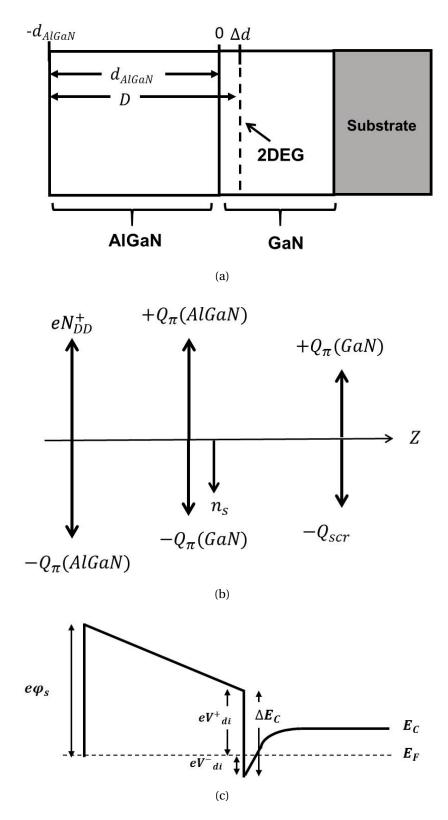

| 1.5  | (a) AlGaN/GaN heterostructure layer stack, (b) charge distribution and           |    |

|      | (c) conduction band diagram of the structure                                     | 13 |

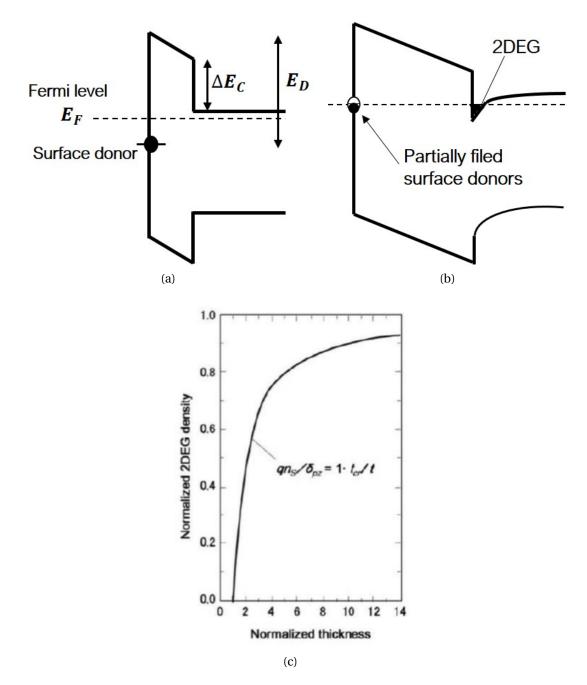

| 1.6  | Band diagram and channel charge density as a function of the AlGaN               |    |

|      | thickness                                                                        | 14 |

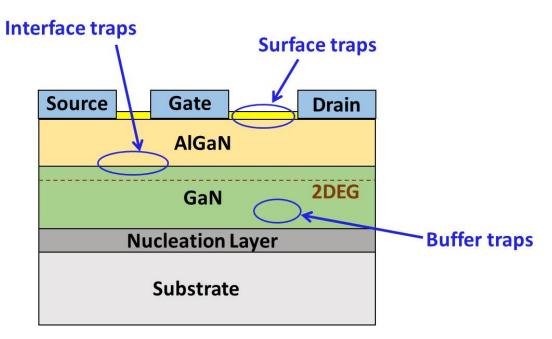

| 1.7  | Trapping-state in the AlGaN/GaN HEMT                                             | 17 |

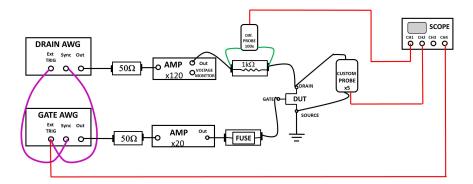

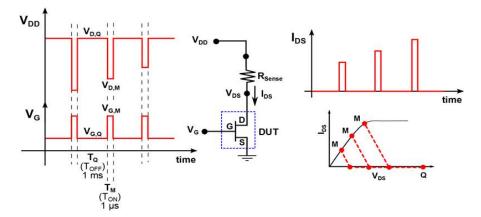

| 1.8  | Schematic of the set up for 600 V double pulse measurements                      | 18 |

| 1.9  | Double pulse measurements, gate and drain are pulsed simultaneously              |    |

|      | from quiescent bias point to a measurement bias point and drain current          |    |

|      | collapse acquired as the potential drop across resistor                          | 18 |

| 1.10 | Double pulsed a) $I_D - V_D$ b) $I_D - V_G$ on a HEMT structure at multiple off- |    |

|      | state quiescent biases, with increasing drain voltage                            | 19 |

| 1.11 | Possible trapping mechanisms and their influence on electrical parame-           |    |

|      | ters in (a) semi-ON-state and (b) OFF-state bias operating points                | 20 |

| 1.12 | Arrhenius plot with apparent activation energies (EA)                            | 21 |

| 1.13 | Drain current transients recorded after different trapping conditions.           | 22 |

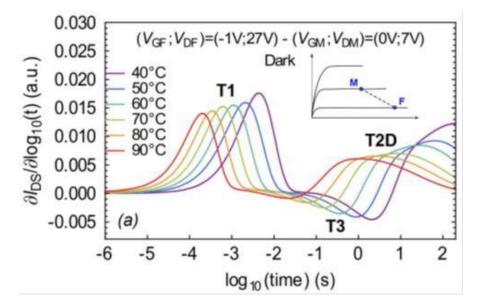

| 1.14 | Thermally activated trapping effects.                                            | 22 |

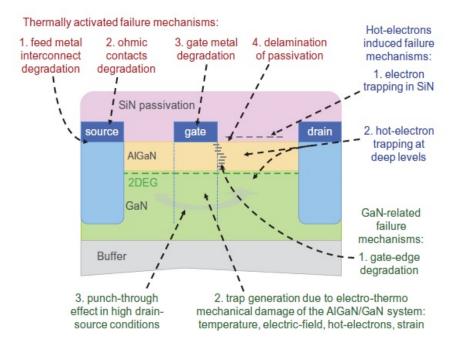

|      | Schematic figure representing the main mechanisms that can affect the            |    |

|      | reliability of GaN-based HEMTs.                                                  | 23 |

|      |                                                                                  |    |

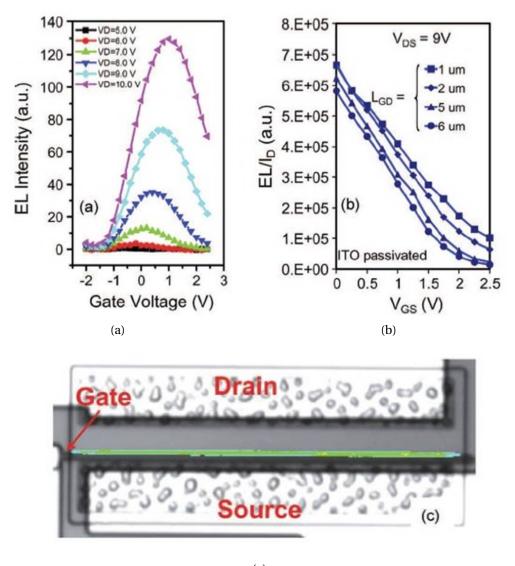

| 1.16         | 6 a) Intensity of the EL signal as a function of gate drain voltage; b) in-<br>tensity as a function of the gate voltage level for samples with different<br>gate-drain spacing; c) false colour image reporting the distribution of |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | EL along the gate.                                                                                                                                                                                                                   | 24  |

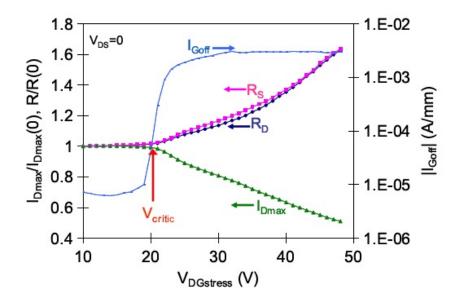

| 1.17         | <sup>7</sup> Typical results of a reverse-bias step stress. We can see the change on $I_{Dmax}$ , $R_D$ and $R_S$ , while the sudden increase of the gate leakage defines                                                            |     |

|              | the critical voltage.                                                                                                                                                                                                                | 25  |

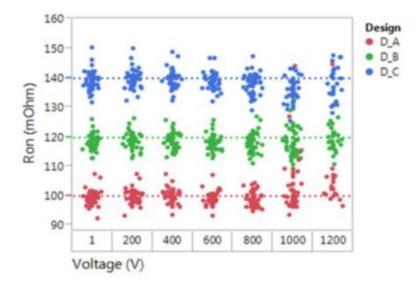

| 2.1          | Ron measured by forcing 10 A, up to 1.2 kV. Data for three different                                                                                                                                                                 | 07  |

| 0.0          | device layouts.                                                                                                                                                                                                                      | 27  |

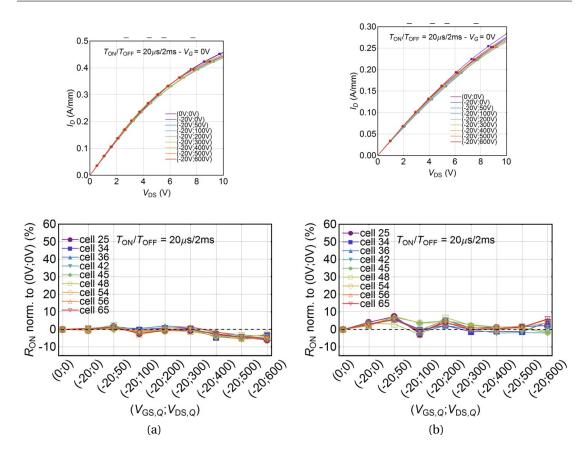

| 2.2          | Double pulsed I-V characteristics up to $V_{ds}$ =600 V. (a) room temperature,                                                                                                                                                       | 20  |

| <b>•</b> • • | (b) T=150°C. $t_{off}$ =2 ms, $t_{on}$ =20 $\mu$ s                                                                                                                                                                                   | 28  |

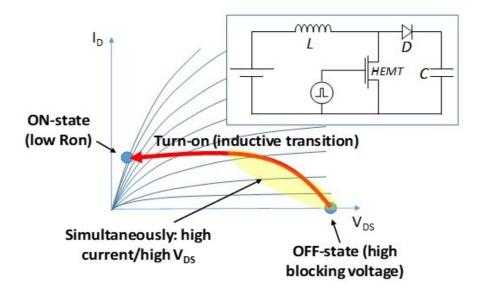

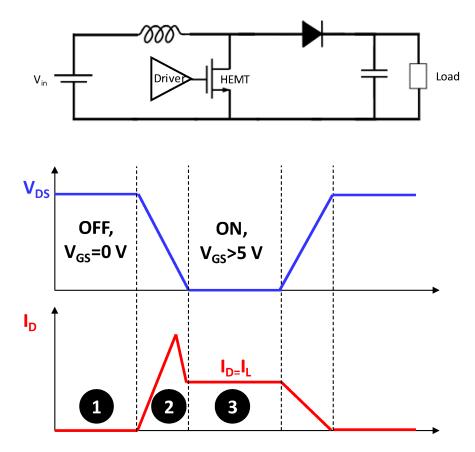

| 2.3          | Schematic representation of a hard-switching transition in a boost power                                                                                                                                                             |     |

|              | converter. During the transition, high electric field and a non-negligible                                                                                                                                                           | 20  |

| 2.4          | drain current are simultaneously present.                                                                                                                                                                                            | 29  |

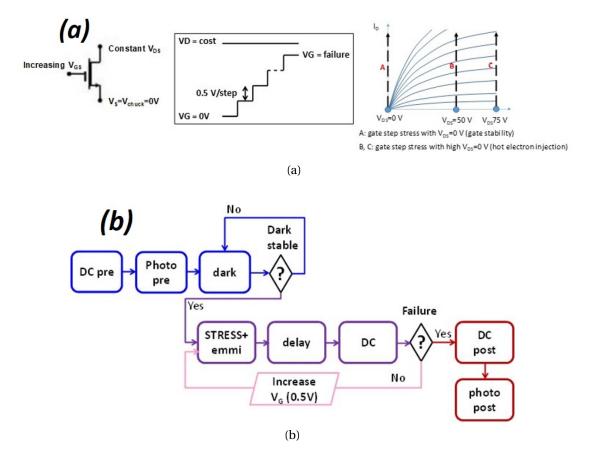

| 2.4          | a) Summary of the adopted stress conditions. A step-stress is applied to the gets $(120 \text{ s}/(-0.5 \text{ W}))$ with different drain values $(120 \text{ s}/(-0.5 \text{ W}))$                                                  |     |

|              | to the gate (120 s/step, 0.5 V/step), with different drain voltages ( $V_{DS} = 0$ V,                                                                                                                                                |     |

|              | no hot electrons, $V_{DS}$ = 50 V, 75 V, hot electron injection). The stress                                                                                                                                                         |     |

|              | conditions used within this experiment allow to explore regions of the $I_D$ -                                                                                                                                                       |     |

|              | V <sub>DS</sub> plane that are not explored by means of conventional HTRB/HTGB                                                                                                                                                       |     |

|              | stress tests, thus allowing to study the degradation processes related to                                                                                                                                                            |     |

|              | hot-electrons. b) Measurement setup (routine) of the step stress up to failure.                                                                                                                                                      | 30  |

| 25           |                                                                                                                                                                                                                                      |     |

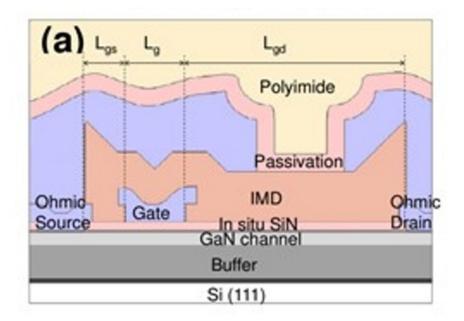

| 2.5          | GaN device structure.                                                                                                                                                                                                                | 31  |

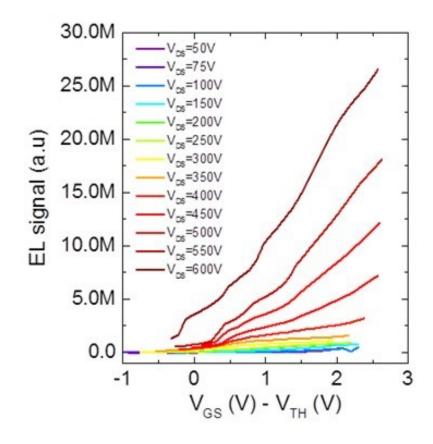

| 2.6          | EL intensity versus gate voltage curves measured at different drain volt-                                                                                                                                                            | 22  |

| 0 7          | ages on a GaN-on-Si HEMT.                                                                                                                                                                                                            | 33  |

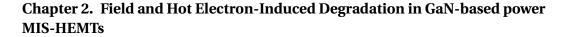

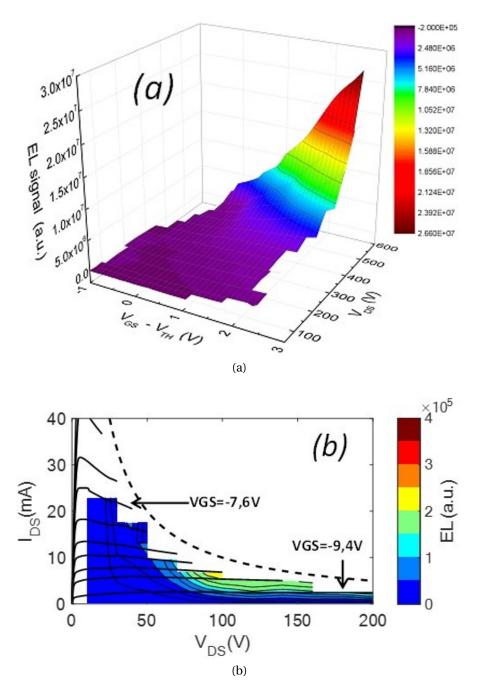

| 2.7          | a) EL intensity versus gate voltage overdrive at different drain voltage on                                                                                                                                                          |     |

|              | a GaN HEMT, (b) Correlation between the EL intensity and the output                                                                                                                                                                  | 0.4 |

|              | curve measured at corresponding bias levels.                                                                                                                                                                                         | 34  |

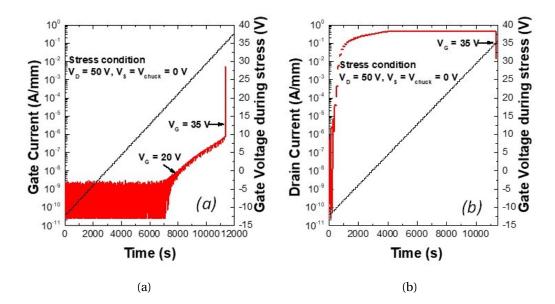

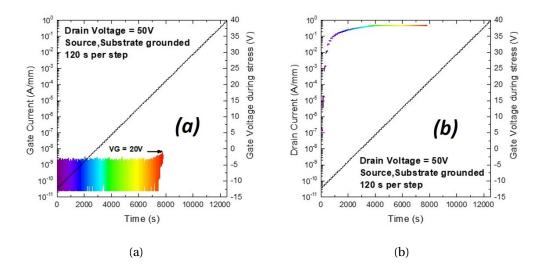

| 2.8          | (a) Gate and (b) drain current versus gate voltage during a step-stress                                                                                                                                                              | 07  |

| o -          | experiment carried out with $V_{DS}$ =50 V, increasing $V_{GS}$ .                                                                                                                                                                    | 35  |

| 2.9          | (a) Gate current versus gate voltage, the shift of the pinch-off voltage                                                                                                                                                             |     |

|              | variation. (b). Drain current versus drain voltage, reduction of the on                                                                                                                                                              |     |

|              | resistance                                                                                                                                                                                                                           | 36  |

### **List of Figures**

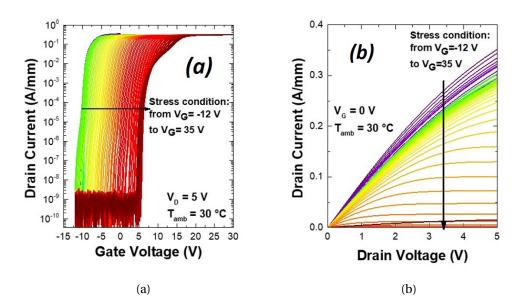

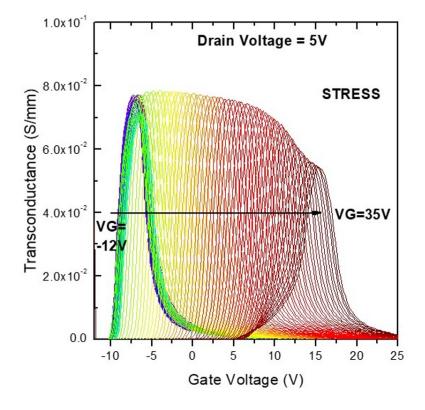

| 2.10 | Shift of the transconductance versus gate voltage after each step                               | 37 |

|------|-------------------------------------------------------------------------------------------------|----|

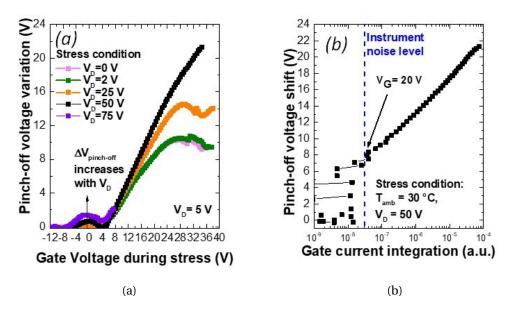

| 2.11 | (a) Pinch-off voltage variation with increasing the gate voltage. (b) de-                       |    |

|      | pendence of the pinch-off voltage shift and gate current. On the hori-                          |    |

|      | zontal axis the integral of gate current during a 2 minutes stress step is                      |    |

|      | reported                                                                                        | 38 |

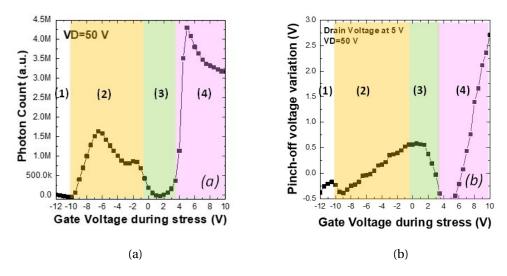

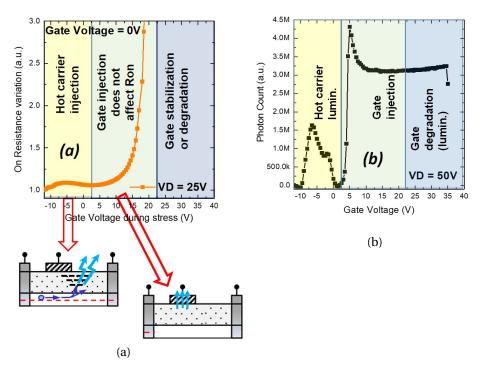

| 2.12 | (a) EL signal measured on a device submitted to step-stress with $V_{\rm DS}$ =50 V,            |    |

|      | increasing $V_{GS}$ . (b) variation of $V_{th}$ measured during the step-stress of              |    |

|      | the same device                                                                                 | 38 |

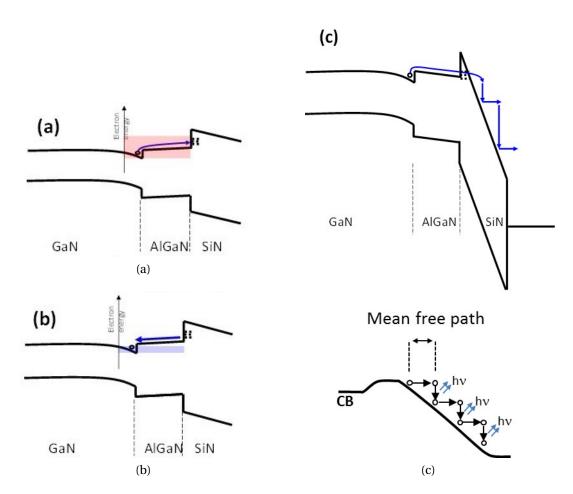

| 2.13 | Scheme of the band diagram of the device: a) injecting electrons in the                         |    |

|      | AlGaN/SiN, b) De-trapping of electrons, c) electrons are injected to the                        |    |

|      | gate insulator.                                                                                 | 40 |

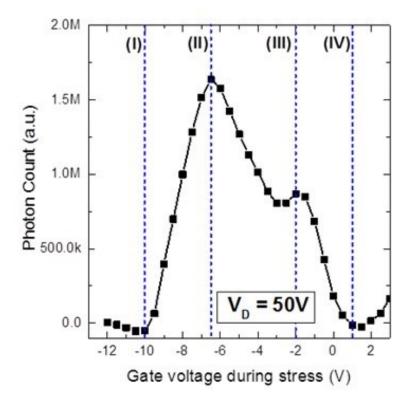

| 2.14 | Intensity of the EL signal as a function of gate voltage with V $_{\rm DS}$ =50 V. $$ .         | 41 |

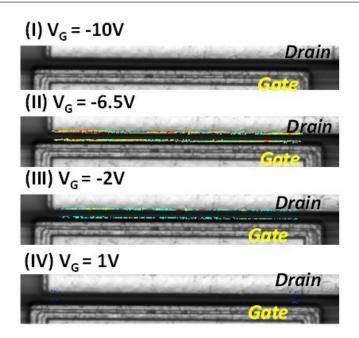

| 2.15 | False colour image reporting the distribution of EL along the gate a $\mathrm{V}_{\mathrm{DS}}$ |    |

|      | = 50 V at different $V_{GS}$ .                                                                  | 42 |

| 2.16 | Scheme of the band diagram of the device: a) injecting electrons in the                         |    |

|      | AlGaN/SiN, b) de-trapping of electrons, c) electrons are injected to the                        |    |

|      | gate insulator.                                                                                 | 42 |

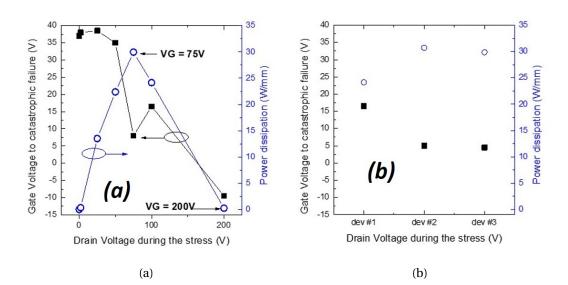

| 2.17 | a) power dissipation for one device versus drain voltage during the stress.                     |    |

|      | b) power dissipation versus different devices.                                                  | 43 |

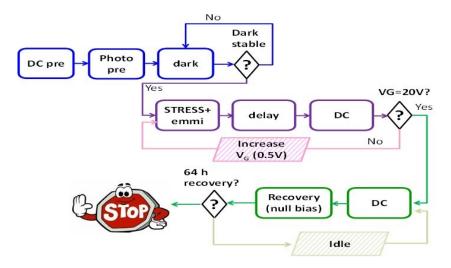

| 2.18 | Measurement setup(routine) step stress and recovery                                             | 44 |

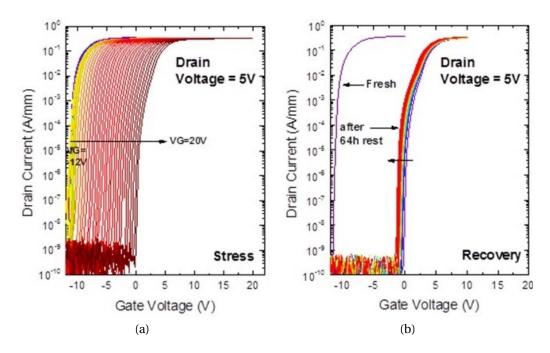

| 2.19 | (a) Gate and (b) drain current versus gate voltage during a step-stress                         |    |

|      | experiment carried out with V $_{\rm DS}$ =50 V, increasing V $_{\rm GS}$                       | 45 |

| 2.20 | a) Gate current versus gate voltage, the shift of the pinch-off voltage                         |    |

|      | variation. (b). Drain current versus drain voltage, reduction of the on                         |    |

|      | resistance.                                                                                     | 45 |

| 2.21 | a) threshold voltage variation during the step stress with increasing the                       |    |

|      | gate voltage. b) threshold voltage variation during the recovery at room                        |    |

|      | temperature and high temperature.                                                               | 46 |

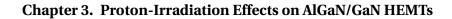

| 3.1  | (a) schematic representation of the structure of the devices under analy-                       |    |

|      | sis and of the proton implantation process used for eliminating dynamic                         |    |

|      | $R_{on}$ ; (b) The cross section of the buffer of the analysed devices                          | 50 |

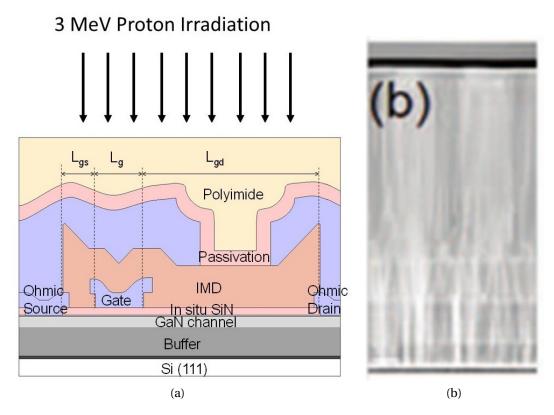

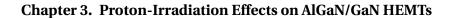

| 3.2  | a) Description of the test procedure and b) the devices used for each test.                     | 51 |

| 3.3  | Description of the test procedure and of the devices used for each test.                        | 52 |

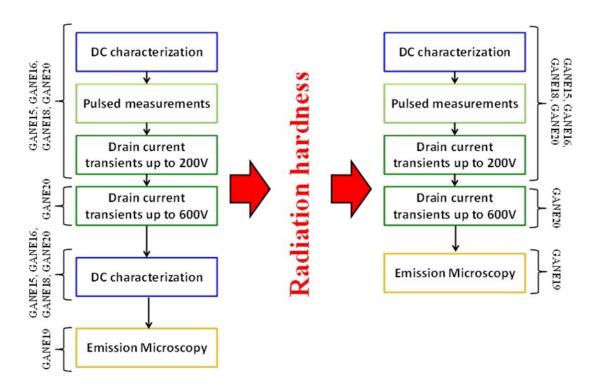

| 3.4  | DC preliminary characterization of devices before submit to proton<br>radiation tests. Monitored parameters are: (a) threshold voltage, (b)<br>drain current, (c) on resistance, (d) transconductance peak                                                                                                                                                  | 54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

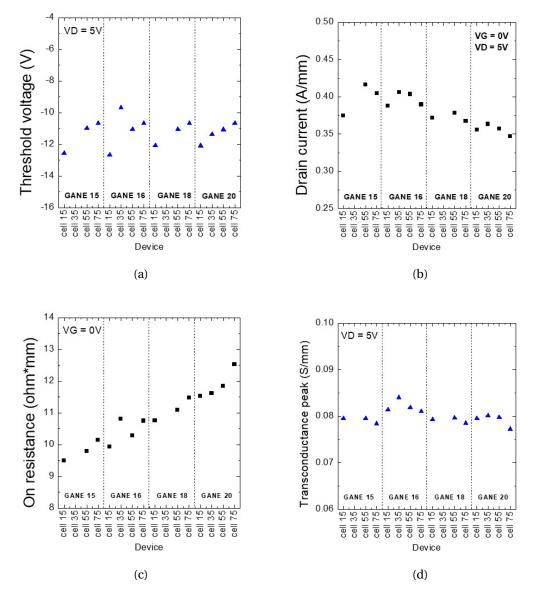

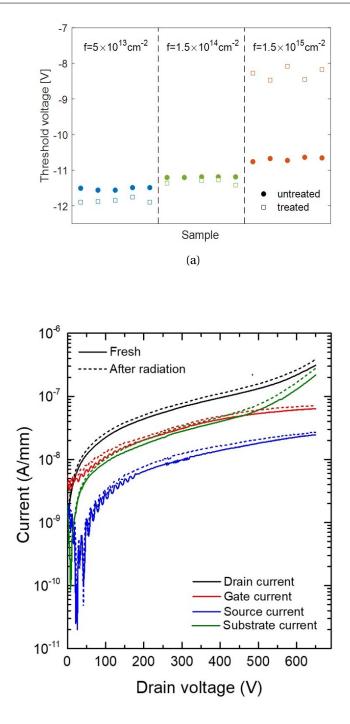

| 3.5  | (a) threshold voltage measured after radiation tests and (b) threshold voltage variation monitored in devices tested at different proton fluence.                                                                                                                                                                                                           | 55 |

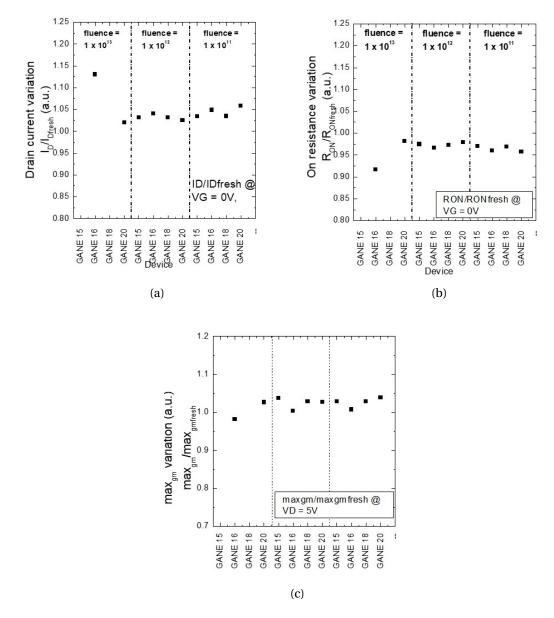

| 3.6  | Variation of the (a) drain current, (b) on resistance, (c) transconductance peak in devices tested at different proton fluences.                                                                                                                                                                                                                            | 56 |

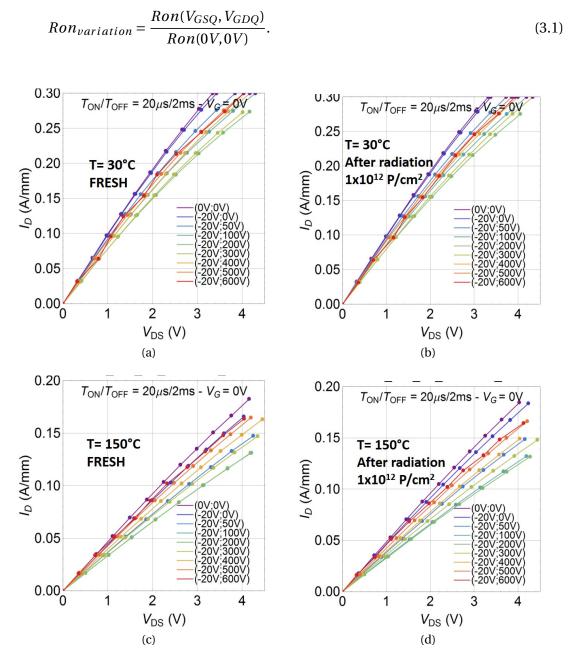

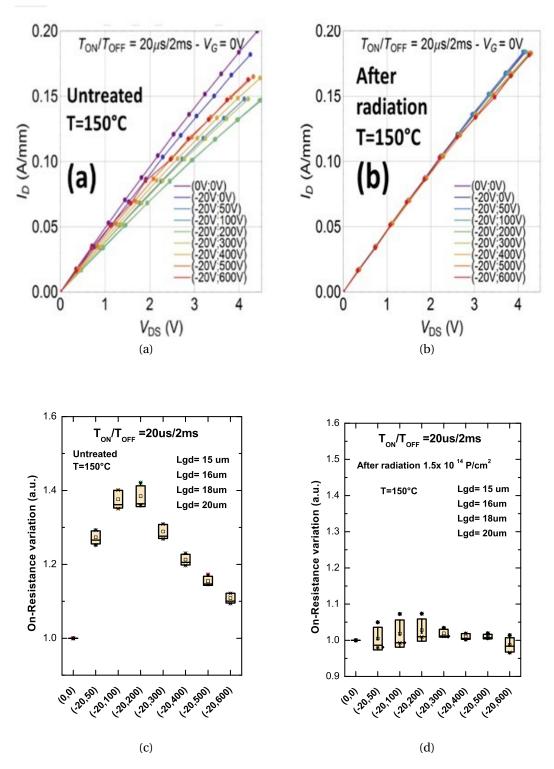

| 3.7  | Pulsed $I_D$ - $V_D$ curve measured at room temperature on representative device (a) before and (b) after radiation at $1 \times 10^{12}$ p/cm <sup>2</sup> . Analogous curves measured on the same device at Tamb = 150°C (c) before and (d) after radiation.                                                                                              | 57 |

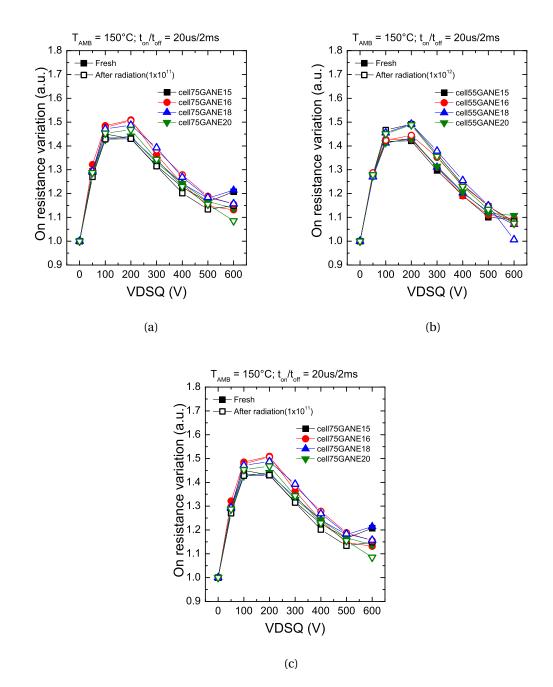

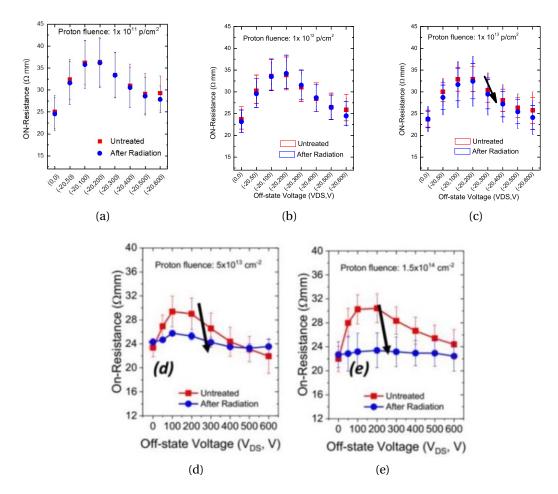

| 3.8  | Comparison of the $R_{ON}$ dynamic increase on devices before (full square)<br>and after (void square) radiationat T = 150°C. The behaviour after four<br>proton fluences (a-d) is compared                                                                                                                                                                 | 59 |

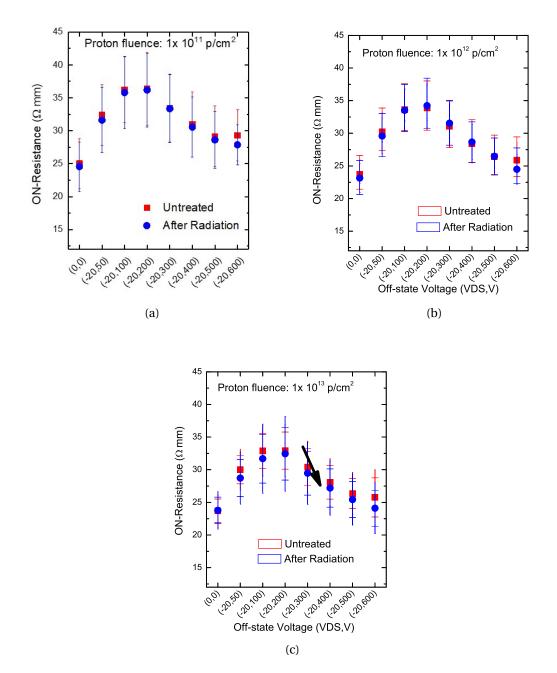

| 3.9  | Comparison of the $R_{ON}$ dynamic increase on devices before and after<br>radiationat T = 150°C. The behaviour after three proton fluences (a-d) is<br>compared with non-normalized values.                                                                                                                                                                | 60 |

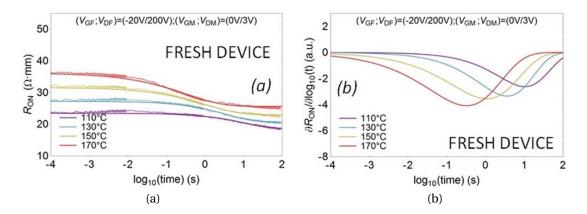

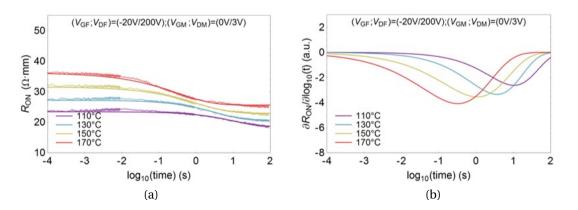

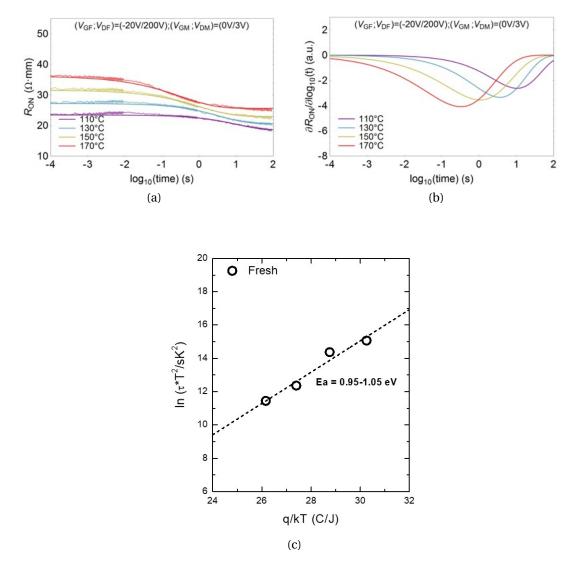

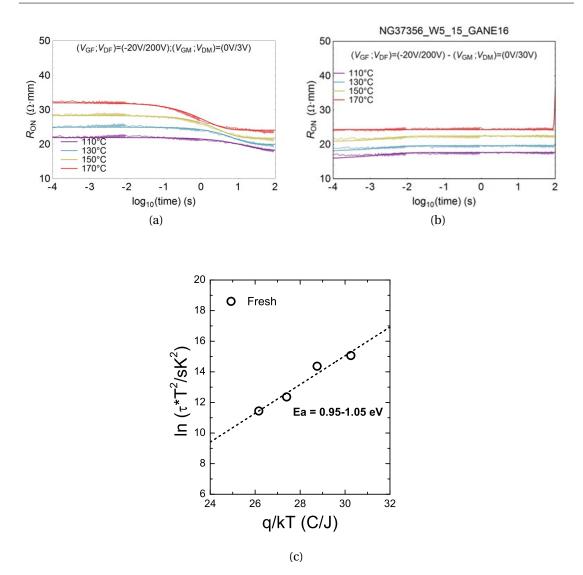

| 3.10 | Drain current transients measured on a fresh device (representative example). (a) on resistance variation; (b) trap amplitude. A filling bias of $(V_{GSQ}, V_{DSQ}) = (-20 \text{ V}, 200 \text{ V})$ is considered.                                                                                                                                       | 61 |

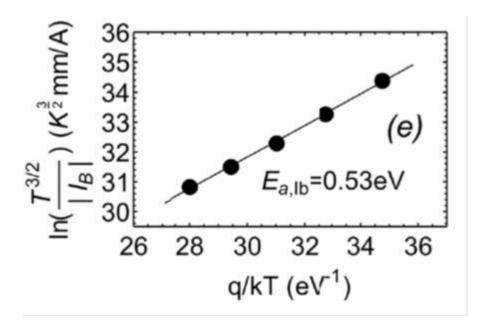

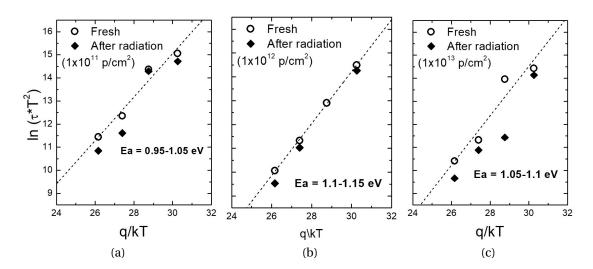

| 3.11 | Arrhenius plot calculated for a representative device (GANE 16) per cell. The impact of three different proton fluences is compared, namely $(a)1 \times 10^{12} \text{ p/cm}^2$ , $(b) 1 \times 10^{13} \text{ p/cm}^2$ and $(c) 1 \times 10^{14} \text{ p/cm}^2$ . A filling bias of $(V_{GSQ}, V_{DSQ}) = (-20 \text{ V}, 200 \text{ V})$ is considered. | 61 |

| 3.12 | Drain current transients measured on a fresh device (representative example). (a) on resistance variation; (b) trap amplitude. A filling bias of $(V_{GSQ}, V_{DSQ}) = (-20 \text{ V}, 600 \text{ V})$ is considered.                                                                                                                                       | 62 |

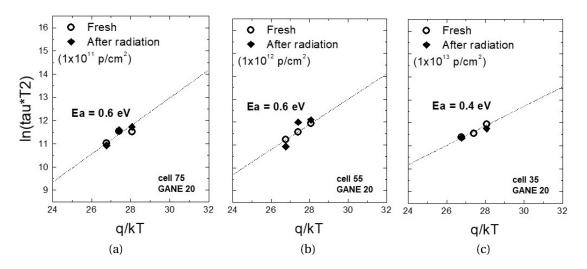

| 3.13 | Arrhenius plot calculated for a representative device (GANE 20) per cell. The impact of three different proton fluences is compared, namely $(a)1 \times 10^{11} \text{ p/cm}^2$ , (b) $1 \times 10^{12} \text{ p/cm}^2$ and (c) $1 \times 10^{13} \text{ p/cm}^2$ . A filling bias of                                                                      |    |

|      | $(V_{GSQ}, V_{DSQ}) = (-20 \text{ V}, 600 \text{ V})$ is considered.                                                                                                                                                                                                                                                                                        | 62 |

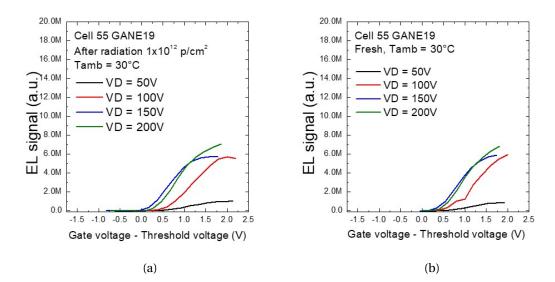

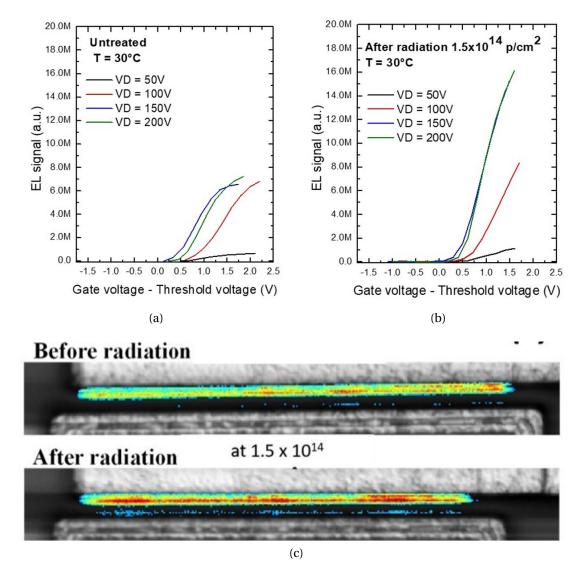

| 3.14 EL intensity versus gate voltage overdrive at different drain voltage on<br>a GaN HEMT. (a) before radiation at $V_D$ from 50 V up to 200 V (b) the<br>samples after radiation show a higher EL signal                                                                                                                                                                                                                                                                                                                                              | 63 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

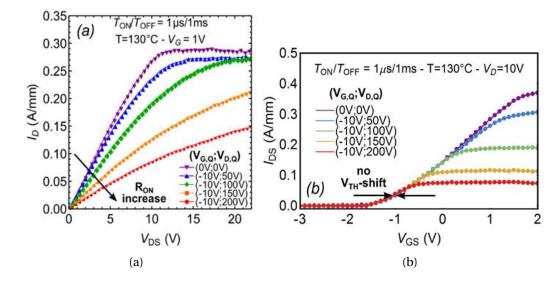

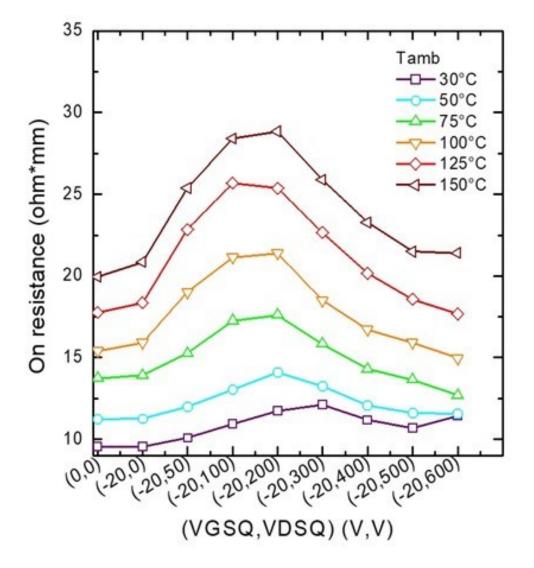

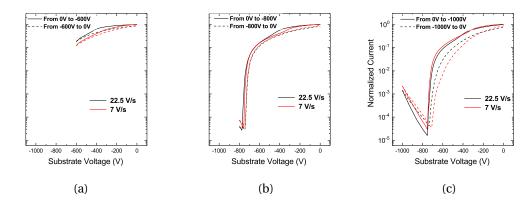

| 3.15 Non-monotonic dependence of dynamic-Ron on trapping voltage, measured at different tempratures between 30°C and 150°C. The drop for $V_{\rm DS}$ >200 V is ascribed to the build up of positive charge in the buffer.                                                                                                                                                                                                                                                                                                                               | 66 |

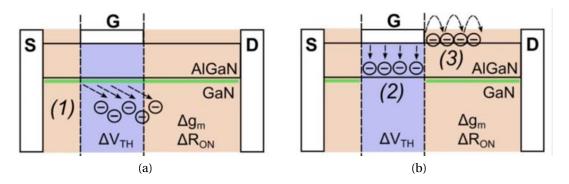

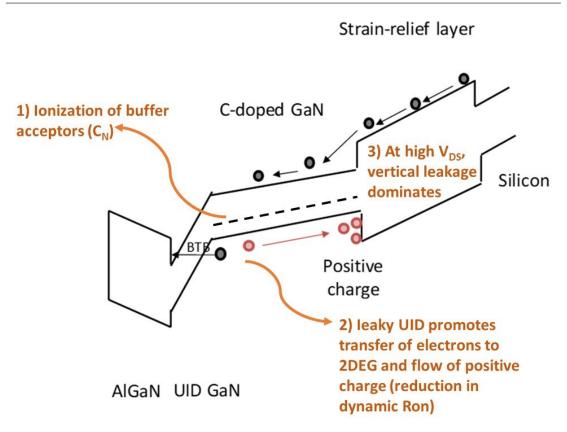

| 3.16 Schematic model explaining the non-monotonic dependence of dynamic-Ron on the trapping voltage ( $V_{DS}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67 |

| 3.17 (a) drain current transient measurements and (b) corresponding spectra measured at $V_{DS}$ = 200 V, showing the existence of a dominant buffer-related trapping process (ionization of the $C_N$ acceptors), which is responsible for high dynamic Ron. (c) Arrhenius plot of the defect responsible for peak dynamic Ron, with activation energy around 0.95 eV.                                                                                                                                                                                  | 68 |

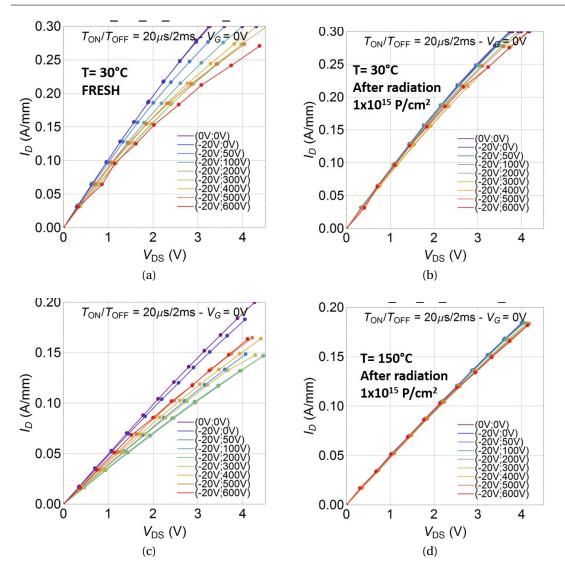

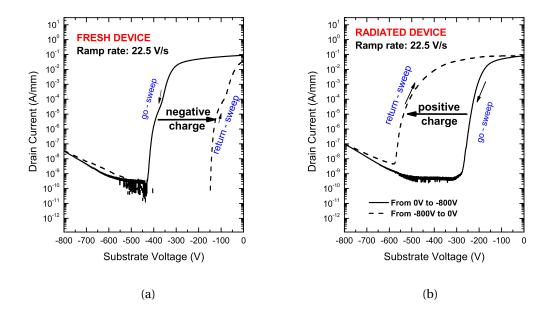

| 3.18 a) Threshold voltage measured before and after the irradiation test at the highest fluences b) leakage current components measured in the off-state ( $V_{GS}$ = -20 V) before and after radiation                                                                                                                                                                                                                                                                                                                                                  | 69 |

| 3.19 Pulsed $I_D$ - $V_D$ curve measured at room temperature on representative<br>device (a) before and (b) after radiation at $1.5 \times 10^{15}$ p/cm <sup>2</sup> . Analogous<br>curves measured on the same device at Tamb = 150°C (c) before and (d)<br>after radiation.                                                                                                                                                                                                                                                                           | 71 |

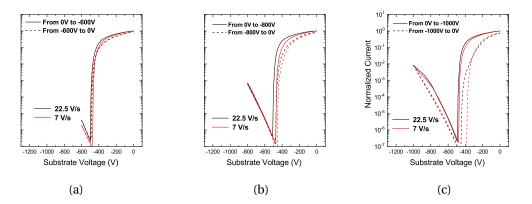

| 3.20 (a) current collapse before radiation at 150°C; (b) current collapse after radiation at 150°C. Variation of dynamic Ron, with the quiescent bias up to 600 V for different $L_{GD}$ . (c) untreated devices, (d) after radiation at T= 150°C.                                                                                                                                                                                                                                                                                                       | 73 |

| 3.21 dynamic-Ron measurement as a function of the trapping bias on un-<br>treated samples and after radiation at different fluences. (a) Fluence =<br>$10^{11}$ cm <sup>-2</sup> ; (b) Fluence = $10^{12}$ cm <sup>-2</sup> (c) Fluence = $10^{13}$ cm <sup>-2</sup> (d) Fluence<br>= $5 \times 10^{13}$ cm <sup>-2</sup> (e) Fluence = $1.5 \times 10^{14}$ cm <sup>-2</sup> ; All measurements were<br>carried out at 150°C. As can be noticed, proton implantation at the high-<br>est fluence induces a complete suppression of dynamic-Ron, even at |    |

| 600 V/150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74 |

| 3.22 Drain current transient measurement before and after radiation at $V_{DS}$<br>= 200 V.(b) no detectable trap level states shows after irradiation. (c | c)        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Arrhenius plot of the defect responsible for peak dynamic Ron, with activation energy around 1.05 eV.                                                      |           |

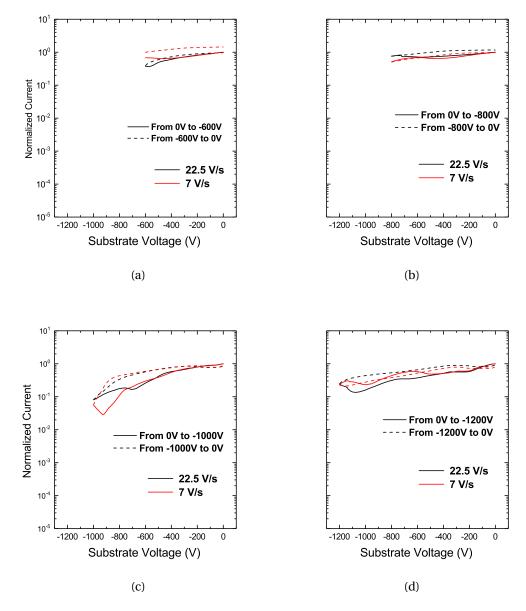

| 3.23 Substrate ramp caried out a) on an untreated sample and b) after proto                                                                                | n         |

| irradiation at the highest fluence. Before irradiation, a negative substrat                                                                                | e         |

| sweep induced a rightwards shift of the curve, indicating a significan                                                                                     | ıt        |

| trapping of negative charge (from the ionization of the buffer acceptors                                                                                   | ).        |

| b) after radiation, a negative substrate sweep induced a leftwards shi                                                                                     | ft        |

| of the curve, due to the increase in positive charge. Such positive charg                                                                                  | e         |

| originates from the increase in the leakage of the uid-GaN channel lay                                                                                     | ver. 76   |

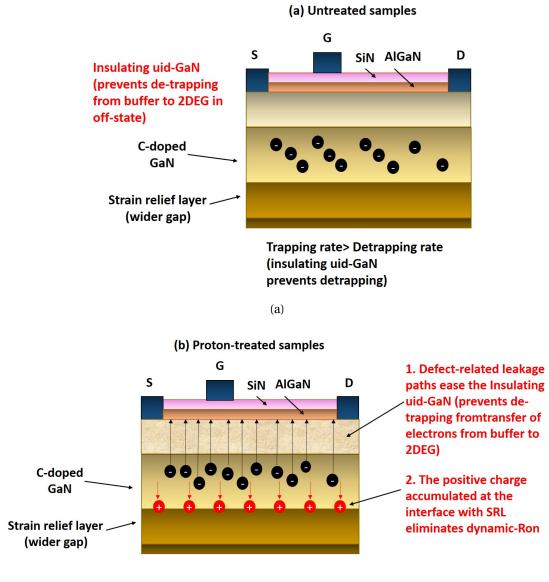

| 3.24 Schematic representation of the process responsible for reduced dynam                                                                                 | ic-       |

| Ron after proton irradiation. Before irradiation, the uid-GaN is insula                                                                                    | t-        |

| ing, and prevents the transfer of electrons from the buffer to the 2DE                                                                                     | Ĵ         |

| when the device is in the off-state. After radiation, the increased leal                                                                                   | <b>C-</b> |

| age through the uid-GaN leads to an increase in the de-trapping rat                                                                                        | e.        |

| Positive charge is also accumulated at the interface between c-GaN and                                                                                     | d         |

| SRL                                                                                                                                                        | . 77      |

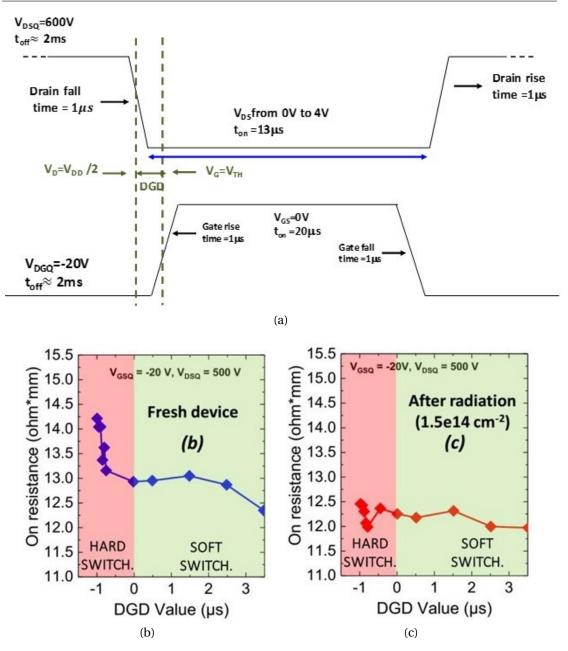

| 3.25 Schematic represe of the waveform timing used to test the hard switch                                                                                 | 1-        |

| ing behaviour of the devices b)and c) dynamic Ron induced by so                                                                                            | ft        |

| switching (drain-gate-delay, DGD> 0 s) and hard switching (DGD< $0$ s                                                                                      | 3)        |

| on b) an untreated sample and c) a sample submitted to the highest ra                                                                                      | 1-        |

| diation fluence. After radiation, the device dose not show any significan                                                                                  | ıt        |

| increase in dynamic-Ron in hard switching, contrary to the untreate                                                                                        | d         |

| sample                                                                                                                                                     | . 79      |

| 3.26 EL intensity versus gate voltage overdrive at different drain voltage of                                                                              | n         |

| a GaN HEMT. (a) before radiation at VD from 50 V up to 200 V (b) th                                                                                        | e         |

| samples after radiation show a higher EL signal. (c ) false color EL map                                                                                   | S         |

| showing the distribution of the EL signal before and after radiation. a                                                                                    | n         |

| acquisition time of 25 s and an EM gain of 200                                                                                                             | . 80      |

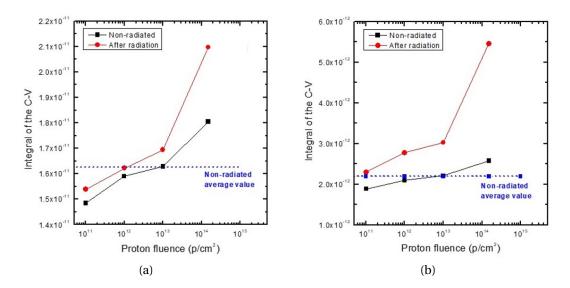

| 3.27 Integral of the C-V curve (a) 2-terminal (b) 3-terminal, demonstrate                                                                                  | S         |

| that although with different intensity, consistent results are observed in                                                                                 | n         |

| the 2-terminal and 3-terminal analysis                                                                                                                     | . 81      |

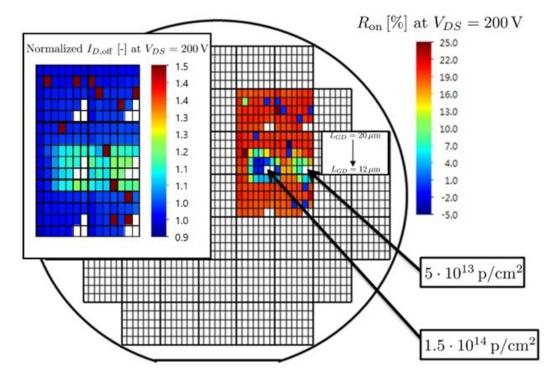

| 3.28 | Wafer map of the on-resistance variation at $V_{DS} = 200 \text{ V}$ and $T = 150^{\circ}\text{C}$ |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | on large power transistors (W=140 mm). Inset: source leakage at $\mathrm{V}_\mathrm{DS}$           |    |

|      | = 200 V normalized with respect to the median of all devices with the                              |    |

|      | same L <sub>GD</sub>                                                                               | 82 |

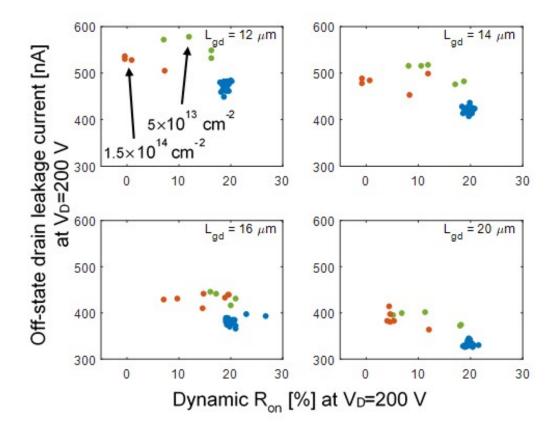

| 3.29 | Off-state drain leakage at $V_{DS}$ = 200 V and T = 150°C on large power                           |    |

|      | transistors (W=140 mm). Blue dots represent large transistors out of the                           |    |

|      | vicinity of any impact zone, while red and green dots represent those in                           |    |

|      | the direct vicinity of the impact zone with proton fluence of $5 \times 10^{13}$ P/cm <sup>2</sup> |    |

|      | and $1.5 \times 10^{14} \text{ p/cm}^2$ , respectively                                             | 84 |

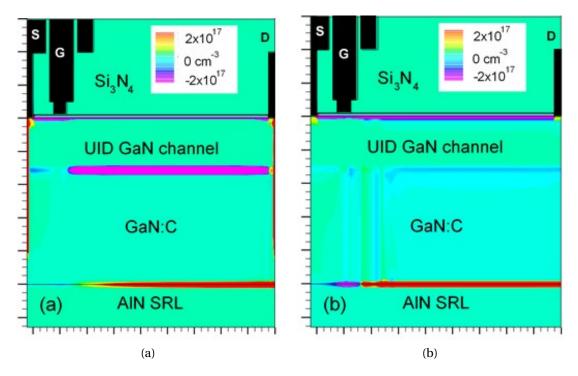

| 3.30 | TCAD simulated cross-section depicting the total charge density distri-                            |    |

|      | bution                                                                                             | 85 |

| 4 1  | Schematic representation of a baset never converter and of the quitch                              |    |

| 4.1  | Schematic representation of a boost power converter and of the switch-                             | 00 |

|      | ing transitions during operation.                                                                  | 88 |

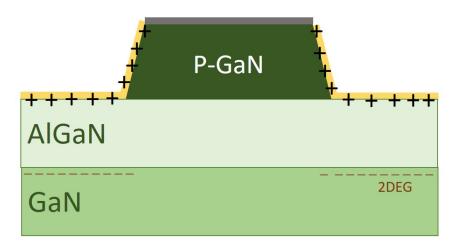

| 4.2  | Schematic representation of the p-GaN gate in AlGaN/GaN HEMT                                       | 91 |

| 4.3  | Gate current versus voltage on different processes for single finger tran-                         |    |

|      | sistors normalized by gate width at T=30, 90, 150 °C in blue, green and                            |    |

|      | red, respectively. Measured at $V_{DS}=0$ V.                                                       | 92 |

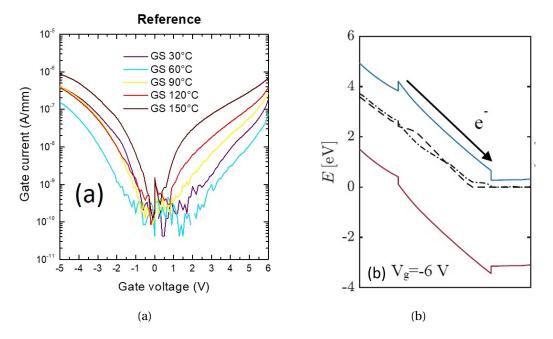

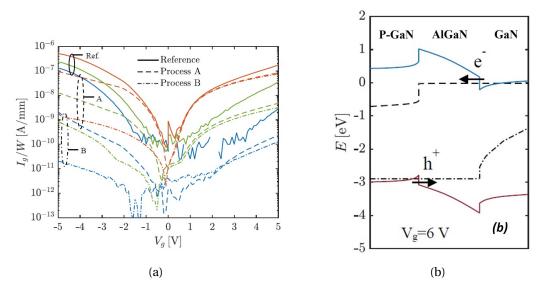

| 4.4  | (a) Gate current versus voltage on different processes normalized by gate                          |    |

|      | width at T=30, 90, 150 °C in blue, green and red, respectively. Measured                           |    |

|      | at $V_{DS}$ =0 V. (b) Energy band diagram of the p-GaN/AlGaN/GaN gate                              |    |

|      | stack at $V_G$ =-6 V: cross-section taken at the gate foot where the electric                      |    |

|      | field in the barrier is maximal. The direction of the electron conduction                          |    |

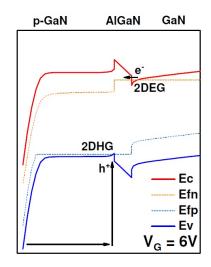

|      | through Poole-Frenkel emission is indicated.                                                       | 93 |

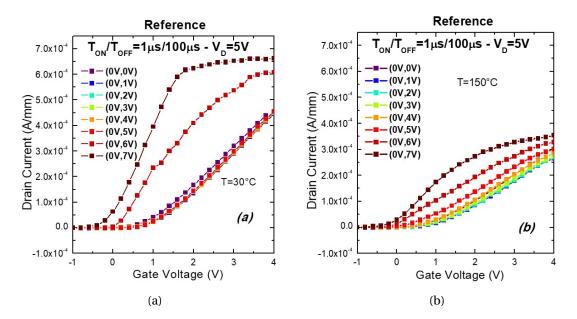

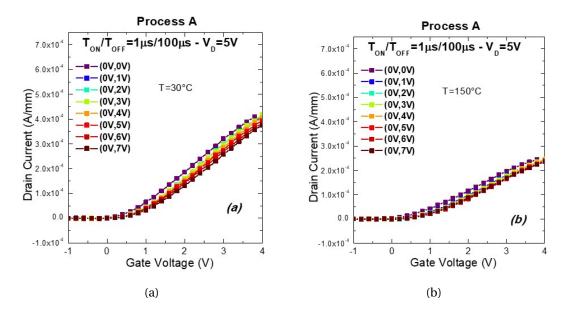

| 4.5  | Drain current versus gate voltage after different forward gate voltage                             |    |

|      | stress on the reference process (a) at room temperature and (b) at high                            |    |

|      | temperature                                                                                        | 94 |

| 4.6  | Drain current versus gate voltage after different forward gate voltage                             |    |

|      | stress on the process A (a) at room temperature and (b) at high tempera-                           |    |

|      | ture                                                                                               | 95 |

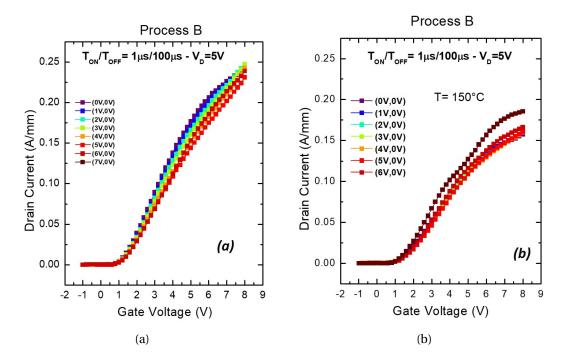

| 4.7  | Drain current versus gate voltage after different forward gate voltage                             |    |

|      | stress on the process B (a) at room temperature and (b) at high tempera-                           |    |

|      | ture                                                                                               | 95 |

|      |                                                                                                    |    |

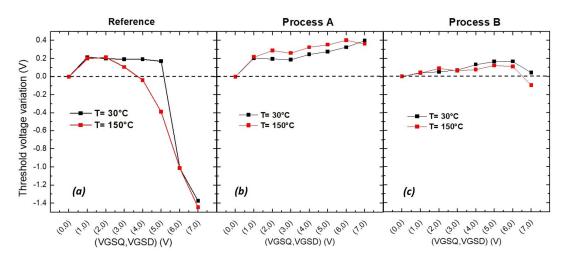

| 4.8  | Pinch-off voltage variation versus forward gate voltage stress for the (a) reference, (b) process A and (c) process B at room temperature (black) |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | and high temperature (red)                                                                                                                        | 96  |

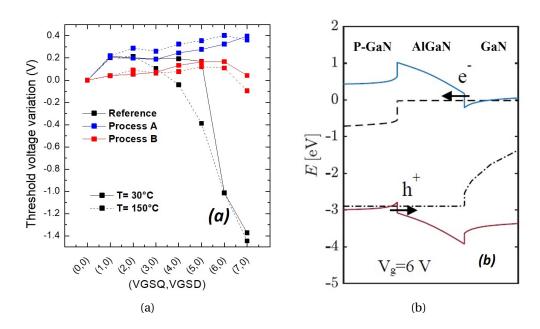

| 4.9  | (a) Pinch-off voltage variation versus forward gate voltage stress for                                                                            |     |

|      | the reference, process A and B (b) Energy band diagram of the p-GaN/                                                                              |     |

|      | AlGaN/ GaN gate stack at (b) $V_G = 6$ V: cross-section taken at the gate foot                                                                    |     |

|      | where the electric field in the barrier is maximal: the arrows depict the                                                                         |     |

|      | trapping of electrons and holes in the barrier. Electron trapping occurs                                                                          |     |

|      | throughout the whole barrier under the gate, while the hole trapping                                                                              |     |

|      | occurs predominantly near the gate foot. Simulated with a high density                                                                            |     |

|      | of Mg in the p-GaN, such that the depletion region does not reach the                                                                             |     |

|      | p-GaN/AlGaN interface.                                                                                                                            | 97  |

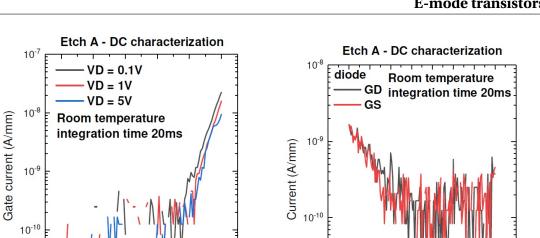

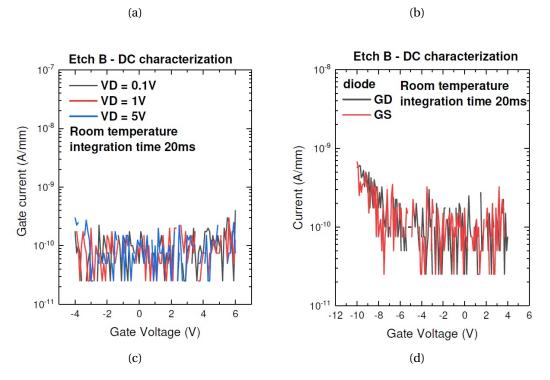

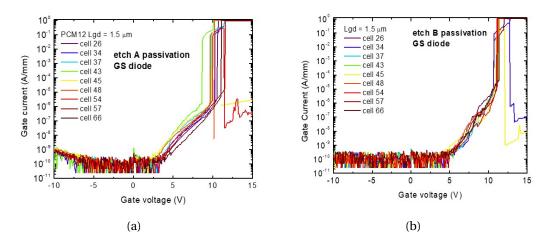

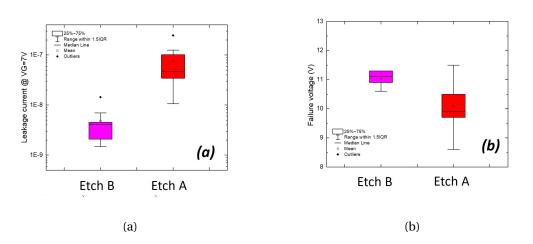

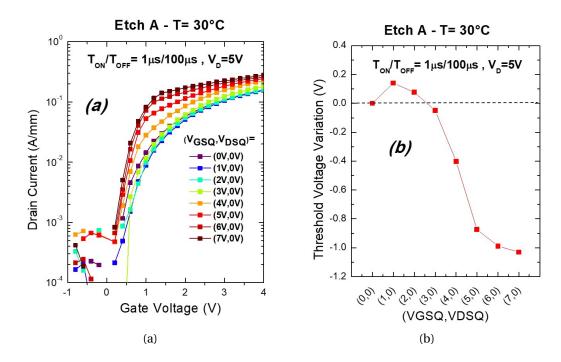

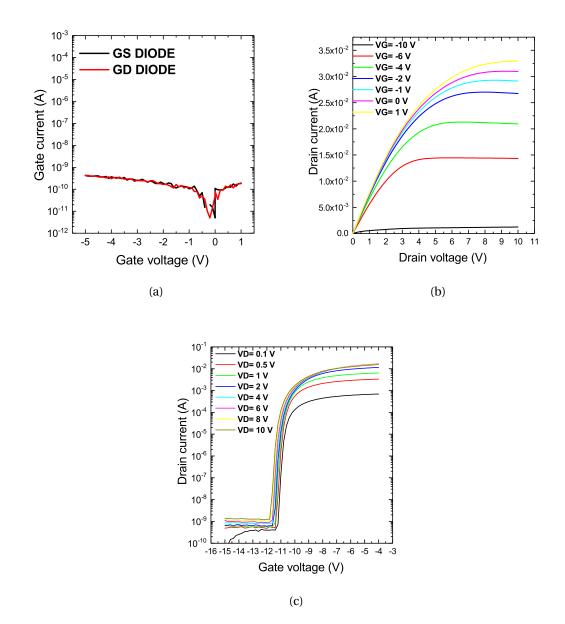

| 4.10 | DC gate leakage measurements on small transistors.                                                                                                | 99  |

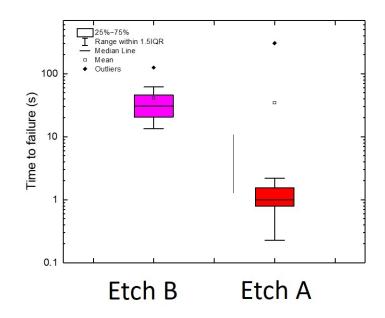

| 4.11 | Catastrophic breakdown, 9 device per wafer.                                                                                                       | 100 |

| 4.12 | (a)Leakage current at $V_G$ = 7 V for tow devices. (b) Failure voltage for etch                                                                   |     |

|      | A and B                                                                                                                                           | 100 |

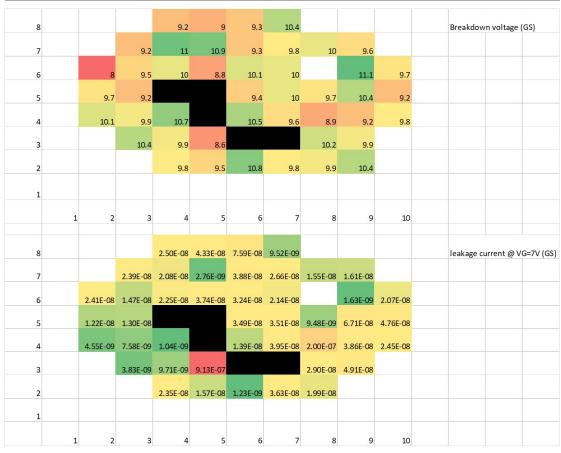

| 4.13 | The spatial map of leakage (at 7 V) breakdown voltage. The leakage                                                                                |     |

|      | current and breakdown voltage strongly depends on the cell position                                                                               |     |

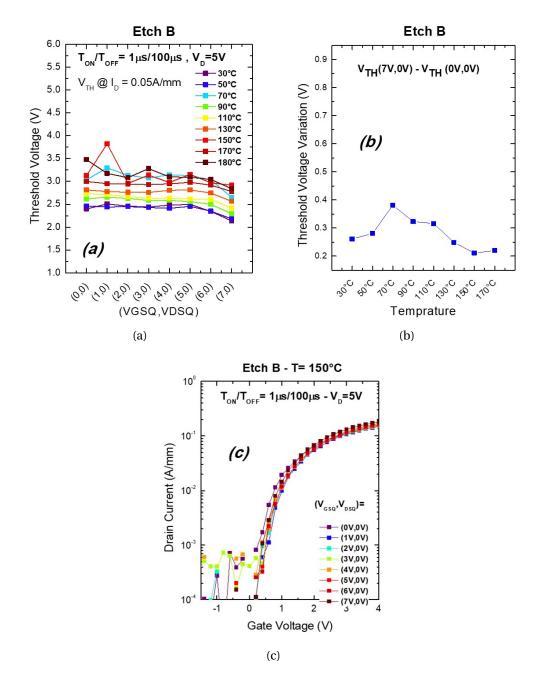

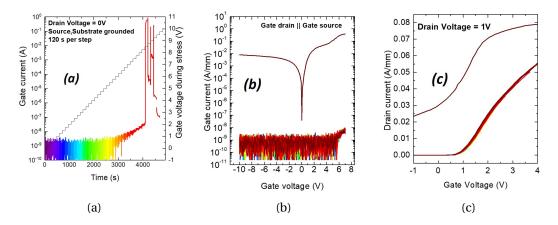

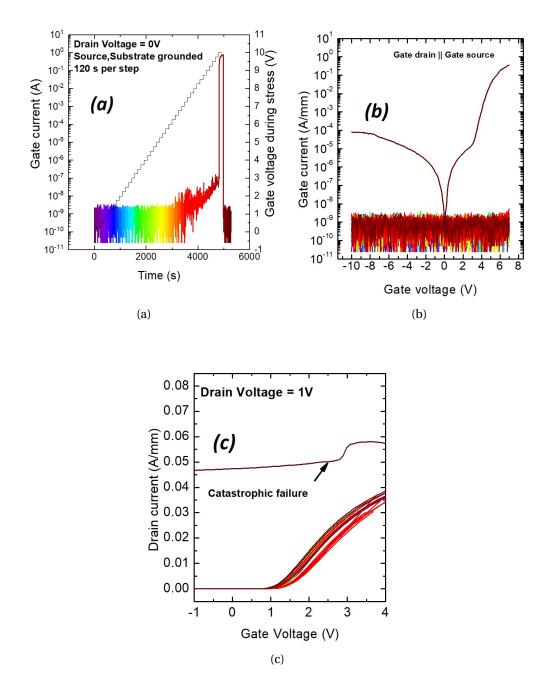

|      | and on the device topology.                                                                                                                       | 101 |