# Modeling & Simulation of High Performance Nanoscale MOSFETs

### Pramod Kumar Agarwal

Department of Electrical Engineering National Institute of Technology, Rourkela Rourkela-769008, Odisha, INDIA May 2013

# Modeling & Simulation of High Performance Nanoscale MOSFETs

A dissertation submitted in partial fulfillment of the requirements for the degree of

Master of Technology

in

Electronic Systems and Communication

by

Pramod Kumar Agarwal

(Roll-211EE1323)

Under the Guidance of

Dr. Prasanna Kumar Sahu

Department of Electrical Engineering National Institute of Technology, Rourkela Rourkela-769008, Odisha, INDIA 2011-2013

### DEDICATED

TO

MY LOVING PARENTS, BROTHERS, SISTERS, BROTHER-IN-LAWS, AND MY SWEET NEPHEW SOHAM.

### **Declaration**

#### I certify that

- The work contained in this thesis is original and has been done by me under the guidance of my supervisor.

- The work has not been submitted to any other Institute for any other degree or diploma.

- I have followed the guidelines provided by the Institute in preparing the thesis.

- I have confirmed to the norms and guidelines given in the Ethical Code of Conduct of the Institute.

- Whenever I have used materials (data, theoretical analysis, figures, and text) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references. Further, I have taken permission from the copyright owners of the sources, whenever necessary.

Pramod Kumar Agarwal Rourkela, May 2013

## Department of Electrical Engineering National Institute of Technology, Rourkela

### CERTIFICATE

This is to certify that the thesis entitled "Modeling & Simulation of High Performance Nanoscale MOSFETs" by Mr. Pramod Kumar Agarwal, submitted to the National Institute of Technology, Rourkela (Deemed University) for the award of Master of Technology in Electrical Engineering with the specialization of "Electronic Systems and Communication", is a record of bonafide research work carried out by him in the Department of Electrical Engineering, under my supervision. I believe that this thesis fulfills part of the requirements for the award of degree of Master of Technology. The results embodied in the thesis have not been submitted for the award of any other degree elsewhere.

Dr. Prasanna Kumar Sahu

Dept. of Electrical Engineering

National Institute of Technology

Rourkela, Odisha, 769008

INDIA

Place: N.I.T., Rourkela

Date:

### **Acknowledgements**

First and foremost, I am truly indebted and wish to express my gratitude to my supervisor Associate Professor Dr. Prasanna Kumar Sahu for his inspiration, excellent guidance, continuing encouragement and unwavering confidence and support during every stage of this endeavour without which, it would not have been possible for me to complete this undertaking successfully.

I express my deep gratitude to the members of Masters Scrutiny Committee, Dr. Dipti Patra, Dr. Susmita Das, Dr. Supratim Gupta and K. R. Subhashini for their loving advise and support. I am also very much obliged to the Head of the Department of Electrical Engineering, NIT Rourkela for providing all possible facilities towards this work. Thanks to all other faculty members in the department.

I would also like to express my heartfelt gratitude to my friend Kumar Prasannajit Pradhan and PhD research scholar Sushanta Kumar Mohapatra who always inspired me and particularly helped me in the lab.

My wholehearted gratitude to my parents, Narayan Das Agarwal, Geeta Agarwal and my uncle late Mr. Krishan Lal Mittal for their constant encouragement, love, wishes and support. Above all, I thank Almighty who bestowed his blessings upon us.

Pramod Kumar Agarwal Rourkela, May 2013

### **Abstract**

Silicon-on-insulator (SOI) has been the forerunner of the CMOS technology in the last few decades offering superior CMOS devices with higher speed, higher density and reduced second order effects for submicron VLSI applications. A new type of transistor without junctions and no doping concentration gradients is analysed and demonstrated. These device structures address the challenge of short channel effects (SCEs) resulting with scaling of transistor dimensions and higher performance for deep submicron VLSI integration.

Recent experimental studies have invigorated interest in partially depleted (PD) SOI devices because of their potentially superior scalability relative to bulk silicon CMOS devices. SELBOX structure offer an alternative way of suppressing kink effect and self heating effects in PD-SOI devices with a proper selection of oxide gap length. Also in order to mitigate the difficulties in fabrication of ultra thin devices for the semiconductor industry, resulting from scaling of gate length in MOSFET, a new device structure called junctionless (JL) transistors have recently been reported as an alternative device.

In conclusion, extensive numerical simulation studies were used to explore and compare the electrical characteristics of SELBOX SOI MOSFET with a conventional single-material gate (SMG) bulk MOSFET. The proposed work investigates the DC and AC characteristics of the junctionless transistors. Also the performance analysis of JL transistors is compared and presented with the conventional DG MOSFET structure. The results presented in this work are expected to provide incentive for further experimental exploration.

# **Contents**

| C            | ntents                                               | i   |

|--------------|------------------------------------------------------|-----|

| $\mathbf{L}$ | t of Figures                                         | vii |

| $\mathbf{L}$ | t of Tables                                          | ix  |

| 1            | INTRODUCTION                                         | 1   |

|              | I.1 Background                                       | 1   |

|              | 1.2 Future Technology Node Requirements              | 3   |

|              | 1.3 Technology Scaling                               | 4   |

|              | 1.3.1 Why MOSFET Scaling?                            | 5   |

|              | 1.3.2 Moore's Law                                    | 6   |

|              | 1.3.3 CMOS Scaling Trends                            | 8   |

|              | 1.3.4 Challenges to Miniaturization of MOSFETs       | 10  |

|              | 1.4 Motivation                                       | 13  |

|              | 1.5 Objectives                                       | 16  |

|              | 1.6 Thesis Organisation                              | 16  |

| <b>2</b>     | Short Channel Effects in Nanoscale MOSFETs: A Review | 18  |

|              | 2.1 Introduction                                     | 18  |

|              | 2.2 Issues for Nanoscale MOSFETs                     | 20  |

|              | 2.2.1 Channel                                        | 20  |

|              | 2.2.2 Gate                                           |     |

|              | 2.2.3 Drain/source                                   | 29  |

CONTENTS ii

|   | 5.1 | Conclusions                                        | 67       |

|---|-----|----------------------------------------------------|----------|

| 5 | Co  | nclusion & Scope for Future Work                   | 67       |

|   | 4.5 | Summary                                            | 66       |

|   |     | 4.4.2 AC Characteristics                           | 64       |

|   |     | 4.4.1 DC Characteristics                           | 58       |

|   | 4.4 | Results and Discussion                             | 57       |

|   | 4.3 | Simulation                                         | 57       |

|   | 4.2 | Device Structures                                  | 55       |

|   | 4.1 | Introduction                                       | 53       |

| 4 | An  | alysis of DC & AC Performance of DG-JL MOSFETs     | 53       |

|   | 3.5 | Summary                                            | 52       |

|   |     | Results and Discussion                             | 47       |

|   |     | Simulation                                         | 46       |

|   |     | Device Structures                                  | 45       |

|   | 3.1 | Introduction                                       | 44       |

| 3 | An  | alysis & Minimization of Kink in PD-SOI MOSFETs    | 44       |

|   | ∠.0 | Summary                                            | 42       |

|   | 26  | 2.5.2 Different Multi-gate MOSFET Structures       | 40<br>42 |

|   |     | 2.5.1 Advantages of Multi-gate MOSFETS             | 39       |

|   | 2.5 | Multi-gate MOSFET: The Future CMOS Transistor      | 39       |

|   | 0.5 | 2.4.3 Conductance based MOSFET model               | 39       |

|   |     | 2.4.2 Potential based MOSFET model                 | 39       |

|   |     | 2.4.1 Charge based MOSFET model                    | 38       |

|   | 2.4 | Standard MOSFET models                             | 38       |

|   |     | 2.3.3 Strained Silicon Technique (S-Si) Structures | 37       |

|   |     | 2.3.2 Silicon-on-Insulator (SOI)                   | 35       |

|   |     | 2.3.1 High-k Dielectric Material Gate              | 32       |

|   | 2.3 | Solutions to Short Channel Effects                 | 32       |

|   |     | 2.2.4 Substrate (bulk)                             | 30       |

| CONTENTS | iii |

|----------|-----|

|          |     |

| $\mathbf{B}$ | Bibliography              | 70 |

|--------------|---------------------------|----|

|              | 5.3 List of Publications  | 69 |

|              | 5.2 Scope for Future Work | 68 |

# **List of Abbreviations**

| Abbreviation | Description                                                |  |  |  |  |  |

|--------------|------------------------------------------------------------|--|--|--|--|--|

| ITRS         | International Technology Roadmap for Semiconductors        |  |  |  |  |  |

| CMOS         | Complementary Metal-Oxide Semiconductor                    |  |  |  |  |  |

| FET          | Field Effect Transistor                                    |  |  |  |  |  |

| GaAs         | Gallium Arsenide                                           |  |  |  |  |  |

| SOI          | Silicon-On- Insulator                                      |  |  |  |  |  |

| SS           | Subthreshold Slope                                         |  |  |  |  |  |

| PD-SOI       | Partially-Depleted Silicon-On- Insulator                   |  |  |  |  |  |

| FD-SOI       | Fully-Depleted Silicon-On- Insulator                       |  |  |  |  |  |

| EOT          | Effective Oxide Thickness                                  |  |  |  |  |  |

| DT           | Direct Tunneling                                           |  |  |  |  |  |

| GIDL         | Gate Induced Drain Lowering                                |  |  |  |  |  |

| DIBL         | Drain Induced Barrier Lowering                             |  |  |  |  |  |

| BTBT         | Band-to-Band Tuneling Current                              |  |  |  |  |  |

| DG-MOSFET    | Double-Gate Metal-Oxide Field Effect Transistor            |  |  |  |  |  |

| DG-JL MOSFET | Double-Gate Junctionless Metal-Oxide Field Effect Transis- |  |  |  |  |  |

|              | tor                                                        |  |  |  |  |  |

| SCEs         | Short Channel Effects                                      |  |  |  |  |  |

| FBEs         | Floating Body Effects                                      |  |  |  |  |  |

| SELBOX       | Selective Buried Oxide                                     |  |  |  |  |  |

# **List of Symbols**

| Symbols              | Description                   |

|----------------------|-------------------------------|

| $V_{dd}$ or $V_{DD}$ | Power Supply Voltage          |

| $V_{th}$ or $V_T$    | Threshold Voltage             |

| $I_{ds}$ or $I_D$    | Drain Current                 |

| $SiO_2$              | Silicon dioxide               |

| $t_{ox}$ or $T_{ox}$ | Gate-Oxide Thickness          |

| $t_b$                | Buried-Oxide Thickness        |

| $L_g$ or L           | Channel Length                |

| W                    | Channel Width                 |

| $N_A$                | Acceptor Doping Concentration |

| $N_D$                | Donor Doping Concentration    |

| $t_{Si}$ or $T_{Si}$ | Silicon-body Thickness        |

| $G_m$                | Transconductance              |

| $t_b$                | Buried-Oxide Thickness        |

| $arepsilon_{si}$     | permittivity of Silicon       |

| $N_{sub}$            | Substrate Doping              |

| $I_{on}$             | On-State drive Current        |

| $I_{off}$            | Off-State Leakage Current     |

| $v_{sat}$            | Carriers Velocity Saturation  |

| $C_G$                | gate Capacitance              |

| $C_{dep}$            | Depletion Capacitance         |

| $C_{ox}$             | Oxide Capacitance             |

| $k_B$                | Boltzman Constant             |

# List of Useful Constants with their Values

| Constants                                     | Values                                            |  |  |

|-----------------------------------------------|---------------------------------------------------|--|--|

| Electronic Charge(q)                          | $1.6 \times 10^{-19}$ Coulomb                     |  |  |

| Electron mass(m)                              | $9.1 \times 10^{-31} Kg$                          |  |  |

| Permeability of $Vaccum(\mu_o)$               | $4\Pi \times 10^{-7} \mathrm{H/m}$                |  |  |

| Permittivity of $Vaccum(\varepsilon_o)$       | $10^{-9}/36\Pi = 8.85 \times 10^{-12} \text{F/m}$ |  |  |

| Boltzman Constant $(k_B)$                     | $1.38 \times 10^{-23} \text{J/K}$                 |  |  |

| Permittivity of Silicon( $\varepsilon_{si}$ ) | $11.68 \simeq 12$                                 |  |  |

| Permittivity of $SiO_2(\varepsilon_{SiO_2})$  | 3.9                                               |  |  |

| Permittivity of $HfO_2(\varepsilon_{HfO_2})$  | $20 \sim 24$                                      |  |  |

| Room $Temperature(T)$                         | 300K                                              |  |  |

| Thermal Voltage $(V_T = k_B T/q)$             | $0.0259V \simeq 26mV$                             |  |  |

# **List of Figures**

| 1.1 Moore's Law                                                          |          | 6  |

|--------------------------------------------------------------------------|----------|----|

| 1.2 Schematic illustration of the scaling of Si technology by a factor   | $\alpha$ | 8  |

| 1.3 Reduction of barrier for majority carrier to enter the channel .     |          | 10 |

| 1.4 Scaling trend of $V_{dd}, V_{th}, T_{ox}$ versus CMOS channel length |          | 11 |

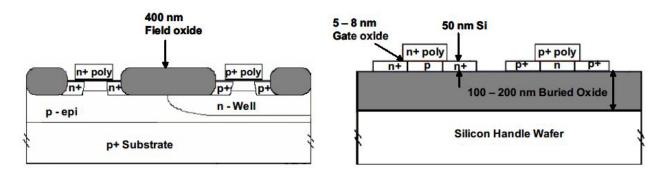

| 1.5 Cross-sectional view of the bulk-Si and SOI CMOS Devices $$          |          | 14 |

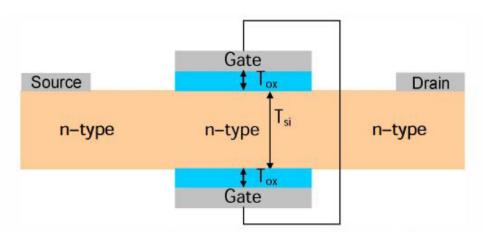

| 1.6 Schematic diagram of Double Gate(DG) JL MOSFET                       |          | 15 |

| 2.1 Characteristics of sub-threshold conduction                          |          | 21 |

| 2.2 Threshold voltage roll-off and drain induced barrier lowering        |          | 22 |

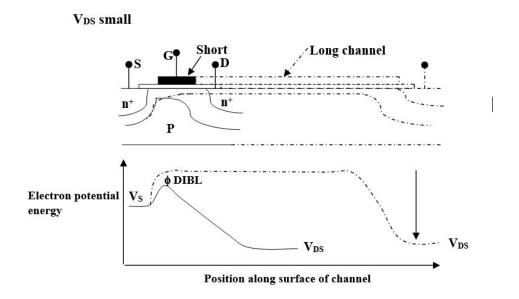

| 2.3 Electron Potential Energy Variations along the position in cham      | nel      | 23 |

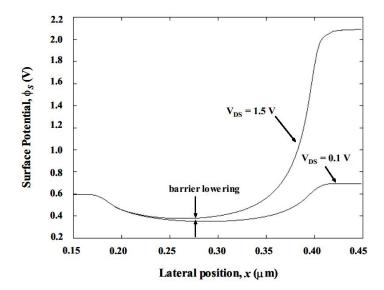

| 2.4 Surface potential variation along the channel for $V_D$ =0.1V and 1  | l.5V     | 24 |

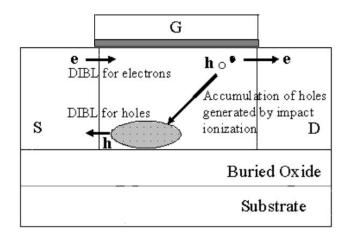

| 2.5 Three mechanisms determining SCE in SOI MOSFETs                      |          | 25 |

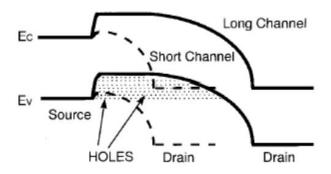

| 2.6 Comparison of energy band diagrams for FD-nMOSFETs                   |          | 26 |

| 2.7 Effects of three mechanisms on $V_{th}$ dependence on gate length .  |          | 26 |

| 2.8 Various leakage mechanisms in a MOSFET                               |          | 31 |

| 2.9 Electric field lines from the drain [1]                              |          | 33 |

| 2.10High-k Metal Gate Structure                                          |          | 33 |

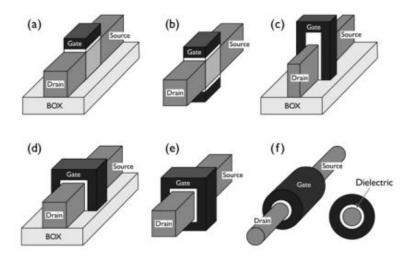

| 2.11Advanced MOSFETs                                                     |          | 35 |

| 2.12 Various SOI devices                                                 |          | 36 |

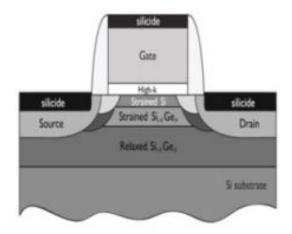

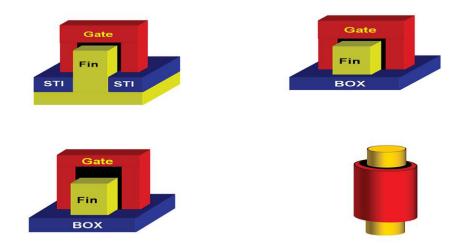

| 2.13MOSFET with a strained-silicon channel [2]                           |          | 38 |

| 2.14 Various Multigate MOSFET structures                                 |          | 41 |

| 2.15Other Multigate MOSFET structures                                    |          | 41 |

LIST OF FIGURES viii

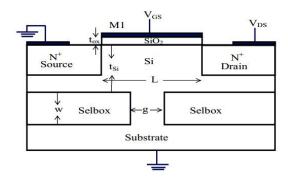

| 3.1 Device structure of PD-SOI                                               | 46 |

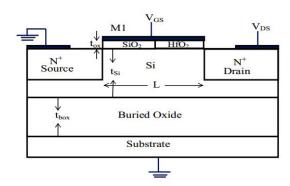

|------------------------------------------------------------------------------|----|

| 3.2 Device structure of Selbox                                               | 46 |

| 3.3 Device structure of PD-SOI using Dual Insulator                          | 46 |

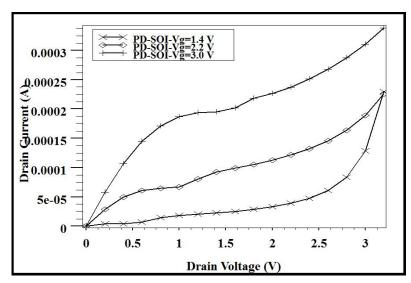

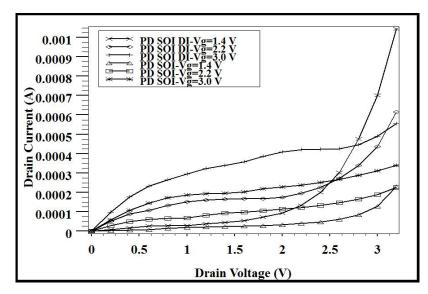

| 3.4 Simulation of $I_D$ Vs. $V_{DS}$ for PD-SOI MOSFET                       | 47 |

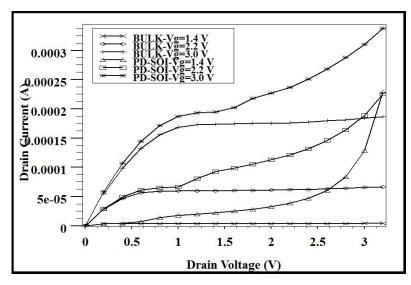

| 3.5 Simulation of $I_D$ Vs. $V_{DS}$ for both BULK and PD-SOI MOSFET .       | 48 |

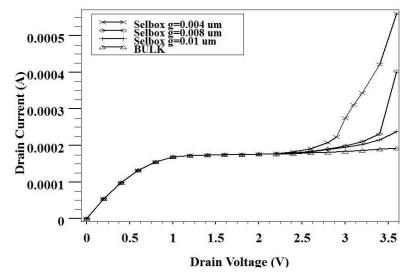

| 3.6 Simulation of $I_D$ Vs. $V_{DS}$ for Selbox Structure with gap length $$ | 49 |

| 3.7 Simulation of $I_D$ Vs. $V_{DS}$ for Selbox Structure with gap width     | 49 |

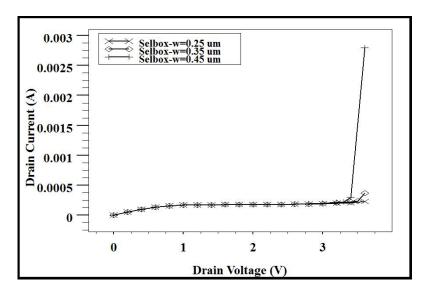

| 3.8 Simulation of $I_D$ Vs. $V_{DS}$ for PD-SOI with Dual Insulator (DI)     | 51 |

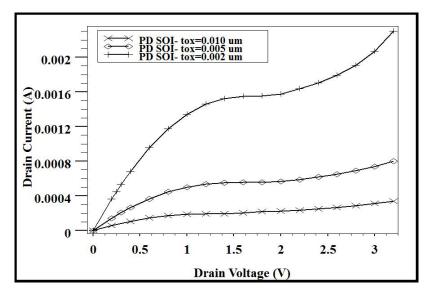

| 3.9 Simulation of $I_D$ Vs. $V_{DS}$ for PD-SOI with varying $t_{ox}$        | 51 |

| 4.1 Schematic diagram of Double Gate(DG) JL MOSFET                           | 54 |

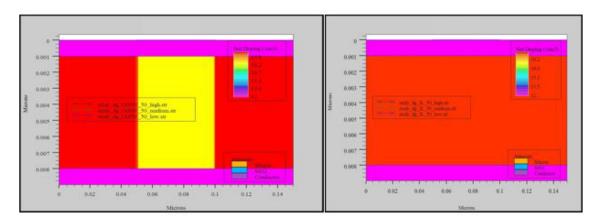

| 4.2 Simulated Structures of Double-Gate nMOSFETs                             | 55 |

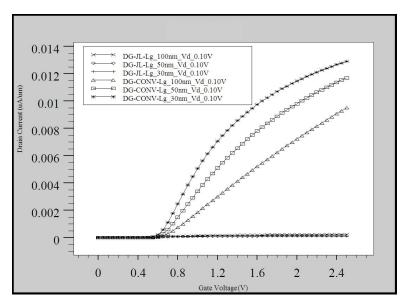

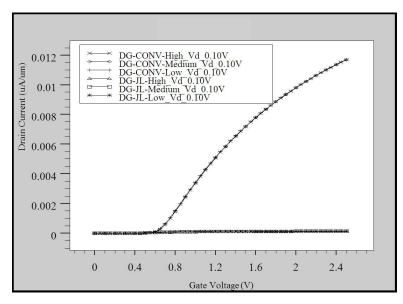

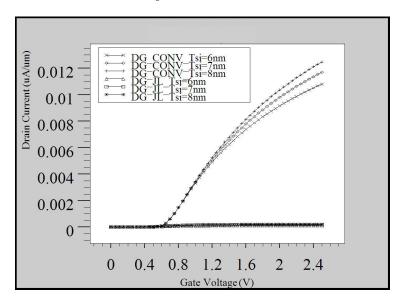

| 4.3 $I_D - V_{GS}$ characteristics for DG nMOSFETs with varying $L_g$        | 58 |

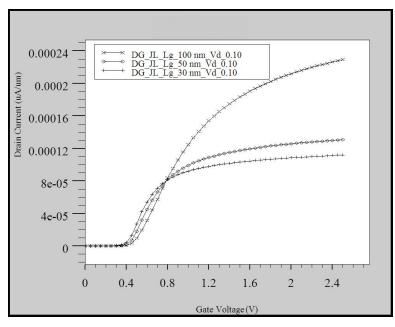

| 4.4 $I_D-V_{GS}$ characteristics for DG JL nMOSFETs with varying $L_g$ .     | 59 |

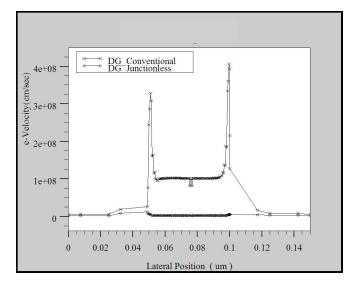

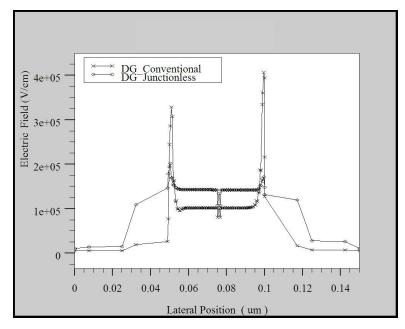

| 4.5 Electron Velocity along the channel position for DG-MOSFETs              | 59 |

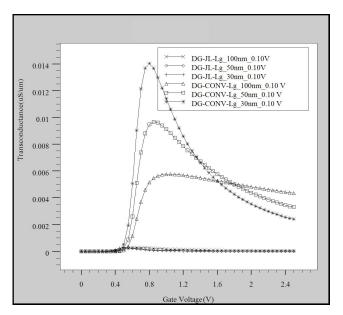

| 4.6 Transconductances( $G_m$ ) for the DG-MOSFETs at $V_D$ =0.1V             | 60 |

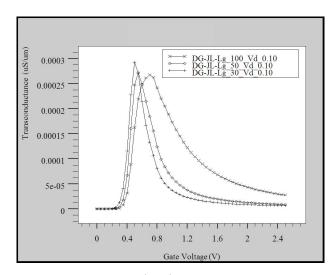

| 4.7 Transconductances( $G_m$ ) for the DG-JL MOSFETs at $V_D$ =0.1V          | 60 |

| 4.8 Electric Field for the DG-MOSFETs at $V_D$ =0.1V                         | 61 |

| 4.9 $I_D - V_{GS}$ curve for DG nMOSFET with varying channel doping          | 62 |

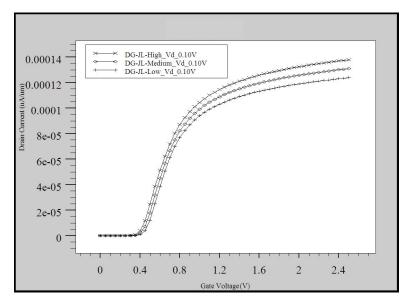

| $4.10I_D-V_{GS}$ curve for DG JL nMOSFETs with varying channel doping.       | 62 |

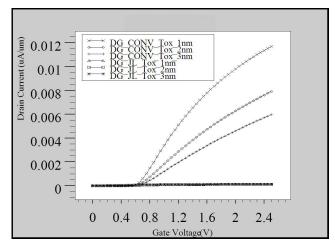

| $4.11I_D - V_{GS}$ curve for DG nMOSFETs with $T_{ox}$                       | 63 |

| $4.12I_D-V_{GS}$ curve for DG JL nMOSFETs with varying $T_{ox}$              | 63 |

| $4.13I_D - V_{GS}$ curve for DG nMOSFETs with varying $T_{si}$               | 64 |

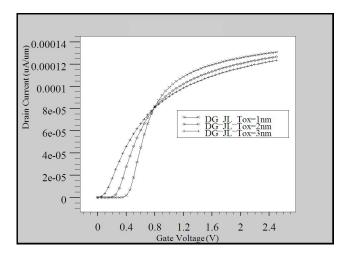

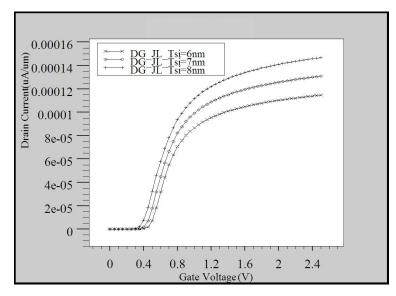

| $4.14I_D-V_{GS}$ curve for DG JL nMOSFETs with varying $T_{si}$              | 65 |

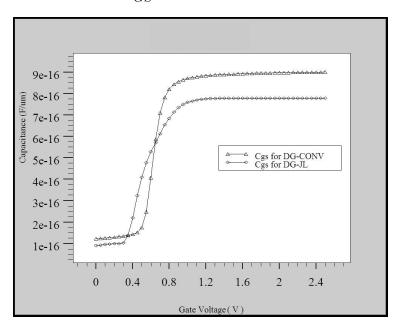

| 4.15Simulated $C_{gs}$ for DG nMOSFETs                                       | 65 |

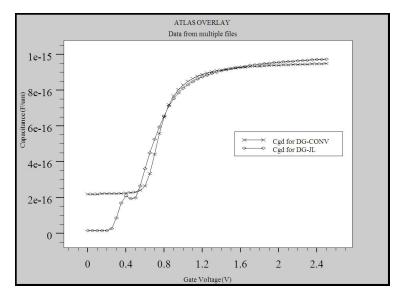

| 4.16Simulated $C_{ad}$ for DG nMOSFETs                                       | 66 |

## **List of Tables**

| 1.1 | Improvements in Technology Node over the years    | 7  |

|-----|---------------------------------------------------|----|

| 1.2 | Technology Scaling Rules for Three Cases          | 12 |

| 4.1 | Parameters for the simulated Double-Gate nMOSFETs | 56 |

| 4.2 | $V_T$ and SS of DG-MOSFETs with varied parameters | 56 |

| 4.3 | DIBL values with varying Gate length( $L_g$ .)    | 57 |

#### Chapter 1

### INTRODUCTION

#### 1.1 Background

The central component of semiconductor electronics is the integrated circuit (IC), which combines the basic elements of electronic circuits - such as transistors, diodes, capacitors, resistors and inductors - on one semiconductor substrate. The two most important elements of silicon electronics are transistors and memory devices. For logic applications MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) are used. MOSFETs have been the major device for ICs over the past two decades. With technology advancement and the high scalability of the device structure, silicon MOSFET-based VLSI circuits have continually delivered performance gain and/or cost reduction to semiconductor chips for data processing and memory functions.

The semiconductor industry has showcased a spectacular exponential growth in the number of transistors per integrated circuit for several decades, as predicted by Moore's law. The relentless evolution of electronics, information technology(IT), and communications has been mainly enabled by continuous progress in silicon-based CMOS technology. This continuous progress has been achieved particularly by its dimensional scaling. CMOS scaling has been the main driving force of Si technology advancement to improve both device density and performance. The reduction in cost-per-function has been steadily increasing the economic productivity with every new technol-

ogy generation. Besides scalability, the other unique device properties such as input resistance, self isolation, zero static power dissipation, simple layout and process steps have made CMOS transistors as the main components of the current integrated circuits(ICs). Today CMOS ICs are found everywhere and indespensible in our daily life, ranging from portable electronics to telecommunications and transportation.

A lot of research has gone into device design over the last thirty years, but the evolution of process technologies brings new obstacles as well as new opportunities to device designers. The future technology trend predicted by ITRS (International Technology Roadmap for Semiconductors), physical dimensions and electrostatic limitations faced by conventional process and fabrication technologies will require the dimensional scaling of complementary metal-oxide-semiconductor (CMOS) devices within the next decade. However, as the device scaling continues for the 21st century, it turns out that the historical growth, doubled circuit density and increased performance by about 40% every technology generation, followed by Moore's Law cannot be maintained only by the conventional scaling theory.

As the CMOS technology scaling enters the nanometer regime, many serious problems called the small geometry effects or short channel effects (SCEs) comes into play. Some of these effects are such as increased laekage currents, diffulty on increase of on-current, large parameter variations, low reliability and yield, increase in manufacturing cost, and etc. In order to sustain the historical improvements, future technology scaling and to mitigate these small geometry effects to a considerable level, several strategies and new device structures have been researched and introduced. A few examples of those are; increasing electrostatic control over the channel by means of the continuous EOT scaling with high-k/metal gate stack, Multi-gate MOSFET structures, silicon-on-insulator(SOI), Strained Silicon (S-Si), Si nanowire/carbon nanotube FETs, etc. Many of these devices have been shown to have favorable device properties and new device characteristics, and require new fabrication

techniques. These nanoscale devices have a significant potential to revolutionize the fabrication and integration of electronic systems and scale beyond the perceived scaling limitations of traditional CMOS.

#### 1.2 Future Technology Node Requirements

The factors or features to be distinguished between several logic technology options are:

#### a) High performance (HP):

The high performance corresponds to high complexity ICs that require high clock frequencies and at the same time can deal with high power consumption. The increase in clock frequency from one technology node to the next can be achieved at the device level by an improvement of the intrinsic switching time of a transistor of 17% per year, while maintaining the transistor off-state current to a value acceptable from a power consumption point of view. The intrinsic switching time  $(\tau)$  is the time needed by a transistor supplying on-state current to make the gate of an identical transistor switching from ground to the supply voltage.

$$I = \frac{Q}{t} = \frac{CV}{\tau}$$

$$\tau = \frac{Q}{I} = \frac{CV}{I} \tag{1.1}$$

where,

$C \to \operatorname{Gate}$  capacitance  $V \to \operatorname{Supply}$  voltage  $I \to \operatorname{On-state}$  current of the device

Therefore, the most efficient way to achieve enhanced performance is to scale the gate length of the transistor aggressively. Consequently, this will result in reduced gate capacitance while increasing the on-state current.

#### b) Low operating power (LOP):

The low operating power technology option mainly aims at relatively high

performance mobile applications such as notebook computers. The key challenge is to increase the circuit performance while decreasing the dynamic power consumption as much as possible when the device is operating. The dynamic power consumption at the device level is a measure of power-delay product given by

$$P\tau = \frac{CV}{I}P = \frac{CV}{I}VI$$

$$P\tau = CV^{2}$$

$$P\tau \propto V^{2}$$

(1.2)

Therefore, the most efficient way to reduce the dynamic power consumption is thus to reduce the supply voltage as far as possible i.e.  $V \Downarrow \Rightarrow P\tau \Downarrow \Rightarrow$  Dynamic Power Consumption (given by  $0.5CV^2f$ ) decreases.

#### c) Low stand-by power dissipation (LSTPD):

The low stand-by power option is used for lower performance, low-cost consumer applications such as cellular phones. For such applications, the main concern or key issue is to continue increasing circuit performance while maintaining the power consumption as low as possible when the IC is idle. This static power consumption at the transistor level is governed by the leakage current of the devices. Therefore, low stand-by power technology option requires very low transistor-off state currents as well as very low parasitic currents such as gate leakage.

#### 1.3 Technology Scaling

The lateral geometric dimensions of devices and interconnects are reduced. This reduction in size is referred to as "scaling" of the geometric dimensions of the integrated circuits(IC). The minimum feature size is smaller size of object (e.g. gate length or interconnect linewidth) on IC. Over the past

decades, the MOSFET has continually been scaled down in size; typical MOSFET channel lengths were once several micrometres, but modern integrated circuits are incorporating MOSFETs with channel lengths of tens of nanometers. As a consequence of this minimum feature size of ICs, the number of transistors have increased over time. The semiconductor industry maintains a "roadmap", the ITRS, which sets the pace for MOSFET development. Historically, the difficulties with decreasing the size of the MOSFET have been associated with the semiconductor device fabrication process, the need to use very low voltages, and with poorer electrical performance necessitating circuit redesign and innovation (small MOSFETs exhibit higher leakage currents, lower output resistance, lower transconductance, interconnect capacitance, process variations, etc.

#### 1.3.1 Why MOSFET Scaling?

Smaller size of MOSFETs is highly desirable for several reasons. The primary reason to make transistors smaller in size is to integrate more and more number of devices in a given chip area. This results in a chip with the same functionality in a smaller area, or chips with more functionality in the same area. Since fabrication costs for a semiconductor wafer are relatively fixed, the cost per integrated circuits is mainly related to the number of chips that can be produced per wafer. Hence, smaller ICs allow more chips per wafer, reducing the price per chip. In fact, over the past 30 years the number of transistors per chip has been doubled every 23 years once a new technology node is introduced. For example the number of MOSFETs in a microprocessor fabricated in a 45 nm technology can well be twice as many as in a 65 nm chip. This doubling of transistor density was first observed by Gordon Moore in 1965 and is commonly referred to as Moore's law.

It is also expected that smaller transistors switch faster. For example, one approach to size reduction is a scaling of the MOSFET that requires all device dimensions to reduce proportionally. The main device dimensions are the channel length, channel width, and oxide thickness. When they are scaled

down by equal factors, the transistor channel resistance does not change, while gate capacitance is cut by that factor. Hence, the RC delay of the transistor scales with a similar factor. However, this has been traditionally the case for the older technologies, for the state-of-the-art MOSFETs reduction of the transistor dimensions does not necessarily translate to higher chip speed because the delay due to interconnections is more significant.

#### 1.3.2 Moore's Law

In the last forty-five years since 1965, the price of one bit of semiconductor memory has been dropped 100 million times. The primary engine that powered the proliferation of electronics is "miniaturization". By making the transistors and interconnects smaller, more circuits can be fabricated on each silicon wafer and therefore each circuit becomes smaller. Miniaturization has also been responsible to the improvements in speed and power consumption in ICs.

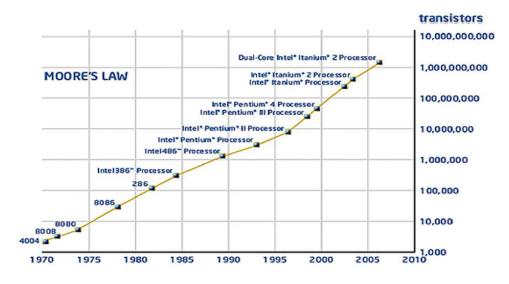

Gordon Moore made an empirical observation in 1965 that the number of devices on a chip doubles every 18 or 24 months or so as shown in Figure 1.1 [3].

Figure 1.1: Moore's Law

This Moore's law is a succint description of the rapid and persistent trend

of miniaturization. Each time the minimum line width is reduced, we say that a new technology generation or technology node is introduced. Examples of technology generations is shown in Table 1.1:

Table 1.1: Improvements in Technology Node over the years

| Year       | 2004 | 2006 | 2008 | 2010 | 2011 | 2013 | 2016 | 2022 |

|------------|------|------|------|------|------|------|------|------|

| Technology | 90nm | 65nm | 45nm | 32nm | 22nm | 16nm | 14nm | 10nm |

| Node:      |      |      |      |      |      |      |      |      |

The numbers shown in the table refers to the minimum metal line width. Poly-Si lengths may be even smaller. At each new node, all the features in the circuit layout, such as the contact holes, are reduced in size to 70% of the previous node. Historically, a new technology node is introduced every two to three years. The main reward for introducing a new technology node is the reduction of circuit size by half. (70% of previous line width means 50% reduction in area i.e., 0.7\*0.7=0.49). Since nearly twice as many circuits can be fabricated on each wafer with each new technology node, the cost per circuit is reduced significantly which drives down the cost of ICs.

It is intuitive that Moore's Law cannot be sustained forever. However, predictions of size reduction limits due to material or design constraints, or even the pace of size reduction, have proven to elude the most insightful scientists. The predicted 'limit' has been dropping at nearly the same rate as the size of the transistors. Further technology scaling requires major changes in many areas, including: 1) improved lithography techniques and non-optical exposure technologies; 2) improved transistor design to achieve higher performance with smaller dimensions; 3) migration from current bulk CMOS devices to novel materials and structures, including silicon-on-insulator, strained Si and novel dielectric materials; 4) circuit sensitivity to soft errors from radiation; 5) smaller wiring for on-chip interconnection of the circuits; 6) stable circuits; 7) more productive design automation tools; 8) denser memory cells, and 9) manageable capital costs. Metal gate and high-k gate dielectrics were introduced into production in 2007 to maintain technology scaling trends.

In addition, packaging technology needs to progress at a rate consistent with on-going CMOS technology scaling at sustainable cost/performance levels. This requires advances in I/O density, bandwidth, power distribution, and heat extraction. System architecture will also be required to maximize the performance gains achieved in advanced CMOS and packaging technologies.

#### 1.3.3 CMOS Scaling Trends

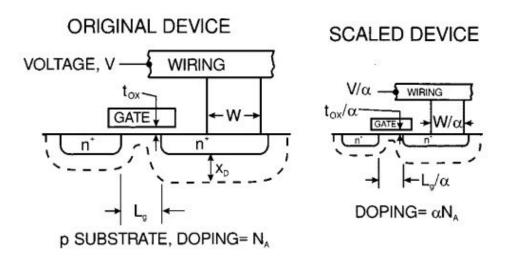

For many years now, the shrinking of MOSFETs has been governed by the ideas of scaling. The basic idea is illustrated in the Figure 1.2 [4]: a large FET is scaled down by factor  $\alpha$  to produce a smaller FET with similar behavior.

Figure 1.2: Schematic illustration of the scaling of Si technology by a factor  $\alpha$

Device scaling is based upon simple principles; by reducing the sizes of devices and interconnects, density, and power, the speed and performance of transistors can be improved. Device scaling mainly focusses on

- a) scaling of threshold voltage with feature size

- b) scaling of gate oxide thickness with feature size

- c) scaling of supply voltage with feature size

With technology scaling, the MOS device channel length is reduced. When

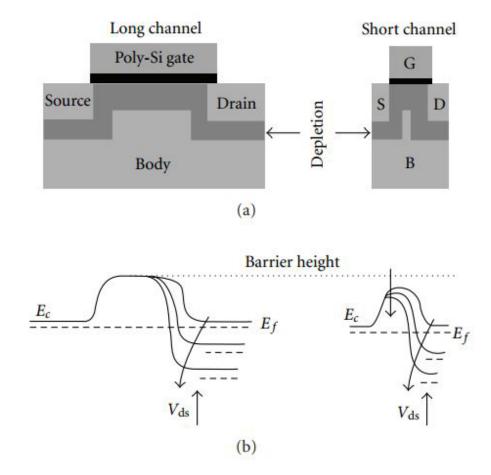

the dimensions of a MOSFET are scaled down, both the voltage level and the gate-oxide thickness are also reduced. The supply voltage  $V_{dd}$  has to be scaled down in order to keep the power consumption under control. The transistor  $V_{th}$  also had to be scaled down to maintain a high drive current and achieve performance improvement. In a given technology node, since the source-body and drain-body depletion widths are predefined based on the doping, the rate at which the barrier height increases as a function of distance from the source into the channel is constant. Therefore, when the channel length is reduced, the barrier for the majority carriers to enter the channel is also reduced as shown in Figure 1.3 [5]. As a result threshold voltage is reduced. In short channel transistor, the barrier height and therefore the threshold voltage are a strong function of the drain voltage. Figure 1.3 [5] indicates, the barrier reduces as the drain voltage is increased.

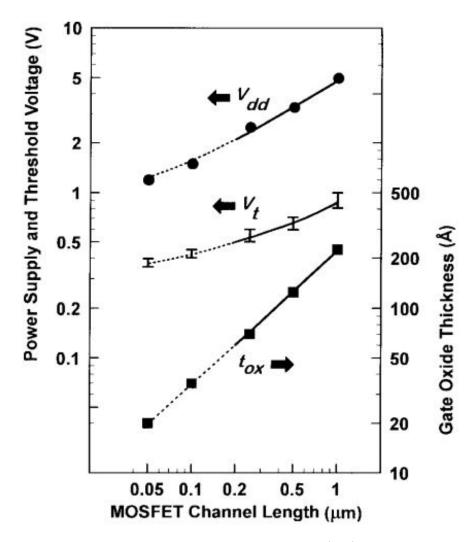

Aggressive scaling of CMOS technology in recent years has reduced the silicon dioxide  $(SiO_2)$  gate dielectric thickness below 20Å. In 90 nm, the gate oxide consists of about 5 atomic layers equivalent to 1.2 nm in thickness. The thinner the gate oxide, the higher the transistor current and consequently the switching speed. The scaling trend of power supply voltage  $(V_{dd})$ , threshold voltage  $(V_{th})$ , and gate-oxide thickness  $(T_{ox})$  as a function of CMOS channel length is shown in Figure 1.4 [6].

When  $V_{dd}$  is reduced towards shorter channel lengths, it becomes increasingly difficult to satisfy both the performance and the off current requirements. Trade-off between leakage current and circuit speed stems due to subthreshold nonscalability. For this reason and for compatibility with the standardized power supply voltage of earlier generation systems, the general trend is that  $V_{dd}$  has not been scaled down in proportion to L and  $V_{th}$  has not been scaled down in proportion to Figure 1.4 [6].

When all of the voltages and dimensions are reduced by the scaling factor  $\alpha$  and the doping and charge densities are increased by the same factor, the electric field configurations inside the FET remains the same as it was in the

Figure 1.3: Channel length reduces the barrier for the majority of carriers to enter the channel

original device. This is called constant field scaling, which results in circuit speed increasing in proportion to the factor  $\alpha$  and circuit density increasing as  $\alpha^2$ . These scaling relations are shown in the second column of Table 1.2 along with the scaling behavior of some of the other important physical parameters.

$\alpha$  is the dimensional scaling parameter,  $\varepsilon$  is the electric field scaling parameter, and  $\alpha_d$  and  $\alpha_w$  are separate dimensional scaling parameters for the selective scaling case.  $\alpha_d$  is applied to the device vertical dimensions and gate length, while  $\alpha_w$  applies to the device width and the wiring.

#### 1.3.4 Challenges to Miniaturization of MOSFETs

Despite formidable challenges, however, many of those in the research community and industry do envision close variants of conventional microelec-

Figure 1.4: Scaling trend of power supply voltage  $(V_{dd})$ , threshold voltage  $(V_{th})$ , and gate-oxide thickness  $(T_{ox})$  as a function of CMOS channel length

tronic transistors becoming miniaturized into the nanometer-scale regime. For example, the International Technology Roadmap for Semiconductors(ITRS), published by the Semiconductor Industry Association, projects that chips will be made from transistors with major features (gate lengths) of 70 nm in the year 2010. Individual working transistors with 40 nm gate lengths have already been demonstrated in silicon. Transistors with gate lengths as small as 25 nm have been made using Strained Silicon (S-Si). However, to provide points of reference for contrasting nanoelectronic devices with scaled-down FETs, a few of the obstacles to FET scaling are simply enumerated below,

| Physical Parameter       | Constant Electric Field | Generalized Scaling      | Generalized Selective            |  |

|--------------------------|-------------------------|--------------------------|----------------------------------|--|

|                          | ScalingFactor           | Factor                   | ScalingFactor                    |  |

| Channel Length,          | $1/\alpha$              | $1/\alpha$               | $1/\alpha_d$                     |  |

| Insulator Thickness      |                         |                          |                                  |  |

| Wiring Width,            | $1/\alpha$              | $1/\alpha$               | $1/\alpha_w$                     |  |

| Channel Width            |                         |                          |                                  |  |

| Electric Field in device | 1                       | $\varepsilon$            | ε                                |  |

| Voltage                  | $1/\alpha$              | $\varepsilon/\alpha$     | $\varepsilon/\alpha_d$           |  |

| On-Current per device    | $1/\alpha$              | $\varepsilon/\alpha$     | $\varepsilon/\alpha_w$           |  |

| Doping                   | α                       | $\varepsilon \alpha$     | $arepsilon lpha_d$               |  |

| Area                     | $1/\alpha^2$            | $1/\alpha^2$             | $1/\alpha_w^2$                   |  |

| Capacitance              | $1/\alpha$              | $1/\alpha$               | $1/\alpha_w$                     |  |

| GateDelay                | $1/\alpha$              | $1/\alpha$               | $1/\alpha_d$                     |  |

| Powerdissipation         | $1/\alpha^2$            | $\varepsilon^2/\alpha^2$ | $\varepsilon^2/\alpha_w\alpha_d$ |  |

| PowerDensity             | 1                       | $arepsilon^2$            | $\varepsilon^2/\alpha_w\alpha_d$ |  |

Table 1.2: Technology Scaling Rules for Three Cases

in increasing order of their intractability.

#### a) High electric fields:

Due to a bias voltage being applied over very short distances, can cause avalanche breakdown by knocking large numbers of electrons out of the semi-conductor at high energies, thus causing current surges and progressive damage to devices. This may remain a problem in nanoelectronic devices made from bulk semiconductors.

#### b) Heat dissipation:

Heat dissipation of transistors (and other switching devices), due to their necessarily limited thermodynamic efficiency, limits their density in circuits, since overheating can cause them to malfunction. This is likely to be a problem for any type of densely packed nanodevices.

### c) Vanishing bulk properties and non-uniformity of doped semiconductors on small scales:

This can only be overcome either by not doping at all (accumulating electrons purely using gates, as has been demonstrated in a GaAs heterostructure) or by making the dopant atoms form a regular array. Molecular nano-electronics is one path to the latter option.

#### d) Shrinkage of depletion regions:

Shrinkage of depletion regions until they are too thin to prevent quantum mechanical tunneling of electrons from source to drain when the device supposedly is turned off. The function of nanoelectronic devices is not similarly impaired, because it depends on such tunneling of electrons through barriers.

# e) Shrinkage and unevenness of the thin oxide layer beneath the gate:

This prevents electrons from leaking out of the gate to the drain. This leakage through thin spots in the oxide also involves electron tunneling.

Long ago, MOSFETs were big and could be described via drift currents and carrier control via the gate capacitance. Now MOSFETs are small in order to increase their operation speed. Pushing the dimensions of the gate length down influences the electrostatics of the devices. In order to preserve the electrostatic integrity of the MOSFET scaling has proceeded in a controlled way:  $L_g \downarrow$  has to go together with  $t_{ox} \downarrow$ ,  $N_A \downarrow$ ,  $t_{si} \downarrow$ ,  $V_{dd} \downarrow$  and  $W \downarrow$ .

#### 1.4 Motivation

In a conventional, bulk-silicon micro-circuit, the active elements are located in a thin surface layer (less than  $0.5~\mu m$  of thickness) and are isolated from the silicon body with a depletion layer of a p-n junction. The leakage current of this p-n junction exponentially increases with temperature, and is responsible for several serious reliability problems. Excessive leakage currents and high power dissipation limit the operation of micro-circuits at high temperatures. Parasitic n-p-n and p-n-p transistors formed in neighboring insulating tubs can cause latch-up failures and significantly degrade circuit performance.

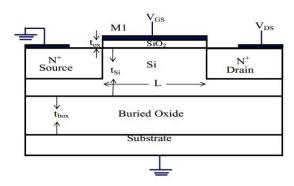

Silicon-on-insulator (SOI) technology employs a thin layer of silicon (tens of nanometers) isolated from a silicon substrate by a relatively thick (hundreds of nanometers) layer of silicon oxide. The SOI technology dielectrically isolates components and in conjunction with the lateral isolation, reduces various parasitic circuit capacitances, and thus, eliminates the possibility of latch-up failures. Figure 1.5 [7] shows the cross-section of the bulk and SOI

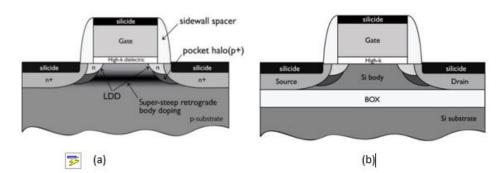

MOS devices. As shown in the Figure 1.5 [7], owing to the buried oxide isolation structure, SOI technology offers superior devices with excellent radiation hardness and high device density. SOI devices are more suitable with their steeper subthreshold slope(SS) which facilitates scaling of the threshold

Figure 1.5: Cross-sectional view of the bulk-Si (left) and SOI (right) CMOS devices

voltage for low-voltage low-power applications. Depending on the thickness of the silicon layer, MOSFETs will operate in fully depleted (FD) or partially depleted (PD) regimes. When the channel depletion region extends through the entire thickness of the silicon layer, the transistor operates in a FD mode. PD transistors are built on relatively thick silicon layers with the depletion depths of the fully powered MOS channel shallower than the thickness of the silicon layer. The PD-SOI devices have many advantages like the fabrication process of PD-SOI devices is totally compatible with bulk silicon technology while fabrication of FD-SOI devices require development of ultra thin body, and, therefore needs more sophisticated technology. Hence, the design of bulk Si devices can be easily transferred to PD-SOI technology. Also  $V_T$  in PD-SOI is relatively less sensitive to the uniformity in the Si-film thickness while in FD-SOI device,  $V_T$  depends on Si film thickness and it is difficult to control the thickness of the ultra thin film body. As a result the film thickness becomes non-uniform across the surface. In spite of so many benefits, PD-SOI devices exhibit certain undesirable effect known as "kink effect".

During the past few decades, excellent high-speed and performance have

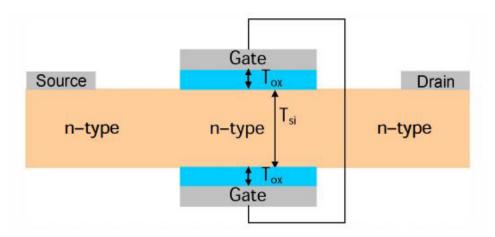

been achieved through improved design, use of high quality material and shrinking device dimensions. However, with the reduction of channel length, control of short-channel effects is one of the biggest challenges in further down-scaling of the technology. The predominating short-channel effects are a lack of pinch-off and a shift in threshold voltage with decreasing channel length as well as drain induced barrier lowering (DIBL) and hot-carrier effect at increasing drain voltage. Therefore, to reduce this short channel effects to a greater extent a new device structure called Junctionless (JL) Transistors have been demostrated. Junctionless devices with a uniform doping concentration and type throughout the channel and source/drain extensions overcomes the challenges faced by the conventional nano devices. The schematic diagram of DG-JL MOSFET is shown in the Figure 1.6 [8]. JL MOSFETs

Figure 1.6: Schematic diagram of Double Gate(DG) JL MOSFET.

have extremely low leakage current and simple fabrication process and are less susceptible to SCEs when compared with classical inversion-mode devices. However, the high doping concentration in the channel reduces carrier mobility which results in lower drive current and transconductance  $(G_m)$  of JL MOSFETs.

#### 1.5 Objectives

The salient objectives of the thesis are:

- i. To study the "kink effect" visible in the output drain current-voltage characteristics of the PD-SOI MOSFET. The SELBOX structure is being proposed to minimize this non-linear effect so that it can be used for practical linear applications. The effect of dual insulator(DI) on the kink effect is also presented.

- ii. To analyze the electrical behavior of the recently newly developed structure called Junctionless transistors which offers excellent advantages over the conventional nano devices. These JL MOSFETs reduces SCEs to a much grater extent than conventional devices. Therefore, the DC and AC characteristics of DG JL MOSFETs are simulated and compared with those of the conventional DG MOSFETs.

#### 1.6 Thesis Organisation

The dissertation is divided into five chapters and its outline is described as given below:

#### • chapter 1: Introduction

Fundamental concepts related to technology scaling, SOI devices and its advantages and disadvantages, objectives of the project and outline of the thesis.

### • chapter 2: Short Channel Effects in Nanoscale MOSFETs: A Review

This chapter analyzes the origin and effect of the short-channel effects in nanoscale MOSFETs. Various methods employed to overcome short-channel effects are also summarized and the feasibility of various MOSFET structures in suppressing short-channel effects is discussed.

# • chapter 3: Analysis & Minimization of Kink Effect in PD-SOI MOSFETs

This chapter demonstrates the development of SELBOX structure in PD-SOI SOI MOSFET and illustrates the role of SELBOX structure in suppressing short-channel effects. The use of dual insulator (DI) for the minimization of kink effect is also presented.

# • chapter 4: Analysis of DC & AC Performance of DG Junctionless(JL) MOSFETs

This chapter deals with the simulation of DC and AC characteristics of junctionless MOSFETs and compared to those of conventional DG MOSFETs. The various AC parameters of DG JL MOSFETs are extracted and a comparison is being made with conventional DG MOSFETs.

• chapter 5: Conclusion & Scope for Future Work

#### Chapter 2

# Short Channel Effects in Nanoscale MOSFETs: A Review

#### 2.1 Introduction

In order to realize higher-speed and higher-packing density MOS integrated circuits, the dimensions of MOSFETs have continued to shrink according to the scaling law proposed by Dennard et al. [9]. However, the power consumption of modern VLSIs has become rather significant as a result of extremely large integration. Reducing this power is strongly desired. Choosing a lower power supply voltage is an effective method. However, it leads to the degradation of MOSFET current driving capability. Consequently, scaling of MOS dimensions is important in order to improve the drivability, and to achieve higher-performance and higher-functional VLSIs.

We can say that the story of MOSFET scaling is the history of how to prevent short-channel effects (SCE) [10]. SCE causes the dependence of device characteristics, such as threshold voltage, upon channel length. This leads to the scatter of device characteristics because of the scatter of gate length produced during the fabrication process. Moreover, SCE degrades the controllability of the gate voltage to drain current, which leads to the degradation of the subthreshold slope and the increase in drain off-current. Thinning gate oxide and using shallow source/drain junctions are known to

be effective ways of preventing SCE.

The detrimental short-channel effects occur when the gate length is reduced to the same order as the channel depth. When the channel length shrinks, the absolute value of threshold voltage becomes smaller due to the reduced controllability of the gate over the channel depletion region by the increased charge sharing from source/drain. The predominating features of SCE are a lack of pinch off and a shift in threshold voltage with decreasing channel length as well as drain induced barrier lowering (DIBL) and hot-carrier effects at increasing drain voltage. Increased charge sharing from source/drain degrades the controllability of gate voltage over channel current. This degradation is described as charge sharing by the gate and drain electric fields in the channel depletion layer in Poon and Yaus model [11], which was reported as the first SCE model.

This description can be applied to conventional MOSFETs fabricated in a bulk silicon wafer. What about the thin-film SOI MOSFETs?. They are attractive devices for low-power high-speed VLSI applications because of their small parasitic capacitance [12]. Young [13] analyzed the SCE using a device simulator, and concluded that SCE is well suppressed in thin-film SOI MOSFETs when compared to bulk MOSFETs. In general, it is believed that thin-film SOI MOSFETs have a higher immunity to SCE compared to bulk MOSFETs. This may be due to the difference in source/drain junction depths between the two kinds of devices. For instance, the thickness of the silicon film, which corresponds to the source/drain junction depth of 50-100 nm, is common in 0.25-0.35  $\mu$ m SOI MOSFETs. It is extremely shallow compared with the junction depth of 100-200 nm in 0.25-0.35  $\mu$ m gate bulk MOSFETs. However, to take advantage of the ameliorated SCEs in deep-submicron fully-depleted SOI,  $t_{Si}$  must be considerably smaller than the source/drain junction depth ( $t_{Si} \sim 10\text{-}15 \text{ nm}$ ). Moreover, there exits a strong coupling through the buried oxide in thin-film devices consequently, very thin buried oxides  $(t_b \sim 100 \text{ nm})$  are needed which trade-offs with junction

capacitance considerations. Hence, for small-geometry SOI CMOS devices, short-channel effects are important [14, 15, 16, 17, 18].

#### 2.2 Issues for Nanoscale MOSFETs

The various issues for nanoscale MOSFETs are categorized based on where the problems occur :

#### 2.2.1 Channel

#### a) Sub-threshold leakage current:

The Sub-threshold leakage current is the weak inversion conduction current, which is dominated by the diffusion current flowing between the drain and source when  $|V_{GS}| < |V_{th}|$ . It is considered as one of non-ideal characteristics of MOSFET as a switching device and contributes major portions of the standby leakage power dissipation. This weak inversion conduction current can be expressed based on the Eq.(2.1) [19],

$$I_{subth} = \mu C_{dep} \left( \frac{W}{L} \right) V_T^2 \left( \exp \left( \frac{V_{GS} - V_{th}}{nV_T} \right) \right) \left( 1 - \exp \left( -\frac{V_{DS}}{V_T} \right) \right)$$

(2.1)

where  $C_{dep} = \sqrt{\varepsilon_{Si}qN_{sub}/4\varphi_B}$  denotes the capacitance of the depletion region under the gate area,  $V_T$  is the thermal voltage which equals to  $k_BT/q$ , and n is the sub-threshold parameter and expressed as  $1+C_{dep}/C_{ox}$ .

Since, from Eq.(2.1),  $I_{subth}$  increases exponentially with both increasing  $V_{GS}$  and decreasing  $V_{th}$ , the partial derivative of  $log_{10}I_{subth}$  with respect to  $V_{GS}$  yields a constant slope called sub-threshold slope (SS) and equals to

$$SS = \frac{\partial \left(\log_{10} I_{subth}\right)}{\partial V_{GS}} = \frac{1}{\ln 10 \cdot I_{subth}} \times \frac{\partial I_{subth}}{\partial V_{GS}}$$

(2.2)

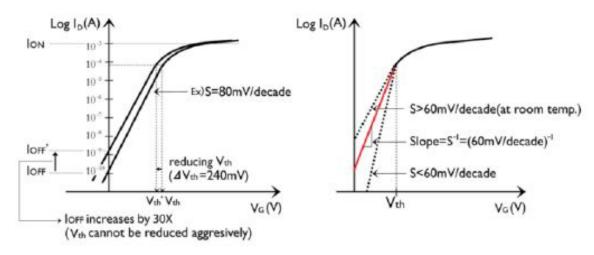

This parameter shows how abruptly the transistor turns off with decreasing gate voltage. In order to turn off the transistor effectively, SS must be designed to be as small as possible. Figure 2.1 [5] shows that SS is always greater than 2.3  $V_T$  ( $\sim$ 60 mV/dec) at room temperature and shows how well the channel surface potential can be controlled by the gate contact. SS can be made smaller (close to  $\sim$ 60 mV/dec) by using a thinner gate oxide thickness

(resulting in larger  $C_{ox}$ ) or a lower substrate doping concentration (resulting in the larger depletion width beneath the channel, hence reduced  $C_{dep}$ ).

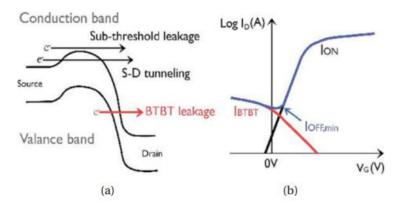

Figure 2.1: Characteristics of sub-threshold conduction.

In addition, under lower temperature operation, SS can be reduced since SS is a function of T. For MOS a transistor built in SOI technology, the sub-threshold swing is usually better than in bulk technology. In fact the sub-threshold swing of SOI devices can even reach the optimum value (2.3  $V_T$ ) depending on whether their bulk is fully depleted or partially depleted. This makes SOI a promising candidate for ultra low power CMOS applications [19].

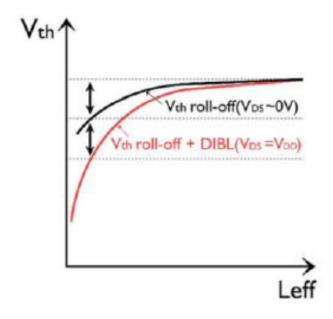

# b) Threshold Voltage Variations and Drain-Induced Barrier Lowering:

Since the threshold voltage  $(V_{th})$  is directly related to the device speed and sub-threshold leakage current, it has to be minimized. It is generally explained in terms of a)  $V_{th}$  roll-off(or falloff) and b) Drain induced barrier lowering (DIBL).

The transistors with a different channel length (L) in the same wafer, even in the same die, yield different  $V_{th}$ . The threshold voltage reduction due to the reduced channel length represents  $V_{th}$  roll-off. Further  $V_{th}$  reduction

caused by increasing drain voltage describes DIBL as shown in Figure 2.2 [5]. Both phenomena stem from the lowered potential barrier between the drain and source due to the relatively increased charge-sharing effect between the channel depletion region and source/drain depletion regions comparing to long-channel device case. This charge-sharing effect makes a transistor require less gate voltage to deplete the substrate beneath the gate dielectric and makes  $V_{th}$  decrease [20].

Figure 2.2: Threshold voltage roll-off and drain induced barrier lowering (DIBL).

The expressions for the drain and source junction widths are:

$$X_{dD} = \sqrt{\left(\frac{2\varepsilon_{Si}}{qN_A}\right)(V_{DS} + \varphi_{Si} + V_{SB})}, \quad X_{dS} = \sqrt{\left(\frac{2\varepsilon_{Si}}{qN_A}\right)(\varphi_{Si} + V_{Si})}$$

(2.3)

where  $V_{SB}$  and  $V_{DB}$  are source-to-body and drain-to-body voltages. When the depletion regions surrounding the drain extends to the source, so that the two depletion layer merge (i.e., when  $x_{dS} + x_{dD} = L$ ), punchthrough occurs. Punchthrough can be minimized with thinner oxides, larger substrate doping, shallower junctions, and obviously with longer channels.

The current flow in the channel depends on creating and sustaining an inversion layer on the surface. If the gate bias voltage is not sufficient to

Figure 2.3: Electron Potential Energy Variations along the position in channel

invert the surface  $(V_{GS} < V_{TO})$ , the carriers (electrons) in the channel face a potential barrier that blocks the flow. Increasing the gate voltage reduces this potential barrier and, eventually, allows the flow of carriers under the influence of the channel electric field. In the weak inversion regime there is a potential barrier between the source and the channel region. The height of this barrier is a result of the balance between drift and diffusion current between these two regions. The barrier height for channel carriers should ideally be controlled by the gate voltage to maximize transconductance. However, in small-geometry MOSFETs, the potential barrier is controlled by both the gate-to-source voltage  $V_{GS}$  and the drain-to-source voltage  $V_{DS}$ . As indicated in Figure 2.3, drain-induced barrier lowering (DIBL) effect [20] occurs when the barrier height for channel carriers at the edge of the source reduces due to the influence of drain electric field, upon application of a high drain voltage. The reduction of the potential barrier eventually allows electron flow between the source and the drain, even if the gate-to-source voltage is lower than the threshold voltage. This increases the number of carriers injected into the channel from the source leading to an increased drain off-current. The channel current that flows under this conditions  $(V_{GS} < V_{TO})$  is called the sub-threshold current. Thus the drain current is controlled not only by the gate voltage, but also by the drain voltage.

Figure 2.4: Surface potential variation along the position in channel for 0.1 V and 1.5 V drain voltages (linear and saturated case).

For device modeling purposes this parasitic effect can be accounted for by a threshold voltage reduction depending on the drain voltage [21]. In addition to the surface DIBL, there are two unique features determining SCEs in thin-film SOI devices viz.(a) positive bias effect to the body due to the accumulation of holes generated by impact ionization near the drain and (b) the DIBL effect on the barrier height for holes at the edge of the source near the bottom, as illustrated in Figure 2.4 [10].

Holes generated near the drain due to impact ionization accumulate in the body region, and then positively bias the body, reducing  $V_T$  as shown in the Figure 2.5. This positive bias effect leads to  $V_T$  lowering for all gate lengths, including rather long gates such as 2  $\mu$ m. The hole generation rate due to impact ionization increases as gate length decreases under a fixed value of  $V_D$ . This effect is predominant in PD SOI nMOSFETs and results in so-called floating body effects(FBE) [22, 23].

The DIBL effect on the barrier height for holes reduces the positive bias

Figure 2.5: Three mechanisms determining SCE in SOI MOSFETs

effect to the body because the accumulated holes in the body can more easily surmount the barrier and flow to the source. As a result fewer number of accumulated holes remain which weakens the  $V_T$  lowering. The potential near the bottom in the thin-film increases as gate length decreases due to the drain electric field. This leads to the lowering of the barrier height for holes at the source edge near the bottom with shorter gate lengths. Figure 2.6 [10] compares the schematic energy band diagrams at threshold condition between short and long channels MOSFETs. The comparison is done near the bottom of the thin-film from the source to the drain. With shorter gate lengths, the barrier height for holes near the bottom is lowered by the influence of the drain electric field, and holes accumulated in the body region can more easily flow into the source.

Due to these three mechanisms,  $V_T$  dependence upon gate length in FD nMOSFETs becomes small, as illustrated in Figure 2.7 [10].

Figure 2.6: Comparison of schematic energy band diagrams near the bottom of the body between the long and short-channel fully depleted (FD) nMOSFETs

Figure 2.7: Effects of the three mechanisms on threshold voltage dependence on gate length

# c) Carrier mobility degradation:

Since the rate of the supply voltage scaling has been reduced while the geometric scaling keeps the same historical rate, the electric fields inside the MOSFETs keep on increasing. The drift velocity of the carriers is proportional to the longitudinal electric field across the channel at low field ( $<10^3$  V/cm). After that point, however, the increasing rate of the carriers velocity decreases with the increasing longitudinal field in Si at room temperature. Finally, the carriers reach their maximum velocity of  $v_{sat} \sim 10^7$  cm/sec when the electric field exceeds  $\sim 3 \times 10^4$ V/cm for electrons and  $\sim 10^5$ V/cm for

holes (here the channel length (L) is assumed to be much greater than the average distance (l) between scattering events such as L $\gg$ 10 nm.) This carrier mobility degradation is called "Velocity Saturation," and originates from various scattering mechanisms such as optical phonon scattering, phonon dispersion, phonon absorption as well as emission, and the energy band non-parabolicity [24, 25].

Another high electric field is developed between the gate and the channel due to the aggressive gate oxide thickness scaling with relatively constant supply voltage, which limits the charge carriers to a narrower region below the oxide-silicon interface, leading to more carrier scattering and hence lower mobility. Furthermore, the increased body doping by means of suppressing SCEs degrades the carrier mobility [25].

# d) Hot carrier effects (HCEs):

The high electric fields in a device also cause reliability problems such as threshold voltage shifts and trans-conductance degradation due to "Hot Carrier Effects (HCEs)." As the average velocity of carriers in the channel saturates by the increased scattering rate at the high electric fields, the carriers can attain high kinetic energy. Once those hot carriers obtain sufficient energy to overcome barriers, they might migrate into the unwanted area such as the gate dielectric, gate, or substrate of a transistor. Particularly, the highly accelerated hot carriers near the drain region can generate new electron-hole pairs by collision with the silicon atoms, which is called "impact ionization." Impact ionization can cause significant increase in substrate current or carrier injection into the gate dielectric, which causes charges to get trapped in the gate oxide. This causes threshold voltage shifts and therefore the device becomes unstable and even can fail [25, 26].

# e) Direct source to drain tunneling:

The ultimate physical scaling limit of MOSFETs is direct source-to-drain

tunneling. If the barrier width (transistor channel length) between source and drain becomes small enough for electrons to tunnel through the barrier without any additional gate bias, MOSFETs no longer can be used as a switch. When we consider only over-barrier transition of electrons but the direct tunneling, from the well-known Shannon-von Neumann-Landauer (SNL) expression, the minimum energy barrier to separate two different states of electrons is  $E_{SNL} = k_B T(\ln 2) = 0.017$  eV at room temperature (T = 300 K), where  $k_B$  is the Boltzmann constant and T is the temperature. Therefore, the smallest energy required to process a bit is  $E_{bit} > E_{SNL} = k_B T(\ln 2) = 0.017$  eV. Also, according to quantum mechanics the minimum channel length (barrier width) able to resist  $E_{bit}$ , not to allow tunneling, is about 5 nm. In order to achieve a smaller channel length, it is necessary to increase the  $E_{bit}$ . However this, in turn, tradeoffs with the growth of total power dissipation in a chip. Therefore, enhanced cooling techniques become the critical issues to achieve this goal.

#### 2.2.2 Gate

# a) Direct tunneling gate leakage current:

With the continuous device scaling, the gate oxide thickness has been accordingly reduced to maintain the gate controllability over the channel. However, as the gate oxide thickness scales below 2 nm, the direct tunneling (DT) gate leakage increases exponentially due to quantum mechanical tunneling. The DT gate leakage current can not only increase standby power dissipation but also limit the proper device operation. These serious problems can be solved by replacing  $SiO_2$  with higher permittivity (high-k) gate dielectrics, which allows a physically thicker dielectric layer to have an EOT [27].

# b) Gate depletion:

Polycrystalline silicon (poly-Si) has been widely used as the gate electrode material of MOSFETs since it replaced aluminum on account of its superior thermal stability to higher processing temperature. In addition, the use of poly-Si as gate electrode has reduced the overall number of processing steps by means of self-aligned processing, where the gate itself is used as a hard mask during ion implantation for the source and drain junction formation. This technique allows tighter overlap between gate and source/drain regions and results in lower parasitic capacitance.

However, even heavily doped poly-Si gate electrode has a certain resistance which contributes to a considerable RC time delay. Furthermore, when the doping concentration of the polySi is not sufficient, at high gate bias during inversion, a region in the poly-Si gate electrode adjacent to the poly-Si/ $SiO_2$  interface becomes depleted with carriers, which is called "Poly-depletion Effect." This results in increased EOT and hence significant decrease in the drive capability of transistor. For these reasons poly-Si is not suitable for the future gate electrode and new materials are required. Fortunately, metal gate electrode with a suitable work function (WF) shows many advantages such as lower gate sheet resistance and no boron penetration and poly depletion effect. However, the selection of metal gate substitutes for poly-Si, which are compatible with the new high-k gate dielectrics, is not as advanced [28].

#### 2.2.3 Drain/source

# a) Parasitic resistance (suppress on-current):

As the device gets smaller, the influence of parasitic resistance on oncurrent increases significantly. Therefore, proper control of parasitic resistance in a MOSFET becomes more important to achieve further performance improvement. The total parasitic resistance, which accounts for the voltage drop between channel and S/D contacts, can be divided into the four components such as overlap resistance, extension resistance, deep resistance, and silicide-diffusion contact resistance. Shallower S/D junction depths are desired to suppress SCEs effectively; however, since the shallower junction also increases the sheet resistance, the S/D doping must be increased accordingly to keep the sheet resistance constant. In addition, the ultra-shallow junctions are difficult to form and also cause significant increase in BTBT leakage current [29].

## b) Parasitic capacitance:

In digital switching applications, lower capacitance, along with higher drive current, is the main factor for high performance CMOS circuit design, because the conventional CMOS inverter delay model is given by  $C_GV_{DD}/I_D$ , where  $C_G$  is gate capacitance,  $V_{DD}$  is supply voltage, and  $I_D$  is drain oncurrent. Thus, with geometry scaling, the performance improvement has been achieved because the gate capacitance consisting of both intrinsic gate capacitance ( $C_{int}=C_{GC}+2C_{OV}$ ) and parasitic capacitance ( $C_{para}\sim C_{fringe}+C_{gco}$ ) decreases in proportion to the gate length reduction in micro MOSFET, where  $C_{GC}$  is gate-to channel capacitance,  $C_{OV}$  is drain/source-to-gate electrode overlap capacitance,  $C_{fringe}$  is inner/outer fringing capacitance, and  $C_{gco}$  is gate-to-contact capacitance. However, as MOSFET enters into nano regime, gate capacitance does not decrease in proportion to the gate length reduction due to relatively increased parasitic capacitance. Therefore, in order to sustain performance improvement from scaling, parasitic capacitance reduction technique is required [30].

### 2.2.4 Substrate (bulk)

# a) Reverse-biased junction leakage current(reverse-biased BTBT current):

Reverse-biased junction leakage current  $(I_{REV})$  is the current flowing between the source/drain(S/D) and the substrate through the parasitic reverse-biased pn-junction diode in the off-state MOSFET.  $I_{REV}$  mainly consists of the diffusion and drift of minority carriers near the depletion region edge and the generation of electron-hole pairs in the depletion region of the reverse-biased pn-junction. If both S/D and substrate regions are heavily doped, BTBT dominates the  $I_{REV}$  since the electric field across the junction depletion region increases. If the high electric field (>10<sup>6</sup>V/cm), so that the volt-

age drop across the junction is bigger than the band gap of silicon, is formed across the reverse-biased junctions of the source/drain (S/D) regions, especially with increasing S/D voltage or reverse body bias, significant amount of BTBT current flows through the S/D to substrate junctions. In nanometer devices, higher channel and S/D doping with shallow junction depths are required to minimize SCEs, there is significant increase in BTBT current.

Recently high-mobility channel materials, such as Ge, strained-Ge(s-Ge), s-SiGe, and III-V materials (GaAs, InAs, InSb, and InGaAs), are actively being researched as candidates for future channel materials of highly scaled MOSFETs. However, since most of high-mobility materials have lower band gaps than Si, BTBT leakage currents increase significantly. Therefore, various device structures to minimize BTBT currents are being developed. The various leakage mechanisms in a MOSFET are illustrated in Figure 2.8.

Figure 2.8: (a) Various leakage mechanisms in a MOSFET (left), (b)  $I_{OFF}$ ,min is the minimum achievable leakage current in a MOSFET. In low  $E_G$  materials it is generally limited by  $I_{BTBT}$ .

# b) GIDL current (Surface BTBT current):

GIDL current, also called surface BTBT current, has become one of the major off-state leakage current components in state-of-the-art MOSFETs. When the drain of n-MOSFET is biased at the supply voltage  $(V_{DD})$  and the gate is biased at either zero or negative voltage, a depletion region is formed

under the gate and drain overlap region. In the same way as the BTBT current, if the high electric field is formed in the narrower depletion region as a result of the reverse-bias between channel and drain, a significant amount of surface BTBT current flows through drain to substrate junctions due to twisting of bandgaps.

## 2.3 Solutions to Short Channel Effects

As the gate length of the MOSFET is scaled into the sub-100-nm regime for improved performance and density, the requirements for body-doping concentration, gate oxide thickness, and source/drain (S/D) doping profiles to control short-channel effects become increasingly difficult to meet when conventional device structures based on bulk silicon substrates are employed. The heavy channel doping required to provide adequate suppression of SCE results in degraded mobility and enhanced junction leakage. The aggressive reduction of the gate dielectric thickness for reduced SCE and improved drive current leads to increased direct tunneling gate leakage current and standby power consumption, and also raises concerns regarding the gate oxide reliability.

Figure 2.9 [1]schematically shows the electric field lines from the drain encroaching on the channel region.

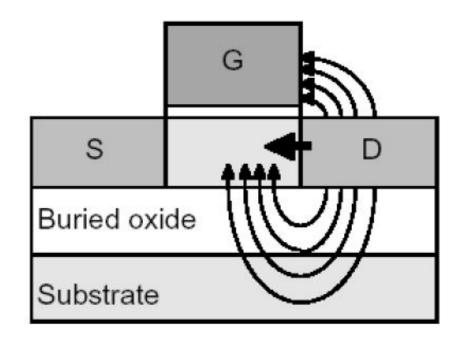

As shown in the Figure 2.9, the gate electrode shields the channel region from those lines at the top of the device, but electric field lines penetrate the device laterally and from underneath, through the buried oxide and the silicon wafer substrate causing the undesirable DIBL for the charge carriers. To overcome all the short channel effects several innovative techniques have been introduced. These are:

#### 2.3.1 High-k Dielectric Material Gate

One of the key innovation enablers for 45 nm process technology and beyond is the high-k/metal gate transistor, which is regarded as one of the biggest

Figure 2.9: Electric field lines from the drain [1]

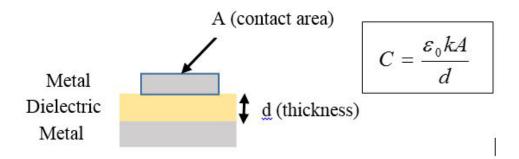

developments in transistor design in 40 years. High-k/metal gate have enabled the continuous EOT scaling. The dielectric constant, k, is a parameter defining ability of material to store charge. Consequently, it also defines capacitance, C of any capacitor comprising of a layer of dielectric sandwiched between two metal plates. In the figure below size of the upper plate defines area of the capacitor contact (A).

Figure 2.10: High-k Metal Gate Structure

All other parameters equal, k would determine capacitance of the above structure, or in other words, it would define the extent of capacitive cou-

pling between two conducting plates - with high-k dielectric such coupling would be strong, and with low-k dielectric being obviously weak. In Si technology the reference is a value of k of silicon dioxide,  $SiO_2$ , which is 3.9. Dielectrics featuring k>3.9 are referred to as high-k dielectric while dielectric featuring k<3.9 are defined as low-k dielectrics. In cutting edge silicon nanoelectronics, both high-k and low-k dielectrics are needed to implement fully functional very high-density integrated circuit, although, for drastically different reasons. High-k dielectrics are needed in MOS gate stacks to maintain sufficiently high capacitance of the metal (gate) - dielectric-Si structure in MOS/CMOS transistors. Due to the continued scaling of the channel length (L), and hence reduced gate area A, the need to maintain sufficient capacitance of the MOS gate stack was met by gradual decrease of the thickness of  $SiO_2$  gate oxide. Recently, high-k dielectric based on Hafnium and dual metal gate has been introduced to increase transistor performance while also reducing gate leakage as gate dielectric thickness actually increased while also the gate capacitance increased.

However, such scaling cannot continue indefinitely as at certain point gate oxide will become so thin (thinner than about 1 nm) that, due to excessive tunnelling current, it would stop playing role of an insulator. Hence, dielectric featuring k higher than 3.9, i.e. one assuring same capacitive coupling but at the larger physical thickness of the film, must be used instead of  $SiO_2$  as a gate dielectric in advanced MOS/CMOS integrated circuits. On the opposite end of the spectrum finds itself a multi-layer metallization scheme in which inter-layer-dielectric (ILD) is used to electrically insulate metal lines. In this case it is of critical importance that the capacitive coupling between adjacent interconnects lines is as limited as possible. Hence, a low-k dielectric must be used to assure as little capacitive coupling between interconnect lines as possible. Whether the problem is with high-k dielectrics for MOS gates or low-k dielectrics for ILDs, lack of viable technical solutions in either of these areas will bring any future progress in mainstream silicon technology [31].

#### 2.3.2 Silicon-on-Insulator (SOI)

With physical separation between individual devices in ultra-high density CMOS integrated circuits measured in nanometers, proper electrical isolation between them is a key challenge. The SOI (Silicon-On-Insulator) substrate wafers, as opposed to conventional bulk wafers, not only solve the problem of electrical isolation between adjacent devices but also allow innovative device layouts resulting insignificantly better than in the case of bulk substrates performance of CMOS circuitry. Hence, SOI substrates rapidly become an important element of the advanced silicon IC technology. The advantages of SOI technology come from its buried oxide (BOX) layer as shown in Figure 2.11. With the reduction of the parasitic capacitances, mostly as a result of the reduced drain/source junction capacitances, SOI devices yield improved switching speed and reduced power consumption. The operating speed is also improved since the isolated channel from substrate bias prevents the increase in a threshold voltage of stacked SOI transistors. In addition, the perfect lateral and vertical isolation from substrate provides latchup and inter-device leakage free CMOS technology, reduction in various interferences, and better soft error immunity. Moreover, SOI technology offers tighter transistor packing density and simplified processing [2].

Figure 2.11: a) Cross-section of an advanced MOSFET. b) Cross-section of a SOI MOSFET [2].

SOI transistors are classified into two types; "partially depleted(PD) SOI,"

if the silicon film (typically 100 nm or more) on the BOX layer is thicker than the depletion region depth beneath the gate oxide, and "fully depleted (FD) SOI," if the body (silicon film) thickness is thin enough (typically 50 nm or less) or the doping concentration of the body is low enough to be fully depleted. FDSOI transistors have superior advantages over PD SOI transistors in terms of extremely low sub-threshold swing (<65 mV/decade), no floating-body effects, and low threshold voltage variation with temperature (2-3 times less). However, since FD SOI transistors are even more sensitive to process variation such as the silicon film layer variation resulting in threshold voltage fluctuation, PD SOI devices were commercially introduced first.

Another important merit of SOI technology is that it provides the cornerstone for new device structures such as multi gate field-effect transistors (MuGFETs), which includes more than one gate into a single device. The double-gate (DG) FET shown in Figure 2.12(b) is the first step for those multi gate devices. Since the transverse electric field induced by  $V_{DS}$  is shared by both top and bottom channels, it mitigates SCEs.