# Design and Implementation of Shunt Active Power Line Conditioner using Novel Control Strategies

Karuppanan. P

Department of Electronics and Communication Engineering National Institute of Technology, Rourkela-769 008 August 2012

# Design and Implementation of Shunt Active Power Line Conditioner using Novel Control Strategies

A Thesis submitted in partial fulfillment of the requirements for the degree of

## Doctor of Philosophy In Electronics and Communication Engineering

<u>≊</u>⊮ Karuppanan. P

Roll No.: 508EC103

<u>Under the Guidance of</u> Prof. Kamala Kanta Mahapatra

Department of Electronics and Communication Engineering National Institute of Technology Rourkela-769 008 (ODISHA) August 2012

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGG,. NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA- 769

008 ODISHA, INDIA

## CERTIFICATE

This is to certify that the thesis entitled "Design and Implementation of Shunt Active Power Line Conditioner using Novel Control Strategies", submitted to the National Institute of Technology, Rourkela by **Mr.P. Karuppanan, Roll No. 508EC103** for the award of the degree of **Doctor of Philosophy** in Department of Electronics and Communication Engineering, is a bonafide record of research work carried out by him under my supervision and guidance.

The candidate has fulfilled all the prescribed requirements.

The Thesis is based on candidate's own work, has not submitted elsewhere for the award of degree/diploma.

In my opinion, the thesis is in standard fulfilling all the requirements for the award of the degree of **Doctor of Philosophy** in Electronics and Communication Engineering.

Prof. Kamala Kanta Mahapatra Supervisor Department of Electronics and Communication Engineering National Institute of Technology-Rourkela, Odisha– 769 008 (INDIA)

# Dedicated to

# my Nation

## ACKNOWLEDGEMENTS

I would like to express my deepest gratitude towards my supervisor, Professor Kamala Kanta Mahapatra for his generous support and supervision, and for the valuable knowledge that he shared with me. I learned valuable lessons from his personality and his visions.

I like to express my gratitude to our honorable Director, Professor Sunil Kumar Sarangi for his motivation and inspiration. I learned valuable morals from his personality, visions and dynamic activities.

I am also grateful to my Doctoral Scrutiny Committee Members, Professor Sukadev Meher, Professor Banshidhar Majhi, Professor K.Barada Mohanty and Professor A.K.Panda.

I am thankful to Professor Sarat Kumar Patra, Professor B.Chitti Babu, Professor Ayas Kanta Swain, Professor R. Jeyabalan, M.Madhan (Library), Professor Asheesh Kumar Singh (MNNIT-Allahabad), Professor Kanhu Charan Bhuyan and Mr. Jaganath Mohanty, who has given the support in carrying out the work.

During the course of this work, part of my work was supported by a project VLSI-SMDP sponsored by DIT, Govt. of India. I am really thankful to them.

With great thanks, I would like to acknowledge Mr. K. Jeyaraman, Manager-Research and Product development; M/s Industrial Controls and Drives (ICD) Pvt. Ltd. Chennai, India- 600 095 for the hardware components and experimental setup to success of this project.

Special thanks to my lovable friends and everybody who has helped me to complete the thesis work successfully.

Finally, and most importantly, I would like to express my deep appreciation to my beloved family members Pitchai-Vijaya, Kanakaraj-Pitchaiammal, P.Selvaraj, Kalaiarasi-Shanmugam, Vasumathi-Karuppanan, Jothi-Krishnan and G.Ramakrishnan, for all their encouragement, understanding, support, patience, and true love throughout my ups and downs.

As always, I thank and praise God for being on my side.

Karuppanan. P

### ABSTRACT

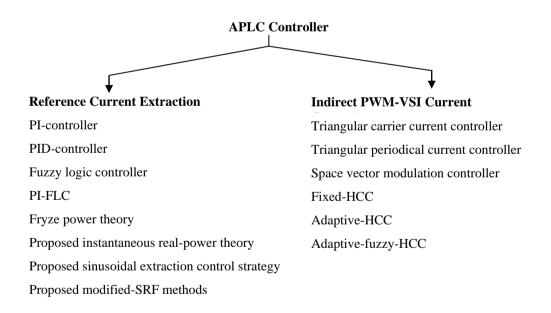

Shunt Active Power Filter (APF) or Active Power Line Conditioner (APLC) is designed and implemented for power quality improvements in terms of current harmonics and reactive-power compensation. The widespread use of non-linear loads in industrial, commercial and domestic facilities cause harmonic problems. Harmonics induce malfunctions in sensitive equipment, overvoltage by resonance, increase heat in the conductors, harmonic voltage drop across the network impedance and affects other customer loads connected at the Point of Common Coupling (PCC). Active power line conditioner is implemented for compensating the harmonics and reactive-power simultaneously in the distribution system. The performance of the active power line conditioner depends on the design and characteristics of the controller adopted for APLC. The objective of this research is to find a suitable control strategy for reference current extraction as well as PWM-VSI current controller. PI / PID / FLC / PI-FLC, Fryze power theory, proposed instantaneous realpower theory, proposed sinusoidal extraction controller and modified-synchronous reference frame theory methods are utilized for extracting reference current. Furthermore, indirect PWM-current control (triangular-carrier / triangular-periodical current controller, space vector modulation controller, fixed-Hysteresis Current Controller (HCC), adaptive-HCC and adaptive-fuzzy-HCC) approach is applied to generate switching pulses of the PWM-inverter. Each reference current extraction method in conjunction with various PWM-current control techniques (or vice-versa) are simulated and investigated for the active power line conditioner. For experimental validation, the modified-synchronous reference frame with adaptive-fuzzy-HCC technique is adopted. This control algorithm is demonstrated through the TMS320F240 Digital Signal Processor for shunt APLC system.

## TABLE OF CONTENTS

| Title             | Page     | No   |

|-------------------|----------|------|

| ACKNOWLEDGEMENTS  |          | i    |

| ABSTRACT          |          | ii   |

| TABLE OF CONTENTS |          | iii  |

| LIST OF TABLES    |          | viii |

| LIST OF FIGURES   |          | ix   |

| ABBREVIATION      |          | xiv  |

| LIST OF SYMBOLS   | · · · •• | xvi  |

### **CHAPTER 1 INTRODUCTION**

| 1.1 | Introduction                               | 1  |

|-----|--------------------------------------------|----|

| 1.2 | Research motivation                        | 2  |

| 1.3 | Harmonics in the power system              | 2  |

|     | 1.3.1 Harmonic sources                     | 4  |

|     | 1.3.2 Harmonic problems                    | 4  |

|     | 1.3.3 End effects of harmonics             | 5  |

|     | 1.3.4 Mitigation of harmonics              | 5  |

| 1.4 | Shunt active power line conditioner        | 6  |

|     | 1.4.1 Approach used in the thesis          | 6  |

| 1.5 | Literature reviews                         | 8  |

|     | 1.5.1. Reference current extraction method | 9  |

|     | 1.5.2. PWM-current control technique       | 11 |

| 1.6 | Objective of the thesis                    | 13 |

| 1.7 | Scopes and contributions                   | 14 |

| 1.8 | Organization of the thesis                 | 15 |

## **CHAPTER 2 STUDY OF SHUNT APLC SYSTEM**

| 2.1 | Introduction                  | 17 |

|-----|-------------------------------|----|

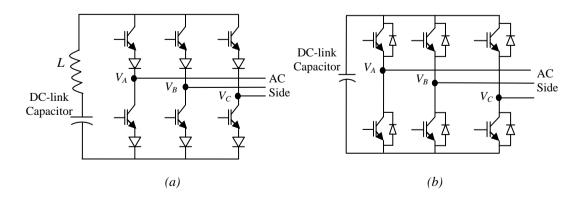

| 2.2 | APLC Topologies               | 17 |

|     | 2.2.1 Current source inverter | 18 |

|     | 2.2.2 Voltage source inverter                  | 19 |

|-----|------------------------------------------------|----|

| 2.3 | Shunt APLC configurations                      | 19 |

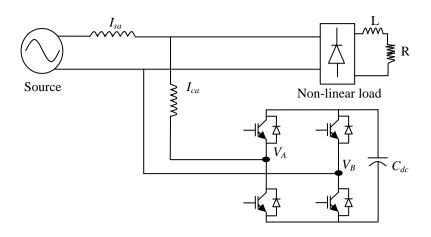

|     | 2.3.1 Single-phase system                      | 19 |

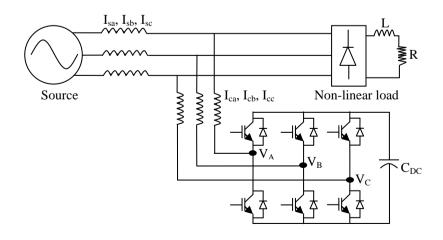

|     | 2.3.2 Three-phase three-wire system            | 20 |

|     | 2.3.3 Three-phase four-wire system             | 21 |

| 2.4 | Principle of the shunt APLC system             | 21 |

|     | 2.4.1 Characteristics of harmonics             | 22 |

|     | 2.4.2 Characteristics of harmonic compensation | 24 |

| 2.5 | Design of the shunt APLC system                | 25 |

| 2.6 | Conlusions                                     | 33 |

## **CHAPTER 3 REFERENCE CURRENT EXTRACTION METHODS**

| 3.1  | Introduction                              | 34 |

|------|-------------------------------------------|----|

| 3.2  | PI Controller                             | 34 |

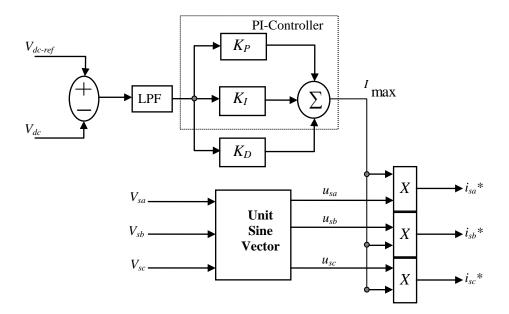

|      | 3.2.1 Unit sine vector                    | 35 |

|      | 3.2.2 Reference current generation        | 36 |

| 3.3  | PID controller                            | 37 |

| 3.4  | Fuzzy logic controller                    | 38 |

| 3.5  | PI with fuzzy logic controller            | 42 |

| 3.6  | Fryze power theory                        | 43 |

| 3.7  | Proposed instantaneous real-power theory  | 45 |

| 3.8  | Proposed sinusoidal extraction controller | 49 |

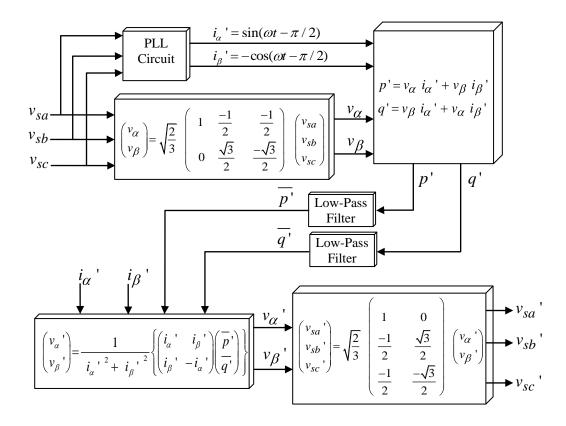

|      | 3.8.1 Positive sequence voltage detector  | 50 |

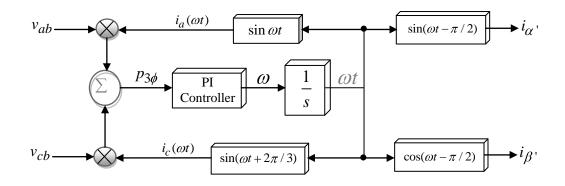

|      | 3.8.1.1 Phase locked loop circuit         | 51 |

|      | 3.8.2 Instantaeous real-power theory      | 52 |

| 3.9  | Synchronous reference frame theory        | 53 |

|      | 3.9.1 Conventional SRF                    | 53 |

|      | 3.9.2 Proposed modified SRF               | 55 |

|      | 3.9.2.1. Unit vector generation           | 55 |

|      | 3.9.2.2. dc-voltage regulator             | 57 |

|      | 3.9.2.3. Reference current extraction     | 57 |

| 3.10 | Conclusions                               | 59 |

## CHAPTER 4 PWM-VSI CURRENT CONTROL TECHNIQUES

| 4.1  | Introduction                                    | 61 |

|------|-------------------------------------------------|----|

| 4.2  | Current control techniques                      | 62 |

|      | 4.2.1 Direct current control technique          | 62 |

|      | 4.2.2 Indirect current control technique        | 63 |

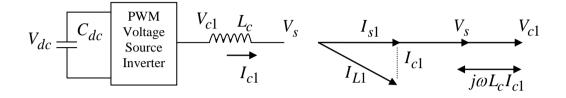

| 4.3  | Modeling of PWM-VSI                             | 64 |

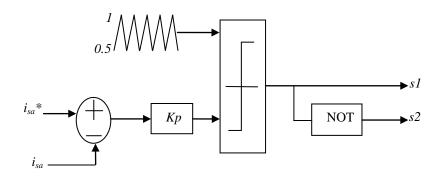

| 4.4  | Triangular-carrier current controller           | 65 |

| 4.5  | Triangular-periodical current controller        | 66 |

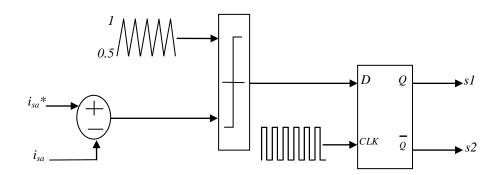

| 4.6  | Space vector modulation controller              | 67 |

| 4.7  | Fixed-hysteresis current controller             | 71 |

|      | 4.7.1 Two-level hysteresis current controller   | 71 |

|      | 4.7.2 Three-level hysteresis current controller | 72 |

| 4.8  | Adaptive-hysteresis current controller          | 75 |

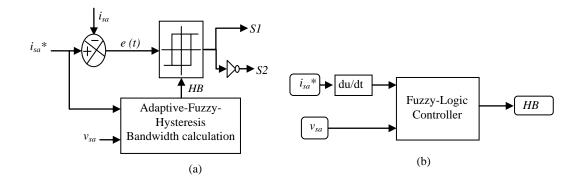

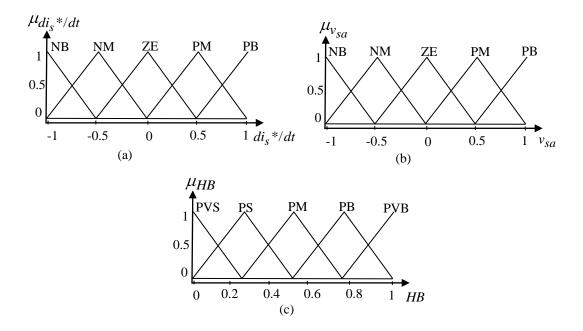

| 4.8  | Adaptive-fuzzy-hysteresis current controller    | 78 |

| 4.10 | Conclusions                                     | 80 |

## **CHAPTER 5 SIMULATION RESULTS AND ANALYSIS**

| Introduction                             | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PI / PID / FLC and PI-FLC                | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.1 Case 1 PI controller               | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.2 Case 2 PID controllers             | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.3 Case 3 Fuzzy logic controller      | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.4 Case 4 PI with FLC                 | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2.5 Case 5 APLC system analysis        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fryze power theory                       | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.1 Case 1 Fixed HCC and adaptive HCC  | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.2 Case 2 Adaptive-fuzzy-HCC          | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3.2 Case 3 APLC system analysis        | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Proposed instantaneous real-power theory | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4.1 Case 1 TCCC, TPCC and SVM          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4.2 Case 2 Fixed-HCC and adaptive-HCC  | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4.3 Case 3 Adaptive-fuzzy-HCC          | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4.4 Case 4 APLC system analysis        | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          | <ul> <li>PI / PID / FLC and PI-FLC.</li> <li>5.2.1 Case 1 PI controller.</li> <li>5.2.2 Case 2 PID controllers.</li> <li>5.2.3 Case 3 Fuzzy logic controller.</li> <li>5.2.4 Case 4 PI with FLC.</li> <li>5.2.5 Case 5 APLC system analysis.</li> <li>Fryze power theory.</li> <li>5.3.1 Case 1 Fixed HCC and adaptive HCC.</li> <li>5.3.2 Case 2 Adaptive-fuzzy-HCC.</li> <li>5.3.2 Case 3 APLC system analysis.</li> <li>Proposed instantaneous real-power theory.</li> <li>5.4.1 Case 1 TCCC, TPCC and SVM.</li> <li>5.4.2 Case 2 Fixed-HCC and adaptive-HCC.</li> <li>5.4.3 Case 3 Adaptive-fuzzy-HCC.</li> </ul> |

| 5.5 | Proposed sinusoidal extraction control strategy | . 104 |

|-----|-------------------------------------------------|-------|

|     | 5.5.1 APLC system analysis                      | 107   |

| 5.6 | Synchronous reference frame theory              | . 108 |

|     | 5.6.1 Case 1 conventional SRF                   | 109   |

|     | 5.6.2 Case 2 proposed modified SRF              | 109   |

|     | 5.6.3 Case 3 APLC system analysis               | 111   |

| 5.7 | Conclusions                                     | 113   |

## CHAPTER 6 EXPERIMENTAL RESULTS AND ANALYSIS

| 6.2 | Introduction                         | 115 |

|-----|--------------------------------------|-----|

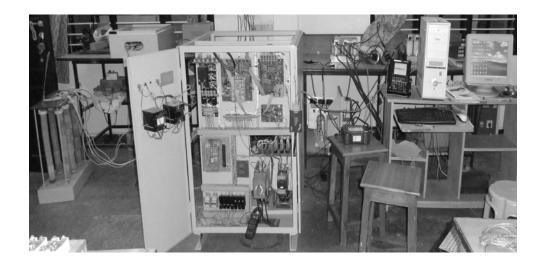

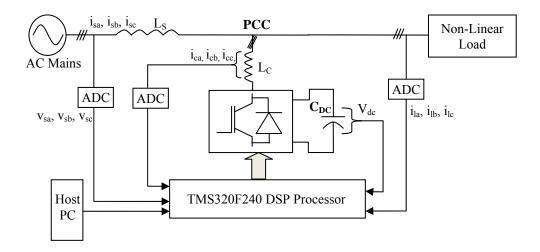

| 6.2 | Experimental setup                   | 116 |

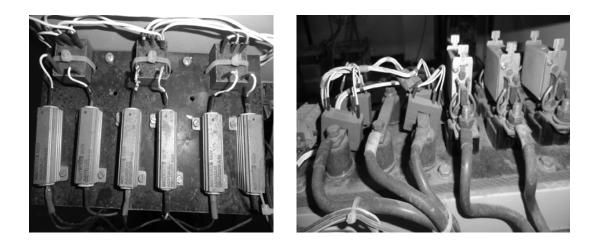

|     | 6.2.1 Thyristor-rectifier load       | 116 |

|     | 6.2.2 Voltage source inverter        | 117 |

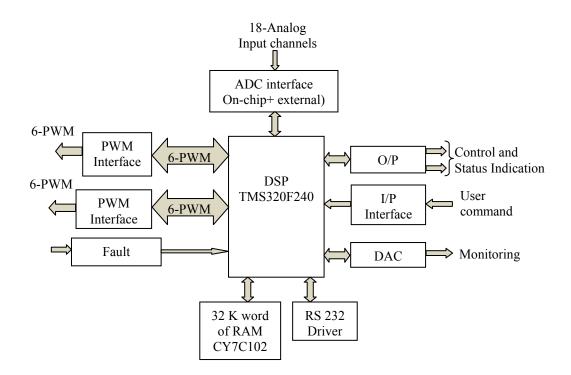

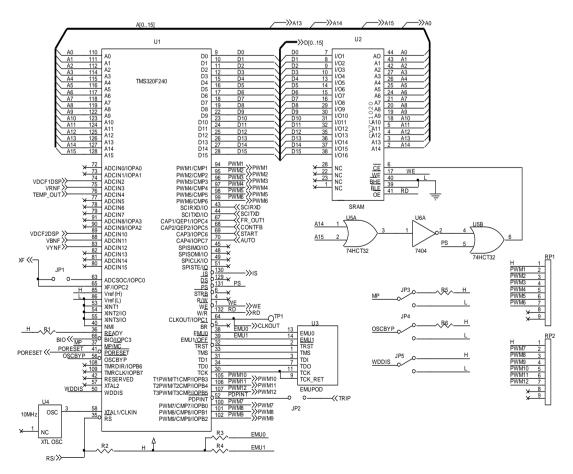

|     | 6.2.3 DSP Processor                  | 118 |

|     | 6.2.4 Hall effect sensors            | 120 |

|     | 6.2.5 Signal conditioning card       | 121 |

|     | 6.2.6 Code composer studio           | 121 |

|     | 6.2.7 Gate driver circuits           | 121 |

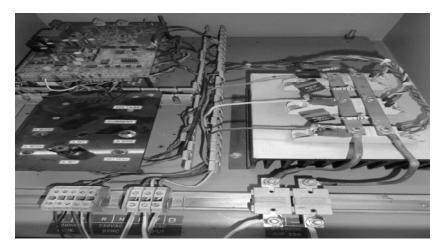

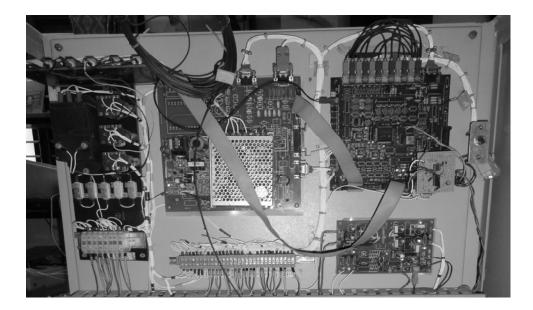

|     | 6.2.8 Complete hardware setup        | 122 |

| 6.3 | Modified-SRF with SVM technique      | 123 |

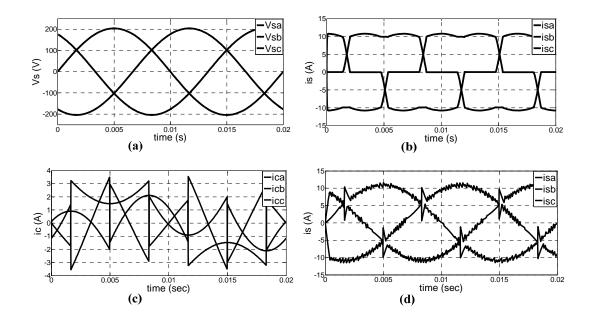

|     | 6.3.1 Simulation results             | 124 |

|     | 6.3.2 Experimental results           | 125 |

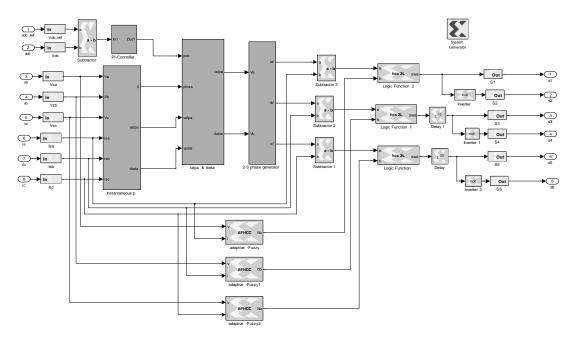

| 6.4 | Modified-SRF with adaptive-fuzzy-HCC | 128 |

|     | 6.4.1 Simulation results             | 130 |

|     | 6.4.2 Experimental results           | 131 |

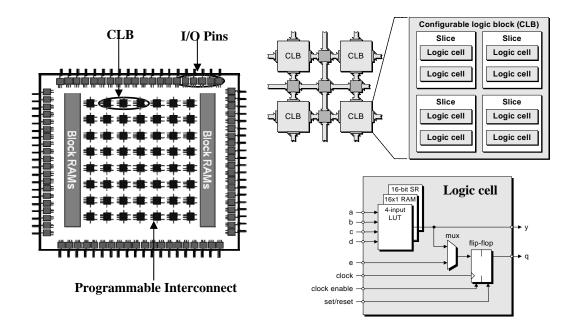

| 6.5 | Study of FPGA Controller             | 140 |

|     | 6.5.1 FPGA architecture              | 141 |

|     | 6.5.2 Configuring FPGAs              | 142 |

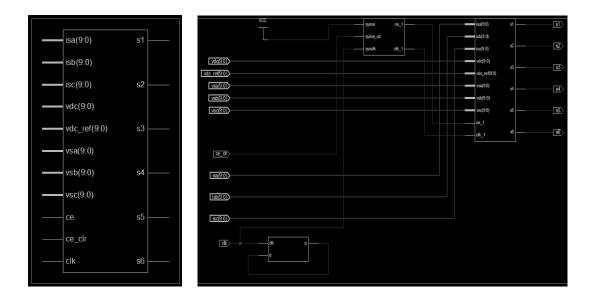

|     | 6.5.3 FPGA controller design         | 143 |

|     | 6.5.4 FPGA implementation            | 145 |

|     | 6.5.4.1 Hardware-co-simulation       | 146 |

|     | 6.5.4.2 Xilinx ISE-iMPACT            | 146 |

|     | 6.5.5 Results and analysis           | 147 |

| 6.6 | Conclusions                          | 150 |

|-----|--------------------------------------|-----|

|     | CHAPTER 7 CONCLUSION AND FUTURE WORK |     |

| 7.1 | General conclusion                   | 151 |

| 7.2 | Scope for future work                | 154 |

|     |                                      |     |

|     |                                      |     |

|     | REFERENCES                           | 155 |

|     |                                      |     |

|     | LIST OF PUBLICATIONS                 | 168 |

|     |                                      |     |

|     | APPENDIX                             |     |

|     |                                      | 171 |

|     | Appendix – A                         | 1/1 |

|     | Appendix – B                         | 173 |

|     |                                      | 175 |

## LIST OF TABLES

| Table | Title                                                                 | Page No |

|-------|-----------------------------------------------------------------------|---------|

| 3.1   | Rule base table using 49-rules                                        | 41      |

| 3.2   | Rule base table using 25-rules                                        | 43      |

| 4.1   | Relative comparison of direct and indirect current control techniques | 64      |

| 4.2   | Space vector components for VSI switching states                      | 69      |

| 4.3   | Fuzzy logic rules                                                     | 79      |

| 5.1   | THD measurements                                                      | 91      |

| 5.2   | Real (P) and Reactive (Q) power measurements                          | 92      |

| 5.3   | THD measurements                                                      | 96      |

| 5.4   | Real (P) and Reactive (Q) power measurements                          | 97      |

| 5.5   | THD measurements                                                      | 103     |

| 5.6   | Real (P) and Reactive (Q) power measurements                          | 104     |

| 5.7   | THD measurements                                                      | 107     |

| 5.8   | THD measurements                                                      | 112     |

| 5.9   | Real (P) and Reactive (Q) power measurements                          | 113     |

| 6.1   | THD measurements                                                      | 139     |

## LIST OF FIGURES

| Fig. No. | Title                                                                                           | Page No.         |

|----------|-------------------------------------------------------------------------------------------------|------------------|

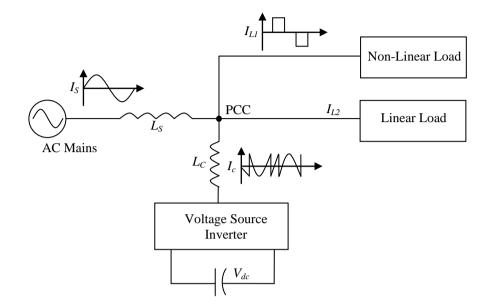

| 1.1      | Schematic diagram of shunt active power line conditioner                                        | 7                |

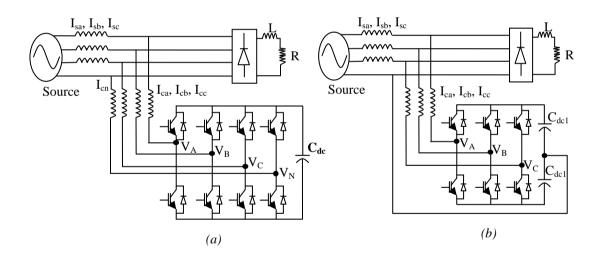

| 2.1      | (a) Current source inverter and (b) Voltage source inverter                                     | 18               |

| 2.2      | Single-phase shunt active power line conditioner system                                         | 20               |

| 2.3      | Three-phase three-wire shunt active power line conditioner system                               | 20               |

| 2.4      | Three-phase 4-wire shunt APLC system (a) 4-leg inverter (b) 3-leg inverter                      | 21               |

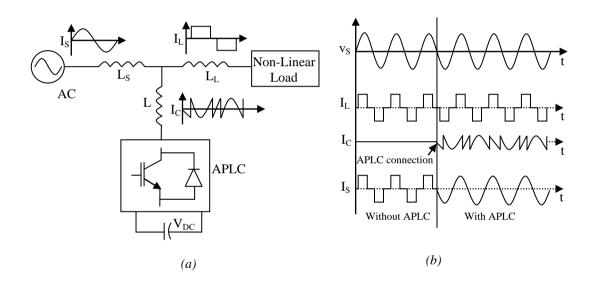

| 2.5      | (a) Schematic diagram of shunt APLC system and (b) Schematic waveforms                          | 22               |

| 2.6      | Vector diagram                                                                                  | 27               |

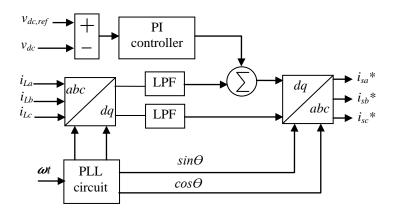

| 3.1      | Block diagram of the PI / PID - controller                                                      | 36               |

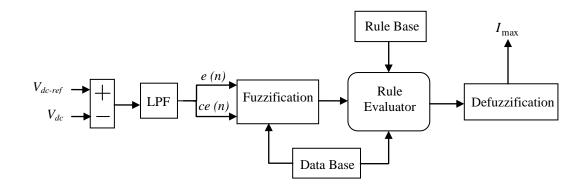

| 3.2      | Schematic diagram of the fuzzy logic controller                                                 | 39               |

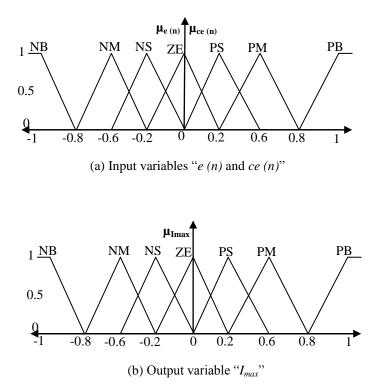

| 3.3      | Membership functions (a) the input variables $e(n)$ , $ce(n)$ and (b) output variable $I_{max}$ | <sub>ax</sub> 40 |

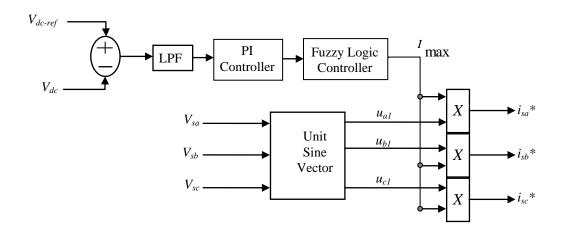

| 3.4      | Block diagram of the PI with fuzzy logic controller                                             | 42               |

| 3.5      | Block diagram of the generalized fryze power theory algorithm                                   | 44               |

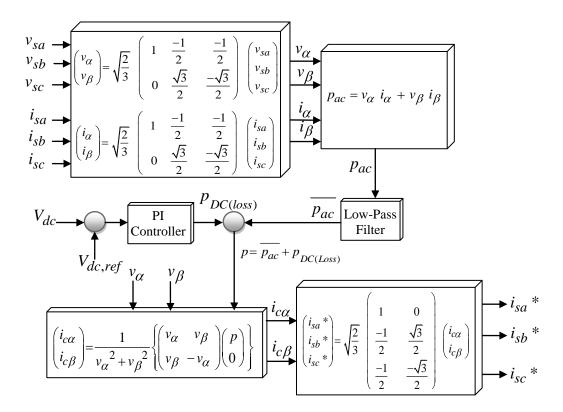

| 3.6      | Block diagram of the instantaneous real-power theory                                            | 46               |

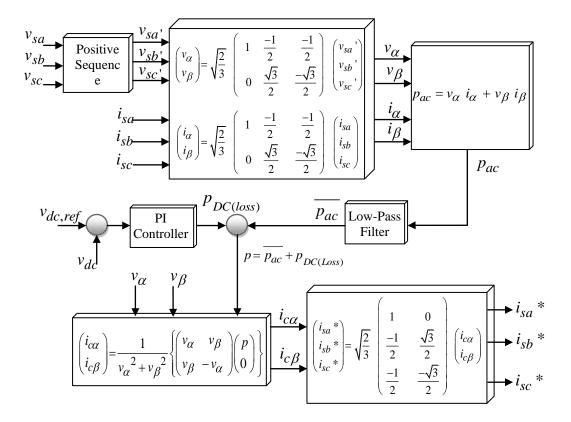

| 3.7      | Block diagram of the sinusoidal extraction controller                                           | 49               |

| 3.8      | Block diagram of the positive sequence voltage detector                                         | 51               |

| 3.9      | PLL-circuit                                                                                     | 52               |

| 3.10     | Block diagram of the conventional-SRF method                                                    | 54               |

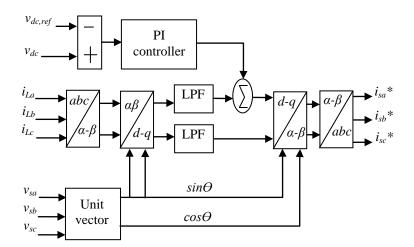

| 3.11     | Block diagram of the modified - SRF method                                                      | 55               |

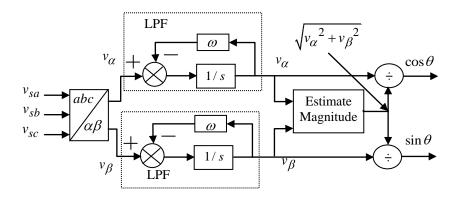

| 3.12     | Block diagram of the unit vector generation                                                     | 56               |

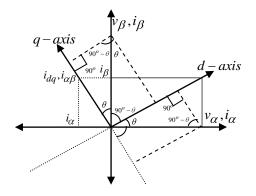

| 3.13     | Voltage and current components in stationary and rotating d-q frame                             | 57               |

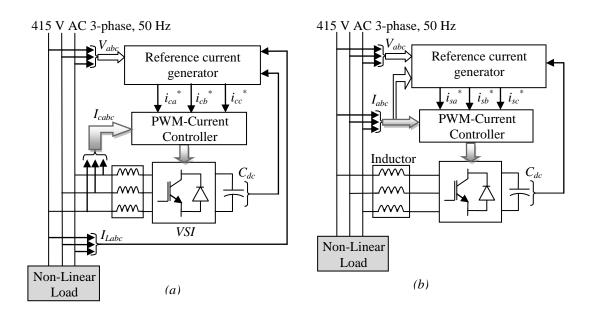

| 4.1      | Block diagram of (a) Direct current controller and (b) Indirect current controller              | 63               |

| 4.2      | Block diagram of triangular-carrier current controller                                          | 66               |

| 4.3      | Block diagram of triangular-periodical current controller                                       | 67               |

| 4.4      | Eight switching state topologies of the VSI                                                     | 68               |

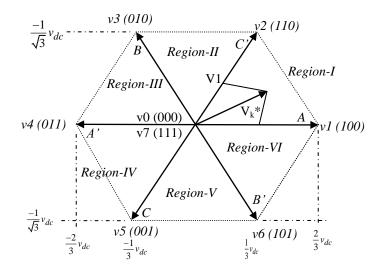

| 4.5      | Space vector diagram of the converter states and modulating signal                              | 70               |

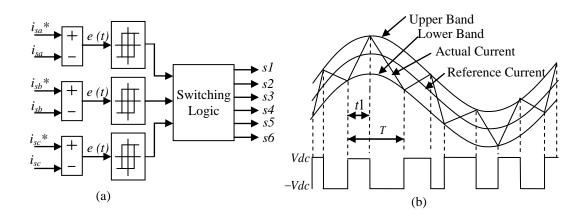

| 4.6      | Block diagram of (a) two-level HCC and (b) two-level switching pattern                          | 72               |

| 4.7  | Switching patterns of the three-level HCC                                                     | 73 |

|------|-----------------------------------------------------------------------------------------------|----|

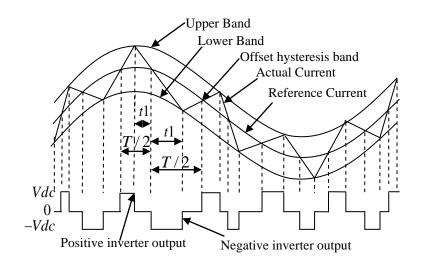

| 4.8  | (a) Block diagram of an adaptive-HCC and (b) Single line switching function                   | 75 |

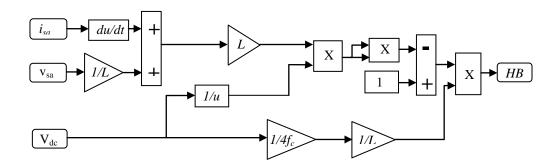

| 4.9  | Block diagram of an adaptive-hysteresis bandwidth calculation                                 | 77 |

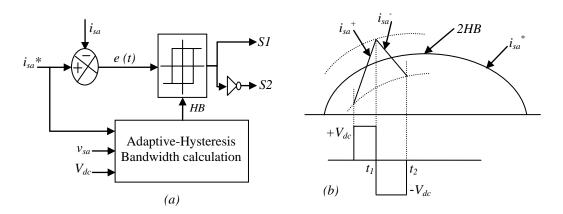

| 4.10 | Block diagram of (a) Adaptive-fuzzy-HCC and (b) Fuzzy processing                              | 78 |

| 4.11 | Membership functions for the input and output variables $di_{sa}/dt$ , $v_{sa}$ and HB        | 79 |

| 5.1  | Subdivision of an APLC controller                                                             | 81 |

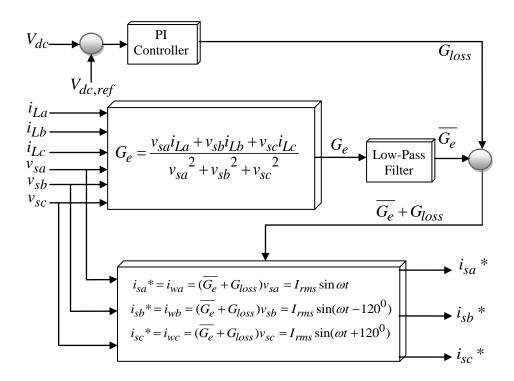

| 5.2  | PI / PID / FLC / PI-FLC based active power line conditioner system                            | 83 |

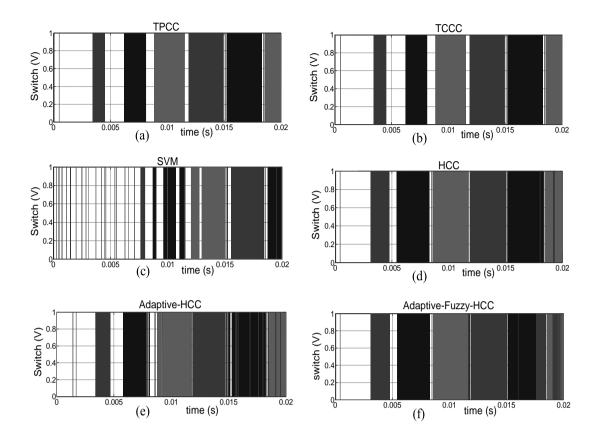

| 5.3  | Switching patterns of (a) TCCC, (b) TPCC, (c) SVM, (d) Fixed-HCC,                             |    |

|      | (e) Adaptive-HCC and (f) Adaptive-fuzzy-HCC techniques                                        | 84 |

| 5.4  | Simulation waveforms of (a) Source current before compensation,                               |    |

|      | (b) Compensation current and (c) Source current after compensation                            | 85 |

| 5.5  | Simulation waveforms of (a) Source current before APLC compensation,                          |    |

|      | (b) Compensation current and (c) Source current after APLC compensation                       | 86 |

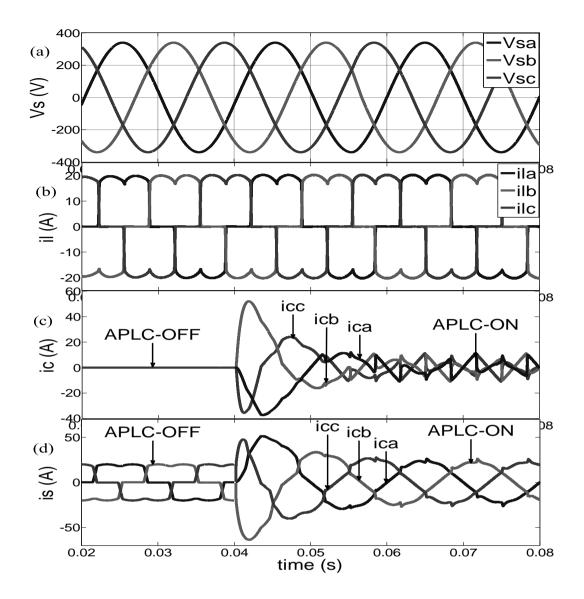

| 5.6  | (a) Supply voltages, (b) Source currents before compensation,                                 |    |

|      | (c) Compensation currents (when APLC is OFF / ON) and                                         |    |

|      | (d) Source currents after compensation (when APLC is OFF / ON) $% \left( A_{1}^{2}\right) =0$ | 87 |

| 5.7  | Simulation of (a) Supply voltages, (b) Source currents before APLC,                           |    |

|      | (c) Compensation currents and (d) Source currents after APLC                                  | 88 |

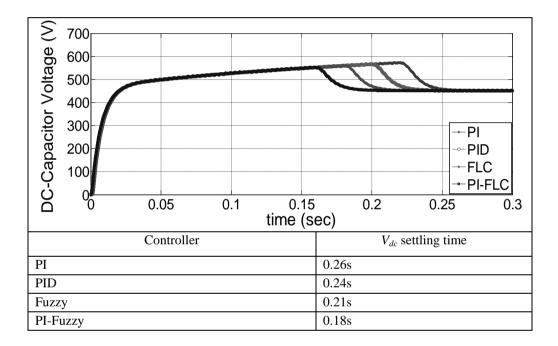

| 5.8  | dc-link capacitor voltage settling time                                                       | 89 |

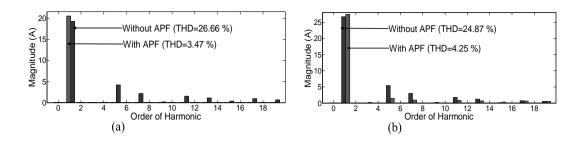

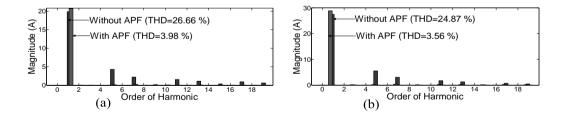

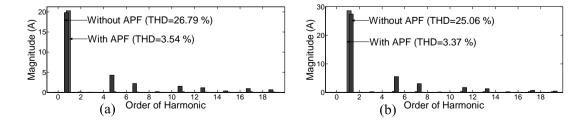

| 5.9  | Order of harmonics (a) Steady-state and (b) Transient-state                                   | 90 |

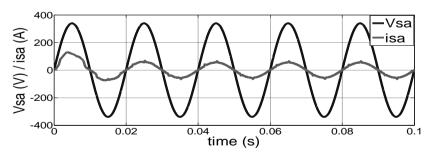

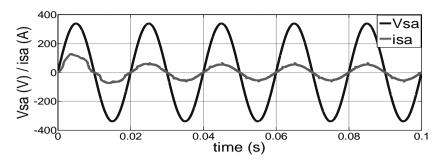

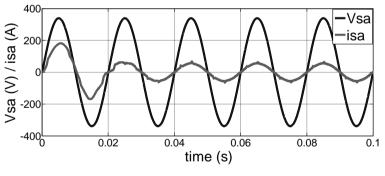

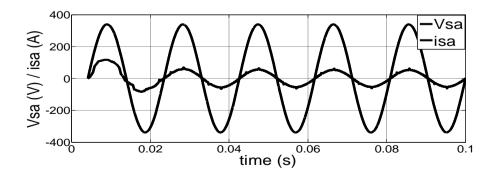

| 5.10 | Source voltage per current for unity power factor                                             | 90 |

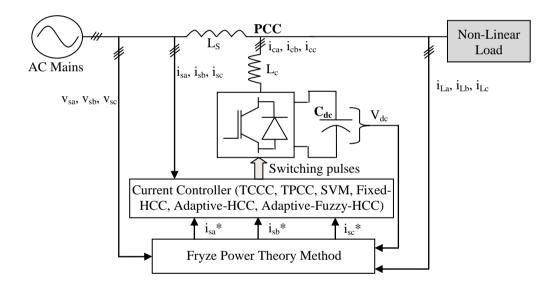

| 5.11 | Fryze power theory based shunt APLC implemented with VSI                                      | 93 |

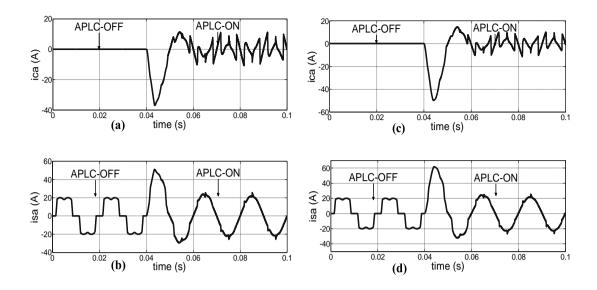

| 5.12 | (a) Compensation current under APLC is OFF / ON,                                              |    |

|      | (b) Source current under APLC is OFF / ON using fixed-HCC, and                                |    |

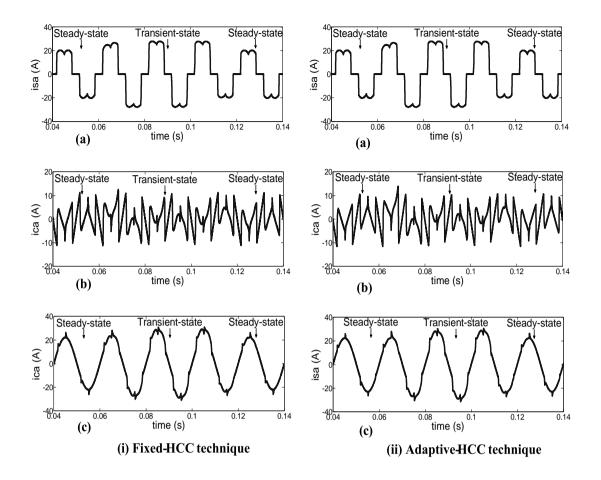

|      | (c-d) Source current under APLC is OFF / ON using adaptive-HCC                                | 94 |

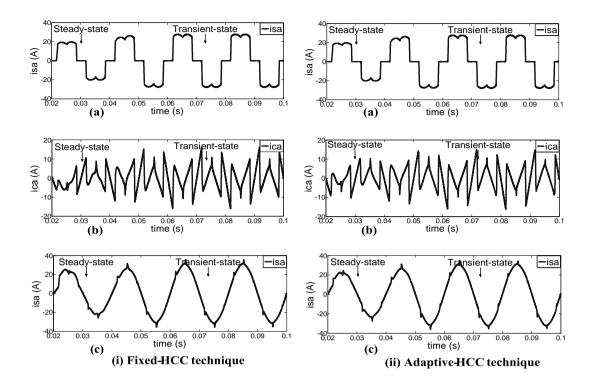

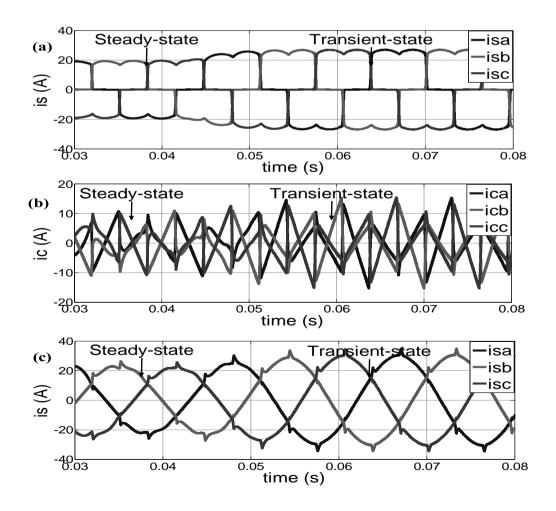

| 5.13 | Simulation waveforms of (a) Steady-state (b) Transient-state                                  | 94 |

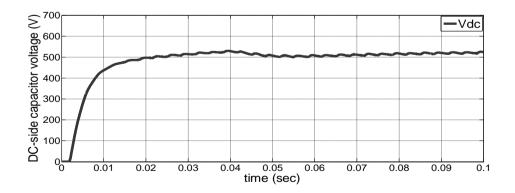

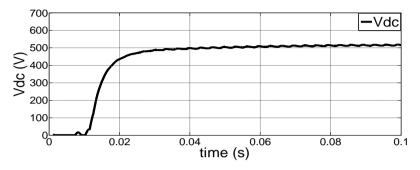

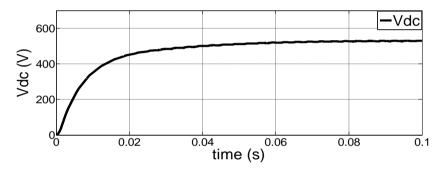

| 5.14 | dc-link capacitor voltage settling time                                                       | 95 |

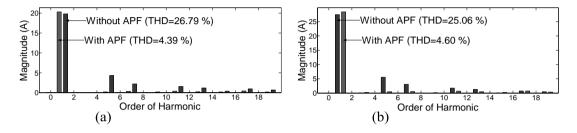

| 5.15 | Order of harmonics (a) Steady-state and (b) Transient-state                                   | 96 |

| 5.16             | Unity power factor                                                                                                                                                                                                   | 97  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.17             | Instantaneous real-power theory / Sinusoidal extraction controller based shunt APLC system                                                                                                                           | 98  |

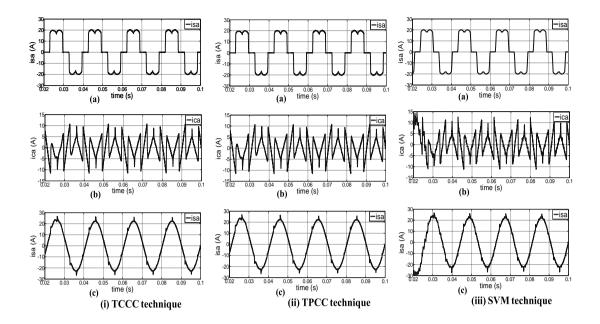

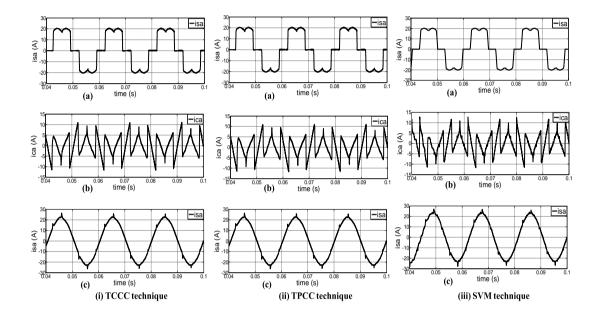

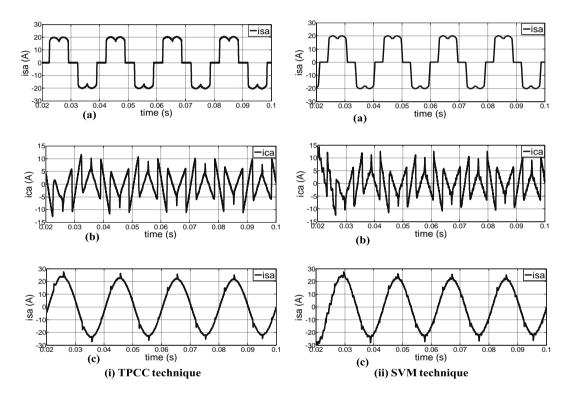

| 5.18             | Simulation waveforms of (a) Source current before compensation,<br>(b) Compensation current and (c) Source current after compensation                                                                                | 99  |

| 5.19             | Simulation waveforms of (a) Source current before APLC compensation,<br>(b) Compensation current and (c) Source current after APLC compensation                                                                      | 100 |

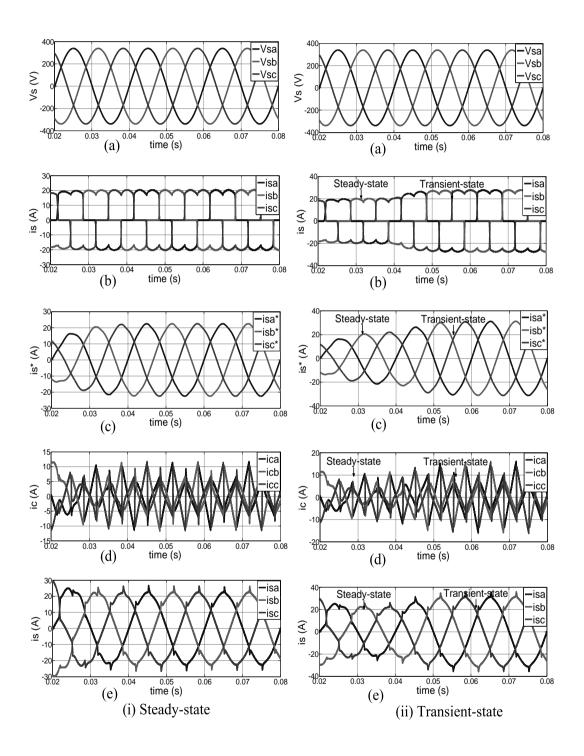

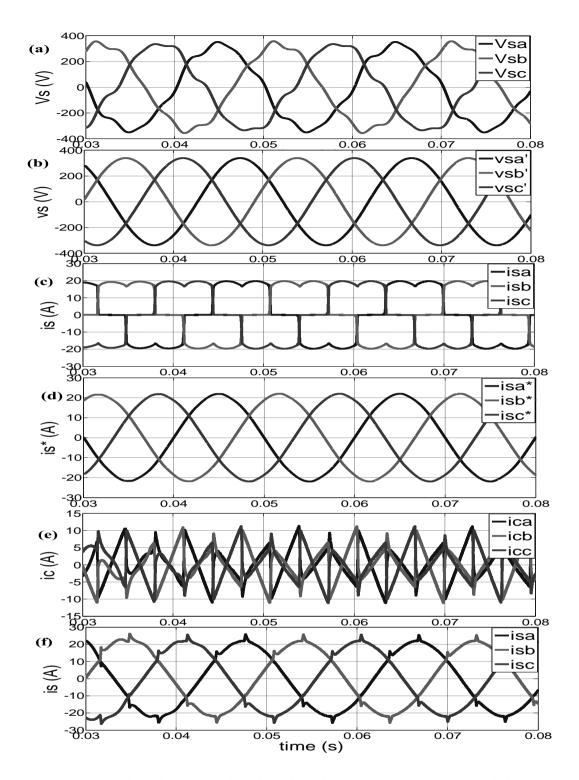

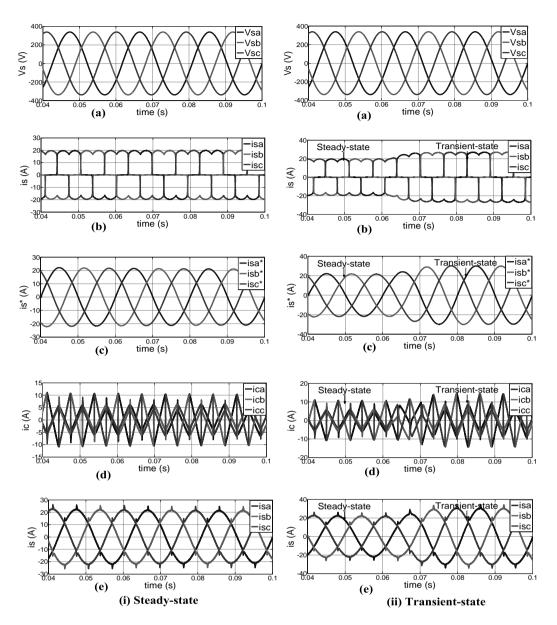

| 5.20             | <ul><li>Simulation waveforms of (a) Supply voltages,</li><li>(b) Source currents before compensation, (c) Reference currents,</li><li>(d) Compensation currents and (e) Source currents after compensation</li></ul> | 101 |

| 5.21             | dc-link capacitor voltage settling time                                                                                                                                                                              | 102 |

| 5.22             | Order of harmonics (a) Steady-state and (b) Transient-state                                                                                                                                                          | 102 |

| 5.23<br>5.24     | Unit power factor<br>(a) Distorted supply voltages, (b) Balanced supply voltages,                                                                                                                                    | 103 |

| J.2 <del>4</del> | <ul><li>(a) Distorted suppry vortages, (b) Balanced suppry vortages,</li><li>(c) Source currents before APLC, (d) Reference currents,</li></ul>                                                                      |     |

|                  | (e) Compensation currents and (d) Source currents after APLC                                                                                                                                                         | 105 |

| 5.25             | Simulation waveforms of (a) Source currents before compensation,<br>(b) Compensation currents and (c) Source currents after compensation                                                                             | 106 |

| 5.26             | Conventional / Modified-SRF controller based shunt APLC system                                                                                                                                                       | 108 |

| 5.27             | Simulation waveforms of (a) Source current before compensation<br>(b) Compensation current (c) Source current after compensation using<br>TPCC, SVM and adaptive-HCC respectively                                    | 109 |

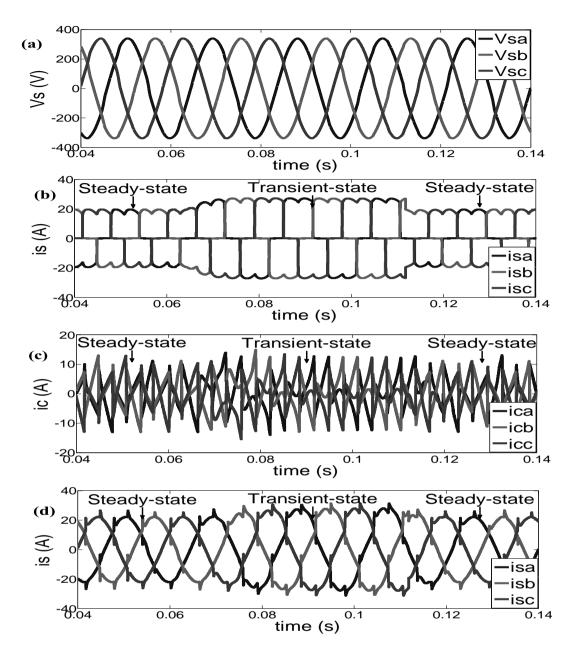

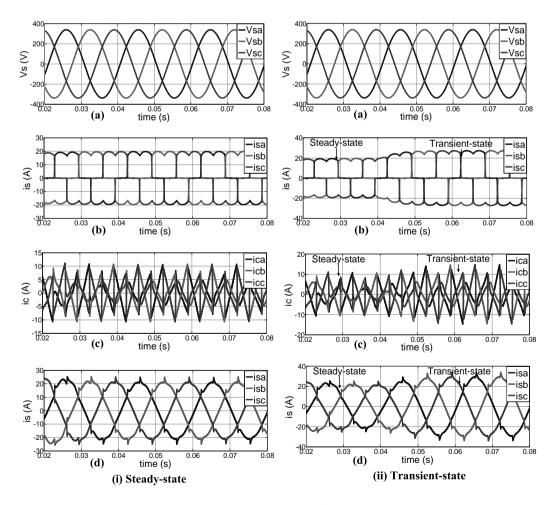

| 5.28             | Simulation waveforms of (a) Steady-state (b) Transient-state                                                                                                                                                         | 110 |

| 5.29             | dc-link capacitor voltage                                                                                                                                                                                            | 111 |

| 5.30             | Order of harmonics (a) Steady-state and (b) Transient-state                                                                                                                                                          | 111 |

| 5.31             | Unit power factor                                                                                                                                                                                                    | 112 |

| 6.1              | Photograph of thyristor-rectifier load                                                                                                                                                                               | 116 |

| 6.2        | Photograph of inductor and resistor load                                        | 117 |

|------------|---------------------------------------------------------------------------------|-----|

| 6.3        | Photograph of (a) Three-phase VSI with gate-driver circuit                      |     |

|            | (b) Interface-inductor and pre-charger                                          | 118 |

| <i>с</i> 1 |                                                                                 | 110 |

| 6.4        | Block diagram of the TMS320F240 DSP controller                                  | 119 |

| 6.5        | Photograph of the TMS320F240DSP and SMPS for powering the DSP                   | 120 |

| 6.6        | Photograph of (a) voltage sensor and (b) current sensor                         | 121 |

| 6.7        | Photograph of the complete hardware setup for APLC system                       | 123 |

| 6.8        | Simulation waveforms of (a) Supply voltages,                                    |     |

|            | (b) Source currents before APLC compensation,(c) Compensation currents          |     |

|            | (d) Source currents after APLC compensation                                     | 124 |

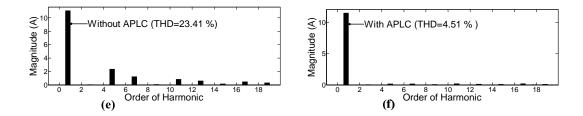

|            | (e) Without-APLC and (f) With-APLC                                              | 125 |

| 6.9        | Block diagram of shunt APLC using modified-SRF with direct SVM-technique        | 126 |

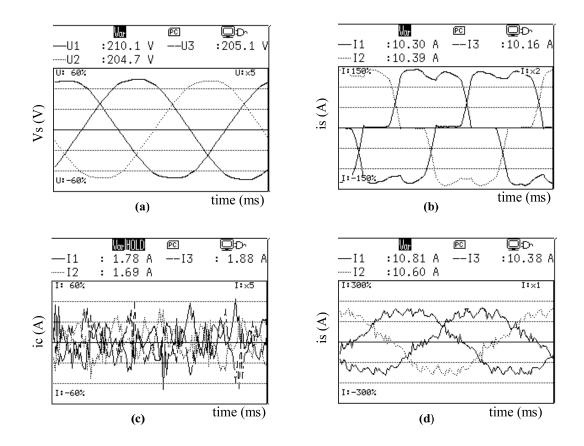

| 6.10       | Experimental waveforms of (a) Supply voltages, (b) Source currents              |     |

|            | before APLC compensation, (c) Compensation currents and                         |     |

|            | (d) Source currents after APLC compensation                                     | 127 |

| 6.11       | Order of harmonics (a) Without APLC and (b) With APLC                           | 128 |

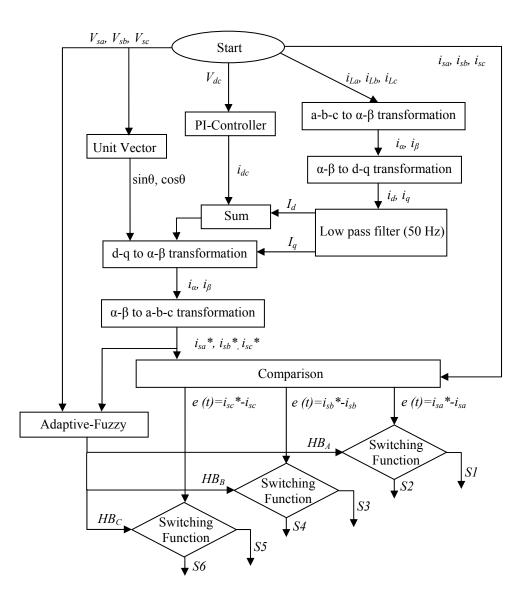

| 6.12       | Flow chart of the modified-SRF with indirect current control adaptive-fuzzy-HCC | 129 |

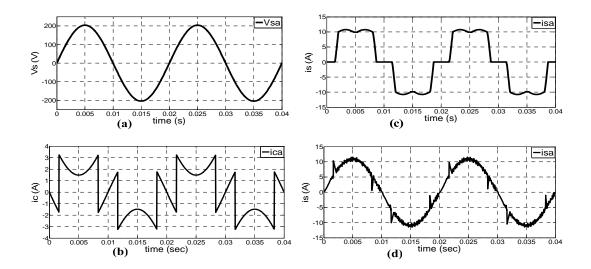

| 6.13       | Simulation waveforms of (a) Supply voltage, (b) Source current                  |     |

|            | before APLC compensation, (c) Compensation current and                          |     |

|            | (d) Source current after APLC compensation                                      | 130 |

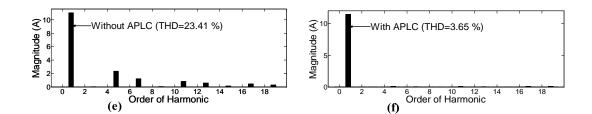

|            | (e) Order of harmonics of source current Without-APLC and (f) With-APLC         | 131 |

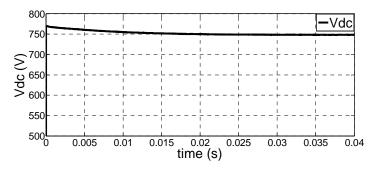

| 6.14       | dc-link capacitor voltage                                                       | 131 |

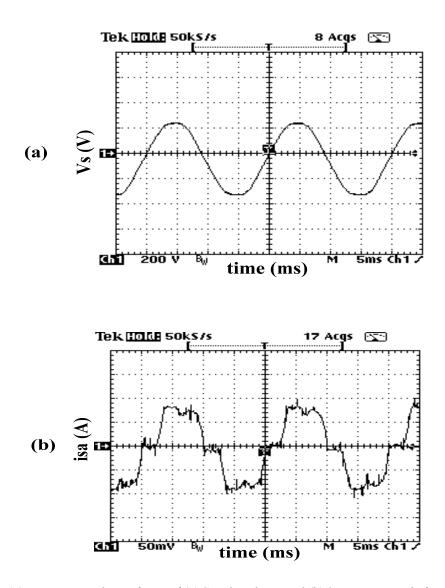

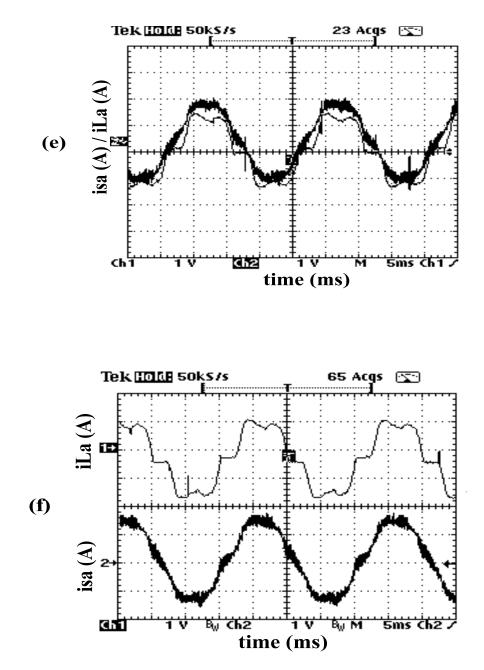

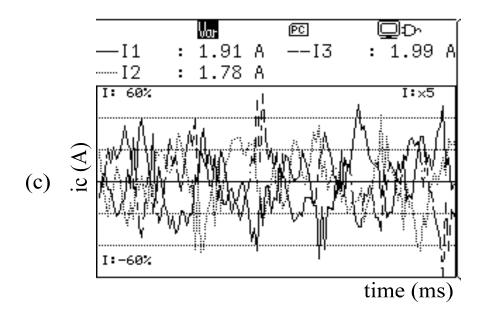

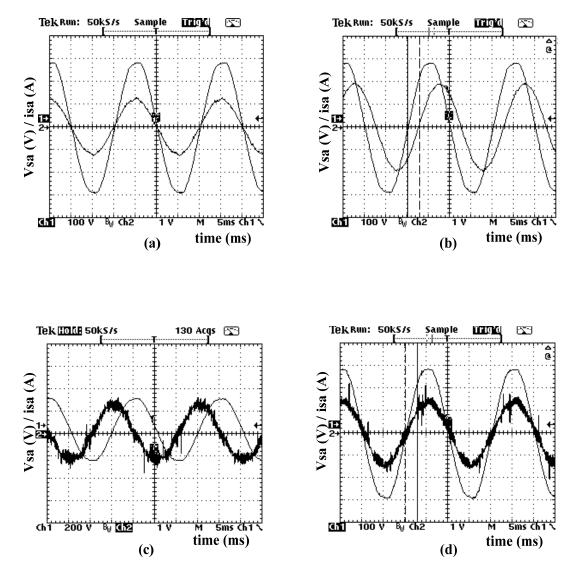

| 6.15       | Experimental waveforms of (a) Supply voltage and                                |     |

|            | (b) source current before APLC compensation                                     | 132 |

|            | (c) Switching pulses and (d) Compensation current                               | 133 |

|            | (e) Source current after compensation, and (f) Load current and Source current  | 134 |

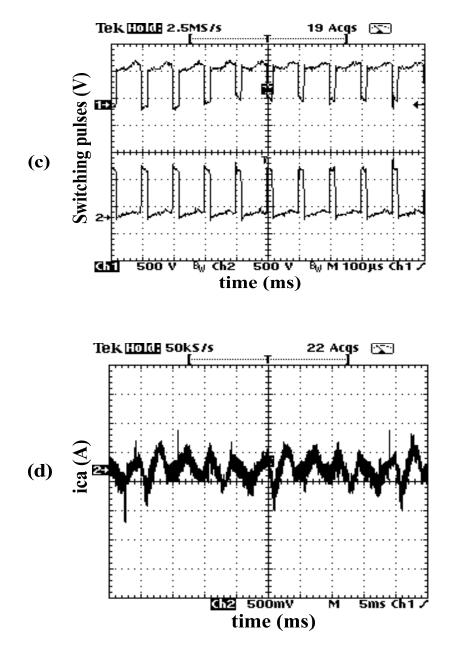

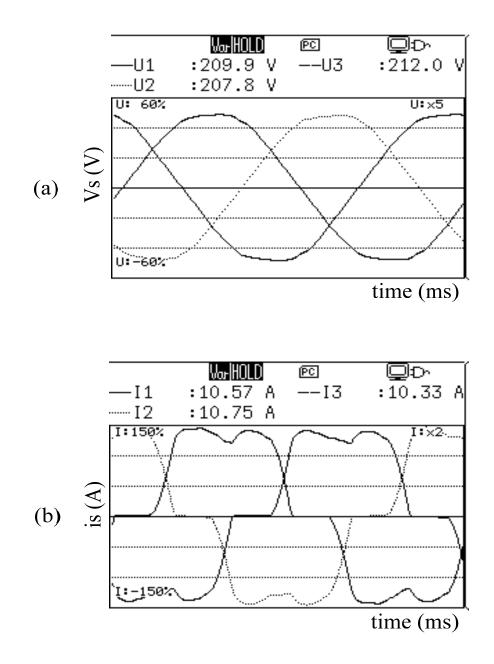

| 6.16       | Experiment waveforms of (a) Supply voltages and                                 |     |

| 0.10       | (b) Source currents before APLC compensation                                    | 135 |

|            | (c) Compensation currents and (d) Source currents after APLC compensation       | 136 |

|            |                                                                                 |     |

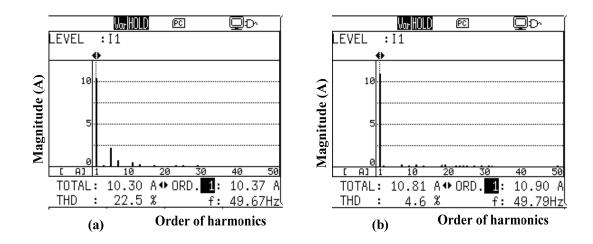

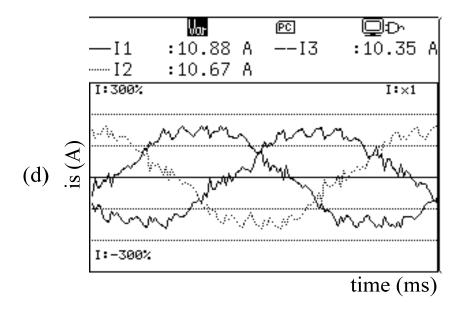

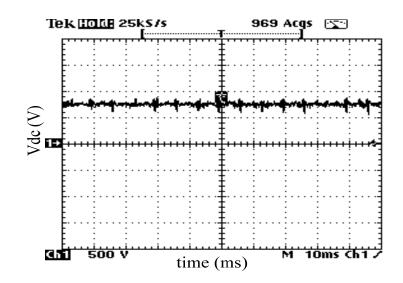

| 6.17 | Order of harmonics (a) Without-APLC (THD=22.5 %) and              |     |  |  |  |

|------|-------------------------------------------------------------------|-----|--|--|--|

|      | (b) With-APLC (THD=3.7 %)                                         | 137 |  |  |  |

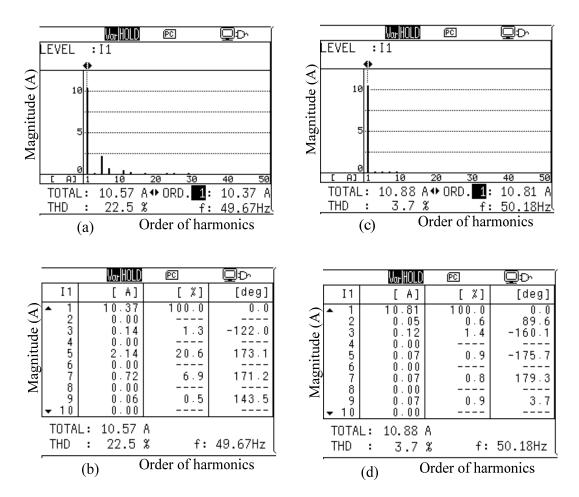

| 6.18 | dc-link capacitor voltage                                         | 138 |  |  |  |

| 6.19 | Experimental waveforms of supply voltage versus current           |     |  |  |  |

|      | (a) Resistor-load (b) Inductor-load, (c) Compensation current and |     |  |  |  |

|      | (d) After APLC compensation under inductive-load                  | 139 |  |  |  |

|      |                                                                   |     |  |  |  |

| 6.20 | Structure of FPGA                                                 | 142 |  |  |  |

| 6.21 | Controller design using Xilinx blockset / Matlab                  | 145 |  |  |  |

| 6.22 | View of the RTL schematic                                         | 147 |  |  |  |

| 6.23 | VHDL simulation result (input signals)                            | 148 |  |  |  |

| 6.24 | Six-channel gate driver switching pulses using VHDL code          | 148 |  |  |  |

| 6.25 | Photograph of Xilinx / Spatran3e FPGA implementation              | 149 |  |  |  |

## **ABBREVIATION**

| AC      | - | Alternating Current                               |

|---------|---|---------------------------------------------------|

| AMP     | - | Amplitude                                         |

| APF     | - | Active Power Filter                               |

| APLC    | - | Active Power-Line Conditioner                     |

| ASD     | - | Adjustable Speed Drive                            |

| ASIC    | - | Application Specific Integrated Circuits          |

| CENELEC | - | Comite Europeen de Normalisation Electrotechnique |

| CLB     | - | Configurable Logic Block                          |

| CMOS    | - | Complementary Metal Oxide Semiconductor           |

| CSI     | - | Current Source Inverter                           |

| DC      | - | Direct Current                                    |

| DSP     | - | Digital Signal Processor                          |

| EDA     | - | Electronic Design Automation                      |

| EPQ     | - | Electric Power Quality                            |

| FBD     | - | Fryze-Buchholz-Dpenbrock                          |

| FFT     | - | Fast Fourier Transformation                       |

| FLC     | - | Fuzzy Logic Controller                            |

| FPGA    | - | Field Programmable Gate Array                     |

| HB      | - | Hysteresis Band                                   |

| HCC     | - | Hysteresis Current Controller                     |

| HDL     | - | Hardware Description Language                     |

| HVDC    | - | High Voltage Direct Current                       |

| IEC     | - | International Electro-technical Commission        |

| IEEE    | - | Institute of Electrical and Electronics Engineers |

| IGBT    | - | Insulated Gate Bibolar Transistor                 |

| IOB     | - | Input Output Blocks                               |

| LOM     | - | Largest of Maximum                                |

| LPF     | - | Low Pass Filter                                   |

| LUT     | - | Look Up Table                                     |

| MOM     | - | Middle of Maximum                                 |

| NB      | - | Negative Big                                      |

| NM      | - | Negative Medium                                   |

| NS      | - | Negative Small                                    |

| PB      | - | Positive Big                                      |

| PCC     | - | Point of Common Coupling                          |

| PI      | - | Proportional Integral                             |

| PID     | - | Proportional Integral and Derivative              |

|         |   |                                                   |

| PLB  | - | Programmable Logic block                                         |

|------|---|------------------------------------------------------------------|

| PLL  | - | Phase locked loop                                                |

| PVS  | - | Positive Very Small                                              |

| PS   | - | Positive Small                                                   |

| PM   | - | Positive Medium                                                  |

| PB   | - | Positive Big                                                     |

| PVB  | - | Positive Very Big                                                |

| PWM  | - | Pulse Width Modulation                                           |

| RAF  | - | Ripple Attenuation Factor                                        |

| RTL  | - | Registor Transistor Logic                                        |

| rms  | - | root mean square                                                 |

| SFU  | - | Switch Fuse Unit                                                 |

| SMPs | - | Switched Mode Power Supply                                       |

| SMPS | - | Switched Mode Power Supplies                                     |

| SOM  | - | Smallest of Maximum                                              |

| SRF  | - | Synchronous Reference Frame                                      |

| SVC  | - | static VAR compensators                                          |

| SVM  | - | Space Vector Modulation                                          |

| TCCC | - | Triangular-Carrier Current Controller                            |

| THD  | - | Total Harmonic distortion                                        |

| TPCC | - | Triangular-Periodical Current Controller                         |

| TTL  | - | Transistor-Transistor Logic                                      |

| TV   | - | Television                                                       |

| UPS  | - | Uninterruptable Power Supply                                     |

| VA   | - | Volt Ampere                                                      |

| VAR  | - | Volt Ampere Reactor                                              |

| VCR  | - | Video Cassette Recorder                                          |

| VHDL | - | Very high speed integrated circuit Hardware Description Language |

| VLSI | - | Very Large Scale Integration                                     |

| VSI  | - | Voltage Source Inverter                                          |

| ZE   | - | Zero                                                             |

|      |   |                                                                  |

## LIST OF SYMBOLS

| f(t)                 | - | periodic function of frequency                    |

|----------------------|---|---------------------------------------------------|

| $T_k$                | - | time duration of $k^{th}$ active state vector     |

| $T_{k+1}$            | - | time duration of $(k+1)^{th}$ active state vector |

| $T_s$                | - | sampling period                                   |

| $T_o$                | - | time duration of null vector                      |

| $I_h$                | - | $h^{th}$ harmonic peak current                    |

| $\phi_h$             | - | $h^{^{th}}$ harmonic current phase                |

| $V_h$                | - | $h^{th}$ harmonic peak voltage                    |

| $	heta_h$            | - | $h^{th}$ harmonic voltage phase                   |

| ω                    | - | angular frequency                                 |

| f                    | - | fundamental frequency                             |

| $V_s$ or $v_s$       | - | supply voltage                                    |

| $I_s$ or $i_s$       | - | source current                                    |

| $I_L$ or $i_L$       | - | load current                                      |

| $I_c$ or $i_c$       | - | compensation filter current                       |

| I <sub>sm</sub>      | - | peak value of the source current                  |

| $V_{sm}$ or $v_{sm}$ | - | peak magnitude value of the source voltage        |

| I <sub>sp</sub>      | - | peak value of the extracted reference current     |

| I <sub>max</sub>     | - | magnitude of peak reference current               |

| I <sub>rms</sub>     | - | rms line current                                  |

| I <sub>sl</sub>      | - | switching loss current                            |

| m <sub>a</sub>       | - | modulation factor                                 |

| V <sub>c1</sub>      | - | fundamendal components at ac-side of PWM-inverter |

| I <sub>c1</sub>      | - | fundamental compensation current                  |

| I <sub>s1</sub>      | - | fundamental supply current                        |

| $m_f$                | - | frequency modulation ratio of the PWM-VSI.        |

| I <sub>ch</sub>      | - | harmonic content of the compensation current      |

| V <sub>ch</sub>                      | - | harmonic content of the compensation voltage                   |

|--------------------------------------|---|----------------------------------------------------------------|

| $Q_{c1}$                             | - | reactive power factor                                          |

| $R_c$                                | - | interface resistor                                             |

| L <sub>c</sub>                       | - | interface inductor                                             |

| $C_{dc}$                             | - | dc-link capacitor                                              |

| $V_{dc,ref}$                         | - | reference of the dc-link capacitor voltage                     |

| V <sub>dc</sub>                      | - | dc-link capacitor voltage                                      |

| $\Delta I_{c(p-p)\max}$              | - | peak compensation current                                      |

| $\Delta V$                           | - | difference between the source voltage and the inverter voltage |

| I <sub>c1,rated</sub>                | - | active power line conditioner current                          |

| $V_{dr,(p-p)\max}$                   | - | peak to peak voltage ripple                                    |

| $E_{\max}$                           | - | maximum energy                                                 |

| $v_{sa}, v_{sb}, v_{sc}$             | - | supply voltages a-phase, b-phase, c-phase                      |

| $u_{sa}, u_{sb}, u_{sc}$             | - | unit sine vector templates of a-phase, b-phase, c-phase        |

| $v_{ca}, v_{cb}$ and $v_{cc}$        | - | inverter voltages a-phase, b-phase, c-phase                    |

| $i_{sa}, i_{sb}, i_{sc}$             | - | source currents a-phase, b-phase, c-phase                      |

| $i_{sa}^{*}, i_{sb}^{*}, i_{sc}^{*}$ | - | Reference currents a-phase, b-phase, c-phase                   |

| $i_{ca}, i_{cb}, i_{cc}$             | - | compensation filter currents a-phase, b-phase, c-phase         |

| $i_{La}, i_{Lb}, i_{Lc}$             | - | load currents a-phase, b-phase, c-phase                        |

| $S_A, S_B, S_C$                      | - | switching signals a-phase, b-phase, c-phase                    |

| e(v)                                 | - | error voltage                                                  |

| $P_L(t)$                             | - | load power contains                                            |

| $P_f(t)$                             | - | fundamental or active power                                    |

| $P_r(t)$                             | - | reactive power                                                 |

| $P_h(t)$                             | - | harmonic power                                                 |

| ζ                                    | - | damping ratio                                                  |

| $\omega_{nv}$                        | - | natural frequency                                              |

| H(s)                                 | - | transfer function                                              |

| K <sub>P</sub>                       | - | proportional gain                                              |

|                                      |   |                                                                |

| K <sub>I</sub>                   | - | integral gain                                                          |

|----------------------------------|---|------------------------------------------------------------------------|

| K <sub>D</sub>                   | - | derivative gain                                                        |

| e(n)                             | - | error signal                                                           |

| ec(n)                            | - | change of error signal                                                 |

| a-b-c                            | - | three-phase coordinate voltage /current signal                         |

| $\alpha - \beta$                 | - | two-phase coordinate voltage/current signal                            |

| <i>P<sub>ac</sub></i>            | - | real power                                                             |

| $\overline{p_{ac}}$              | - | real power losses                                                      |

| р                                | - | instantaneous real-power                                               |

| $i_{\alpha}$ ' and $i_{\beta}$ ' | - | auxiliary currents                                                     |

| p' and $q'$                      | - | auxiliary powers                                                       |

| $p_{3\varphi}$                   | - | three-phase instantaneous active power                                 |

| $G_{e}$                          | - | conductance or admittance                                              |

| $i_d - i_q$                      | - | direct axis $(d)$ – quadratic axis $(q)$ rotating coordinates currents |

| $\vec{V}$                        | - | magnitude of the space vector                                          |

| i <sub>dc</sub>                  | - | dc-current component                                                   |

| v <sub>ref</sub>                 | - | reference voltage vector                                               |

| L                                | - | phase inductance                                                       |

| $i_{sa}$ +                       | - | rising current segment                                                 |

| i <sub>sa</sub> –                | - | falling current segment                                                |

| $t_1$ and $t_2$                  | - | switching intervals of time $t_1$ and $t_2$                            |

| $f_c$                            | - | modulation frequency                                                   |

| m                                | - | slope of the reference current                                         |

| Hz                               | - | Hertz                                                                  |

| μF                               | - | Micro Farad                                                            |

| mH                               | - | milli Hentry                                                           |

| kW                               | - | Kilo Watts                                                             |

| mV/div milli                     | - | Volt per division                                                      |

| Ω                                | - | Ohm                                                                    |

| S                                | - | time periods in seconds                                                |

| %                                | - | percentage                                                             |

### **CHAPTER 1**

## **INTRODUCTION**

#### **1.1. Introduction**

Generally, electrical engineers are focused on the subject of generation, transmission, distribution and utilization of electric energy. The distribution system is a vital connection between the generation and utilization of electrical power at rated amplitude and frequency, which indicates the Electric Power Quality (EPQ) [1]. EPQ is often used to express voltage as well as current quality, reliability of service, and quality of power supply, etc. Poor power quality sources are raised from two categories: (i) Non-linear loads, electrical components and equipments (ii) Subsystems of transmission and distribution systems. Quality degradation of electric power mainly occurs due to power line disturbances such as impulses, notches, voltage sags / swell, voltage and current unbalance, interruption and harmonic distortions [2]. The electric power quality has become an important part of the distribution power system. Harmonics are the primary cause for the poor power quality of the distribution system.

Harmonics are qualitatively defined as sinusoidal waveforms having frequencies that are integral multiples of the power line frequency. In power system engineering, the term harmonic is widely used to describe the distortion for voltage or current waveforms [3]. The power line frequency (fundamental) is 50 Hz or 60 Hz. In case the fundamental frequency is 50 Hz, then 5<sup>th</sup> harmonic is 250 Hz, and 7<sup>th</sup> harmonics is 350 Hz, etc. Nonlinear loads are the main source of harmonic related problems. All electronic loads are mostly non-linear and generate harmonics in the power system. These non-linear loads draw only short pulses of current from supply network and combine with the source impedance resulting in distortion of the supply voltage [4]. The modern power electronics provide suitable topology to mitigate the power quality problems [5]. This chapter discusses the harmonic distortion and its solutions based on shunt active power line conditioner.

#### **1.2. Research motivation**

AC power supply feeds different kind of linear and non-linear loads. The non-linear loads like power converters and solid state drives that use high speed switches are the main sources of harmonics in the power system [6]. The harmonics in the system induce several undesirable issues; such as increased heating in transformers, low power factor, torque pulsation in motors, overvoltage by resonance, harmonic voltage drop across the network impedance, poor utilization of distribution plant and also affects other loads connected at the same Point of Common Coupling (PCC). Traditionally, passive filters have been used to compensate the harmonic distortion in the distribution system. Passive filters consist of inductive and capacitive elements and are tuned to control harmonics. The passive filter is connected in shunt with the distribution system and is tuned to present low impedance to a particular harmonic current. However, it is found that the passive filter is not commonly used for lowvoltage or medium-voltage applications since the complexity and reliability factors are matters of concern. It also inherits several shortcomings such as ageing and tuning problems, resonance that affects the stability of the power distribution systems, bulky in size and also fixed compensation [7]. To solve these problems, different configurations of Static VAR Compensators (SVCs) have been proposed. Unfortunately some SVC generates lower-order harmonics themselves and the response time of the SVC system may be too long to be acceptable for fast-fluctuating loads. Recently, Active Power Filter (APFs) or Active Power-Line Conditioners (APLCs) are developed for compensating the harmonics and reactive-power simultaneously [8]. The APLC topology can be connected in series or shunt and combinations of both (unified power quality conditioners) as well as hybrid configurations [9-11]. The shunt active power line conditioner is most commonly used than the series active power line conditioner, because most of the industrial, commercial and domestic applications need current harmonic compensation.

#### **1.3.** Harmonics in the power system

Harmonic related problems are not new in the electric power system. From the early 1920's harmonics are observed in power equipment because of telephone line interference. The proliferation of power converter equipment connected to the distribution power system which limits harmonic current injection maintains good power quality [12]. The various standards and guidelines have been established that specify limits on the magnitudes of harmonic currents and voltages. The Comite Europeen de Normalisation Electrotechnique (CENELEC), International Electrotechnical Commission (IEC), and Institute of Electrical and Electronics Engineers (IEEE) specify the limits on the voltages at various harmonic frequencies of the utility frequency [13]. In 1983, IEEE Working Group made a reference about harmonic sources and effects on the electric power system. There is significant activity in the IEEE-Power Engineering Society and IEEE-Industry Applications Society to detect harmonic effects. These societies and institutes define standards for harmonics [14]. T.C.Shuter surveyed and reported the harmonic levels (three classes of distribution circuits; residential, commercial and industrial) in the American Electric Power Distribution System [15]. Christopher reported the statement "The Static Power Converter Committee of the Industry Applications Society recognized the harmonic related problems and started work on a standard that would give guidelines to users and engineer-architects in the application of static power converter drives and other uses on electric power systems that contained capacitors. The result was IEEE 519-1981, IEEE Guide for Harmonic Control and Reactive Compensation of Static Power Converters" [16]. Joseph mentioned about harmonics-causes, effects, measurements, and analysis with Specific system in the cement, steel and carbon industries [17]. Alexander E. Emanuel surveyed the harmonic voltages and currents at the customer point of industrial, commercial and residential applications [18]. In 1996, IEEE working group proposed definitions for power terms that are practical and effective when voltage and/or currents are distorted and/or unbalanced. It also suggests definitions for measurable values that may be used to indicate the level of distortion and unbalance [19]. Eric J. Davis reported the harmonic pollution metering as a theoretical consideration. He advocated "Toll Road" concept: this method requires each consumer to pay according to the amount of stress (usage) his equipment causes to the mitigation equipment [20]. Jacques discussed the concept of apparent power in single-phase sinusoidal and unbalanced three-phase situations under IEEE Standard 1459-2000. Here power factor is defined as the ratio of the actual active power to the apparent power in the power system [21]. Salvador noticed about IEEE Standard 1459. It includes new definitions for the measurement of electric power quantities

under sinusoidal, non-sinusoidal and balanced or unbalanced conditions [22]. Predrag reported about power components estimation according to IEEE Standard 1459–2010 under wide-range frequency deviations. This statement clarifies using adaptive phase shifter, cascaded integrator–comb filter, finite-impulse-response comb filter, algorithm [23]. Yao Xiao described the harmonic summation method for the standard IEC / TR 61000-3-6 in the power system [24]. The IEEE standard 1459 is intended to evaluate the performance of modern equipment or to design and build the new generation of instrumentation for energy and power quantification.

#### 1.3.1. Harmonic sources [13-154]

- Modern power electronic devices such as fluorescent lamp, static power converter, arc furnace, Adjustable Speed Drives (ASDs), electronic control and Switched Mode Power Supplies (SMPS) are drawing non-sinusoidal current which contain harmonics.

- *Switching of power electronic devices* which includes power electric converter, controlled rectifiers, uncontrolled rectifiers, inverter, static VAR compensator, cycloconverters and High Voltage Direct Current (HVDC) transmission

- Single-phase power supplies including personal computers, fax machines, photocopier, Uninterruptable Power Supplies (UPSs), Televisions (TVs), Video Cassette Recorders (VCRs), microwave ovens, air conditioners, electronic ballasts for high efficiency lighting and single phase ac and dc drives

#### 1.3.2. Harmonic problems [15-17]

- Amplification of harmonic levels resulting from series and parallel resonance.

- Plant mal-operation.

- Malfunctioning and failure of electronic components.

- Overheating and failure of electric motors.

- Overloading, overheating and failure of power factor correction capacitors.

- Overloading and overheating of distribution transformers and neutral conductors.

- Excessive measurement errors in metering equipments.

- Spurious operation of fuses, circuit breakers and other protective equipments.

- Voltage glitches in computer systems results in loss of data.

- Electromagnetic interference in HF communication systems such as television, radio, communication and telephone systems and similar signal conditioning devices.

#### 1.3.3. End effects of harmonics [18-20]

- Higher power cost

- Premature office equipment failure and data corruption or loss

- Computer and system lockups

- Loss of productivity and higher cost of products and/or services

- Reduced product or service quality and reduced quality assurance

- Loss of Customer Confidence and revenue

#### 1.3.4. Mitigation of harmonics

The harmonic related problem is mitigated by using active power quality conditioner. The active power quality conditioner can be connected in series or parallel and combinations of both (unified power quality conditioners) as well as hybrid configurations [9-12]. The series APLC operates as a voltage regulator and harmonic isolator between the nonlinear load and distribution system. The series active filter injects voltage component in series with the supply voltage and therefore can be regarded as controlled voltage source, compensating voltage sags and swells on the load side. The injected harmonic voltages are added or subtracted, to / from the source voltage to maintain pure sinusoidal voltage across the load. Hybrid APLC is a combination of passive and active power line conditioner. The hybrid series APLC is controlled to act as harmonic isolator between the source and non-linear load by injection of controlled harmonic voltage source. Unified power quality conditioner is the integration of the series and shunt APLC. The series active power filter has the capability of voltage regulation and harmonic compensation at the utility-consumer point of common coupling. The shunt active power filter absorbs current harmonics, compensate for reactive-power and negative-sequence current, and regulate the dclink voltage between both active power line conditioners. Power system current harmonics are the major problems in the distribution system, due to widespread use of non-linear loads. From the literature, the shunt active power line conditioner is an

attractive choice to solve the current harmonic as well as reactive-power problems. The shunt APLC is compensating harmonic currents drawn by the non-linear loads besides power factor correction.

#### **1.4. Shunt active power line conditioner**

Shunt active power line conditioner uses power electronics to produce complementary harmonic components that compensates the harmonic components produced by the non-linear load. This harmonic filter consists of a power converter unit and control unit, which controls the harmonic injection of the filter into the ac network based on the measured load harmonics. Therefore, this device senses voltage and current harmonics and generates offsetting harmonics to cancel out the superfluous harmonics in the source. There obviously exists a feedback mechanism by virtue of which the source provides clean waveforms for the load. Voltage regulation and power factor control are also normal byproducts of this filter operation. Some of the merits of using active power line conditioner are [25]

- Harmonic reduction

- Reduction of three-phase neutral return current

- Impact minimization upon the distribution transformer

- Power factor improvement

- Voltage regulation

- Automatically adapts to changes in the ac network and load fluctuation

- Eliminating risk of resonance between filters and network impedance

#### 1.4.1. Approach used in the thesis

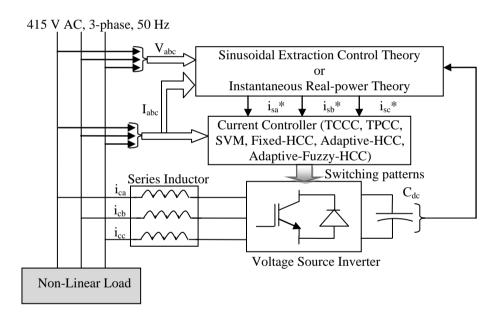

In this thesis, the parallel or shunt active power line conditioner configuration is chosen. The active power line conditioner is connected in parallel with the load being compensated at Point of Common Coupling (PCC). For this power circuit, a Pulse Width Modulation (PWM) based two-level voltage source inverter is in use, which operates in a current control mode. The current compensation is performed in time domain approach (specification) for faster response. The purpose is to inject the compensating current at the parallel point such that the source current becomes sinusoidal, since this shunt active power line conditioner is used for cancelling the current harmonics [26].

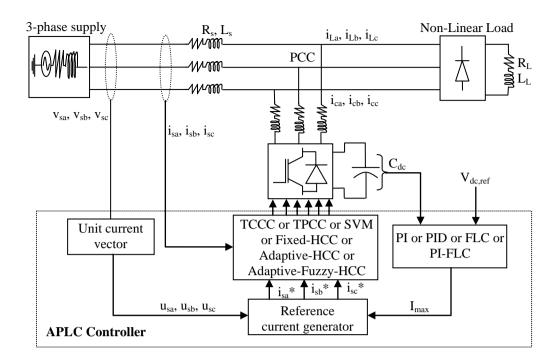

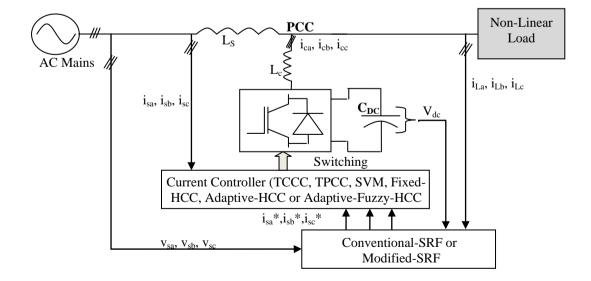

Fig.1.1 Schematic diagram of shunt active power line conditioner

Fig.1.1 shows the schematic diagram of shunt active power line conditioner. The dc-side of the voltage source inverter (also called shunt active power inverter) is connected to an energy storing capacitor and the ac-side of the inverter is connected to the ac-bus through the interface inductor. The ac-bus can supply industrial, commercial and domestic loads including the non-linear loads. The active power line conditioner is controlled in a closed loop manner, the inverter switches are controlled to actively shape the current through the coupling (interface) inductor ( $L_c$ ) following a reference current such that the input current from the source is in-phase and of the same shape as the input sinusoidal voltage. Thus, the active power line conditioner supplies reactive and harmonic components of the load current and hence the source will be required to supply only the in-phase fundamental component of the load current.

The current waveform for cancelling harmonics is achieved with the help of active power inverter and an interfacing inductor. This interfacing inductor or filter provides isolation inductance to convert the voltage signal created by the inverter to a current signal for cancelling harmonics. The compensation filter current waveform is obtained by accurately controlling the switches in the active power inverter. Control of current wave shape is limited by the switching frequency of the inverter and by the available voltage across the interfacing inductor. The voltage across the interfacing inductance determines the maximum di/dt that can be achieved by the active power inverter. This is important in the sense that relatively high values of di/dt may be required to compensate the higher order harmonic components. Therefore the choice of the inductor is essential. A large inductor would be better for isolation from the power system and protection from transient disturbances. However, the large size of the inductor would limit the ability of the compensator to compensate the higher order harmonics [27].

In this configuration, it is important to know the active power line conditioner is required to supply the compensating filter current at PCC. In an ideal situation, the active power line conditioner is required only to supply the reactive power of the load and hence the average dc-link capacitor voltage should remain constant. In practice, this however is not true as the losses of the inverter and interface inductor will make the dc charge stored in the capacitor to fall. However, it is important to keep the dc charge or voltage of the dc storage capacitor nearly constant so that the functioning of the system remains unaffected. This can only be done by drawing active current from the source to replenish the losses through a feedback mechanism. Therefore to put the active power line conditioner in use it is significant to discuss the following concerns

- The efficient reference current extraction method to extract the required reference current

- The control strategy, taking into account transient and steady state

- The high efficiency large capacity converter used as the power circuit

- The indirect PWM-current control scheme of the converter

#### **1.5.** Literature reviews

The controller is the most significant part of the active power line conditioner system and currently various control strategies are reported in the literature. There are essentially two types of controllers requirement in an active power line conditioner: (i) Reference current extraction method to generate the reference current from the distorted line current (ii) PWM-VSI current control technique to generate the switching pulses to drive the inverter.

#### 1.5.1. Reference current extraction method