# Efficient VLSI Architectures for Image Compression Algorithms

Vijay Kumar Sharma

# Efficient VLSI Architectures for Image Compression Algorithms

Thesis submitted in partial fulfillment of the requirements for the degree of

Master of Technology (Research)

In

Electronics and Communication Engineering

By

Vijay Kumar Sharma

(Roll No. 609EC101)

January 2012

Under the guidance of

Dr. U. C. Pati Dr. K. K. Mahapatra

Department of Electronics & Communication Engineering National Institute of Technology Rourkela Rourkela-769008,Odisha, India

# Department of Electronics & Communication Engineering National Institute of Technology Rourkela Rourkela-769008, Odisha, India

## Certificate

This is to certify that the thesis entitled "*Efficient VLSI Architectures for Image Compression Algorithms*" by Mr. Vijay Kumar Sharma, submitted to the National Institute of Technology, Rourkela for the degree of Master of Technology (Research), is a record of an original research work carried out by him under our supervision in the department of Electronics and Communication Engineering during session 2009-2011. We believe that the thesis fulfills the part of the requirements for the award of degree of Master of Technology (Research). Neither this thesis nor any part of it has been submitted elsewhere for the degree or academic award.

Prof. U. C. Pati

Department of Electronics and

Communication Engineering

National Institute of Technology, Rourkela

Prof. K. K. Mahapatra

Department of Electronics and Communication Engineering

National Institute of Technology, Rourkela

## Acknowledgement

I am grateful to my research advisors Prof. U. C. Pati and Prof. K. K. Mahapatra for providing me the opportunity to realize this work. They inspired, motivated, encouraged and gave me full freedom to do my work with proper suggestions throughout my research work. I am indebted to Prof. K.K. Mahapatra for his kind and moral support throughout my academics at NIT Rourkela.

I am also grateful to NIT Rourkela for providing adequate facilities in my research work.

I acknowledge MHRD and DIT (Ministry of Information & Communication Technology), Govt. of India, for giving financial support.

My special thanks to Prof. S. K. Patra, Prof. D. P. Acharya and Prof. A. K. Swain for their help and valuable suggestions. I would like to thank Sushant sir, my senior, for helping me in VLSI.

I am thankful to Prof. S. Meher and Prof. S. K. Behera for his inspiration and support. I am also thankful to Prof. G. S. Rath, Prof. B. D. Sahoo, Prof. K. B. Mohanty and Prof. N.V. L. N. Murty for their valuable support in my research work.

I would like to give special thank to Prakash sir, Preeti madam and Ranjan sir who helped and supported me throughout my research work.

I must thank Karupannan sir, Kanhu sir, Jagannath and Tom sir for their support and help. I also thank Srinivas sir and Venkatratnam sir for their good attitude and behavior.

I sincerely thank to all my friends, Research scholars of ECE Department, M.Tech (VLSI) students and all academic and non-teaching staffs in NIT Rourkela who helped me

Vijay Kumar Sharma

# Contents

| Certificate  |                                                          | III  |

|--------------|----------------------------------------------------------|------|

| Acknowled    | gement                                                   | IV   |

| Contents     |                                                          | V    |

| List of Figu |                                                          | VII  |

| List of Tab  | les                                                      | XIII |

| Abstract     |                                                          | 1    |

| Chapter 1    | Introduction                                             | 3    |

| 1.1          | Motivation                                               | 4    |

| 1.2          | Background                                               | 6    |

| 1.3          | Objective of the Thesis                                  | 9    |

| 1.4          | Chapter Wise Contribution of the Thesis                  | 10   |

| 1.5          | Summary                                                  | 1    |

| Chapter 2    | Image Compression                                        | 13   |

| 2.1          | Introduction                                             | 1.   |

| 2.2          | Image representation and classification                  | 14   |

| 2.3          | Image Quality Measurement Metric                         | 15   |

| 2.4          | Image Compression Model                                  | 17   |

| 2.5          | Transform based Image Coding                             | 19   |

| 2.6          | JPEG baseline Image Coding                               | 2    |

| 2.7          | Discrete Cosine Transform (DCT)                          | 2.   |

| 2            | 2.7.1 2-D DCT Equation                                   | 24   |

|              | 2.7.2 Energy Compaction Property of 2-D DCT              | 25   |

| 2            | 2.7.3 Image Reconstruction by Selective DCT Coefficients | 27   |

| 2.8          | Separable Discrete Hartley Transform (SDHT)              | 31   |

| 2.9          | Conclusions                                              | 35   |

| Chapter 3    | Distributed Arithmetic and Its VLSI Architecture         | 36   |

| 3.1          | Introduction                                             | 36   |

| 3.2          | Systolic Architecture                                    | 37   |

| 3.3          | ROM based Distributed Arithmetic (DA)                    | 39   |

| :         | 3.3.1  | FPGA Implementation of 8-points 1-D DHT using ROM based DA                           | 45  |

|-----------|--------|--------------------------------------------------------------------------------------|-----|

|           | 3.3.2  | FPGA Implementation of SDHT using ROM based DA                                       | 46  |

| 3.4       | RON    | M Free DA                                                                            | 48  |

|           | 3.4.1  | FPGA Implementation of DCT using ROM free DA                                         | 51  |

|           | 3.4.2  | Area and Power Efficient VLSI Architecture of 8x1 1-D DCT                            | 58  |

| 3.5       | SDF    | IT Implementation using ROM free DA                                                  | 64  |

| 3.6       | Con    | clusions                                                                             | 67  |

| Chapter 4 | Ef     | ficient JPEG Image Compression Architecture                                          | 68  |

| 4.1       | Intro  | oduction                                                                             | 68  |

| 4.2       | Non    | malization matrix for hardware simplification in JPEG                                | 68  |

| 4.3       | Effic  | cient Architecture from DCT to Quantization and Re-ordering                          | 72  |

| 4.4       | Huf    | fman Coding Architecture Implementation in FPGA for JPEG                             | 78  |

| 4.5       | Con    | clusions                                                                             | 93  |

| Chapter 5 |        | irect Computation of 8x8 2-D DCT Coefficients Equation and Its Hardware Architecture | 94  |

| 5.1       | Intro  | oduction                                                                             | 94  |

| 5.2       | Equa   | ation for Direct computation of 2-D DCT                                              | 95  |

| 5.3       | Non    | -recursive VLSI architecture of 2-D DCT                                              | 102 |

| 5.4       |        | G Image Compression Architecture using Proposed -recursive 2-D DCT                   | 114 |

| 5.5       | Con    | clusions                                                                             | 117 |

| Chapter 6 | Su     | ummary and Conclusions                                                               | 118 |

| 6.1       | Sum    | nmary                                                                                | 118 |

| 6.2       | Gen    | eral Conclusions                                                                     | 119 |

| 6.3       | Futu   | are Scope                                                                            | 120 |

| Apper     | ndix A | L                                                                                    | 121 |

| Apper     | ndix B | }                                                                                    | 122 |

# List of Figures

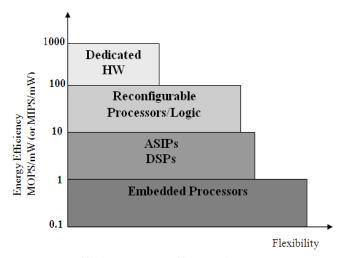

| Fig.1.1 | Energy efficiency on different implementations [23]                                                                                                                                                                                        | 5                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

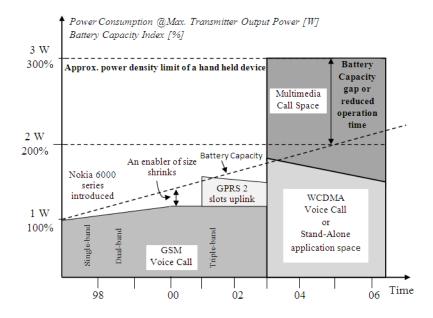

| Fig.1.2 | Trends in power consumption and battery capacity [37]                                                                                                                                                                                      | 6                                      |

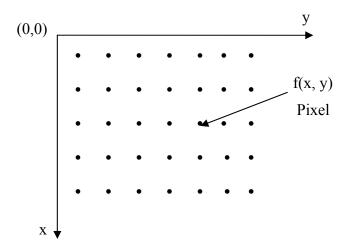

| Fig.2.1 | Representation of digital image in two dimensional spatial coordinate                                                                                                                                                                      | 14                                     |

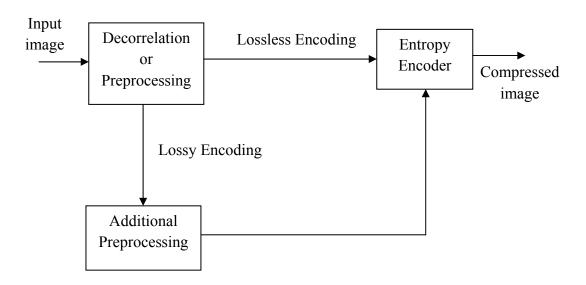

| Fig.2.2 | A generalized image compression model [76]                                                                                                                                                                                                 | 18                                     |

| Fig.2.3 | Transform based image compression model                                                                                                                                                                                                    | 19                                     |

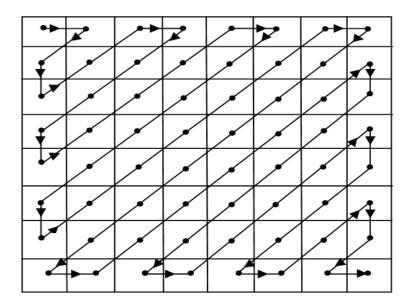

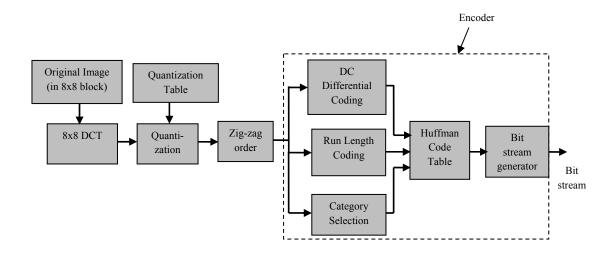

| Fig.2.4 | <ul><li>(a) Zig-zag ordering for DCT coefficients</li><li>(b) JPEG baseline Image compression</li></ul>                                                                                                                                    | 23<br>23                               |

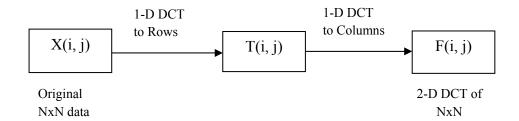

| Fig.2.5 | 2-D DCT from separable property                                                                                                                                                                                                            | 24                                     |

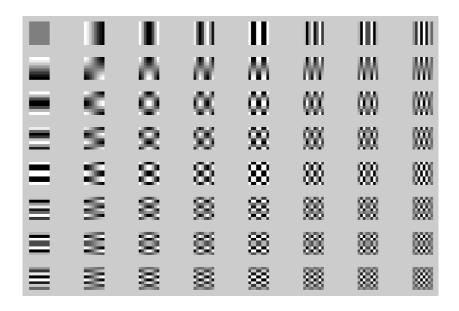

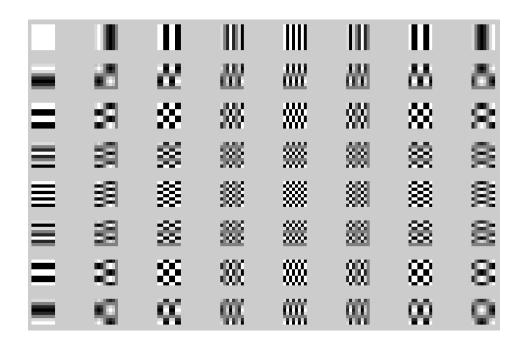

| Fig.2.6 | 64 basis functions image of an 8x8 2-D DCT matrix                                                                                                                                                                                          | 25                                     |

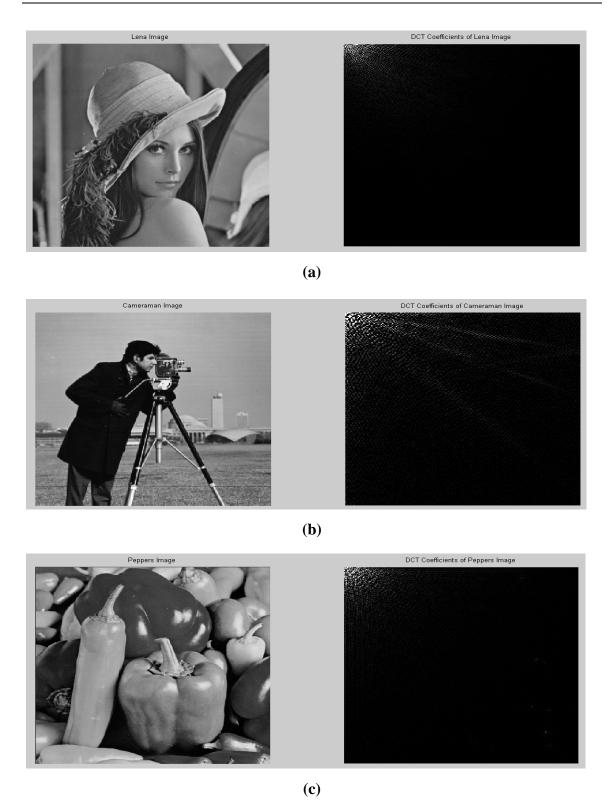

| Fig.2.7 | Energy compaction of DCT. Image (left) and its DCT coefficients image (right)                                                                                                                                                              |                                        |

|         | <ul><li>(a) 450x450 Lena,</li><li>(b) 256x256 Cameraman and</li><li>(c) 512x512 Peppers</li></ul>                                                                                                                                          | 26<br>26<br>26                         |

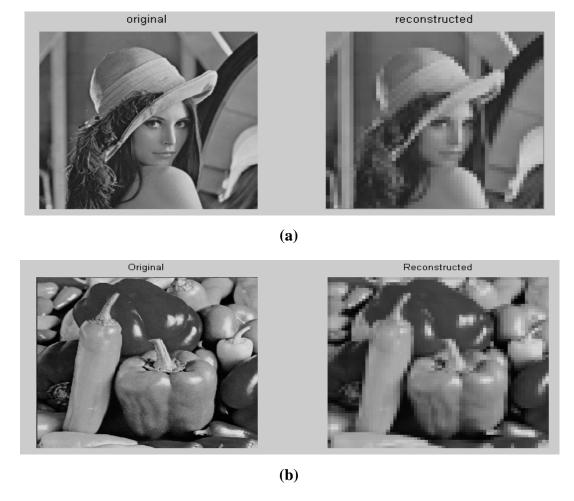

| Fig.2.8 | Original (left) and reconstructed (right) image after quantizing all AC coefficients of 8x8 DCT to zero                                                                                                                                    |                                        |

|         | <ul><li>(a) Lena and</li><li>(b) Peppers</li></ul>                                                                                                                                                                                         | 27<br>27                               |

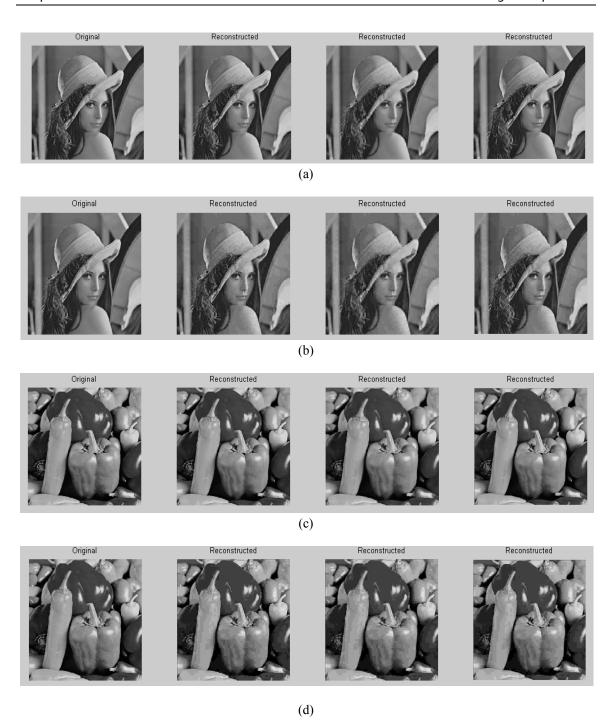

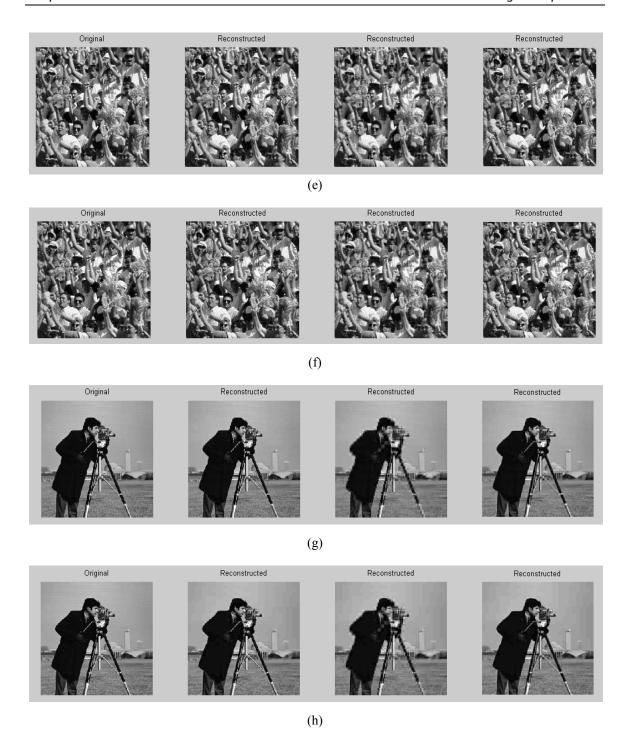

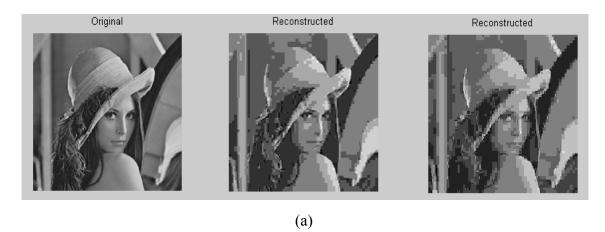

| Fig.2.9 | From left to right, original image, reconstructed image by taking all DCT coefficients, reconstructed image by taking first row and first column DCT coefficients, reconstructed image by taking first 15 coefficients in zig-zag order of |                                        |

|         | (a) 448x448 Lena, quality=1<br>(b) 448x448 Lena, quality=5<br>(c) 512x512 Peppers, quality=1<br>(d) 512x512 Peppers, quality=8<br>(e) 512x512 Crowd, quality=1<br>(f) 512x512 Crowd, quality=5<br>(g) 256x256 Cameraman, quality=1         | 29<br>29<br>29<br>29<br>30<br>30<br>30 |

|           | (h) 256x256, Cameraman, quality=3                                                                                            | 30       |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig.2.10  | Basis function image of SDHT                                                                                                 | 32       |

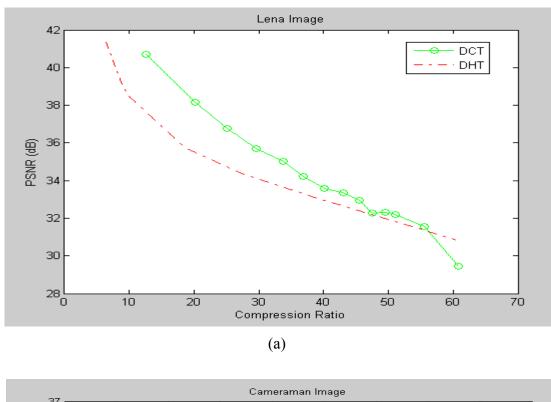

| Fig.2.11  | PSNR performance of SDHT and DCT for                                                                                         |          |

|           | <ul><li>(a) Lena image</li><li>(b) Cameraman image</li></ul>                                                                 | 33<br>33 |

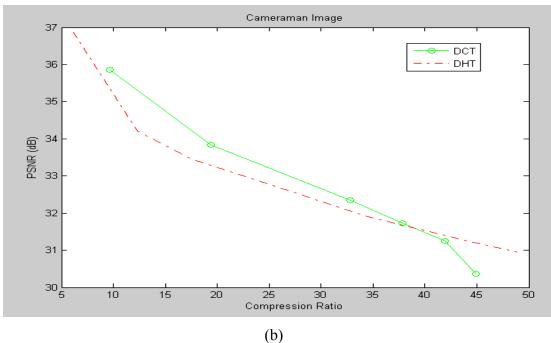

| Fig. 2.12 | Original (left), reconstructed image using DCT (middle) and reconstructed image using SDHT (right) at very high compressions | 34       |

|           | <ul><li>(a) Lena</li><li>(b) Cameraman</li></ul>                                                                             | 34<br>34 |

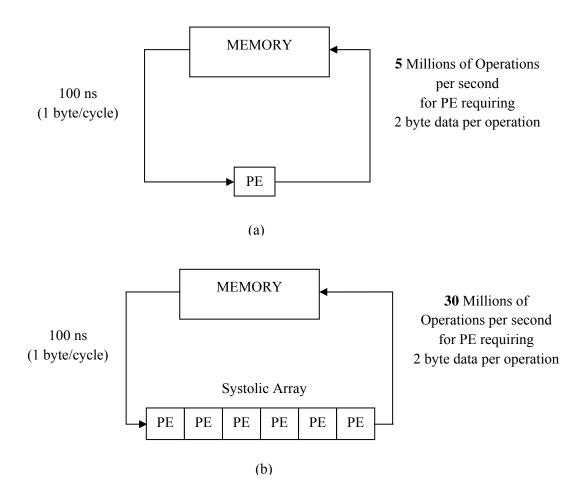

| Fig. 3.1  | Operations using                                                                                                             |          |

|           | <ul><li>(a) single processing element</li><li>(b) Systolic Array [42]</li></ul>                                              | 37<br>37 |

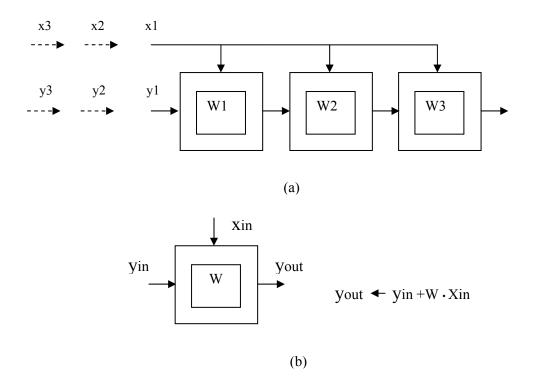

| Fig. 3.2  | <ul><li>(a) Systolic convolution array</li><li>(b) basic operations of one PE [42]</li></ul>                                 | 39<br>39 |

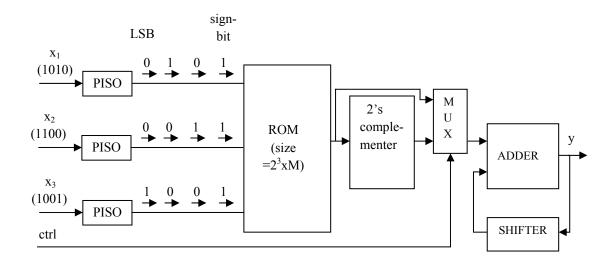

| Fig. 3.3  | Architecture of ROM based DA                                                                                                 | 42       |

| Fig. 3.4  | Architecture of ROM based DA using OBC technique                                                                             | 44       |

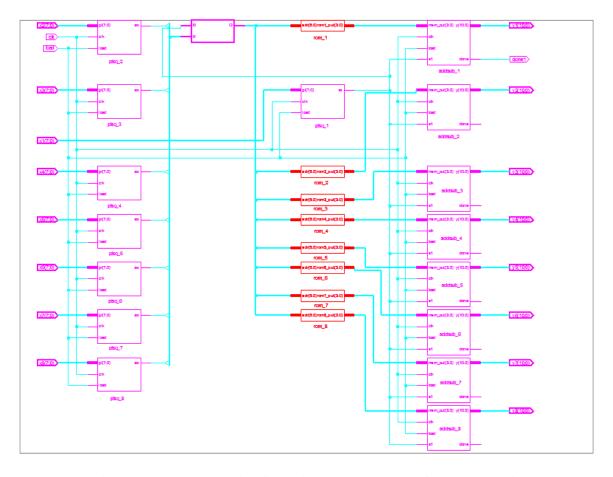

| Fig. 3.5  | RTL schematic of 8-points DHT using ROM based DA                                                                             | 46       |

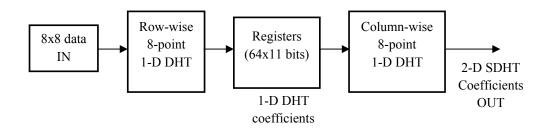

| Fig. 3.6  | Row-column decomposition technique for 2-D SDHT implementation                                                               | 46       |

| Fig. 3.7  | Hardware implementation in Xilinx FPGA of 8x8 data matrix Di through ChipScope Pro tool                                      | 48       |

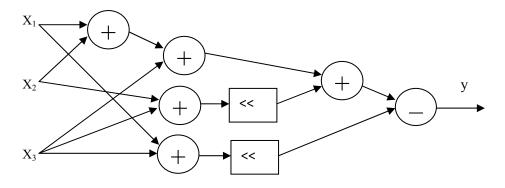

| Fig. 3.8  | Structure to realize the sum of vectors in the example using ROM free DA                                                     | 50       |

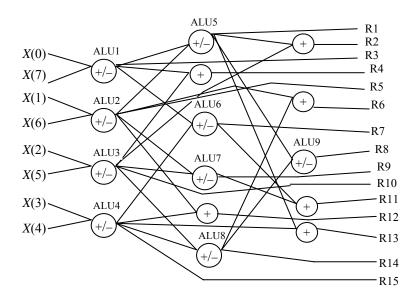

| Fig. 3.9  | Adder/subtractor structure to realize the 8-points DCT of equation (3.8) [58]                                                | 53       |

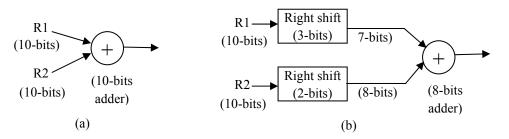

| Fig. 3.10 | Adder bit width reduction in ROM free DA to save area and power                                                              |          |

|           | <ul><li>(a) without shift</li><li>(b) with right shift</li></ul>                                                             | 55<br>58 |

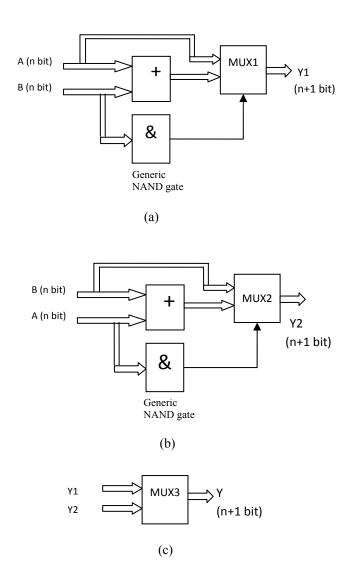

| Fig. 3.11 | Circuits to reduce sign extension error propagation when number is negative                                                  |          |

|           | <ul><li>(a) MUX1 selects A if B is -1 else sum of A and B</li><li>(b) MUX2 selects B if A is -1 else sum of A and B</li><li>(c) Final sum is from MUX1 or MUX2 output</li></ul> | 56<br>56<br>56 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

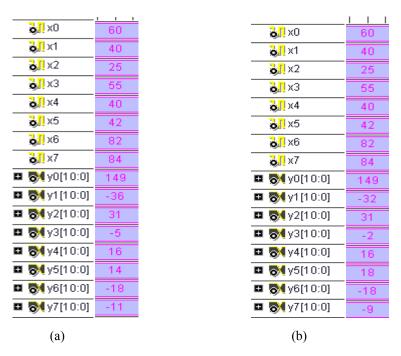

| Fig. 3.12 | VHDL simulation result using Xilinx ISE Simulator of data X for the Implementation of 1-D DCT architecture using                                                                |                |

|           | <ul><li>(a) simple addition operator</li><li>(b) proposed adder</li></ul>                                                                                                       | 57<br>57       |

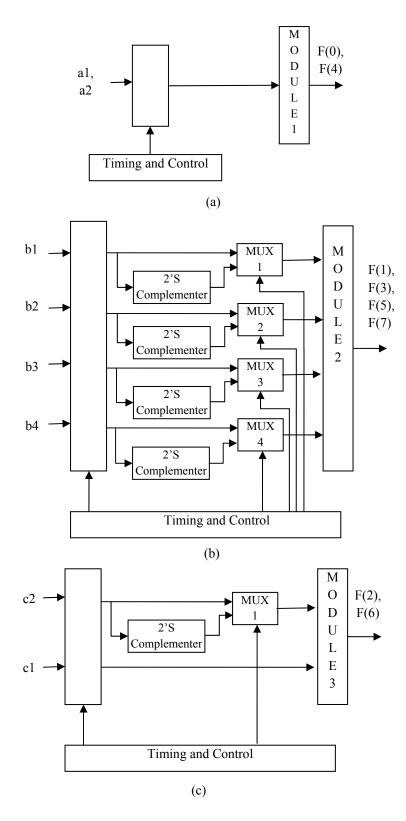

| Fig. 3.13 | VLSI architecture for computation of 8 point DCT in pipeline manner for                                                                                                         |                |

|           | <ul> <li>(a) computation of F(0) and F(4)</li> <li>(b) computation of F(1), F(3), F(5) and F(7)</li> <li>(c) computation of F(2) and F(6)</li> </ul>                            | 60<br>60<br>60 |

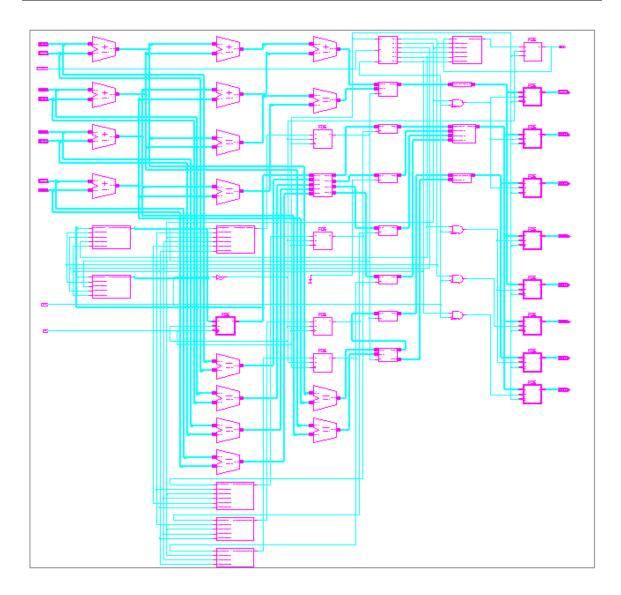

| Fig. 3.14 | RTL Schematic of Proposed 8-point 1-D DCT in Xilinx ISE 10.1                                                                                                                    | 62             |

| Fig. 3.15 | Adder/subtractor for all 8-points DHT coefficients calculation                                                                                                                  | 65             |

| Fig. 3.16 | Hardware implementation result of 8x8 image data matrix D <sub>i</sub> by proposed DA for DHT method                                                                            | 66             |

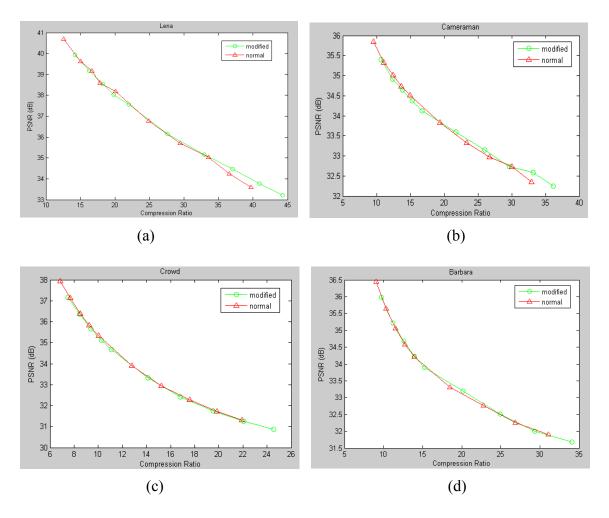

| Fig. 4.1  | PSNR against compression ratio for                                                                                                                                              |                |

|           | (a) 448x448 Lena                                                                                                                                                                | 70             |

|           | (b) 256x256 Cameraman,                                                                                                                                                          | 70             |

|           | (c) 512x512 Crowd<br>(d) 512x512 Barbara Images                                                                                                                                 | 70<br>70       |

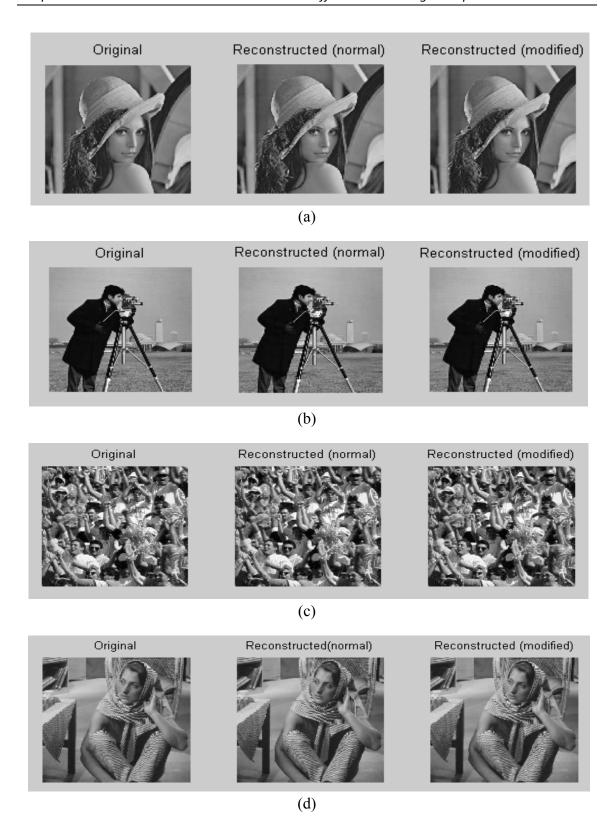

| Fig. 4.2  | Original and reconstructed images using normal quantization matrix and modified matrix                                                                                          |                |

|           | (a) 448x448 Lena                                                                                                                                                                | 71             |

|           | (b) 256x256 Cameraman                                                                                                                                                           | 71             |

|           | (c) 512x512 Crowd<br>(d) 512x512 Barbara                                                                                                                                        | 71<br>71       |

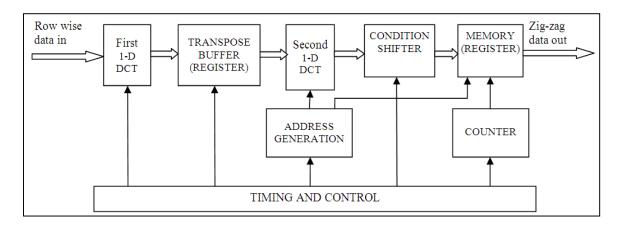

| Fig. 4.3  | DCT to Zig-zag re-ordering Architecture                                                                                                                                         | 72             |

|           | DCT to Zig-zag re-ordering Architecture                                                                                                                                         | 12             |

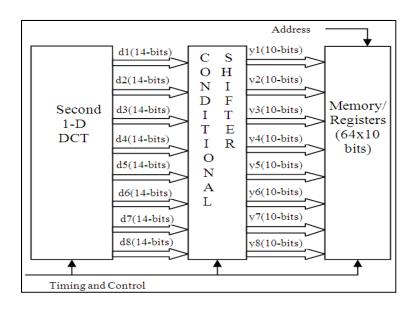

| Fig. 4.4  | 2-D DCT Coefficients storage in 64x10 bits registers after shifting                                                                                                             | 73             |

| Fig. 4.5  | MATLAB Simulation results for 2-D DCT of sample data $D_s$                                                                                                                      | 77             |

| Fig. 4.6  | Quantized and zig-zag ordered coefficients of $D_s$ (arranged in left to right and top to bottom order)                                                                         | 77             |

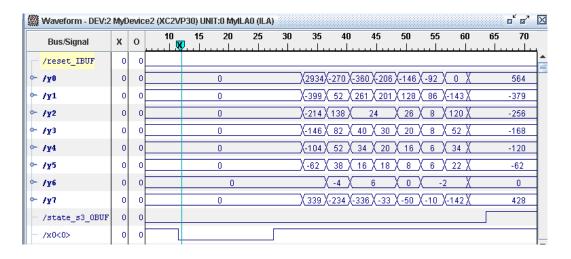

| Fig. 4.7  | 2-D DCT coefficients of <i>D</i> <sub>s</sub> obtained through Xilinx ChipScope Logic Analyzer               | 77             |

|-----------|--------------------------------------------------------------------------------------------------------------|----------------|

| Fig. 4.8  | Quantized and Zig-zag ordered 2-D DCT coefficients of $D_s$ obtained through Xilinx ChipScope Logic Analyzer | 78             |

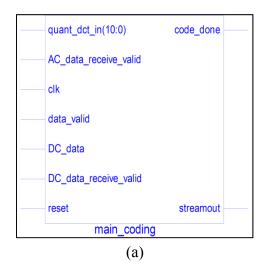

| Fig. 4.9  | Coding Sequence of DCT coefficients in JPEG                                                                  | 79             |

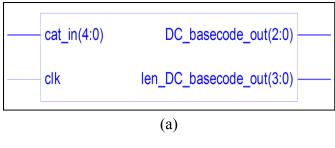

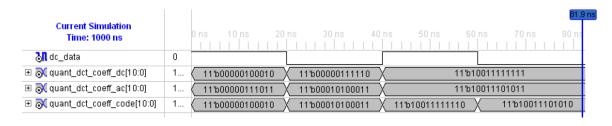

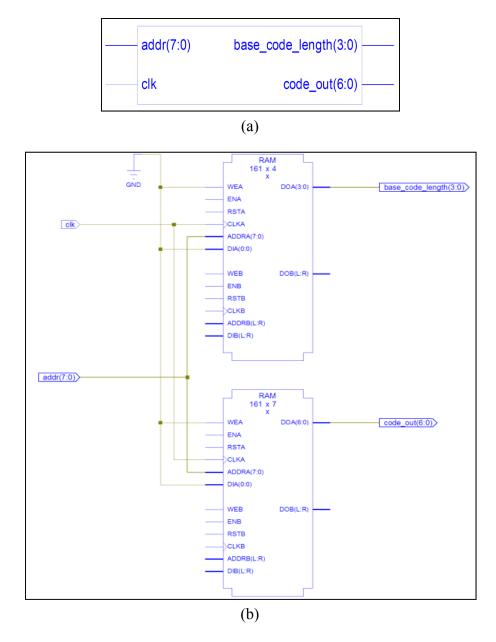

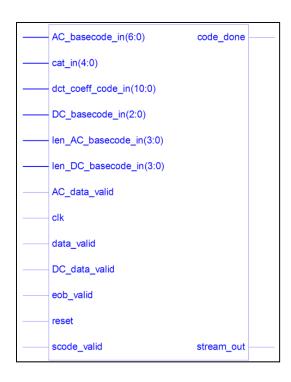

| Fig. 4.10 | RTL Schematic of Huffman Coding implemented in Xilinx FPGA                                                   |                |

|           | <ul><li>(a) Top module</li><li>(b) Detail schematic</li></ul>                                                | 80<br>80       |

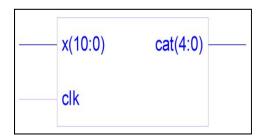

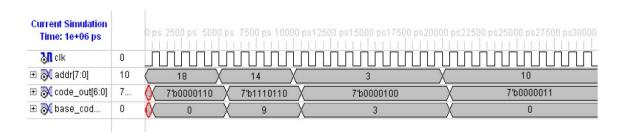

| Fig. 4.11 | Top Level Interface of Category selection module                                                             | 81             |

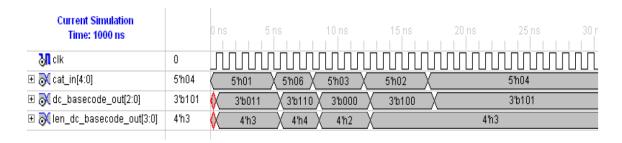

| Fig. 4.12 | Simulation output of Category selection module                                                               | 81             |

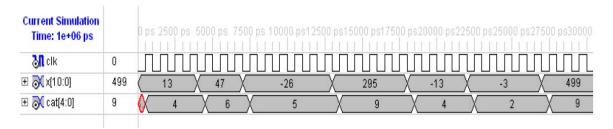

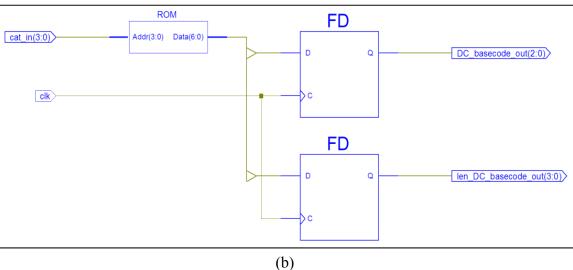

| Fig. 4.13 | RTL Schematic of DC base code module                                                                         |                |

|           | <ul><li>(a) Top interface</li><li>(b) Details</li></ul>                                                      | 82<br>82       |

| Fig. 4.14 | Simulation result of DC base code module                                                                     | 82             |

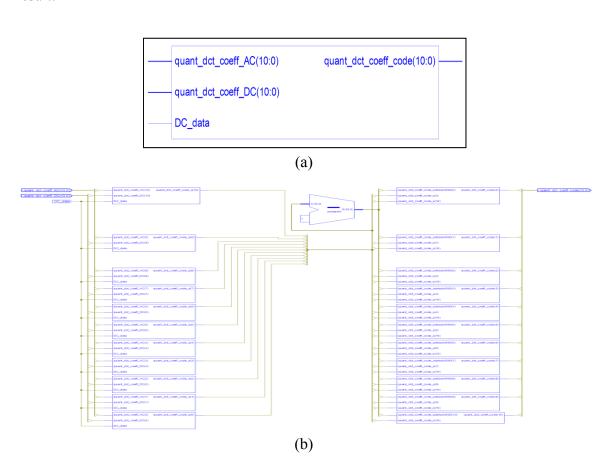

| Fig. 4.15 | RTL Schematic of DCT Coefficient code module                                                                 |                |

|           | <ul><li>(a) Top interface</li><li>(b) Details</li></ul>                                                      | 83<br>83       |

| Fig. 4.16 | Simulation result of DCT coefficient code module                                                             | 83             |

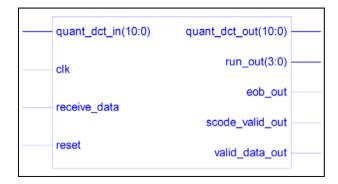

| Fig. 4.17 | RTL Schematic of Run Module (top view)                                                                       | 84             |

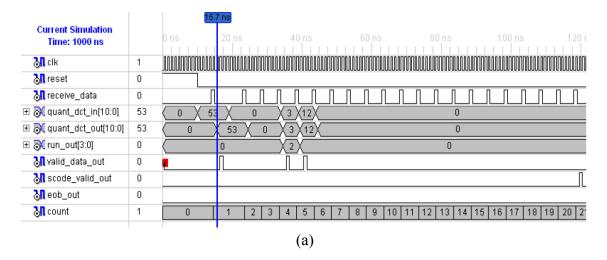

| Fig. 4.18 | Simulation result of run module for received AC coefficients                                                 |                |

|           | (a) 1 to 21<br>(b) 22 to 45<br>(c) 46 to 63                                                                  | 84<br>85<br>85 |

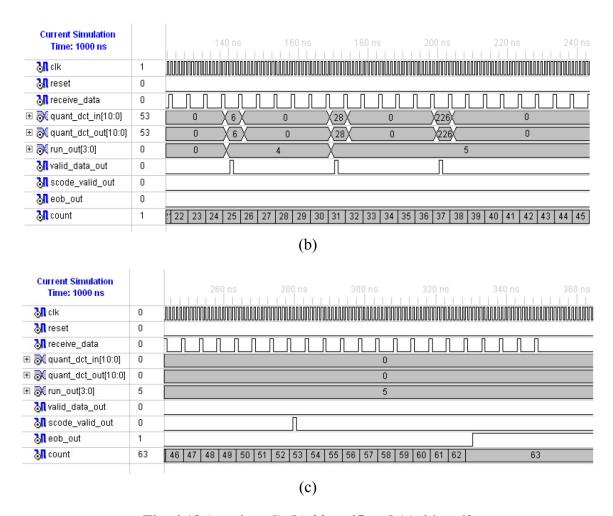

| Fig. 4.19 | RTL Schematic of Address formation module                                                                    |                |

|           | <ul><li>(a) top view</li><li>(b) detail view</li></ul>                                                       | 86<br>86       |

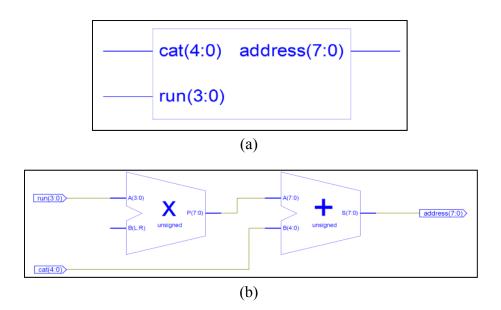

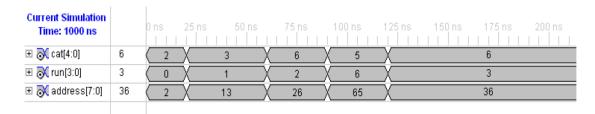

| Fig. 4.20 | Simulation result from address formation module                                                              | 86             |

| Fig. 4.21 | RTL Schematic of Memory module for AC base code storage                                                      |                |

|           | <ul><li>(a) top view</li><li>(b) detail view</li></ul>                                                       | 87<br>87       |

| Fig. 4.22 | Simulation result from AC base code memory module                                                            | 87             |

| Fig. 4.23 | RTL Schematic of control module (top view)                                                                                  | 89       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----------|

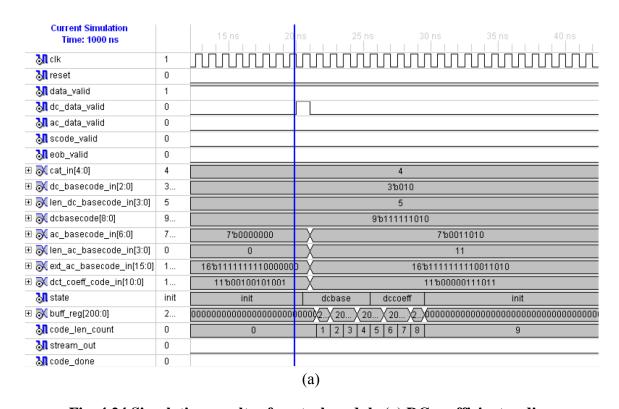

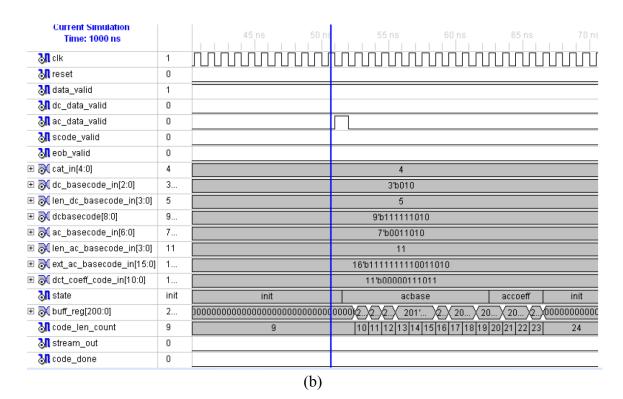

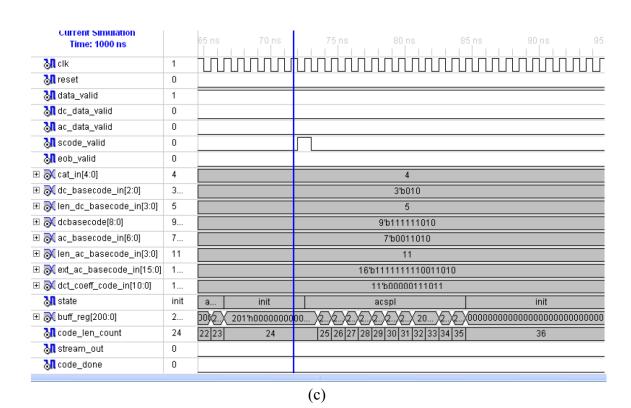

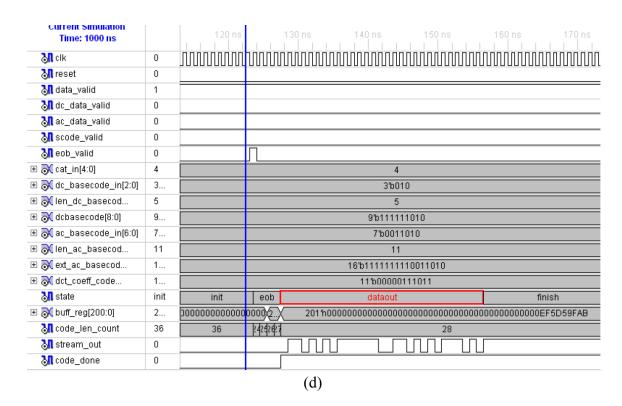

| Fig. 4.24 | Simulation results of control module                                                                                        |          |

|           | (a) DC coefficient coding                                                                                                   | 89       |

|           | (b) AC coefficient coding                                                                                                   | 90       |

|           | (c) Special code                                                                                                            | 90       |

|           | (d) Buffered Output as bit stream                                                                                           | 91       |

| Fig. 4.25 | Macro Statistics of Advance HDL Synthesis of<br>Complete Huffman Coding                                                     | 91       |

| Fig. 5.1  | 2-D DCT computation                                                                                                         |          |

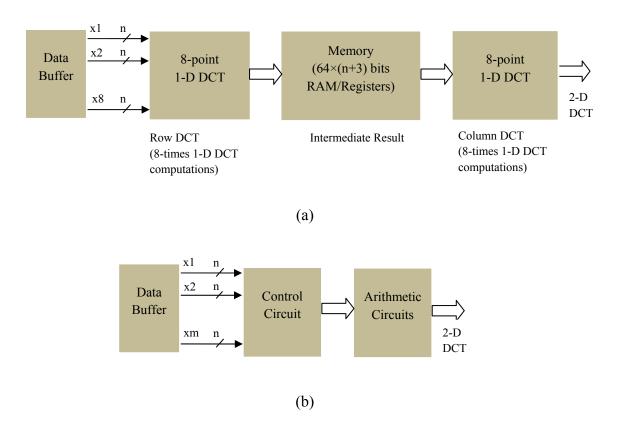

|           | <ul><li>(a) using 1-D DCT and transposition memory</li><li>(b) without transposition memory</li></ul>                       | 96<br>96 |

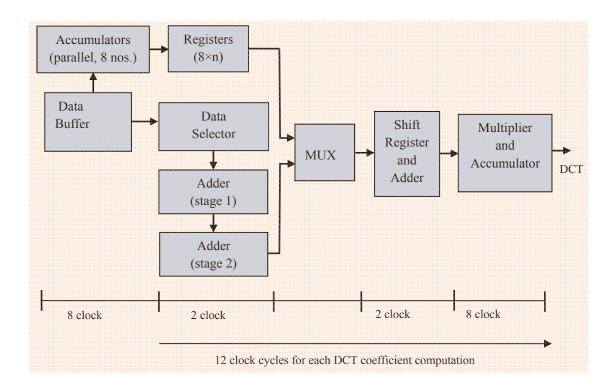

| Fig. 5.2  | Architectural components of direct 2-D DCT computation                                                                      | 102      |

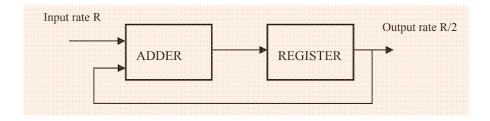

| Fig. 5.3  | Adder and shifter stage in the architecture                                                                                 | 103      |

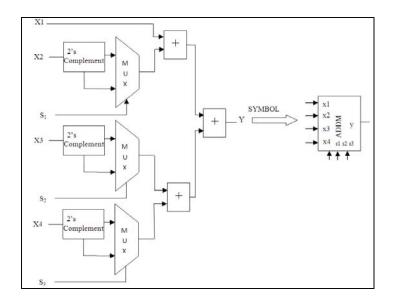

| Fig. 5.4  | A basic cell to add four inputs with different sign                                                                         | 104      |

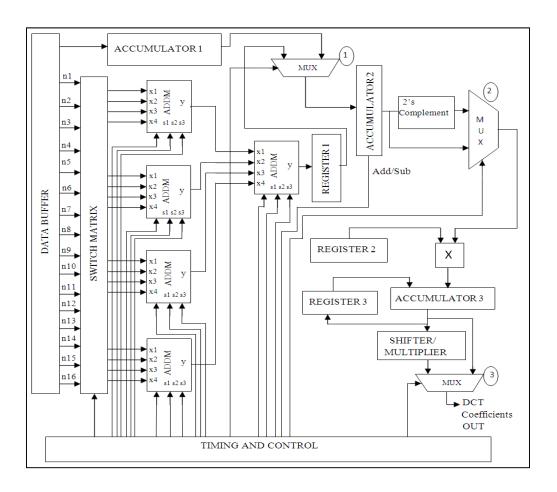

| Fig. 5.5  | Proposed non-recursive VLSI architecture for the direct computation of 2-D DCT                                              | 104      |

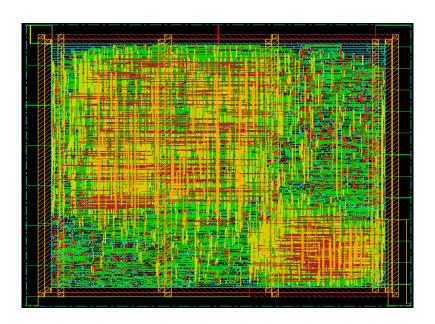

| Fig. 5.6  | Layout of proposed 2-D DCT design with 64x8 bits registers for the data buffer                                              | 107      |

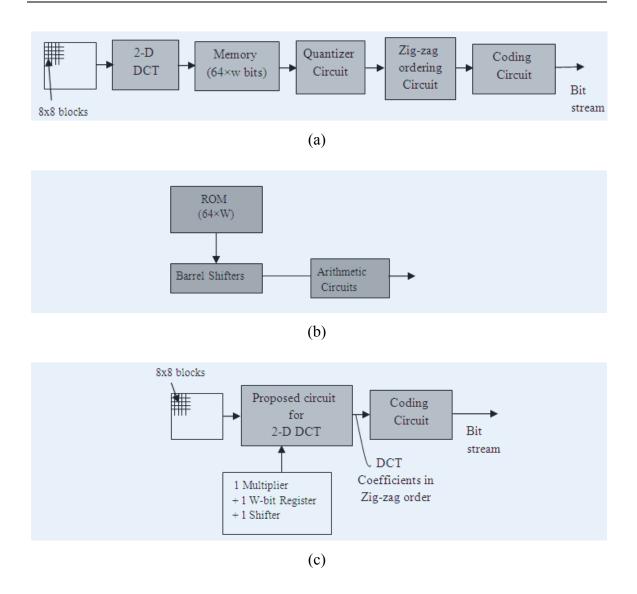

| Fig. 5.7  | JPEG Image and MPEG video compression flow with                                                                             |          |

|           | (a) general DCT model                                                                                                       | 108      |

|           | (b) quantizer circuit                                                                                                       | 108      |

|           | (c) proposed DCT model                                                                                                      | 108      |

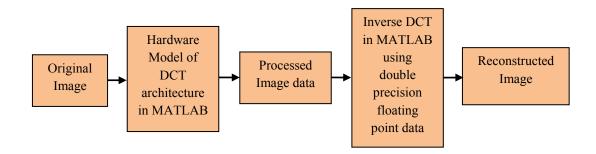

| Fig. 5.8  | Image processing using proposed 2-D DCT architecture model in MATLAB                                                        | 109      |

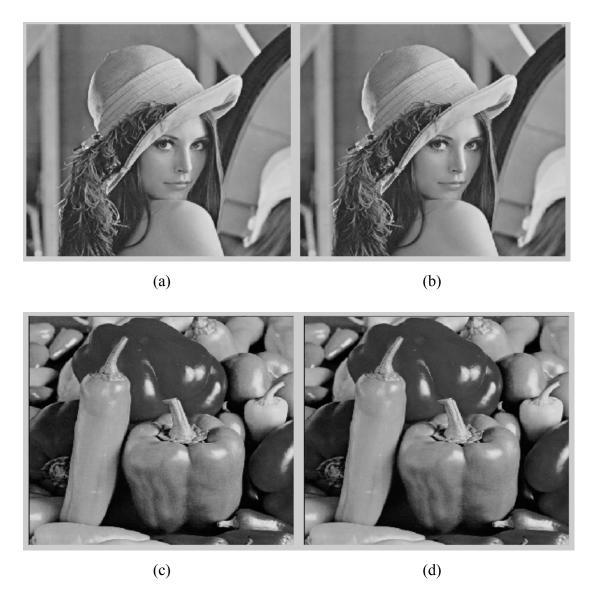

| Fig. 5.9  | Original, (a) and (c), and reconstructed,<br>(b) and (d), images using proposed<br>non-recursive 2-D DCT architecture model | 110      |

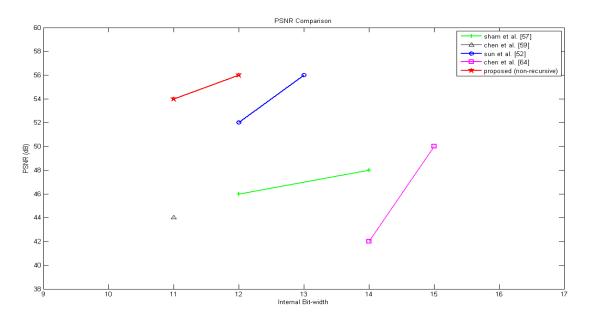

| Fig. 5.10 | PSNR with different internal bit-width precision used                                                                       | 111      |

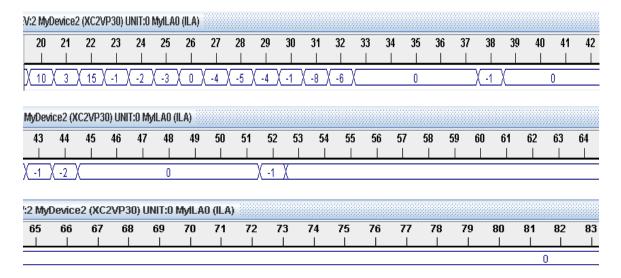

| Fig. 5.11 | Zig-zag order DCT coefficients                                                                                              |          |

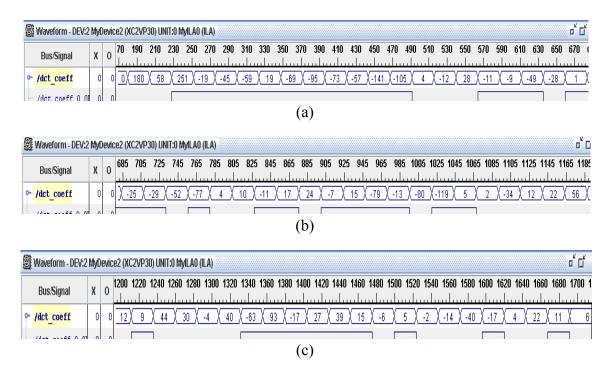

|           | (a) 1 to 21                                                                                                                 | 112      |

|           | (b) 22 to 42                                                                                                                | 112      |

|           | (c) 43 to 64                                                                                                                | 112      |

|           | obtained from Xilinx xc2vp30 device using ChipScope                                                                         |          |

|           | pro logic analyzer                                                                                                          |          |

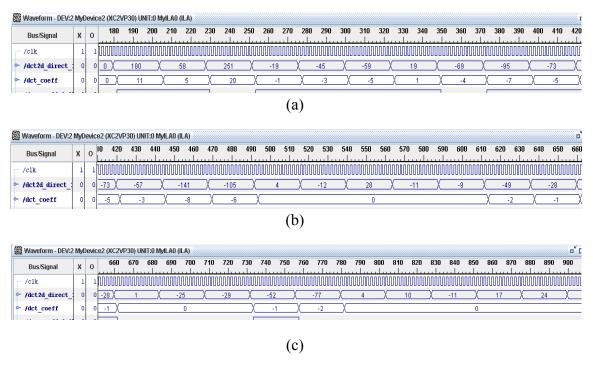

| Fig. 5.12 | Zig-zag ordered DCT coefficients along with Quantization              |     |

|-----------|-----------------------------------------------------------------------|-----|

|           |                                                                       | 112 |

|           | (a) 1 to 10                                                           | 113 |

|           | (b) 11 to 20                                                          | 113 |

|           | (c) 21 to 30                                                          | 113 |

|           | (d) 31 to 40                                                          | 114 |

|           | (e) 41 to 51                                                          | 114 |

|           | (f) 51 to 64                                                          | 114 |

|           | obtained from Xilinx xc2vp30 device                                   |     |

|           | using ChipScope pro logic analyzer                                    |     |

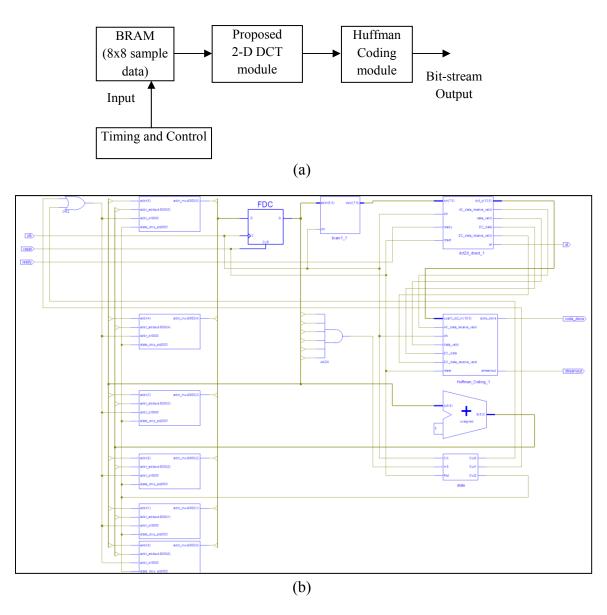

| Fig.5.13  | Architecture of JPEG compression using proposed non-recursive 2-D DCT |     |

|           | (a) block diagram                                                     | 115 |

|           | (b) RTL Schematic in Xilinx                                           | 115 |

|           | (b) KTE Schematic in Annix                                            | 113 |

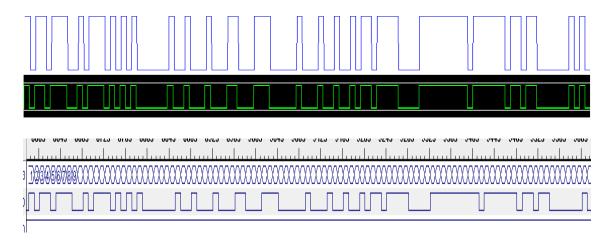

| Fig.5.14  | Bit stream of 8x8 sample JPEG processed data                          | 116 |

| 1 18.0.11 | using non-recursive 2-D DCT architecture model                        | 110 |

|           | in MATLAB (top), VHDL simulation (middle) and                         |     |

|           | \ <b>1</b> //                                                         |     |

|           | Hardware output through Xilinx ChipScope Pro (bottom)                 |     |

# List of Tables

| TABLE 2.1  | COMPRESSION RATIO OBTAINED FOR DIFFERENT QUANTIZATION LEVEL                                                                     | 28 |

|------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 2.2  | PSNR AND COMPRESSION RATIOS OF IMAGES SHOWN IN FIG.2.12                                                                         | 34 |

| TABLE 3.1  | ROM CONTENTS FOR THREE 4-BITS INPUTS                                                                                            | 41 |

| TABLE 3.2  | ROM CONTENTS FOR THREE 4-BITS INPUTS IN OBC TECHNIQUE                                                                           | 44 |

| TABLE 3.3  | DEVICE UTILIZATION FOR THE FPGA IMPLEMENTATION OF 8-POINT DHT USING ROM BASED DA                                                | 45 |

| TABLE 3.4  | FUNCTIONS OF EACH ALU FOR DIFFERENT DCT COEFFICIENTS [58]                                                                       | 54 |

| TABLE 3.5  | DEVICE UTILIZATION FOR THE FPGA IMPLEMENTATION OF 8-POINT 1-D DCT                                                               | 58 |

| TABLE 3.6  | AREA AND POWER COMPARISONS FOR SYNOPSYS DC IMPLEMENTATION OF 1-D DCT                                                            | 58 |

| TABLE 3.7  | (a) Pipeline Computation of DCT Coefficients $F(0)$ and $F(4)$                                                                  | 61 |

|            | (b) Pipeline Computation of DCT Coefficients $F(1)$ , $F(3)$ , $F(5)$ and $F(7)$                                                | 61 |

|            | (c) Pipeline Computation of DCT Coefficients $F(2)$ and $F(6)$                                                                  | 61 |

| TABLE 3.8  | DEVICE UTILIZATION FOR THE FPGA IMPLEMENTATION OF 8-POINT 1-D DCT                                                               | 62 |

| TABLE 3.9  | AREA AND POWER COMPARISONS FOR SYNOPSYS DC IMPLEMENTATION OF 8-POINT 1-D DCT                                                    | 63 |

| TABLE 3.10 | Device Utilization Summary for 2-D DCT Implementation Using Row-Column Decomposition Technique of Proposed 1-D DCT Architecture | 63 |

| TABLE 3.11 | 2-D DCT Architecture Implementation Area and Power USING Row-Column Decomposition Technique of Proposed 1-D DCT                 | 63 |

| TABLE 3.12 | FUNCTIONS OF EACH ALU FOR DIFFERENT DHT COEFFICIENTS                                                                            | 65 |

| TABLE 3.13 | COMPARISON OF ADDERS OF DHT AND DCT IN [58]                                                                                     | 66 |

| TABLE 3.14 | HARDWARE UTILIZATION FOR PROPOSED DA FOR 1-D DHT                                                                                | 66 |

| TABLE 4.1  | ZIG-ZAG ORDER SEQUENCE MATRIX                                                                                                   | 72 |

| TABLE 4.2  | CLOCK CYCLE OPERATIONS FOR THE COMPUTATION OF 2-D DCT                                                                           | 74 |

| TABLE 4.3    | MEMORY BITS AND LATENCY COMPARISONS FOR THE QUANTIZATION AND ZIG-ZAG BUFFER IN PROPOSED HARDWARE SCHEME WITH EXISTING | 74  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 4.4    | MEMORY/REGISTERS SAVINGS ACHIEVED IN PROPOSED DCT TO ZIG-ZAG ARCHITECTURE                                             | 74  |

| TABLE 4.5    | Hardware utilization power dissipation for DCT to Zig-zag ordering architecture implemented in $FPGA$                 | 75  |

| TABLE 4.6    | HARDWARE UTILIZATION POWER DISSIPATION FOR DCT TO ZIG-ZAG ORDERING ARCHITECTURE IMPLEMENTED IN ASIC LIBRARY           | 76  |

| TABLE 4.7    | CATEGORY OF DCT COEFFICIENTS                                                                                          | 79  |

| TABLE 4.8    | DESIGN SUMMARY OF HUFFMAN CODING IMPLEMENTED IN FPGA                                                                  | 92  |

| TABLE 4.9    | COMPARISON OF PROPOSED HUFFMAN CODING IMPLEMENTATION IN TERMS OF TOTAL MEMORY USES IN TABLE STORAGE                   | 93  |

| TABLE 4.10   | COMPARISON OF PROPOSED HUFFMAN CODING IMPLEMENTATION IN TERMS OF NO. OF BITS PER AC TABLE ENTRIES                     | 93  |

| TABLE 5.1    | SHORT NOTATIONS OF IMAGE DATA VALUES                                                                                  | 98  |

| TABLE 5.2    | SHORT NOTATIONS OF TERMS                                                                                              | 100 |

| TABLE 5.3    | ACCUMULATOR VALUES AND COSINE ANGLES REQUIRED IN GENERALISED EQUATION (5.7) FOR ALL AC COEFFICIENTS CALCULATION       | 101 |

| TABLE 5.4    | ANGLE GROUP VALUES USED IN TABLE 5.3                                                                                  | 102 |

| TABLE 5.5    | COMPARISON OF DIFFERENT 2-D DCT ARCHITECTURES                                                                         | 106 |

| TABLE 5.6    | FPGA IMPLEMENTATION AND COMPARISON RESULT OF PROPOSED NON-RECURSIVE 2-D DCT ARCHITECTURE WITH DA                      | 111 |

| TABLE 5.7    | FPGA IMPLEMENTATION RESULTS OF COMPLETE JPEG USING PROPOSED NON-RECURSIVE 2-D DCT                                     | 116 |

| TABLE A.1    | BASE CODES FOR DC COEFFICIENTS                                                                                        | 121 |

| TABLE A.2    | BASE CODES FOR AC COEFFICIENTS                                                                                        | 122 |

| Symbols Used |                                                                                                                       |     |

| Name         | Symbol                                                                                                                |     |

| Number       | #                                                                                                                     |     |

#### **Abstract**

An image, in its original form, contains huge amount of data which demands not only large amount of memory requirements for its storage but also causes inconvenient transmission over limited bandwidth channel. Image compression reduces the data from the image in either lossless or lossy way. While lossless image compression retrieves the original image data completely, it provides very low compression. Lossy compression techniques compress the image data in variable amount depending on the quality of image required for its use in particular application area. It is performed in steps such as image transformation, quantization and entropy coding. JPEG is one of the most used image compression standard which uses discrete cosine transform (DCT) to transform the image from spatial to frequency domain. An image contains low visual information in its high frequencies for which heavy quantization can be done in order to reduce the size in the transformed representation. Entropy coding follows to further reduce the redundancy in the transformed and quantized image data.

Real-time data processing requires high speed which makes dedicated hardware implementation most preferred choice. The hardware of a system is favored by its low-cost and low-power implementation. These two factors are also the most important requirements for the portable devices running on battery such as digital camera. Image transform requires very high computations and complete image compression system is realized through various intermediate steps between transform and final bit-streams. Intermediate stages require memory to store intermediate results. The cost and power of the design can be reduced both in efficient implementation of transforms and reduction/removal of intermediate stages by employing different techniques.

The proposed research work is focused on the efficient hardware implementation of transform based image compression algorithms by optimizing the architecture of the system. Distribute arithmetic (DA) is an efficient approach to implement digital signal processing algorithms. DA is realized by two different ways, one through storage of precomputed values in ROMs and another without ROM requirements. ROM free DA is more efficient. For the image transform, architectures of one dimensional discrete Hartley transform (1-D DHT) and one dimensional DCT (1-D DCT) have been optimized using ROM free DA technique. Further, 2-D separable DHT (SDHT) and 2-D DCT

architectures have been implemented in row-column approach using two 1-D DHT and two 1-D DCT respectively.

A finite state machine (FSM) based architecture from DCT to quantization has been proposed using the modified quantization matrix in JPEG image compression which requires no memory in storage of quantization table and DCT coefficients. In addition, quantization is realized without use of multipliers that require more area and are power hungry.

For the entropy encoding, Huffman coding is hardware efficient than arithmetic coding. The use of Huffman code table further simplifies the implementation. The strategies have been used for the significant reduction of memory bits in storage of Huffman code table and the complete Huffman coding architecture encodes the transformed coefficients one bit per clock cycle.

Direct implementation algorithm of DCT has the advantage that it is free of transposition memory to store intermediate 1-D DCT. Although recursive algorithms have been a preferred method, these algorithms have low accuracy resulting in image quality degradation. A non-recursive equation for the direct computation of DCT coefficients have been proposed and implemented in both 0.18 µm ASIC library as well as FPGA. It can compute DCT coefficients in any order and all intermediate computations are free of fractions and hence very high image quality has been obtained in terms of PSNR. In addition, one multiplier and one register bit-width need to be changed for increasing the accuracy resulting in very low hardware overhead. The architecture implementation has been done to obtain zig-zag ordered DCT coefficients. The comparison results show that this implementation has less area in terms of gate counts and less power consumption than the existing DCT implementations. Using this architecture, the complete JPEG image compression system has been implemented which has Huffman coding module, one multiplier and one register as the only additional modules. The intermediate stages (DCT to Huffman encoding) are free of memory, hence efficient architecture is obtained.

# Chapter 1

## Introduction

An image in its original representation carries huge amount of data. Thus, it requires large amount of memory for storage [1]. Image compression is an important area in image processing which efficiently removes the visually insignificant data [2–8]. Compressed images are sent over limited bandwidth channel with some additional processing for robust (error free) transmission [9–12]. Transform based image compression algorithm is a most preferred choice which consists of image transform (in non-overlapping blocks), quantization of transformed coefficients and entropy coding [13]. Joint photographic expert group (JPEG) is a committee that standardizes the image compression algorithm [14]. The 8x8 block-wise two-dimensional discrete cosine transform (2-D DCT) is used as orthogonal transform in JPEG image compression [15]. Images compressed by this standard are used globally. This algorithm provides the user to choose between amount of compression and quality as per the requirement of the image in different applications. The variable amount of compression makes this algorithm very much suitable for the transmission purpose as user can adjust the bit rate of the transmission according to channel capacity.

JPEG is fixed algorithm and it has some flexibility that can be incorporated easily without any major changes in the basic structural feature [16–18]. JPEG system can be implemented in software as well as in hardware. Software solution is not promising for the applications requiring high speed. Therefore, real-time processing is done through the dedicated hardware [19,20]. In custom hardware implementation, architecture plays a vital role in deciding area, power and throughput of the design. Architecture optimizations lead to lower computational units (adders, multipliers), reduced memory size for storage of temporary variables and smaller interconnects. Architecture explorations to minimize the area and power consumption is a issue for portable devices running on battery. Low silicon area reduces the cost of the appliance [21,22] and low

power consumption increases the battery lifetime (time between recharges for chargeable battery) which in turn reduces the weight of the battery and overall size [23]. 2-D DCT is a complex algorithm and requires high computations. Further, subsequent stages in transform based image compression require high memory storage along with arithmetic circuits. For portable devices, having image compression system (like JPEG compression in digital camera [24–27]), low-cost design, that can be achieved by reducing silicon area is highly required [28–31]. By efficiently designing the hardware architecture, image compression can be performed with low-cost and low power budget.

#### 1.1 Motivation

System level implementation of a digital device can be performed in embedded processors, digital signal processors (DSPs), application specific instruction set processors (ASIPs), reconfigurable logic/processors and dedicated hardware. Each implementation gives best performance for a particular application area. Unlike embedded processors, where low cost and low power consumption are basic requirements, price and performance of DSP processors vary according to application areas. They come in three categories, i.e., low cost, low power midrange and diversified high end. In the high end category, ultra high speed applications are implemented in DSPs [32]. ASIPs are designed for a particular application area. Their hardware and instruction-set may be optimized for power, area or performance. In terms of power consumption and hardware cost ASIPs are intermediate between general purpose processors (GPPs) and application specific integrated circuits (ASICs) [33–36].

Although processors, mentioned above, have flexibility that their functionality can be modified by changing the soft codes without any hardware modifications unless major changes (like throughput improvement by adding hardware in parallel or pipeline manner) are required, it (flexibility) comes at the cost of lower energy efficiency. Fig.1.1 depicts the energy efficiency of various implementations with respect to the flexibility. Reconfigurable processors provide the functionality of a hardware accelerator by assembling a number of functional units on temporal basis through configurable interconnect and configurable bus of the processor. Thus, when accelerator work is finished, the same functional units can be used for other applications, unlike dedicated

Fig.1.1 Energy efficiency on different implementations[23]

accelerator in DSPs which brings additional hardware overhead. FPGA is used for this purpose [23]. DSP processors are traditionally used inside the digital camera. Nevertheless, it requires the hardware processor and memory to store soft codes. Since the JPEG is a standard and changes in it is rare (and almost none), dedicated hardware for the JPEG compression in a digital camera is a promising solution because of the following reasons. Dedicated hardware possesses the maximum energy efficiency as compared to embedded processors, DSPs and reconfigurable hardwares, that increase the battery life time between recharges and has the low silicon area. It is important in camera (and in all consumer electronic appliances) because silicon area directly relates to cost of the device. In battery perspective, there is a constant annual growth of battery capacity in tune with the technology evolutions that enabled the battery volume shrinkage and also good talk-time for first WCDMA phones (Fig.1.2) [37]. But, for multimedia space (very high computation is involved) there is need to reduce power as battery capacity is not enough to meet the computations. Dedicated hardware has high speed which is necessary for the digital camera (and in all real time applications) where images are captured, compressed and stored in a pipeline manner in real time. Efficient design strategy of the dedicated hardware system can lead to reduction in power demanding computational units such as adders and multipliers [38]. An image processing system requires high storage (memory) elements. Moreover, memory related operations dominate the system

Fig.1.2 Trends in power consumption and battery capacity [37]

power consumption [39,40]. Techniques can be used for well defined system to reduce the memory and hence power consumption [41].

## 1.2 Background

Systolic architecture is used to implement digital signal processing and arithmetic algorithms in which fast processing is required. It was the preferred design approach for the special purpose systems because of its simple, regular and pipeline operations performed by set of small interconnected similar array cells called processing elements (PEs). Breaking the whole processing into small cells has the two major advantages. In case of systolic architecture, a set of data brought from the memory is processed by several PEs in a pipeline structure i.e., multiple operations are performed on each data item. Therefore, computation is increased at the same memory bandwidth [42]. One example for systolic array is given by H.T. Kung [42], where convolution operation were mapped on systolic array. A major area and power consuming module in VLSI is multiplier. Past research in the implementation of any DSP algorithm using systolic array was centered on the reduction of the number of multipliers. In many literatures, DCT is implemented by systolic array architectures with the purpose of reducing number of

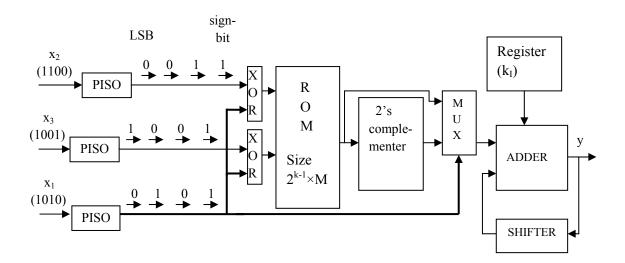

multipliers [43-48]. Apart from systolic, other DCT implementations also favored the multiplier reduction. H. Malvar [49] implemented DCT using DHT with reduced number of multipliers. Y.-M. Chin et al. [50] proposed a new convolution based algorithm for computing DCT. Still, all these algorithms are not free of multipliers, i.e. they need multipliers along with adders and other logic components for the VLSI implementation. Distributed arithmetic (DA) algorithm can implement DSP algorithms without multipliers, which is important for area and power savings in VLSI designs. For DA implementation of inner product of arrays, one of the inputs should be constant array. ROM based DA relies on the manual pre-computations of constants and their storage in ROM. These pre-computed values are fetched from the ROM addressed by the input bits. According to S.A. White [51], by careful design one may reduce the total gate count in a signal processing arithmetic unit upto 80 percent. ROM based DA is utilized for DCT implementations in literatures [52-54]. ROM based design is not preferred choice in VLSI because ROM has slow speed (ROM access time) and more power consumption [55,56]. Moreover, size of memory (ROM) has to be increased exponentially with the size of transform and also high accuracy requirements. ROM free DA architecture exploits the sparse nature of matrix formed by binary representation of coefficients (most places are zero) in contrast to pre-computing and storing them in ROM based DA i.e., constant coefficients are distributed. Shams et. al, [57] first gave the analysis of ROM free DCT and named the algorithm NEDA (New DA). The reduced adder tree of ROM free DA is implemented by P. Chungan et al. [58]. Yuan-Ho Chen et al. [59] proposed high throughput DCT architecture using DA which uses less number of bit-width in DA precision for hardware reduction.

For 2-D DCT implementation from 1-D DCT using techniques mentioned above requires transposition memory resulting in high cost design along with irregular architecture for realization of data pipelined computation [60]. Also, row-column decomposition technique is unsuitable for the applications requiring transmission in limited bandwidth as all DCT coefficients need to be calculated in advance for sending, though it is sent one by one. To reduce the circuit cost, direct recursive computation of 2-D DCT is carried out using recursive kernel in which DCT coefficients are computed one by one at regular clock cycles [61–67]. The disadvantage of recursive kernel is that

accuracy is reduced to a large extent due to round-off error. More errors are introduced as recursive cycle increases because each processed register values requires higher number of bits for its representation and fixed size of register in VLSI makes it non-practical.

Quantization and Huffman coding are the other parts in the image compression system which requires huge storage and controlling circuitry. Quantization is division of 2-D DCT coefficients with a quantization step-size (different for different DCT coefficients in 8x8 blocks). Zig-zag ordering [15] has to be performed of the quantized DCT coefficients to encode the most important image information contents first. Hardware implementation of complete JPEG image compression is done in literatures [19], [68–71]. For the Huffman coding in JPEG compression, JPEG committee provides an optimized table (having codes for DCT coefficients) for the Huffman code. These tables need to be stored in memory. M. Kovac et al. [69], have implemented quantization with 16-bit multiplier and RAM. M. Kovac et al. [70] used 13x10-bit multiplier and RAM to store quantization table. Adders and shifters along with 64x12-bits ROM memory have been used by L. V. Agostini et al. [19]. M. Kovac et al. [70] used adders and shifters for division purpose and one division takes eight clock cycles. Five adders and five pipeline register stages along with quantization table have been used by Sung-Hsien Sun et al. [71] for quantization. The zig-zag ordering is performed by 8x8 arrays of register pairs by M. Kovac et al. [69] and M. Kovac et al. [70] whereas L. V. Agostini et al. [19] used time-interleaved RAM pairs of size 64x10-bits for the reading and writing operations. Similarly, Sung-Hsien Sun et al. [71] have used two RAM blocks for loading 64 DCT coefficients. Agostini et al. [19] used two ROM having sizes 12x13-bits and 176x21 bits to store Huffman code table. Efficient way of storing Huffman code table is presented by Sun et al. [71], where instead of storing 16-bits code word (required for the base code [1]), 8-bits width of memory size has been used and the whole system operate at 4.1 MHz in FPGA implementation.

After review of these articles, efficient hardware architectures for the image compression have been proposed. The architectures are optimized in all the stages for memory as well as datapath reductions by appropriate controlling circuitry and also by exploiting redundant nature of image in original representation. The objectives and outline of the work proposed in the thesis are presented in the following section.

#### 1.3 Objective of the Thesis

A novel equation for the computation of 2-D DCT coefficients without use of transposition memory is proposed. The equation can compute DCT coefficients one by one in any order in a non-recursive way. All the internal computations are performed in integer format making hardware architecture highly accurate for DCT coefficient computation. The fractional cosine values are stored in a register which is multiplied with a multiplier at last stage only. Therefore, hardware overhead becomes negligibly small as only a multiplier and a register bit width needs to be changed for higher accuracy of DCT coefficients. From the proposed equation, VLSI architecture is implemented in both FPGA as well ASIC library. The implemented architecture has less area and low power consumption when compared to existing 2-D DCT implementations. From this implementation, an additional multiplier and a register are enough to get the quantized and zig-zag ordered DCT coefficients without extra memory requirements and at the same latency.

Hardware architecture for computation of 1-D DCT with reduced area and power using memory free DA approach is presented and implemented in FPGA as well ASIC library for area and power comparisons. The presented 1-D DCT architecture reduces the DA computational units from architecture presented by P. Chungan *et al.* [58] from seven to three with clock latency increased by 3 cycles. Image compression using separable discrete Hartley transform (SDHT) has been done and it is found that SDHT performs same as DCT at high compression. Hardware architecture for DHT using ROM free DA is proposed which has less adder bit-width requirement than DCT. The architecture for 1-D DHT and 2-D DHT is implemented in FPGA.

A simple finite state machine (FSM) based architecture for computation of DCT to zig-zag ordering of quantized DCT coefficients is proposed. The architecture removes memory requirements for 64 DCT coefficients storage, quantization table storage as well storage of quantized coefficients for zig-zag ordering. The energy compaction property of DCT coefficients is studied by reconstructing the image using less number of DCT coefficients.

Huffman coding is implemented for JPEG Huffman code table. Strategies have been used to reduce the code memory requirements.

The major research works done are listed here:

- 1. The energy compaction property of DCT is studied by reconstructing the different images with the help of only selected DCT coefficients in the decompression.

- Image compression and decompression is done using 2-D separable discrete Hartley transform (2-D SDHT). Basis function image of SDHT is plotted, PSNR vs. compression ratio (rate-distortion curve) is plotted and compared with the 2-D DCT for different standard images.

- 3. FPGA implementation of SDHT is performed using efficient ROM free DA approach and results are compared with ROM based DA.

- 4. Area and power efficient VLSI architecture for 8 point 1-D DCT using ROM free DA is presented and implemented in FPGA as well as ASIC library.

- 5. A simple finite state machine (FSM) based VLSI architecture from DCT to Zigzag reordering of transformed coefficients for JPEG baseline encoder using quantization table suitable for less complex hardware design is presented and implemented in FPGA as well as standard cell.

- 6. Non-recursive equation and its VLSI architecture for direct computation of 8x8 two dimensional 2-D DCT without transposition memory for high image quality is presented and implemented in FPGA as well as standard cell based technology.

- 7. Huffman coding is implemented using memory requiring less number of bit storage as compared to original.

## 1.4 Chapter Wise Contribution of the Thesis

#### **Chapter-1: Introduction**

Introduction to transform based image compression along with motivation behind the dedicated hardware design for image compression is presented. Background work and main research contribution is also mentioned.

#### **Chapter-2: Image Compression**

The focus of this chapter is to study the energy compaction property of DCT and DHT in transformed based image compression. Image reconstruction is done using selective 2-D DCT coefficients. Quality assessment is done by reconstruction. Compression ratios are tabulated for different images at different quantization level. 2-D SDHT is used for the image compression and decompression.

#### Chapter-3: Distributed Arithmetic and its VLSI Architecture

Distributed Arithmetic (DA) implementation approach for DCT and DHT is main aim of this chapter. Efficient implementation of DCT and DHT using ROM free DA approach is described. Different implementation results (like 1-D DCT, 1-D DHT etc.) are summarized and compared with the existing implementations.

#### **Chapter-4: Efficient JPEG Image Compression Architecture**

This chapter focuses on efficient architecture of JPEG from DCT to zig-zag ordering where memory requirements for intermediate storage of DCT coefficients before and after quantization is removed by simple control circuit design. Also, efficient implementation of Huffman code table with reduced storage is done.

# Chapter-5 : Direct Computation of 8x8 2-D DCT Coefficients Equation and Its Hardware Architecture

The direct computation equation of 2-D DCT coefficients is explained. The proposed equation computes DCT coefficients in non-recursive way without transposition memory and require less hardware for image compression as demonstrated with the complete JPEG implementation.

#### **Chapter-6: Summary and Conclusions**

The comprehensive summary of the thesis is provided with scope for future work.

#### 1.5 Summary

In this introductory chapter, transformed based image compression and requirement for the low cost and low power image compression hardware are introduced. Motivations

towards the dedicated hardware implementation rather than software implementation are explained. The related works done in hardware implementation of DCT and complete JPEG image compression system is highlighted. The thesis objective is mentioned with major contributions illustrated point wise. Finally, chapter organization of the thesis is summarized.

# Chapter 2

## **Image Compression**

#### 2.1 Introduction

A digital image is two-dimensional functional in space where amplitudes at each location are called pixels. There are different types of images depending upon the different number of data bits per pixel for their representation. Quality of an image can be assessed either visually or by mathematical formulation. The former is called subjective quality assessment and the later objective quality assessment. A common objective quality assessment metric for images obtained after decompression is PSNR (peak signal-to-noise ratio). Transform based lossy image compression is flexible as it can compress images at different qualities depending upon the application of the image. JPEG uses 8x8 block-wise 2-D DCT as the transform. DCT has very high energy compaction and its performance is almost similar to optimal Karhunen-Lo'eve transform (KLT) with the advantage of constant kernel and less computational complexity. Still, for the hardware implementation, similar kind of transform which will have less computational complexity and hence less hardware requirement with performance almost similar to DCT can be a preferred choice.

In this chapter, introduction about digital image representations and its various classifications have been given. Image quality assessment has been briefed. Basics of transform based image compression along with JPEG image compression have been described. The energy compaction property of DCT has been studied by compressing the images with few low frequency DCT coefficients. Compression ratios at different scale of compression for different standard images have been tabulated and images are displayed for quality visual assessment. Separable discrete Hartley transform (SDHT) has been introduced for image compression and decompression. Quality of images obtained from compression and decompression by SDHT is compared with DCT.

#### 2.2 Image representation and classification

Image of a natural scene has infinite level of brightness and color intensity variations. Apart from intensity, they are continuous function in two dimensional space. To process the image for various applications by digital processors along with its storage in memory, image data obtained from electronic image sensors (CCD or CMOS) in digital camera, scanner or any similar device are converted into digital form by A/D converter. Sampling and quantization steps are used [1]. The infinite intensity levels of the image has now become digital having finite levels. Spatial continuity, itself being sampled by the fixed points present on the sensor, is converted to discrete. Continuous image signal (natural scene), now, is a two dimensional digital function, represented by f(x, y), where the magnitude of function f represents the intensity from among finite levels of intensities at any point (x, y) in the space. The coordinate (x, y) is discrete as shown in Fig.2.1. The intensities at different points in space are called pixel elements or pixels of the image. One example of finite level of intensities can be all integral values from 0 to 255. In general, any digital image will have the fixed number of pixel elements in horizontal as well as vertical directions. The term *size* of the image is used for the total number of pixel elements in an image. It is represented by MxN, where M is the number of rows and N is the number of columns of image data.

Fig.2.1 Representation of digital image in two dimensional spatial coordinate

In digital representation, the magnitude of intensity is represented by a fixed number of bits for the entire pixels. Classification of image on the basis of the number of bits used for representing each of its pixel value is as follows [72]

#### (a) Bi-level image

Each pixel will have one bit (binary) value, representing black and white. Textual information can be represented by the bi-level image.

#### (b) Grayscale image

This is a most common type of image used in many applications. A grayscale image represents the 2<sup>n</sup> shades of a gray, where n is the number of bits representing each pixel. The 8-bits (one byte) representation is most preferred and used for display in computer monitor and printing purpose as well. In 8-bit representation there are 256 shades of gray (or intensities) between black and white.

#### (c) Continuous-tone image

In a continuous-tone image there are many shades of a color (or gray). In other words, one pixel has many intensity levels such that nearby pixel intensity, though it differs by one unit intensity level, appears same to the eyes. Images obtained from the digital cameras and scanners are example of continuous-tone image. Color image is represented by 24-bits pixel value in three color component planes R (red), G (green) and B (blue) with 8-bits allocated for intensities of each color.

## 2.3 Image Quality Measurement Metric

Images are degraded in quality while going through the different processing steps such as acquisition, compression, transmission and reproduction [73]. In image and video processing fields, there are various systems and they all convey visual information for human perception. There is trade-off between system resources and visual quality obtained from these systems [74]. These requirements lead to necessity for the image quality measurement metric. In addition, there are engineers working on the optimization of signal processing algorithms [75]. So, it is also important for this perspective to test

algorithms for quality of the obtained signal (benchmarking algorithms). There are two methods to evaluate the quality of images. These are as follows:

#### Subjective Quality Measure

In the most of the image processing applications, human beings are the ultimate viewer and hence, subjective quality evaluation is done by the human beings. Consensus of the individuals regarding quality of compressed/decompressed images is taken in account. Viewer gives ratings among different choices available. Mean opinion score (MOS) is a numerical value that is the output of the observation given by [13],

$$MOS = \frac{\sum_{i=1}^{C} n_i R_i}{\sum_{i=1}^{C} n_i}$$

(2.1)

Here,  $R_i$  is the numerical value corresponding to category i,  $n_i$  is the number of judgments in that category and C is the number of category. However, subjective evaluation is expensive and process is slow. So, quality measurement cannot be incorporated in the automatic systems [73, 74].

#### ➤ Objective Quality Measure

Accurate and automatic quality measurement can be done by formulating a mathematical model. Signal-to-noise ratio (SNR) is a simple mathematical model of quality measurement expressed in terms of mean square error (MSE) and signal variance ( $\sigma_s$ ), given by [13],

$$SNR(dB) = 10\log_{10}\left(\frac{\sigma_s^2}{MSE}\right)$$

(2.2)

where variance is expressed by,

$$\sigma_s^2 = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} (f[m, n] - \mu)^2, \quad \mu = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} f[m, n]$$

(2.3)

and MSE is given by,

$$MSE = \frac{1}{MN} \sum_{m=1}^{M} \sum_{n=1}^{N} (f[m, n] - \hat{f}[m, n])^{2}$$

(2.4)

where f[m, n] represents original image and  $\hat{f}[m, n]$  represents the image after the application of compression/decompression process, the quality of which has to be determined. The size of the image is MxN. SNR being dependent on the image variance, another quantitative measurement metric is peak signal-to-noise ratio (PSNR). PSNR is expressed by the same SNR equation with variance replaced by maximum intensity level in the image representation. In case of 8-bits per pixel (gray scale) image, the maximum intensity is 255.

$$PSNR(dB) = 10\log_{10}\left(\frac{255^2}{MSE}\right) \tag{2.5}$$

PSNR is a better measurement matrix for comparing two images processed by the hardware, as it gives the truncation error introduced due to limited bit-width representation (e.g., register bit-width) [57].

## 2.4 Image Compression Model

Image compression reduces the amount of data from the original image representation. There are two approaches to compress an image. These are:

- (a) Lossless compression

- (b) Lossy compression

Image data compressed by lossless compression method can be retrieved back accurately in the reverse process called decompression. Lossless compression method has the disadvantage that images can be compressed by a maximum compression ratio of about 3 to 4 (very low compression), where compression ratio (CR) is given by,

$$CR = \frac{n1}{n2} \tag{2.7}$$

Here, n1 is the total number of bits in original image and n2 is the total number of bits in compressed image. In lossy compression method, an image is compressed at the cost of

removing unwanted information from it which cannot be perceived by human visual system (the human eyes are not able to distinguish the changes). With the help of lossy compression technique, images can be compressed to a large extent (very high compression) subject to quality requirement for image application. Hence, lossy compression is a most common and used in many image and video coding standard such as JPEG, MPEG etc.

Fig.2.2 shows a general image compression model. Image data representation has redundancy (also called pixel correlation, interpixel redundancy or spatial redundancy), in the sense, a pixel value can be predicted by its neighborhood pixels [1, 76]. Decorrelation process removes the spatial redundancy and hence, facilitates compression. Some of the techniques used for this process are predictive coding, transform coding and subband coding [76]. Apart from the interpixel redundancy, there is statistical redundancy present in the data after de-correlation (not only image but any data possess statistical redundancy). This is removed by entropy encoding process where more probable symbol is assigned less number of bits and vice-versa (also called variable length encoding). Huffman coding and arithmetic coding are two important techniques used for entropy encoding of data [77], [78]. Although, arithmetic encoding gives slightly

Fig.2.2 A generalized image compression model [76]

more compression than the Huffman encoding, it is a more complex and computation intensive. Therefore, Huffman coding is preferred choice in hardware implementation of entropy coding. In case of lossless compression, images undergo entropy encoding directly after de-correlation, whereas lossy compression require additional preprocessing stage called quantization before it is encoded by entropy process. Quantization is irreversible process and it is the only lossy stage in image compression model.

#### 2.5 Transform based Image Coding

Transform based image coding is most preferred and widely used lossy image compression (coding) method. Fig.2.3 shows the block diagram of transformed based image compression coding technique. The purpose of the transform is to remove interpixel redundancy (or de-correlate) from the original image representation. The image data is transformed to a new representation where average values of transformed data are smaller than the original form. This way the compression is achieved. The higher the correlation among the image pixels, the better is the compression ratio achieved. An image transform should have the following properties.

- (a) Inverse transformation should exist

- (b) De-correlate the original image data

- (c) Clear separation of frequency

Inverse transformation is a pre-requisite requirement in any transform because transformed data should be re-constructed for image formation by inverse process (decompression). Orthogonal transform (like DCT, DHT, DWT, etc.) is used for this purpose. A de-correlation property makes the transformed data independent from each other. In lossy image compression, some coefficients are quantized to zero or altered to a

Fig.2.3 Transform based image compression model

new smaller value. Therefore, by the de-correlation property, in inverse transforms, original image data remains nearly unchanged. Frequency separation brings the transformed data made up of different frequency coefficients. An image contains very high visual information in the low frequency contents than the high frequency content. Very fine details are represented by high frequency contents of the image and in many applications, fine details are not required (also in many cases these details are not important as they are not visible to human eyes). Therefore, if clear order of frequency is known, high frequency coefficients can be ignored (quantized to zero) in the coding stage and hence compression is achieved. An ideal image transform should possess the following two properties. These are:

- (a) Maximum energy compaction

- (b) Less computational complexity

By the energy compaction, very few coefficients can have high values in the transform domain. Therefore, lesser the coefficients value, higher is the compression. Fast image compression is required in many compression systems and complex transform leads to high computation time making the process slower. Also, in case of faster implementation, dedicated hardware is used. Furthermore, high complex algorithm requires more hardware area, making the encoder design costly and also more power consuming.

#### **Block based transform**

Images can be transformed in non-overlapped smaller block size, like 4x4, 8x8, 16x16, 32x32, etc. Since, nearby pixels possess correlations, this trend is valid throughout the entire image pixels. Therefore, larger the block size taken for the transform, more correlation can be exploited and interpixel redundancy can be removed. In practice, it is found that average coding gain improvement is much lower when increasing the transform size [13, 79]. In contrast, the computational complexity increases by a larger amount with increase of block size. Hence, a compromise is made for the transform size between the computational complexity and coding gain and 8x8 block based transform is adopted in many image and video coding standards, like JPEG image compression, MPEG video compression, etc.

#### Quantization

Quantization process brings variable compression in the image compression process. Quantization process is done by dividing each transformed coefficients by a constant step size. In this process, transformed coefficients are made smaller to bring the compression [15]. Inverse quantization step restores original coefficients but with round-off error. Higher step size used for the quantization makes transformed coefficients smaller i.e., more compressed, with the cost of losing data in rounding and truncation. Quantization step size can be controlled by a variable number. Automatic compression size is incorporated by meeting the trade-off between image quality, bit-rate for transmission and memory size used for the storage of compressed images. Transformed coefficients possess the different frequency values. Accordingly, high frequency coefficients which carry low visual information can be quantized heavily without losing important image information.

#### Coefficients Re-arrangement

Many high frequency transformed coefficients when quantized heavily become zero. In order to code the quantize coefficients efficiently, Run-Length encoding procedure is applied. In Run-Length encoding procedure, not all zeros are encoded by a unique code for zero, but it is encoded by the number of zeros preceding the non-zero coefficient. Hence, larger zeros make little change in code length. Therefore, it is important that zero quantized coefficients are not distributed among non-zero coefficients, rather for optimal encoding, all zeros should come together in sequence. For this purpose, transformed and quantized coefficients are re-arranged in increasing frequency order so that higher frequencies (which are quantized to zero) appear last.

## 2.6 JPEG baseline Image Coding

JPEG baseline image coding is a transform based lossy image compression technique and it is standardized by JPEG committee [14]. Image is processed in 8x8 blocks to reduce the computational complexity for the implementation. The 8x8 block-wise 2-D DCT is taken followed by quantization of DCT coefficients. A typical quantization matrix is given by,

$$Q_m = \begin{bmatrix} 16 & 11 & 10 & 16 & 24 & 40 & 51 & 61 \\ 12 & 12 & 14 & 19 & 26 & 58 & 60 & 55 \\ 14 & 13 & 16 & 24 & 40 & 57 & 69 & 56 \\ 14 & 17 & 22 & 29 & 51 & 87 & 80 & 62 \\ 18 & 22 & 37 & 56 & 68 & 109 & 103 & 77 \\ 24 & 35 & 55 & 64 & 81 & 104 & 113 & 92 \\ 49 & 64 & 78 & 87 & 103 & 121 & 120 & 101 \\ 72 & 92 & 95 & 98 & 112 & 100 & 103 & 99 \end{bmatrix}$$