### Investigation on Cascade Multilevel Inverter for Medium and High-Power Applications

A Thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

By

**Y.Suresh**

Under the supervision of

#### **Prof. Anup Kumar Panda**

Department of Electrical Engineering

#### National Institute of Technology, Rourkela

July 2012

## Investigation on Cascade Multilevel Inverter for Medium and High-Power Applications

Y. Suresh

Department of Electrical Engineering

National Institute of Technology, Rourkela

### Investigation on Cascade Multilevel Inverter for Medium and High-Power Applications

A Thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy In Electrical Engineering

By

Y.Suresh Roll No.:509EE104

Under the supervision of

Prof. Anup Kumar Panda

Department of Electrical Engineering

#### National Institute of Technology, Rourkela

July 2012

#### Declaration

I hereby declare that the work which is being presented in the thesis entitled "Investigation on Cascade Multilevel inverter for Medium and High power Applications" in partial fulfillment of the requirements for the award of the degree of DOCTOR OF PHILOSOPHY submitted to the Department of Electrical Engineering of National Institute of Technology, Rourkela, is an authentic record of my own work under the supervision of Prof. A. K. Panda, Department of Electrical Engineering. I have not submitted the matter embodied in this thesis for the award of any other degree or diploma of the university or any other institute.

Date 17<sup>th</sup> July, 2012

Y.Suresh

DEPARTMENT OF ELECTRICAL ENGINEERING NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA ORISSA, INDIA - 769008

# CERTIFICATE

This is to certify that the thesis titled "**Investigation on Cascade Multilevel inverter for Medium and High-Power Applications**", submitted to the National Institute of Technology, Rourkela by **Mr. Y. Suresh.**, Roll No. **509EE104** for the award of Doctor of Philosophy in Electrical Engineering, is a bona fide record of research work carried out by him under my supervision and guidance.

The candidate has fulfilled all the prescribed requirements.

The Thesis which is based on candidate's own work, has not submitted elsewhere for a degree/diploma.

In my opinion, the thesis is of standard required for the award of a Doctor of Philosophy degree in Electrical Engineering.

Prof. A. K. Panda Department of Electrical Engineering National Institute of Technology Rourkela – 769008 Email: akpanda@nitrkl.ac.in

#### **BIO-DATA OF THE CANDIDATE**

| Name              | : Y.Suresh                          |

|-------------------|-------------------------------------|

| Date of Birth     | : 11 <sup>st</sup> Aug, 1984        |

| Permanent Address | : Do No: 23/57, Venkatagiri Town,   |

|                   | Nellore [DT], Andhra Pradesh, India |

| Email             | : <u>ysuresh.ee@gmail.com</u>       |

#### ACADEMIC QUALIFICATION

- Pursuing Ph. D in Electrical Engineering, National Institute of Technology, Rourkela.

- M. Tech in Electrical Engineering, National Institute of Technology, Rourkela.

- B. E. in Electrical Engineering from JNTU University, Andhrapradesh.

#### **RESEARCH PUBLICATIONS**

#### JOURNAL

- A.K.panda, Y.Suresh, "Research on Cascade Multilevel Inverter with Single DC Source by Using Three-Phase Transformers", Int J Electric Power Energy Syst. (Elsevier) 40 (2012) 9–20.

- Y. Suresh, A.K Panda, Research on Cascade Multilevel Inverter by Employing Three-Phase Transformers, IET Power Electron., 5 (5) 2012, 561 – 570.

- 3. A.K.panda, Y.Suresh, "Performance of Cascade Multilevel Inverter by Employing Single and Three-Phase Transformers", IET Power Electron, 2012 (Accepted )

#### **CONFERENCE**

Y.Suresh, A.K.Panda, "Performance of Cascaded Multilevel Inverter with Single DC Source by Employing Three- Phase Low frequency Transformers, IECON-2010 is the 36th Annual Conference of the IEEE Industrial Electronics Society Pheonix, Arezona, USA -2010.

- Y.Suresh, A.K.Panda, M.Mahesh , "An Improved Performance of Cascaded Multilevel Inverter with Single DC Source by Employing Three-Phase Transformers" IEEE International power and energy conference (IPEC) Singapore, 27-29, oct-2010.

- Y.Suresh, A.K.Panda, "Dynamic Performance of STATCOM under Single Line to Ground Faults in Power System", 5<sup>th</sup> IET International Conference on Power Electronics, Machines & Drives (PEMD 2010), Brighton, UK, 19th– 21th April 2010, Digital Object Identifier: 10.1049/cp.2010.0125, pp.1-6.

- M.Suresh, S.S Patniak, A.K.Panda ,Y.Suresh, , "Current Harmonics Cancellation in Three-Phase Four wire systems, **IEEE-PES** Power Systems Conference & Exposition, April -29, 2011, Phoenix, Arizona, USA.

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisor Prof. A. K. Panda, for his guidance, encouragement, and support throughout the course of this work. It was a precious learning experience for me and I am proud to be one of his students. In fact, he is backbone to my research carrier. From him I have gained not only extensive knowledge, but also careful research thoughts.

I am very much thankful to Prof. B. D. Subudhi, Head, Department of Electrical Engineering, for his constant support. Also, I am indebted to him who provided me all official and laboratory facilities.

I am grateful to my Doctoral Scrutiny Members, Prof. K. B. Mohanty and Prof. K. K. Mahapatra for their valuable suggestions and comments during this research period.

I am especially indebted to my colleagues in the power electronics group. First, I would like to specially thank Mr. Mikilli Suresh, who helps me in implementing my real time experiments. We share each other a lot of knowledge in the field of power electronics. I would also thank my beloved friend Mr. Kalapraveen for his valuable thoughts in my research carrier. I would also like to thank the other members of the team, Prof. Matiy, Prof. B. Chitti Babu, Mr. Matada Mahesh, for extending their technical and personal support making my stay pleasant and enjoyable.

This section would remain incomplete if I don't thank the lab assistants Mr. Rabindra Nayak without whom the work would have not progressed.

lastly, with deepest love, I would be grateful to my beloved Father & Mother who supported and encouraged me all the time, no matter what difficulties are encountered.

Y. Suresh

|   | Title                                                       | Page<br>No. |

|---|-------------------------------------------------------------|-------------|

|   | Abbreviations                                               | v           |

|   | Notations                                                   | viii        |

|   | Abstract                                                    | xi          |

|   | List of Figures                                             | xii         |

|   | List of Tables                                              | xvii        |

| 1 | Introduction                                                |             |

|   | 1.1 Research Background                                     | 1           |

|   | 1.2 Medium and High Power Converters                        | 1           |

|   | 1.3 Challenging Aspects in medium and high-power            | 3           |

|   | converters                                                  |             |

|   | 1.4 Concept of Classical Converters (Two-Level Converters)  | 5           |

|   | 1.5 Concept of Multilevel Inverters                         | 9           |

|   | 1.6 A Brief Review on Traditional Multilevel Inverters      | 15          |

|   | 1.6.1 Neutral Point Inverters.                              | 15          |

|   | 1.6.2 Flying Capacitor Converters                           | 17          |

|   | 1.6.3 Cascaded H-Bridge Converters                          | 19          |

|   | 1.7 Multilevel Topologies and Manufacturing companies       | 20          |

|   | 1.8 Merits of Multilevel Inverter                           | 26          |

|   | 1.9 Motivation                                              | 27          |

|   | 1.10 Dissertation Objectives                                | 32          |

|   | 1.11 Dissertation Outline                                   | 32          |

| 2 | Multilevel Inverters                                        |             |

|   | 2.1 Importance of Cascade Multilevel Inverters              | 35          |

|   | 2.2 Applications of Traditional Cascade Multilevel Inverter | 37          |

|   | 2.2.1 Traction                                              | 37          |

|   | 2.2.2 LNG Plant                                             | 38          |

|   | 2.2.3 Pumps and Fans                                        | 39          |

#### CONTENTS

|   | 2.2.4 STATCOM                                              | 39 |

|---|------------------------------------------------------------|----|

|   | 2.3 Modulation Techniques and Control Strategies for       | 41 |

|   | Cascade Multilevel inverters:                              |    |

|   | 2.3.1 Multilevel SHE                                       | 42 |

|   | 2.3.2 Multilevel SVM                                       | 44 |

|   | 2.3.3 Multilevel Carrier-Based PWM:                        | 45 |

|   | 2.3.4 Phase Shifted (PS-PWM)                               | 46 |

|   | 2.3.5 Level Shifted (LS-PWM)                               | 48 |

|   | 2.4 Performance of Traditional Cascade Multilevel inverter | 49 |

|   | with Separate DC source                                    |    |

|   | 2.5 Challenging Issues in Cascade Multilevel Inverter with | 54 |

|   | Separate DC Sources                                        |    |

|   | 2.6 Summery                                                | 55 |

| 3 | Conventional Cascaded H-Bridge Multilevel Inverter         |    |

|   | Topologies                                                 |    |

|   | 3.1 Cascade H-Bridge with Unequal Dc Sources.              | 56 |

|   | 3.2 Cascaded Multilevel Inverter with Minimum DC           | 58 |

|   | Sources                                                    |    |

|   | 3.3 Hybrid Cascade Multilevel with Bottom Three Leg        | 62 |

|   | Inverter                                                   |    |

|   | 3.4 Hybrid Cascade H-Bridge Multilevel Inverter Sources    | 65 |

|   | 3.5 Cascade H-Bridge Multilevel Inverter By Employing      | 68 |

|   | Single Phase Transformers                                  |    |

|   | 3.6 Cascade Multilevel Inverter with Cascaded Transfomers  | 70 |

|   | 3.7 Summery                                                | 73 |

| 4 | Proposed CMI With Single Dc Source By Using Three Phase |     |

|---|---------------------------------------------------------|-----|

|   | Transfomers                                             |     |

|   | 4.1 Proposed CMI with three-phase transformers.         | 74  |

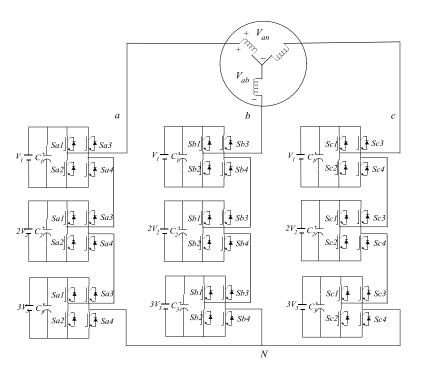

|   | 4.2 Output voltage characteristics                      | 77  |

|   | 4.3 Performance Verifications                           | 80  |

|   | 4.3.1 Fundamental Frequency Approach                    | 80  |

|   | 4.3.2 Multilevel Selective Harmonic Elimination PWM     | 83  |

|   | Technique                                               | 86  |

|   | 4.3.2.1 Harmonic elimination and phase shift            |     |

|   | 4.3.3 Multilevel Sinusoidal PWM Technique               | 86  |

|   | 4.3.3.1 PWM techniques                                  | 86  |

|   | 4.3.3.2 Switching and phase shifting:                   | 86  |

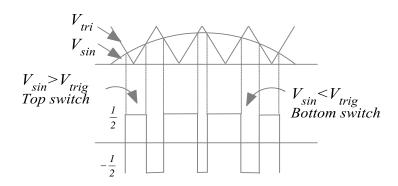

|   | 4.3.3.3 Unipolar switching                              | 87  |

|   | 4.4 System Hardware                                     | 88  |

|   | 4.5 Experimental Results                                | 89  |

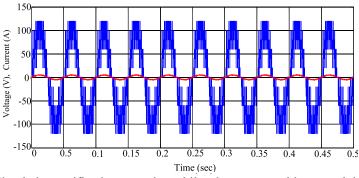

|   | 4.5.1 Fundamental Frequency Approach                    | 90  |

|   | 4.5.2 Selective harmonic approach                       | 91  |

|   | 4.5.3 Sinusoidal PWM approach                           | 93  |

|   | 4.5.4 Important features of proposed CMI                | 94  |

|   | 4.6 Comparative Study                                   | 95  |

|   | 4.7 Summery                                             | 97  |

| 5 | Proposed CMI Based Active Power Filter                  |     |

|   | 5.1 Introduction to Active power filter                 | 99  |

|   | 5.2 Proposed system configuration                       | 100 |

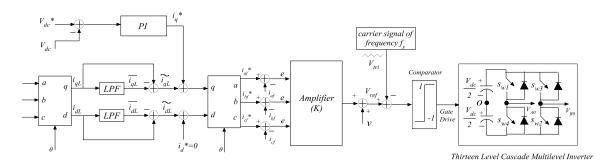

|   | 5.3 Control strategy                                    | 103 |

|   | 5.3.1 Harmonic current regulator                        | 105 |

|   | 5.3.2 Multilevel voltage source modulation              | 105 |

|   | 5.3.3 DC voltage controller                             | 106 |

|   | 5.4 Simulation Result and System Performance            | 107 |

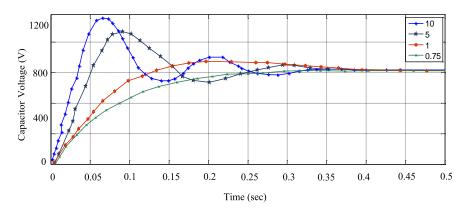

|   | 5.4.1 Proportional-integral (PI) controller design      | 108 |

|   | aspects                                                 |     |

|   | 5.5 Verifications with Real Time Digital Simulator | 112 |

|---|----------------------------------------------------|-----|

|   | 5.6 Summery                                        | 117 |

| 6 | CONCLUSION                                         |     |

|   | 6.1 Summary                                        | 118 |

|   | 6.2 Future Work                                    | 120 |

|   | REFERENCES                                         | 122 |

|   |                                                    |     |

#### ABBREVIATIONS

| SCR     | -Silicon-Controlled Rectifier                            |

|---------|----------------------------------------------------------|

| GE      | -General Electric                                        |

| IGBT    | -Insulated Gate Bipolar Transistor                       |

| FACTS   | -Flexible Ac Transmission Systems                        |

| IGCT    | -The Integrated Gate Commutated Thyristors               |

| SiC     | -Silicon Carbide Material                                |

| TRIAC   | -Triode For Alternating Current                          |

| BJT     | -Bipolar Junction Transistor                             |

| MOSFET  | -Power Metal-Oxide Semiconductor Field Effect Transistor |

| CPLD    | -Complex Programmable Logic Devices                      |

| ASIC    | -Application Specific Integrated Circuit                 |

| PEBB    | Power Electronics Building Blocks                        |

| APF     | -Active Power Filters                                    |

| EPQ     | -Electric Power Quality                                  |

| VSC     | -Voltage Source Converter                                |

| LNG     | -Liquefied Natural Gas                                   |

| NPC     | -Neutral-Point-Clamped Converter                         |

| NPC-MLI | Neutral-Point-Clamped Multilevel Inverter                |

| FC-MLI  | Flying Capacitor Multilevel Inverter                     |

| DCC     | -Diode-Clamped Converter                                 |

| FC      | -Flying Capacitor Converter                              |

| СНВ     | -Cascade H-Bridge                                        |

| L       |                                                          |

| PWM- Pulse Width ModulationSVG-Static Var GenerationMLI-Multi Level InverterCMI-Cascaded Multilevel InverterCMLICascaded Multi-Level InverterHBBB-H-Bridge Building BlockPWM-Pulse Width ModulationSVM-Space-Vector ModulationCML-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterHV-High Voltage | CHB-MLI | -Cascade H-Bridge Multilevel Inverter                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------|

| MLI-Multi Level InverterCMI-Cascaded Multi-Level InverterCMLICascaded Multi-Level InverterHBBB-H-Bridge Building BlockPWM-Pulse Width ModulationSVM-Space-Vector ModulationCML-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterFCMLI-Flying Capacitor Multi Level Inverter                        | PWM     | - Pulse Width Modulation                               |

| CMI-Cascaded Multilevel InverterCMLICascaded Multi-Level InverterHBBB-H-Bridge Building BlockPWM-Pulse Width ModulationSVM-Space-Vector ModulationCM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationSVM-Space Vector ModulationGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationSHE-Selective Harmonic EliminationSHE-Selective Harmonic EliminationSVC-Space Vector ControlDTC-Direct Torque ControlVSI-Voltage-Source InverterFCMLI-Flying Capacitor Multi Level Inverter | SVG     | -Static Var Generation                                 |

| CMLICascaded Multi-Level InverterHBBB-H-Bridge Building BlockPWM-Pulse Width ModulationSVM-Space-Vector ModulationCM-Space-Vector ModulationCM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterFCMLI-Flying Capacitor Multi Level Inverter                                 | MLI     | -Multi Level Inverter                                  |

| HBBB-H-Bridge Building BlockPWM-Pulse Width ModulationSVM-Space-Vector ModulationCM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                   | CMI     | -Cascaded Multilevel Inverter                          |

| PWM-Pulse Width ModulationSVM-Space-Vector ModulationCM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                     | CMLI    | Cascaded Multi-Level Inverter                          |

| SVM-Space-Vector ModulationCM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                        | HBBB    | -H-Bridge Building Block                               |

| CM-Common-ModeNPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                              | PWM     | -Pulse Width Modulation                                |

| NPC-Neutral-Point ClampedGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                            | SVM     | -Space-Vector Modulation                               |

| GTO-Gate Turn Off ThyristorsGTO-Gate Turn Off ThyristorsSVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                         | СМ      | -Common-Mode                                           |

| SVM-Space Vector ModulationTHD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                 | NPC     | -Neutral-Point Clamped                                 |

| THD-Total Harmonic DistortionSHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                                            | GTO     | -Gate Turn Off Thyristors                              |

| SHE-Selective Harmonic EliminationSHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                         | SVM     | -Space Vector Modulation                               |

| SHEPWM-Selective Harmonic Elimination Pulse Width ModulationSVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                           | THD     | -Total Harmonic Distortion                             |

| SVC-Space Vector ControlDTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                       | SHE     | -Selective Harmonic Elimination                        |

| DTC-Direct Torque ControlUPQC-Unified Power-Quality ConditionerVSI-Voltage-Source InverterDCI-Diode Clamped InverterFCMLI-Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                                               | SHEPWM  | -Selective Harmonic Elimination Pulse Width Modulation |

| UPQC       -Unified Power-Quality Conditioner         VSI       -Voltage-Source Inverter         DCI       -Diode Clamped Inverter         FCMLI       -Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                 | SVC     | -Space Vector Control                                  |

| VSI       -Voltage-Source Inverter         DCI       -Diode Clamped Inverter         FCMLI       -Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                                                                       | DTC     | -Direct Torque Control                                 |

| DCI     -Diode Clamped Inverter       FCMLI     -Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                        | UPQC    | -Unified Power-Quality Conditioner                     |

| FCMLI     -Flying Capacitor Multi Level Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSI     | -Voltage-Source Inverter                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DCI     | -Diode Clamped Inverter                                |

| HV -High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FCMLI   | -Flying Capacitor Multi Level Inverter                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | HV      | -High Voltage                                          |

| FPGA    | -Field Programmable Gate Array     |

|---------|------------------------------------|

| LV      | -Low Voltage                       |

| EMC     | -Electro Magnetic Compatibility    |

| SPWM    | -Sinusoidal Pulse Width Modulation |

| DC      | -Direct Current                    |

| DSP     | -Digital Signal Processing         |

| EMI     | -Electro Magnetic Interference     |

| STATCOM | -Static Synchronous Compensators   |

| SSSC    | -Static Series Compensators        |

| RTDS    | -Real Time Digital Simulator       |

| VFD     | -Variable Frequency Devices        |

| APF     | -Active Power Filters              |

| PCC     | -Point of Common Coupling          |

#### NOTATIONS

| V <sub>in</sub>                   | - Input Voltage                 |

|-----------------------------------|---------------------------------|

| V <sub>out</sub>                  | -Output Voltage                 |

| P <sub>in</sub>                   | -Input Power                    |

| Pout                              | -Output Power                   |

| D                                 | -Duty cycle                     |

| T <sub>S</sub>                    | -Time period                    |

| Ploss                             | -Power loss                     |

| V <sub>O</sub>                    | -Output Voltage                 |

| I <sub>0</sub>                    | -Output Current                 |

| V <sub>dc</sub>                   | -Input DC voltage               |

| S <sub>W1</sub>                   | -Switch                         |

| V <sub>an</sub>                   | -Phase to neutral voltage       |

| V <sub>ab</sub>                   | -Line to Line voltage           |

| V <sub>a0</sub>                   | -Phase " a" voltage             |

| $C_{\rm a,} C_{\rm b}, C_{\rm c}$ | -Storage Capacitance            |

| $H_1, H_2$                        | -Bridge cell                    |

| Vc                                | -Capacitor votalge              |

| Tr.1                              | -Transformer 1                  |

| N                                 | -Transformation matrix          |

| V <sub>AS</sub>                   | -Summation of Phase "a" Votlage |

| Vak                               | -Input voltage                  |

| М                                 | -Modulation index               |

| $\alpha_k$       | -Switching angle                                |

|------------------|-------------------------------------------------|

| β                | -Phase shift angle                              |

| $\varphi_{cr}$   | -Phase difference between two adjacent carriers |

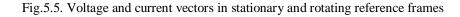

| V <sub>sin</sub> | -Reference waveform                             |

| V <sub>tri</sub> | -Carrier waveform                               |

| IL               | -Load current                                   |

| θ                | -Transformation angle                           |

| i <sub>d</sub>   | -Active Currents                                |

| $i_q$            | -Reactive Currents                              |

| I <sub>Lah</sub> | -Load Harmonic current                          |

| fc               | -Cut off frequency                              |

| $V_{ m dc}*$     | -Reference DC link voltage                      |

| Ki               | -Integral coefficient                           |

| K <sub>P</sub>   | -Proportional coefficient                       |

| Is               | -Source Current                                 |

| I <sub>F</sub>   | -Filter Current                                 |

#### ABSTRACT

It is hard to connect a single power semiconductor switch directly to medium voltage grids (2.3, 3.3, 4.16, or 6.9 kV). For these reasons, a new family of multilevel inverters has emerged as the solution for working with higher voltage levels. Multilevel inverters have received more attention in industrial application, such as motor drives, static VAR compensators and renewable energy systems, etc. Primarily multilevel inverters are known to have output voltages with more than two levels. As a result, the inverter output voltages have reduced harmonic distortions and high quality of waveforms. Additionally, the devices are confined to fraction of dc-link voltage. These characteristics make multilevel inverter to adopt for high-power and high-voltage applications. A good number of multilevel inverter topologies have been proposed during the last two decades. Contemporary research has engaged novel converter topologies and unique modulation schemes. Moreover, four major multilevel inverter structures have been reported in the literature these are as follows: cascaded H-bridges inverter (CHB) with separate dc sources, diode clamped (neutralclamped), and flying capacitors (capacitor clamped), P2 Multilevel inverters. Although different multilevel inverter exists, Cascade Multilevel Inverter (CMI) is one of the productive topology from multilevel family. In reality, on comparing with other multilevel based topologies, CMI feature a high modularity degree because each inverter can be seen as a module with similar circuit topology, control structure, and modulation. Therefore, in the case of a fault in one of these modules, it is possible to replace it quickly and easily. Moreover, with an appropriated control strategy, it is possible to bypass the faulty module without stopping the load, bringing an almost continuous overall availability. All this features make CMI an outstanding power converter. However, one of the greatest limitations of CMI

is utilization of separate DC source for each H-Bridge cell. This not only increases cost but also affects the reliability of the system. This is the key motivation for this dissertation.

In the present work, we have investigated different CMI based topologies with separate and single DC sources and finally proposed a new CMI based configuration with single dc source by using three-phase transformers. The proposed CMI based inverter presented in this thesis is well defined with logical and mathematical approach. Additionally to illustrate the merits, it is compared with traditional multilevel inverters. The feasibility of proposed inverter is demonstrated with different illustrations and confirmed by experimental results. The proposed CMI is well suited for *grid / photovoltaic* and *FACTS* systems. To elevate the application of proposed CMI a shunt active power filter (APF) design is demonstrated. In this case, the goal is to inject, in parallel with the load, compensation current to get a sinusoidal source current. The proposed APF is verified through Matlab-simulation. Finally, Opal-RT verifications are performed to verify the final design.

| Fig.<br>No. | Title                                                                                                                                                                        | Page<br>Number |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

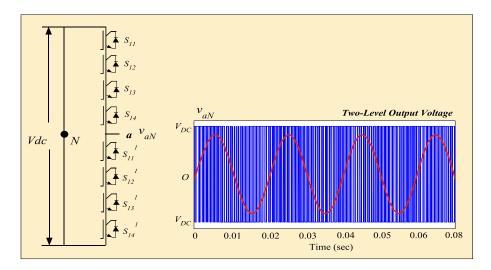

| 1.1         | Classical converter and output waveform                                                                                                                                      | 5              |

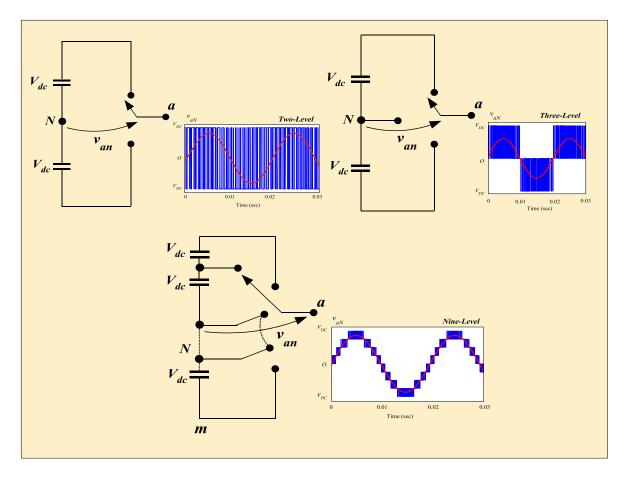

| 1.2         | Converter output voltage waveforms a) two level b) three level c) nine level                                                                                                 | 10             |

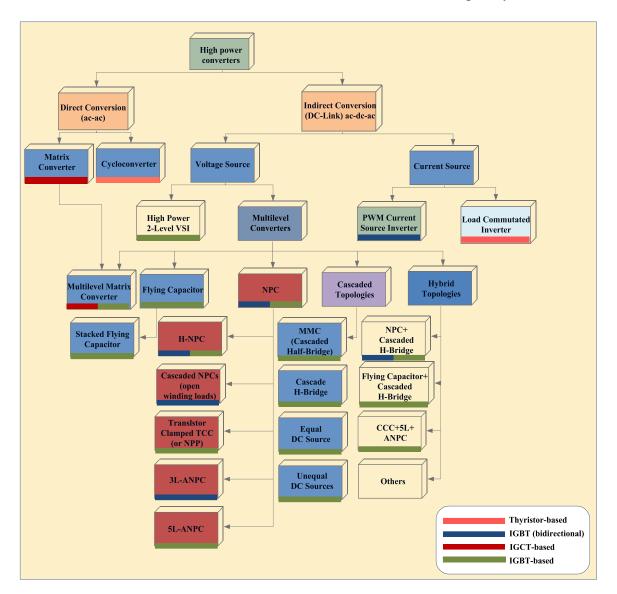

| 1.3         | Classification of high-power converters                                                                                                                                      | 12             |

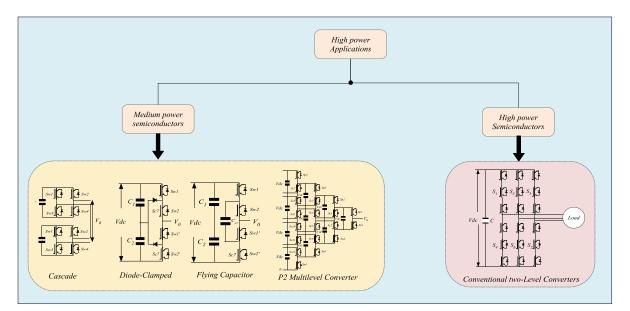

| 1.4         | Classical two level power converters versus most common mutlilvel<br>power converters                                                                                        | 14             |

| 1.5         | Three-level neutral point clamped power circuit                                                                                                                              | 15             |

| 1.6         | Three-level NPC-MLI switching states and corresponding output voltage levels                                                                                                 | 16             |

| 1.7         | Three-level flying capacitor power circuit                                                                                                                                   | 18             |

| 1.8         | Three-level FC-MLI switching states and corresponding output voltage levels                                                                                                  | 18             |

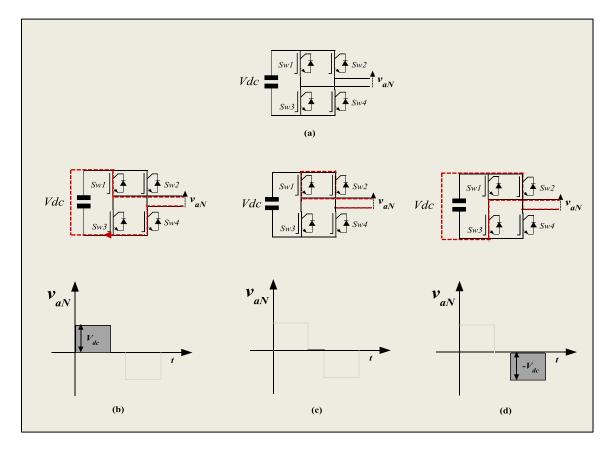

| 1.9         | Three-level CHB-MLI switching states and corresponding output voltage levels                                                                                                 | 20             |

| 1.10        | Topologies and phase voltages of the conventional two-level and<br>multilevel voltage source inverters                                                                       | 24             |

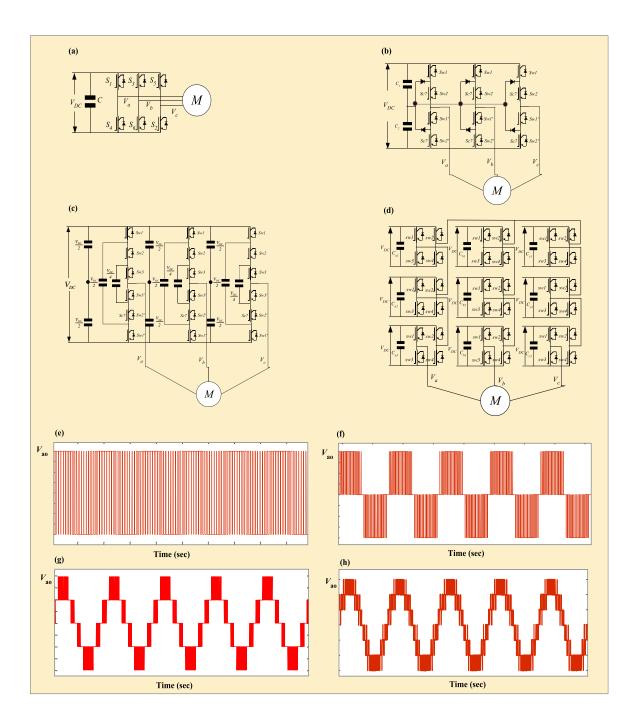

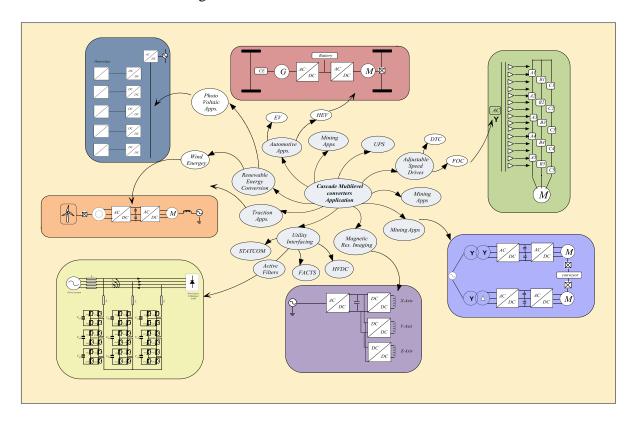

| 2.1         | Cascade multilevel converter applications                                                                                                                                    | 38             |

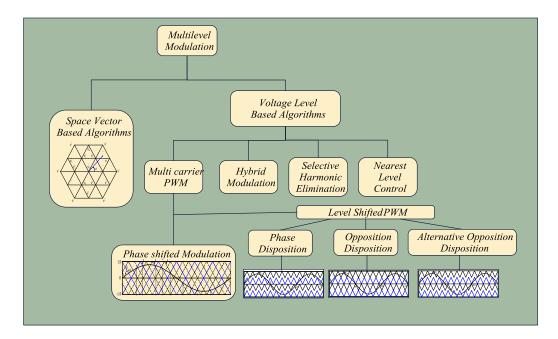

| 2.2         | Details of PWM techniques                                                                                                                                                    | 41             |

| 2.3         | One angle per voltage level with multilevel selective harmonic elimination technique                                                                                         | 43             |

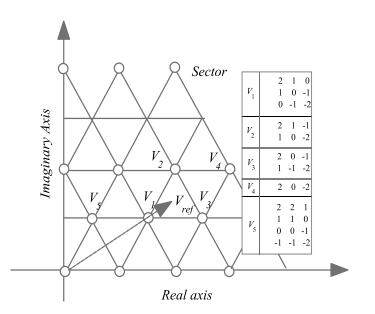

| 2.4         | Multilevel Space Vector Modulation.                                                                                                                                          | 44             |

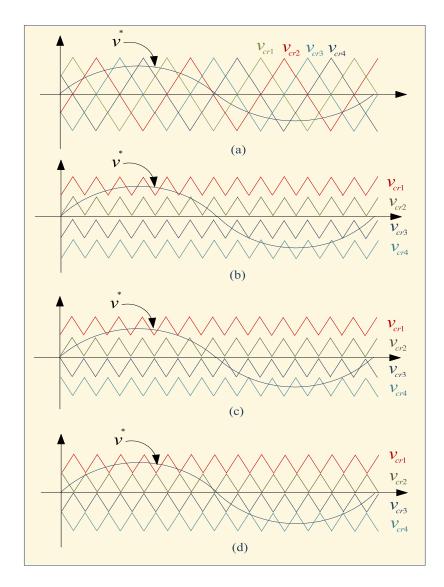

| 2.5         | Phase shifted and Level shifted PWM carrier arrangements (a) Phase shifted PWM (b) PD, (c) POD, (d) APOD                                                                     | 47             |

| 2.6         | a) Conventional cascade H-Bridge multilevel inverter (7level) b)<br>Operational waveforms for seven level inverter                                                           | 50             |

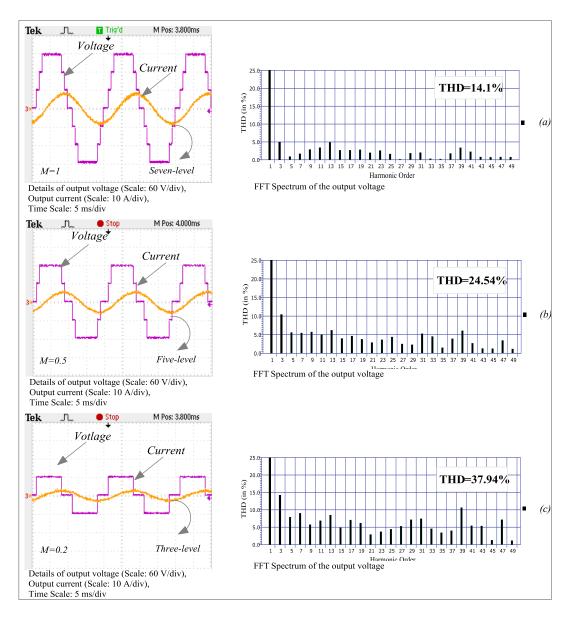

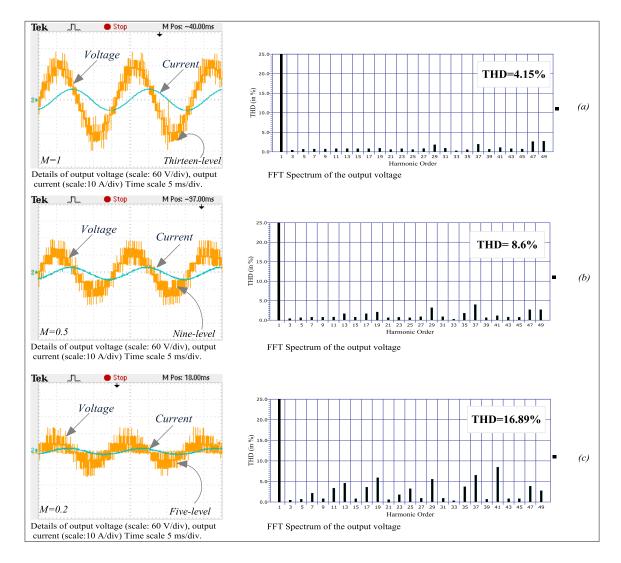

| 2.8         | Performance of cascaded multilevel inverter with three-phase transformers by using fundamental frequency approach at Modulation index 1, 0.5, and 0.2 (from top to bottom).  | 51             |

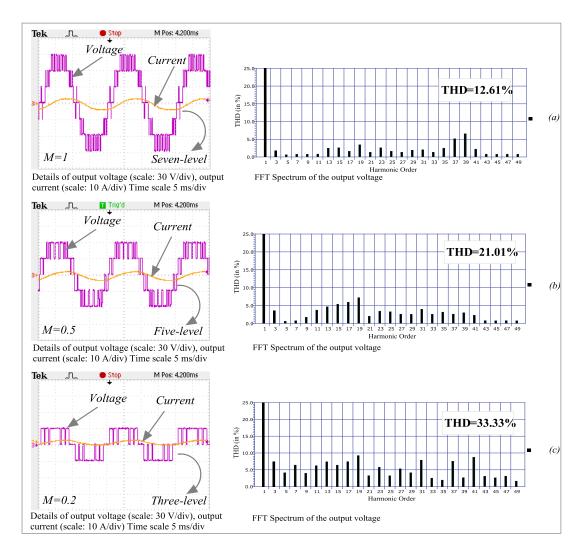

| 2.9         | Performance of cascaded multilevel inverter with three-phase transformers by using selective harmonic PWM approach at Modulation index 1, 0.5, and 0.2 (from top to bottom). | 52             |

| 2.10        | Performance of cascaded multilevel inverter with three-phase transformers by using fundamental frequency approach at Modulation                                              | 53             |

|      | index 1, 0.5, and 0.2 (from top to bottom                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.10 | Short circuit possibility of each case                                                                                                          | 54 |

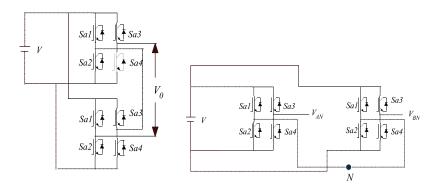

| 3.1  | Cascade multilevel converter with minimum number of dc sources.                                                                                 |    |

| 3.2  | Simulation verification cascade multilevel converter with unequal dc voltages.                                                                  | 56 |

| 3.3  | Output voltage and current waveform for cascade H-Bridge multilevel inverter with unequal dc sources at m=0.85                                  |    |

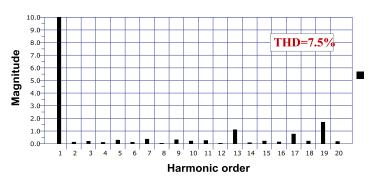

| 3.4  | Detials of FFT Spectra                                                                                                                          |    |

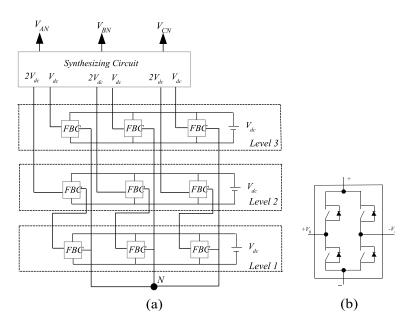

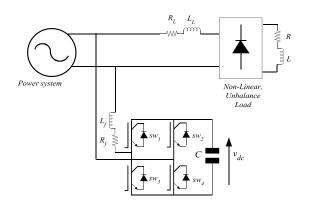

| 3.5  | Cascade multilevel inverter with single dc-source with minimum<br>number of isolated dc sources a) circuit diagram b) full-Bridge cell<br>(FBC) | 58 |

| 3.6  | Output waveform of CMI with three dc source                                                                                                     | 59 |

| 3.7  | Simulation verification for CMI with reduced dc source                                                                                          | 60 |

| 3.8  | Output voltage and current waveform of CMI with three dc sources at m=0.85.                                                                     | 61 |

| 3.9  | Details of FFT Spectra                                                                                                                          | 61 |

| 3.10 | Hybrid cascade multilevel inverter with single dc-source                                                                                        |    |

| 3.11 | Five level output waveform                                                                                                                      |    |

| 3.12 | Simulaiton verification of Five level Hybrid cascade multilevel inverter                                                                        | 64 |

| 3.13 | Output voltage and current waveform of the hybrid cascaded multilevel inverter at m=0.85                                                        | 64 |

| 3.14 | Detials of FFT Spectra                                                                                                                          | 64 |

| 3.15 | Hybrid cascade H-bridge multilevel inverter with single dc-source                                                                               | 65 |

| 3.16 | Seven level output waveform                                                                                                                     | 65 |

| 3.17 | Simulaiton verification of seven level Hybrid cascade multilevel inverter.                                                                      | 67 |

| 3.18 | Output voltage and current waveform of the hybrid cascaded H-Bridge multilevel inverter at m=0.85                                               |    |

| 3.19 | Details of FFT Spectra                                                                                                                          | 67 |

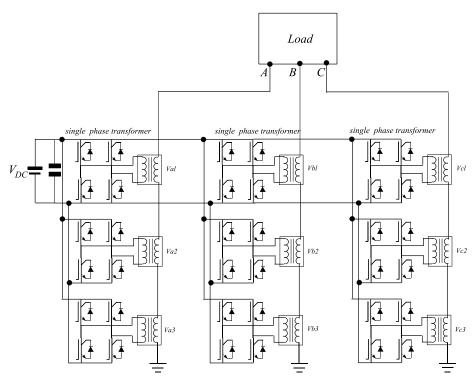

| 3.20 | Details of cascaded-inverters with Single dc source by employing single phase transformers.                                                     | 69 |

| 3.21 | Simulaiton verification Output voltage and current waveform of the cascaded multilevel inverter with single-phase transformers.                                                                                                                                                 | 69  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

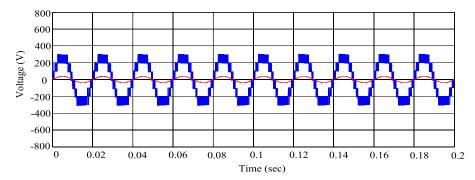

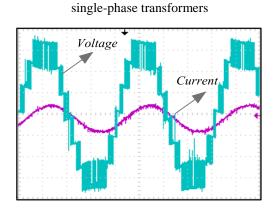

| 3.22 | Output voltage and current waveform of the cascaded multilevel<br>inverter with single-phase transformers                                                                                                                                                                       |     |

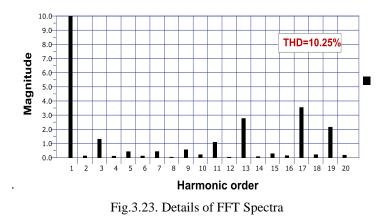

| 3.23 | Details of FFT Spectra                                                                                                                                                                                                                                                          | 70  |

| 3.24 | Details of Cascade multilevel inverter with Single dc source by<br>employing cascaded transformers                                                                                                                                                                              |     |

| 3.25 | Output voltage waveforms for cascaded H-Bridge multilevel inverter<br>by employing single-phase transformers                                                                                                                                                                    |     |

| 3.26 | Output voltage waveforms for cascaded H-Bridge multilevel inverter<br>by employing cascaded transformers                                                                                                                                                                        |     |

| 3.27 | Details of FFT Spectra                                                                                                                                                                                                                                                          | 73  |

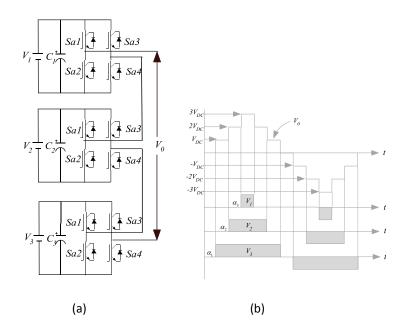

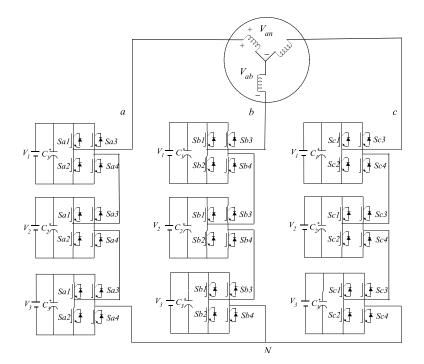

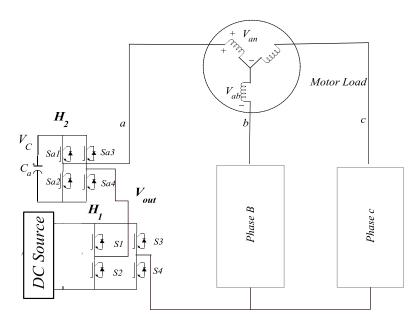

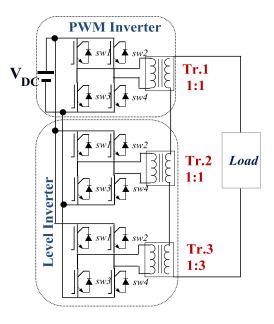

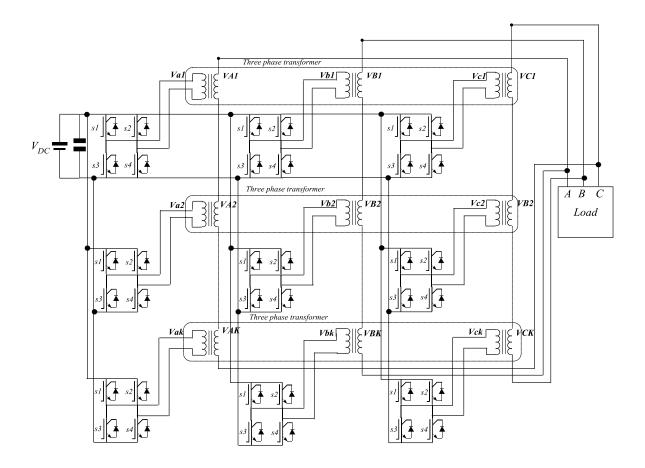

| 4.1  | Proposed multilevel inverter employing three-phase transformer.                                                                                                                                                                                                                 | 76  |

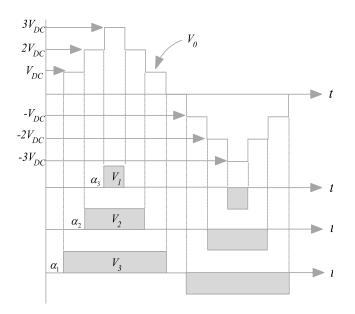

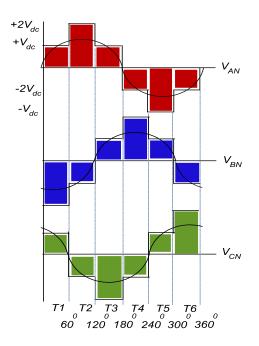

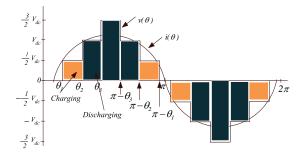

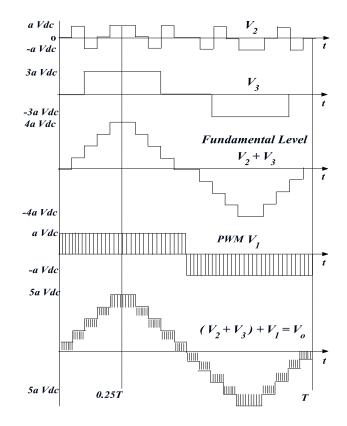

| 4.2  | Details of swithing pattern and output voltage waveform characteristics<br>for CMI with three-phase transformers                                                                                                                                                                | 78  |

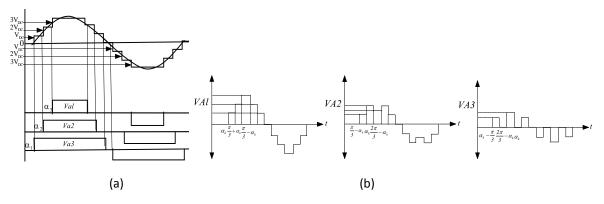

| 4.3  | Details of waveforms for (a) conventional seven level inverter, (b) proposed CMI with three-phase transformers                                                                                                                                                                  | 81  |

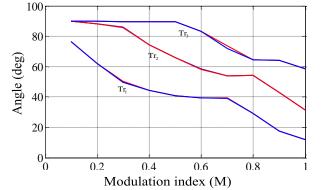

| 4.4  | Variation of switching angles based on different modulation indexes.                                                                                                                                                                                                            |     |

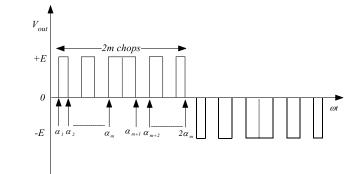

| 4.5  | Details of generalized three-level SHEPWM waveform                                                                                                                                                                                                                              | 84  |

| 4.6  | Details of single H-Bridge Cell b) Unipolar modulation of one arm of<br>H-Bridge of VSC                                                                                                                                                                                         | 87  |

| 4.7  | Details of Prototype set up for the proposed cascaded multilevel<br>converter with three-phase transformers                                                                                                                                                                     | 89  |

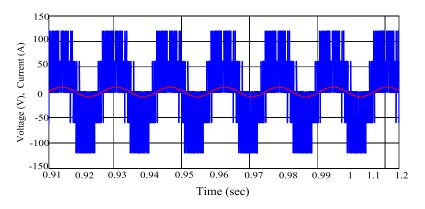

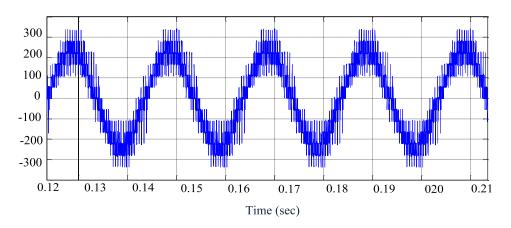

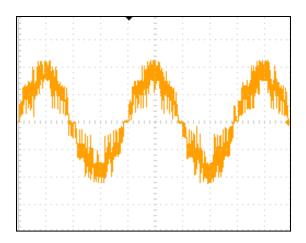

| 4.8  | Performance of the proposed cascaded multilevel inverter with by using by using fundamental frequency approach at modulation index 1, 0.5, and 0.2 (from top to bottom)                                                                                                         | 90  |

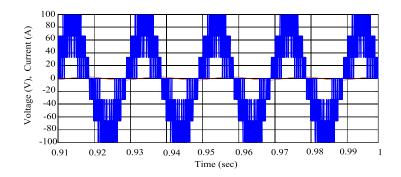

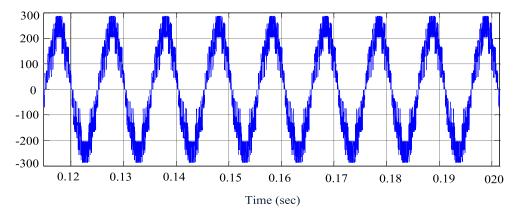

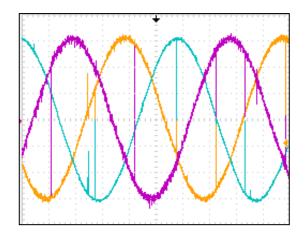

| 4.9  | Performance of the proposed cascaded multilevel inverter with by using selective harmonic PWM approach at Modulation index 1 ,0.5, 0.2 (from top to bottom)                                                                                                                     | 92  |

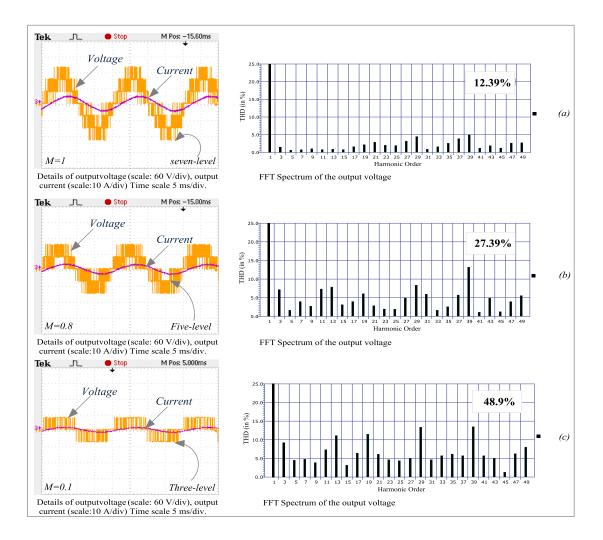

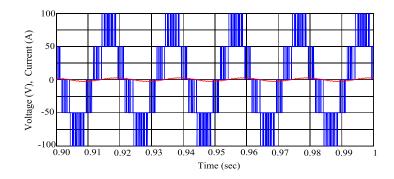

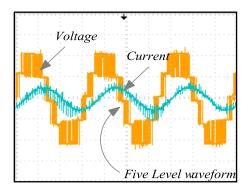

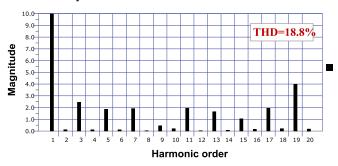

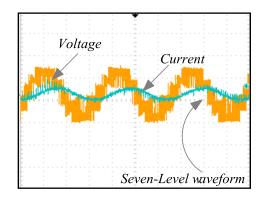

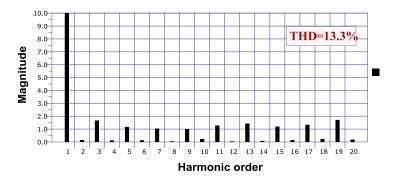

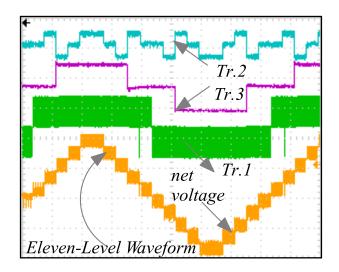

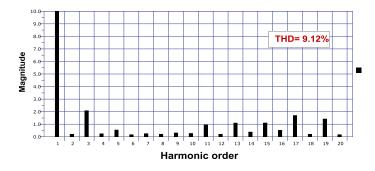

| 4.10 | Performance of the proposed cascaded multilevel inverter with by using sinusoidal PWM approach (a) & (b) Modulation index= 1, (c) & (d) Modulation index = $0.8$ , (e) & (f) Modulation index = $0.6$ , (g) & (h) Modulation index= $0.4$ . (i) & (j) Modulation index= $0.2$ . | 93  |

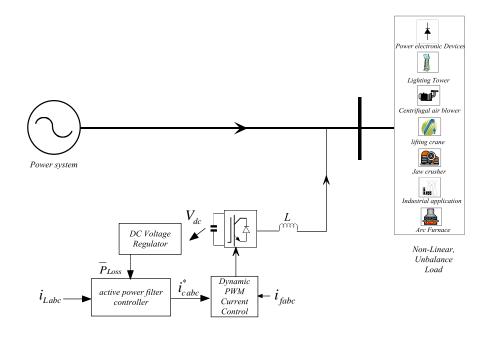

| 5.1  | Simplified diagram of Active Power filter applied to non-linear loads in<br>the power system                                                                                                                                                                                    | 100 |

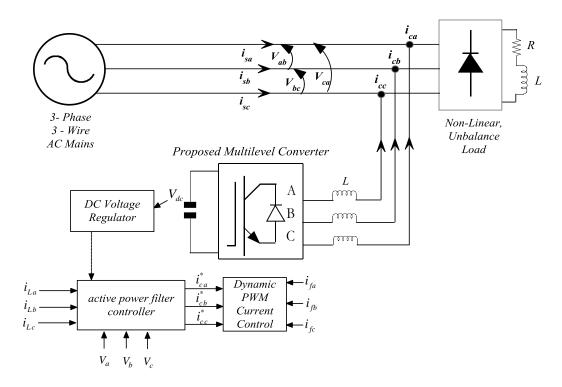

| 5.2  | Block diagram of power network.                                                                                                                                                                                                                                                 | 101 |

| 5.3  | Simplified system under steady state.                                                                                                                                                                                                                                             | 102 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Control block diagram for proposed APF.                                                                                                                                                                                                                                           | 103 |

| 5.5  | Voltage and current vectors in stationary and rotating reference frames.                                                                                                                                                                                                          |     |

| 5.6  | Unipolar modulation of one arm of H-Bridge of VSC                                                                                                                                                                                                                                 |     |

| 5.7  | Step response of capacitor voltage for different valued of $K_P at$<br>$K_I = 0.75$ .                                                                                                                                                                                             | 109 |

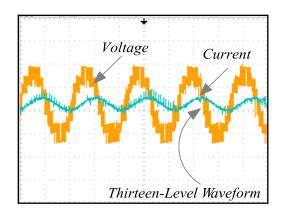

| 5.8  | Details of simulated thirteen-level output waveform.                                                                                                                                                                                                                              |     |

| 5.9  | Details of simulated thirteen-levels filter output waveform.                                                                                                                                                                                                                      | 109 |

| 5.10 | Balanced supply voltages.                                                                                                                                                                                                                                                         | 110 |

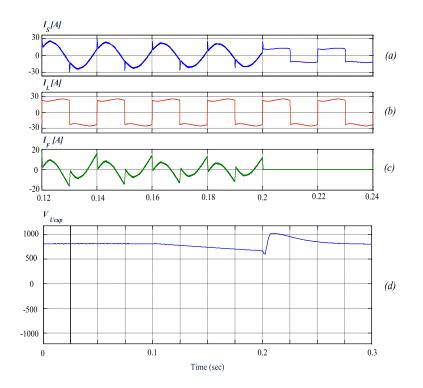

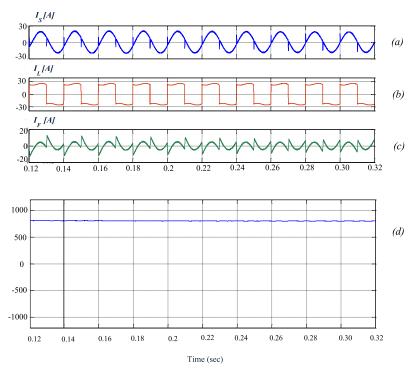

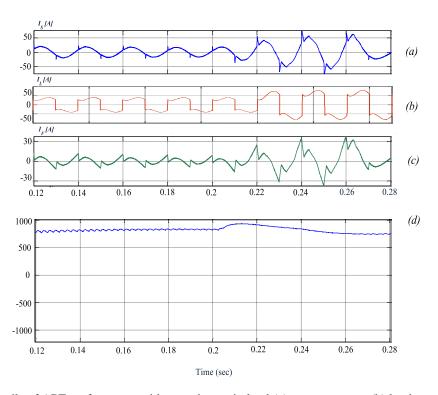

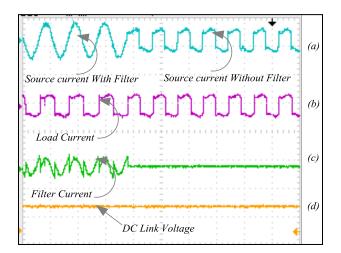

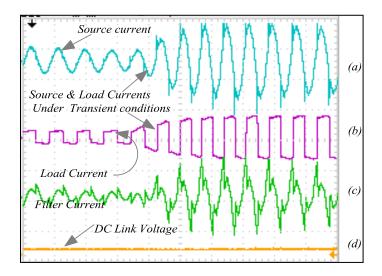

| 5.11 | Details of APF performance (with and without filter) (a) source current<br>(b) load currents (c) filter current and (d) dc capacitor voltage, under<br>balanced condition.                                                                                                        | 110 |

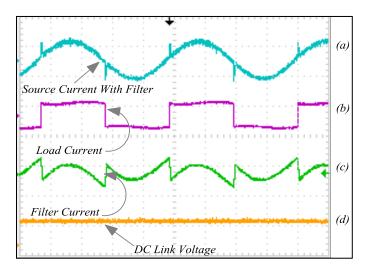

| 5.12 | Details of steady state performance (a) source current (b) load currents<br>(c) filter current and (d) dc capacitor voltage, under balanced condition.                                                                                                                            | 111 |

| 5.13 | <ul> <li>(c) Inter current and (d) de cupacitor voltage, under summed condition.</li> <li>Details of APF performance with step change in load (a) source current</li> <li>(b) load currents (c) filter current and (d) dc capacitor voltage, under balanced condition.</li> </ul> |     |

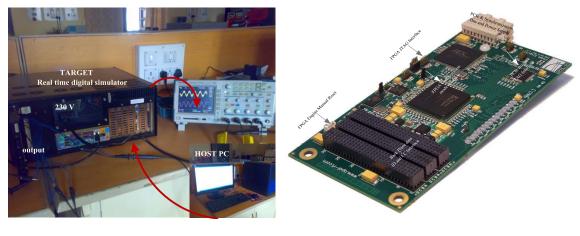

| 5.14 | Details of RTDS Hardware setup b) OP5142 layout and connectors                                                                                                                                                                                                                    |     |

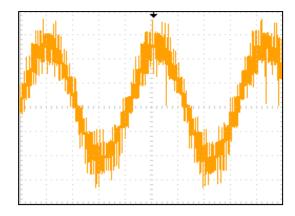

| 5.15 | Detials of output votlage of phase a . scale (100 V/div), Time scale: 5 ms/div.                                                                                                                                                                                                   | 113 |

| 5.16 | Details of thirteen level filter voltage of phase a. scale (100 V/div).<br>Time scale: 5 ms/div                                                                                                                                                                                   | 114 |

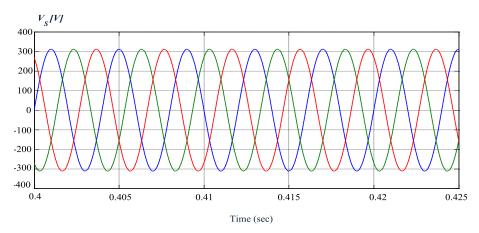

| 5.17 | Detials of balanced supply votlages, scale (100 V/div), Time scale: 10 ms/div.                                                                                                                                                                                                    | 114 |

| 5.18 | Performance of a system (with and without APF) (a) Supply current (scale: 30 A/div). (b) Load current (scale: 30 A/div.). (c) Filter current (scale: 20 A/div.). (d) DC capacitor voltage (800 V) under balanced condition. Time scale: 20 ms/div.                                | 114 |

| 5.19 | Performance of a APF under study state conditions (a) Supply current (scale: 30 A/div). (b) Load current (scale: 30 A/div.). (c) Filter current (scale: 20 A/div.). (d) DC capacitor voltage (800 V). Time scale: 5 ms/div.                                                       | 115 |

| 5.20 | Performance of a system (with and without APF) (a) Supply current (scale: 30 A/div). (b) Load current (scale: 30 A/div.). (c) Filter current (scale: 20 A/div.). (d) DC capacitor voltage (800 V) under balanced condition. Time scale: 25 ms/div.                                | 116 |

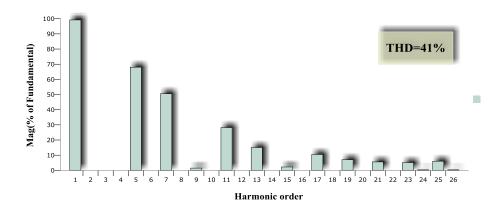

| 5.21 | Details of harmonic spectra of source current before compensation. | 116 |

|------|--------------------------------------------------------------------|-----|

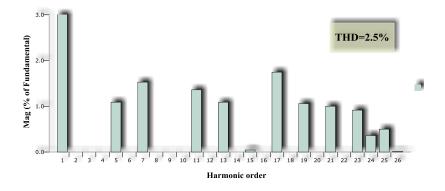

| 5.22 | Details of harmonic spectra of source current after compensation.  | 117 |

#### LIST OF TABLES

| TABLE                                       | PAGE NUMBER |

|---------------------------------------------|-------------|

|                                             |             |

| Table 1.1.Manufacturing Companies of        | 22          |

| Classical and Multilevel Converters         |             |

| Table 1.2.Traditional Multilevel Topologies | 23          |

| and Their Commercial Ratings                |             |

| Table 4.1. Calculated Switching Angle Based | 82          |

| on the Modulation Index                     |             |

| Table 4.2. Hardware specifications          | 89          |

|                                             |             |

| Table 4.3.Components Comparison with        | 95          |

| Conventional Cascade Multilevel Inverter    |             |

| Table 4.4.Components Comparison with        | 96          |

| Conventional Multilevel Inverter            |             |

# Chapter 1

# Introduction

**Research Background**

Investigation on Medium and High Power Inverters

Introduction to Classical Inverters (Two-Level Inverters)

**Introduction to Multilevel Inverters**

Manufacturing companies and overview of multilevel inverters

Motivation

**Dissertation Objectives**

**Dissertation Outline**

#### Chapter 1:

#### **1.1 Research Background**

Multilevel inverters have been under research and development for more than three decades and have found successful industrial applications. However, this is still a technology under development, and many new contributions and new commercial topologies have been reported in the last few years. The aim of this dissertation is to group and review recent contributions, in order to establish the current state of the art and trends of the technology to provide readers with a comprehensive and insightful review of where multilevel converter technology stands and is heading. This chapter first presents a brief overview of wellestablished multilevel inverters strongly oriented to their current state in industrial applications and then centers the discussion on the new multilevel inverters that have made their way into the industry. Multilevel inverters have been attracting increasing interest recently the main reasons are; increased power ratings, improved harmonic performance, and reduced electromagnetic interference (EMI) emission that can be archived with multiple dc levels that are synthesis of the output voltage waveform. In particular multilevel inverters have abundant demand in applications such as medium voltage industrial drives, electric vehicles, and grid connected photovoltaic systems. The present work provides a solution to design an efficient multilevel topology which is suited for medium and high power applications. In the subsequent sections the research background is discussed in detailed. Motivation and objectives are clearly outlined.

#### **1.2 Medium and High Power Inverters**

There are different power converter topologies and control strategies used in inverter designs. Different design approaches address various issues that may be more or less

important depending on the way that the converter is intended to be used. The issue of waveform quality is one the important concern and it can be addressed in many ways. In practice capacitors and inductors can be used to filter the waveform [1-2]. If the design includes a transformer, filtering can be applied to the primary or the secondary side of the transformer or to both sides. Low-pass filters are applied to allow the fundamental component of the waveform to pass to the output while limiting the passage of the harmonic components. Thus quality of waveform can be adjusted. Note that, normal inverters always generate very low quality output waveforms. To make the output waveform qualitative, low pass (LC filter) are often added in the circuit. Thus, at this point of time readers might have a question that, why the quality of converter output is low? And why Low pass filter are frequently added in the circuit. Further, what kinds of solutions are available to increase quality of output waveform without losing its efficiency? All this are open problems associated with present day inverters. However, eventually all this will be addressed in this thesis. But at first we try to figure out the converter applications from low power to high power and then we summarize the requirements to meet the high power demand. Finally we try to present the problems and solutions available to meet the high power demand.

Consider Table 1.1, which presents the important applications from low power to high power range. From Table 1.1 it is quite predictable that, power inverters are an enabling technology. They are potentially useful for a wide range of applications like; low power devices, home appliances, electric vehicles, photovoltaic, transport (train traction, ship propulsion, and automotive applications), and energy conversion, manufacturing, mining, and petrochemical applications. The inverters mentioned in Table 1.1 are available in a wide range. Note that, either it may be suited for DC or AC. But, at present industries are in chase of finding new type of power converter for medium to high power range, moreover it seems to be challenging issues for present generation researchers.

#### TABLE 1.1

#### Summary of Power Inverters

|                                                  | Low Power Medium Power                 |                                                         | High Power                                                              |

|--------------------------------------------------|----------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------|

| Power Range                                      | Up to 2 KW                             | 2-500 KW                                                | More Than 500 KW                                                        |

| Usual Converter Topologies ac/dc, dc/dc ac/dc, d |                                        | ac/dc, dc/dc, dc/ac                                     | ac/dc, dc/ac                                                            |

| Typical Power Semiconductors                     | MOSFET                                 | MOSFET, IGBT                                            | IGBT, IGCT, Thyristor                                                   |

| Technology Trend                                 | High Power Density,<br>High Efficiency | Small Volume and Weight Low Cost and<br>High Efficiency | High Nominal Power of the Converter high<br>Power Quality and Stability |

| Typical Applications                             | Lower-Power Devices                    | Electric Vehicles         Roof PV                       | Transportation<br>Renewable Energy Industry                             |

Although research pioneers have built a numerous power inverters, but still researchers are in look for a new sort of architecture which can produce high quality waveform with less number of components. In other terms improving power quality is the greatest requirement. By considering above aspects, let us make an outline regarding the demanding aspects of power inverters, particular in Medium and high power range.

#### **1.3 Challenging Aspects in Medium and High Power Inverters**

The current energy arena is changing. The feeling of dependence on fossil fuels and the progressive increase of its cost is leading to the investment of huge amounts of resources, economical and human, to develop new cheaper and cleaner energy resources not related to fossil fuels [3]. In fact, for decades, renewable energy resources have been the focus for researchers, and different families of power inverters have been designed to make the integration of these types of systems into the distribution grid a current reality. Besides, in the transmission lines, high-power electronic systems are needed to assure the power distribution and the energy quality. Therefore, power electronic inverters have the responsibility to carry out these tasks with high efficiency. The increase of the world energy demand has entailed the appearance of new power converter topologies and new semiconductor technology capable to drive all needed power. A continuous race to develop higher-voltage and higher-current power semiconductors to drive high-power systems still goes on. However, at present there is tough competition between the use of classic power converter topologies using high-voltage semiconductors and new converter topologies using medium-voltage devices. Power inverters are an amazing technology for industrial practice powered by electric drive systems. They are potentially helpful for a wide range of applications: transport (train traction, ship propulsion, and automotive applications), energy conversion, manufacturing, mining, and petrochemical, to name a few. Many of these processes have been continuously raising their demand of power to reach *higher production rates, cost reduction* (large-scale economy), and *efficiency* [4].

The power electronics research community and industry have reacted to this demand in two different ways: developing semiconductor technology to reach higher nominal voltages and currents (currently 8 kV and 6 kA) while maintaining traditional converter topologies (mainly two-level voltage and current source inverters); and by developing new converter topologies, with traditional semiconductor technology, known as *multilevel inverters* [5]. The first approach inherited the benefit of well known circuit structures and control methods. Adding to that, the newer semi-conductors are more expensive, and by going higher in power, other power-quality requirements have to be fulfilled, thereby there may be need of additional power filters. Therefore it will be quite feasible to choose to build a new converter topology based on multilevel concept. This is the challenging issue right now.

#### 1.4 Concept of Classical Inverters (Two-Level Inverters)

At present there is tough competition between the use of classic power converter topologies using high-voltage semiconductors and new converter topologies using mediumvoltage devices. This idea is shown in Fig.1.1, where inverters are built by adding devices in series. In past, these inverters are only viable options for medium and high-power applications. But in present scenario, multilevel technology with medium voltage semiconductors are fighting in a development race with classic power inverters using highpower semiconductors, which are under continuous development and are not mature. Although, classical inverters are good for low power applications, but they fail to fill the requirements of high-power levels.

Fig.1.1 Classical converter and output waveform

In view of later, to retrieve the demerits of classical inverters we should know about the multilevel technology and the merits it offer. Multilevel inverters are a good alternative for power applications due to the fact that, they can achieve high power using mature medium-power semiconductor technology. Practically, multilevel inverters present great advantages compared with conventional and very well-known two-level converter. These advantages are fundamentally focused on improvements in the output signal quality (Voltage & Current) and a nominal power increase in the converter [6].

These properties make multilevel inverters very attractive to the industry and, nowadays, researchers all over the world are spending great efforts trying to improve multilevel converter performances such as the control simplification and the performance of different optimization algorithms in order to enhance the THD [7] of the output signals, the balancing of the dc capacitor voltage [8], and the ripple of the currents. For instance, nowadays researchers are focused on the harmonic elimination using pre-calculated switching functions, harmonic mitigation to fulfill specific grid codes, the development of *new multilevel converter* topologies (hybrid or new ones), and new control strategies [9]. However, before introducing about the multilevel inverters, let's make an overview about the classical inverters and their problems. To address the problems of conventional inverters, one should have an idea about the Medium to high-power range inverters and related challenging issues. Below are some of the facts summarized.

- At present, application power range of inverter circuits using the basic "inverter leg" building block is vast (<1 kW to 10 MW+)</li>

- Very large application area is in industrial (PWM controlled induction motor) drives (See Fig.3) are around 3 kW to 100 kW power range. IGBT devices are used almost exclusively in this power range.

- Recently the application area for these circuits has extended to power levels (>1 MW), Most importantly,

- (a) Railway locomotives (1-5 MW)

- (b) Ship propulsion (e.g. Frigate 20 MW)

- (c) Power systems applications, for example FACTS (Flexible AC Transmission Systems) - see H5CPNW - up to 100 MW+

- 4. Above all applications use devices like: IGBT (Insulated Gate Bipolar Transistor), GTO (Gate Turn-off Thyristor), IGCT (Insulated Gate Commutated Thyristor). However, design of these high power inverters (MW range) presents serious problems:

- (a) Single devices can't handle the V and I.

- (b) For example a 1 MW drive would be typically supplied at 3.3 kV (UK) or 4.16 kV (US) giving a DC link of 5 to 7 kV. The voltage supplied to the motor is also 3.3 kV (or 4.16 kV).

- (c) Device voltage rating required 8-10 kV not available.

- (d) Handling high currents by putting devices (or inverters) in parallel is fairly well established. Getting the voltage handling capability remains the problem.

Thus to solve above mentioned problems some of the conventional solutions too available, and solutions are;

- 1. Using standard converter topologies with devices in series.

- 2. Using alternative topology inverters which a number of low voltage devices and that have some means for distributing the voltage stress amongst those devices (Multi-level inverters).

Anyhow first case is demonstrated in Fig.1.1. Observe the arrangement (it is also called as classical converter); it uses the semiconductor devices in series [10]. In other sense, by adding devices in series voltage capability is increasing [11]. Somehow with this

arrangement inverters can meet high power demand. But one of the greatest limitations is the output voltage quality. However with classical arrangement converter has the potential to generate only two level output. In fact such kind of waveforms composes with huge harmonic content. Particularly low order harmonics like  $3^{rd}$ ,  $5^{th}$ ,  $7^{th}$ , .etc. This harmonics drastically affects the equipment performance. Frequently, to suppress such harmonics several low filters are used to improve the quality at the output end. But filter size is still greater in extent if the quality is poor. Additionally, a well known fact is that, designing *Low Pass Filter* is a hectic job and it is bulky in nature too. Plenty of research is going on this subject i.e., to reduce the filter size in the circuits [12-13]. Overall from above prospects we can summarize some of the problems of classical inverters as follows:

- (a) The entire DC voltage appears across each switch when it is off. This will be greater than the voltage rating of the individual devices.

- (b) The devices will not automatically share the voltage in the off state because of differences in leakage current - high value parallel resistors can be used to overcome this (static sharing).

- (c) More seriously, the devices will not share the voltage during switching due to variations in switching speed. Special gate drive techniques and/or special snubbers are required (dynamic sharing). Not well established yet.

- (d) Two level output causes very large voltage steps on the load can be a problem for motor insulation.

- (e) Harmonic content (distortion) is larger for a given switching frequency than with multi-level techniques (given in next section)

On the flip side, classical inverters too have finite advantages those are:

- a. Standard PWM techniques can be used.

- b. Number of power circuit components is less as compared to other (multi-level) circuits.

- c. Redundancy can be incorporated (to improve reliability) by using more series devices than actually required the circuit can then still work if one fails.

However with this demonstration it is clear that conventional inverters have huge drawbacks than merits. So alternative solution to meet the high power demand is through multilevel concept.

#### **1.5 Concept of Multilevel Inverters**

Multilevel inverter includes an array of power semiconductor devices and capacitors voltage sources, the output of which generates voltages with stepped waveforms [14-15]. The commutation of the switches permits the addition of the capacitor voltages to obtain high-voltage at the output, while the power semiconductors have to withstand only reduced voltages.

Fig.1.2 shows a schematic diagram of one phase leg of inverters with different numbers of levels, for which the action of power semiconductors is represented by an ideal switch with several positions. Form Fig.1.3, we can observe a two level inverter generates an output voltage with two values (levels) with respect to negative terminal of the capacitor. While the three level inverter generates three voltages, and a nine-level inverter generates a nine level output voltages. In all this cases devices are not arranged in series but they are arranged in such way that, they gain the capability to generate such kind of voltages. Herein, we should remember one important thing i.e. as the number of steps increases in the output waveforms; harmonic content comes down [16]. Thus power quality of such waveforms will increase drastically. However, in order to generate step kind of waveforms in output side, different *Multilevel* based archetypes are successfully built and verified. But general principle

Fig.1.2 Converter output voltage waveforms a) two level b) three level c) nine level

of multilevel inverters is the synthesis of the ac voltage from several different voltage levels on the dc bus. As the number of voltage levels on the input dc side increases, the output voltage adds more steps [17-19], which approach the sinusoidal wave. However, from above thought, to present a general idea about the steps in the output waveform, consider m to be the number of steps of the phase voltage with respect to the negative terminal of the inverter, and then the number of steps in the voltage between two phases of the load K is given by equation A and B: And the number of steps P in the phase voltage of a three phase load in wye connection is

$$P = 2k - l \tag{1.2}$$

The term multilevel starts with the three-level inverter introduced by the Nabae et al.[15]. However topologically, multilevel inverters are largely divided into many configurations. The most common multilevel converter topologies are the neutral-point-clamped converter (NPC) [15], flying capacitor converter (FC) [18], and Cascade H-Bridge (CHB).

At present these inverters are highly visible in all Medium voltage drives, grid connected systems and FACTS devices. An extensive survey has been done on the multilevel inverters; these are addressed in the next chapter. However, at this point of time it is clear that, multilevel inverters are one of the best option for Medium and high power applications [19]. Now a question may arise; are there any other inverters which are competitive to multilevel inverters? Obviously the answer is yes. Any how to resolve this question and for a better idea, a complete list of high-power inverters are demonstrated in Fig.1.3. However, the main competitors of multilevel technology are: the cycloconverter and load commutated inverters (LCIs).

Other high-power converter topologies like current source and matrix inverters are also observed in the classification. Although they are capable of meeting high power demand, but they are less preferred because of their limited merits. However, some of which have recently found practical application and this content is not discussed in this dissertation as it is mentioned that, study is confined to only multilevel structures. Operating principles, multilevel waveform generation, special characteristics, modulation schemes, and other information related to the NPC, FC, and CHB are demonstrated subsequently.

Fig.1.3 Classification of high-power inverters

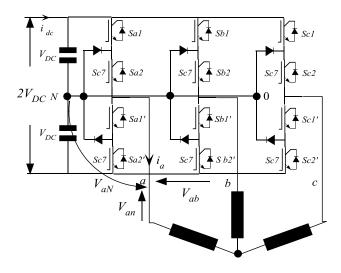

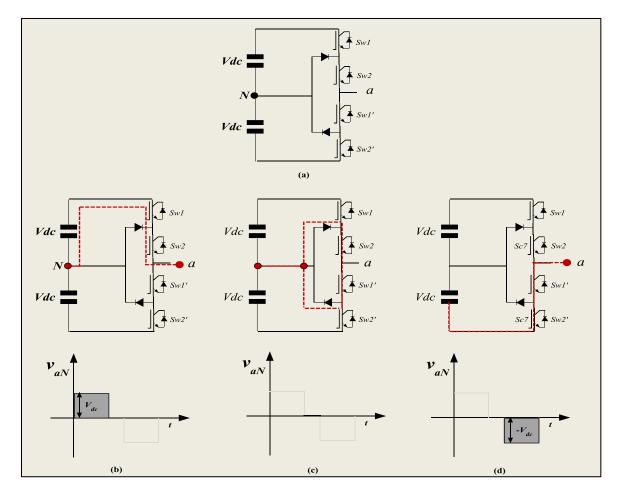

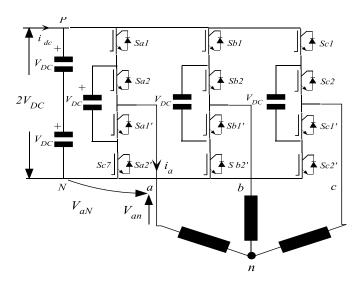

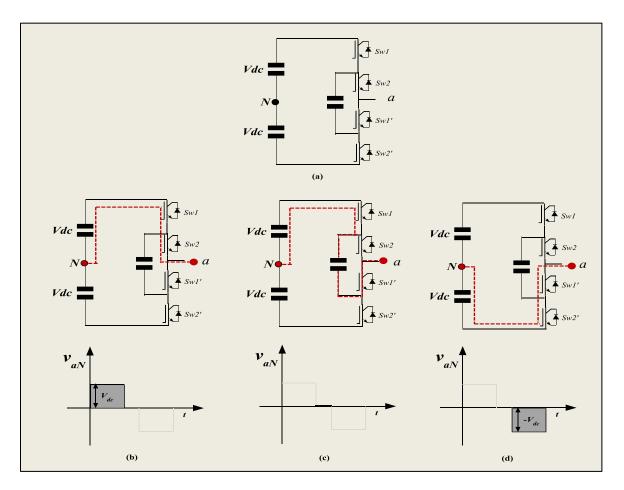

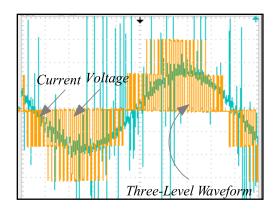

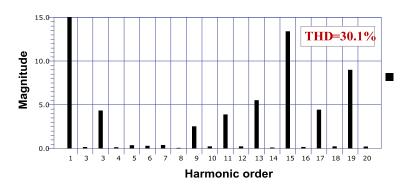

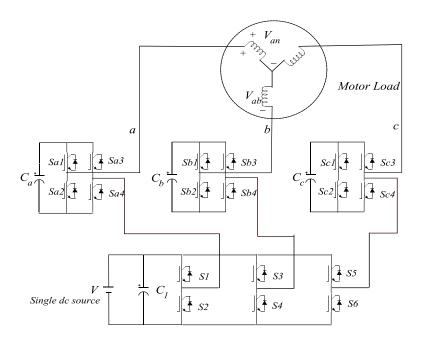

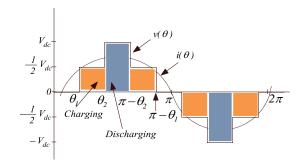

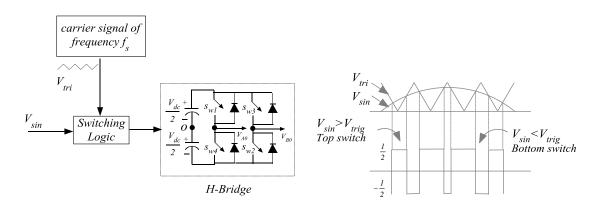

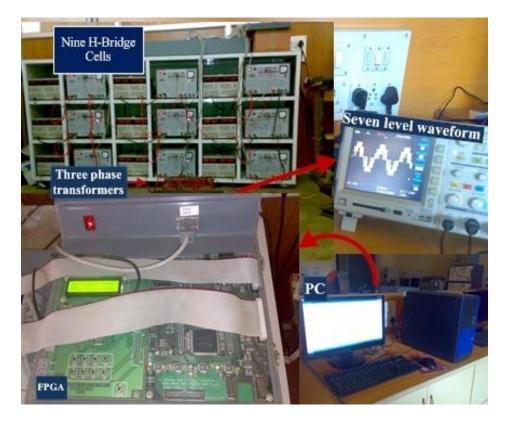

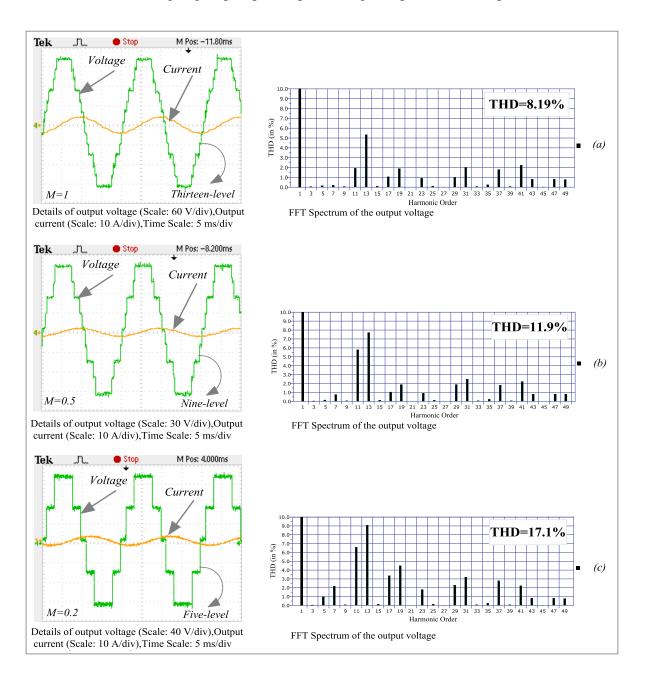

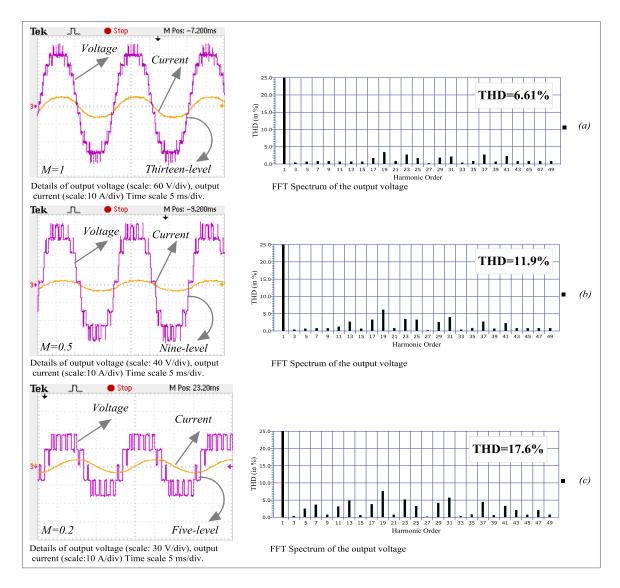

At first, preliminary studies on multilevel inverters have been performed using threelevel inverter that has been proposed by Nabae. In the study, the third level has been constituted by using neutral point of DC line and the topology has been defined as diode clamped (DC) converter [34 35]. Since the first multilevel converter was patented in 1975, many different multilevel inverter topologies have been introduced and analyzed by different authors. An interesting survey of this kind of device is presented in [36].