## **REAL TIME IMPLEMENTATION OF DES ALGORITHM BY USING TMS3206713 DSK.**

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

**Master of Technology**

in

### **Telematics & Signal Processing**

By

**B.Rajesh**

Department of Electronics and Communication Engineering National Institute Of Technology Rourkela

2008

# REAL TIME IMPLEMENTATION OF DES ALGORITHM BY USING TMS3206713 DSK.

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Master of Technology

in

### **Telematics & Signal Processing**

Ву

**B.Rajesh**

Under the Guidance of

Prof. G.S.Rath.

# Department of Electronics and Communication Engineering

National Institute Of Technology

Rourkela

2008

### National Institute Of Technology Rourkela

### CERTIFICATE

This is to certify that the thesis entitled, "**Real Time Implementation of DES Algorithm by using TMS320C6713 DSK**" submitted by **B.Rajesh** in partial fulfillment of the requirements for the award of Master of Technology Degree in **Electronics & communication Engineering** with specialization in "**Telematics & Signal Processing**" at the National Institute of Technology, Rourkela (Deemed University) is an authentic work carried out by him under my supervision and guidance.

To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University / Institute for the award of any Degree or Diploma.

Prof. G.S.Rath. Dept. of Electronics & Communication Engg. National Institute of Technology Rourkela-769008

Date: 29-05-2008.

### **Acknowledgement**

First of all, I would like to express my deep sense of respect and gratitude towards my advisor and guide **Prof. G. S. Rath**, who has been the guiding force behind this work. I am greatly indebted to him for his constant encouragement, invaluable advice and for propelling me further in every aspect of my academic life. His presence and optimism have provided an invaluable influence on my career and outlook for the future. I consider it my good fortune to have got an opportunity to work with such a wonderful person.

Next, I want to express my respects to **Prof. G. Panda, Prof. K. K. Mahapatra, Prof. S.K. Patra** and **Dr. S. Meher** for teaching me and also helping me how to learn. They have been great sources of inspiration to me and I thank them from the bottom of my heart.

I would like to thank all faculty members and staff of the Department of Electronics and Communication Engineering, N.I.T. Rourkela for their generous help in various ways for the completion of this thesis.

I would also like to mention the names of **madhu** and **arun** for helping me a lot during the thesis period.

I would like to thank all my friends and especially my classmates for all the thoughtful and mind stimulating discussions we had, which prompted us to think beyond the obvious. I've enjoyed their companionship so much during my stay at NIT, Rourkela.

I am especially indebted to my parents for their love, sacrifice, and support. They are my first teachers after I came to this world and have set great examples for me about how to live, study, and work.

> **Rajesh.B** Roll No: 20607025 Dept of ECE, NIT, Rourkela

## Contents

| 1. Certificate                                                                                                                                                                                                                                                                      | 1                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2. Acknowledgement                                                                                                                                                                                                                                                                  | 4                                |

| 3. Abstract.                                                                                                                                                                                                                                                                        | 7                                |

| 4. List of figures                                                                                                                                                                                                                                                                  | 8                                |

| 5. List of tables                                                                                                                                                                                                                                                                   | 9                                |

| 6. Introduction                                                                                                                                                                                                                                                                     | 10                               |

| 7. Chapter 1<br>Data Encryption Standard Algorithm<br>1.1 DES Model<br>1.2 Sixteen Rounds of DES                                                                                                                                                                                    | 13<br>14                         |

| <ul> <li>8. Chapter 2</li> <li>Introduction to TMS320C6713 DSK</li> <li>2.1 Introduction</li> <li>2.2 DSK Support Tools</li> <li>2.2.1 DSK Board</li> <li>2.2.2 TMS320C6713 Digital Signal Processor</li> <li>2.3 Code Composer Studi006F</li> <li>2.4 Quick Test of DSK</li> </ul> | 19<br>20<br>21<br>23<br>23<br>24 |

| <ul> <li>9. Chapter 3 <ul> <li>Input and Output with DSK</li> <li>3.1 Introduction</li> <li>3.2 TLV320AIC23 (AIC23) Onboard Stereo Codec for Input and Output</li> <li>3.3 Programming Examples Using C Code</li> </ul> </li> </ul>                                                 | 27<br>28<br>30                   |

| <ul> <li>10. Chapter 4         <ul> <li>Architecture and Instruction set of the C6x processor</li> <li>4.1 Introduction</li> <li>4.2 TMS320C6x Architecture</li> <li>4.3 Functional Units</li> <li>4.4 Fetch and Execute Packets</li> </ul> </li> </ul>                             | 50<br>52<br>53<br>57             |

| 4.5 Pipelining                           | 58 |

|------------------------------------------|----|

| 4.6 Registers                            | 60 |

| 4.7 Linear and Circular Addressing Modes | 61 |

| 4.7.1 Indirect Addressing                | 61 |

| 4.7.2 Circular Addressing                | 62 |

| 4.8 TMS320C6713 Instruction set          | 64 |

| 4.8.1 Assembly code format               | 64 |

| 4.8.2 Types of Instruction set           | 65 |

### 11. Chapter 5

| Real Time implementation of DES Algorithm by using                    |  |

|-----------------------------------------------------------------------|--|

| TMS320C6713 Processor                                                 |  |

| 5.1 Implementation of DES Algorithm for Voice by using TMS320C6713 69 |  |

| Processor.                                                            |  |

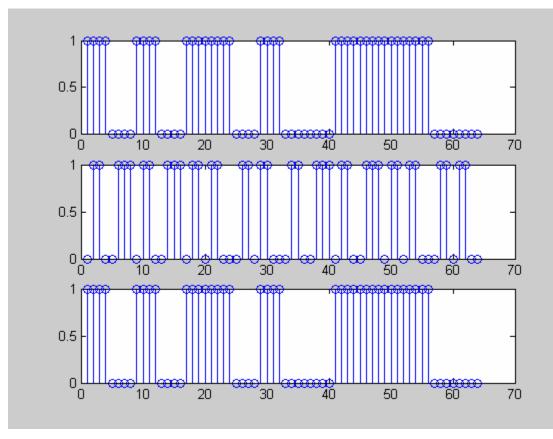

| 5.2 Matlab Results.70                                                 |  |

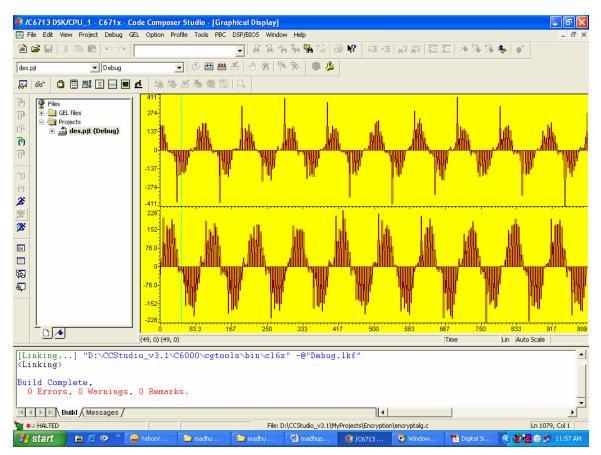

| 5.3 CCS Results.72                                                    |  |

| <b>12. Conclusion.</b> 74                                             |  |

| 13. References. | 75 |

|-----------------|----|

|                 |    |

### **ABSTRACT**

The data encryption standard (DES) is an algorithm that was formerly considered to be the most popular method for private key encryption. DES is still appropriate for moderately secured communication. In this project I have implemented DES algorithm for voice data encryption by using the Texas Instruments TMS320C6713 dsp processor. TMS320C6713 is a 32-bit floating point dsp processor which is one of the Texas TMS320C6x family. Digital signal processors such as the TMS320C6x (C6x) family of processors are like fast special-purpose microprocessors with a specialized type of architecture and an instruction set appropriate for signal processing. The architecture of the C6x digital signal processor is very well suited for numerically intensive calculations. Based on a very-long-instruction-word (VLIW) architecture, the C6x is considered to be TI's most powerful processor.

## List of figures:

| a. | Fig 1.1: DES Model.                                                                  | 13  |

|----|--------------------------------------------------------------------------------------|-----|

| b. | Fig 1.2: Encryption process—one round.                                               | 15  |

| c. | Fig 1.3: Core f-function of DES.                                                     | 17  |

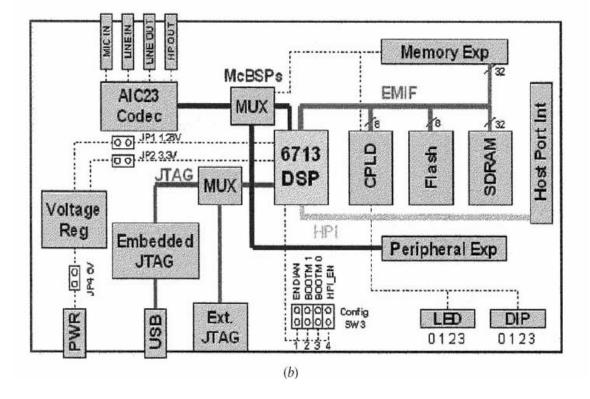

| d. | Figure 2.0: TMS320C6713-based DSK board: (a) board; (b) diagram                      | 22. |

|    | (Courtesy of Texas Instruments)                                                      |     |

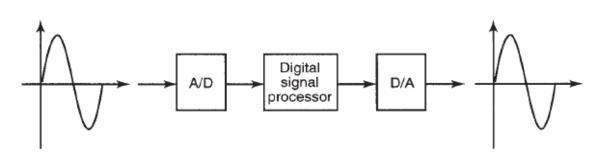

| e. | Figure 2.1: DSP System with input and output.                                        | 28  |

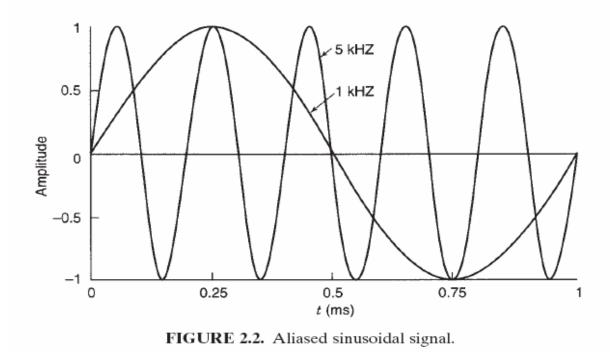

| f. | Figure 2.2: Aliased sinusoidal signal.                                               | 28  |

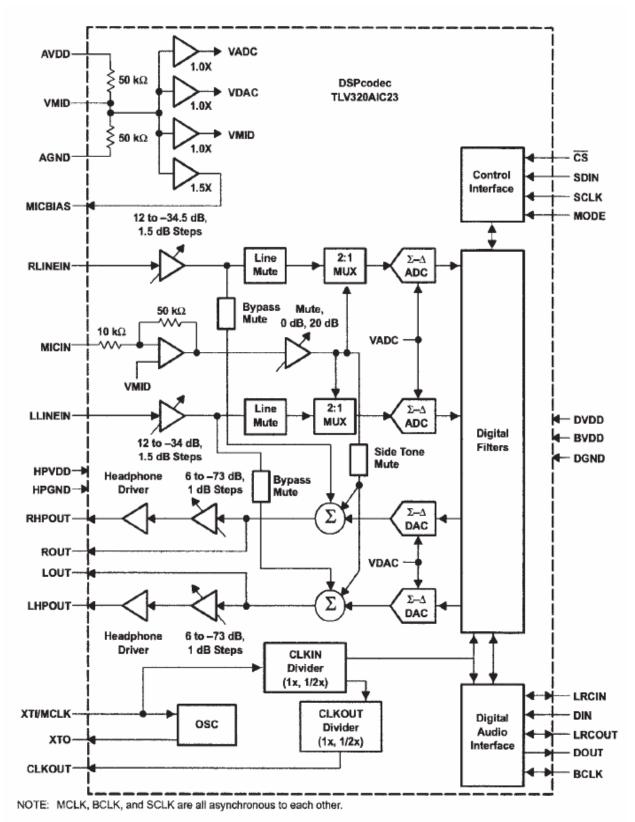

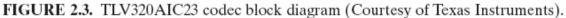

| g. | Figure 2.3: TLV320AIC23 codec block diagram.                                         | 31  |

| h. | Figure 2.4: Loop program using interrupt (loop_intr.c).                              | 32  |

| i. | Figure 2.5: Loop program using polling (loop_poll.c).                                | 35  |

| j. | Figure 2.6: Loop program with stereo input and output (loop_stereo.c).               | 37  |

| k. | Figure 2.7: Sine generation with stereo outputs (sine_stereo.c).                     | 38  |

| 1. | Figure 2.8: Sine generation making use of two sliders to control the                 | 40  |

|    | amplitude and frequency of the sine wave generated (sine2sliders.c).                 |     |

| m. | Figure 2.9: GEL file with two slider functions to control the amplitude              | 41  |

|    | and frequency of the sine wave generated (sine2sliders.gel).                         |     |

| n. | Figure 2.10: Loop program with input data stored in memory                           | 42  |

|    | (loop_store.c).                                                                      |     |

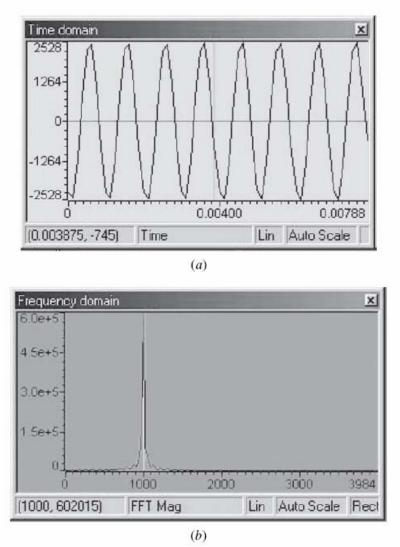

| 0. | Figure 2.11: CCS graphs with the <i>loop_store</i> program: ( <i>a</i> ) time-domain | 43  |

|    | plot of stored input data representing a 1-kHz sine wave; (b) FFT                    |     |

|    | magnitude of stored data representing a 1-kHz sine wave.                             |     |

| p. | Figure 2.12: Loop program to store I/O data in memory and in a file                  | 44  |

|    | (loop_print.c).                                                                      |     |

| q. | Figure 2.13: Square-wave generation program (squarewave.c).                          | 47  |

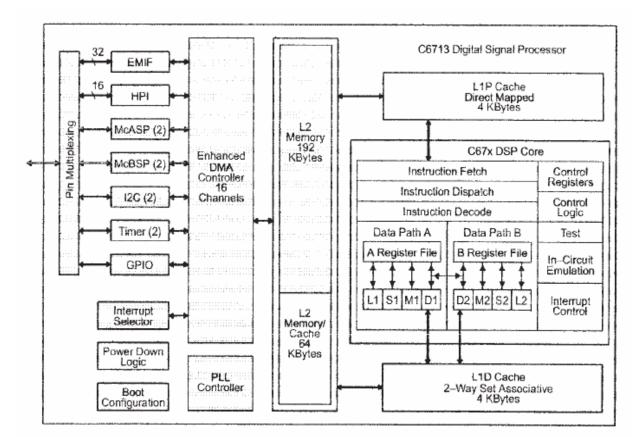

| r. | Figure 3.1: Functional Block Diagram of TMS320C6713.                                 | 54  |

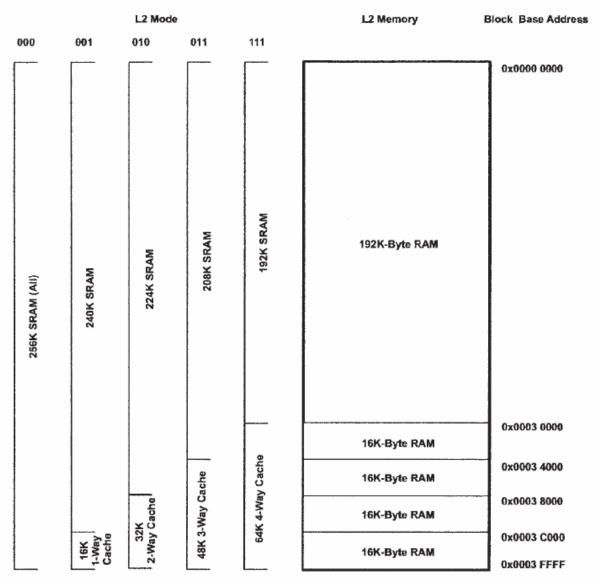

| s. | Figure 3.2: Internal memory configuration of L2.                                     | 55  |

| t. | Figure 3.3: One FP with three EPs showing "p" bit of each instruction.               | 57  |

| u. | Matlab plots for DES algorithm.                                                      | 71  |

| v. | CCS plots for DES.                                                                   | 72  |

### List of tables:

| a. | Table 1.1: Initial permutation table.  | 14 |

|----|----------------------------------------|----|

| b. | Table 1.2: Expansion of 32 bits to 48. | 15 |

| c. | Table 1.3: S-Box example, S1           | 16 |

| d. | Table 1.4: P-BOX.                      | 16 |

| e. | Table 3.1: Memory map.                 | 56 |

| f. | Table 3.2: Pipeline Phases.            | 59 |

| g. | Table 3.3: Pipelining Effects.         | 59 |

| h. | Table 3.4: AMR Mode and Decryption.    | 63 |

### **INTRODUCTION**

Cryptography is the art of communicating with secret data. In voice communication, cryptography refers to the encrypting and decrypting of voice data through a possibly insecure data line. The goal is to prevent anyone who does not have a "key" from receiving and understanding a transmitted message.

The data encryption standard (DES) is an algorithm that was formerly considered to be the most popular method for private key encryption. DES is still appropriate for moderately secured communication.

IN this project I have implemented DES algorithm to voice data by using the TMS320C6713 dsp processor. TMS320C6713 is a 32-bit floating point dsp processor which is one of the Texas TMS320C6x family. Digital signal processors such as the TMS320C6x (C6x) family of processors are like fast special-purpose microprocessors with a specialized type of architecture and an instruction set appropriate for signal processing. The architecture of the C6x digital signal processor is very well suited for numerically intensive calculations. Based on a very-long-instruction-word (VLIW) architecture, the C6x is considered to be TI's most powerful processor.

Digital signal processors are used for a wide range of applications, from communications and controls to speech and image processing. The general-purpose digital signal processor is dominated by applications in communications (cellular). Applications embedded digital signal processors are dominated by consumer products. They are found in cellular phones, fax/modems, disk drives, radio, printers, hearing aids, MP3 players, high-definition television (HDTV), digital cameras, and so on.

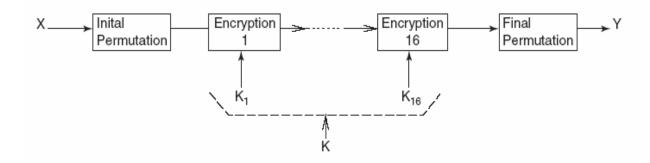

DES is a bit-manipulation technique with a 64-bit block cipher that uses an effective key of 56 bits. It is an iterated Feistel-type cipher with 16 rounds. The general model of DES has three main components for: (1) initial permutation; (2) encryption—the core iteration/*f*-function (16 rounds); and (3) final permutation.

This thesis consists of five chapters. For processing this project first there is a need of knowing about the TMS320C6713 dsp processor that means we want to know about its architecture and how its take inputs and how its produce outputs etc. that's why in second chapter I have explained about the total architecture of TMS320C67 processor and in third chapter I have explained how this processor takes inputs and how its produce outputs and in fourth chapter I have explained about the architecture and instruction set of TMS320C67 processor. In fourth chapter I have explained about the about the architecture and instruction set of TMS320C67 processor.

# **CHAPTER-1**

**Data Encryption Standard Algorithm**

### 1.1 DES Model

Cryptography is the art of communicating with secret data. In voice communication, cryptography refers to the encrypting and decrypting of voice data through a possibly insecure data line. The goal is to prevent anyone who does not have a "key" from receiving and understanding a transmitted message.

The data encryption standard (DES) is an algorithm that was formerly considered to be the most popular method for private key encryption. DES is still appropriate for moderately secured communication.

DES is a bit-manipulation technique with a 64-bit block cipher that uses an effective key of 56 bits. It is an iterated Feistel-type cipher with 16 rounds. The general model of DES has three main components for (see Figure 4.1): (1) initial permutation; (2) encryption—the core iteration/*f*-function (16 rounds); and (3) final permutation. *X* and *Y* are the input and output data streams in 64-bit block segments, respectively, and *K*1 through *K*16 are distinct keys used in the encryption algorithm. The initial permutation is based on the predefined Table 1.1. The value at each position is used to scramble the input before the encryption routine. For example, the 58<sup>th</sup> data to be moved into the first position

#### Fig 1.1: DES Model

| IP |    |    |    |    |    |    |   |  |  |  |  |

|----|----|----|----|----|----|----|---|--|--|--|--|

| 58 | 50 | 42 | 34 | 26 | 18 | 10 | 2 |  |  |  |  |

| 60 | 52 | 44 | 36 | 28 | 20 | 12 | 4 |  |  |  |  |

| 62 | 54 | 46 | 38 | 30 | 22 | 14 | 6 |  |  |  |  |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |  |  |  |  |

| 57 | 49 | 41 | 33 | 25 | 17 | 9  | 1 |  |  |  |  |

| 59 | 51 | 43 | 35 | 27 | 19 | 11 | 3 |  |  |  |  |

| 61 | 53 | 45 | 37 | 29 | 21 | 13 | 5 |  |  |  |  |

| 63 | 55 | 47 | 39 | 31 | 23 | 15 | 7 |  |  |  |  |

**Table 1.1: Initial permutation table:**

of a 64-bit array, the 50th bit into position 2, and so on. The input stream is permutated using a nonrepetitive random table of 64 integers (1-64) that corresponds to a new position of each bit in the 64-bit data block. The final permutation is the reverse of the initial permutation to reorder the samples into the correct original formation. The initial permutation is followed by the actual encryption. The permutated 64-bit block is divided into a left and a right block of 32 bits each.

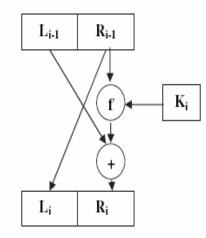

#### **1.2 Sixteen Rounds of DES**

Sixteen rounds take place, each undergoing a similar procedure, as illustrated in Figure 1.3. The right block is placed into the left block of the next round, and the left block is combined with an encoded version of the right block and placed into the right block of the next round, or

$$L_i = R_{i-1}$$

$$R_{i} = L_{i-1} \text{ XOR } f(R_{i-1},k_i)$$

where  $L_{i-1}$  and  $R_{i-1}$  are the left and right blocks, respectively, each with 32 bits, and  $k_i$  is the distinct key for the particular round of encryption. The original key is sent through a key scheduler that alters the key for each round of encryption. The left block is not utilized until the very end, when it is XORed with the encrypted right block.

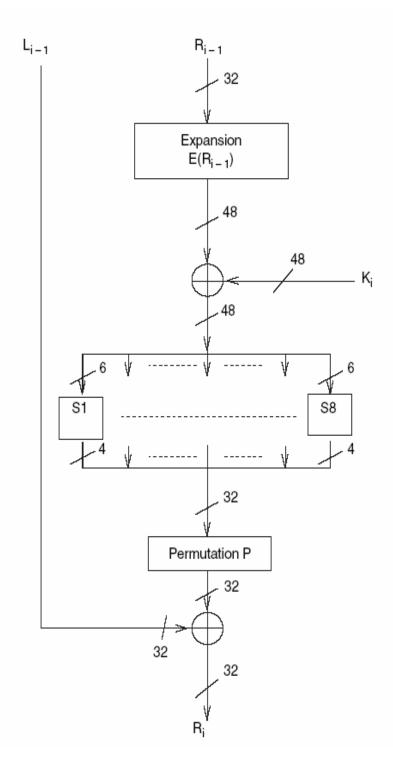

The *f*-function operating on a 32-bit quantity expands these 32 bits into 48 bits using the expansion table (see Table 1.2). This expansion table performs a permutation while duplicating 16 of the bits (the rightmost two columns). For example, the first integer is 32, so that the first bit in the output block will be bit 32; the second integer is 1, so that the second bit in the output block will be bit 1; and so on.

Fig 1.2: Encryption process—one round.

| 32 | 1  | 2  | 3  | 4  | 5  |

|----|----|----|----|----|----|

| 4  | 5  | 6  | 7  | 8  | 9  |

| 8  | 9  | 10 | 11 | 12 | 13 |

| 12 | 13 | 14 | 15 | 16 | 17 |

| 16 | 17 | 18 | 19 | 20 | 21 |

| 20 | 21 | 22 | 23 | 24 | 25 |

| 24 | 25 | 26 | 27 | 28 | 29 |

| 28 | 29 | 30 | 31 | 32 | 1  |

Table 1.2: Expansion of 32 bits to 48.

Table 1.3: S-Box example, S<sub>1</sub>

| 14 | 4  | 13 | 1 | 2  | 15 | 11 | 8  | 3  | 10 | 6  | 12 | 5  | 9  | 0 | 7  |

|----|----|----|---|----|----|----|----|----|----|----|----|----|----|---|----|

| 0  | 15 | 7  | 4 | 14 | 2  | 13 | 1  | 10 | 6  | 12 | 11 | 9  | 5  | 3 | 8  |

| 4  | 1  | 14 | 8 | 13 | 6  | 2  | 11 | 15 | 12 | 9  | 7  | 3  | 10 | 5 | 0  |

| 15 | 12 | 8  | 2 | 4  | 9  | 1  | 7  | 5  | 11 | 3  | 14 | 10 | 0  | 6 | 14 |

The 48-bit key transformations are XORed with these expanded data, and the results are used as the input to eight different *S*-boxes. Each *S*-box takes 6 consecutive bits and outputs only 4 bits. The 4 output bits are taken directly from the numbers found in a corresponding *S*-box table. This process is similar to that of a decoder where the 6 bits act as a table address and the output is a binary representation of the value at that address. The zeroth and fifth bits determine the row of the *S*-box, and the first through fourth bits determine which column the number is located in. For example, 110100 points to the third row (10) and 10th column (1010). The first 6 bits of data correspond to the first of eight *S*-box tables, shown in Table 1.3. The 32 bits of output from the *S*-boxes are permutated according to the *P*-box shown in Table 1.4, and then output from the *f*-function shown in Figure 1.3. For example, from Table1.4, bits 1 and 2 from the input block will be moved to bits 16 and 7 in the output, respectively. After the 16 rounds of encryption, a final permutation occurs, which reverses the initial permutation, yielding an encrypted data signal.

Table 1.4: P-BOX

| 16 | 7 | 20 | 21 | 29 | 12 | 28 | 17 | 1  | 15 | 23 | 26 | 5  | 18 | 31 | 10 |

|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 2  | 8 | 24 | 14 | 32 | 27 | 3  | 9  | 19 | 13 | 30 | 6  | 22 | 11 | 4  | 25 |

Fig 1.3: Core f-function of DES

# **CHAPTER-2**

# **INTRODUCTION TO TMS320C6713 DSPKIT**

### 2.1 INTRODUCTION

Digital signal processors such as the TMS320C6x (C6x) family of processors are like fast special-purpose microprocessors with a specialized type of architecture and an instruction set appropriate for signal processing. The C6x notation is used to designate a member of Texas Instruments' (TI) TMS320C6000 family of digital signal processors. The architecture of the C6x digital signal processor is very well suited for numerically intensive calculations. Based on a very-long-instruction-word (VLIW) architecture, the C6x is considered to be TI's most powerful processor.

Digital signal processors are used for a wide range of applications, from communications and controls to speech and image processing. The general-purpose digital signal processor is dominated by applications in communications (cellular). Applications embedded digital signal processors are dominated by consumer products. They are found in cellular phones, fax/modems, disk drives, radio, printers, hearing aids, MP3 players, high-definition television (HDTV), digital cameras, and so on. These processors have become the products of choice for a number of consumer applications, since they have become very cost-effective. They can handle different tasks, since they can be reprogrammed readily for a different application. DSP techniques have been very successful because of the development of low-cost software and hardware support. For Example, modems and speech recognition can be less expensive using DSP techniques.

DSP processors are concerned primarily with real-time signal processing. Real-time processing requires the processing to keep pace with some external event, whereas non-real-time processing has no such timing constraint. The external event to keep pace with is usually the analog input. Whereas analog-based systems with discrete electronic components such as resistors can be more sensitive to temperature changes, DSP-based systems are less affected by environmental conditions. DSP processors enjoy the advantages of microprocessors. They are easy to use, flexible, and economical.

The basic system consists of an analog-to-digital converter (ADC) to capture an input signal. The resulting digital representation of the captured signal is then processed by a digital signal processor such as the C6x and then output through a digital-to-analog converter (DAC). Also included within the basic system are a special input filter for antialiasing to eliminate erroneous signals and an output filter to smooth or reconstruct the processed output signal.

### **2.2 DSK SUPPORT TOOLS**

Most of the work presented in this book involves the design of a program to implement a DSP application. To perform the experiments, the following tools are used:

- 1. TI's DSP starter kit (DSK). The DSK package includes:

- (a) Code Composer Studio (CCS), which provides the necessary software Support tools. CCS provides an integrated development environment (IDE), bringing together the C compiler, assembler, linker, debugger, and so on.

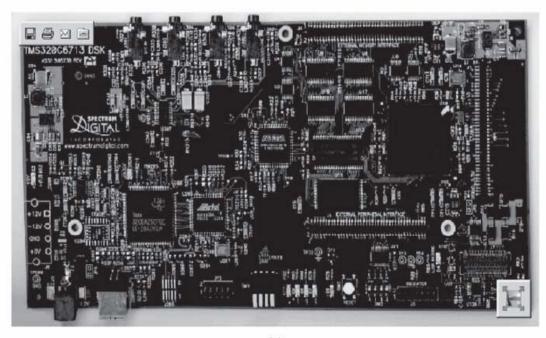

- (b) A board, shown in Figure 1.1 that contains the TMS320C6713 (C6713) Floating-point digital signal processor as well as a 32-bit stereo codec for Input and output (I/O) support.

- (c) A universal synchronous bus (USB) cable that connects the DSK board to a PC.

- (d) A 5V power supply for the DSK board.

- **2.** *An IBM-compatible PC*. The DSK board connects to the USB port of the PC Through the USB cable included with the DSK package.

**3.** *An oscilloscope, signal generator, and speakers*. A signal/spectrum analyzer is optional. Shareware utilities are available that utilize the PC and a sound card to create a virtual instrument such as an oscilloscope, a function generator, or a spectrum analyzer.

#### 2.2.1 DSK Board

The DSK package is powerful, yet relatively inexpensive (\$395), with the necessary hardware and software support tools for real-time signal processing. It is a complete DSP system. The DSK board, with an approximate size of 5 \* 8 in., includes the C6713 floating-point digital signal processor and a 32-bit stereo codec TLV320AIC23 (AIC23) for input and output.

The onboard codec AIC23 uses a sigma-delta technology that provides ADC and DAC. It connects to a 12-MHz system clock. Variable sampling rates from 8 to 96 kHz can be set readily.

A daughter card expansion is also provided on the DSK board. Two 80-pin connectors provide for external peripheral and external memory interfaces. Two project examples in Chapter 10 illustrate the use of the external memory interface (EMIF) with light-emitting diodes (LEDs) and liquid-crystal displays (LCDs) for spectrum display.

The DSK board includes 16MB (megabytes) of synchronous dynamic random access memory (SDRAM) and 256kB (kilobytes) of flash memory. Four connectors on the board provide input and output: MIC IN for microphone input, LINE IN for line input, LINE OUT for line output, and HEADPHONE for a headphone output (multiplexed with line output). The status of the four user dip switches on the DSK board can be read from a program and provides the user with a feedback control interface. The DSK operates at 225MHz.Also onboard the DSK are voltage regulators that provide 1.26 V for the C6713 core and 3.3 V for its memory and peripherals.

(*a*)

**FIGURE 2.0.** TMS320C6713-based DSK board: (*a*) board; (*b*) diagram. (Courtesy of Texas Instruments)

### 2.2.2 TMS320C6713 Digital Signal Processor

The TMS320C6713 (C6713) is based on the VLIW architecture, which is very well suited for numerically intensive algorithms. The internal program memory is structured so that a total of eight instructions can be fetched every cycle. For example, with a clock rate of 225MHz, the C6713 is capable of fetching eight 32-bit instructions every 1/(225 MHz) or 4.44 ns.

Features of the C6713 include 264 kB of internal memory (8kB as L1P and L1D Cache and 256kB as L2 memory shared between program and data space), eight functional or execution units composed of six arithmetic-logic units (ALUs) and two multiplier units, a 32-bit address bus to address 4 GB (gigabytes), and two sets of 32-bit general-purpose registers.

The C67xx (such as the C6701, C6711, and C6713) belong to the family of the C6x floating-point processors, whereas the C62xx and C64xx belong to the family of the C6x fixed-point processors. The C6713 is capable of both fixed- and floating-point processing.

#### 2.3 CODE COMPOSER STUDIO

CCS provides an IDE to incorporate the software tools. CCS includes tools for code generation, such as a C compiler, an assembler, and a linker. It has graphical capabilities and supports real-time debugging. It provides an easy-to-use software tool to build and debug programs.

The C compiler compiles a C source program with extension .c to produce an assembly source file with extension.*asm*.The assembler assembles an.*asm* source file to produce a machine language object file with extension.*obj*.The linker combines object files and object libraries as input to produce an executable file with extension.*out*. This executable file represents a linked common object file format (COFF), popular in Unix-

based systems and adopted by several makers of digital signal processors. This executable file can be loaded and run directly on theC6713 processor.

To create an application project, one can "add" the appropriate files to the project. Compiler/linker options can readily be specified. A number of debugging features are available, including setting breakpoints and watching variables; viewing memory, registers, and mixed C and assembly code; graphing results; and monitoring execution time. One can step through a program in different ways (step into, over, or out).

Real-time analysis can be performed using real-time data exchange (RTDX). RTDX allows for data exchange between the host PC and the target DSK, as well as analysis in real time without stopping the target. Key statistics and performance can be monitored in real time. Through the joint team action group (JTAG), communication with on-chip emulation support occurs to control and monitor program execution. The C6713 DSK board includes a JTAG interface through the USB port.

### 2.4(a) QUICK TEST OF DSK

- 1. On power, a program *post.c* (Power On Self Test), stored in onboard flash memory, uses the board support library (BSL) to test the DSK. It tests the internal, external, and flash memories, the two multichannel buffered serial ports (McBSP), direct memory access (DMA), the onboard codec, and the LEDs. If all tests are successful, all four LEDs blink three times and stop (with all LEDs on). During the testing of the codec, a 1-kHz tone is generated for 1 sec.

- 2. Launch CCS from the icon on the desktop. A USB enumeration process Takes place. Then CCS will be opened and the LEDs will turn off. Press GEL Æ Check DSK Æ Quick Test. The Quick Test can be used for confirmation Of correct operation and installation. The following message is then displayed:

Switches: 15 Board Revision: 1 CPLD Revision: 2 This assumes that the four dip switches

This assumes that the four dip switches (0, 1, 2, 3) are all in the up position. Change the switches to (1110)2 so that the first three switches (0, 1, 2) are up and press the fourth switch (3) down. Repeat the procedure to select GEL Æ Check DSK Æ Quick Test and verify that the value of the switches is now 7 (with the display "Switches: 7"). You can set the value of the four user switches from 0 to 15. Within your program you can then direct the execution of your code based on these 16 values.

### 2.4(b) Alternative Quick Test of DSK

- 1. Open/launch CCS from the icon on the desktop if this has not been done already. Select File ÆLoad Program. Click on the folder *sine8\_LED\Debug* within myprojects to load the file *sine8\_LED.out*. This loads the executable file *sine8\_LED.out* into the C6713 processor. This assumes that you have already copied all the folders on the accompanying CD into your folder: *c:\c6713\myprojects*.

- 2. Select Debug Æ Run. Press the dip switch #0, which should light LED #0 on and generate a 1-kHz tone. Connect the LINE OUT (or the HEADPHONE) on the DSK board to a speaker or to an oscilloscope and verify the generation of the 1-kHz tone. The four connectors on the DSK board for I/O (MIC, LINE IN, LINE OUT, and HEADPHONE) use a 3.5-mm jack audio cable.

# **CHAPTER-3**

# INPUT AND OUTPUT TO THE DSK

### **3.1 INTRODUCTION**

Typical applications using DSP techniques require at least the basic system shown in Figure 2.1, consisting of analog input and output. Along the input path is an antialiasing filter for eliminating frequencies above the *Nyquist frequency*, defined as one-half of the sampling frequency  $F_s$  Otherwise, aliasing occurs, in which case a signal with a frequency higher than one-half  $F_s$  is used as a signal with a lower frequency. The sampling theorem tells us that the sampling frequency must be at least twice the highest-frequency component f in a signal, so that

$$F_{s} > 2$$

Which s also

$$1/T_s > 2(1/T)$$

Where  $T_s$  is the sampling period. Or

$T_s < T/2$

The sampling period  $T_s$  must be less than one-half the period of the signal. For example, if we assume that the ear cannot detect frequencies above 20 kHz, we can use a lowpass input filter with a bandwidth or cutoff frequency at 20 kHz to avoid aliasing. We can then sample a music signal at  $F_s > 40$  kHz (typically, 44.1 or 48 kHz) and remove frequency components higher than 20 kHz. Figure 2.2 illustrates an aliased signal. Let the sampling frequency  $F_s = 4$  kHz, or a sampling period of  $T_s = 0.25$ ms. It is impossible to determine whether it is the 5- or 1-kHz signal that is represented by the sequence (0, 1, 0, -1). A 5-kHz signal will appear as a 1-kHz signal; hence, the 1-kHz signal is an aliased signal. Similarly, a 9-kHz signal would also appear as a 1-kHz aliased signal.

FIGURE 2.1. DSP system with input and output.

# **3.2 TLV320AIC23 (AIC23) ONBOARD STEREO CODEC FOR INPUT AND OUTPUT**

The DSK board includes the TLV320AIC23 (AIC23) codec for input and output. The ADC circuitry on the codec converts the input analog signal to a digital representation to be processed by the DSP. The maximum level of the input signal to be converted is determined by the specific ADC circuitry on the codec, which is 6V p-p with the onboard codec. After the captured signal is processed, the result needs to be sent to the outside world. Along the output path in Figure 2.1 is a DAC, which performs the reverse

operation of the ADC. An output filter smoothes out or reconstructs the output signal. ADC, DAC, and all required filtering functions are performed by the single-chip codec AIC23 on board the DSK.

The AIC23 is a stereo audio codec based on sigma-delta technology. The functional block diagram of the AIC23 codec is shown in Figure 2.3. It performs all the functions required for ADC and DAC, lowpass filtering, oversampling, and so on. The AIC23 codec contains specifications for data transfer of words with length 16, 20, 24, and 32 bits. A diagram of the AIC23 codec interfaced to the C6713 DSK is shown in *6713\_dsk\_schem.pdf*, included with the CCS package.

Sigma–delta converters can achieve high resolution with high oversampling ratios but with lower sampling rates. They belong to a category in which the sampling rate can be much higher than the Nyquist rate. Sample rates of 8, 16, 24, 32, 44.1, 48, and 96 kHz are supported and can be readily set in the program.

A digital interpolation filter produces the oversampling. The quantization noise power in such devices is independent of the sampling rate. A modulator is included to shape the noise so that it is spread beyond the range of interest. The noise spectrum is distributed between 0 and  $F_s/2$ , so that only a small amount of noise is within the signal frequency band. Therefore, within the actual band of interest, the noise power is considerably lower. A digital filter is also included to remove the out-ofband noise.

A 12-MHz crystal supplies the clocking to the AIC23 codec (as well as to the DSP and the USB interface). Using this 12-MHz master clock, with oversampling rates of  $250F_s$  and  $272F_s$ , an exact audio sample rate of 48 kHz (12MHz/250) and a CD rate of 44.1kHz (12MHz/272) can be obtained. The sampling rate is set by the codec's register SAMPLERATE.

The ADC converts an input signal into discrete output digital words in a 2'scomplement format that corresponds to the analog signal value. The DAC includes an

interpolation filter and a digital modulator. A decimation filter reduces the digital data rate to the sampling rate. The DAC's output is first passed through an internal lowpass reconstruction filter to produce an output analog signal. Low noise performance for both ADC and DAC is achieved using oversampling techniques with noise shaping provided by sigma–delta modulators.

Communication with the AIC23 codec for input and output uses two multichannel buffered serial ports McBSPs on the C6713. McBSP0 is used as a unidirectional channel to send a 16-bit control word to the AIC23. McBSP1 is used as a bidirectional channel to send and receive audio data.

Alternative I/O daughter cards can be used for input and output. Such cards can plug into the DSK through the external peripheral interface 80-pin connector J3 on the DSK board.

### **3.3 PROGRAMMING EXAMPLES USING C CODE**

Several examples follow to illustrate input and output with the DSK. They are included to familiarize you with both the hardware and software tools and provide some background to implement a specific application. The example *sine2sliders* illustrates the use of two sliders, an echo example demonstrates the effects of a variable-length buffer on an echo, a noise generator example is used in Chapter 4 as the input to a digital filter, an example illustrates the use of onboard flash memory, and so on.

### Example 3.1: Loop Program Using Interrupt (loop\_intr)

This example illustrates input and output with the AIC23 codec. Figure 2.4 shows the C source program *loop\_intr.c*, which implements the loop program. It is interrupt-driven using INT11.

This program example is very important since it can be used as a base program to build on. For example, to implement a digital filter, one would need to insert the appropriate algorithm between the input and output functions. The two functions input\_sample and output\_sample, as well as the function comm\_intr, are included in the communication support file *C6713dskinit.c*.This is done so that the C source program is kept as small as possible.

After the initialization and selection/enabling of an interrupt, execution waits within the infinite while loop until an interrupt occurs. Upon interrupt, execution proceeds to the ISR c\_int11, as specified in the vector file vectors\_intr.asm. An interrupt occurs every sample period  $T_s = 1/F_s = 1/(8 \text{ kHz}) = 0.125 \text{ms}$ , at which time an input sample value is read from the codec's ADC and then sent as output to the codec's DAC.

Execution returns from interrupt to the while(1) statement waiting for a subsequent interrupt. [Note that in lieu of waiting within the while(1) infinite loop, one could be processing code.] Upon interrupt, execution proceeds to ISR, "services" the necessary task dictated by ISR, then returns to the calling function waiting for the occurrence of a subsequent interrupt.

//Loop\_intr.c Loop program using interrupt.Output=delayed input #include "dsk6713\_aic23.h" //codec-DSK support file Uint32 fs=DSK6713\_AIC23\_FREQ\_8KHZ; //set sampling rate

interrupt void c\_int11() //interrupt service routine

short sample\_data;

```

sample_data = input_sample(); //input data

output_sample(sample_data); //output data

return;

}

```

```

void main()

{

comm_intr(); //init DSK, codec, McBSP

while(1); //infinite loop

}

```

FIGURE 2.4. Loop program using interrupt (loop\_intr.c).

- Within the function *output\_sample*, support functions from the BSL are included to write data using the two serial ports: McBSP0 for control and McBSP1 for data transfer (*MCBSP\_write*). Most of the programs in the book will output using 16 bits. In this fashion, output\_sample is made to default to the left 16-bit channel and no adapter need be used (see the comments in C6713dskinit.c). Otherwise, one would need to use output\_right\_sample.

- 2. Within the function *comm\_intr*, the following tasks are performed.

- (a) Initialize the DSK.

- (**b**) Configure/select INT11.

- (c) Enable the specific interrupt.

- (d) Enable the global enable interrupt (GIE) bit and the nonmaskable interrupt.

- (e) Initiate communication.

The interrupt functions called for the tasks above are within the board and chip support files included with CCS. Create and build this project as **loop\_intr**. The main C source file is in the folder *loop\_intr*. Use the same support files as in Example 1.2: the vector file for the interrupt-driven and linker command file located in the folder *support*, and the runtime support, board support, and chip support library files that can be added with the building option for the linker.

Input a sinusoidal waveform to the LINE IN connector on the DSK, with amplitude of approximately 2 V p-p and a frequency between approximately 1 and 3 kHz. Connect the output of the DSK, LINE OUT to a speaker or to an oscilloscope and verify a tone of the same input frequency, but attenuated to approximately 0.8 V p-p. Using an oscilloscope, the output is a delayed version of the input signal.

Increase the amplitude of the input sinusoidal waveform beyond 6V p-p and observe that the output signal becomes distorted.

#### Input with Gain

To adjust the gain of the left line-input channel, the corresponding header support file *c6713dskinit.h* of the communication/init "black box" file needs to be modified slightly. First, copy this header file AND *c6713dskinit.c from* the *support* folder into the folder *loop\_intr* so that you do not modify the original header file. Remove the init file from the project and replace it with the one in the folder *loop\_intr*.This will keep the original init support file unchanged in the folder *support*. Modify the setup register 0, which controls the left input volume, from 0x0017 to 0x001c in order to increase the left line-input volume.

Rebuild the project, making sure that you are adding *c6713dskinit.c* from the folder *loop\_intr* (and not from the folder *support*). In this fashion, the corresponding header file *c6713dskinit.h* that will be included will come from that same folder. Load/run the executable file *loop\_intr.out*, and verify that the output amplitude is not attenuated and is

the same as the input amplitude of 2V p-p. Values for the set-up register 0 from 0x0018 to 0x001c will cause the output amplitude to increase from 0.8 to 2V p-p.

The left input channel was selected since *input\_sample* and *output\_sample* default to the left channel. Otherwise, if the right line-input volume is to be increased by modifying the set-up register 1, an adapter/connector with two inputs and one single-ended output connections would be needed. See Example 2.3 (*loop\_stereo/sine\_stereo*).

### Input from a Microphone

To select an input from a microphone in lieu of line input, modify the header file set-up register 4 from 0x0011 to 0x0015 (third LSB as a 1) so that the ADC gets its input from MIC IN. The microphone input and line input are multiplexed, and only one is active at a time. Rebuild the project to verify your output, with the input to the MIC IN connector.

### Example 3.2: Loop Program Using Polling (loop\_poll)

This example implements a polling-based loop program to illustrate the input and output of a sample value every sample period *Ts*. Note that the program loop\_intr.c in Example 2.1 is an interrupt-driven program. The C source program loop\_poll.c shown in Figure 2.5 implements this loop program. The polling technique uses a continuous procedure of testing when the data are ready. Although it is simpler than the interrupt technique, it is less efficient since the input and output data need to be continuously tested to determine when they are ready to be received or transmitted.

//loop\_poll.c Loop program using polling.Output=delayed input

#include "DSK6713\_AIC23.h" //codec-DSK file support Uint32 fs=DSK6713\_AIC23\_FREQ\_8KHZ; //set sampling rate

void main()

```

{

short sample_data;

comm_poll(); //init DSK, codec, McBSP

while(1) //infinite loop

{

sample_data = input_sample(); //input sample

output_sample(sample_data); //output sample

}

}

```

FIGURE 2.5. Loop program using polling (loop\_poll.c).

The input to the ADC is from the data receive register (DRR) of the McBSP1. Since this is a polling-driven program, the SPCR bit 1, which is the receive ready register (RRDY), is first tested to determine if it is a 1 or enabled (see Figure B.8).Within input\_sample, execution of the statement

```

While (!MCBSP_rrdy())

```

remains in an infinite loop until RRDY becomes 1 or enabled. Execution then proceeds to read/receive the data.

2. Within the function output\_sample, the MCBSP1 *writes* the output from the DAC to the data transmit register (DXR) of McBSP1. Since this is a polling-driven program, the transmit ready register (XRDY) bit 17 of SPCR is first tested to see if it is a 1 or enabled. Within output\_sample, execution of the statement

While (!MCBSP\_xrdy())

remains in an infinite loop until the transmit ready register becomes 1 or enabled. Execution then proceeds to transmit/write the data. The same support files as in Example 1.1 are used: the "black box" communication/ init file *c6713dskinit.c*, the vector file vectors\_poll.asm, the linker command file c6713dsk.cmd (all three from the folder support), and the three library-support files.

Create and build this project as **loop\_poll**. Use the same input as in Example 2.1 and verify the same results.

## **Example 3.3:** Stereo Input and Stereo Output (loop\_stereo/sine\_stereo)

#### Loop Program with Stereo Input and Stereo Output (loop\_stereo)

This example demonstrates input and output using the stereo capability of the onboard AIC23 codec. It requires the use of an adapter with two inputs and one output that connects to the DSK. Such an adapter has one input connector white (or silver) that represents the left channel and another input connector red (or gold) that represents the right channel. This adapter becomes essential for some of the examples on adaptive filtering that require two separate input signals, processing each input separately. Figure 2.6 shows the loop program *loop\_stereo* to illustrate.

//Loop\_stereo.c Stereo input and output with both channels

```

#include "dsk6713_aic23.h" //codec-DSK support file

Uint32 fs=DSK6713_AIC23_FREQ_8KHZ; //set sampling rate

```

```

#define LEFT 0 //reversed in init file

#define RIGHT 1

union {Uint32 combo; short channel[2];} AIC23_data;

interrupt void c_int11() //interrupt service routine

{

AIC23_data.combo = input_sample(); //input 32-bit sample

output_left_sample(AIC23_data.channel[LEFT]);//left channels for I/O

return;

}

void main() //main function

{

comm_intr(); //init DSK, codec, McBSP

while(1); //infinite loop

}

FIGURE 2.6. Loop program with stereo input and output (loop_stereo.c).

```

Within the function input\_sample, support functions from the BSL are included to read a 32-bit data. The function *input\_sample* captures 32-bit data, 16 bits from the left input channel and 16 bits from the right input channel. The *union* statement is used to process each channel independently. The union of *AIC23\_data* and *combo* contains these 32-bit input data. The line of code for output is from the left channel (by default) to output 16-bit data from the left input channel.

Build and run this project as **loop\_stereo** using the support files as in Example 1.2 for an interrupt-driven program. The main C source file *loop\_stereo.c* is contained in the folder loop\_stereo. Connect a 1 kHz (with approximate amplitude of 2 V p-p) sine wave into the left input channel and a 2-kHz sine wave into the right input channel. Verify that the left (default) output channel has the same input signal frequency of 1kHz, but reduced in amplitude (as expected).You do not need a second adapter for the output side since the output defaults to the left channel. Change the output line of code to

#### output\_left\_sample(AIC23\_data.channel[RIGHT]);

and verify that the output is the 2-KHz sine wave from the right input channel.With the line of code output\_right\_sample(AIC23\_data.channel[RIGHT]);

//Sine\_stereo.c Sine generation with output to both channels

#include "dsk6713\_aic23.h" //codec-DSK support file Uint32 fs=DSK6713\_AIC23\_FREQ\_8KHZ; //set sampling rate

#define LEFT 0 //reversed in init file

#define RIGHT 1

union {Uint32 combo; short channel[2];} AIC23\_data;

```

short loop = 0, gain = 10;

short sine_table[8]={0,707,1000,707,0,-707,-1000,-707};//sine values

```

```

interrupt void c_int11() //interrupt service routine

```

#### {

AIC23\_data.channel[RIGHT]=sine\_table[loop]\*gain; //for right channel AIC23\_data.channel[LEFT]=sine\_table[loop]\*gain; //for left channel output\_sample(AIC23\_data.combo); //output to both channels

```

if (++loop > 7) loop = 0; //reint index if @ end of table

}

void main()

{

comm_intr(); //init DSK, codec, McBSP

while(1); //infinite loop

}

```

FIGURE 2.7. Sine generation with stereo outputs (sine\_stereo.c).

two adapters are required to verify that the output from the right channel is the 2-kHz sine wave from the right input channel. You can also use one adapter at the input side to capture the two different signals and one stereo cable at the output side.

Experiment with this project, inputting different signals into each channel and outputting from each channel using adapters and stereo cable. Verify that you can select each input and output channel independently.

#### Sine Generation with Stereo Output (sine\_stereo)

Figure 2.7 shows the C source file *sine\_stereo.c*, included in the folder *sine\_stereo*, to illustrate further the codec as a stereo device. Build and run this project as **sine\_stereo**. Verify that the generated 1 kHz sinusoid is through both output channels, using an adapter or stereo cable at the output side of the DSK.

# Example 3.4: Sine Generation with Two Sliders for Amplitude and Frequency Control (sine2sliders)

The polling-based program *sine2sliders.c* in Figure 2.8 generates a sine wave. Two sliders are used to vary both the amplitude (gain) and the frequency of the sinusoid

//Sine2sliders.c Sine generation with different # of points

```

#include "DSK6713_AIC23.h" //codec-DSK interface support

Uint32 fs=DSK6713_AIC23_FREQ_8KHZ; //set sampling rate

short loop = 0;

short sine_table[32]={0,195,383,556,707,831,924,981,1000,

981,924,831,707,556,383,195,0,-195,-383,-556,-707,-831,-924,

-981,-1000,-981,-924,-831,-707,-556,-383,-195}; //sine data

short gain = 1; //for gain slider

short frequency = 2; //for frequency slider

void main()

{

comm_poll(); //init DSK,codec,McBSP

while(1) //infinite loop

{

output_sample(sine_table[loop]*gain);//output scaled value

loop += frequency; //incr frequency index

loop = loop \% 32; //modulo 32 to reinit index

}

}

```

**FIGURE 2.8.** Sine generation making use of two sliders to control the amplitude and frequency of the sine wave generated (sine2sliders.c).

/\*Sine2sliders.gel Two sliders to vary gain and frequency\*/

```

menuitem "Sine Parameters"

slider Gain(1,8,1,1,gain_parameter) /*incr by 1,up to 8*/

{

gain = gain_parameter; /*vary gain*/

}

slider Frequency(2,8,2,2,frequency_parameter) /*incr by 2,up to 8*/

{

frequency = frequency_parameter; /*vary frequency*/

}

```

**FIGURE 2.9.** GEL file with two slider functions to control the amplitude and frequency of the sine wave generated (sine2sliders.gel).

generated. Using a lookup table with 32 points, the variable frequency is obtained by selecting a different number of points per cycle. The gain slider scales the volume/amplitude of the waveform signal. The appropriate GEL file *sine2sliders.gel* is shown in Figure 2.9.

The 32 sine data values in the table or buffer correspond to sin(t), where t = 0,11.25, 22.5, 33.75, 45, . . . , 348.75 degrees (scaled by 1000). The frequency slider takes on a value from 2 to 8, incremented by 2. The modulo operator is used to test when the end of the buffer that contains the sine data values is reached. When the loop index reaches 32, it is reinitialized to zero. For example, with the frequency slider at position 2, the loop or frequency index steps through every other value in the table. This corresponds to 16 data values within one cycle.

Build this project as **sine2sliders**. Use the appropriate support files for a pollingdriven program. The main C source file *sine2sliders.c* is contained in the folder **sine2sliders**. Verify that the frequency generated is f = Fs/16 = 500Hz. Increase the slider position (the use of a slider was introduced in Example 1.1) to 4, 6, 8 and verify that the signal

frequencies generated are 1000, 1500, and 2000Hz, respectively. Note that when the slider is at position 4, the loop or frequency index steps through the table selecting the eight values (per cycle): sin[0], sin[4], sin[8], . . . , sin[28] that correspond to the data values 0, 707, 1000, 707, 0, -707, -1000, and -707.The resulting frequency generated is then f = Fs/8 = 1 kHz (as in Example 1.1).

# Example 3.5: Loop Program with Input Data Stored in Memory (loop\_store)

The program *loop\_store.c* in Figure 2.10 is an interrupt-based program and is included in the folder **loop\_store**. Each time an interrupt INT11 occurs, a sample is read from the codec's ADC and written to the codec's DAC. Furthermore, each sample is written to a 512-element circular buffer implemented using an array *buffer* and an index i that is incremented after each sample is stored. The index is reset to zero when it reaches the end of the buffer. Consequently, the array always contains the 512 most recent sample values.

//Loop\_store.c Data acquisition.Input data stored also into buffer

```

#include "DSK6713_AIC23.h" //codec-DSK interface support

Uint32 fs=DSK6713_AIC23_FREQ_8KHZ; //set sampling rate

#define BUFFER_SIZE 512 //buffer size

short buffer[BUFFER_SIZE]; //buffer where data is stored

int i = 0;

interrupt void c_int11() //interrupt service routine

{

output_sample((short)input_sample());//output acquired data

buffer[i] =((short)input_sample());//store input data into buffer

i++; //increment buffer index

if (i==BUFFER_SIZE) i = 0; //reinit index if buffer full

return; //return from ISR

```

```

}

void main()

{

comm_intr(); //init DSK, codec, McBSP

while(1); //infinite loop

}

```

FIGURE 2.10. Loop program with input data stored in memory (loop\_store.c).

**FIGURE 2.11.** CCS graphs with the *loop\_store* program: (*a*) time-domain plot of stored input data representing a 1-kHz sine wave; (*b*) FFT magnitude of stored data representing a 1-kHz sine wave.

Build this project as **loop\_store**. Input a sinusoidal signal with amplitude of approximately 1/2 V p-p and a frequency of 1 kHz. Run and verify your output results.

Use CCS to plot the stored input data in both the time and frequency domains (see also Example 1.2). Select View Æ Graph Æ Time/Frequency. For the timedomain plot, specify a starting address "buffer," 512 points for the acquisition buffer size, 64 points for the data size display (for a clearer plot), a 16-bit signed integer for the data type, and 8000 for the sampling rate.Verify the 1-kHz time-domain sinewave plot within CCS, as shown in Figure 2.11*a*.

Select View Æ Graph Æ Time/Frequency again and FFT magnitude for display to obtain a frequency-domain plot of the stored input data. Specify a display data size of 512 with an FFT order of M = 9, where 2M = 512. The spike at 1 kHz in Figure 2.11b represents the 1-kHz sine wave plot within CCS.

//Loop\_print.c Data acquisition.Loop with data printed to a file

```

#include "DSK6713_AIC23.h" //codec-DSK support file

Uint32 fs=DSK6713_AIC23_FREQ_8KHZ; //set sampling rate

#include <stdio.h>

#define BUFFER_SIZE 64 //buffer size

int i=0, j=0;

short buffer[BUFFER_SIZE]; //buffer for data

FILE *fptr; //file pointer

interrupt void c_int11() //ISR

{

buffer[i]=((short)input_sample()); //store data in buffer

```

```

i++; //increment buffer count

if (i==BUFFER_SIZE - 1) //if buffer full

{

fptr = fopen("sine.dat", "w"); //create output data file

for (j=0; j<BUFFER_SIZE; j++)

fprintf(fptr,"%d\n",buffer[j]);//write buffer data to file

fclose(fptr); //close file

i = 0; //initialize buffer count

puts("done"); //finished storing to file

}

output_sample((short)input_sample()); //output data

return; //return from ISR

}

void main()

{

comm_intr(); //init DSK, codec, McBSP

puts("start\n"); //print "start" indicator

while(1); //infinite loop

}

```

FIGURE 2.12. Loop program to store I/O data in memory and in a file (loop\_print.c).

## Example 3.6: Loop with Data in a Buffer Printed to a File (loop\_print)

This example extends the preceding loop program so that the acquired input data are stored in a memory buffer and then printed to a file. Figure 2.12 shows the C source program *loop\_print.c* (included in the folder **loop\_print**) that implements this example. It takes a long time (more than 3000 cycles) to execute the printf statement in the program (see Example 1.3).This can be reduced to about 30 cycles using DSP/BIOS.

After initialization of the DSK, the *puts* statement prints the word start as an indicator within the CCS command window; then execution proceeds to the infinite while loop. Upon each interrupt, execution proceeds to ISR, and a newly acquired data value is stored in a buffer of size 64.

The buffer index i is incremented to store each new sampled data value. When the end of the buffer is reached, indicating that the buffer is full, a file sine.dat is "opened" and the contents of the buffer are written into that file. Then the indicator done is printed within the CCS window. This process is repeated continuously so that a new set of 64 data points is acquired, and the done indicator is again displayed (after each set of data fills the buffer and is written to sine.dat).

Build and run this project as *loop\_print*. Input a sine-wave signal of approximately 1/2 V p-p with a 1-kHz frequency. Halt execution after the indicator done is displayed. The buffer of 64 input data representing the sine wave can be retrieved from the file *sine.dat* in the same folder loop\_print\Debug. Note that the third set of 64 points will be stored in the buffer and printed in the file *sine.dat* if execution of the program is halted after the third done indicator. A plot program or MATLAB can be used to plot sine.*dat* and verify a 1-kHz sine wave.You can also verify your results by plotting the content of the buffer within CCS, as in the previous example. Note that the output is not displayed appropriately in real time due to the slow execution of the print statement. You can comment the section of code that is associated with printing the input data into a file to verify that a loop program is also implemented.

# *Example 3.7: Square-Wave Generation Using a Lookup Table* (squarewave)

This example generates a square wave using a lookup table. Figure 2.13 shows a listing of the program *squarewave.c* (located in the folder **squarewave**) that implements this project example. A buffer of size 64 is created.Within *main*, the buffer table is loaded with data: the first half with (215 - 1) = 32,767 and the second half with -215 = -32,768. Upon each interrupt that occurs every sample period *Ts*, one data value from the buffer is

sent for output. After each data value from the. table is output, execution returns to the infinite while loop, waiting for the next interrupt to occur and output the subsequent value in the table. When the end of the buffer (table) is reached, the buffer index is reinitialized to the beginning of the buffer.

Build and run this project as **squarewave**. Verify a square-wave output signal of approximately 3V p-p. Note that the valid input data to the codec are between -215 and (215 - 1) or between -32,768 and 32,767. Change the values in the first half of the table using 0x8000 = 32,768 in lieu of 0x7FFF = 32,767. Rebuild/run and verify that the square-wave signal is no longer generated.

Note that increasing the number of points in the table produces a more pronounced charging/discharging effect (since it is AC coupled) due to the output capacitor (see the block diagram of the AIC23 codec). For example, with 64 points, the fundamental frequency is at 8 kHz/64 = 125Hz. Doubling the number of points will double the period of the square wave, and the discharging effect will be more pronounced (time constant reduced relative to one-half of the period of the square wave). Change the sampling frequency to 16 or 24 kHz and verify that the charching/ discharging effect of the capacitor is less pronounced.

#### //Squarewave.c Generates a squarewave using a look-up table

```

#include "dsk6713_aic23.h" //codec-DSK interface support

Uint32 fs=DSK6713_AIC23_FREQ_8KHZ; //set sampling rate

#define table_size (int)0x40 //size of table=64

short data_table[table_size]; //data table array

int i;

interrupt void c_int11() //interrupt service routine

{

output_sample(data_table[i]); //output value each Ts

if (i < table_size) ++i; //if table size is reached</pre>

```

```

else i = 0; //reinitialize counter

return; //return from interrupt

}

main()

{

for(i=0; i<table_size/2; i++) //set 1st half of buffer

data_table[i] = 0x7FFF; //with max value (2^15)-1

for(i=table_size/2;i<table_size;i++) //set 2nd half of buffer

data_table[i] = -0x8000; //with -(2^15)

i = 0; //reinit counter

comm_intr(); //init DSK, codec, McBSP

while (1); //infinite loop

}

```

FIGURE 2.13. Square-wave generation program (squarewave.c).

# **CHAPTER-4**

# ARCHITECTURE AND INSTRUCTION SET OF THE C6713 PROCESSOR

#### **4.1 INTRODUCTION**

Texas Instruments introduced the first-generation TMS32010 DSP in 1982, the TMS320C25 in 1986, and the TMS320C50 in 1991. Several versions of each of these processors—C1x, C2x, and C5x—are available with different features, such as faster execution speed. These 16-bit processors are all fixed-point processors and are codecompatible.

In a von Neumann architecture, program instructions and data are stored in a single memory space. A processor with a von Neumann architecture can make a read or a write to memory during each instruction cycle. Typical DSP applications require several accesses to memory within one instruction cycle. The fixed-point processors C1x, C2x, and C5x are based on a modified Harvard architecture with separate memory spaces for data and instructions that allow concurrent accesses.

Quantization error or round-off noise from an ADC is a concern with a fixedpoint processor. An ADC uses only a best-estimate digital value to represent an input. For example, consider an ADC with a word length of 8 bits and an input range of  $\pm 1.5$ V.The steps represented by the ADC are: input range/28 = 3/256 = 11.72mV. This produces errors that can be up to  $\pm (11.72$ mV)/2 =  $\pm 5.86$ mV. Only a best estimate can be used by the ADC to represent input values that are not multiples of 11.72mV.With an 8-bit ADC, 28 or 256 different levels can represent the input signal. An ADC with a larger word length, such as a 16-bit ADC (or larger, currently very common), can reduce the quantization error, yielding a higher resolution.The morebits an ADC has, the better it can represent an input signal.

The TMS320C30 floating-point processor was introduced in the late 1980s. The C31, the C32, and the more recent C33 are all members of the C3x family of floating-point processors. The C4x floating-point processors, introduced subsequently, are code-compatible with the C3x processors and are based on the modified Harvard architecture. The C62x is not code-compatible with the previous generation of fixed-point processors. Subsequently, the TMS320C6701 (C67x) floating-point processor was introduced as

another member of the C6x family of processors. The instruction set of the C62x fixedpoint processor is a subset of the instruction set of the C67x processor. Appendix A contains a list of instructions available on the C6x processors.

An application-specific integrated circuit (ASIC) has a DSP core with customized circuitry for a specific application. A C6x processor can be used as a standard general-purpose DSp programmed for a specific application. Specific-purpose digital signal processors are the modem, echo canceler, and others.

A fixed-point processor is better for devices that use batteries, such as cellular phones, since it uses less power than does an equivalent floating-point processor. The fixed-point processors, C1x, C2x, and C5x, are 16-bit processors with limited dynamic range and precision. The C6x fixed-point processor is a 32-bit processor with improved dynamic range and precision. In a fixed-point processor, it is necessary to scale the data. Overflow, which occurs when an operation such as the addition of two numbers produces a result with more bits than can fit within a processor's register, becomes a concern.

A floating-point processor is generally more expensive since it has more "real estate" or is a larger chip because of additional circuitry necessary to handle integer as well as floating-point arithmetic. Several factors, such as cost, power consumption, and speed, come into play when choosing a specific DSp. The C6x processors are particularly useful for applications requiring intensive computations. Family members of the C6x include both fixed-point (e.g., C62x, C64x) and floating-point (e.g., C67x) processors. Other DSp's are also available from companies such as Motorola and Analog Devices.

Other architectures include the Super Scalar, which requires special hardware to determine which instructions are executed in parallel. The burden is then on the processor more than on the programmer, as in the VLIW architecture. It does not necessarily execute the same group of instructions, and as a result, it is difficult to time. Thus, it is rarely used in DSP.

#### 4.2 TMS320C6x ARCHITECTURE

The TMS320C6713 onboard the DSK is a floating-point processor based on the VLIW architecture. Internal memory includes a two-level cache architecture with 4 kB of level 1 program cache (L1P), 4 kB of level 1 data cache (L1D), and 256 kB of level 2 memory shared between program and data space. It has a glueless (direct) interface to both synchronous memories (SDRAM and SBSRAM) and asynchronous memories (SRAM and EPROM). Synchronous memory requires clocking but provides a compromise between static SRAM and dynamic DRAM, with SRAM being faster but more expensive than DRAM.

On-chip peripherals include two McBSPs, two timers, a host port interface (HPI), and a 32-bit EMIF. It requires 3.3 V for I/O and 1.26 V for the core (internal). Internal buses include a 32-bit program address bus, a 256-bit program data bus to accommodate eight 32-bit instructions, two 32-bit data address buses, two 64-bit data buses, and two 64-bit store data buses. With a 32-bit address bus, the total memory space is 232 = 4GB, including four external memory spaces: CE0, CE1, CE2, and CE3. Figure 3.1 shows a functional block diagram of the C6713 processor included with CCS.

Independent memory banks on the C6x allow for two memory accesses within one instruction cycle. Two independent memory banks can be accessed using two independent buses. Since internal memory is organized into memory banks, two loads or two stores of instructions can be performed in parallel. No conflict results if the data accessed are in different memory banks. Separate buses for program, data, and direct memory access (DMA) allow the C6x to perform concurrent program fetches, data read and write, and DMA operations. With data and instructions residing in separate memory spaces, concurrent memory accesses are possible. The C6x has a byte-addressable memory space. Internal memory is organized as separate program and data memory spaces, with two 32-bit internal ports (two 64- bit ports with the C64x) to access internal memory.

The C6713 on the DSK includes 264kB of internal memory, which starts at 0x00000000, and 16MB of external SDRAM, mapped through CE0 starting at 0x80000000.The DSK also includes 512 kB of Flash memory (256 kB readily available to the user), mapped through CE1 starting at 0x90000000. Figure 3.2 shows the L2 internal memory configuration, included with CCS. Table 3.1 shows the memory map, also included with CCS.

With the DSK operating at 225MHz, one can ideally achieve two multiplies and accumulates per cycle, for a total of 450 million multiplies and accumulates (MACs) per second. With six of the eight functional units in Figure 3.1 (not the .D units described below) capable of handling floating-point operations, it is possible to perform 1350 million floating-point operations per second (MFLOPS). Operating at 225MHz, this translates into 1800 million instructions per second (MIPS) with a 4.44-ns instruction cycle time.

#### **4.3 FUNCTIONAL UNITS**

The CPU consists of eight independent functional units divided into two data paths, A and B, as shown in Figure 3.1. Each path has a unit for multiply operations (.M), for logical and arithmetic operations (.L), for branch, bit manipulation, and arithmetic operations (.S), and for loading/storing and arithmetic operations (.D). The .S and .L units are for arithmetic, logical, and branch instructions. All data transfers make use of the .D units.

The arithmetic operations, such as subtract or add (SUB or ADD), can be performed by all the units, except the .M units (one from each data path). The eight functional units consist of four floating/fixed-point ALUs (two .L and two .S), two fixed-point ALUs (.D units), and two floating/fixed-point multipliers (.M units). Each functional unit can read directly from or write directly to the register file within its own path. Each path includes a set of sixteen 32-bit registers, A0 through A15 and B0 through B15. Units ending in 1 write to register file A, and units ending in 2 write to register file B.

FIGURE 3.1. Functional block diagram of TMS320C6713 (Courtesy of Texas Instruments).

FIGURE 3.2. Internal memory configuration of L2 (Courtesy of Texas Instruments).

| TABLE 3.1 | Memory | Мар |

|-----------|--------|-----|

|-----------|--------|-----|

| Memory Block Description                   | Block Size (Bytes) | Hex Address Range   |

|--------------------------------------------|--------------------|---------------------|

| Internal RAM (L2)                          | 192K               | 0000 0000-0002 FFFF |

| Internal RAM/cache                         | 64 K               | 0003 0000-0003 FFFF |

| Reserved                                   | 24 M-256 K         | 0004 0000-017F FFFF |

| External memory interface (EMIF) registers | 256 K              | 0180 0000-0183 FFFF |

| L2 registers                               | 128K               | 0184 0000–0185 FFFF |

| Reserved                                   | 128K               | 0186 0000-0187 FFFF |

| HPI registers                              | 256 K              | 0188 0000-018B FFFF |

| McBSP 0 registers                          | 256 K              | 018C 0000-018F FFFF |

| McBSP 1 registers                          | 256 K              | 0190 0000-0193 FFFF |

| Timer 0 registers                          | 256 K              | 0194 0000-0197 FFFF |

| Timer 1 registers                          | 256 K              | 0198 0000-019B FFFF |

| Interrupt selector registers               | 512                | 019C 0000-019C 01FF |

| Device configuration registers             | 4                  | 019C 0200-019C 0203 |

| Reserved                                   | 256 K516           | 091C 0204-019F FFFF |

| EDMA RAM and EDMA registers                | 256 K              | 01A0 0000-01A3 FFFF |

| Reserved                                   | 768 K              | 01A4 0000-01AF FFFF |

| GPIO registers                             | 16K                | 01B0 0000-01B0 3FFF |

| Reserved                                   | 240 K              | 01B0 4000-01B3 FFFF |

| I2C0 registers                             | 16K                | 01B4 0000-01B4 3FFF |

| I2C1 registers                             | 16K                | 01B4 4000–01B4 7FFF |

| Reserved                                   | 16K                | 01B4 8000-01B4 BFFF |

| McASP0 registers                           | 16K                | 01B4 C000–01B4 FFFF |

| McASP1 registers                           | 16K                | 01B5 0000-01B5 3FFF |

| Reserved                                   | 160 K              | 01B5 4000-01B7 BFFF |

| PLL registers                              | 8K                 | 01B7 C000-01B7 DFFF |

| Reserved                                   | 264 K              | 01B7 E000-01BB FFFF |

| Emulation registers                        | 256 K              | 01BC 0000-01BF FFFF |

| Reserved                                   | 4 M                | 01C0 0000-01FF FFFF |

| QDMA registers                             | 52                 | 0200 0000–0200 0033 |

| Reserved                                   | 16 M–52            | 0200 0034-02FF FFFF |

| Reserved                                   | 720 M              | 0300 0000–2FFF FFFF |

| McBSP0 data port                           | 64 M               | 3000 0000–33FF FFFF |

| McBSP1 data port                           | 64 M               | 3400 0000–37FF FFFF |

| Reserved                                   | 64 M               | 3800 0000–3BFF FFFF |

| McASP0 data port                           | 1 M                | 3C00 0000-3C0F FFFF |

| McASP1 data port                           | 1 M                | 3C10 0000-3C1F FFFF |

| Reserved                                   | 1G + 62M           | 3C20 0000-7FFF FFFF |

| EMIF CE0*                                  | 256 M              | 8000 0000-8FFF FFFF |

| EMIF CE1*                                  | 256 M              | 9000 0000-9FFF FFFF |

| EMIF CE2*                                  | 256 M              | A000 0000-AFFF FFFF |

| EMIF CE3*                                  | 256 M              | B000 0000-BFFF FFFF |

| Reserved                                   | 1G                 | C000 0000-FFFF FFFF |

\* The number of EMIF address pins (EA[21:2]) limits the maximum addressable memory (SDRAM) to 128MB per CE space.

Source: Courtesy of Texas Instruments.

Two cross-paths (1x and 2x) allow functional units from one data path to access a 32bit operand from the register file on the opposite side. There can be a maximum of two cross-path source reads per cycle. Each functional unit side can access data from the registers on the opposite side using a cross-path (i.e., the functional units on one side can access the register set from the other side). There are 32 generalpurpose registers, but some of them are reserved for specific addressing or are used for conditional instructions.

| 3 | 1 0 | 31 | 0 | 31 0 | 31 | 0 | 31 | 0 | 31 | 0 | 31 | 0 | 31 | 0 |

|---|-----|----|---|------|----|---|----|---|----|---|----|---|----|---|

|   | 1   |    | 0 | 1    |    | 1 |    | 0 |    | 1 |    | 1 |    | 0 |

|   | А   | В  |   | С    |    | D | E  |   | F  |   | G  |   | ł  | H |

FIGURE 3.3. One FP with three EPs showing the "p" bit of each instruction.

#### 4.4 FETCH AND EXECUTE PACKETS

The architecture VELOCITI, introduced by TI, is derived from the VLIW architecture. An execute packet (EP) consists of a group of instructions that can be executed in parallel within the same cycle time. The number of EPs within a fetch packet (FP) can vary from one (with eight parallel instructions) to eight (with no parallel instructions). The VLIW architecture was modified to allow more than one EP to be included within an FP.

The least significant bit of every 32-bit instruction is used to determine if the next or subsequent instruction belongs in the same EP (if 1) or is part of the next EP (if 0). Consider an FP with three EPs: EP1, with two parallel instructions, and EP2 and EP3, each with three parallel instructions, as follows:

Instruction A

|| Instruction B

Instruction C

|| Instruction D

|  | Instruction E |  |  |  |  |  |  |

|--|---------------|--|--|--|--|--|--|

|  | Instruction F |  |  |  |  |  |  |

|  | Instruction G |  |  |  |  |  |  |

|  | Instruction H |  |  |  |  |  |  |

EP1 contains the two parallel instructions A and B; EP2 contains the three parallel instructions C, D, and E; and EP3 contains the three parallel instructions F, G, and H. The FP would be as shown in Figure 3.3. Bit 0 (LSB) of each 32-bit instruction contains a "p" bit that signals whether it is in parallel with a subsequent instruction. For example, the "p" bit of instruction B is zero, denoting that it is not within the same EP as the subsequent instruction C. Similarly, instruction E is not within the same EP as instruction F.

#### **4.5 PIPELINING**

Pipelining is a key feature in a DSp to get parallel instructions working properly, requiring careful timing. There are three stages of pipelining: program fetch, decode, and execute.

- **1.** The *program fetch stage* is composed of four phases:

- (a) PG: program address generate (in the CPU) to fetch an address

- (b) *PS*: program address send (to memory) to send the address

- (c) PW: program address ready wait (memory read) to wait for data