# DESIGN OF ZIGBEE TRANSMITTER FOR IEEE 802.15.4 STANDARD

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIRMENTS FOR THE DEGREE OF

# **MASTER OF TECHNOLOGY**

IN

# VLSI DESIGN AND EMBEDDED SYSTEMS

By

**JOSHNA PALEPU**

**Roll No: 209EC2131**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING NATIONAL INSTITUTE OF TECHNOLOGY ROURKELA, ODISHA INDIA

# 2011

# DESIGN OF ZIGBEE TRANSMITTER FOR IEEE 802.15.4 STANDRAD

A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIRMENTS FOR THE DEGREE OF

# MASTER OF TECHNOLOGY

IN

# VLSI DESIGN AND EMBEDDED SYSTEMS

# BY

# JOSHNA PALEPU

# **Roll No: 209EC2131**

# UNDER THE GUIDANCE OF

# Prof. KAMALAKANTA MAHAPATRA

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING NATIONAL INSTITUTE OF TECHNOLOGY ROURKELA, ODISHA, INDIA 2011

# NATIONAL INSTITUTE OF TECHNOLOGY ROURKELA

# CERTIFICATE

This is to certify that the thesis entitled, "DESIGN OF ZIGBEE TRANSMITTER FOR IEEE 802.15.4 STANDRAD" submitted by JOSHNA PALEPU Roll no: 209EC2131 in partial fulfilment of the requirements for the award of Master of Technology Degree in Electronics & Communication Engineering with specialization in VLSI Design and Embedded Systems during 2010-2011 at the National Institute of Technology, Rourkela (Deemed University) is an authentic work carried out by her under my supervision and guidance. To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University / Institute for the award of any Degree or Diploma.

DATE

# Prof.KAMALAKANTA MAHAPATRA

(Supervisor) Dept. of Electronics & Communication Engg. National Institute of Technology Rourkela-769008

#### ACKNOWLEDGEMENTS

I am deeply indebted to **Prof. KAMALAKANTA MOHAPATRA** Dept. of E&CE, my supervisor on this project, for consistently providing me with the required guidance to help me in the timely and successful completion of this project. In spite of his extremely busy schedules in Department, he was always available to share with me his deep insights, wide knowledge and extensive experience.

I would like to express my gratitude to the following members **Mr M. Madhav Kumar, Sc-D, Mrs Nalini Vidhulatha, Sc-C**, **Mr Dinesh Kumar** of ANURAG Lab, DRDO for giving sufficient guidance for completing the project.

I would like to express my humble respects to **Prof. Sarat Kumar Patra HOD Dept. of E&CE, Prof. D.P.Acharya, Prof.N.V.L.N Murthy,** for teaching me and also helping me how to learn.

I would like to thank my institution and all the faculty members of ECE Department for their help and guidance. They have been great sources of inspiration to me and I thank them from the bottom of my heart.

I would like to thank all my friends and especially my classmates for all the thoughtful and mind stimulating discussions we had, which prompted us to think beyond the obvious. I've enjoyed their companionship so much during my stay at NIT Rourkela.

I would to like to extend my heartfelt appreciation to my parents, my uncle V.Ananda Rao and well wishers for their understanding and constant support in this academic pursuits.

Last but not least, I would like to give thanks to my personal Savior, Jesus Christ, who has given me strength and wisdom to overcome all the difficulties in my life. Without His guidance, love and promise, I would not have had the courage to purse graduate studies.

# Abstract

ZigBee is a standard defines a set of communication protocols for low-data-rate shortrange wireless networking. ZigBee-based wireless devices operate in 868 MHz, 915 MHz, and 2.4 GHz frequency bands. The maximum data rate is 250 K bits per second. ZigBee is mainly for battery-powered applications where low data rate, low cost, and long battery life are main requirements. This thesis explores low power RFIC design for various blocks in Zigbee Transmitter.

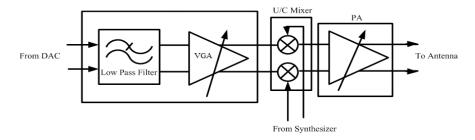

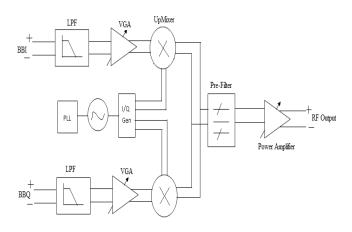

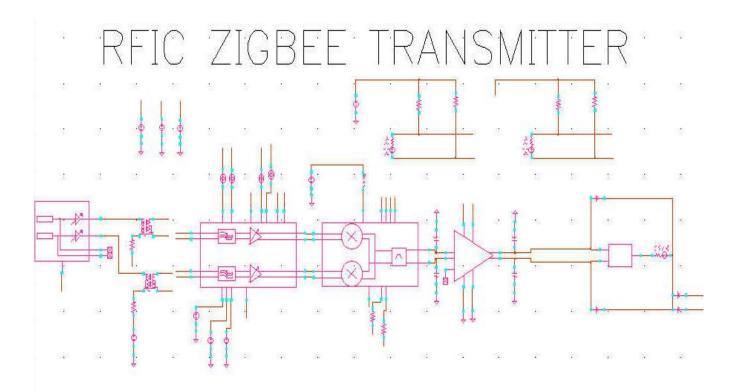

Zigbee RFTransmitter Comprises of Low Pass Filter, Variable Gain Amplifier, Up conversion Mixer and Power Amplifier.

The proposed VGA is characterized by a wide range of gain variation The singlestage VGA is designed in UMC 0.18-*u* m CMOS technology and shows the maximum gain variation of 62 dB. The VGA dissipates 630 *u*A from 1.8-V supply while occupying (250  $\mu$ m x 167.3  $\mu$ m) of chip area.

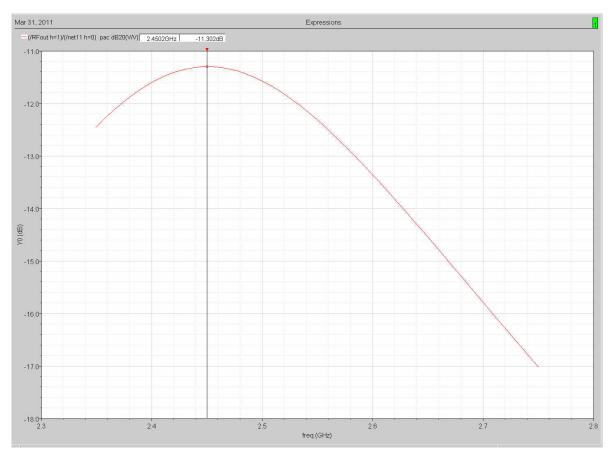

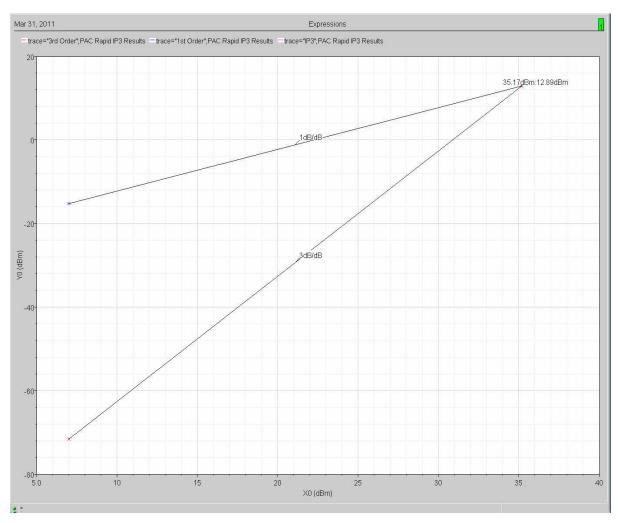

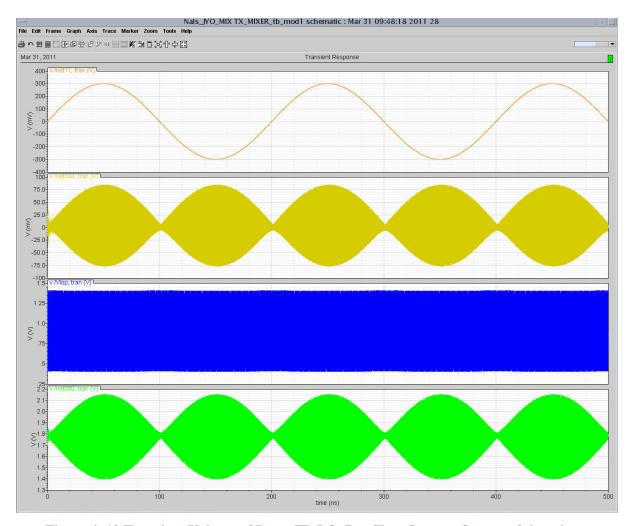

A low-voltage low-power and high linearity up-conversion mixer, designed in UMC 0.18-um RFCMOS technology is proposed to realize the transmitter front-end in the frequency band of 2.45 GHz. The proposed mixer can convert a 5 MHz intermediate frequency (IF) signals to a 2.45GHz RF signals, with a local oscillator at 2.45GHz. Simulation results demonstrate that at 2.45GHz, the circuit provides -11.30dB of conversion gain and the input-referred third-order intercept point (IIP3) of 35.16 dBm, output-referred third order intercept point(OIP3) of 12.88 dBm while drawing only 10mA for the mixer core under a supply voltage of 1.8 V.

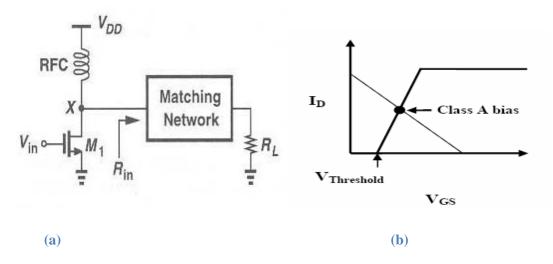

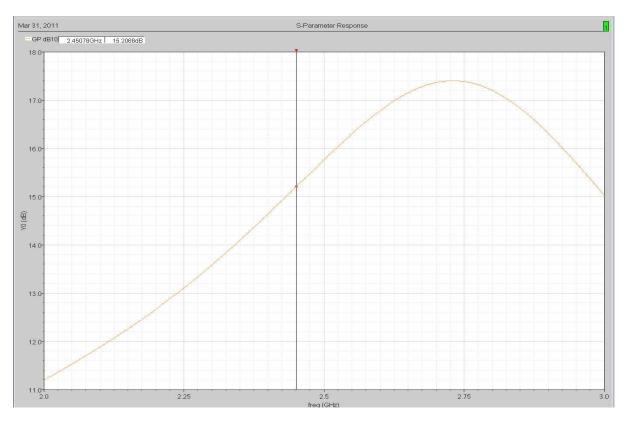

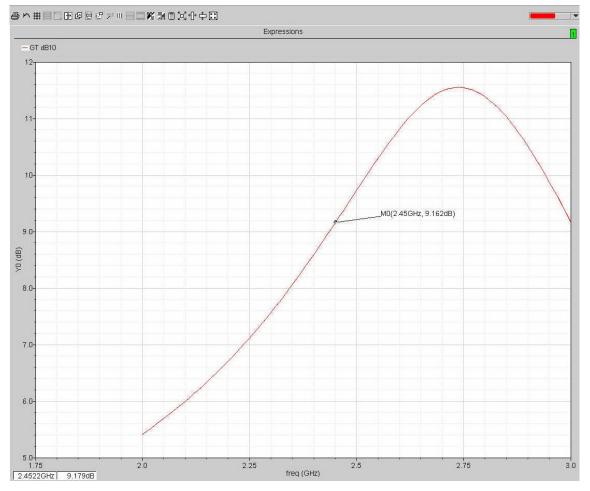

A low power Differential class A power amplifier is designed in the UMC 0.18um RFCMOS technology. The class A power amplifier provides 0 dBm output power with a power-added efficiency (PAE) of 22% and Power Gain of 10dB with 1.8V supply voltage. The dc power consumption is only 4.5mW.

And all these blocks were integrated and simulated using Cadence<sup>®</sup> SpectreRF simulator in UMC-0.18um Mixed Signal CMOS RF models for the best simulation results.

# Contents

| Abstract  | iv                                                 |

|-----------|----------------------------------------------------|

| LIST OF   | F FIGURES viii                                     |

| LIST OF   | F TABLESxi                                         |

| Chapter-  | .11                                                |

| Introduc  | tion1                                              |

| Introd    | uction1                                            |

| 1.1       | Research Goal                                      |

| 1.2       | Thesis outline                                     |

| Chapter-  | -2                                                 |

| Radio Ti  | ransceiver Architectures4                          |

| 2.1       | Radio Transceiver Architectures                    |

| 2.1.      | 1 Superheterodyne receiver                         |

| 2.1.      | 2 Low IF receiver                                  |

| 2.1.      | 3 Direct Conversion receiver                       |

| 2.2       | Transmitter Architectures                          |

| 2.2.      | 1 Direct Conversion Architecture                   |

| 2.2.2     | 2 Two Step Architecture                            |

| 2.3       | Design of Zigbee Transmitter                       |

| 2.3.      | 1 Specifications for the IEEE 802.15.4 RF Frontend |

| Chapter-  | -315                                               |

| Design of | of a Variable Gain Amplifier15                     |

| 3.1       | Introduction                                       |

| 3.2       | Decibel Linear Function16                          |

| 3.3       | Variable Gain Amplifier Design                     |

| 3.3.      | 1 Control Circuit Block                            |

| 3.3.      | 2 Amplifier Block                                  |

| 3.3     | .3                | Buffer Block                                 |

|---------|-------------------|----------------------------------------------|

| 3.4     | The               | e Single Stage Overall VGA21                 |

| 3.5     | Res               | sults and Discussion                         |

| 3.5     | .1                | Layout Issues                                |

| Chapter | :-4               |                                              |

| Design  | of a <sup>1</sup> | Up-Conversion Mixer                          |

| 4.1     | Intr              | roduction                                    |

| 4.2     | Miz               | xer Topology                                 |

| 4.2     | .1                | Gilbert Cell                                 |

| 4.3     | Per               | formance Parameters                          |

| 4.3     | .1                | Conversion Gain                              |

| 4.3     | .2                | Gain Compression                             |

| 4.3     | .3                | Third order Intermodulation Distortion       |

| 4.4     | Pro               | posed up conversion mixer for High Linearity |

| 4.4     | .1                | Circuit Operation                            |

| 4.5     | Res               | sults and Discussion                         |

| Chapter | :-5               |                                              |

| Design  | of a l            | Power Amplifier                              |

| 5.1     | Intr              | roduction                                    |

| 5.2     | RF                | Power Amplifier Classification               |

| 5.2     | .1                | Class A Power Amplifier41                    |

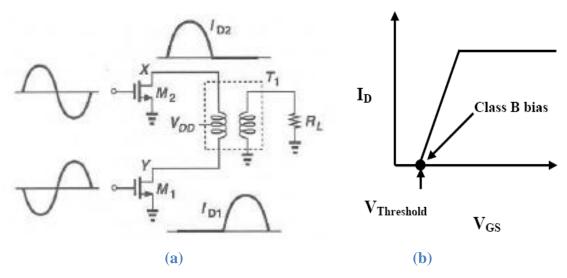

| 5.2     | .2                | Class B Power Amplifier                      |

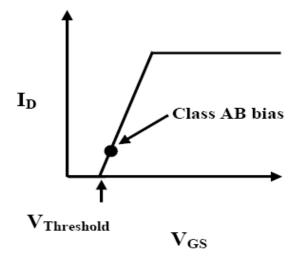

| 5.2     | .3                | Class AB Power Amplifier                     |

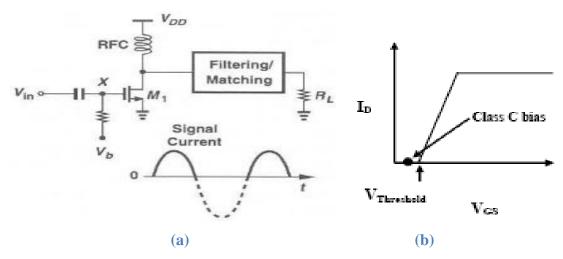

| 5.2     | .4                | Class C Power Amplifier                      |

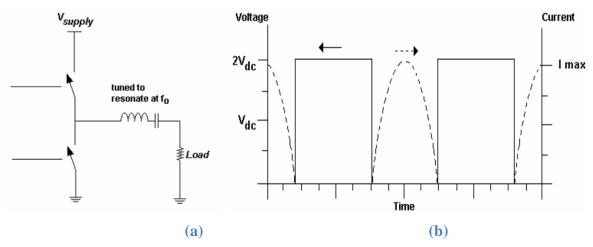

| 5.2     | .5                | Class D Power Amplifier                      |

| 5.2     | .6                | Class E Power Amplifier                      |

| 5.2     | .7                | Class F Power Amplifier                      |

| 5.3 Per      | formance Parameters                        |

|--------------|--------------------------------------------|

| 5.3.1        | Power Added Efficiency48                   |

| 5.3.2        | Power Gain                                 |

| 5.3.2.1      | Operating Power Gain                       |

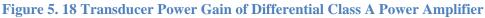

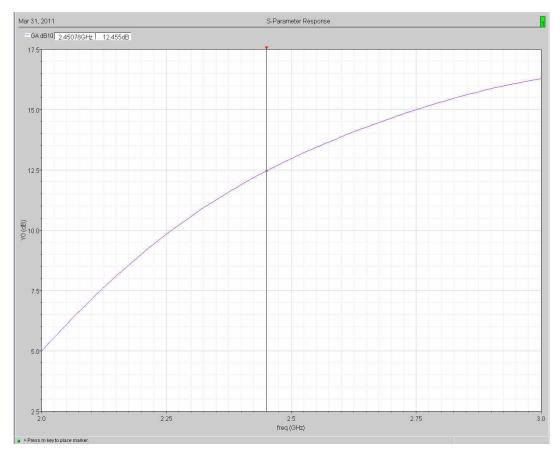

| 5.3.2.2      | Transducer Power Gain                      |

| 5.3.2.3      | Available Power Gain                       |

| 5.3.3        | One dB Compression Point                   |

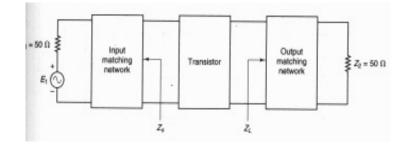

| 5.4 Imj      | pedance Matching Network                   |

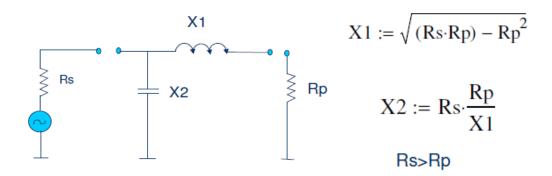

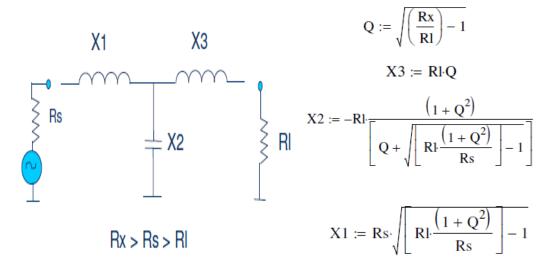

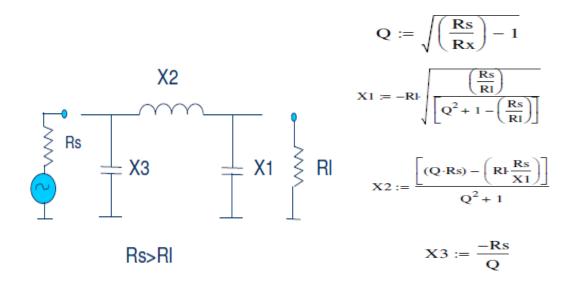

| 5.4.1        | L Section Matching Network                 |

| 5.4.2        | T Section Matching Network                 |

| 5.4.3        | $\pi$ Section Matching Network             |

| 5.5 Pro      | posed Differential Class A Power Amplifier |

| 5.5.1        | Circuit Operation                          |

| 5.6 Res      | sults and Discussion                       |

| 5.6.1        | Layout Issues                              |

| Chapter-6    |                                            |

| Design of a  | Zigbee RFTransmitter63                     |

| 6.1 De       | sign of a Zigbee RFTransmitter63           |

| 6.2 Res      | sults and Discussion64                     |

| Chapter-7    |                                            |

| Conclusion a | and Future Research                        |

| 7.1 Co       | nclusion66                                 |

| 7.2 Fut      | ure Research                               |

| REFERENC     | CES:                                       |

# **LIST OF FIGURES**

| FIGURE 1.1 SIMPLIFIED BLOCK DIAGRAM OF RADIO FREQUENCY TRANSCEIVER             | 1  |

|--------------------------------------------------------------------------------|----|

| FIGURE 1.2 RFTRANSMITTER BLOCK DIAGRAM                                         | 2  |

| FIGURE 2.1 BLOCK DIAGRAM OF SUPERHETERODYNE RECEIVER                           | 5  |

| FIGURE 2. 2 BLOCK DIAGRAM OF DIRECT CONVERSION RECEIVER                        | 8  |

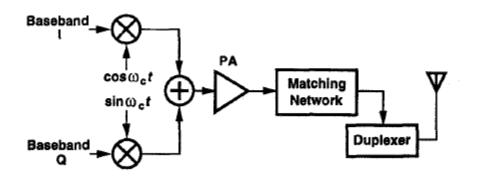

| FIGURE 2. 3 BLOCK DIAGRAM OF DIRECT CONVERSION TRANSMITTER                     | 9  |

| FIGURE 2. 4 LO PULLING BY PA                                                   | 9  |

| FIGURE 2. 5 INJECTION PULLING AS THE MAGNITUDE OF THE INJECTED NOISE INCREASES | 10 |

| FIGURE 2. 6 DIRECT CONVERSION TRANSMITTER WITH OFFSET LO                       | 10 |

| FIGURE 2. 7 TWO-STEP TRANSMITTER                                               | 11 |

| FIGURE 2. 8 RF FRONT END FOR IEEE 802.15.4                                     | 12 |

| FIGURE 2. 9 ZIGBEE TRANSMITTER ARCHITECTURE                                    | 13 |

| FIGURE 3. 1 (A) DIGITAL CONTROLLED VGA, (B) ANALOG CONTROLLED VGA              | 15 |

| FIGURE 3. 2 DECIBEL SCALE PLOTS OF (1), (2) AND THE IDEAL EXPONENTIAL FUNCTION | 17 |

| FIGURE 3. 3 : DECIBEL SCALE PLOTS OF (3) FOR VARIOUS VALUES OF K               | 17 |

| FIGURE 3. 4 BLOCK DIAGRAM OF TWO STAGE VARIABLE GAIN AMPLIFIER                 | 18 |

| FIGURE 3. 5 SCHEMATIC OF CONTROL STAGE                                         | 18 |

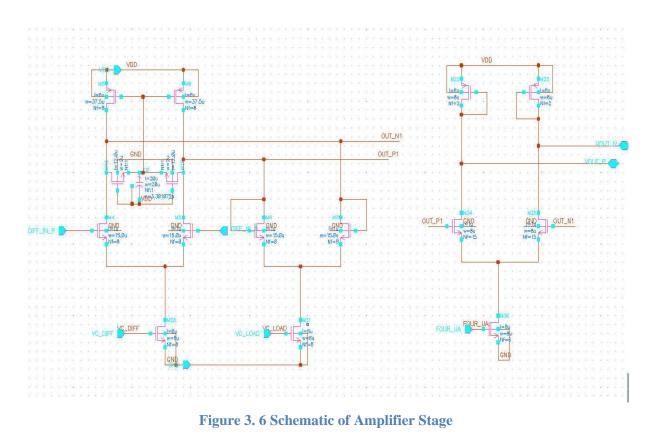

| FIGURE 3. 6 SCHEMATIC OF AMPLIFIER STAGE                                       | 20 |

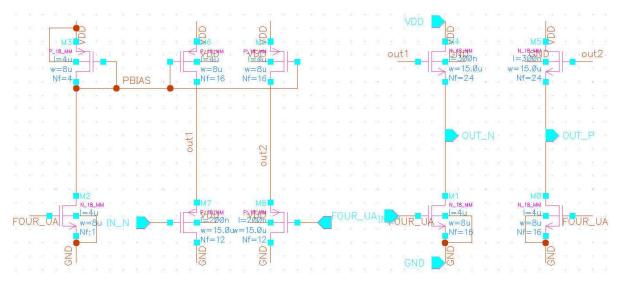

| FIGURE 3. 7 SCHEMATIC OF BUFFER STAGE                                          | 21 |

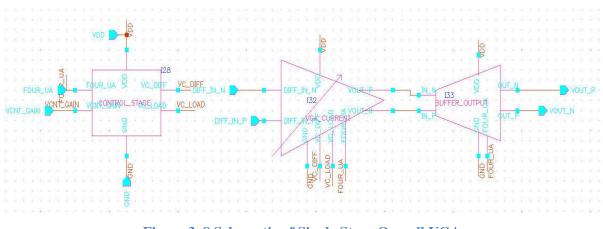

| FIGURE 3. 8 SCHEMATIC OF SINGLE STAGE OVERALL VGA                              | 21 |

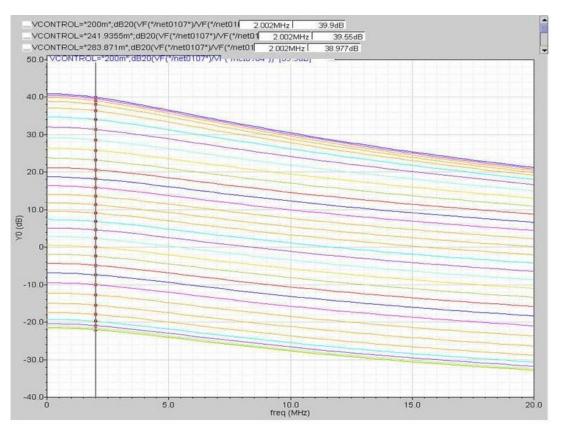

| FIGURE 3. 9 FREQUENCY VERSUS GAIN FOR VARIOUS CONTROL VOLTAGES                 | 23 |

| FIGURE 3. 10 SCHEMATIC OF PROPOSED VGA SETUP                                   | 24 |

| FIGURE 3. 11 ANALOG DESIGN ENVIRONMENT FOR VGA SETUP                           | 24 |

| FIGURE 3. 12 LAYOUT OF SINGLE STAGE VARIABLE GAIN AMPLIFIER                    | 25 |

| FIGURE 3. 13 CONFIG WINDOW OF VGA FOR ANALOG EXTRACTED VIEW                    | 26 |

| FIGURE 3. 14 POST-LAYOUT SIMULATIONS FOR VGA                                   | 26 |

| FIGURE 4. 1 ZIGBEE RFTRANSMITTER ARCHITECTURE                                  | 28 |

| FIGURE 4. 2 SCHEMATIC OF CONVENTIONAL GILBERT MIXER                            | 29 |

| FIGURE 4. 3 GRAPHICAL REPRESENTATION OF INPUT 1DB COMPRESSION POINT OF MIXER   | 31 |

| FIGURE 4. 4 FREQUENCY SPECTRUM AT INPUT AND OUTPUT PORT OF MIXER               | 32 |

| FIGURE 4. 5 GRAPHICAL REPRESENTATION OF INPUT THIRD ORDER INTERCEPT POINT IIP3 | 33 |

| FIGURE 4. 6 SCHEMATIC OF PROPOSED UP CONVERSION MIXER SETUP                    | 34 |

| FIGURE 4. 7 SCHEMATIC OF PROPOSED UP CONVERSION MIXER                          | 35 |

| FIGURE 4. 8 SCHEMATIC OF PRE-FILTER                                                       |

|-------------------------------------------------------------------------------------------|

| FIGURE 4. 9 ANALOG DESIGN ENVIRONMENT FOR CONVERSION GAIN                                 |

| FIGURE 4. 10 CONVERSION GAIN OF THE PROPOSED MIXER                                        |

| FIGURE 4. 11 IIP3 AND OIP3 OF THE PROPOSED MIXER                                          |

| FIGURE 4. 12 TRANSIENT VOLTAGE OF INPUT IF, LO, PRE-FILTER OUTPUT, OUTPUT OF THE          |

| MIXER                                                                                     |

| FIGURE 5. 1 (A) CLASS A POWER AMPLIFIER, (B) BIASING FOR CLASS A POWER AMPLIFIER 41       |

| FIGURE 5. 2 (A) CLASS B STAGE USING TRANSFORMER, (B) BIASING FOR CLASS B AMPLIFIER.43     |

| FIGURE 5. 3 BIASING FOR CLASS AB AMPLIFIER                                                |

| FIGURE 5. 4 (A) CLASS C STAGE , (B) BIASING FOR CLASS C AMPLIFIER44                       |

| FIGURE 5. 5 (A) CLASS D STAGE, (B) CLASS D VOLTAGE AND CURRENT WAVEFORMS46                |

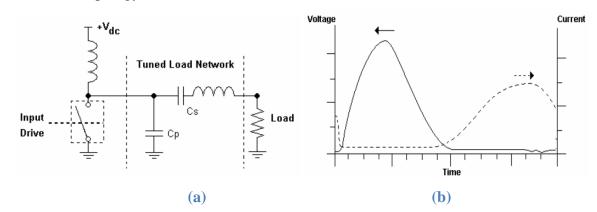

| FIGURE 5. 6 (A) CLASS E STAGE , (B) CLASS E VOLTAGE AND CURRENT WAVEFORMS                 |

| Figure 5.7 (a) Class F stage , (b) Class F voltage and Current Waveforms47                |

| FIGURE 5. 8 GAIN COMPRESSION PLOT                                                         |

| FIGURE 5. 9 BLOCK DIAGRAM OF AMPLIFIER WITH MATCHING NETWORKS                             |

| FIGURE 5. 10 L SECTION MATCHING NETWORK                                                   |

| FIGURE 5. 11 T SECTION MATCHING NETWORK                                                   |

|                                                                                           |

| Figure 5. 12 $\Pi$ Section matching network                                               |

| FIGURE 5. 12 IT SECTION MATCHING NETWORK                                                  |

|                                                                                           |

| FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER53                  |

| FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER                    |

| FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER                    |

| FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER                    |

| FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER                    |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

| <ul> <li>FIGURE 5. 13 SCHEMATIC OF SINGLE ENDED CASCODE CLASS A POWER AMPLIFIER</li></ul> |

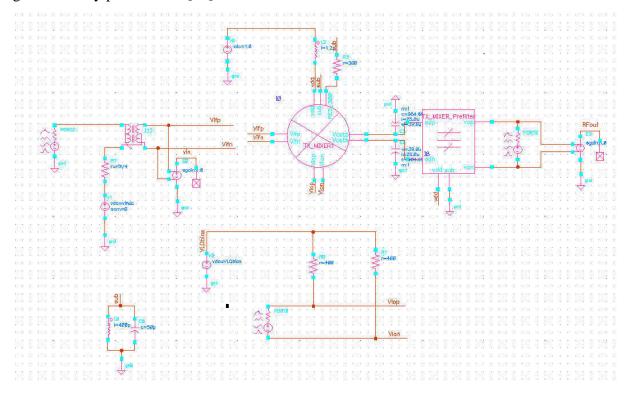

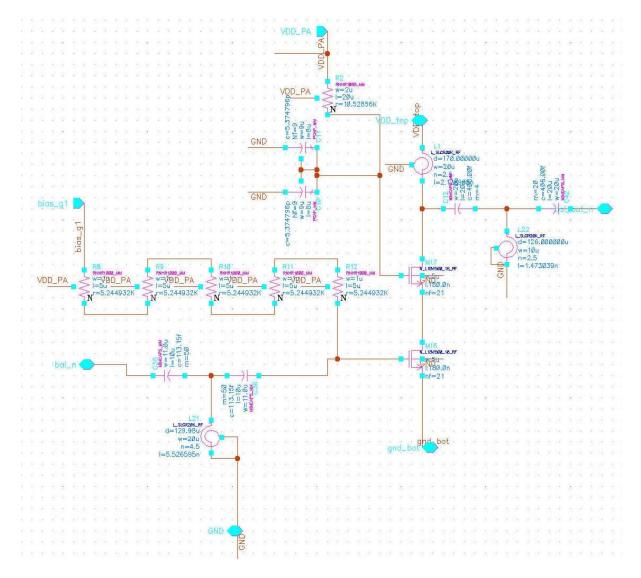

| FIGURE 6. 1 SCHEMATIC OF ZIGBEE RFTRANSMITTER                                                              |

|------------------------------------------------------------------------------------------------------------|

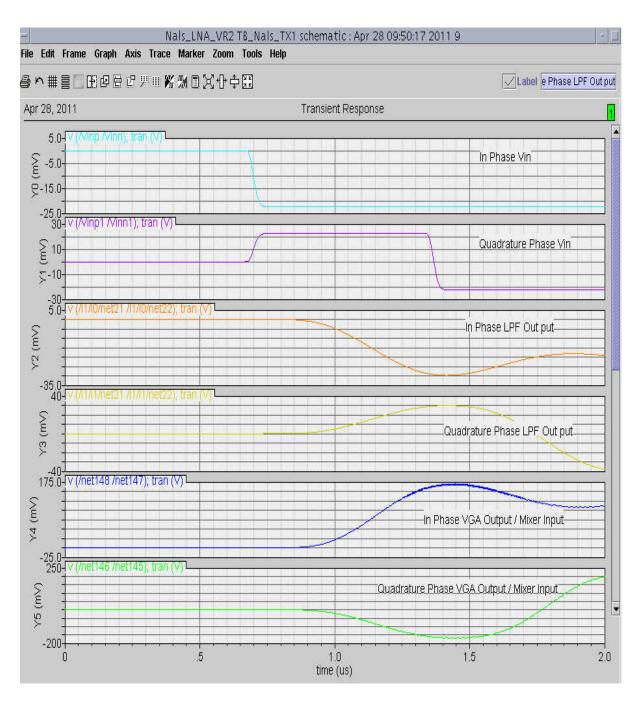

| Figure 6. 2 Transient Voltage of In phase and Quadrature phase components of $V_{\mbox{\scriptsize IN}}$ , |

| LPF OUTPUT, VGA OUTPUT/MIXER INPUT64                                                                       |

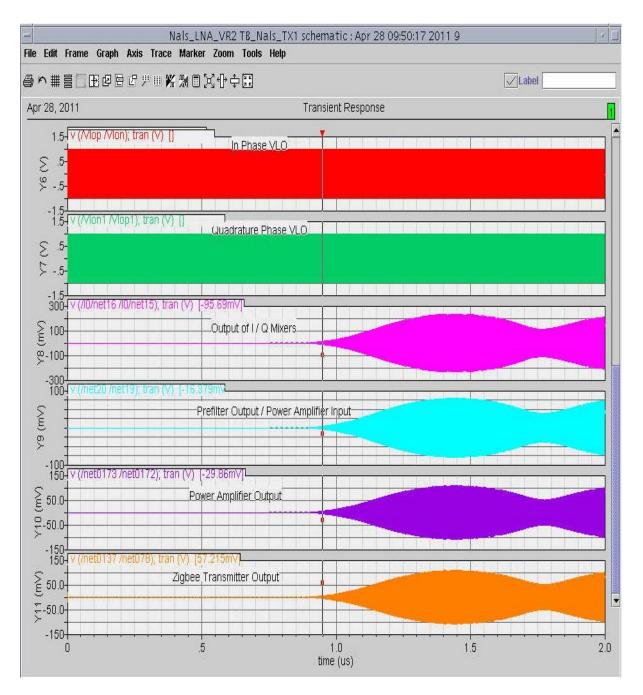

| FIGURE 6. 3 TRANSIENT VOLTAGE OF IN PHASE AND QUADRATURE PHASE COMPONENTS OF                               |

| VLO, OUTPUT OF MIXER, POWER AMPLIFIER INPUT, POWER AMPLIFIER OUTPUT AND                                    |

| ZIGBEE TRANSMITTER OUTPUT                                                                                  |

# LIST OF TABLES

| TABLE 2. 1 Specification of Zigbee technology                             | 13 |

|---------------------------------------------------------------------------|----|

| TABLE 3. 1 VCONTROL VERSUS VGA OUTPUT (GAIN DB)                           | 22 |

| TABLE 4. 1 SUMMARY OF LINEARITY IMPROVED MIXER PERFORMANCE                | 39 |

| TABLE 5. 1 THE PERFORMANCE SUMMARY OF PROPOSED DIFFERENTIAL CLASS A POWER |    |

| Amplifier                                                                 | 62 |

# **Chapter-1**

# Introduction

#### Introduction

In past decades, the tremendous growth in wireless communication systems has given push to the development of low power radio frequency integrated circuits (RFICs). Power consumption of a RFIC design has become a major concern due to battery lifetime consideration. Therefore, a single battery solution becomes very attractive for commercial and industrial purposes.

In recent years, down-scaling in CMOS advanced technologies has provided high performance in digital circuits and inexpensive cost to meet the increasing demand of wireless communication products. With this technology advancement, the unity-current gain frequency ( $f_T$ ) of CMOS technology is now over several tens of GHz and this makes the realization of system-on-chip solution possible to further reduce the cost. The demand of highly integrated CMOS RF building blocks with low power consumption has driven our research initiatives to explore an area of low power CMOS RFIC designs for applications in a RF front-end transceiver [1].

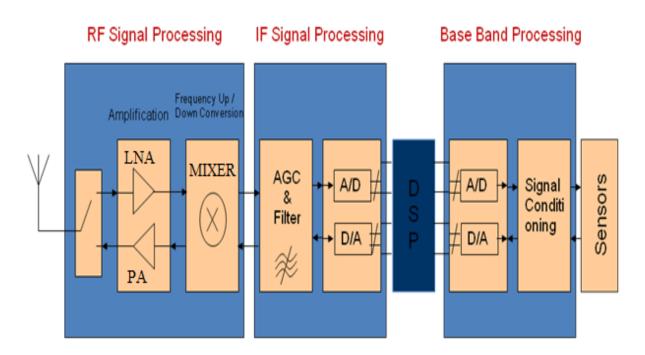

Figure 1.1 Simplified Block Diagram of Radio Frequency Transceiver

A transceiver is a system that transmits or receives a signal. Figure 1.1 shows a simplified block diagram of a radio frequency (RF) transceiver. The transceiver can be split into the RF front-end part that performs the transmission and reception of signals and the digital part that takes care of the signal processing functions. In general, the RF front-end part is the most power hungry portion of a transceiver. If we can reduce the power consumption of the front-end part, it will be a significant achievement to minimize the power consumption of the transceiver. As a result, the overall power consumption of the wireless device can also be reduced. Therefore, the goal of this thesis is to explore the low voltage design issues in the RF front-end part of a transceiver [2].

#### 1.1 Research Goal

There are several major RF building blocks in a front-end transceiver. This thesis concentrates on the design of a low-voltage CMOS up conversion mixer and a Class A Power Amplifier in the transmitting path of the RF front-end section in a transceiver.

A Variable Gain Amplifier is designed such that it stabilizes the amplitude of the output signal under various conditions and supplies a constant-amplitude signal to the detector and filter sections of the read channel.

With the access to UMC 0.18-mm CMOS technology up-conversion mixer is designed to operate at 1.8V supply. The mixer performance is characterized and the measurement results are simulated using SpectreRF simulator in Cadence.

The third objective is to investigate a Class A Power Amplifier. Power amplifiers are typically the most power hungry building block of RF Transceiver. The Power Amplifier is designed to operate at 1.8V voltage supply with Operating frequency of 2.45GHz. The analysis of the performance is verified through simulation using SpectreRF simulator in Cadence.

**Figure 1.2 Transmitter Block Diagram**

#### **1.2** Thesis outline

This thesis is divided into seven chapters. It is organized in such way as to properly layout the detail investigations and results of the research work.

The motivation and research goal are presented in Chapter 1 with a summary of the thesis outline.

Chapter 2 is an overview on modern radio receivers. A general background on different types of receiver architectures are presented. The state-of-the-art of these architectures is reviewed.

Chapter 3 provides a background theory review of the variable gain amplifier and the circuit design details of variable gain amplifier and concluded with the post layout simulations.

Chapter 4 provides a background theory review of the up-conversion mixer operation. The fundamentals and parameters of performance are discussed and followed by the circuit design details of mixer .The chapter is concluded with simulation results.

Chapter 5 starts with a background theory review of the Power amplifier and their classifications followed by the circuit design description of the Class A power amplifier. Simulation results of class A power amplifier are provided to verify the performance analysis. This chapter concluded with the post layout simulation of Class A power amplifier

Chapter 6 starts with the design of the zigbee transmitter and concludes with the simulation results.

Conclusion and future work of this thesis are presented in Chapter 7.

# Chapter-2

# **Radio Transceiver Architectures**

## 2.1 Radio Transceiver Architectures

Primary criteria in selecting Transceiver Architectures [3]:

- ➢ Complexity

- > Cost

- > Power dissipation

- > No. of external components

The first consideration in designing an RFIC is the system architecture and its frequency plan. Architecture is determined by choosing among different possible ones:

- Superheterodyne using one or several IF stages

- Direct conversion

- ► Low IF

By frequency plan, it means the intermediate frequency/frequencies choice (Not Applicable for direct conversion architecture), with considerations on image interference avoidance, blockers, and RF leakage/isolation analysis, DC-offset issue, I/Q imbalance issue, etc. Frequency plan specification impacts on system noise, interference, and distortion analysis. In a generalized sense, special issues associated with chosen RF transceiver architecture are addressed in frequency plan specification.

For direct conversion, the following issues are important:

- DC offset or order-two products

- 1/f or flicker noise

- I/Q imbalance impacts

- etc.

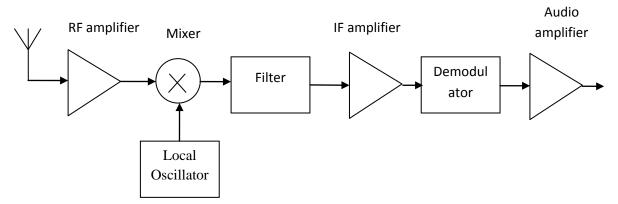

#### 2.1.1 Superheterodyne receiver

Superheterodyne receiver uses frequency mixing or heterodyning to convert a received signal to a fixed intermediate frequency, which can be more conveniently processed than the original radio carrier frequency.

Figure 2.1 Block Diagram of Superheterodyne Receiver

The principle of operation of the superheterodyne receiver depends on the use of frequency mixing or heterodyning. The signal from the antenna is filtered sufficiently at least to reject the image frequency and possibly amplified. A local oscillator in the receiver produces a sine wave which mixes with that signal, shifting it to a specific intermediate frequency(IF), usually a lower frequency. The IF signal is itself filtered and amplified and possibly processed in additional ways. The demodulator uses the IF signal rather than the original radio frequency to recreate a copy of the original modulation (such as audio).

The Figure 2.1 shows the minimum requirements for a single-conversion superheterodyne receiver design. The following elements are common to all superheterodyne circuits: a receiving antenna, a tuned stage which may optionally contain amplification (RF amplifier), a variable frequency local oscillator, a frequency mixer, a band pass filter and intermediate frequency (IF) amplifier, and a demodulator plus additional circuitry to amplify or process the original audio signal.

The advantages of heterodyne scheme are

- Good overall performance.

- Flexibility in frequency planning.

- No DC offset problem.

- Inphase and quadrature matching is superior.

The disadvantages of superheterodyne receiver are

- Requires external components.

- It suffers from image problems.

- Higher power consumption.

- High implementation results.

- Difficulties in multimode transceivers.

Due to high power consumption and high implementation costs, this superheterodyne is not suitable for IEEE 802.15.4.

### 2.1.2 Low IF receiver

In a low-IF receiver, the RF signal is mixed down to a non-zero low or moderate intermediate frequency, typically a few megahertz.

It combines the advantages of both heterodyne and direct conversion scheme.

The advantages of this receiver are

- Avoids DC offset problem.

- Eliminate IF SAW filter, PLL and image filtering.

The disadvantage of this scheme is that it suffers impairments such as even order nonlinearities, local oscillator pulling and local oscillator leakage.

Mainly, the low IF scheme requires stringent image rejection as an adjacent channel becomes its image. Image rejection in low IF can be achieved either in analog or digital domain. In analog domain, we can reduce this image frequency by using complex band pass filters. By the use of this band pass filters chip size and power consumption will increases. Also it requires a second low frequency digital mixer. In digital domain, the chip size will not increase. The disadvantage in digital domain solution is it requires good inphase and quadrature phase matching. Also signal bandwidth in low IF is two times that of direct conversion, so ADC sampling rate will be doubled and hence power consumption will be higher. Another disadvantage is design complexity also increases.

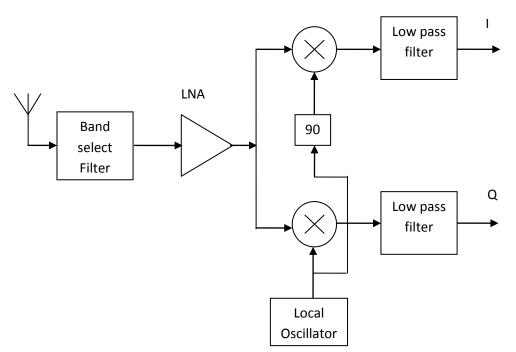

#### 2.1.3 Direct Conversion receiver

The direct conversion receiver converts the carrier of the desired channel to the zero frequency immediately in the first mixers. Hence the direct conversion is often called also as

a zero IF receiver, or a homodyne receiver if the LO is coherently synchronised with the incoming carrier. The synchronization of the LO directly to the RF carrier can be avoided with other techniques in current applications used mostly in optical reception.

Homodyne receivers translates the channel of interest directly from RF to baseband ( $\omega_{IF}=0$ ) in a single stage. Hence these architectures are called Direct IF architectures or Zero-IF architectures. For frequency and phase modulated signals, down conversion must provide quadrature outputs so as to avoid loss of information. It translates the RF signal directly to the baseband signal.

The block diagram of direct conversion receiver is shown in the Figure 2.2 below. Two direct conversion mixers must be used for demodulation already at RF if a signal with Quadrature modulation is received. Otherwise, a single sideband signal with suppressed carrier containing quadrature information, like QPSK, would alias its own independent single sideband channels in quadrature over each other. Hence, the RF mixers are already a part of the demodulator although several other processing steps are performed before the detection of bits. This is also a distinct benefit of the direct conversion scheme. Because the information at the both sides of the carrier comes from the same source having an equal power. Hence the image power is always the same with the desired signal and the quadrature accuracy requirements are only moderate. Thus the required image rejection is realizable with IC technologies even at high frequencies.

A low pass filter with a bandwidth of half the symbol rate is suitable for the channel selection. This gives a noise advantages over other architectures and also image noise filtering is needed between the LNA and mixers. The external components in the signal path are now limited to the pre-selection filter at the input. Hence only the input of LNA must be matched in order to maintain the filter response unchanged. The interfaces between other blocks can be optimized during the design independently to optimize the performance with respect to noise, linearity and power. Of course, flexibility also increases the design complexity.

Figure 2. 2 Block Diagram of Direct Conversion Receiver

The advantages of this scheme are

- Low cost.

- No image problem.

- No image filters.

The disadvantages of this scheme are

- DC offset.

- I/Q mismatch.

- Even order nonlinearity.

- Flicker noise or noise. This noise is very high in CMOS implementation.

- Local oscillator frequency planning while LO pulling and leakage.

In this receiver, DC offset and flicker noise are more dominant. Dc offset can be cancelled easily without impairing the signal information using capacitive coupling method or dc offset cancellation technique.

Usually, flicker noise arises from random trapping charge at the oxide silicon interface. For CMOS technology, corner frequency is high (around 1MHz). The remedy for this flicker

noise problem is by using passive mixers or by using vertical NPN transistors in CMOS technology for the switching core of active mixers.

On comparing the three transceiver architectures, we were selected the direct conversion scheme because of low power consumption, low cost and high integrable chip.

### 2.2 Transmitter Architectures

The choice of transmitter architecture is determined by two important factors: wanted and unwanted emission requirement and the number of oscillators and external filters. In general, the architecture and frequency planning of the transmitter must be selected in conjunction with those of the receiver so as to allow sharing hardware and possibility power [4].

#### 2.2.1 Direct Conversion Architecture

In direct conversion transmitters, the output carrier frequency is equal to the LO frequency, and modulation and up conversion occur in the same circuit as shown in Figure. The simplicity of the topology makes it attractive for high level of integration.

Figure 2. 3 Block Diagram of Direct Conversion Transmitter

The direct conversion architecture nonetheless suffers from an important drawback: disturbance of the local oscillator by the power amplifier output. Illustrated in Figure 2.4, this

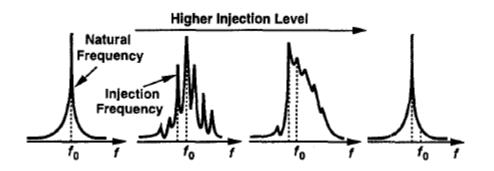

Figure 2. 4 LO pulling by PA

issue arises because the PA output is a modulated waveform having a high power and a spectrum centered around the LO frequency. Despite various shielding techniques employed to isolate the VCO, the noisy output of the PA still corrupts the oscillator spectrum. This corruption occurs through "injection pulling " or "injection locking", whereby the frequency of an oscillator tends to shift towards the frequency of the injected noise is close to the oscillator natural frequency, then the LO output is disturbed increasingly as the noise magnitude rises, eventually "locking" to noise frequency. In practice, noise levels as low as 40dB below the oscillation level may create tremendous disturbance.

Figure 2. 5 Injection pulling as the magnitude of the injected noise increases

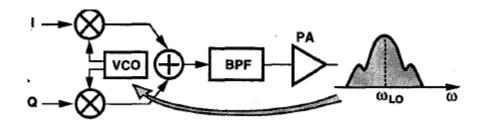

The phenomenon of LO pulling is alleviated if the PA output spectrum is sufficiently far from the oscillator frequency. For Quadrature up conversion, this can be accomplished by "offsetting" the LO frequency, that is by adding or subtracting the output frequency of another oscillator. Figure 2.6 shows an example where the output signals of VCO<sub>1</sub> and VCO<sub>2</sub> are

Figure 2.6 Direct conversion transmitter with offset LO

mixed and the result is filtered such that the carrier frequency is equal to  $\omega_1 + \omega_2$ , far from either  $\omega_1$  or  $\omega_2$ .

The selectivity of the first band pass filter.BPF<sub>1</sub>, in Figure 2.6 impacts the quality of the transmitted signal. Owing to nonlinearities in the offset mixer, many spurs of the form  $mw_1+nw_2$  appear at the input of BPF<sub>1</sub>. IF not adequately suppressed by the filter, such components degrade the quadrature generation of the carrier phases as well as create spurs in the up converted signal.

#### 2.2.2 Two Step Architecture

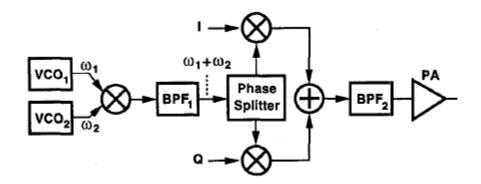

Another approach to circumventing the problem of LO pulling in transmitters is to up convert the base band of signal in two (or more) steps so that the PA output spectrum is far from the frequency of the VCOs. As an example, consider the circuit shown in Figure 2.7.Here, the

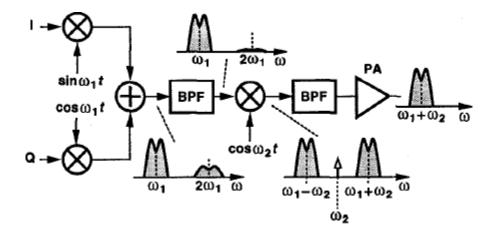

Figure 2.7 Two-step transmitter

baseband I and Q channels undergo quadrature modulation at a lower frequency,  $w_1$ [called the intermediate frequency (IF)], and the result is up converted to  $w_1+w_2$  by mixing and band pass filtering. The first BPF suppresses the harmonics of the IF signal while the second remove the unwanted sideband centered around  $\omega_1-\omega_2$ .

An advantage of two-step up conversion over the direct approach is that since quadrature modulation is performed at lower frequencies, I and Q matching is superior, leading to less cross talk between the two bit streams. Also, a channel filter may be used at the first IF to limit the transmitted noise and spurs in adjacent channels.

The difficulty in two-step transmitters is that the band pass filter following the second up conversion must reject the unwanted sideband by a large factor, typically 50 to 60dB. This is because the simple up conversion missing sidebands with equal magnitudes. Owing to the higher centre frequency, this filter is typically a passive, relatively expensive off-chip device.

## 2.3 Design of Zigbee Transmitter

### CMOS RF Front-end for IEEE 802.15.4

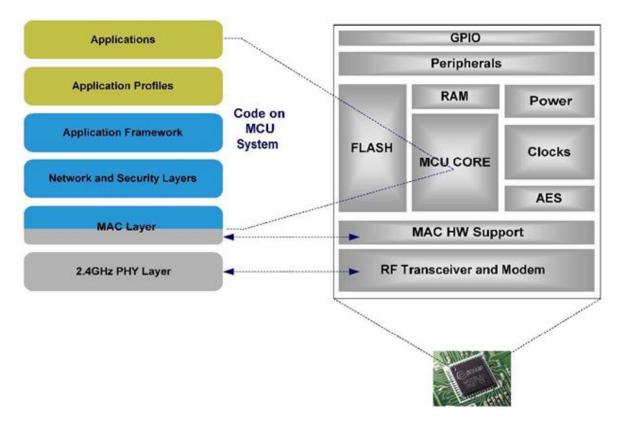

The Architecture of the Zigbee Frontend is shown in Figure 2.8, block diagram is shown in Figure 2.9.

**RF Front-end for IEEE 802.15.4**

#### Architecture:

Figure 2.8 RF Front end for IEEE 802.15.4

IEEE 802.15.4 assigns three frequency bands of operation: the 868-MHz, 915-MHz, and 2.4-GHz unlicensed industrial, scientific, and medical (ISM) bands. Among the three, the 2.4-GHz band is highly attractive, since this unlicensed band is commonly available throughout the world. Typical applications of this low data rate standard include those for industrial and commercial uses, home automation, PC peripherals, consumer electronics, and personal health care appliances, as well as for toys and games that should be able to run for six months to two years on just button cells or batteries[3].

#### 2.3.1 Specifications for the IEEE 802.15.4 RF Frontend

| S.No | Parameter                                           | Specification |  |  |  |  |

|------|-----------------------------------------------------|---------------|--|--|--|--|

| 1.   | Operating frequency                                 | 2.45GHz       |  |  |  |  |

| 2.   | Supply Voltage 1.8V                                 |               |  |  |  |  |

| 3.   | 3. Spread spectrum Direct Sequence Spre<br>Spectrum |               |  |  |  |  |

| 4.   | Modulation                                          | OQPSK         |  |  |  |  |

| 5.   | Number of channels                                  | 16            |  |  |  |  |

| 6.   | Data rate                                           | 250 kbps      |  |  |  |  |

| 7.   | Channel spacing 5 MHz                               |               |  |  |  |  |

Table 2. 1 Specification of Zigbee technology

In this Thesis Zigbee Transmitter is designed in 0.18um CMOS technology operated at 1.8v supply voltage. Here Zigbee Transmitter employs Direct Sequence Spread spectrum and used OQPSK as a modulation scheme. An IEEE 802.15.4-based 2.4-GHz PHY can support 250 kb/s data rate. Sixteen channels are available for 2.4-GHz band applications, with channel spacing of 5 MHz.

Figure 2. 9 Zigbee transmitter architecture

As shown in Figure 2.9 Zigbee Transmitter comprises of Low Pass Filter, Variable Gain Amplifier, up conversion Mixer, Power Amplifier. The Low Pass Filter allows low frequency range signal and attenuates all other high frequency signals.

The Variable Gain Amplifier stabilizes the amplitude of the LPF output signal and provides a constant amplitude signal to the following blocks. The circuit design details are discussed in following Chapter 3.

The Mixer translates signals from one frequency band to another. The output of the mixer consists of multiple images of the mixers input signal where each image is shifted up or down by multiples of the local oscillator (LO) frequency. The circuit design details are discussed in following Chapter 4.

The Power Amplifier converts a low-power radio-frequency signal into a larger signal of significant power, typically for driving the antenna of a transmitter. In this thesis Class A Power Amplifier which comes under Linear amplifier is designed. The circuit design details are discussed in following Chapter 5.

# **Chapter-3**

# **Design of a Variable Gain Amplifier**

### 3.1 Introduction

**V**ARIABLE gain amplifiers (VGAs) can be found in many applications and are used to maximize the dynamic range of overall systems in medical equipments, telecommunication systems, hearing aids, disk drives, and others[5]-[9]. In disk drives and CCD imaging equipments, the VGAs play the important role of stabilizing the amplitude of the output signal under various conditions and supply a constant-amplitude signal to the detector and filter sections of the read channel. The VGA for these applications requires a gain variation range of more than 30dB. In communication systems, the VGA is normally employed in a feedback loop to implement an automatic gain control (AGC) amplifier.

The AGC amplifier is a circuit that automatically controls its gain in response to the amplitude of the input signal, leading to a constant-amplitude output. The gain as an exponential function of control voltage, which is not an easily obtainable characteristic in CMOS technology, is desirable for minimizing the settling time of the AGC loops. Moreover, code-division multiple-access (CDMA) systems require VGAs with high linearity and wide range of gain variation.

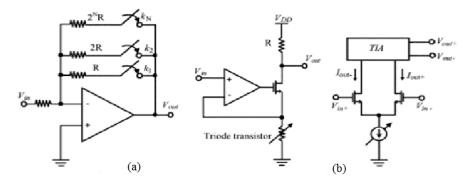

As an all-CMOS implementation, there are two approaches used to realize VGAs depending on whether the control signal is digital or analog. The digitally controlled VGAs use a series of switchable resistors or switched-capacitor techniques to control gain as shown in Figure. 3.1(a). In digitally controlled VGAs, gain varies as a discrete function of the control signal, which can lead to discontinuous signal phases that can cause problems in many systems.

Figure 3.1 (a) Digital Controlled VGA, (b) Analog Controlled VGA

In order to reduce the amount of jumps, a large number of control bits are required with digitally controlled VGAs. Therefore, for applications that require smooth gain transitions, the VGAs controlled by analog signal are preferred. The VGAs controlled by analog signals typically adopt variable transconductance or resistance stages for gain variation as shown in Figure. 3.1(b). With these topologies, the gains can be controlled continuously, but obtaining a wide exponential gain variation as a function of control voltage is a big issue, especially in CMOS technology.

In cellular wireless communication systems, the amplitude of the receiver and transmitter signals varies greatly. For this reason, for example, in a CDMA system, the transceiver requires at least 80 dB of dynamic gain variation and splits into RF and IF/baseband stages. In a typical receiver, most of the gain variation is assigned to the baseband stage. Therefore, to cover such a wide dynamic range, conventional CMOS-based VGAs require at least 4 or 5 gain-varying stages. The multiple gain-varying stages lead to a higher amount of power dissipation, larger chip area, and higher cost.

### **3.2 Decibel Linear Function**

The pseudo-exponential and Taylor series approximation functions used for VGA designs are given, respectively [7],

= --

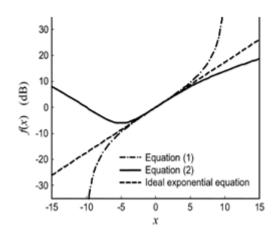

by where is *a* constant and an independent variable. The plots of (1), (2), and the ideal exponential function in decibel scale as a function of are shown in Figure. 3.2, Equations (1) and (2) approximate the exponential function when. Otherwise, (1) and (2) deviate significantly from the ideal exponential function. As can be seen in Figure. 3.2, (1) and (2) provide less than 15- and 12-dB linear range with a linearity error of less than 0.5 dB.

Figure 3. 2 Decibel scale plots of (1), (2) and the ideal exponential function

Compared to (1) and (2), the new approximated exponential function, is

### (3)

Where is a *k* constant. The numerator and denominator of (3) are squaring functions of the variable *x*. For *k* less than unity, the decibel linear range of (3) extends drastically and reaches its maximum value at around k = 0.12. As can be seen in Figure. 3.3,the decibel linear range of (3) extends to more than 60 dB with a linearity error of less than 0.5 dB for (solid line), which is a significant improvement compared to (1) and (2).

Figure 3. 3 : Decibel scale plots of (3) for various values of k

### **3.3 Variable Gain Amplifier Design**

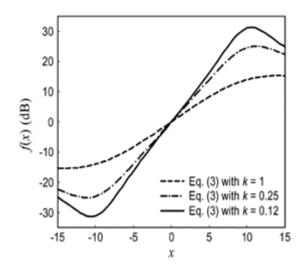

The Basic building blocks of Variable Gain Amplifier are (a).Control circuit,(b).Amplifier Block,(c).Buffer Block.

Figure 3. 4 Block Diagram of Two Stage Variable Gain Amplifier

#### 3.3.1 Control Circuit Block

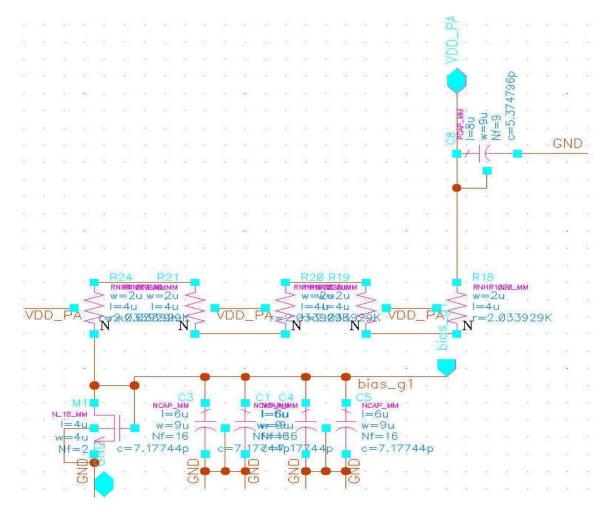

The control circuit block generates the numerator and denominator of (3), where all the transistors are assumed to be in saturation mode. In Figure. 3.5, the body terminals of pMOS and nMOS transistors are tied to supply voltages  $V_{DD}$  and  $V_{SS}$  respectively, and the lengths of transistors  $M_{18}$ , M24 and are chosen long enough that the channel length modulation can be neglected.

**Figure 3. 5 Schematic of Control Stage**

In Figure. 3.5, to guarantee the saturation-mode operation of transistors  $M_{18}$  and  $M_{24}$  the control voltage must stay within a range of  $(V_{SS}+V_{THn})\sim(V_{DD}-|V_{THp}|)$ , where  $V_{THn}$ ,

$V_{THp}$  are the threshold voltages of nMOS and pMOS transistors, respectively. The drain currents of transistors  $M_{18}$ ,  $M_{24}$  in Fig. 3.5 can be given as

where Kp Kn ,are constants  $[Kp=(W_1/2L_1)u_P C_{ox}and Kn=(W_2/2L_2)u_n C_{ox}]$ . In Figure. 3.5, since the current  $I_{C1}$  and  $I_{C2}$  are  $I_{D1}$ +I0 and  $I_{D2}$ +I0 respectively, the resulting currents  $I_{C1}$  and  $I_{C2}$  assuming Kp =Kn=K,  $V_{DD}$  =- $V_{SS}$  and  $|V_{THp}| = V_{THn} = V_{TH}$ , the ratios of  $I_{C1}$  and  $I_{C2}$  is given by

The VGA that adopts (6) shows a wide range of gain variation however, the required dynamic gain range for different applications is not equal; therefore, if the VGA provides a wider range of gain variation than the requirement, then the range of the control signal is reduced. Consequently, in order to maximize the range of control signal, the gain variation range of the VGA should be controllable.

#### 3.3.2 Amplifier Block

The circuit schematic of the amplifying block that is adopted for the VGA, including the common-mode feedback circuit. In Figure 3.6, the amplifier consists of an input Source-coupled pair (M4 and M5) and diode-connected loads (M6 and M7). The sizes of M4 and M6 are equal to M5 and M7 respectively. In Figure 3.6, the two currents and from the control block in Figure 3.5 are mirrored to M28 and M31. Therefore, the differential gain of the VGA shown in Figure 3.6 can be expressed as

$$A_V = ---- = ---- (7)$$

Where *gm-input* is the transconductance of the input transistors (M4 and M5) and *gm-load* the transconductance of the diode connected transistors (M6 and M7), respectively.

From (6) and (7), the differential gain as a function of the control voltage is given by

From Figure. 3.6, the amplifier gain can be varied by controlling the current through transistors and M28 and M31. Since the amplifier adopts current sources as active loads, the currents through transistors M8 and M9 must also vary accordingly. From (6), the sum of the currents through and is given as

$$I_{C1} + I_{C2} = 2K$$

(1 + \_\_\_\_\_) (9)

which is a second-order polynomial of the control voltage  $V_C$ . As a result, the drain currents through transistors M28 and M31 vary as a function of gain variation. Therefore, the strong common-mode feedback circuit shown in Figure. 3.6 is required in order to prevent any of the transistors from entering linear mode operation and to maintain a specific dc value for the biasing of the next stage.

#### 3.3.3 Buffer Block

Figure 3. 7 Schematic of Buffer Stage

The buffer is designed as a differential source follower, in which the gates of the input different transistors are differential inputs of the buffer with high impedance while the output impedance can be adjusted to  $50\Omega$  by a proper choice of the bias current and the size of input different transistors of the buffer. The buffer in Figure 3.7 is added for the convenience of measurements, providing high-input and  $50\Omega$  output impedances.

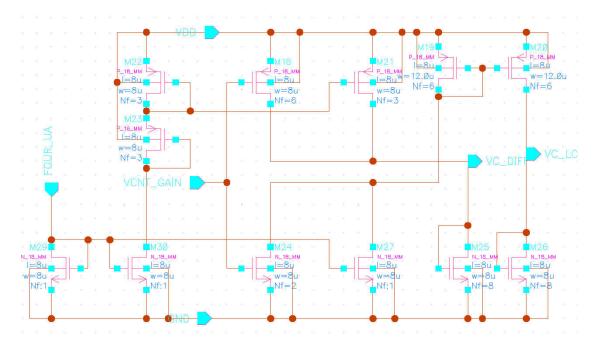

### 3.4 The Single Stage Overall VGA

Figure 3. 8 Schematic of Single Stage Overall VGA

Regarding the frequency response, assuming that the VGA is evaluated under a  $50\Omega$  environment, the bandwidth of the VGA is dominated by the pole at the input and the interstage node between two amplifiers. The input pole is a function of the input capacitance and resistance. Due to the Miller effect, the input capacitance is proportional to the amplifier gain; therefore, the bandwidth is reduced at higher gain settings. The output pole is proportional to the action the output capacitance and resistance. Since the resistance from the inter-stage node to the action of the action of the inter-stage node to the action.

ground is dominated by the diode-connected transistors M6 and M7 in Figure 3.6, which vary as a function of gain, the bandwidth of the amplifier varies accordingly. At higher gains, the current flowing through the diode-connected transistors is reduced leading to narrower bandwidths. Since the currents flow through M6 and M7 are squaring functions of the control voltage, the bandwidth of the VGA varies significantly from low- to high-gain modes.

### 3.5 **Results and Discussion**

| S. No | V <sub>control</sub> (mV) | VGA OP (dB) |

|-------|---------------------------|-------------|

| 1     | 200                       | 39.9        |

| 2     | 241.9                     | 39.55       |

| 3     | 283.87                    | 38.58       |

| 4     | 325.8                     | 37.96       |

| 5     | 367.7                     | 36.29       |

| 6     | 409.67                    | 33.99       |

| 7     | 451.6                     | 31.31       |

| 8     | 493.55                    | 28.5        |

| 9     | 535.5                     | 25.77       |

| 10    | 577.4                     | 23.13       |

| 11    | 619.5                     | 20.59       |

| 12    | 661.29                    | 18.15       |

| 13    | 703.22                    | 15.8        |

| 14    | 745.16                    | 11.24       |

| 15    | 787                       | 9           |

| 16    | 829                       | 6.74        |

| 17    | 870.96                    | 6.79        |

| 18    | 912.9                     | 4.54        |

| 19    | 954.8                     | 2.27        |

| 20    | 996.77                    | -71.8       |

| 21    | 1.0387                    | -2.46       |

| 22    | 1.0806                    | -4.9        |

#### Table 3. 1 Vcontrol versus VGA output (Gain dB)

| 23                                                                                                              | 1.1225 | -7.43   |

|-----------------------------------------------------------------------------------------------------------------|--------|---------|

| 24                                                                                                              | 1.1645 | -10.069 |

| 25                                                                                                              | 1.2    | -12.5   |

| 26                                                                                                              | 1.248  | -15.5   |

| 27                                                                                                              | 1.29   | -17.99  |

| 28                                                                                                              | 1.33   | -19.845 |

| 29                                                                                                              | 1.374  | -20.985 |

| 30                                                                                                              | 1.416  | -21.595 |

| 31                                                                                                              | 1.5    | -22     |

| the second se |        |         |

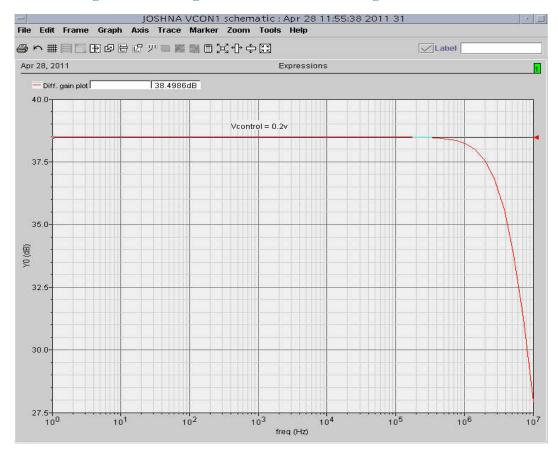

Figure 3. 9 Frequency versus Gain for Various Control voltages

The Proposed single stage Variable Gain Amplifier shows a maximum gain variation of 62dB (from 40 to -22), while dissipating an average current of 630u A from a 1.8v supply.

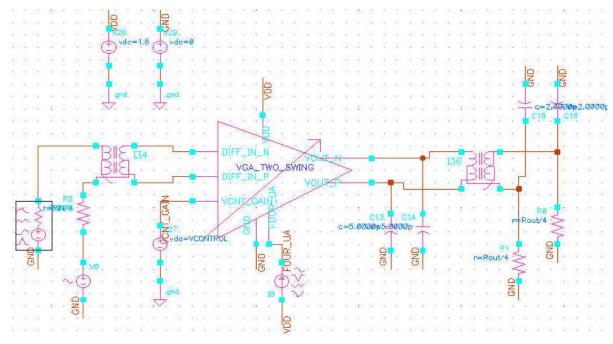

Figure 3. 10 Schematic of Proposed VGA Setup

The VGA setup as shown in the Figure 3.10 is simulated in Cadence<sup>©</sup> using SpectreRF simulator in UMC-0.18um Mixed Signal CMOS RF models. The VGA is designed to operate at 1.8v supply voltage. Chosen transient, dc, ac analysis for simulation and observed the gain variation of 62dB (from 40dB to -22dB).

| •                                                               | Status: Rea                                      | ady                                   |               |                 |             | T=          | 27 C Si                 | mulator: sp | ectre            | 11                    |

|-----------------------------------------------------------------|--------------------------------------------------|---------------------------------------|---------------|-----------------|-------------|-------------|-------------------------|-------------|------------------|-----------------------|

| Se                                                              | ssion Set                                        | up Analyses                           | Vari          | ables Outp      | uts Simu    | lation F    | Results                 | Tools       |                  | Help                  |

|                                                                 | De                                               | sign                                  |               |                 | .4          | Analyse     | es                      |             |                  | K                     |

| Library DIN_PA_FINAL<br>Cell TB_VGA_CONTROL_B<br>View schematic |                                                  |                                       | #             | Туре            |             | 1000        | the factor of the later |             | Enable           | JAC<br>■ TRAN<br>J DC |

|                                                                 |                                                  |                                       | 1 1<br>2<br>3 | xf<br>dc<br>ac  | 1<br>t<br>0 | 10M<br>200M |                         |             | yes<br>yes<br>no |                       |

|                                                                 | Design \                                         | /ariables                             |               | •               |             | Output      | s                       |             |                  |                       |

| #                                                               | Name                                             | Value                                 | #             | Name/Sig        | mal/Expr    | Va          | lue P                   | lot Save    | March            | 4                     |

| 1<br>2<br>3<br>4<br>5<br>6                                      | vindc<br>cacmag<br>zref<br>vdcoff<br>Rout<br>RIN | 900m<br>1m<br>50<br>0<br>500K<br>1.2K | 12            | IDC<br>Diff. ga | in plot     | -6<br>wa    | 30.1u<br>ve y           | es          |                  |                       |

| 7                                                               | pin                                              | -30                                   | -             |                 |             | Plotting    | mode:                   | Replace     |                  | +-                    |

Figure 3. 11 Analog Design Environment for VGA Setup

#### 3.5.1 Layout Issues

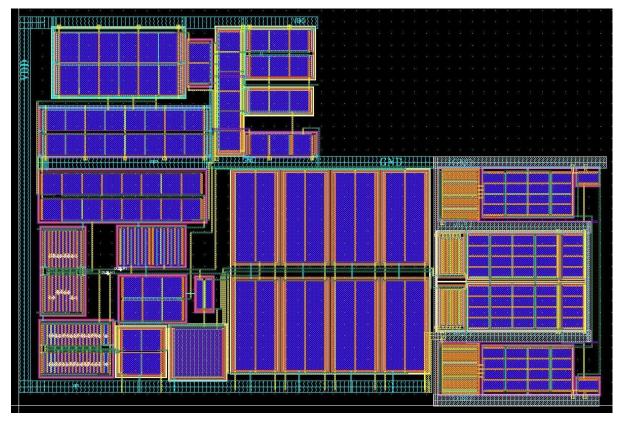

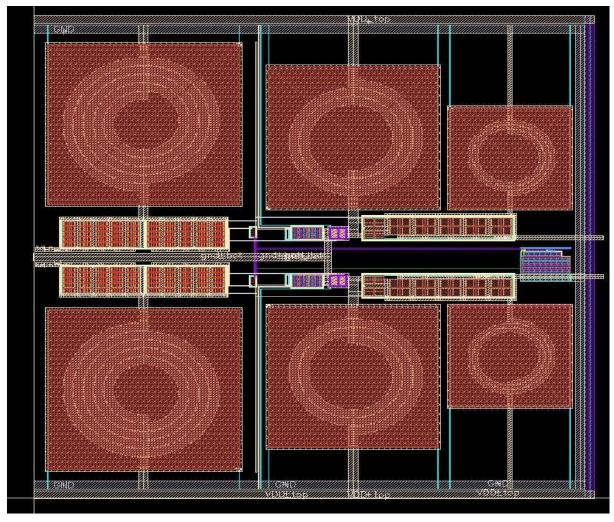

In Differential topology, to achieve better matching, transistors are arranged in a symmetric, common-centroid structure along with dummy transistors so that current flows symmetrically from left to right. The failure mechanisms for electrical overstress, such as electro-migration and antenna effect are also considered for the layout. To sustain the large currents in different parts of the PA circuit, wide tracks and stacked metal layers are used. The transistors which have larger width. This demands the use of multifinger and folded transistors connected in parallel to reduce the resistance and obtain better current distribution. Different blocks are encapsulated with guard-rings to avoid cross-talk and decouple substrate noise. The layout of the Variable Gain Amplifier is displayed in Figure. 3.12. The total chip area is (250  $\mu$ m x 167.3  $\mu$ m).

Figure 3. 12 Layout of Single stage variable gain amplifier

After creating Layout for VGA, we go for DRC to check all the process specific design rules have been met. Then we compare our layout with the schematic that we made earlier to see if they are both the same .Once the netlists matched we go for Post layout simulation. For performing Post layout simulation, an **analog\_extracted** view for the VGA is required. So we generate a config window as shown in the Figure 3.13 and do the post layout simulation same as like schematic simulation.

| ile Edit \     | liew     |                                                |                                     |                 | Plug-Ins He             |  |  |  |  |  |  |

|----------------|----------|------------------------------------------------|-------------------------------------|-----------------|-------------------------|--|--|--|--|--|--|

| D 🚔 🖪          |          | / କିଂ ରେଜ ଏକି <b>ଶି</b>                        | 1e m Th                             |                 |                         |  |  |  |  |  |  |

| fop Cell       |          |                                                | 10- 110                             |                 |                         |  |  |  |  |  |  |

| Library: UC    | SHNA     | Cell: TB_VG/                                   | A_CONTROL_BUFF_SV                   |                 | iew: schematic Open     |  |  |  |  |  |  |

| Global Bindir  | ngs      |                                                |                                     |                 |                         |  |  |  |  |  |  |

| Library List:  | myL      | 16                                             |                                     |                 |                         |  |  |  |  |  |  |

| LIDPARY LIST:  | huxr     | dL                                             |                                     |                 |                         |  |  |  |  |  |  |

| View List:     | spe      | ctre cmos_sch cmos.sch schematic veriloga ahdl |                                     |                 |                         |  |  |  |  |  |  |

| Stop List:     | spe      | ctre                                           |                                     |                 |                         |  |  |  |  |  |  |

| Cell Bindings  |          |                                                |                                     |                 |                         |  |  |  |  |  |  |

| Library        | ,        | Cell                                           | View Found                          | View to Use     | Inherited View List     |  |  |  |  |  |  |

| DIN PA FINA    |          | DIN VGA BUFF SWIN                              | av_extracted_RC                     | av_extracted_RC | spectre cmos_sch cmos   |  |  |  |  |  |  |

| DIN_PA_FINA    | 4L       | TB_VGA_CONTROL_BU                              | schematic                           |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| JMC_18_CM      | os       | N_18_MM                                        | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| UMC_18_CMOS P_ |          | P_18_MM                                        | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| JMC_18_CM      | os       | pcapacitor                                     | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| JMC_18_CM      | OS       | presistor                                      | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| analogLib      |          | cap                                            | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| analogLib      |          | ideal_balun                                    | schematic                           |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| analogLib      |          | isource                                        | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| analogLib      |          | port                                           | spectre                             |                 | spectre cmos_sch cmos   |  |  |  |  |  |  |

| nalarlih       |          |                                                | anastra                             |                 | anastro ama a cab ama a |  |  |  |  |  |  |

| Messages       | 00000000 |                                                |                                     |                 |                         |  |  |  |  |  |  |

|                | o Doci   | gn Systems program and on                      | line documentation are              |                 |                         |  |  |  |  |  |  |

|                |          | ntial information and may be                   |                                     |                 |                         |  |  |  |  |  |  |

|                |          | icense agreement controlling                   | 지수가 사람이 많은 것이 같아 같아 같아 가지 않는 것이 많다. | e               |                         |  |  |  |  |  |  |

|                |          |                                                |                                     |                 |                         |  |  |  |  |  |  |

| RESTRICTED     |          | HTS NOTICE (SHORT FORM                         | n                                   |                 |                         |  |  |  |  |  |  |

|                |          | isclosure is subject to restric                |                                     |                 |                         |  |  |  |  |  |  |

|                |          | 52.227-19 or its equivalent.                   |                                     |                 |                         |  |  |  |  |  |  |

|                |          | onfiguration (JOSHNA VCO                       | N1 config).                         |                 |                         |  |  |  |  |  |  |

|                |          | uration (JOSHNA VCON1 col                      |                                     |                 |                         |  |  |  |  |  |  |

# Figure 3. 13 Config Window of VGA for Analog Extracted View

Figure 3. 14 Post-Layout Simulations for VGA

The Post layout simulation for VGA as shown in the Figure 3.14 differs slightly from schematic simulation due to the influence of circuit parasitics such as parasitic capacitances and resistances.

# **Chapter-4**

# **Design of a Up-Conversion Mixer**

# 4.1 Introduction

In RF communication systems, mixers play a key role. In these systems, many functions are implemented with mixers, such as down conversion, up conversion, product detection, I/Q modulation, phase locked loops, etc. Mixers are key components in both receivers and transmitters. Mixers translate signals from one frequency band to another. The output of the mixer consists of multiple images of the mixers input signal where each image is shifted up or down by multiples of the local oscillator (LO) frequency. The most important mixer output signals are usually the signals translated up and down by one LO frequency.

In an ideal situation, the mixer output would be an exact replica of the input signal. In reality mixer output is distorted due to non-linearity in the mixer. In addition, the mixer components and a non-ideal LO signal introduce more noise to the output. Bad design might also cause leakage effects, complicating the design of the complete system. Linearity is important to transmitter performance, where you want an error-free output signal.

The Up Conversion mixers are one of the key building blocks in all those transmission systems[10]. A carefully designed and integrated mixer contain several good qualities: large conversion gain, good LO to RF isolation, small noise figure, and excellent linearity.

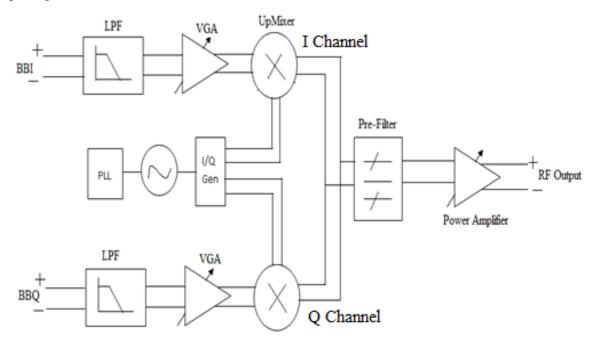

The mixer, as a nonlinear circuit by definition, is the most critical analog building block in the Zigbee Transceiver. One typical transmitter architecture applied in Zigbee system shown in Figure 4.1.

**Figure 4.1 Zigbee Transmitter Architecture**

#### 4.2 Mixer Topology

#### 4.2.1 Gilbert Cell

The linearity of an RF mixer is in most cases rather limited. The Gilbert topology is the most common used in a CMOS technology[11]. Its operation is based on a translinear configuration. Techniques like predistortion and emitter degeneration are necessary to obtain a reasonable linearity. In CMOS a double balanced structure which cancels out the quadratic term of the MOS transistor can be used. These mixers have not only a limited linearity which highly depends on matching, even more important Iss their limited frequency range. The input transistors of these mixers can only be biased with a relatively small VGS - VTH, in order to keep them in saturation at all times.

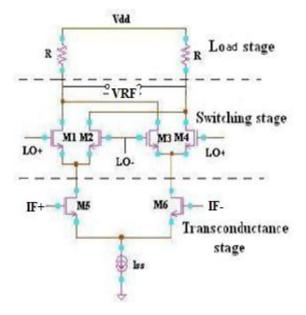

**Figure 4. 2 Schematic of Conventional Gilbert Mixer**

A schematic representation of the Gilbert mixer is shown in Figure.4.2. A Gilbert-cell mixer is able to achieve high RF-LO isolation, high dynamic range, and also cancel evenorder inter-modulation products two single-balanced circuits with the RF transistors connected in parallel and the switching pair in anti- parallel. The LO terms sum to zero and the IF signal doubled in the output. This configuration provides a high degree of LO-RF isolation, which alleviates filter requirements at the output.

Double Balanced mixers are less susceptible to noise than the single-balanced mixers because of the differential IF signal[14]. The input voltage in the IF frequency is amplified by the transconductance stage at the bottom of the circuit. The current is then steered to one side of the output or the other depending on the value of the LO. The result is a mixing of the LO and IF frequencies. The load stage used to convert mixed signal current into output RF

voltage, these resistors will influence the overall gain of the system and will be limited by remaining headroom voltage[15].

It is often that two factors affect linearity in the mixer circuit. First, if the applied signal at the driver stage is greater than the maximum differential input (also known as overdriving), the first compression will take place. Linearity can be improved in this situation by decreasing the driver stage transistor ratio (W/L), or increasing the bias current. The second, once the output load resistor size R is too large, the voltage drop VDS across the switching transistors will decrease, forcing the switching transistors out of saturation and into the triode region of operation (VDS  $\leq$  VGS – VTH).Reducing the size of the load resistors force the DC output voltage to a higher level, which make the gain lower.

However, three stacked transistors imply quite high supply voltage in the order of above 1.8 V and a strong LO voltage. This is a serious drawback of this architecture with respect to power consumption. But a reduction of the supply voltage leads to worse conversion gain and linearity performance.

Besides, the Gilbert mixer is based on the square-law characteristic of the MOS transistor in saturation. This characteristic restricts the linear range of the multiplier to small input voltage. The Gilbert cell has to be modified in order to cancel the quadratic terms originating from the basic MOS device for improving linearity and support low voltage operation[16]. Since in the conventional Gilbert Cell mixer, the IF input transistors operate in the saturation region and the LO transistors operate in the perfect switching situation.

Consequently, it appears that the mixer performance in terms of conversion gain and linearity can be simply improved by increasing the bias current of the driver stage. The IIP3 determines the maximum signal level that the mixer can handle a mixer with low NF and high IIP3 has larger dynamic range.

### 4.3 **Performance Parameters**

#### 4.3.1 Conversion Gain

The conversion gain of a mixer is defined as the ratio of the desired IF output to the RF input. If the ratio is less than 1, it is referred as a conversion loss. Conversion gain is expressed in terms of voltage or power and it is usually given in dB:

Power Gain

$$(dB) = 10 \log -$$

Voltage Gain (dB) =

$$20 \log -$$

If input is matched, the relationship between power gain and voltage gain is given by:

where Rs is the source resistance and RL is the load resistance.

The conversion gain of a mixer is important because it affects the noise figure and linearity of the overall s by the loss. Moreover, the conversion gain of the mixer also determines the signal level at the output of the mixer, in which the signal will be fed into the following stages. Therefore, the conversion gain will affect the linearity performance of the system.

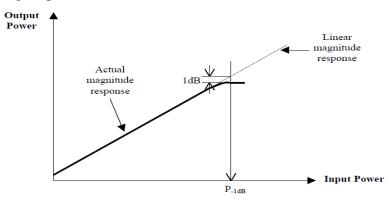

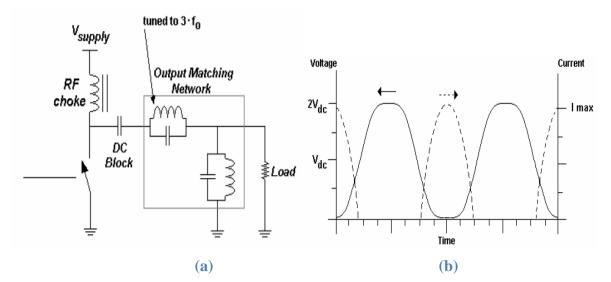

#### 4.3.2 Gain Compression

A strong signal can saturate a mixer and reduce its gain. The input 1 dB compression point (P-1dB) measures the input power level that causes the mixer to depart from its linear magnitude response by 1 dB. Figure 4.3 shows the magnitude response of a mixer as a function of input signal power

Figure 4. 3 Graphical representation of input 1dB Compression Point of Mixer

The dotted line shows the linear magnitude response of an ideal mixer. Due to odd-order nonlinearities and limiting such as voltage headroom limits the conversion gain of an actual mixer is compressed at high input power level. The actual output power is plotted with solid line. The point where the actual output power (solid line) is 1 dB lower than the ideal linear response (dotted line) is the input 1 dB compression point (P-1dB). If the gain compression is caused by limiting, the gain drops abruptly and the output power stays constant as the input power exceeds the input P-1dB. If the gain compression is caused by the odd-order nonlinearities, the gain decreases more gradually as the input power exceeds the input P-1dB.

At medium input power levels, gain compression is dominated by the third-order nonlinearity. If the input power continues to increase, higher-order non-linearities become significant.

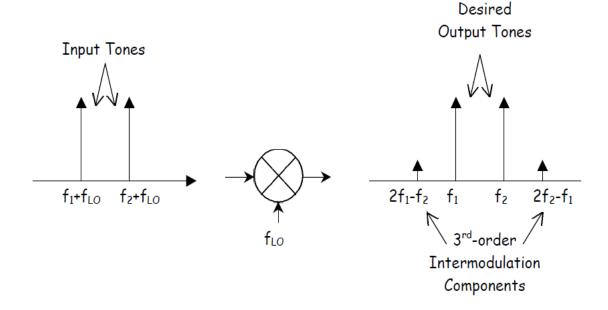

#### 4.3.3 Third order Intermodulation Distortion

The major function of a mixer is to perform frequency translation. Therefore it is inherently a non-linear circuit. However it is desirable for a mixer to behave very linearly with respect to all non-linearities except the one giving the desired frequency conversion. If we apply two tone input signal as follows

$v_i = V_1 \cos w_1 t + V_2 \cos w_2 t$

$$v_0 = c_0 + c_1 + c_2 + c_3 + \dots$$

4.1.1

4 1 1

Figure 4. 4 Frequency spectrum at input and output port of Mixer

Figure 4.4 shows the frequency spectra at the input and output of a mixer including the 3rdorder intermodulation (IM3) components. When two tones are inputted to a mixer, distortion components at many different frequencies will be generated at the output of the mixer. Most of these distortion components are outside the desired signal band and can be filtered out along the receiver chain. However, some of these distortion components fall within the signal band and they cannot be filtered. If the two input tones are close in frequency, the third-order intermodulation components (IM3) will be closed to or lie inside the signal band.

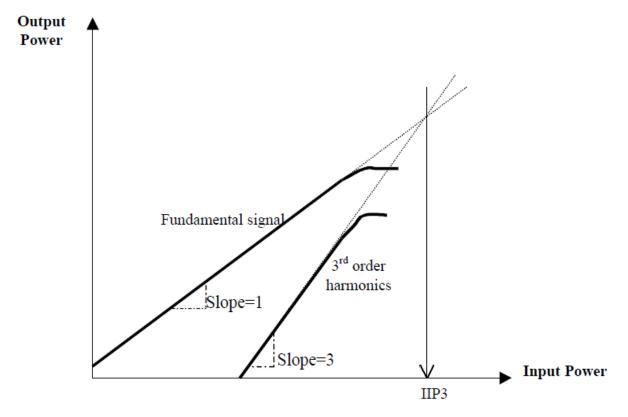

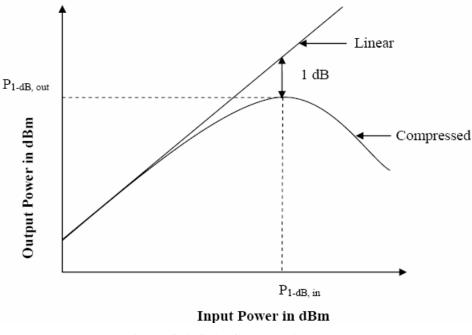

The input third-order intercept point (IIP3) is used to characterize the linearity performance of the mixer. IIP3 is defined as the input power level where the 3rd order distortion product's power is equal to the power of desired output. The desired output comes from the first order term in equation (4.11). For 1dB increase in the input power, it results in a 1dB increase in the output power. The 3rd order distortion comes from the 3<sup>rd</sup> order term in equation (4.1.1). For 1dB increase from the 3<sup>rd</sup> order term in equation (4.1.1). For 1dB increase from the 3<sup>rd</sup> order term in equation (4.1.1). For 1dB increase from the 3<sup>rd</sup> order term in equation (4.1.1). For 1dB increase in the input power, it results in 3 dB increase in the output distortion power. The graphical presentation of the input referred 3rd order intercept point is illustrated in Figure 4.5.

The curves in solid lines are the actual signal power observed at the frequency of interest and the dashed lines are the ideal behaviour of the first and the 3rd order terms of equation (4.1.1). When the input power is low, the curves of the actual signal power and ideal behaviour overlap. When the input power continues to increase, the curves of the actual signal power depart from their ideal behaviour lines, showing compressions from their ideal values. The compression is caused by the frequency components generated by the higher order terms in equation (4.1.1). These frequency components are the higher order distortion components. From Figure 4.5, IIP3 can be easily calculated

IIP3 = + -

where Pout1 and Pout3 are the measured output power of the desired signal and the 3rd order distortion respectively and Pin is the input power.

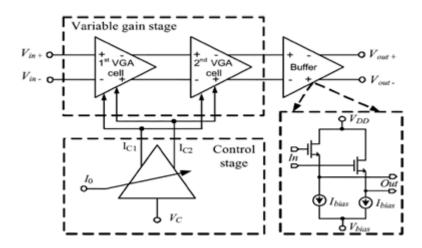

### 4.4 Proposed up conversion mixer for High Linearity

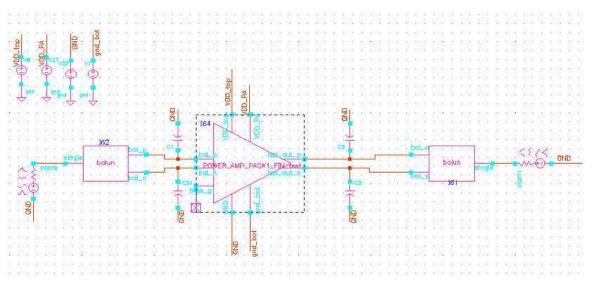

A Schematic of proposed up conversion mixer is shown in Figure 4.6. This Schematic consists of modified Gilbert type mixer with Pre-filter. There are three ports in this mixer setup. These three ports are for IF frequency, LO frequency and Output. The main purpose of the Pre-filter after the mixer is to suppress the Intermodulation Products before they are amplified by power Amplifier. The Pre-filter consists of passive LC circuit. The proposed Mixer is a High Performance Up Conversion Mixer for Zigbee Transmitter because of its good linearity performance[17].

#### Figure 4. 6 Schematic of proposed Up Conversion Mixer setup

The IF input signal is provided by an ideal balun driven by port element connected having a characteristic impedance of 1 $\Omega$  Ohm. The LO signal is provided by another port element and is directly coupled to the mixer inputs [18]. This mixer does not have an internal LO bias and therefore LO DC bias is provided by an external source as shown in the Figure 4.6. The output of the mixer is converted to the pre-filter as described above. The output of the filter is

connected to a port element having  $50\Omega$  Ohm characteristic impedance. The output is also converted to a single-ended output by a vcvs (Voltage-Controlled Voltage Source) element. The mixer is characterized at the block level. Therefore, it is important to include other circuit elements to represent parasitic associated with the top-level chip, package, and printed circuit board (PCB) substrate interconnect. If models for these interconnect elements are not available then estimated models can be implemented using lumped elements as is done here.

### 4.4.1 Circuit Operation

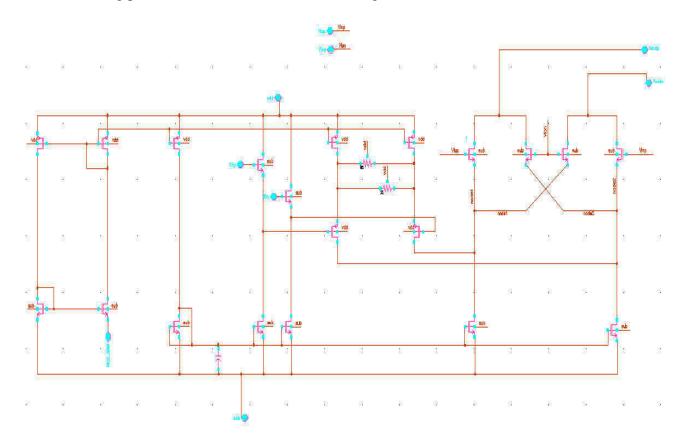

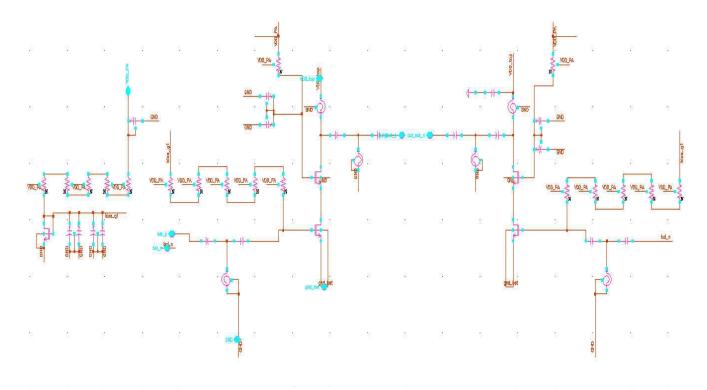

The baseband (IF) inputs first feed into a pair of level shifting devices followed by the transconducting pair of transistors PM0 and PM3 in Figure 4.7

#### Figure 4. 7 Schematic of Proposed Up Conversion Mixer

For correct linear operation, these devices should not be driven into saturation and therefore should be operated with signals well below their 1dB compression point. The current output signals are then folded into a Gilbert cell double balanced mixer core formed by transistors NM7-NM10 as shown in Figure 4.7. These transistors multiply the baseband currents with the LO signal to produce the RF signal which consists of 2 side-bands (FLO-FBB, FLO+FBB). The differential mixer outputs are left as open drains so that the currents from both the I and Q mixers can be summed in the subsequent Tx pre-filter stage. As a

consequence of the quadrature LO drive and the summation process the upper sideband RF products will add constructively while the lower sideband products are suppressed

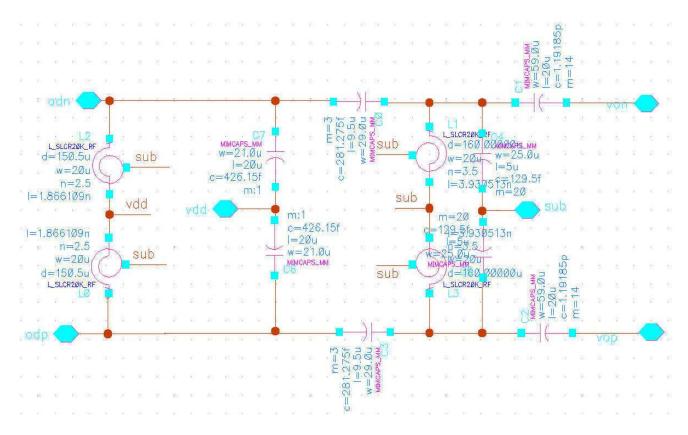

Figure 4. 8 Schematic of Pre-filter

The pre-filter shown in Figure 4.8 consists of a passive LC-circuit. In addition to being the output load for both mixers forming the I/Q modulator it helps to suppress the higher order modulation products before they are amplified by the power amplifier [19].

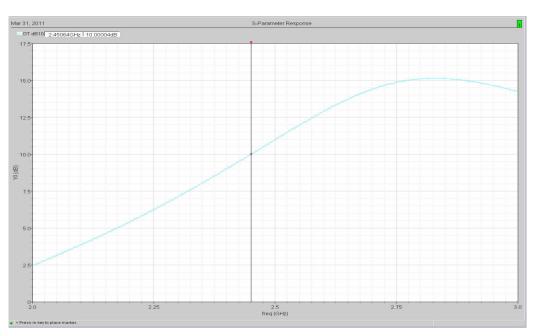

### 4.5 **Results and Discussion**

The mixer circuit is simulated in Cadence<sup>©</sup> using SpectreRF simulator in UMC-0.18um Mixed Signal CMOS RF models. The mixer is designed to operate at 1.8V voltage supply. Frequencies of three ports in the mixer are specified at IF Frequency of 5 MHz, LO frequency of 2.45 GHz and RF frequency of 2.45GHz respectively.

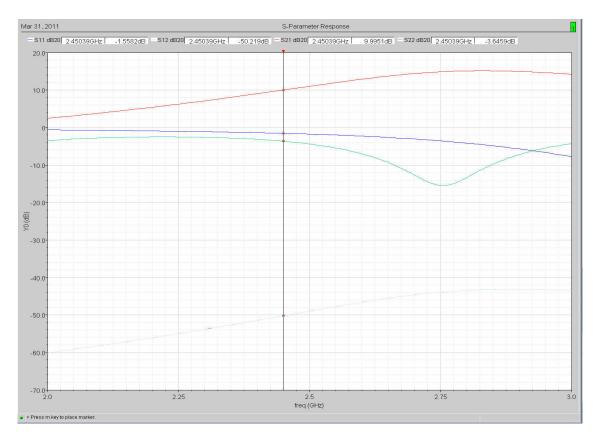

A mixer's frequency conversion is characterized by conversion gain. The *voltage conversion* gain is the ratio of the RMS voltages of the RF and IF signals. The conversion gain is measured to be -11.3dB.Choosen PAC and PSS analysis for simulating Conversion Gain and IIP3.

| S      | tatus: Re       | ady         |         |           |         |            | T=    | 27.0 C   | Simulator | : spectre  | 46      |

|--------|-----------------|-------------|---------|-----------|---------|------------|-------|----------|-----------|------------|---------|

| Sea    | ssion Set       | up Analyse: | s Varia | bles      | Outputs | Simul      | ation | Results  | Tools     |            | Help    |

|        | De              | sign        |         |           |         | 0.10       | Analy | ses      |           |            | -Ł      |

| jbr    | <b>ary</b> Nals | _JYO_MIX    | #       | Type      | ia<br>  | Argume     |       |          |           | Enable     | J AC    |

| Cell   | TX_M            | IXER_TEST   | 1       | pac       |         | 1          | 10K   | 3001     | 1         | yes        | - DC    |

| /iev   | v scher         | matic       | 2       | pss<br>dc |         | 2.450<br>t | 3     |          |           | yes<br>yes |         |

|        | Design 1        | Variables   |         |           |         |            | Outp  | uts      |           |            | E.      |