# INVESTIGATION OF POWER FACTOR CORRECTION IN SINGLE PHASE AC-DC CONVERTERS

A THESIS

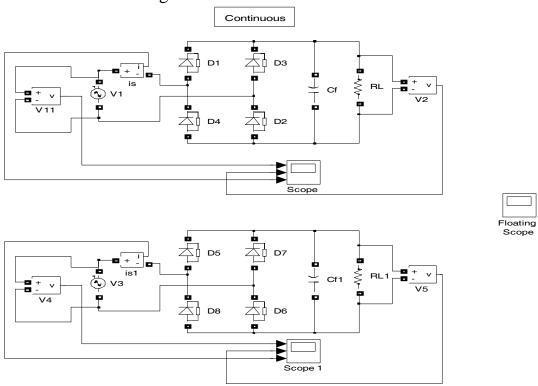

## SUBMITTED IN PARTIAL FULFILLMENT OF THE

**REQUIREMENTS FOR**

THE DEGREE OF

MASTER OF TECHNOLOGY (RESEARCH)

IN POWER ELECTRONICS

By

## Ms. NIRJHARINI SAHOO

Department of Electrical Engineering National institute of Technology Rourkela-769008 2009

# INVESTIGATION OF POWER FACTOR CORRECTION IN SINGLE PHASE AC-DC CONVERTERS

A THESIS

### SUBMITTED IN PARTIAL FULFILLMENT OF THE

## **REQUIREMENTS FOR**

## THE DEGREE OF

## MASTER OF TECHNOLOGY (RESEARCH)

IN POWER ELECTRONICS

By

## Ms. NIRJHARINI SAHOO Roll No-60702002

Under the Guidance of

Dr. A K PANDA

Department of Electrical Engineering National institute of Technology Rourkela-769008 2009

National Institute of Technology Rourkela

#### **CERTIFICATE**

This is to certify that the thesis entitled "**Investigation Of Power factor correction in single phase ac-dc converters**" submitted by **Ms. Nirjharini Sahoo**, in partial fulfillment of the requirements for the award of Master of Technology (Research) in the Department of Electrical Engineering, with specialization in '**Power Electronics**' at National Institute of Technology, Rourkela (Deemed University) is an authentic work carried out by her under my supervision and guidance.

To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University/Institute for the award of any Degree or Diploma.

# Prof. Anup Kumar Panda

Dept of Electrical Engineering NIT Rourkela-769008

## **BIO-DATA OF THE CANDIDATE**

| Name:              | Nirjharini Sahoo           |  |  |

|--------------------|----------------------------|--|--|

| Date of Birth:     | 4 <sup>th</sup> March 1980 |  |  |

| Permanent Address: | At-Ostia, P:O-Taras        |  |  |

|                    | Via-Rajkanika              |  |  |

|                    | Kendrapara                 |  |  |

|                    | 754220                     |  |  |

| Email:             | nirjharini80@gmail.com     |  |  |

## ACADEMIC QUALIFICATION

• Pursuing M.Tech (Research) in Electrical Engineering, National Institute of Technology, Rourkela.

• B. Tech in Electrical Engineering at College of Engineering and Technology (CET) Bhubaneswar

### PUBLICATIONS

- Published One Paper in International Conferences.

- Published Two Papers in National Conference.

#### ACKNOWLEDGEMENTS

On the submission of my thesis report of "Investigation of Power factor correction in single phase ac-dc converters", I would like to extend my gratitude & my sincere thanks to my supervisors **Dr. A K Panda**, Professor, Department of Electrical Engineering for their constant motivation and support during the course of my work in the last two years. I truly appreciate and value their esteemed guidance and encouragement from the beginning to the end of this thesis. I am indebted to them for having helped me shape the problem and providing insights towards the solution.

I express my gratitude to **Dr. S. Dash**, Asst. Professor, Department of Electrical Engineering for her invaluable suggestions and constant encouragement all through the thesis work.

I will be failing in my duty if I do not mention the laboratory staff and administrative staff of this department for their timely help.

I would like to thank all whose direct and indirect support helped me completing my thesis in time.

This thesis would have been impossible if not for the perpetual moral support from my family members, and my friends. I would like to thank them all.

Ms.Nirjharini Sahoo M.Tech (Research) (Power Electronics)

# CONTENTS

|           | List of abbreviations                                                       | v   |

|-----------|-----------------------------------------------------------------------------|-----|

|           | List of symbols                                                             | vi  |

|           | Abstract                                                                    | vii |

|           | List of Figures                                                             | ix  |

|           | List of Tables                                                              | xii |

| Chapter 1 | Introduction                                                                | 1   |

| 1.1       | Nonlinear loads and their effect on the electricity distribution network    | 1   |

| 1.2       | Standards regulating line current harmonics                                 | 3   |

| 1.2.1     | Standard IEC 1000-3-2                                                       | 5   |

| 1.2.1     | Standard IEEE 519-1992                                                      | 5   |

| 1.3       | Power Factor Correction                                                     | 6   |

| 1.3.1     | Benefits Of Power Factor                                                    | 8   |

| 1.4       | Applications of PFC                                                         | 8   |

| 1.4.1     | Electricity industry: power factor correction of linear loads               | 8   |

| 1.4.2     | Switched mode power supply: power factor correction of non-<br>linear loads | 9   |

| 1.5       | Research Background                                                         | 10  |

| 1.5.1     | Passive PFC                                                                 | 10  |

| 1.5.2     | Active PFC                                                                  | 10  |

| 1.5.3     | EMI Problem                                                                 | 11  |

| 1.5.4     | Switching Loss                                                              | 12  |

| 1.5.5     | Solution                                                                    | 13  |

| 1.5.6     | ZVT and ZCT                                                                 | 14  |

| 1.6       | Problem Formulation                                                         | 15  |

| 1.7       | Aim of the Dissertation                                             | 15 |

|-----------|---------------------------------------------------------------------|----|

| 1.8       | Thesis Organization                                                 | 16 |

| Chapter 2 | PASSIVE PFC                                                         | 17 |

| 2.1       | Diode bridge rectifier                                              | 18 |

| 2.1.1     | Rectifier with ac side inductor                                     | 19 |

| 2.1.2     | Rectifier with dc-side inductor                                     | 20 |

| 2.1.3     | Rectifier with series-resonant band-pass filter                     | 21 |

| 2.1.4     | Rectifier with parallel-resonant band-stop filter                   | 22 |

| 2.1.5     | Capacitor-fed rectifier                                             | 23 |

| 2.1.6     | Rectifier with an additional inductor, capacitor and diode (LCD)    | 24 |

| 2.1.7     | Valley-fill rectifier                                               | 25 |

| 2.2       | Advantages of passive PFC                                           | 26 |

| 2.3       | Disadvantages of passive PFC                                        | 26 |

|           | Summary                                                             | 27 |

| Chapter 3 | Active PFC                                                          | 28 |

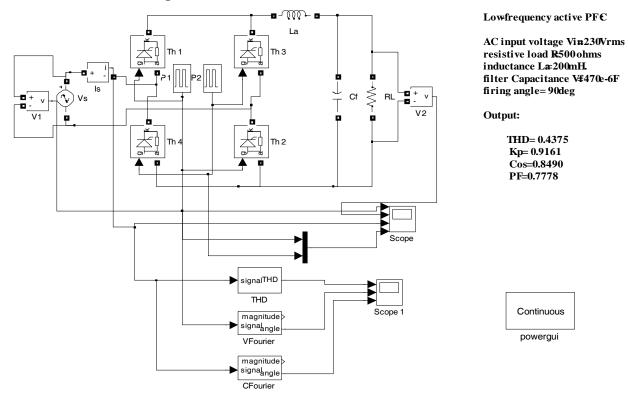

| 3.1       | Low-frequency active PFC                                            | 28 |

| 3.1.1     | Phase controlled rectifier with dc-side inductor                    | 29 |

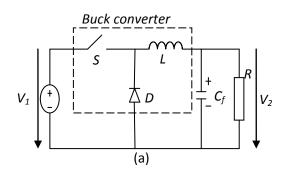

| 3.1.2     | Low frequency switching buck converter                              | 30 |

| 3.1.3     | Low-frequency switching boost converter                             | 31 |

| 3.2       | High-frequency active PFC                                           | 34 |

| 3.2.1     | Second-order switching converters applied to PFC                    | 34 |

| 3.2.1.1   | Buck converter                                                      | 35 |

| 3.2.1.2   | Boost converter                                                     | 37 |

|           | Summary                                                             | 39 |

| Chapter 4 | Operation In Discontinuous Inductor Current Mode – DICM             | 41 |

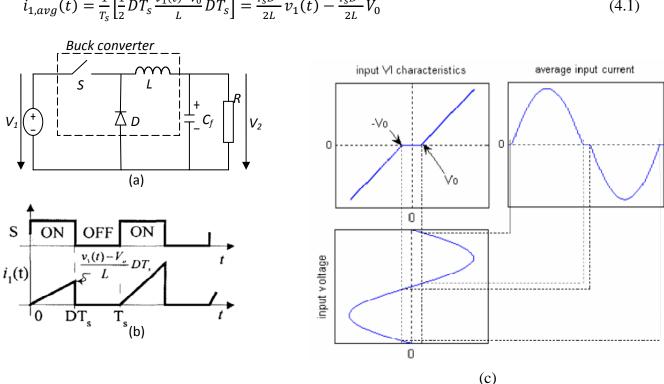

| 4.1       | Input voltage-current characteristics of basic converter topologies | 41 |

| 4.1.1     | Buck converter                                                      | 42 |

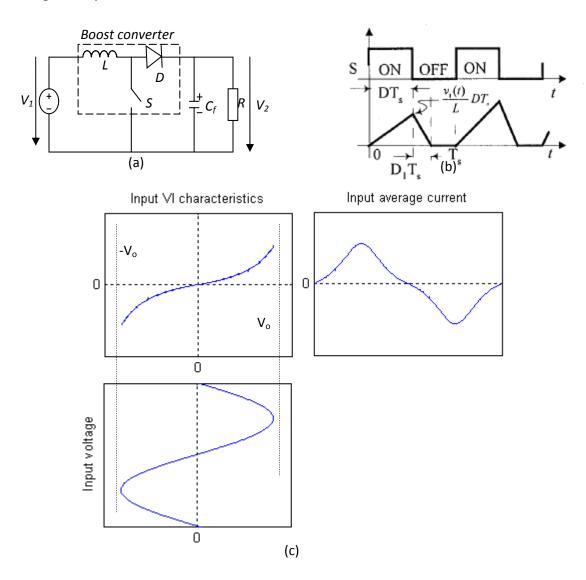

| 4.1.2     | Boost converter                                      | 43 |

|-----------|------------------------------------------------------|----|

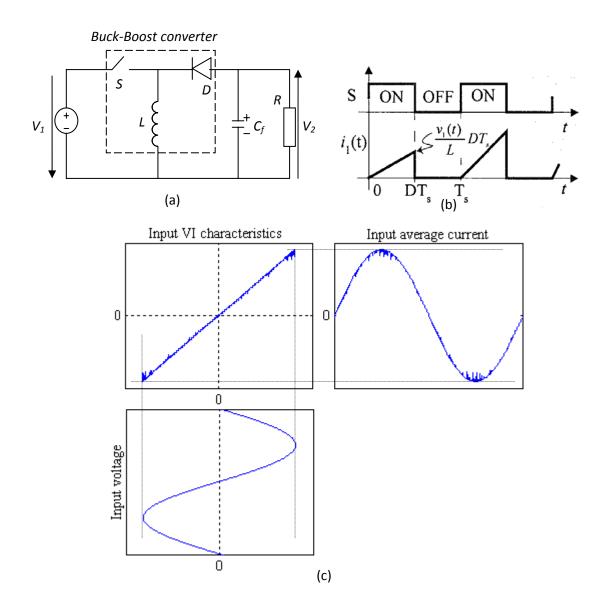

| 4.1.3     | Buck-boost converter                                 | 44 |

| 4.2       | Design procedure                                     | 46 |

| 4.2.1     | Summary: mode boundary                               | 46 |

|           | Summary                                              | 47 |

| Chapter 5 | Operation In Continuous Inductor Current Mode – CICM | 48 |

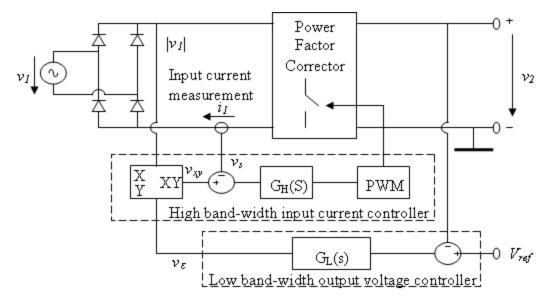

| 5.1       | Control scheme for CICM operation                    | 48 |

| 5.2       | Peak current control                                 | 50 |

| 5.2.1     | Advantages                                           | 51 |

| 5.2.2     | Disadvantages                                        | 52 |

| 5.3       | Average current mode control                         | 52 |

| 5.3.1     | Advantages                                           | 54 |

| 5.3.2     | Disadvantages                                        | 54 |

| 5.4       | Hysteresis control                                   | 54 |

| 5.4.1     | Advantages                                           | 55 |

| 5.4.2     | Disadvantages                                        | 55 |

| 5.5       | Borderline control                                   | 56 |

| 5.5.1     | Advantages                                           | 56 |

| 5.5.2     | Disadvantages                                        | 56 |

| 5.6       | Simulation results                                   | 58 |

| 5.6.1     | Peak current control                                 | 58 |

| 5.6.2     | Average current control                              | 59 |

| 5.6.3     | Hysteresis control                                   | 60 |

| 5.6.4     | Borderline control                                   | 61 |

|           | Summary                                              | 62 |

| Chapter 6 | Methods For Improving The Efficiency                 | 63 |

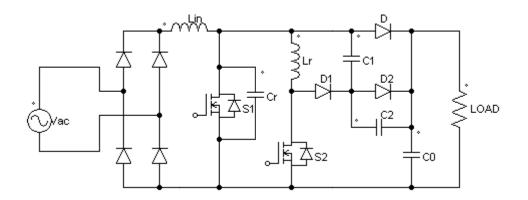

| 6.1       | An improved ZVT technique                            | 63 |

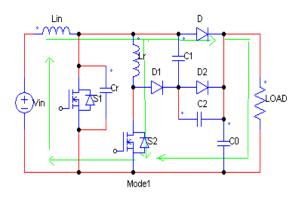

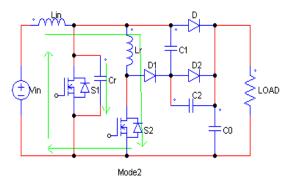

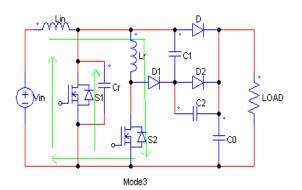

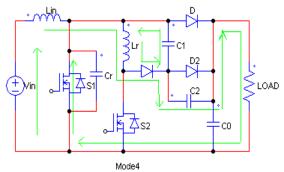

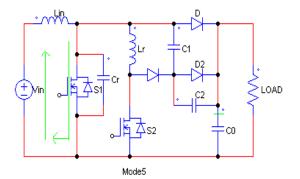

| 6.1.1     | Mode of operation                      |     |

|-----------|----------------------------------------|-----|

| 6.2       | Design Considerations                  | 70  |

| 6.2.1     | Switching Frequency $(f_s)$            | 70  |

| 6.2.2.2   | Minimum Duty Ratio (D <sub>min</sub> ) | 70  |

| 6.2.3     | Primary Input Inductor (L)             | 70  |

| 6.2.4     | Output Capacitor (C <sub>o</sub> )     | 70  |

| 6.2.5     | Delay Time $(T_D)$                     | 71  |

| 6.2.6     | Resonant Capacitor ( $C_r$ )           | 71  |

| 6.2.7     | Resonant Inductor $(L_r)$              | 71  |

| 6.2.8     | Additional Capacitor $(C_1, C_2)$      | 71  |

| 6.2.9     | Design of boost ZVT converter          | 72  |

| 6.3       | Selection of Devices                   | 73  |

| 6.3.1     | MOSFET Selection                       | 73  |

| 6.3.2     | Inductor and Capacitor Selection       | 74  |

| 6.3.3     | Diodes Selection                       | 74  |

| 6.4       | Simulation results                     | 74  |

| 6.5       | Experimental Verifications             | 79  |

|           | Summary                                | 82  |

| Chapter 7 | Conclusions                            | 83  |

| 7.1       | Conclusions                            | 83  |

| 7.2       | Future work                            | 85  |

|           | Appendix                               | 86  |

|           | References                             | 100 |

# ABBREVIATIONS

| AC     | -Alternating Current                               |  |

|--------|----------------------------------------------------|--|

| CICM   | - Continuous Inductor Current Mode                 |  |

| DC     | -Direct Current                                    |  |

| DICM   | - Discontinuous Inductor Current Mode              |  |

| EMI    | - Electromagnetic Interference                     |  |

| HPF    | -High Power Factor                                 |  |

| IEEE   | -Institute of Electrical and Electronics Engineers |  |

| IEC    | - International Electro-technical Committee        |  |

| IGBT   | -Insulated Gate Bipolar Transistor                 |  |

| MOSFET | -Metal Oxide Semiconductor Field Effect Transistor |  |

| PFC    | -Power Factor Correction                           |  |

| PWM    | - Pulse Width Modulation                           |  |

| RMS    | -Root Mean Square                                  |  |

| THDi   | -Total Harmonic Distortion of input line current   |  |

| ZVT    | - Zero Voltage Transition                          |  |

| ZVS    | - Zero Voltage Switching                           |  |

| ZCS    | - Zero Current Switching                           |  |

## LIST OF SYMBOLS

| С                 | -Capacitance                                     |

|-------------------|--------------------------------------------------|

| L                 | - Inductance Of The Ideal Inductor               |

| Р                 | -Active Power In A Sinusoidal System             |

| R                 | -Resistance Of The Ideal Resistor R              |

| S                 | -Active Switch                                   |

| S                 | - Apparent Power                                 |

| $T_{\rm off}$     | -Off-Time Of An Active Switch                    |

| T <sub>on</sub>   | -On-Time Of An Active Switch                     |

| T <sub>s</sub>    | -Switching Period                                |

| T <sub>D</sub>    | - Delay Time                                     |

| Thd <sub>i</sub>  | -Total Harmonic Distortion Of The Line Current   |

| V                 | -Phasor Representation Of A Sinusoidal Voltage   |

| V <sub>rms</sub>  | -RMS Value Of The Purely Sinusoidal Line Voltage |

| PF                | -Power Factor                                    |

| Ø                 | -Displacement Angle                              |

| K <sub>p</sub>    | - Purity Factor                                  |

| Ivref             | -Inductor Valley Current Reference               |

| I <sub>pref</sub> | -Inductor Peak Current Reference                 |

| $C_{\mathrm{f}}$  | - Filter Capacitance                             |

| L <sub>r</sub>    | Resonant Inductor                                |

| Cr                | - Resonant Capacitor                             |

| $I_{lr}$          | Resonant Inductor Current                        |

| V <sub>cr</sub>   | -Resonant Capacitor Voltage                      |

| $\mathbf{V}_0$    | Output Voltage                                   |

| L <sub>in</sub>   | Primary Input Inductor Current                   |

#### ABSTRACT

An ac to dc converter is an integral part of any power supply unit used in the all electronic equipments. These electronic equipments form a major part of load on the utility. Generally, to convert line frequency ac to dc, a line frequency diode bridge rectifier is used. To reduce the ripple in the dc output voltage, a large capacitor is used at the rectifier output. But due to this large capacitor, the current drawn by this converter is peaky in nature. This input current is rich in low order harmonics. Also, as power electronics equipments are increasingly being used in power conversion, they inject low order harmonics into the utility. Due to the presence of these harmonics, the total harmonic distortion is high and the input power factor is poor. Because of the problems associated with low power factor and harmonics, utilities will enforce harmonic standards and guidelines, which will limit the amount of current distortion allowed into the utility, and thus the simple diode rectifier may not be in use. So, there is a need to achieve rectification at close to unity power factor and low input current distortion. Initially, power factor correction schemes have been implemented mainly for heavy industrial loads like induction motors, induction heating furnaces etc., which forms a major part of lagging power factor load. Hence, PFC is becoming an important aspect even for low power application electronic equipments.

There are two types of PFC's. 1) Passive PFC, 2) Active PFC. The active PFC is further classified into low-frequency and high-frequency active PFC depending on the switching frequency. Different techniques in passive PFC and active PFC are presented here. Among these PFC's, we will get better power factor by using high-frequency active PFC circuit. Any DC-DC converters can be used for this purpose, if a suitable control method is used to shape its input current or if it has inherent PFC properties. The DC-DC converters can operate in Continuous Inductor Current Mode – CICM, where the inductor current never reaches zero during one switching cycle or Discontinuous Inductor Current Mode - DICM, where the inductor current is zero during intervals of the switching cycle.

In DICM, the input inductor is no longer a state variable since its state in a given switching cycle is independent on the value in the previous switching cycle. The peak of the inductor current is sampling the line voltage automatically. This property of DICM input circuit can be called "self power factor correction" because no control loop is required from its input side. In

CICM, different control techniques are used to control the inductor current. Some of them are (1) peak current control (2) average current control (3) Hysteresis control (4) borderline control. These control techniques specifically developed for PFC boost converters are analyzed. For each control strategy advantages and drawbacks are highlighted.

This high frequency switching PFC stage also has drawbacks, such as: it introduces additional losses, thus reducing the overall efficiency; it increases the EMI, due to the high frequency content of the input current. The efficiency will be improved by reducing the losses using soft switching techniques such as 'Zero Voltage Switching'- (ZVS), 'Zero Voltage Transition' (ZVT), and 'Zero Current Switching'- (ZCS).

We study circuit techniques to improve the efficiency of the PFC stage by lowering the conduction losses and/or the switching losses. Operation of a ZVT converter has been discussed, in which the switching losses are minimized by using an additional auxiliary circuit incorporated in the conventional PWM boost converter. The proposed converter achieves zero voltage or zero current turn-on and turn-off for the main switch and soft switching for the auxiliary switch. Thus, the switching losses are reduced and the higher efficiency of the system is achieved.

Finally, ZVT technique has been implemented in a single-phase active power factor correction circuit based on an ac-dc boost converter topology and operating in a continuous inductor current mode with peak current control method. A 500 W, 40 kHz ZVT PWM boost PFC converter has been simulated and simulation results are validated with experimental results.

### LIST OF FIGURES

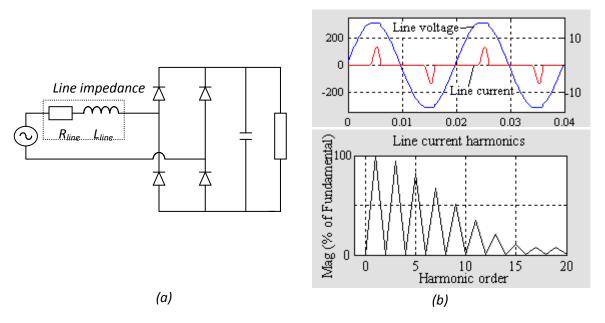

- Figure. 1.1. Single-phase diode bridge rectifier: (a) Schematic; (b) Typical line 3 Voltage and line current waveforms (upper plot) and odd line current harmonics (Lower plot).

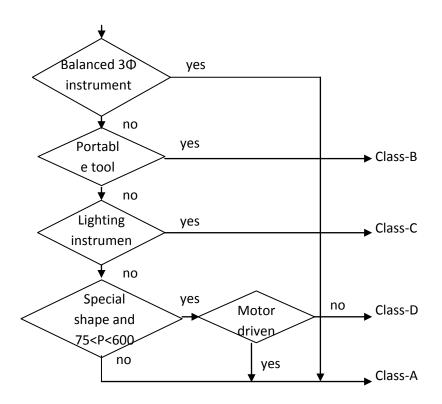

- Figure. 1.2. Classification of equipment under Standard IEC 1000-3-2 4

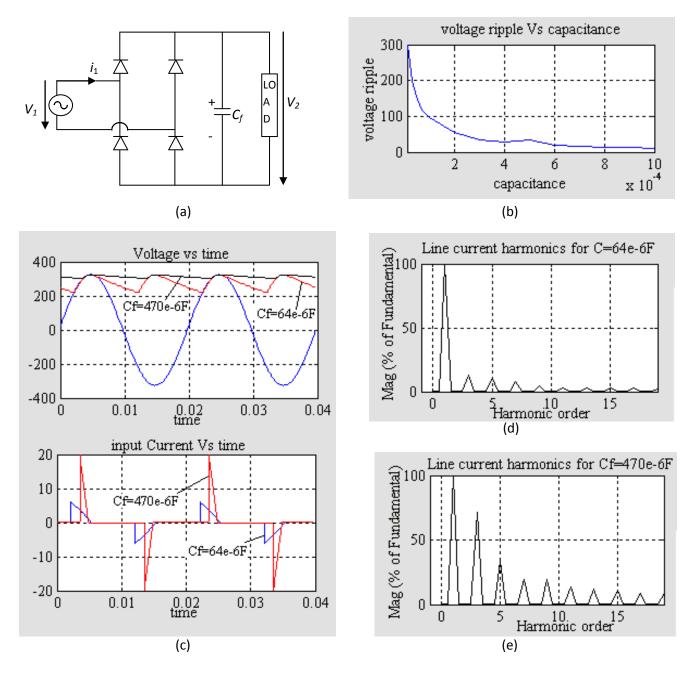

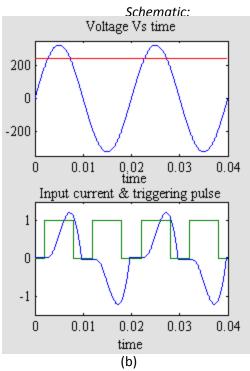

- Figure. 2.1 Diode bridge rectifier: (a) Schematic; (b) voltage ripple as a function of 17 the output filter capacitance; (c) Line voltage and output voltage (upper plot), and input current (lower plot); (d) and (e) Line current harmonics with C<sub>f</sub> and without C<sub>f</sub> respectively

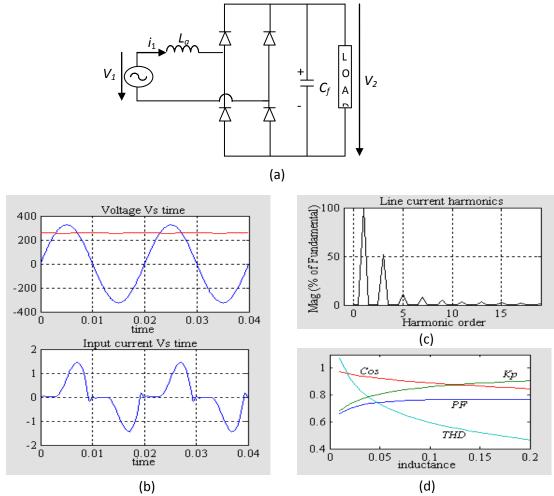

- Figure. 2.2 Rectifier with AC side inductor. (a) Schematic; (b)Line voltage, output 19 voltage (upper plot) and line current (lower plot); (c) Line current harmonics; (d) Variation of different parameters as a function of inductance

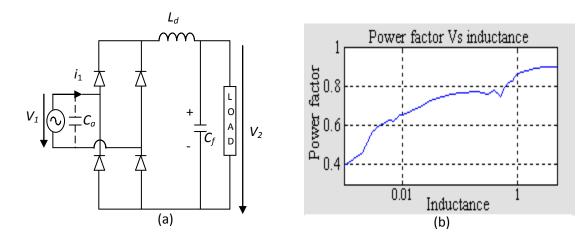

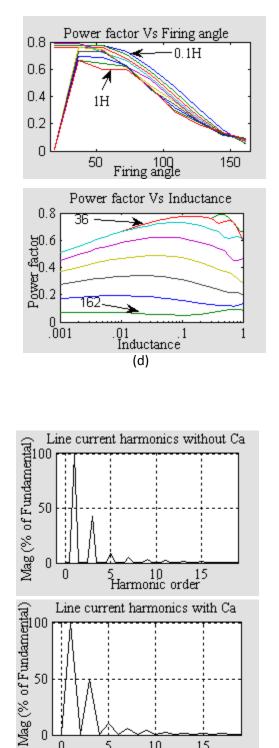

- Figure. 2.3 Rectifier with DC-side inductor. (a) Schematic; (b) Power factor Vs 21 inductance without Ca; (c)Line voltage, output voltage (upper plot) and line current(lower plot); (d) and (e) Line current harmonics without and with Ca.

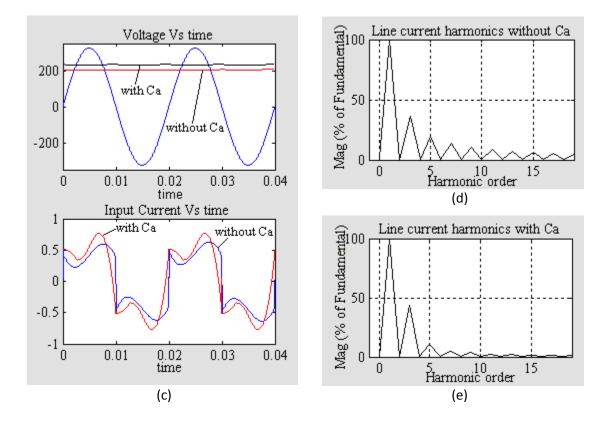

- Figure. 2.4 Rectifier with series-resonant band-pass filter. (a) Schematic; (b) Line 22 current harmonics; (c) Line voltage, output voltage (upper plot) and line current (lower plot).

- Figure. 2.5 Rectifier with parallel-resonant band-stop filter. (a) Schematic; (b) Line 23 current harmonics; (c) Line voltage and output voltage (upper plot) and line current (lower plot).

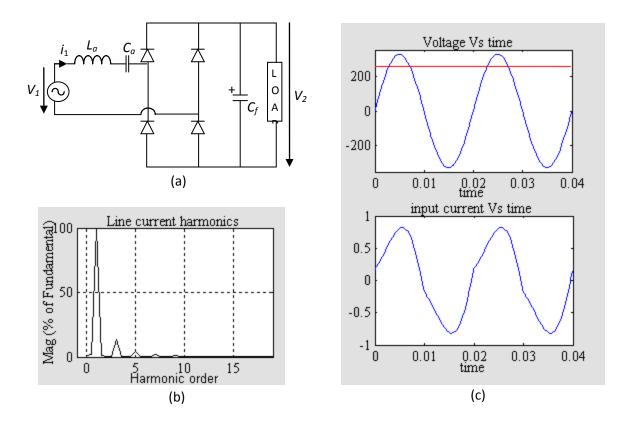

- Figure. 2.6 Capacitor-fed rectifier. (a) Schematic; (b) Line current harmonics; (c) Line 24 voltage, output voltage (upper plot) and line current (lower plot).

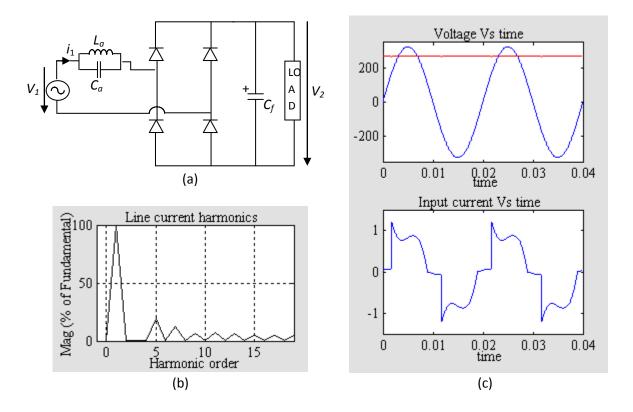

- Figure. 2.7 Rectifier with an additional inductor, capacitor and diode (LCD). (a) 25 Schematic; (b) Line current harmonics; (c) Line voltage, output voltage (upper plot) and line current (lower plot)..

- Figure. 2.8 Valley-fill rectifier: (a) Schematic; (b) Line current harmonics; (c) Line 26 voltage, output voltage (upper plot), and line current (lower plot).

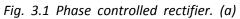

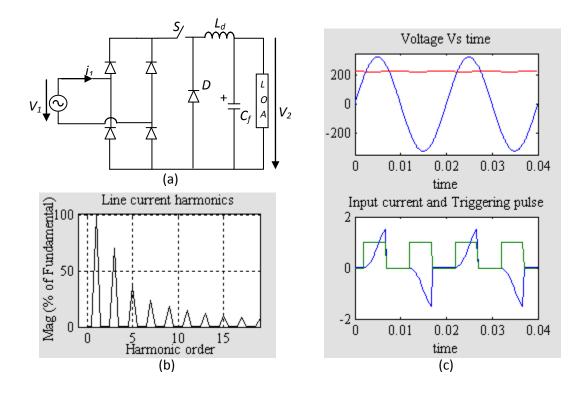

- 29 Figure. 3.1 Phase controlled rectifier. (a) Schematic; (b) Line voltage and output

voltage (upper plot) and line current (lower plot); (c) Power factor Vs firing angle for different values of inductance (upper plot) and vice versa. (d) Line voltage and output voltage (upper plot) and line current (lower plot); with additional capacitance Ca. (e) Line current harmonics without and with capacitance Ca.

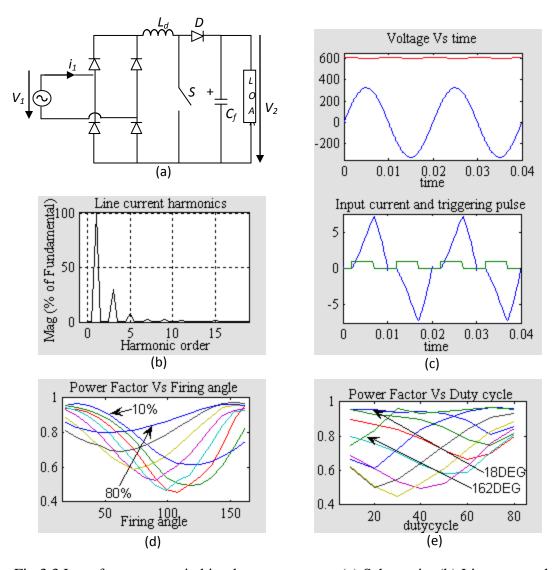

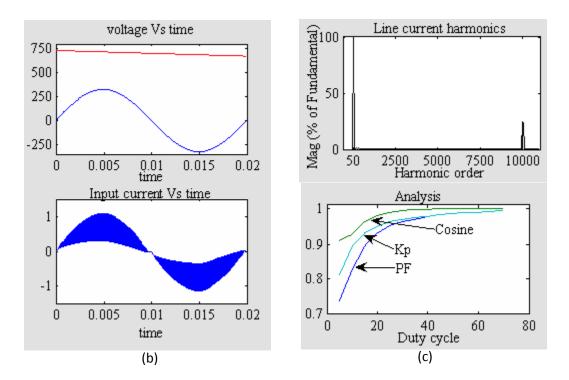

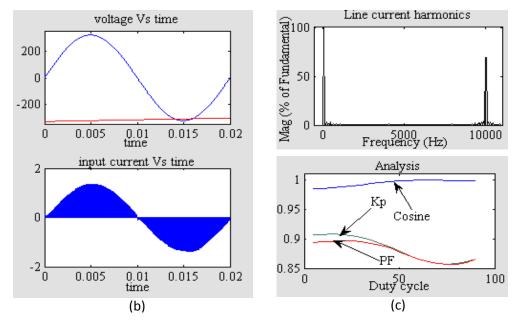

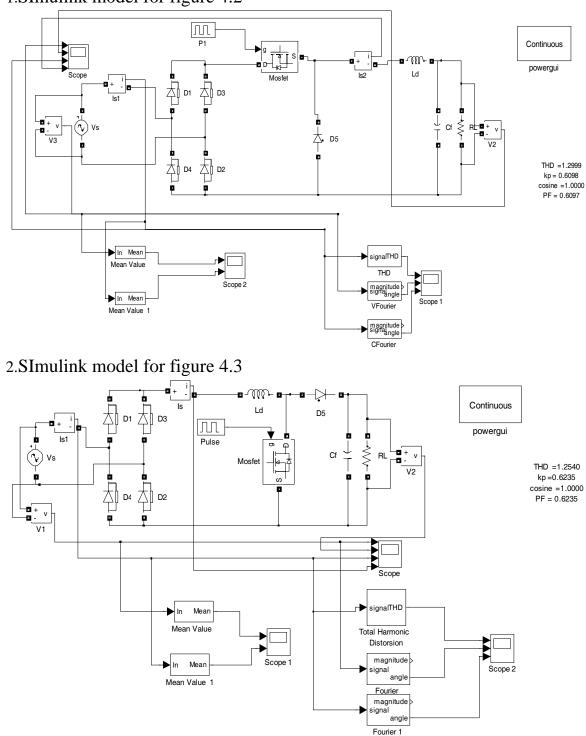

| Figure. 3.2 | Low-frequency switching buck converter. (a) Schematic; (b) Line Current harmonics; (c) Line voltage and output voltage (upper plot), line current and firing pulse (lower plot); (d) & (e) Power factor Vs firing angle for different values of duty cycles and vice versa respectively. | 32 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

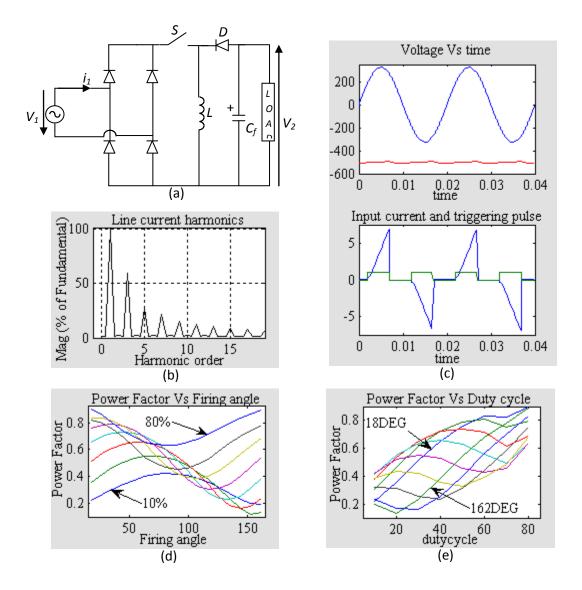

| Figure. 3.3 | Low-frequency switching boost converter. (a) Schematic; (b) Line current harmonics; (c) Line voltage, output voltage (upper plot), line current and firing pulse (lower plot); (d) & (e) Power factor Vs firing angle for different values of duty cycles and vice versa respectively.   | 32 |

| Figure. 3.4 | Low-frequency switching buck-boost converter                                                                                                                                                                                                                                             | 33 |

| Figure. 3.5 | First order switching cell                                                                                                                                                                                                                                                               | 34 |

| Figure. 3.6 | High-frequency switching buck converter. (a) Schematic; (b) Line voltage, output voltage (upper plot), Line current (lower plot).                                                                                                                                                        | 36 |

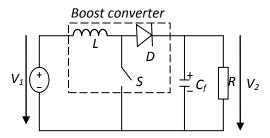

| Figure 3.7  | High-frequency switching boost converter.                                                                                                                                                                                                                                                | 37 |

| Figure 3.8  | High-frequency switching buck-boost converter.                                                                                                                                                                                                                                           | 38 |

| Figure. 4.1 | converter (a) Schematic; (b) Input current; (c) Input VI Characteristic of basic buck converter operating in DICM.                                                                                                                                                                       | 42 |

| Figure. 4.2 | Boost converter. (a) Schematic; (b) Input current; (c) Input V-I Characteristic of basic boost converter operating in DICM.                                                                                                                                                              | 43 |

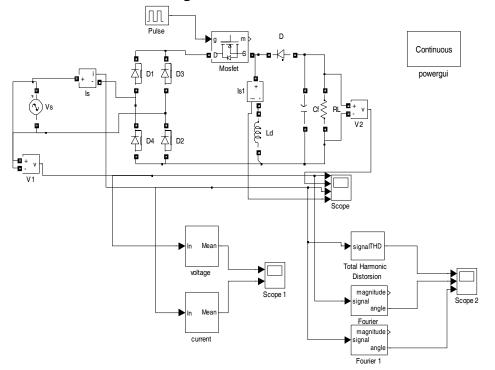

| Figure. 4.3 | Buck-boost converter. (a) Schematic; (b) Input current; (c) Input V-I Characteristic of basic boost converter operating in DICM.                                                                                                                                                         | 45 |

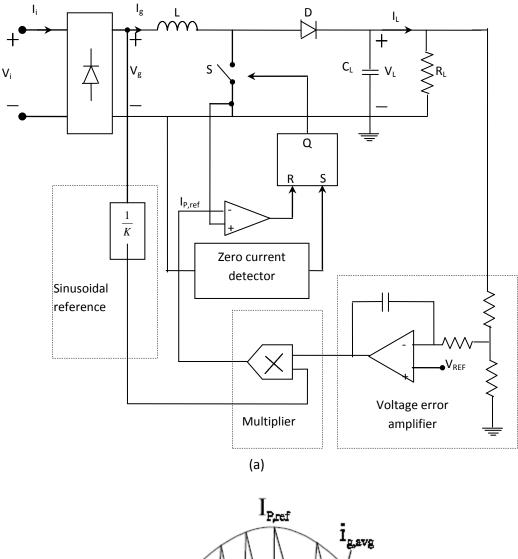

| Figure. 5.1 | Control scheme for PFC using a switching converter operating in CICM                                                                                                                                                                                                                     | 49 |

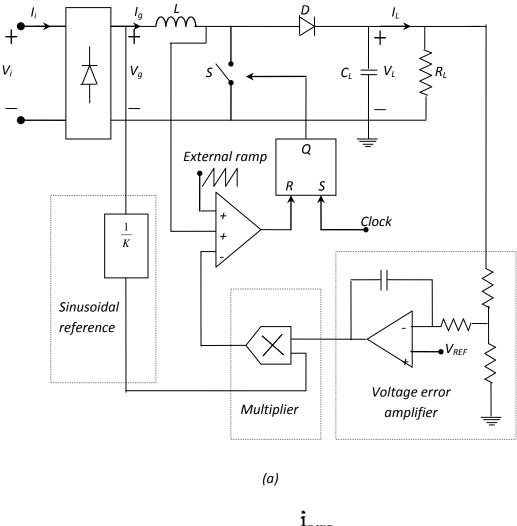

| Figure. 5.2 | Peak current control scheme                                                                                                                                                                                                                                                              | 51 |

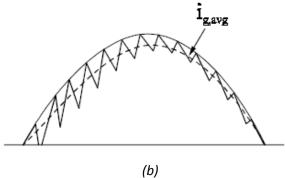

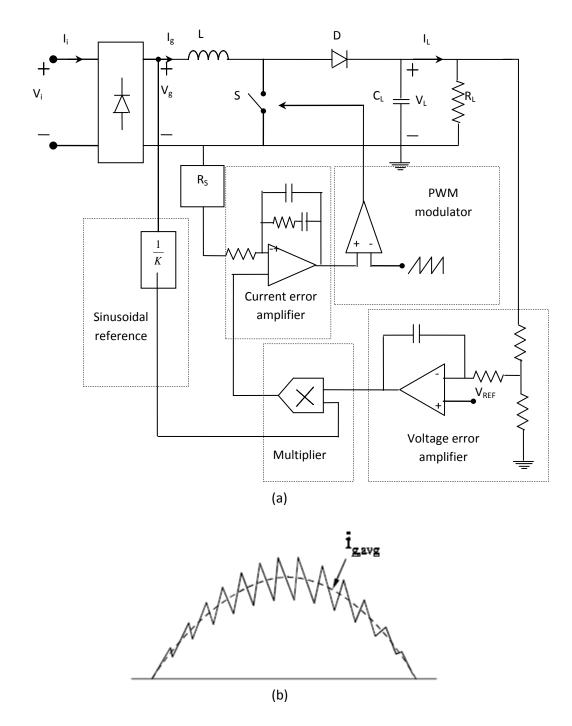

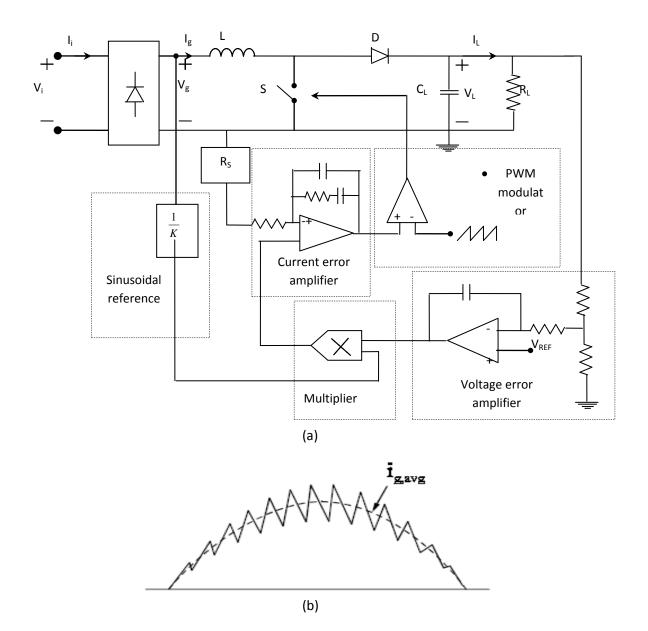

| Figure. 5.3 | Average current control scheme                                                                                                                                                                                                                                                           | 53 |

| Figure. 5.4 | Hysteresis control scheme                                                                                                                                                                                                                                                                | 55 |

| Figure. 5.5 | Borderline control scheme                                                                                                                                                                                                                                                                | 57 |

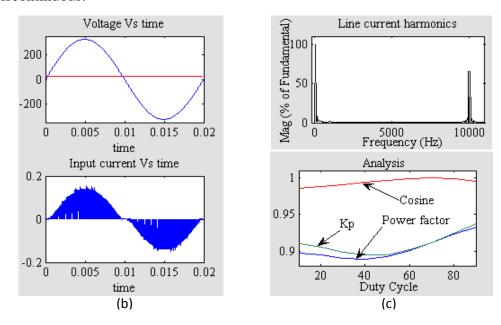

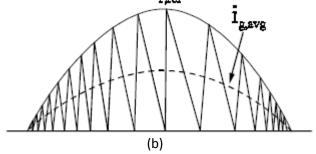

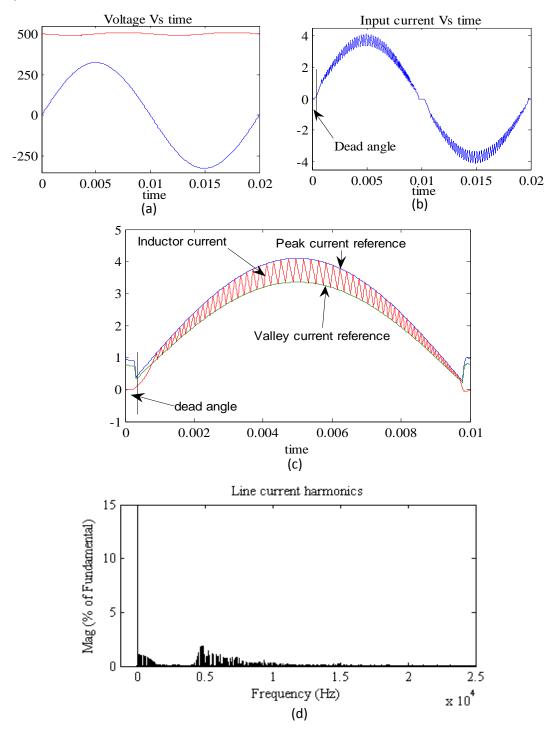

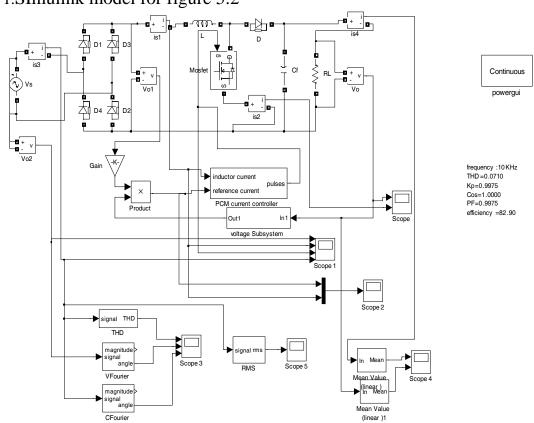

| Figure. 5.6 | peak current controlled boost converter. (a)Input voltage and output voltage; (b) Input current; (c) Inductor current and reference current; (d) Line current harmonics.                                                                                                                 | 58 |

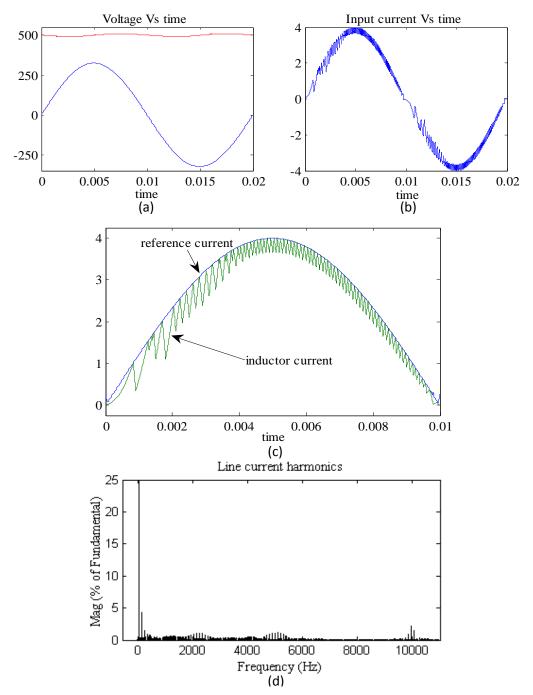

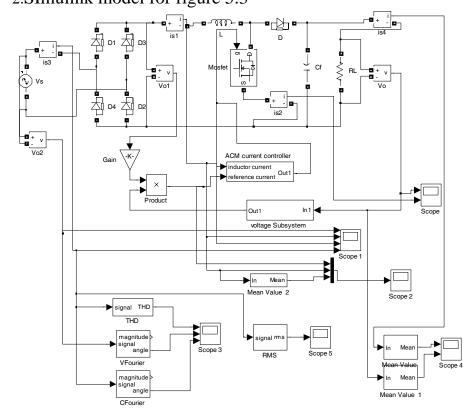

| Figure. 5.7 | Average current mode controlled boost converter. (a) Input voltage and.<br>output voltage; (b) Input current; (c) Inductor current and reference<br>current;(d)Line current harmonics.                                                                                                   | 59 |

| Figure. 5.8 | Hysteresis controlled boost converter. (a) Input voltage and output voltage;                                                                                                                                                                                                             | 60 |

(b) Input current; (c) Inductor current and reference current; (d) Line current harmonics. (e) Power factor at various dead angles for different current ripples; (f) Total harmonic distortion versus dead angle.

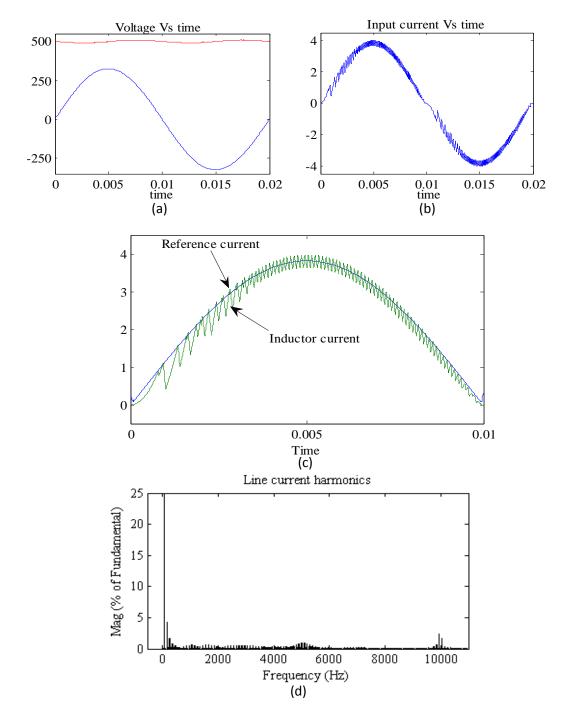

| Figure. 5.9  | Borderline controlled boost converter. (a) Input voltage and output voltage; (b) Input current; (c) Inductor current and reference current; (d) Line current harmonics | 61 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

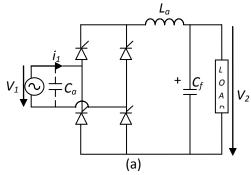

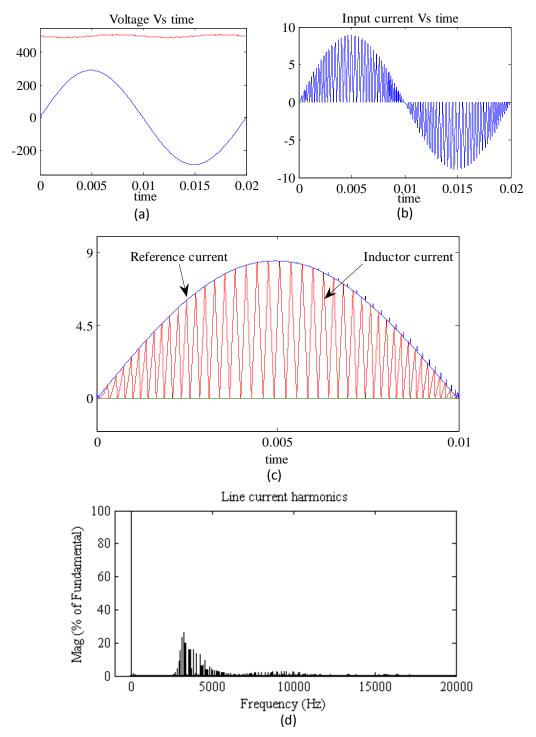

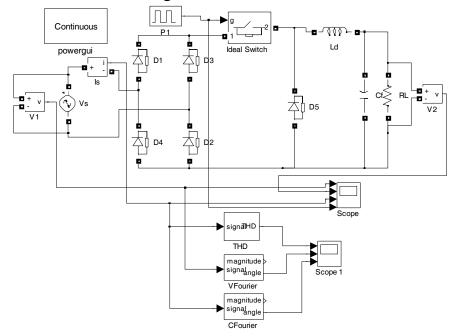

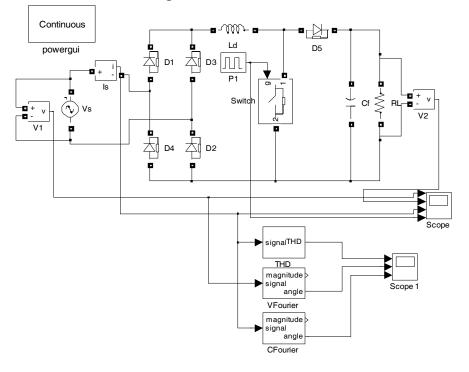

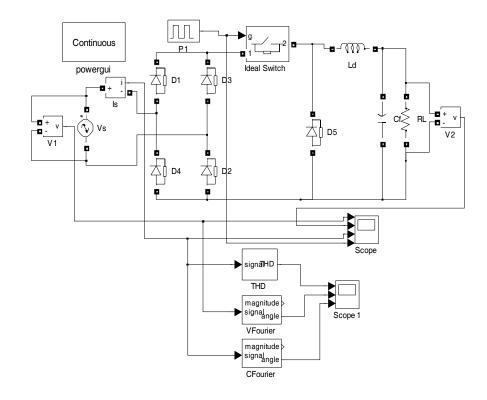

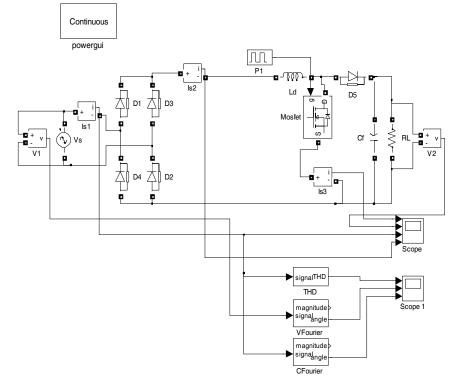

| Figure. 6.1  | ZVT PWM boost PFC converter                                                                                                                                            | 63 |

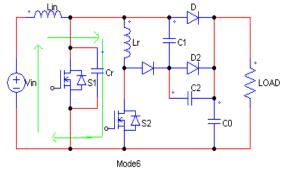

| Figure. 6.2  | Equivalent circuit of each operating mode                                                                                                                              | 66 |

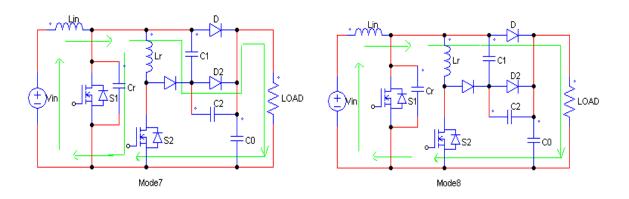

| Figure. 6.3  | Theoretical waveforms of the ZVT converter                                                                                                                             | 69 |

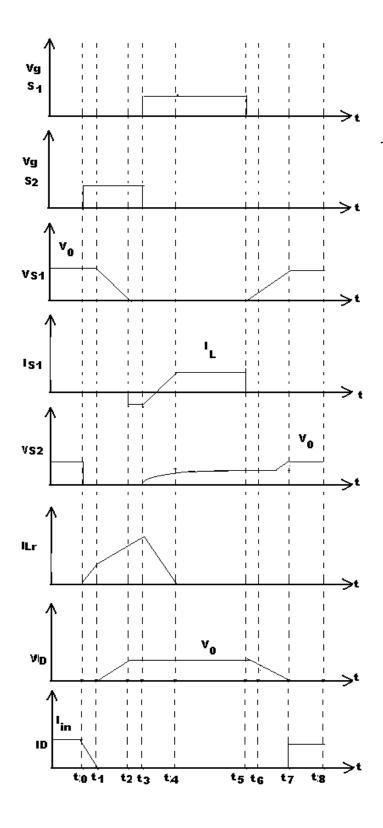

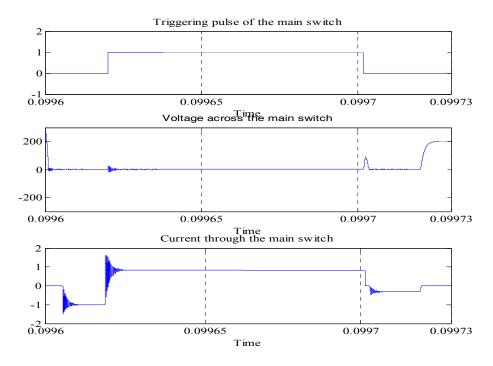

| Figure. 6.4  | Triggering pulse of auxiliary switch, current and the voltage across it in ZVT converter.                                                                              | 75 |

| Figure. 6.5  | Triggering pulse of the main switch and the voltage across it in ZVT Converter.                                                                                        | 75 |

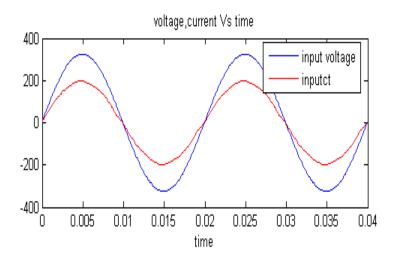

| Figure. 6.6  | ZVT converter. Input voltage and the output voltage (upper plot) and input current (lower plot).                                                                       | 76 |

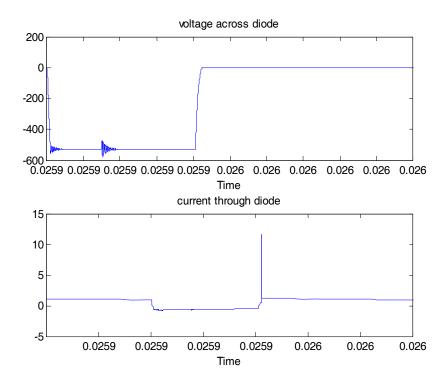

| Figure. 6.7  | Voltage across the diode and Current through the diode.                                                                                                                | 76 |

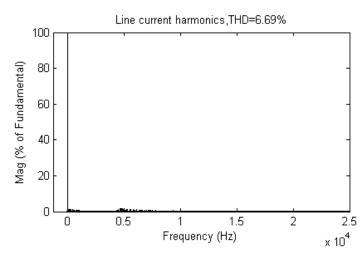

| Figure 6.8   | Harmonic distortion Without ZVT.                                                                                                                                       | 77 |

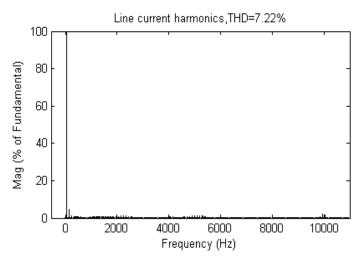

| Figure 6.9   | Harmonic distortion With ZVT.                                                                                                                                          | 77 |

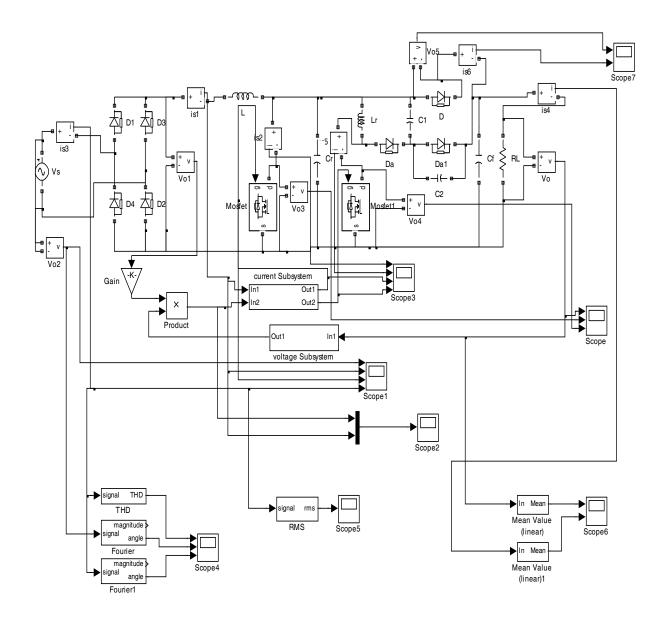

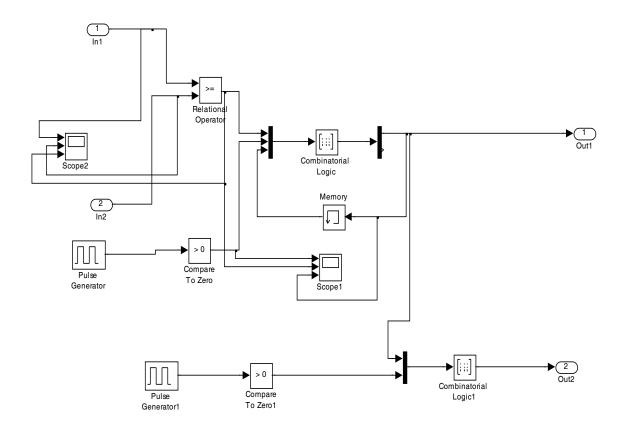

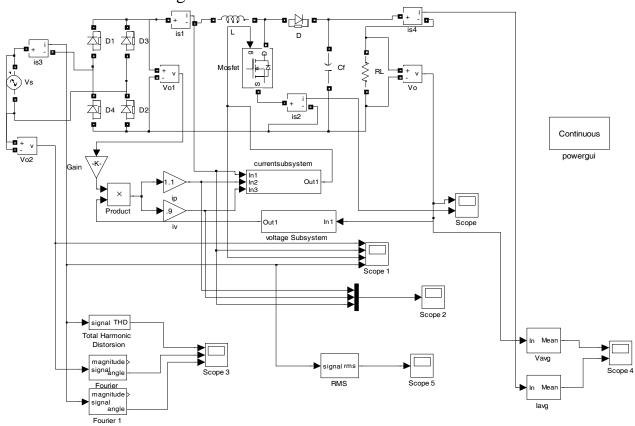

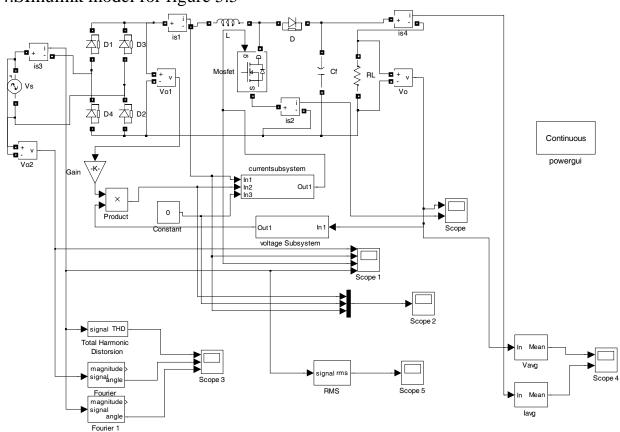

| Figure.6.10  | Simulation model of the proposed ZVT converter.                                                                                                                        | 78 |

| Figure.6.11. | Current sub system of the proposed ZVT converter.                                                                                                                      | 79 |

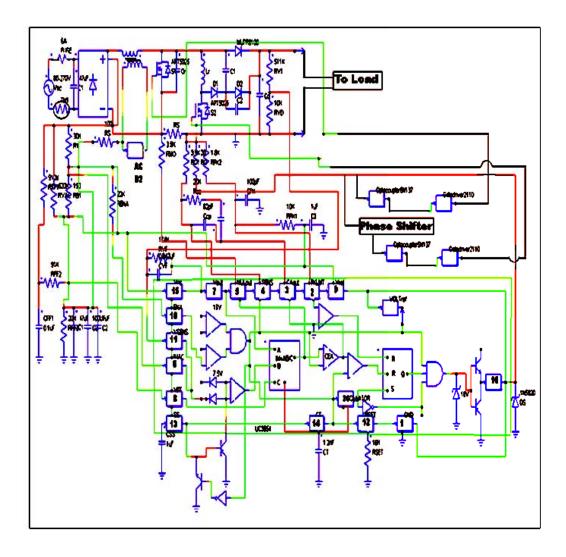

| Figure.6.12. | Experimental circuits.                                                                                                                                                 | 80 |

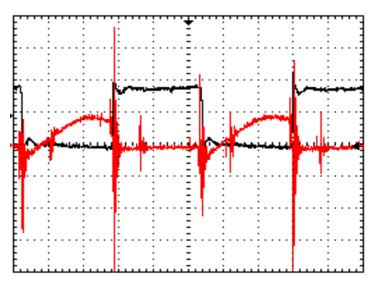

| Figure. 6.13 | Current and voltage waveforms of auxiliary switch S2, for the proposed ZVT PFC converter.                                                                              | 81 |

| Figure. 6.14 | Current and voltage waveforms of main switch S1 for the proposed ZVT PFC converter.                                                                                    | 81 |

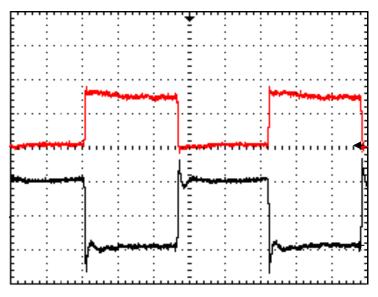

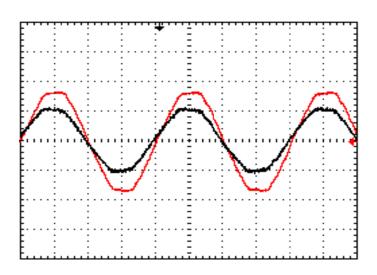

| Figure.6.15. | Experimental results of the input voltage and current waveform for the Proposed ZVT PFC converter.                                                                     | 82 |

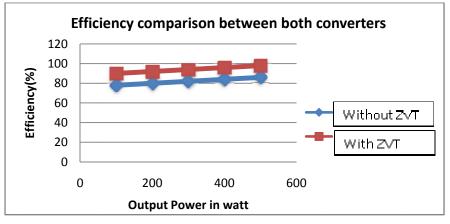

| Figure.6.16. | Efficiency plot between without ZVT converter and with ZVT converter                                                                                                   | 82 |

# LIST OF TABLES

| Table 1.1(a): | Limits for Class-A and Class-D in standard IEC 1000-3-2            |    |  |

|---------------|--------------------------------------------------------------------|----|--|

| Table 1.1(b): | Limits for Class-B and C in standard IEC 1000-3-2                  |    |  |

| Table 1.2:    | Odd harmonic limits in standard IEEE 519-1992                      | 7  |  |

| Table 3.1     | Topology-specific characteristics                                  | 39 |  |

| Table 4.2:    | CICM-DICM mode boundaries for the buck, boost, and buck-boost      | 44 |  |

|               | converters.                                                        |    |  |

| Table.6.1:    | Designed Values for the converter.                                 | 69 |  |

| Table 6.2:    | Comparison of different parameters with and without soft-switching | 72 |  |

# **CHAPTER 1**

# **INTRODUCTION**

Nonlinear loads and their effects

**Standards regulating line current harmonics**

**Power factor correction**

**Applications of PFC**

**Research Background**

**Objective of this thesis work**

#### **INTRODUCTION:**

Most applications requiring *ac-dc* power converters need the output *dc* voltage to be well regulated with good steady-state and transient performance. The circuit typically favored until recently (diode rectifier-capacitor filter) for the utility interface is cost effective, but it severely deteriorates the quality of the utility supply thereby affecting the performance of other loads connected to it besides causing other well-known problems. In order to maintain the quality of the utility supply, several national and international agencies have started imposing standards and recommendations for electronic instrument connected to the utility. Since the mid-1980's power electronics engineers have been developing new approaches for better utility interface, to meet these standards. These new circuits have been collectively called *Power factor correction* (*PFC*) circuits.

With the increase of consumer electronics the power quality becomes poor. The reactive power drawn from the supply is increasing [3]. This is because of the use of rectification of the AC input and the use of a bulk capacitor directly after the diode bridge rectifier. Reducing the input current harmonics to meet the agency standards implies improvement of power factor as well. For this reason the publications reported in this area have used "Power factor correction methods" and "Harmonic elimination/reduction methods" almost inter changeably. Several techniques for PFC and harmonic reduction have been reported and a few of them have gained greater acceptance over the others.

This chapter discusses the i) Nonlinear loads and their effect on the electricity distribution network, ii) Standard IEC and IEEE regulation for harmonics, iii) Power factor correction and its benefits, iv) application of PFC both for linear and non-linear loads, v) research background, vi) problem formulation, and vii) aim of the dissertation

# 1.1 NONLINEAR LOADS AND THEIR EFFECT ON THE ELECTRICITY DISTRIBUTION NETWORK:

The instrument connected to an electricity distribution network usually needs some kind of power conditioning, typically rectification, which produces a non-sinusoidal line current due to the non-linear input characteristic.

Line-frequency diode rectifiers convert AC input voltage into DC output voltage in an uncontrolled manner. Single-phase diode rectifiers are needed in relatively low power instrument that needs some kind of power conditioning, such as electronic instrument and household appliances. For higher power, three-phase diode rectifiers are used. In both single and three-phase rectifiers, a large filtering capacitor is connected across the rectifier output to obtain DC output voltage with low ripple. As a consequence, the line current is non sinusoidal.

In most of these cases, the amplitude of odd harmonics of the line current is considerable with respect to the fundamental. While the effect of a single low power nonlinear load on the network can be considered negligible, the cumulative effect of several nonlinear loads is important. Line current harmonics have a number of undesirable effects on both the distribution network and consumers.

These effects include:

- 1. Losses and overheating in transformers, shunt capacitors, power cables, AC machines and Switchgear, leading to premature aging and failure.

- Excessive current in the neutral conductor of three-phase four-wire systems, caused by odd Triple current harmonics (triple-n: 3rd, 9th, 15th, etc.).

- 3. Reduced power factor, hence less active power available from a wall outlet having a certain apparent power rating.

- 4. Electrical resonances in the power system, leading to excessive peak voltages and RMS currents, and causing premature aging and failure of capacitors and insulation.

- 5. The distorted line voltage may affect other consumers connected to the electricity distribution network.

- 6. Telephone interference.

- 7. Errors in metering instrument.

- 8. Increased audio noise.

- Cogging or crawling in induction motors, mechanical oscillation in a turbine-generator combination or in a motor-load system.

10. Distortion of the line voltage via the line impedance shown in Fig.1.1 where the typical worst case values: R-Line=0.5 ohm, and L-Line=1mH have been considered. The effect is stronger in weaker grids. For example, some electronic instrument is dependent on accurate determination of aspects of the voltage wave shape, such as amplitude, RMS and zero-crossings

Fig. 1.1: Single-phase diode bridge rectifier: (a) Schematic; (b) Typical line voltage and line current waveforms (upper plot) and odd line current harmonics (lower plot). And the line current has  $THD_i=1.5079$  and power factor of 0.5475.

#### **1.2. Standards regulating line current harmonics:**

#### 1.2.1 Standard IEC 1000-3-2:

- 1. It applies to instrument with a rated current up to and including 16Arms per phase which is to be connected to 50Hzor 60 Hz, 220-240Vrms single-phase or 380-415Vrms three-phase mains [1],[2].

- 2. Items of electrical instrument are categorized into four classes (A, B, C, and D), for which specific limits are set for the harmonic content of the line current.

- 3. These limits do not apply for the instrument with rated power less than 75w, other than lighting instrument.

#### CLASS-A:

Instrument not specified in one of the other three classes should be considered as class-A instrument. The classification can also be represented using the flowchart:

Fig: 1.2. Classification of instrument under Standard IEC 1000-3-2

#### CLASS-B:

It includes portable tools, and nonprofessional arc welding instrument.

#### CLASS-C:

It includes lighting instrument (except for dimmers for incandescent lamps, which belong to class-A).

#### CLASS-D:

Instrument with special line current shape i.e. includes instrument having an active input power less than or equal to 600w, of the following types:

- i. Personal computers.

- ii. Personal computer monitors.

- iii. Television receivers.

## Limits in standard IEC 1000-3-2:

Table 1.1(a): Limits for Class-A and Class-D

Table 1.1(b): Limits for Class-B and C

|               | Harmonic<br>order | Class-<br>A      | C                | lass-D |

|---------------|-------------------|------------------|------------------|--------|

|               |                   | A <sub>rms</sub> | A <sub>rms</sub> | mA/W   |

|               | 3                 | 2.30             | 2.30             | 3.40   |

|               | 5                 | 1.14             | 1.14             | 1.90   |

|               | 7                 | 0.77             | 0.77             | 1.00   |

|               | 9                 | 0.40             | 0.40             | 0.50   |

|               | 11                | 0.33             | 0.33             | 0.35   |

| nonics        | 13                | 0.21             | 0.21             | 0.29   |

| odd harmonics | 15 to 39          | 2.25/n           | 2.25<br>/n       | 3.85/n |

| onics [       | 2                 | 1.08             |                  |        |

| n harmo       | 4                 | 0.43             |                  |        |

| Eve           | 6                 | 0.30             |                  |        |

|               | 8 to 40           | 1.84/n           |                  |        |

|   | armonic<br>order | Class-B          | Class-C |

|---|------------------|------------------|---------|

|   |                  | A <sub>rms</sub> | %       |

|   | 3                | 3.45             | 30*PF   |

|   | 5                | 1.71             | 10      |

|   | 7                | 1.15             | 7       |

|   | 9                | 0.60             | 5       |

|   | 11               | 0.49             | 3       |

|   | 13               | 0.31             | 3       |

| 1 | 5 to 39          | 3.375/n          | 3       |

|   | 2                | 1.62             | 2       |

|   | 4                | 0.64             |         |

|   | 6                | 0.45             |         |

| 8 | 8 to 40          | 2.76/n           |         |

odd harmonics

Even harmonics

#### 1.2.2 STANDARD IEEE 519-1992:

Gives recommended practices and requirements for harmonic control in electrical power systems for both individual consumers and utilities. The limits for line current harmonics are given as a percentage of the maximum demand load current  $I_L$  at the point of common coupling-PCC at the utility. They decrease as the ratio  $I_{SC}/I_L$  decreases where  $I_{SC}$  is the maximum short circuit current at PCC, meaning that the limits are lower in weaker grids. This standard covers also high voltage loads of much higher power.

#### Limits in standard IEEE 519-1992:

| $I_{SC}/I_L(\%)$ | h<11 | 11≤h<17 | 17≤h<23 | 23≤h<35 | 35≤h | TDD <sup>*</sup> |

|------------------|------|---------|---------|---------|------|------------------|

| <20              | 4.0  | 2.0     | 1.5     | 0.6     | 0.3  | 5                |

| 20 to 50         | 7.0  | 3.5     | 2.5     | 1.0     | 0.5  | 8                |

| 50 to 100        | 10.0 | 4.5     | 4.0     | 1.5     | 0.7  | 12               |

| 100 to 1000      | 12.0 | 5.5     | 5.0     | 2.0     | 1.0  | 15               |

| >1000            | 15.0 | 7.0     | 6.0     | 2.5     | 1.4  | 20               |

Table 1.2: Odd harmonic limits:

\*TDD=Total Demand Distortion.

#### **1.3 POWER FACTOR CORRECTION:**

Reduction of line current harmonics is needed in order to comply with the standard. This is commonly referred to as the Power Factor Correction – PFC, which may be misleading. When an electric load has a PF lower than 1, the apparent power delivered to the load is greater than the real power that the load consumes. Only the real power is capable of doing work, but the apparent power determines the amount of current that flows into the load, for a given load voltage.

Power factor correction (PFC) is a technique of counteracting the undesirable effects of electric loads that create a power factor PF that is less than 1.

The power factor is defined as the ratio of the active power P to the apparent power S:

$$PF = P/S \tag{1.1}$$

For purely sinusoidal voltage and current, the classical definition is obtained:

$$PF = \cos \phi \tag{1.2}$$

Where  $\cos \Phi$  is the displacement factor of the voltage and current. In classical sense, PFC means compensation of the "displacement factor".

The line current is non-sinusoidal when the load is nonlinear. For sinusoidal voltage and nonsinusoidal current the PF can be expressed as.

$$PF = \frac{V_{rms}I_{1rms}}{V_{rms}I_{rms}}\cos\phi = \frac{I_{1rms}}{I_{rms}}\cos\phi = K_p\cos\phi$$

(1.3)

$$K_p = \frac{I_{1rms}}{I_{rms}}, K_p \in [0,1]$$

$$(1.4)$$

$K_p$  describes the harmonic content of the current with respect to the fundamental. Hence, the power factor depends on both harmonic content and displacement factor.  $K_p$  is referred to as purity factor or distortion factor.

The total harmonic distortion factor THD<sub>i</sub> is defined as

$$\text{THDi} = \frac{\sqrt{\sum_{n=2}^{\infty} I_{n,rms}^2}}{I_{1rms}} \tag{1.5}$$

Hence the relation between Kp and THDi is

$$K_p = \frac{1}{\sqrt{1 + THD^2}} \tag{1.6}$$

Standard IEC 1000-3-2 sets limits on the harmonic content of the current but does not specifically regulate the purity factor Kp or the total harmonic distortion of the line current THD<sub>i</sub>. The values of Kp and THD<sub>i</sub> for which compliance with IEC 1000-3-2 is achieved depend on the power level. For low power level, even a relatively distorted line current may comply with the standard. In addition to this, it can be seen from (1.6) that the distortion factor Kp of a waveform with a moderate THD<sub>i</sub> is close to unity (e.g. Kp=0.989 for THDi=15%). Considering (1.3) as well, the following statements can be made:

- Power factor PF is not significantly degraded by harmonics, unless their amplitude is quite large (low K<sub>p</sub>, very large THD<sub>i</sub>).

- 2. Low harmonic content does not guarantee high power factor ( $K_p$  close to unity, but low  $\cos \Phi$ ).

#### 1.3.1 Benefits Of Power Factor:

- 1. Voltage distortion is reduced.

- 2. All the power is active.

- 3. Smaller RMS current.

- 4. Higher number of loads can be fed.

Most of the research on PFC for nonlinear loads is actually related to the reduction of the harmonic content of the line current. There are several solutions to achieve PFC [3], [4]. The shape of the input current can be further improved by using a combination of low pass input and output filters [5],[6][7],[8].Depending on whether active switches (controllable by an external control input) are used or not, PFC solutions can be categorized as "Passive" or "Active".

In *passive* PFC, only passive elements are used in addition to the diode bridge rectifier, to improve the shape of the line current. Obviously, the output voltage is not controllable. For *active* PFC, active switches are used in conjunction with reactive elements in order to increase the effectiveness of the line current shaping and to obtain controllable output voltage. The switching frequency further differentiates the active PFC solutions into two classes. In *low-frequency* active PFC, switching takes place at low-order harmonics of the line-frequency and it is synchronized with the line voltage. In *high-frequency* active PFC, the switching frequency is much higher than the line frequency.

#### **1.4 APPLICATIONS OF PFC:**

#### 1.4.1 Electricity industry: Power factor correction of linear loads.

Power factor correction is achieved by complementing an inductive or a capacitive circuit with a (locally connected) reactance of opposite phase. For a typical phase lagging PF load, such as a large induction motor, this would consist of a capacitor bank in the form of several parallel capacitors at the power input to the device. Instead of using a capacitor, it is possible to use an unloaded synchronous motor. This is referred to as a synchronous condenser. It is started and connected to the electrical network. It operates at full leading power factor and puts VARs onto the network as required to support a system's voltage or to maintain the system power factor at a specified level. The condenser's installation and operation are identical to large electric motors.

The reactive power drawn by the synchronous motor is a function of its field excitation. Its principal advantage is the ease with which the amount of correction can be adjusted; it behaves like an electrically variable capacitor.

#### 1.4.2 Switched mode power supply: Power factor correction of non-linear loads.

A typical switched-mode power supply first makes a DC bus, using a bridge rectifier or similar circuit. The output voltage is then derived from this DC bus. The problem with this is that the rectifier is a non-linear device, so the input current is highly non-linear. That means that the input current has energy at harmonics of the frequency of the voltage. This presents a particular problem for the power companies, because they cannot compensate for the harmonic current by adding capacitors or inductors, as they could for the reactive power drawn by a linear load. Many jurisdictions are beginning to legally require PFC for all power supplies above a certain power level.

The simplest way to control the harmonic current is to use a filter: it is possible to design a filter that passes current only at line frequency (e.g. 50 or 60 Hz). This filter kills the harmonic current, which means that the non-linear device now looks like a linear load. At this point the power factor can be brought to near unity, using capacitors or inductors as required. This filter requires large-value high-current inductors, however, which are bulky and expensive.

It is also possible to perform active PFC. In this case, a boost converter is inserted between the bridge rectifier and the main input capacitors. The boost converter attempts to maintain a constant DC bus voltage on its output while drawing a current that is always in phase with and at the same frequency as the line voltage. Another switch-mode converter inside the power supply produces the desired output voltage from the DC bus. This approach requires additional semiconductor switches and control electronics, but permits cheaper and smaller passive components. It is frequently used in practice. Due to their very wide input voltage range, many power supplies with active PFC can automatically adjust to operate on AC power from about 100 V (Japan) to 240 V (UK). That feature is particularly welcome in power supplies for laptops and cell phones.

#### **1.5 Research Background:**

There is a significant interest on the part of society to reduce the amount of nonlinear loading on AC power systems. This loading reduces the distribution capacity of the public power system, and it can degrade the quality of the power by distorting the AC power waveform delivered to nearby customers. The negative effects of line current distortion have prompted a need for setting limits for the line current harmonics of instrument connected to the electricity distribution network. Standardization activities in this area have been carried out for many years. As early as 1982, the International Electro-technical Committee-IEC published its standard IEC 555-2, which was also adopted in 1987 as European standard EN 60555-2, by the European Committee for Electro-technical Standardization - CENELEC. Standard IEC 555-2 has been replaced in 1995 by standard IEC 1000-3-2 [1], [2], also adopted by CENELEC as European standard EN 61000-3-2. Most of the research on PFC for nonlinear loads is actually related to the reduction of the harmonic content of the line current. There are several solutions to achieve PFC, which were discussed in [3], [4]. Depending on whether active switches (controllable by an external control input) are used or not, PFC solutions can be categorized as "Passive" or "Active".

#### 1.5.1 Passive PFC

In Passive PFC circuit only passive elements are used in addition to the diode bridge rectifier, to improve the shape of the line current. In order to improve the shape of the line current Passive Power Factor correction circuit simply uses an inductor in the input circuits. The shape of the input current can be further improved by using a combination of low pass input and output filters was given in [5-8]. To maintain the flow of input current, voltage doublers is inserted to feed the valley fill circuit [9], [10]. Even though line current harmonics are reduced, the fundamental component may show an excessive phase shift that reduces the power factor. Better characteristics can be obtained by using "Active PFC".

#### 1.5.2 Active PFC

Active power factor correction can be accomplished by many ways. The Boost converter operated on the rectified output uses a constant switching frequency PWM and DCM operation reduces the total harmonic distortion of the input current [11], [12], [14], [15]. In a Boost circuit the switching device can handles only a portion of output power which increases the efficiency. The efficiency can be increased by keeping the ratio of output voltage to input voltage closer to unity. The effect of second harmonic in PWM in reducing third harmonic component in the input current is established. In this converter the output is varied by varying the duty cycle keeping the

frequency constant. In this control method, the duty cycle D is varied by injecting second harmonic to the reference signal. The variation of D is given by  $D = K[1 + m.\sin(2\omega t + \Omega)]$ , where k proportional coefficient which controls the input power, m modulation index, w input frequency,  $\Omega$  initial phase angle that controls the THD value in the input current[16].

The other converter topologies for a PFC based Sepic topology are reported in [17-19], which allow comparison of converter performance with different control techniques. The advantages of clamped current control include overall simplicity, relatively low inductive energy storage and component stresses, and fixed operating frequency discussed in[20],[22]. Another control method, which allows a better input current waveform, is the average current control represented in Fig.5.3 [21, 23-25].

Hysteresis control technique has been reported in [26-27]. In this control technique, the switch is turned on when the inductor current goes below the lower reference  $I_{vref}$ , and is turned off when the inductor current goes above the upper reference, giving rise to a variable frequency control. But in Borderline Control approach [28] the switch on-time is held constant during the line cycle and the switch is turned on when the inductor current falls to zero, so that the converter operates at the boundary between Continuous and Discontinuous Inductor Current Mode (CICM-DICM). The paper [48] presents a new approach for generating reference currents for an active filter and a static compensator. The purpose of the compensating scheme is to balance the load, as well as make the supply side power factor a desired value. Here a suitable compensator structure is proposed which tracks the reference currents in a hysteresis band control scheme.

#### 1.5.3 EMI Problem

The converters operating in CICM reduces the line current harmonics, but it has some drawbacks, such as: 1) It increases the EMI, due to the high-frequency content of the input current. 2) It introduces additional losses, thus reducing the overall efficiency. However the high frequency EMI can be eliminated by introducing an EMI filter between AC supply and diode bridge rectifier were found in various studies [29],[30],[31]. The second requirement for the EMI filter: the displacement angle  $\Phi$  must be kept low. The third requirement is related to the overall stability of the system. It is known that unstable operation may occur due to the interaction between the EMI filter and the power stage. This phenomenon is given in [32], [33] and [34].

However the losses are reduced by inserting an inductor in the series path of the boost rectifier to reduce the di/dt rate during its turn-off [35]. Better characteristics are obtained in Zero Voltage

Transition – ZVT topologies, at the expense of increased complexity. Several ZVT topologies was found in [36-41]. The converter proposed in [42] reduces the current stress on the main switch, and it will still keep the advantages of a PWM converter because after the switching transition is over, the circuit reverts back to PWM operation mode. Most attention is paid to the damping of voltage harmonics. However, this control strategy allows mitigating voltage dips in [43].

The focus of the topology [44] is to reduce the DC bus voltage at light load without compromising with input power factor and voltage regulation. The boost inductor operation is maintained in the discontinuous current mode (DCM) [45], So that natural power factor correction is obtained. The research got a tremendous boost with the strides made in the miniaturization of the electrical industry [47]. According to this the harmonics and noise can be reduced by using EMI Filter connected at the input side of Boost PFC Converter. The purpose of the compensating scheme [48] is to balance the load, as well as make the supply side power factor a desired value. However Over the years, lot of research has been carried out for the supply of quality power to the consumers, by minimizing Electro Magnetic Interference is presented in [49].

#### **1.5.4** Switching Loss:

In active PFC circuit, switching of semiconductor devices normally occurs at high current levels. Therefore, when switching at high frequencies these converters are associated with high power dissipation. Also, the higher input and lower output voltages bring about very low duty cycles. Hence, the high side MOSFET switch should turn on and off in a very short period of time, which also brings switching losses into picture [50], [51], [52]. The losses due to switching produce three considerable effects [53] on the converters in general,

- 1. Achievable f<sub>s</sub> and efficiency limited

- 2. EMI at high frequencies due to high di/dt, dv/dt and induces noise

- 3. Switching losses may sometimes exceed safe operating area

Switching loss of a MOSFET can be represented mathematically as,

$$P_{SW} = \frac{V_{DS.}I_{D.}f_{S}}{2}(t_{on} + t_{off})$$

From above equation some important result can be deduced that switching losses can be reduced by two methods:

(i) By reducing the turn-on and turn-off delay times. This is done by using faster and more efficient switches in the converter.

(ii) By making the current or voltage across the switch zero before turning it on or off. Soft switching resonant converters are based on this concept.

Also it is inferred from the equation that the switching loss in any semiconductor switch varies linearly with  $f_s$  and the delay times [53], [54].

Hard switching is the predominant loss mechanism in the high side MOSFET followed by the conduction losses of the low side MOSFET [55], [56]. Some 60% to 70% of the total losses are in the MOSFET for a 60W power converter (Step – Down). Thus, more efficient power MOSFETs is needed that offer both reduced conduction and switching losses at higher frequencies [57]. The switching losses at higher frequencies can be eliminated by the soft switching techniques available.

#### 1.5.4.1 Solution

There are mainly two techniques to eliminate the switching losses namely ZVS and ZCS. QRCs were introduced to overcome the disadvantages of conventional PWM converters operating at high switching frequency by achieving ZVS for the active switch and ZCS for the rectifier diode [58]-[61]. ZVS MRCs technique utilizes all major parasitic of the power stages and all semiconductor devices in MRC operate with ZVS, which substantially reduces the switching losses and noise [62].

In both techniques, the switching losses in the semiconductor devices are eliminated due to the fact that current through or voltage across the switching device at switching point is equal to or near zero. This reduction in the switching loss allows the designer to attain a higher operating frequency without sacrificing converter efficiency. By doing so, the resonant converters show promise of achieving what could not be achieved by the PWM converter that is the design of small size and weight converters. Currently, resonant power converters operating in the range of a few megahertz are available. Another advantage of resonant converters over PWM converters is the decrease of harmonic content in the converter voltage and current waveforms. Therefore, when the resonant and PWM converters are operated at the same power level and frequency, it is expected that the resonant converter will have lower harmonic emission [63].

The Resonant converters operate with sinusoidal current through the power switches which results in high peak and RMS currents for the power transistors and high voltage stresses on the rectifier diodes. Furthermore, when the line voltage or load current varies over a wide range, QRCs are modulated with a wide switching frequency range, making the circuit design difficult to optimize [64]. As a compromise between the PWM and resonant techniques, various soft switching PWM converter techniques has been proposed to aim at combining desirable features of both the conventional PWM and Quasi Resonant techniques without a significant increase in circulating energy.

#### 1.5.4.2 ZVT and ZCT

Such a solution has been achieved by ZVT and ZCT. The choice between the two depends on the semiconductor device technology that will be used. In the case of majority carrier semiconductors, the best choice would be ZVS, where the capacitive turn-on losses can be eliminated. On the other hand, in the case of minority carrier semiconductors, the ZCS technique can avoid the turn off losses caused by the current tail [65].

The voltage-mode soft-switching method that has attracted most interest in recent years is the ZVT. This is because of its low additional conduction losses and because its operation is closest to the PWM converters. Instead of using a series resonant network across the power switch, an alternative way is to use a shunt resonant network across the power switch. The auxiliary circuit of the ZVT converters is activated just before the main switch is turned on and ceases after it is accomplished. The auxiliary circuit components in this circuit have lower ratings than those in the main power circuit because the auxiliary circuit is active for only a fraction of the switching cycle. A partial resonance is created by the shunt resonant network to achieve ZCS or ZVS during the switching transition. And it will still keep the advantages of a PWM converter because after the switching transition is over, the circuit reverts back to PWM operation mode [66 -70].

Previously proposed ZVT-PWM converters have at least one of the following key drawbacks.

- 1. The auxiliary switch is turned off while it is conducting current. This causes switching losses and EMI to appear that offsets the benefits of the using the auxiliary circuit. In converters such as the ones proposed in [71], [72] the turn off is very hard.

- 2. The auxiliary circuit components have high voltage and/or current stresses. Such as converters proposed in [73], [74]. The converter proposed in [70] reduces the current stress on the main switch, but circuit is very complex.

3. The active clamp technique have been reported in [46], where zero-voltage switching has been achieved for main and auxiliary switch.

Reducing switching loss for high side switch is of more importance. Hence this work presents the implementation of ZVT techniques in PFC circuit, where soft switching is achieved for both main and auxiliary switches.

#### **1.6 Problem Formulation:**

The investigation of PFC faces the following problems:

1. High PF with low efficiency.

2. High efficiency with low PF.

#### **1.7 Aim of This Dissertation:**

To better define the scope of the research reported in this dissertation, the PFC is performed by a high frequency switching DC/DC converter that shapes the input current as close as possible to a Sinusoidal waveform which is in phase with the line voltage. Thus, from the electrical point of view, the instrument connected to the line behaves like a resistive load.

While the high-frequency switching PFC stage reduces the line current harmonics, it also has drawbacks, such as: it introduces additional losses, thus reducing the overall efficiency; it increases the EMI, due to the high-frequency content of the input current; and it increases the complexity of the circuit, with negative effects on the reliability of the instrument, as well as on its size, weight and cost. The general aim of this dissertation is to investigate high-frequency switching circuit topologies and methods to be applied in the PFC stage, which would alleviate some of the aforementioned drawbacks. The research addresses several aspects which can be divided into seven topics.

#### **1.8 Thesis Organization:**

- Chapter 2: Provides the fundamental concepts and overview of passive PFC

- **Chapter 3:** Deals with in-depth study of low frequency and high frequency active PFC.

- Chapter 4: Discusses operations of converters In Discontinuous Inductor Current Mode (DICM).

- Chapter 5: Presents detail control techniques during operation of converter in Continuous Inductor Current Mode (CICM).

- **Chapter 6:** Presents the analysis, simulation, and experimental results of the proposed converters.

- **Chapter 7**: Provides the concluding remarks and points to possible directions for future work to be carried out in this field.

# **CHAPTER 2**

# **PASSIVE PFC**

**Diode bridge rectifier**

**Advantages of passive PFC**

**Disadvantages of Passive PFC**

#### **PASSIVE PFC**:

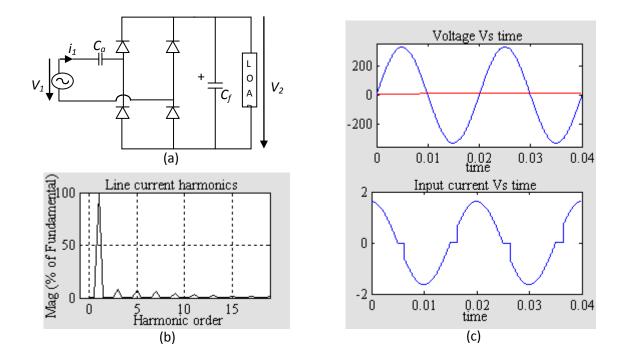

Passive PFC methods use only passive elements in addition to the diode bridge rectifier, to improve the shape of the line current. As mentioned in the previous chapter, the diode bridge rectifier, shown again in Fig.2.1 (a), has non-sinusoidal line current. This is because most loads require a supply voltage with low ripple, which is obtained by using a correspondingly large capacitance the output capacitor  $C_f$ . Consequently, the conduction intervals of the rectifier diodes are short and the line current consists of narrow pulses with an important harmonic content.

Fig. 2.1 Diode bridge rectifier: (a) Schematic; (b) Voltage ripple as a function of the output filter capacitance; (c) Line voltage and output voltage (upper plot), and input current (lower plot), with  $V_1$ =230Vrms 50Hz and constant power load P = 200W. With  $C_f = 470\mu$ F, the line current has  $K_p = 0.4349$ ,  $\cos\Phi = 0.9695$  and PF =0.4216, and the output voltage ripple is  $V_2$  =25V. With Cf = 64 $\mu$ F, the line current has  $K_p = 0.6842$ ,  $\cos\Phi = 0.8805$  and PF =0.6024, and the output voltage ripple is  $V_2$  =105V; (d) and (e) Line current harmonics with  $C_f$ =64 $\mu$ F and  $C_f$  =470 $\mu$ F respectively.

The simplest way to improve the shape of the line current, by adding additional components, is to use a lower capacitance of the output capacitor  $C_f$ . When this is done, the ripple of the output voltage increases and the conduction intervals of the rectifier diodes widen. The shape of the input current depends on the type of load that the rectifier is supplying. The shape of the input current is improved to a certain extent with the lower capacitance, at the expense of increased output voltage ripple, which can be seen from the results listed in the caption of Fig. 2.1. The concept is highlighted by the simulated waveforms shown in Fig. 2.1c), for two values of the output capacitor and assuming constant power load.

#### 2.1 Diode Bridge Rectifiers:

Before going to passive PFC, let us discuss the simplest way to improve the shape of the line current by adding an output capacitor  $C_f$  When this is done, the ripple of the output voltage increases (shown in fig. 2.1(b) ) and the conduction intervals of the rectifier diodes increases. The shape of the input current becomes also dependent on the type of load that the rectifier is supplying. The concept is highlighted by the simulated waveforms shown in Fig. 2.1, for two values of the output capacitor and assuming constant power load. The shape of the input current is improved to certain extent with the lower capacitance, at the expense of increased output voltage ripple, as can be seen also from the Fig. 2.1(b). The method presented above has severe limitations: it does not reduce substantially the harmonic currents and the output voltage ripple is large, which is not acceptable in most of the cases. Several other methods to reduce the harmonic content of the line current in single-phase systems exist, and an overview of the Passive PFC is presented next.

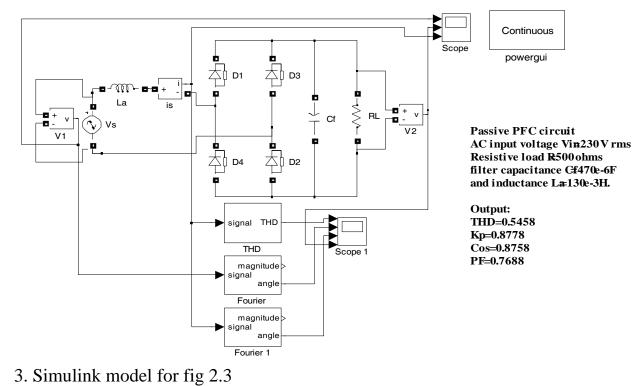

#### 2.1.1 Rectifier with AC side inductor:

One of the simplest methods is to add an inductor at the AC-side of the diode bridge, in series with the line voltage as shown in Fig.2.2 (a), and to create circuit conditions such that the line current is zero during the zero crossings of the line voltage. The maximum power factor that can be obtained is PF= 0.78. Simulated results for the rectifier with AC-side inductor are presented in Fig.2.2. From the simulation results we can observe that increase in inductance  $L_a$  results in improved line current waveform with a lower THD<sub>i</sub>, a better distortion factor and a better power factor.

Fig.2.2 Rectifier with AC side inductor.(a) Schematic; Rectifier with AC-side inductor. (b)Line voltage, output voltage (upper plot) and line current (lower plot) with  $V_1$ =230Vrms 50Hz, resistive load R=500 $\Omega$ : C<sub>f</sub> =470 $\mu$ F, and L<sub>a</sub>=130mH. The line current has K<sub>p</sub>=0.8778, cos $\varphi$  =0.8758 and PF =0.7688.The output voltage is V<sub>2</sub> =257V; (c) Line current harmonics; (d) Variation of different parameters as a function of inductance.

#### 2.1.2 Rectifier with DC-side inductor:

The inductor can be also placed at the DC-side [5], as shown in Fig. 2.3(a) .The inductor current is continuous for a large value of inductance  $L_d$ . In the theoretical case of near infinite inductance, the inductor current is constant, so the input current of the rectifier has a square shape and the power factor is PF = 0.9, shown in Fig. 2.3(b). However, operation close to this condition would require a very large and impractical inductor, as illustrated by the simulated line current waveform for  $L_d = 3H$  (without Ca), shown in Fig. 2.3(b). For lower inductance  $L_d$ , the inductor current becomes discontinuous. The maximum power factor that can be obtained in such a case is PF = 0.78, the operating mode being identical to the case of the AC-side inductor previously discussed. An improvement of the power factor can be obtained by adding the capacitor Ca between the bridge rectifier and AC power supply as shown in Fig. 2.3(a), which compensates for the displacement factor  $\cos\Phi$ . A design for maximum purity factor Kp and unity displacement factor  $\cos\Phi$  is possible, leading to a maximum obtainable power factor PF = 0.9118. The simulation results for  $L_d = 275$ mH with and without  $C_a=4.8\mu$ F is shown in Fig. 2.3(c).

Fig.2.3 Rectifier with DC-side inductor. (a) Schematic; (b) Power factor Vs inductance without Ca; (c)Line voltage, output voltage (upper plot) and line current (lower plot) with  $V_1 = 230$ Vrms 50Hz, resistive load R=500 $\Omega$ : and C<sub>f</sub>=470 $\mu$ F. With La=275mH and without Ca, the line current has Kp = 0.8846, cos $\Phi$  = 0.9580 and PF = 0.8474, and the output voltage is V<sub>2</sub>= 210V. With La=275mH and with Ca=4.8 $\mu$ F,the line current has Kp=0.9128, cos $\Phi$ =0.9989 and PF=0.9118, and the output voltage is V<sub>2</sub>=231V. (d) Line current harmonics without C<sub>a</sub> and (e) with Ca respectively.

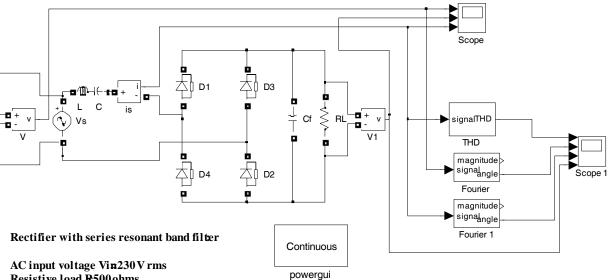

# 2.1.3 Rectifier with series-resonant band-pass filter:

A band-pass filter of the series-resonant type, tuned at the line-frequency, is introduced inbetween the AC source and the bridge rectifier as shown in Fig. 2.4 together with simulated waveforms [4, pp. 488-489]. By this method we can obtain almost unity power factor. For 50Hz networks, large values of the reactive elements are needed. Therefore, this solution is more practical for higher frequencies, such as for 400Hz and especially 20 kHz networks.

Fig.2.4 Rectifier with series-resonant band-pass filter. (a) Schematic; (b) Line current harmonics; (c) Line voltage, output voltage (upper plot) and line current (lower plot) with output voltage (red line) for V<sub>1</sub>=230Vrms 50Hz, resistive load R=500 $\Omega$ : C<sub>f</sub> =470 $\mu$ F, La=1.5H and Ca=6.75 $\mu$ F. The line current has K<sub>p</sub>=0.9937, cos $\Phi$ =0.9997 and PF=0.9934. The output voltage is V<sub>2</sub>=254V.

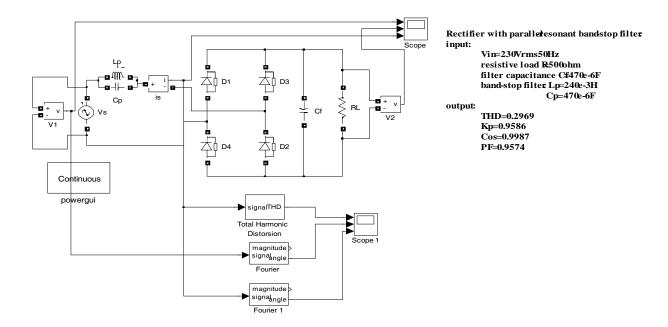

# 2.1.4 Rectifier with parallel-resonant band-stop filter:

The band-stop filter of the parallel-resonant type [6] is presented in Fig. 2.5 together with simulated waveforms. The filter is tuned at the third harmonic, hence it allows for lower values of the reactive elements when compared to the series-resonant band-pass filter.

Fig.2.5 Rectifier with parallel-resonant band-stop filter. (a) Schematic; (b) Line current harmonics; (c) Line voltage (upper plot) and line current (lower plot) with output voltage is the straight line for V<sub>1</sub>=230Vrms 50Hz, resistive load R=500 $\Omega$ : filter capacitance C<sub>f</sub>=470 $\mu$ F, band-stop filter components Lp=240mH, Cp=470 $\mu$ F tuned at third harmonic. Line current has Kp=0.9586,cos $\Phi$ =0.9987, and PF=0.9574. The output voltage is V<sub>2</sub>=266V.

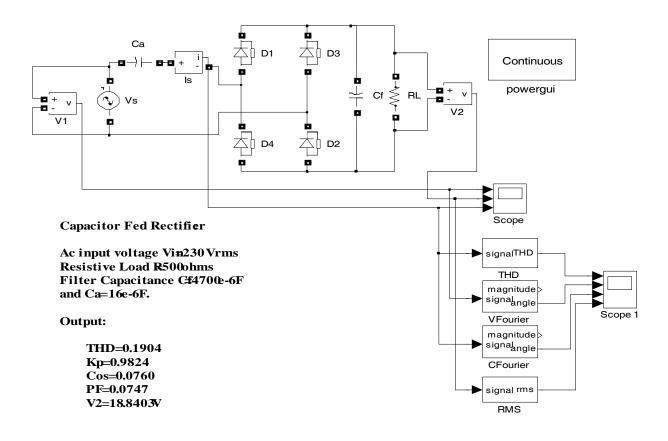

## 2.1.5 Capacitor-fed rectifier:

The capacitor-fed rectifier [7], shown in Fig. 2.6 together with simulated waveforms, is a very simple circuit that ensures compliance with standard IEC 1000-3-2 for up to approximately 250W input power at a  $230V_{rms}$  line voltage. The conversion ratio is a function of  $X_a/R$ , where  $X_a=1/(\omega_L C_a)$ . Therefore, it is possible to obtain a specific output voltage, which is nevertheless lower than the amplitude of the line voltage and strongly dependent on the load. Despite the harmonic current reduction, the power factor is extremely low. This is not due to current harmonics, but due to the series-connected capacitor that introduces a leading displacement factor  $cos\Phi$ . An advantage could be that the leading displacement factor  $cos\Phi$  can assist in compensating for lagging displacement factors elsewhere in the power system.

Fig.2.6 Capacitor-fed rectifier (a) Schematic; (b) Line current harmonics; (c) Line voltage, output voltage and line current (lower plot) with  $V_1$ =230Vrms 50Hz, resistive load R=500 $\Omega$ : C<sub>f</sub> =470 $\mu$ F, and Ca=16 $\mu$ F. The line current has Kp=0.9824, cos $\Phi$ =0.076 and PF=0.0747. The output voltage is  $V_2$ =12V, efficiency=3.5387.

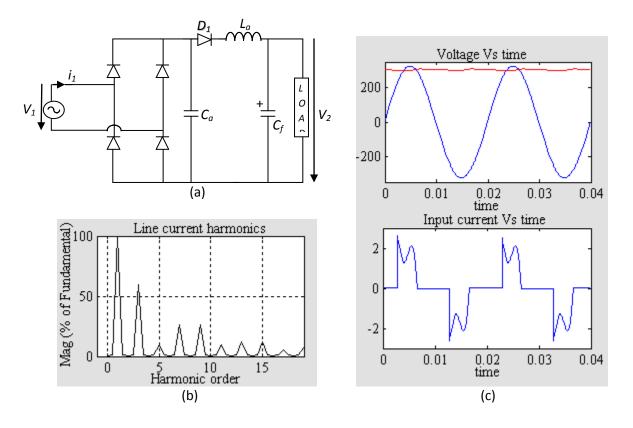

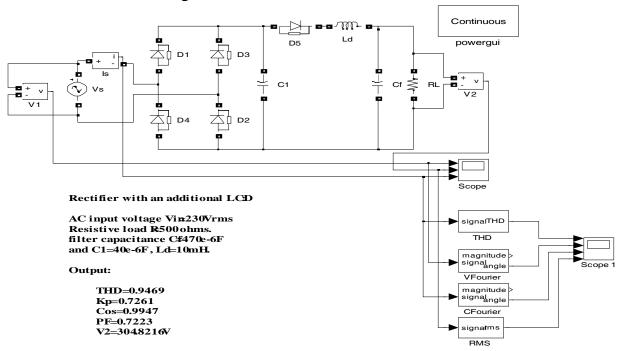

#### 2.1.6 Rectifier with an additional inductor, capacitor and diode (LCD):

The rectifier with an additional inductor, capacitor, and diode – LCD rectifier [8] – is shown in ig.2.7, together with simulated waveforms. The circuit can be used to about 300W. The added reactive elements have relatively low values. The idea behind the circuit is linked to the previous definition of Class-D of the Standard IEC 1000-3-2. The circuit changes the shape of the input current .Here the power-related to limits of Class-D were avoided and the absolute limits of Class-A could be met for low power, in spite of the line current being relatively-distorted.

Fig.2.7 Rectifier with an additional inductor, capacitor and diode (LCD). (a) Schematic; (b) Line current harmonics; (c) Line voltage, output voltage (upper plot) and line current (lower plot) with V<sub>1</sub>=230Vrms 50Hz, resistive load R=500 $\Omega$ ,C<sub>f</sub> =470 $\mu$ F, Ca=40 $\mu$ F, and La=10mH.The line current has Kp= 0.7261, cos $\Phi$ =0.9947 and PF=0.7223. The output voltage is V<sub>2</sub> =304V.

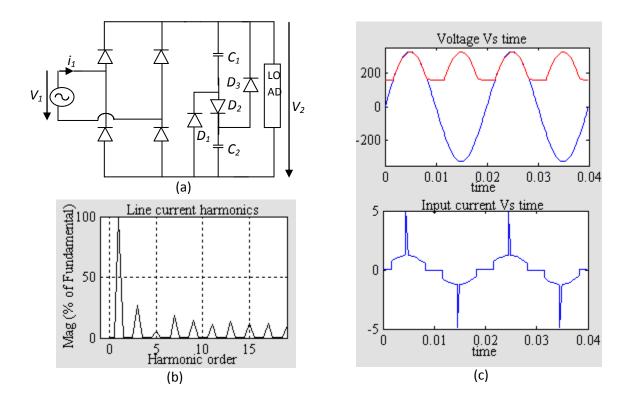

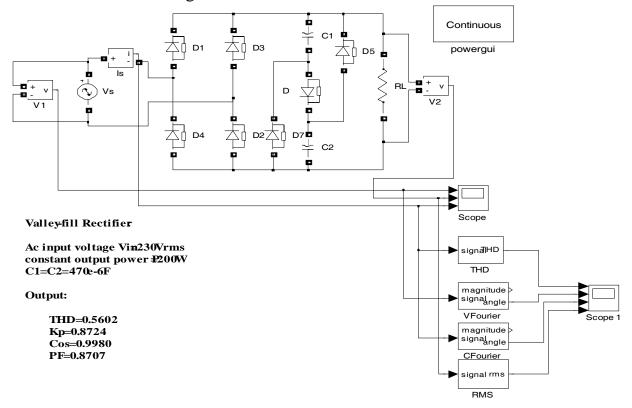

## 2.1.7 Valley-fill rectifier:

Most of the input current distortion is caused by the discontinuous operation which crosses from positive to negative, and then from negative to positive, during each cycle. Due to these discontinuities substantial amount of harmonics were introduced into the input current waveform. If this cross-over distortion can be lessened or eliminated, then the likelihood of using this circuit to meet the IEC specifications would be very high. To maintain the flow of input current, a voltage doublers is inserted to feed the valley-fill circuit [10]. The current response can further be improved by the insertion of another resistor  $R_1$ . Insertion of this resistor will remove the charging spike at the cross-over points, and further enhance the quality of the input current.

Fig.2.8 Valley-fill rectifier: (a) Schematic; (b) Line current harmonics; (c) Line voltage, output voltage, and line current with V<sub>1</sub>=230Vrms 50Hz, resistive load R=500 $\Omega$ :and C<sub>1</sub>=C<sub>2</sub>=470 $\mu$ F. The line current has Kp=0.8724, cos $\Phi$ =0.998 and PF=0.8707. The output voltage ripple is  $\Delta$ V<sub>2</sub>=168V, efficiency=0.3791.

#### 2.2 Advantages Of Passive PFC:

Passive power factor correctors have certain advantages, such as:

- 1. Simplicity.

- 2. Reliability.

- 3. Ruggedness.

- 4. Insensitive to noises and surges.

- 5. No generation of high-frequency EMI.

- 6. No high-frequency switching losses.

## 2.3 Disadvantages Of Passive PFC:

On the other hand, they also have several drawbacks:

1. They have poor dynamic response.

2. Solutions based on filters are heavy and bulky, because line-frequency reactive components are used.

3. Lack voltage regulation and the shape of their input current depend on the load. Even though line current harmonics are reduced, the fundamental component may show an excessive phase shift that reduces the power factor.

Better characteristics are obtained with active PFC circuits, which are reviewed in the next chapter.

# **Summary:**