# Archvied in Dspace@nitr

http://dspace.nitrkl.ac.in/dspace

# DEVELOPMENT OF LOW POWER IMAGE COMPRESSION TECHNIQUES

Sunil Kumar Pattanaik

Department of Electronics & Communication Engineering National Institute of Technology Rourkela

# DEVELOPMENT OF LOW POWER IMAGE COMPRESSION TECHNIQUES

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Technology (Research) in Electronics & Communication Engineering

Ву

Sunil Kumar Pattanaik

Roll No: 60407004

Under the supervision of

Dr. Kamala Kanta Mahapatra Professor

Department of Electronics & Communication Engineering National Institute of Technology Rourkela May, 2006

Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA ORISSA, INDIA – 769 008

### **CERTIFICATE**

This is to certify that the thesis titled "*Development of Low Power Image Compression techniques*", submitted to the National Institute of Technology, Rourkela by **Mr. Sunil Kumar Pattanaik**, Roll No. **60407004** for the award of the degree of Master of Technology (Research) in Electronics & Communication Engineering, is a bona fide record of research work carried out by him under my supervision and guidance.

The candidate has fulfilled all the prescribed requirements.

The thesis, which is based on candidate's own work, has not been submitted elsewhere for a degree/diploma.

In my opinion, the thesis is of standard required for the award of a Master of Technology (Research) degree in Electronics & Communication Engineering.

To the best of my knowledge, he bears a good moral character and decent behavior.

Prof. K. K. Mahapatra Department of Electronics & Communication Engineering National Institute of Technology Rourkela-769 008 (INDIA) Email: kkm@nitrkl.ac.in

# Dedicated

# to

# my Grand Parents

# **BIO-DATA OF THE CANDIDATE**

| Name of the Candidate | : | Sunil Kumar Pattanaik                                                   |

|-----------------------|---|-------------------------------------------------------------------------|

| Father's Name         | : | Purna Chandra Pattanaik                                                 |

| Permanent Address     | : | Gajapati Marga<br>At/po: Hinjilicut<br>Dist: Ganjam<br>Orissa<br>761102 |

| Email ID              | : | pattanaiksunil@yahoo.co.in                                              |

## ACADEMIC QUALIFICATION

- Continuing M. Tech. (Research) in Electronics & Communication Engineering, National Institute of Technology Rourkela, Orissa (INDIA).

- M.Sc. in Electronics, Berhampur University, Orissa (INDIA).

- P.G.D.C.A, Pondicherry University, (INDIA)

- B. Sc. Science College Hinjilicut, *Berhampur University*, Orissa (INDIA).

## PUBLICATION

- Published/Accepted 05 papers in National and International Conferences;

- Communicated 02 papers to International Journals.

## ACKNOWLEDGEMENT

I would like to take this opportunity to extend my deepest gratitude to my teacher and supervisor, Prof. K. K. Mahapatra, for his continuous encouragement and active guidance. I am indebted to him for the valuable time he has spared for me during this work. He is always there to meet and talk about my ideas, to proofread and mark up my research papers and chapters, and to ask me good questions to help me think through my problems.

I am very much thankful to Prof. G. Panda, for his continuous encouragement. Also, I am indebted to him who provided me all official and laboratory facilities.

I am grateful to Dr. S. Meher and Prof. T.K. Dan for his valuable suggestions and comments during this research period.

My sincere thanks go to Prof. G.S. Rath, Dr. S.K. Patra, Prof. S. Pramanik, Dr. B. Majhi, and Prof. B.D. Sahoo whose valuable suggestions helped me a lot in completing this thesis.

I would like to thank Dr. Debi Prasad Das, Scientist, CEERI, Pilani for his kind support during the on period of my thesis work. In addition, let me thank all my friends Saroj, Pankaj, Rana babu, Sushant, Manas, Vamsi, Alekhika, Babita Madam, Sabuj, Debi, Nilamani sir, Jitendra sir and Peter for their great support and encouragement during the research period. Also, I am thankful to all the non-teaching staffs of ECE Department for their kind cooperation.

During the course of this work, I am supported by a project VLSI-SMDP sponsored by DIT, Govt. of India. I am really thankful to them.

Last but not the least, I take this opportunity to express my regards and obligation to my parents and family members for educating me in all expects. I can never forget for their unconditional support and encouragement to pursue my interests.

Sunil Kumar Pattanaik

# LIST OF ABBREVIATIONS

| AC   | Arithmetic Compression             |

|------|------------------------------------|

| ANN  | Artificial Neural Network          |

| CR   | Compression Ratio                  |

| DCT  | Discrete Cosine Transform          |

| DHT  | Discrete Hartley Transform         |

| DPCM | differential pulse code modulation |

| DWT  | Discrete Wavelet Transform         |

| EQ   | Energy Quantisation                |

| FPGA | Field Programmable Gate Array      |

| JPEG | Join Picture Expert Group          |

| MEQ  | Modified Energy Quantisation       |

| MLP  | Multi-Layer Perceptron             |

| MPEG | Moving Pictures Experts Group      |

| MSE  | Mean Square Error                  |

| PSNR | Peak Signal to Noise Ratio         |

| RBEQ | Rule Based Energy Quantisation     |

| RBF  | Radial Basis Function              |

| SNR  | Signal to Noise Ratio              |

| VLC  | Variable Length Code               |

| VLSI | Very Large Scale Integration       |

| VQ   | Vector Quantisation                |

|      |                                    |

# LIST OF FIGURES

| Figure<br>Number | Title                                                                                      | Page |

|------------------|--------------------------------------------------------------------------------------------|------|

| 1.1              | Image Compression System                                                                   | 3    |

| 1.2              | Image Decompression System                                                                 | 4    |

| 1.3              | Block Diagram of Transform Loop                                                            | 6    |

| 1.4              | Limits of an Arithmetic Coder                                                              | 10   |

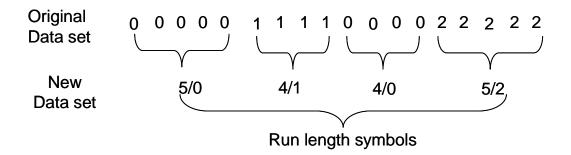

| 1.5              | Diagram Illustrating the Run Length Coder                                                  | 11   |

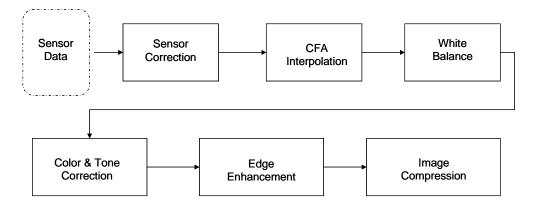

| 1.6              | Digital Image Processing steps in a Digital Camera                                         | 14   |

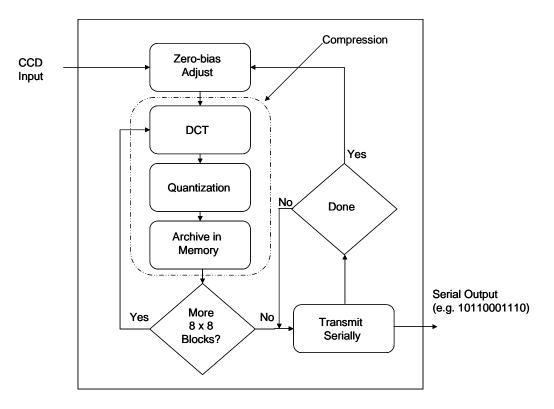

| 1.7              | Functional block-diagram specification of a digital camera                                 | 17   |

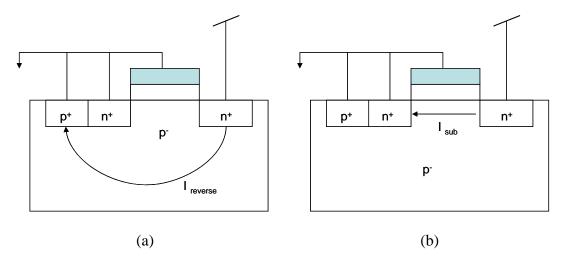

| 2.1              | Leakage current types: (a) reverse biased diode current, (b) subthreshold leakage current. | 23   |

| 2.2              | Low-power design methodology at different abstraction levels                               | 25   |

| 2.3              | Clock Gating                                                                               | 26   |

| 2.4              | Asynchronous design with dynamic voltage scaling.                                          | 26   |

| 2.5              | (a) Original signal flow graph. (b) Unrolled signal flow graph.                            | 27   |

| 2.6              | Original Data Path                                                                         | 28   |

| 2.7              | Parallel Implementation                                                                    | 29   |

| 2.8              | Pipelining Implementation                                                                  | 29   |

| 2.9              | A precomputaiton structure for low power                                                   | 30   |

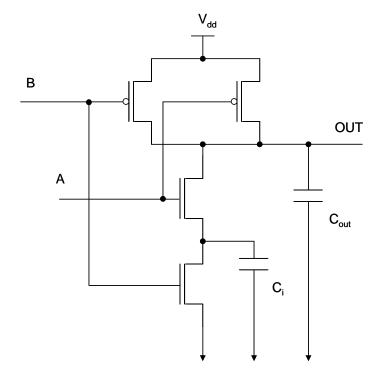

| 2.10             | A two input NAND gate                                                                      | 33   |

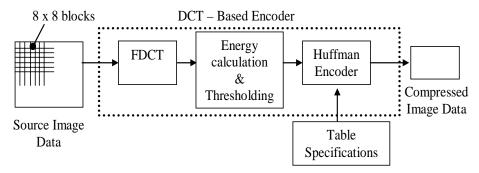

| 3.1              | JPEG Encoder                                                                               | 36   |

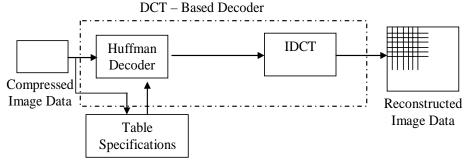

| 3.2              | JPEG Decoder                                                                               | 37   |

| 3.3              | JPEG Quantiser                                                                             | 40   |

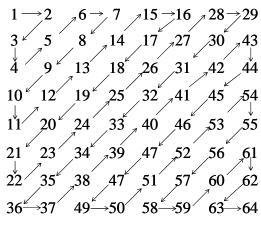

| 3.4              | Zigzag Scanning                                                                            | 41   |

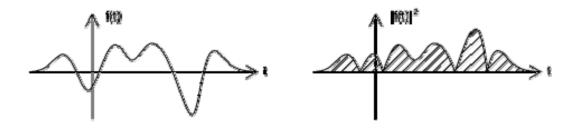

| 3.5              | Original Signal $f(t)$ and Energy signal $ f(t) ^2$                                        | 42   |

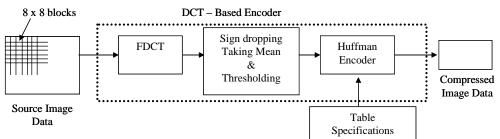

| 3.6              | Energy Quantisation based Image Compression Encoder                                        | 43   |

| 3.7              | Energy Quantisation Decoding and Encoding example                                          | 44   |

| 3.8              | Energy Quantisation based Image Compression Decode                                         | 45   |

| 3.9              | Modified Energy Quantisation based Image Compression Decoder                               | 45   |

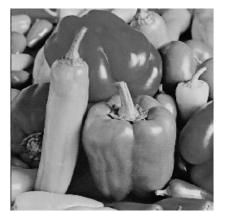

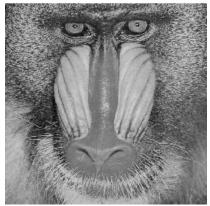

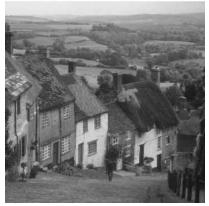

| 3.10             | Standard (512x512) test images used for testing the proposed algorithms                    | 48   |

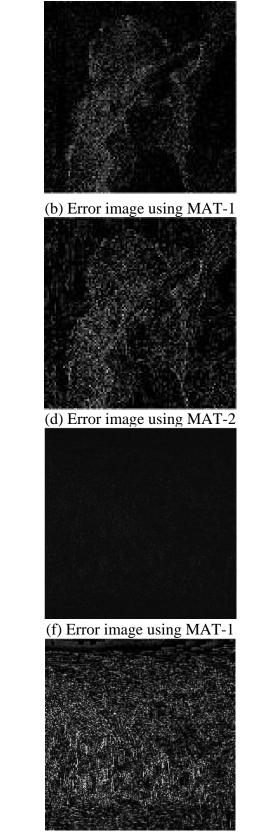

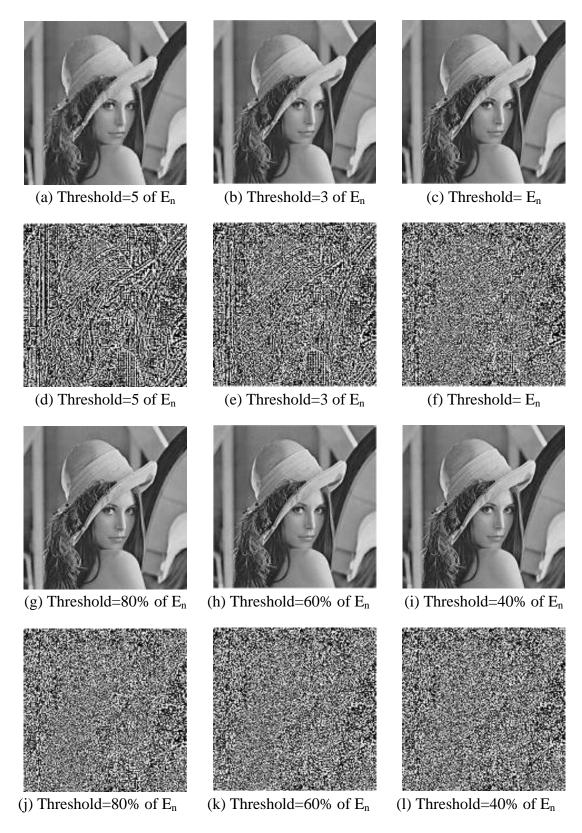

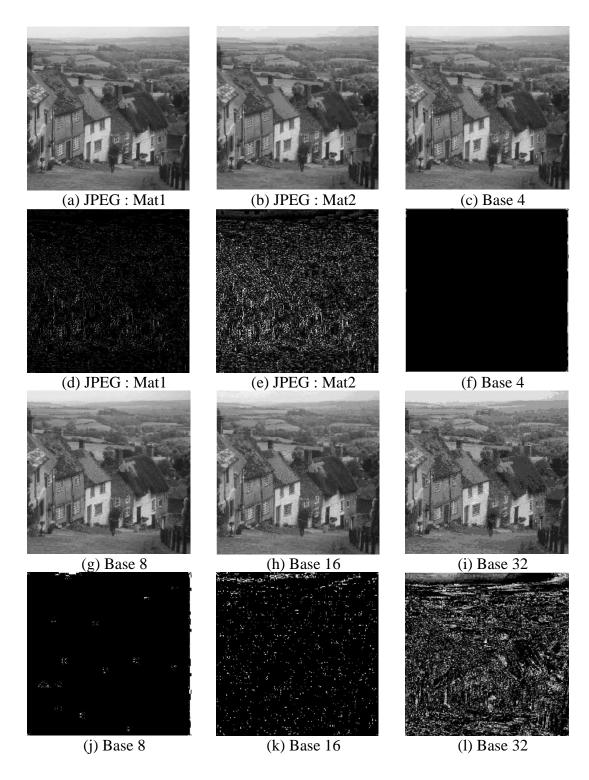

| 3.11 | Reconstructed image and error images of JPEG quantisation technique         | 50 |

|------|-----------------------------------------------------------------------------|----|

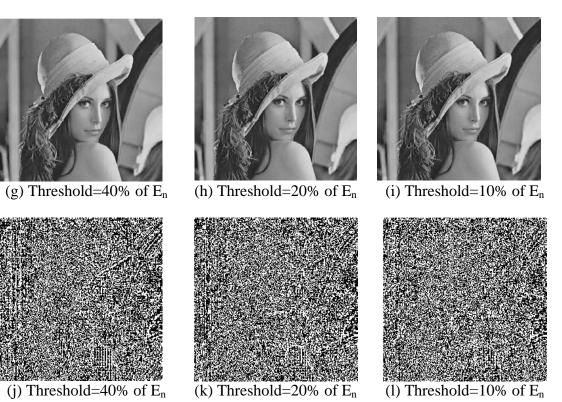

| 3.12 | Reconstructed image and error images of EQ technique                        | 51 |

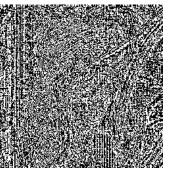

| 3.13 | Reconstructed image and error images of MEQ technique                       | 52 |

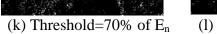

| 3.14 | Reconstructed image and error images of RBEQ technique                      | 53 |

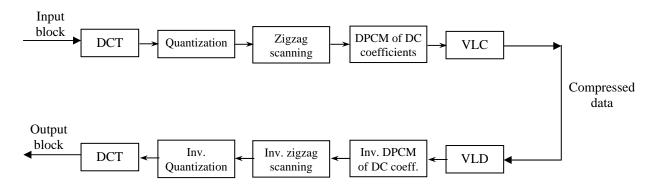

| 4.1  | Schematic block diagram of the conventional JPEG scheme of data compression | 55 |

| 4.2  | Scanning order of DHT coefficient                                           | 57 |

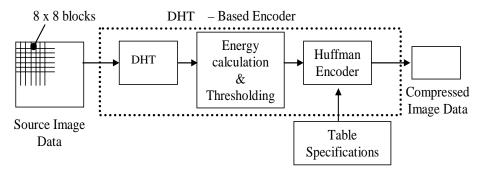

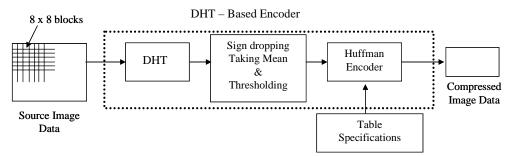

| 4.3  | Energy Quantisation based Image Compression Encoder                         | 61 |

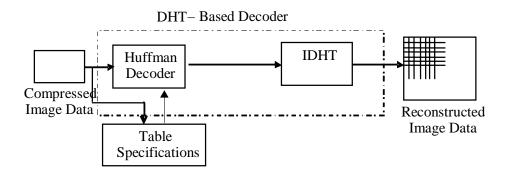

| 4.4  | Energy Quantisation based Image Compression Decoder                         | 61 |

| 4.5  | Modified Energy Quantisation based Image Compression Decoder                | 62 |

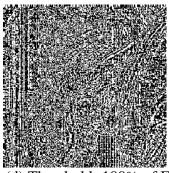

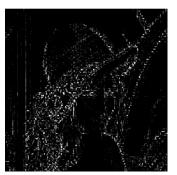

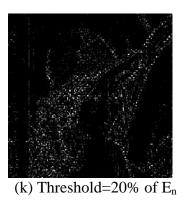

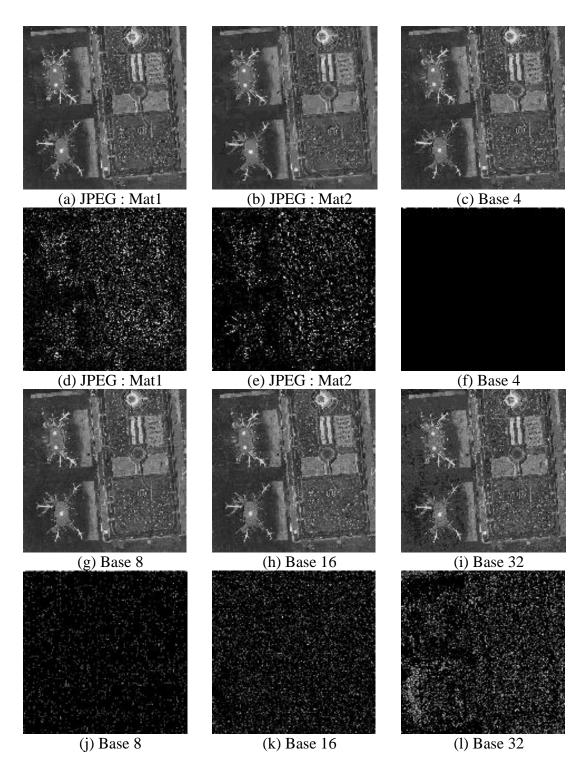

| 4.6  | Reconstructed image and error images of EQ technique                        | 66 |

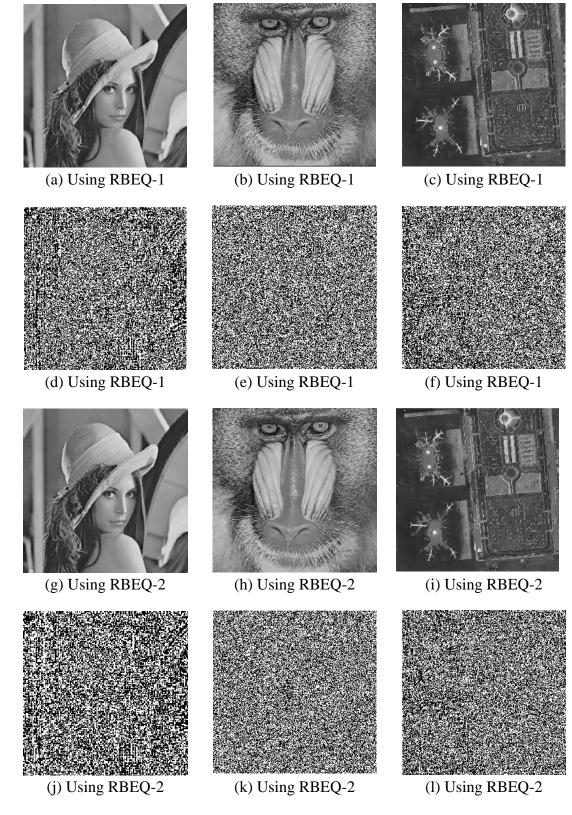

| 4.7  | Reconstructed image and error images of MEQ technique                       | 67 |

| 4.8  | Reconstructed image and error images of RBEQ technique                      | 68 |

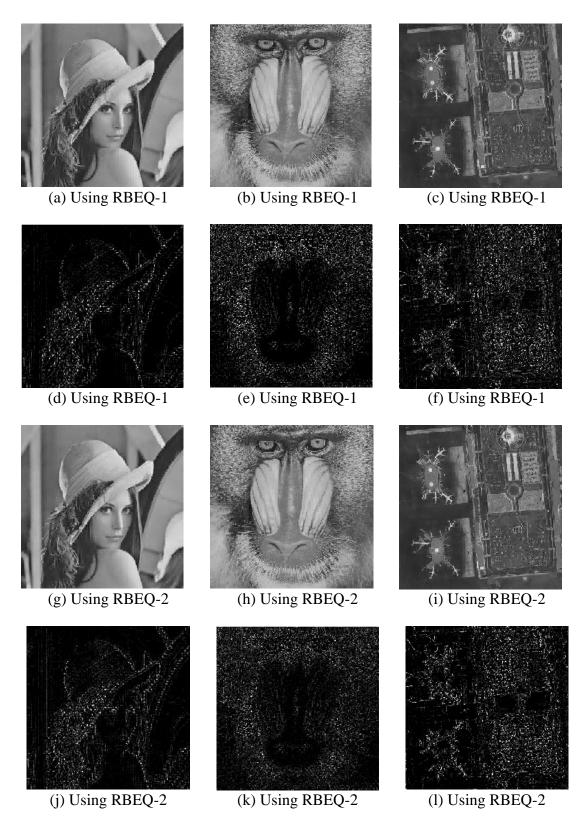

| 5.1  | Schematic Diagram of Arithmetic Compression (AC) System                     | 71 |

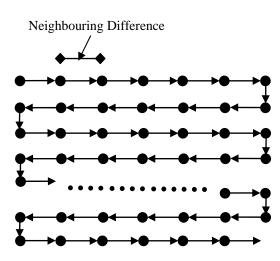

| 5.2  | Snake Scanning                                                              | 72 |

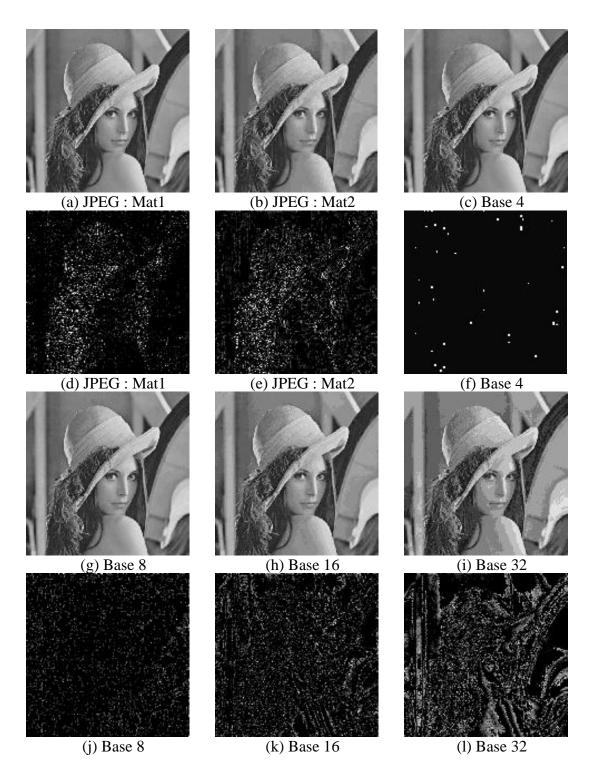

| 5.3  | Arithmetic Compression Simulation Results of LENA Image                     | 74 |

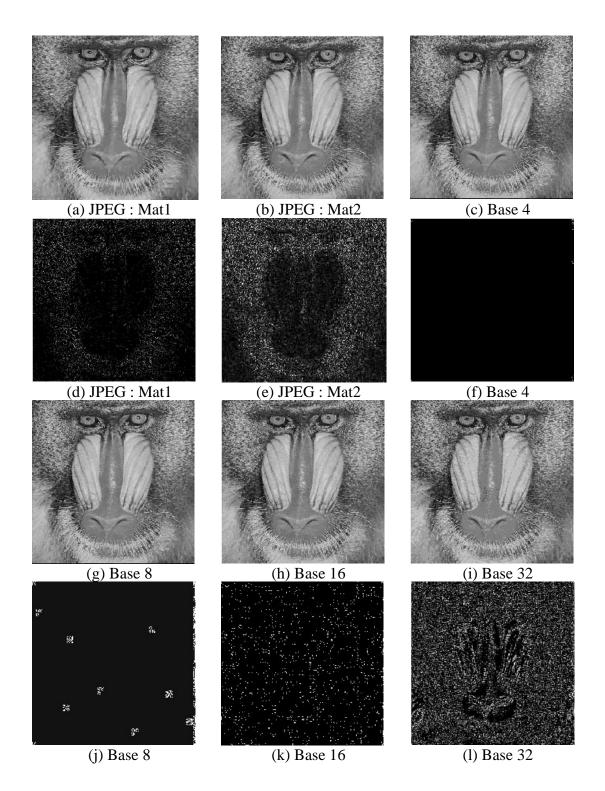

| 5.4  | Arithmetic Compression Simulation Results of Babbon Image                   | 75 |

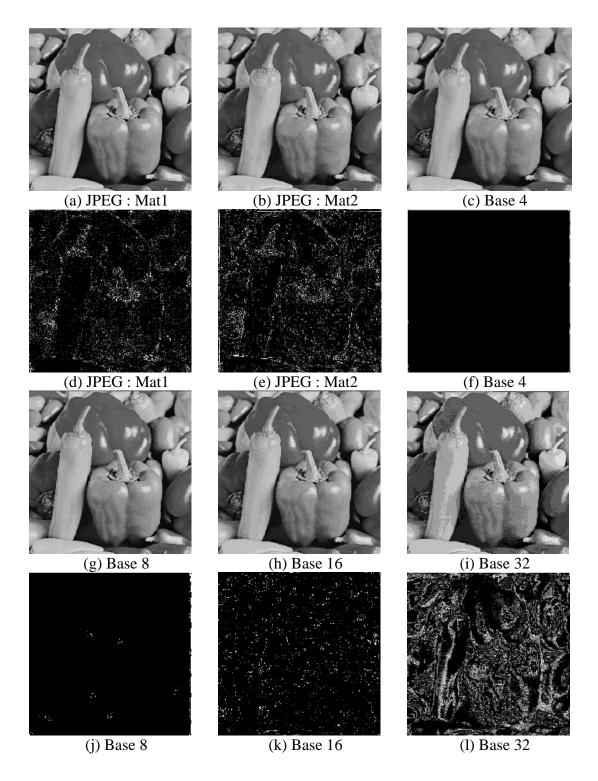

| 5.5  | Arithmetic Compression Simulation Results of Peppers Image                  | 76 |

| 5.6  | Arithmetic Compression Simulation Results of Gold Hill Image                | 77 |

| 5.7  | Arithmetic Compression Simulation Results of Airport Image                  | 78 |

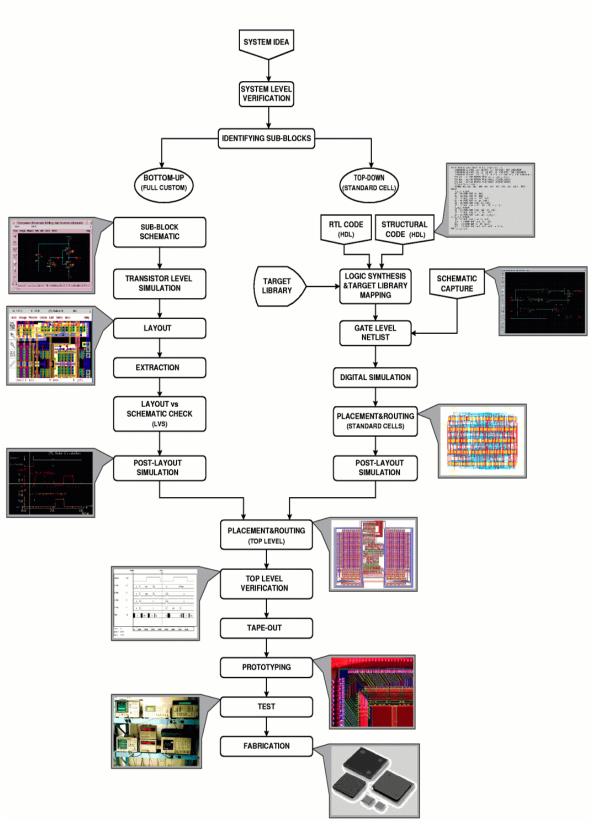

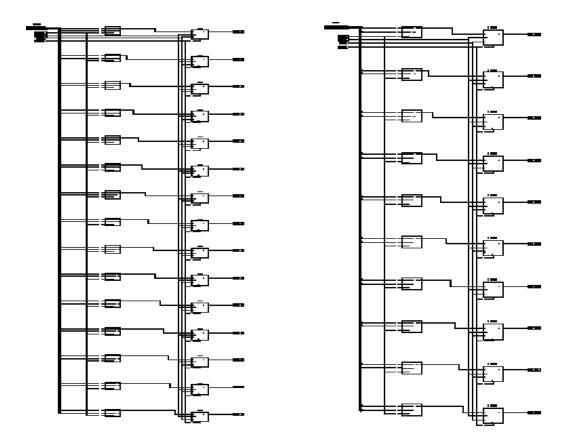

| 6.1  | Steps involved in VLSI designing                                            | 84 |

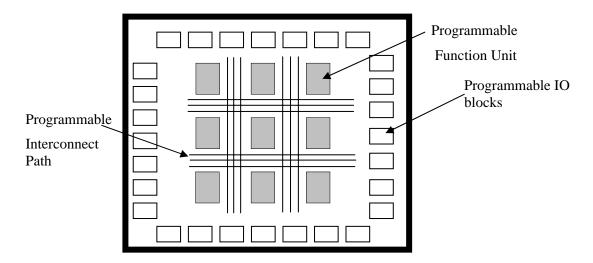

| 6.2  | Internal Structure of an FPGA                                               | 85 |

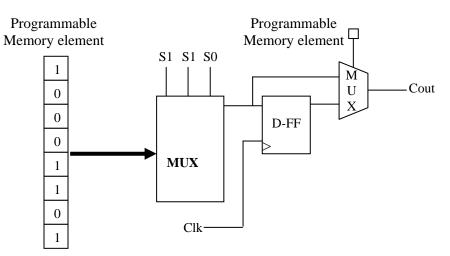

| 6.3  | Building block in basic cell design                                         | 86 |

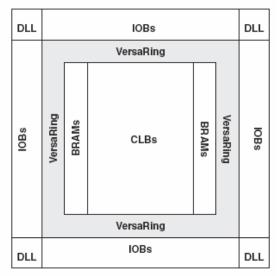

| 6.4  | Virtex Architecture                                                         | 87 |

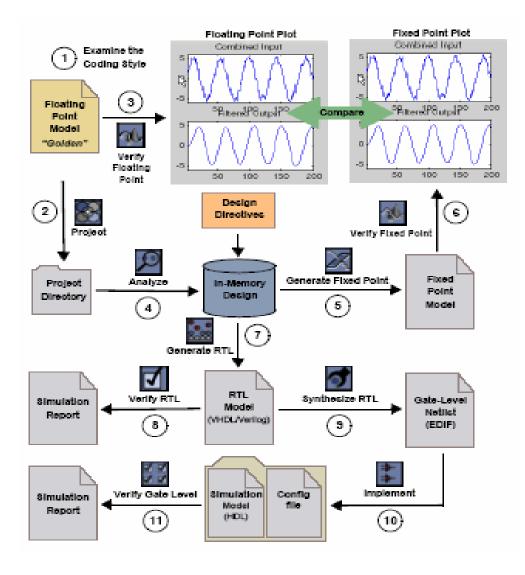

| 6.5  | AccelChip DSP Synthesis Flow                                                | 90 |

## ABSTRACT

Digital camera is the main medium for digital photography. The basic operation performed by a simple digital camera is, to convert the light energy to electrical energy, then the energy is converted to digital format and a compression algorithm is used to reduce memory requirement for storing the image. This compression algorithm is frequently called for capturing and storing the images. This leads us to develop an efficient compression algorithm which will give the same result as that of the existing algorithms with low power consumption. As a result the new algorithm implemented camera can be used for capturing more images then the previous one.

1) Discrete Cosine Transform (DCT) based JPEG is an accepted standard for lossy compression of still image. Quantisation is mainly responsible for the amount loss in the image quality in the process of lossy compression. A new Energy Quantisation (EQ) method proposed for speeding up the coding and decoding procedure while preserving image quality. Some of the high frequency components of the transformed sub image are preserved in accordance to the quantisation value. There is no need of a dequantiser at the decoder side. This would enable reduction of hardware and would make the implementation much simpler. The proposed EQ method is modified and two new quatisation techniques Modified Energy Quantisation (MEQ) and Rule Based Energy Quantisation (RBEQ) proposed to further reduce the hardware requirement.

2) DCT and IDCT are used for the coding and decoding of the image. Calculations of both are independent to each other, so there is a need of two different hardware. Where as in case of DHT transform the forward and inverse transforms are same except a scale factor in the inverse transform. As a result the hardware requirement to compute both the forward and inverse DHT is approximately reduced by 50% as those of the DCT and IDCT.

3) All the Energy Quantisation techniques proposed are applied to further reduce the complexity of DHT based JPEG compression technique.

4) A new simple arithmetic compression technique is proposed for lossless compression. The computational complexity is very less compare to previous techniques.

5) All the image compression techniques proposed are synthesised for Virtex XCV1000 device for the testing and verification of low complexity and hence low power. DHT based JPEG with rule based energy quantisation is an ideal solution for lossy image compression technique as the hardware requirement is less and power consumption is very low compare to other techniques.

# Contents

#### Certificate

Bio-data of the Candidate

Acknowledgement

List of Abbreviations

List of Figures

## **CHAPTER 1: Introduction**

|     | Preamble                             |                                        | 1  |

|-----|--------------------------------------|----------------------------------------|----|

| 1.1 | Image Compression and Reconstruction |                                        |    |

|     | 1.1.1                                | Transformations                        | 4  |

|     | 1.1.2                                | Quantisation                           | 7  |

|     | 1.1.3                                | Lossless coding                        | 8  |

| 1.2 | Performa                             | nce measures of Image Compression      | 12 |

| 1.3 | Digital C                            | amera Fundamentals                     | 13 |

|     | 1.3.1                                | Requirements specification             | 16 |

|     | 1.3.2                                | Nonfunctional Requirement              | 16 |

|     | 1.3.3                                | Functional Requirement                 | 17 |

| 1.4 | Motivatio                            | on                                     | 18 |

| 1.5 | Literature Survey 1                  |                                        | 18 |

| 1.6 | Chapter-                             | wise Organization                      | 19 |

|     | CHAPT                                | ER 2: Low Power VLSI Design Techniques |    |

|     | Preamble                             |                                        | 21 |

| 2.1 | Power Di                             | issipation Sources                     | 22 |

| 2.1.1 | Short-Circuit Power | 22 |

|-------|---------------------|----|

| 2.1.2 | Leakage Power       | 23 |

| 2.1.3 | Switching Power     | 24 |

| 2.2 | 2 Low Power Techniques |                    | 24 |

|-----|------------------------|--------------------|----|

|     | 2.2.1                  | System Level       | 25 |

|     | 2.2.2                  | Algorithm Level    | 26 |

|     | 2.2.3                  | Architecture Level | 27 |

|     | 2.2.4                  | Logic Level        | 30 |

|     | 2.2.5                  | Circuit Level      | 32 |

| 2.3 | Summ                   | ary                | 34 |

# CHAPTER-3: Image Compression Using Discrete Cosine Transform

|     | Preamble                                                | 35 |

|-----|---------------------------------------------------------|----|

| 3.1 | JPEG Compression                                        | 36 |

|     | 3.1.1 Discrete Cosine Transform (DCT)                   | 37 |

|     | 3.1.2 Quantisation                                      | 39 |

|     | 3.1.3 Coding                                            | 41 |

| 3.2 | Signal Energy                                           | 42 |

| 3.3 | Energy Quantisation (EQ)                                | 42 |

|     | 3.3.1 Technique-1: Energy Quantisation (EQ)             | 42 |

|     | 3.3.2 Technique-II : Modified Energy Quantisation (MEQ) | 45 |

|     | 3.3.3 Rule Based Energy Quantisation (RBEQ)             | 46 |

| 3.4 | Simulation Results                                      | 47 |

| 3.5 | Summary                                                 | 54 |

|     | CHAPTER-4: Hartley Transform Based JPEG                 |    |

|     | Preamble                                                | 55 |

| 4.1 | JPEG Baseline Algorithm                                 | 55 |

|     | 4.1.1 DCT computation                                   | 55 |

|     | 4.1.2 Quantisation of the DCT coefficients              | 56 |

|     | 4.1.3 Coding of the quantised coefficients              | 56 |

|     | 4.1.4 Reconstruction of the original image              | 56 |

| 4.2 | Motivation                                              | 57 |

| 4.3 | Discrete Hartley Transform (DHT)                            | 58 |

|-----|-------------------------------------------------------------|----|

|     | 4.3.1 1D DHT                                                | 58 |

|     | 4.3.2 2D DHT                                                | 59 |

| 4.4 | Energy Quantisation                                         | 60 |

|     | 4.4.1 Technique-1: Energy Quantisation (EQ)                 | 60 |

|     | 4.4.2 Technique-II : Modified Energy Quantisation (MEQ)     | 62 |

|     | 4.4.3 Rule Based Energy Quantisation (RBEQ)                 | 63 |

| 4.5 | Simulation Results                                          | 64 |

| 4.6 | Summary                                                     | 69 |

|     |                                                             |    |

|     | CHAPTER-5: Arithmetic Lossless Compression Technique        |    |

|     | Preamble                                                    | 70 |

| 5.1 | Arithmetic Compression (AC)                                 | 71 |

|     | 5.1.1 Forward Arithmetic Compression Algorithm              | 72 |

|     | 5.1.2 Forward Arithmetic Compression Algorithm              | 73 |

| 5.2 | Simulation Results                                          | 73 |

| 5.3 | Summary                                                     | 79 |

|     |                                                             |    |

|     | CHAPTER-6: FPGA Implementation of the compression techiques |    |

|     | Preamble                                                    | 80 |

| 6.1 | VLSI Overview and Reconfigurable Computing                  | 80 |

|     | 6.1.1 Advantages of Using ASIC                              | 81 |

|     | 6.1.2 Major Risks of Using ASIC                             | 82 |

| 6.2 | VLSI Design Methodologies                                   | 82 |

| 6.3 | FPGA Devices                                                | 85 |

|     | 6.3.1 Selection of FPGA deice                               | 86 |

| 6.4 | Introduction to AccelChip                                   | 88 |

|     | 6.4.1 AccelChip DSP Synthesis Flow                          | 88 |

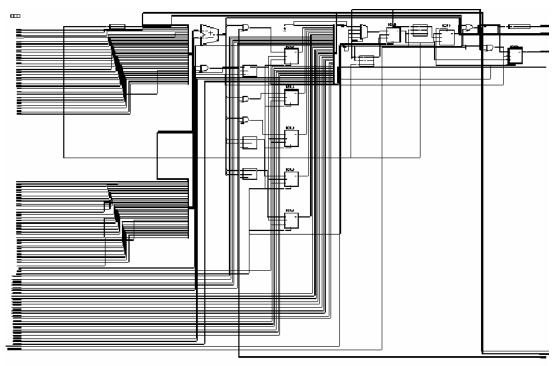

| 6.5 | Simulation Results                                          | 90 |

| 6.6 | Summary                                                     | 92 |

## **CHAPTER-7:** Conclusion

|     | Preamble                                 | 93 |

|-----|------------------------------------------|----|

| 7.1 | Achievements and Limitations of the work | 93 |

| 7.2 | Further Development                      | 95 |

## Bibliography

LOW POWER Image Compression Techniques

# Introduction

Data compression is the process of converting data files into smaller files for efficiency of storage and transmission. As one of the enabling technologies of the multimedia revolution, data compression is a key to rapid progress being made in information technology. The digital data have become an important source of information in the present world of communication systems. In this Internet age the power of the digital images to convey information as compared to the text data is obvious to all. This power of the images can be accessible and possible through the digital technology that enhances through its ability to process, transmit and reproduce with unparalleled faithfulness to the original images. It would not be practical to put images, audio, and video alone on websites without compression.

What is data compression? And why do we need it? Many people may have heard of JPEG (Joint Photographic Experts Group) and MPEG (Moving Pictures Experts Group), which are standards for representing images and video. Data compression algorithms are used in those standards to reduce the number of bits required to represent an image or a video sequence. Compression is the process of representing information in a compact form. Data compression treats information in digital form, which is, as binary numbers represented by bytes of data with very large data sets. Fox example, a single small 4" x 4" size color picture, scanned at 300 dots per inch (dpi) with 24 bits/pixel of true color, will produce a file containing more than 4 megabytes of data. At least three floppy disks are required to store such a picture. This picture requires more than one minute for transmission by a typical transmission line (64k bit/second ISDN). That is why large image files remain a major bottleneck in a distributed environment. Although increasing the bandwidth is a possible solution, the relatively high cost makes this less attractive. Therefore, compression is a necessary and essential method for creating image files with manageable and transmittable sizes.

Data and information are not the same thing rather the data are the means by which the information is conveyed. Thus while conveying the same information by different formats of the data, there is every possibility that some data are common between the ways of representing the information and can be removed as redundant. The basic motive behind the data compression is to search for such redundancy and then to remove them faithfully without compromising with the quality of the reconstructed data. Mathematically the concept of redundancy may be expressed as follows:

If  $n_1$  and  $n_2$  denote the number of information–carrying units in two data sets which represents the same information, the relative data redundancy  $R_D$  of the first data set (the one characterized by  $n_1$ ) can be defined as

$$R_D = 1 - \frac{1}{C_R} \tag{1.1}$$

where  $C_R$ , commonly called the compression ratio, is

$$C_R = \frac{n_1}{n_2} \tag{1.2}$$

For the case of  $n_1 = n_2$ ,  $C_R = 1$  and  $R_D = 0$ , indicating that the first representation of the information contains no redundant data. When  $n_2 << n_1, C_R \rightarrow \infty$  and  $R_D \rightarrow 1$ , signifies that highly redundant data. When  $n_2 >> n_1, C_R \rightarrow 0$  and  $R_D \rightarrow -\infty$ , indicates that the second data set contains much more data than the original representation. Generally a  $C_R = 10$  (or 10:1) defines that the first data set has 10 information carrying units for every 1 unit in the second or compressed data set. Thus corresponding redundancy of 0.9 means 90 percent of the data in the first data set is redundant with respect to the second one.

In order to be useful, a compression algorithm has a corresponding decompression algorithm that reproduces the original file once the compressed file is given. There have been many types of compression algorithms developed. These algorithms fall into two broad types, lossless algorithms and lossy algorithms. A lossless algorithm reproduces the data exactly same as the original one. A lossy algorithm, as its name implies, loses some data. Data loss may be unacceptable in many applications. For example, text compression must be lossless because a very small difference can result in statements with totally different meanings. There are also many situations where loss may be either unnoticeable or acceptable. In image compression, for example, the exact reconstructed value of each sample of the image

is not necessary. Depending on the quality required of the reconstructed image, varying amounts of loss of information can be accepted.

## **1.1 Image Compression and Reconstruction**

Three basic data redundancies can be categorized in the image compression standard.

- 1. Spatial redundancy due to the correlation between neighboring pixels.

- 2. Spectral redundancy due to correlation between the color components.

- 3. Psycho-visual redundancy due to properties of the human visual system.

The spatial and spectral redundancies are present because certain spatial and spectral patterns between the pixels and the color components are common to each other, whereas the psycho-visual redundancy originates from the fact that the human eye is insensitive to certain spatial frequencies. The principle of image compression algorithms are (i) reducing the redundancy in the image data and (or) (ii) producing a reconstructed image from the original image with the introduction of error that is insignificant to the intended applications. The aim here is to obtain an acceptable representation of digital image while preserving the essential information contained in that particular data set.

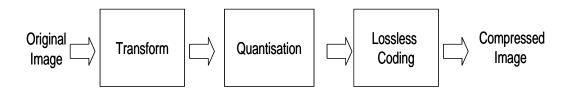

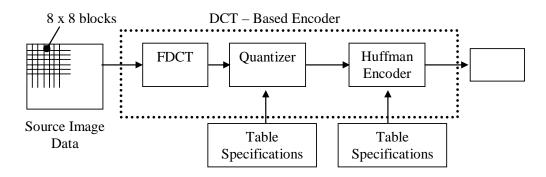

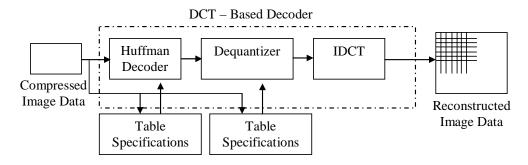

Figure 1.1: Image Compression System

The problem faced by image compression is very easy to define, as demonstrated in figure 1.1. First the original digital image is usually transformed into another domain, where it is highly de-correlated by using some transform. This de-correlation concentrates the important image information into a more compact form. The compressor then removes the redundancy in the transformed image and stores it into a compressed file or data stream. In the second stage, the quantisation block reduces the accuracy of the transformed output in accordance with some preestablished fidelity criterion. Also this stage reduces the psycho-visual redundancy of the input image. Quantisation operation is a reversible process and thus may be omitted when there is a need of error free or lossless compression. In the final stage of the data compression model the symbol coder creates a fixed or variable-length code to represent the quantiser output and maps the output in accordance with the code. Generally a variable-length code is used to represent the mapped and quantised data set. It assigns the shortest code words to the most frequently occurring output values and thus reduces coding redundancy. The operation in fact is a reversible one.

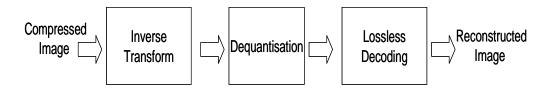

The decompression reverses the compression process to produce the recovered image as shown in figure 1.2. The recovered image may have lost some information due to the compression, and may have an error or distortion compared to the original image.

Figure 1.2: Image Decompression System

### 1.1.1 Transforms

The first stage in an image compressor is the transform. Transformation of the image data is required to convert the image into a domain where it is easier to compress. A transform operates on an image's pixel intensities and converts them into a set of transform coefficients. Natural images (which are the most common images to be compressed) have a lot of spatial correlation between pixel intensities, and these correlations can be exploited by the transform. This is achieved by mapping similar large scale changes in the data onto single transform coefficients. This type of mapping causes the transformed image to become highly decorrelated and standard compression techniques can then be used to further compress the transform coefficients.

The general form of a spatial intensity transform used on the image data is shown by equation (1.3):

$$c(k,l) = \sum_{i} \sum_{j} h(f(i,j))$$

(1.3)

where c(k,l) is the transform coefficient, f(i, j) is the image pixel intensity array, h(f(i, j)) is the transform function. This equation shows that the transform coefficients are the sum of the effects of the transform on the pixel intensities, over the whole section of the image to be transformed.

The transform is rarely applied to the whole of the image. As the area of the image to which the transform has to be applied increases, the number of calculations also increases proportionally. This suggests that to keep the number of calculations small (and manageable), the area that the transform is applied to should be as small as possible. However, the decorrelation effects on the transform improve, when a larger area of the image is considered, and this in turn improves the compression performance.

In a real system a compromise is established between the compression and the speed of the transform. The effects of decorrelation are not linearly proportional to the area used so it is not possible to theoretically determine the best area to apply the transform to; it has to be done using practical results.

The image is broken into a sub-blocks and the transform is applied to each block separately. Each block then has a set of transform coefficients, which describe it. Although it has been stated that images are highly correlated, this is only true over local areas of the image. There may be little or no correlation between distant sections (100 pixels) of the image. Applying the transform to image blocks exploits the local similarity of the image without losing the benefits of decorrelation in the transform coefficients.

Transforming image blocks also introduces a blocking artifact effect, which can be a major problem. Since the coefficients that describe one block are not related to those describing the surrounding blocks, it is possible for discontinuities to occur along the block edge of compressed images. Blocking artifact is only visible at higher compression rates, in most systems, but can severely reduce the visual quality of a compressor, even if the rate distortion performance is still acceptable. The blocks that the image is broken into do not have to be a fixed size or shape, but they are generally non-overlapping.

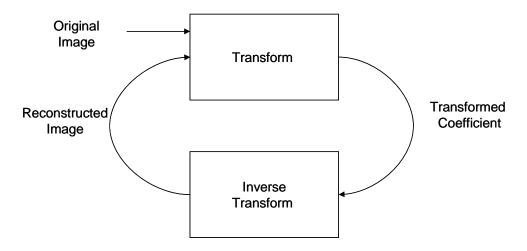

Transforms are generally formed in pairs so that the image can be reconstructed by applying the inverse transform. If the transforms are applied to an image without compression, then there are two possibilities, as shown in figure 1.3:

1. The transform is perfectly reconstructing and there is no error in the recovered image. This type of transform is often quite complex, since no data is lost and it can take a long time to compute.

2. The transform is "lossy" and information is lost on either the forward or inverse transform stage. These transforms can be useful, since they are very easy to calculate and often represent the image using a low number of transform coefficients. They produce a moderate compression without any further processing.

Figure 1.3: Block Diagram of Transform Loop

If the image is passed through the transform loop (figure 1.3) multiple times, then theoretically either lossless or lossy transforms should produce the same recovered error each time. However since lossy transforms often favour a variable block size method, it is not always the case that reapplying a codec to a recovered image (coded with the same codec) will produce the same result i.e. an image is coded many times it may never converge to a fixed result. This problem is cause for great concern in broadcast compression as images can be compressed many times after they are originally captured.

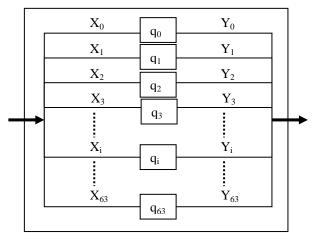

#### 1.1.2 Quantisation

The transform stage spatially decorrelates the spatial property of the image, but does not always produce compression. Quantisation relevant to image coding is discussed in this section and simplified to allow a general rule for the quantisation of transform image coefficients to be developed. Quantisation is the main stage in case of lossy image compression, where most of the image compression is achieved. Before quantisation a transform coefficient may take an infinite range of values, limited only by the accuracy of the medium it is stored in. After quantisation the transform coefficient will be represented by a number of discrete values. This could be represented as:

$$c_q = q \circ c \tag{1.4}$$

where q is the quantisation function, c is the transform coefficients and  $c_q = \{c_0, c_1, c_2, \dots, c_n\}$ .

Linear quantisation is the most basic form of quantisation. The transform coefficients are divided by a quantisation step and the result is converted to an integer, by truncation of the decimal point equation (1.5).

$$c_q = Integer(\frac{c_i}{q_i}) \tag{1.5}$$

where  $q_i$  is the quantisation step,  $c_i$  is the transform coefficient, and  $c_q$  is the integer quantised coefficients.

The transform data is limited based on the 8 bit pixel intensities of standard images. This allows a quantisation step to be chosen, which limits the number of quantised states available, hence compressing the coefficient to a desired number of bits. However, it is not possible to control compression in this way, since a real system losslessly codes the quantised coefficients and this operation is not well defined.

The choice of q can vary since some transform coefficients are more important than others and, as a result, a quantisation table (q(k,l)) is usually formed, providing different q values for each transform coefficient. How to choose q is quite difficult since there is no simple relationship between the compression and the value q takes.

#### 1.1.3 Lossless Coding

Lossless coding aims at reducing the redundant data, by exploiting its statistics. Theoretically this coding method should compress a data source without introducing any new errors into the data. It is possible to reduce the information required to store data to a theoretical minimum, by exploiting the 'blind' statistics of the data, without considering the order in which it is received. This is usually achieved with a Huffman coding [1 - 2], but arithmetic coding [1 - 2] can also be useful.

In lossless coding it is useful to refer the inputs as data symbols to be compressed and the output from the lossless coder as compressed symbols. The data symbols are usually quantised transform coefficients in image compression, but they can be anything, provided the coder has knowledge of their statistics.

#### 1.1.3.1 Entropy Coding

This is the most effective method of lossless coding and is nearly always present in image compression. Entropy is the average minimum number of bits that a data symbol stream can be compressed into, when each symbol is considered in isolation, based on its statistics. It can be calculated directly using equation (1.6), but it is sometimes not possible to reach the theoretical minimum entropy due to the implementation of the entropy coder.

$$Entropy = \sum PDD(x)\log_2(PDD(x))$$

(1.6)

where PDD(x) is the probability density distribution of symbol x.

There are two different approaches to entropy coding, Huffman coding [1 - 2] and arithmetic coding [1 - 2]. Huffman compression is a more common and robust method, however cannot compress data to less than one bit/symbol. Arithmetic coding is less controllable and does not compress well at higher bits/symbol, however it can reduce its entropy below one bit/symbol. For this reason arithmetic

coders are not often used, unless the average entropy of the source is expected to drop below one bit / symbol.

#### 1.1.3.2 Huffman Coding

Huffman compression [1 - 2] is designed to reduce the entropy of a data source close to the theoretical minimum entropy described in equation (1.6). The Huffman coder does this by representing common data symbols with short compressed symbols and rare data symbols with long compressed symbols. The average effect of this method is to reduce the redundancy of each compressed symbol to a minimum.

A Huffman coder determines the compressed symbols by forming a data tree from the original data symbols and their associated probabilities. The tree is formed by applying the following rules until it is complete.

1. Link the two unlinked data symbols with the lowest probability to form a new data symbol with probability equal to the sum of the previous two symbols.

2. Continue to link the active data symbols with the smallest probability until a complete data tree is formed.

| Symbol | Probability | Binary Symbol | Binary Compressed Symbol |

|--------|-------------|---------------|--------------------------|

| А      | 0.06        | 00            | 111                      |

| В      | 0.04        | 01            | 110                      |

| C      | 0.2         | 10            | 10                       |

| D      | 0.7         | 11            | 0                        |

Table 1.1 showing four symbols compressed using Hoffman Coding

Consider the example shown in Table 1.1. There are four symbols, which can be described by the binary data symbols shown, and have an average bits/symbol coding rate of 2. If the four symbols are Huffman coded, then we obtain the compressed binary symbols shown in Table 1.1. The average bits/symbol for the compressed binary symbols is 1.3, which is a lossless compression of 1.5:1. The example shown in Table 1.1 shows the major failing of the Huffman coder. The entropy of the source given is 1.0, but the Huffman coder is only able to reduce the bit/symbol coding rate to 1.3. If the entropy of the data source is often close to or below 1 bit/symbol, then the Huffman coder does not perform optimally, and needs to be improved.

#### 1.1.3.3 Arithmetic Coding

Arithmetic coding [1-2] works by treating a stream of data symbols as a whole and does not replace individual data symbols with compressed versions. The coder is always implemented in binary and to avoid confusion it will be explained by reference to binary numbers.

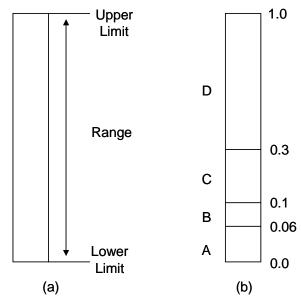

An arithmetic coder takes an upper and lower limit, and defines a range between these upper and lower limits to be equivalent to a symbol with the probability of 1.0. Symbols are encoded by modifying the range of the arithmetic coder and sending symbols to reconstruct this range information at the decoder. The operation of an arithmetic coder can be demonstrated by using the data previously used in Table 1.1. The data can be represented as probabilities in the arithmetic coder as shown in figure 1.4.(b). It can be seen that the symbol probabilities stack to form a continuous range of probabilities between 0.0 and 1.0. This gives a range of probabilities that represent each symbol.

Figure 1.4: Limits of an Arithmetic Coder

The upper limit of the arithmetic coder is initially set to a value which corresponds to a probability of 1.0 but with infinite precision. This can be represented in binary as an infinite number of bits set to 1, since there is no fixed position for the decimal point. The lower limit is set to zero with infinite precision, again using an infinite number of binary bits set to 0. The only problem with this assumption is that computers work with fixed length numbers, commonly 4 to 8 bytes long, so it is impossible to represent the infinite precision. To over come this the limits are set as large as possible and their infinite length is simulated, by the coding algorithm.

The operation of encoding a symbol by the coder requires the range to be reduced in the following way:

where  $P_{HIGH}$  (*Symbol*) is the higher probability range of the symbol, and  $P_{LOW}(Symbol)$  is the lower probability range of the symbol.

#### 1.1.3.4 Run Length Coding

Run length coding is effective on data sources that have linear runs of the same symbol inside a data stream. The run length coder works by counting the number of occurrences of the same symbol and then forming a new symbol which describes the run length and the run symbol type. This is demonstrated in figure 1.5.

Figure 1.5: Diagram Illustrating the Run Length Coder

The entropy of the new symbol stream, which contains the run length codes is less than the original, providing there are sufficient runs to make the method viable. Run length coding has a similar effect to arithmetic coding without the complication of the arithmetic coder.

#### **1.2 Performance Measures of Image Compression**

Normally the performance of a data compression scheme can be measured in terms of three parameters. These are:

- i. compression efficiency

- ii. complexities

- iii. Distortion measurement for lossy compression

Compression efficiency is measured through compression ratio (CR). The CR can be defined as the ratio of the data size (number of bits) of the original data to the size of the corresponding compressed data. The complexities of a digital data compression algorithms are measured by a number of data operations required performing both the encoding and decoding process. The data operations include additions, subtractions, and multiplication, divisions and shift operations. Generally there are two parameters: efficiency and complexities, which are mutually conflicting. One can not be benefited from both sides that are the efficiency of a compression algorithm varies proportionally with the complexity. More complex algorithm yields better compression performance with a greater data reduction and takes a longer time to execute. In the lossy compression algorithms, distortion measurement is used to measure the amount of information lost on the reconstruction of the original signal or image data that has been recovered from the compressed data through encoding and decoding operations. The mean square error (MSE) is one of the distortion measurements in the reconstructed data. The performance measurement parameter; signal to noise ratio (SNR) is also used to measure the performance of the lossy compression algorithms. These measurement criteria are often used for 1D data. For image data (2D) compression, the SNR is replaced by a parameter known as peak signal to noise ratio (PSNR). Another way of distortion measurement is the

percentage of energy retained in the compressed data. The above distortion measurements can be mathematically expressed as:

For One Dimensional data Mean Square Error calculated as

$$MSE = \frac{1}{N} \sum_{n=0}^{N-1} \left| x(n) - x'(n) \right|^2$$

(1.7)

where N is the number of pixels in the image, x(n) is the original data and x'(n) is the compressed data.

PSNR(Peak Signal to Noise Ratio) for two dimensional image data is

$$PSNR = 10\log_{10}(\frac{255^2}{MSE1})$$

(1.8)

Where

$$MSE1 = \frac{1}{MN} \sum_{m}^{M-1} \sum_{n=0}^{N-1} \left| x(m,n) - x'(m,n) \right|^2$$

(1.9)

Percentage of energy retain is given by

$$\frac{(Vector norm of data after compression)^2}{(Vector norm of data before compression)^2} \times 100$$

(1.10)

None of the main methods for measuring image distortion takes into account, how good the recovered image looks to the human visual system. This is an area called psycho-visual image analysis, and it is an area of research which has a large scope. Unfortunately little progress has been made into an automated method for calculating a psycho-visual distortion measure.

## **1.3 Digital Camera**

A digital camera is a popular consumer electronic device that can capture images, or "take pictures," and store them in digital format. A digital still camera does not contain film, but rather then it contains one or more ICs, possessing processors and memories [7]. The key advantage of digital photography systems is their ability to provide noise-free storage, duplication, editing, and transmission of the digital images. The increased processing, storage, and communications capabilities of desktop PCs, coupled with their decreasing cost, have sparked the growth of digital photography.

From a designer's point of view, a simple digital camera performs two key tasks. The first task is that of processing images and storing them in internal memory. The second task is that of uploading the images serially to an attached PC. The task of processing and storing images is initiated when the user presses the shutter button. At this point, the image is captured and converted to digital form by a charge-coupled device (CCD) or CMOS. Then, the image is processed and stored in internal memory.

Figure 1.6: Digital Image Processing Steps in a Digital Camera

Figure 1.6, shows the key image processing steps implemented in digital cameras [4, 6, 7], or in host computers that process the raw image files provided by digital cameras. The sensor data may be processed to conceal defective or noisy pixels, and to correct for sensitivity variations caused by the lens or sensor.

CFA - Most digital cameras use this approach. A mosaic *color filter array* (CFA) is fabricated on top of the individual sensor photosites. Many different arrangements of colors are possible [4, 6], but each photosite is sensitive to only one spectral band. An optical anti-aliasing filter is normally used to reduce false color artifacts.

Color sequential - The color image is created with a monochrome sensor using three successive exposures taken with different optical red, green, and blue (RGB) filters, or a tunable LCD, in the optical path. These cameras are used for studio photography of inanimate scenes, but cannot be used for portraits, because subject motion causes colored edge artifacts. The CFA data from the sensor is interpolated to reconstruct the "missing" color pixel values. Adaptive FIR filters are used for better results.

White balance corrects for the scene illuminant, since daylight has a greater proportion of blue energy than tungsten lamps. The R and B signals are multiplied by R and B gain values intended to provide equal RGB pixel values for neutral (e.g., white or gray) objects. Color correction may use a 3 x 3 matrix to correct the camera spectral sensitivities, and tone correction uses a set of lookup tables. Image sharpening, achieved by simple or adaptive spatial filters, compensates lens blur and provides a subjectively sharper image.

To store images on memory cards, standard JPEG compression [2, 3, 32] is typically used to reduce the file size to less than 2 bits per pixel, in order to increase the number of images that can be stored. Exif format JPEG-compressed files produced by digital cameras, and by film scanners to picture CD discs, include metadata that provides information about the image capture device and the picture taking conditions. This metadata can be used to simplify image retrieval and provide higher quality prints from the digital files. The metadata often includes a "thumbnail" size image at the beginning of the PEG file, to allow groups of images to be rapidly viewed so that appropriate images can be quickly selected for viewing, copying, or printing.

Some of the new compression standard features are:

- Improved compression efficiency

- Multiple resolution representation

- Embedded bit stream (progressive decoding from lossless to lossy)

- Region-of-interest coding

Many of these features are invaluable for digital cameras. For example, improved compression efficiency allows for either more images to be stored on the same memory card or for the same number of images to be stored with a higher image quality. The multi-resolution feature allows the various segments of the bit stream to be decoded to provide multiple resolutions of the image as needed. For example, the

low-resolution image can be used as a thumbnail display on the camera LCD, while the medium resolution image is shared through e-mail, and the higher resolution images are used to create high-quality prints.

#### **1.3.1 Requirements Specification**

Specification describes what a particular 'system should do, namely the system's requirements [6]. Specifications include both functional and nonfunctional requirements. Functional requirements describe the system's behavior, meaning the system's outputs as a function of inputs (e.g., "output X should equal input y times 2"). Nonfunctional requirements describe constraints on design metrics (e.g., "the system should use 0.001 watt or less"), battery life should be as long as possible. The initial functional specification of a system may be very general and may come from the company's marketing department.

#### **1.3.2** Nonfunctional Requirements

Given our initial requirements specification, we might want to pay attention to several design metrics in particular: performance, size, power, and energy. Performance is the time required to process an image [6]. Size is the number of elementary logic gates (such as a two input NAND gate) in our IC. Power is a measure of the average electrical energy consumed by the IC while processing an image. Energy is power times time, which directly relates to battery lifetime. Some of these metrics will be constrained metrics-those metrics must have values below (or in some cases above) a certain threshold. Some metrics may be optimization metrics those metrics should be improved as much as possible, since this optimization improves the product. A metric can be both a constrained and optimization metric.

Regarding size, our design must use an IC that fits in a reasonably sized camera. Suppose that, based on current technology, we determine that our IC has a size constraint of 200,000 gates. In addition to being a constrained metric, size is also an optimization metric, since smaller ICs are generally cheaper. They are cheaper because we can either get higher yield from a current technology or use an older and hence cheaper technology.

16

Figure 1.7: Functional block-diagram specification of a digital camera

The high-level functionality of the digital camera can be described by using the flowchart in figure 1.7 [6]. The major functions involved in image capture, namely zero-bias adjust, Image compression (DCT, quantisation and archive in memory). The compressed image data transmitted serially. Note that figure 1.4 does not dictate that each of the blocks be mapped onto a distinct processor. Instead, the description only aids in capturing the functionality of the digital camera by breaking that functionality down into simpler functions. The functions could be implemented on any combination of single-purpose and general-purpose processors.

Finally, power is a constrained metric because the IC must operate below a certain temperature. Note that the digital camera cannot use a fan to cool the IC, so low power operation is crucial. Let's assume we determine the power constraint to be 200 mill watt. Energy will be an optimization metric because we want the battery to last as long as possible. Notice that reducing power or time each reduces energy.

# **1.4 Motivation**

Image compression is an important issue in digital image processing and finds extensive applications in many fields. This is the basic operation performed frequently by any digital photography technique to capture an image. For longer use of the portable photography device it should consume less power so that battery life will be more. To improve the Conventional techniques of image compressions using the DCT have already been reported and sufficient literatures are available on this. The JPEG is a lossy compression scheme, which employs the DCT as a tool and used mainly in digital cameras for compression of images. In the recent past the demand for low power image compression is growing. As a result various research workers are actively engaged to evolve efficient methods of image compression using latest digital signal processing techniques. The objective is to achieve a reasonable compression ratio as well as better quality of reproduction of image with a low power consumption. Keeping these objectives in mind the research work in the present thesis has been undertaken. In sequel the following problems have been investigated.

For solving for low power image compression we have modified the existing JPEG architecture which is the basic technique used for image compression and proposed some new low complexity method of compression technique. The performances of the proposed compression techniques have been evaluated and have been compared with that of the standard technique. Finally the proposed algorithms implemented in hardware and the power consumption is estimated. It is in general, observed that the proposed techniques are efficient than the conventional one. The results of the investigation have been outlined and discussed in subsequent Chapters.

# **1.5** Literature Survey

Interest in portable devices [6] has enhanced the requirement of developing low-power signal processors and algorithms, as well as the development of low-power general purpose processors. Designers have been able to reduce the energy requirements of particular functions, such as video compression, by several orders of magnitude [15, 63]. Low power techniques [11 - 23] can be discussed at various levels of abstractions: system level, algorithm and architecture level, logic level, circuit level, and technology level [12 - 14]. One important technique for low power is at algorithmic level by using algorithmic transformations [12 - 14]. This technique exploits the complexity, concurrency, regularity, and locality of an algorithm. Reducing the complexity of an algorithm reduces the number of operations and hence the power consumption. This technique is used for reduction of power consumption by reducing the complexity.

The JPEG [24, 32, 41, 50] is one of the standard digital image compression for multilevel still images including both grayscale and colour images. Among the different models the JPEG baseline is the most widely used. It is based on the Transform coding using the DCT. Due to the lossy transformation, the JPEG output at high CR (at 15-20:1) becomes effected by the blocking artifacts and ridges separated in the image that are found to merge during compression. Normally the DCT has been used in the JPEG compression scheme. However, in the DSP literature many other efficient transforms such as Discrete Hartley Transform (DHT) [56 – 60] can be used in place of DCT, which may enhances the performance of the JPEG.

Vector quantisation, (VQ) mainly used for lossy image compression to reduce the image data [42]. Many VQ techniques applied for image compression has been reported [41 - 45]. The main problem with existing VQs is preparation of the code book [44, 52]. In VQ techniques creating the code book is a complicated process which has to be designed mainly to preserve the low frequency coefficients, and most of the high frequency coefficients are discarded.

Many lossless image compression techniques [66 -73] are exists. The main aim behind these compression techniques to get good quality image reconstruction and low compression. These techniques are mainly used for those images like medical images [66, 68, 69], satellite images etc.

# **1.6** Chapter-wise Organization of the thesis:

The thesis is organised as follows:

Chapter-1 outlines the basic principle of image compression and deals with the performance measurement of digital image compression. It gives a brief idea of digital camera architecture. It also reviews the relevant literature on digital image compression and formulates the problems to be investigated in sequel. The motivation behind choosing various problems is also outlined.

- (2) Chapter-2 presents an overall idea about low power VLSI design, such as what are the sources of power loss in a circuit and how to control these losses. Describes all the low power techniques such as system level, algorithm level, architecture level, logic level and circuit level. Lastly it describes the basic steps to be followed for low power design.

- (3) Chapter-3 introduces DCT and its application in JPEG image compression technique briefly. The work reported in the literature on JPEG based compression is clearly reviewed. Three new quantisation techniques are proposed to reduce the computational complexity. The proposed techniques are compared with the standard JPEG technique through computer simulation on standard images.

- (4) In Chapter-4 the standard DCT is replaced by DHT to reduce the computational complexity, ringing effect and blocking effect. The three quantisation techniques proposed in chapter-1 is used with DHT to further reduce the complexity of compression technique. The performance of these new techniques is compared with the standard conventional JPEG.

- (5) In **Chapter-5** a new method of lossless image compression technique is proposed. The computational complexity of this technique is very less compared to other image compression technique. The performance of these new techniques is compared with the standard conventional lossless JPEG compression technique.

- (6) Chapter-6 briefly introduces VLSI design and AccelChip synthesis process. Also lists the FPGA implementation results of all the proposed techniques and compared with the standard JPEG technique.

- (7) In Chapter-7, conclusion has been made and some further research scopes are suggested.

LOW POWER Image Compression Techniques

# Low Power VLSI Design Techniques

In the past few years there has been an explosive growth in the demand for portable computing and communication devices, from mobile telephones to sophisticated multimedia gadgets [11]. This interest in these devices has enhanced the requirement of developing low-power signal processors and algorithms, as well as the development of low-power general purpose processors. In the digital signal processing area, the results of this attention to power are quite remarkable. Designers have been able to reduce the energy requirements of particular functions, such as video compression, by several orders of magnitude [14]. This reduction has come as a result of focusing on the power dissipation at all levels of the design process, from algorithm design to the detailed implementation. In the general purpose processor area, however, there has been little work done to understand how to design energy efficient processors.

Performance of processors has been growing at an exponential rate, doubling every 18 to 24 months. However, at the same time the power dissipated by these processors has also been growing considerably. Although the rate of growth of power dissipation is perhaps not quite proportional to performance and size (the number of transistors) it still has led to processors which dissipated more than 50W. For such processors cooling becomes an absolute necessity and at high power dissipation level this is even difficult and expensive. If this trend continues processors will soon dissipate hundreds of watts, which would be unacceptable in most systems. Thus there is great interest in understanding how to continue increasing performance without increasing the power dissipation.

For portable applications the problem is even more severe since battery life depends on the power dissipation. Lithium-ion batteries have an energy density of approximately 100Wh/kg, the highest available today. To operate a 50 W processor for 4 hours requires a 2 kg battery; hence it can hardly be termed as a portable device. In order to compare processor designs that have different performance and power one needs a measure of "goodness". If two processors have the same performance or the same power, then it is trivial to choose which is better—users prefer higher performance for the same power level or the lower power one if they have the same performance. But processor designs rarely have the same performance. Designers have to determine whether to add a particular feature will make a processor more

21

desirable or not. However micro-architectural designing changes the amount of parallelism of the processor, affects the efficiency of the processor. Since both the performance and energy dissipation of modern processors depend heavily on the design of the memory hierarchy, one must look not only at the processor itself, but also have to look at the design of the memory. Since memories and clocking circuits are critical components of every digital system, much work already has been done to reduce the energy requirements. A different approach to reduce the energy dissipation of clocks and memories is to change the technology by scaling the supply voltage and the threshold voltage of transistors.

## **2.1 Power Dissipation Sources**

In CMOS circuits, the main contributions to the power consumption are from short-circuiting current, leakage current, and switching currents [18], [21]. In the following subsections, we introduce them separately.

### 2.1.1 Short-Circuit Power

In a static CMOS circuit, there are two complementary networks: p-network (pull-up network) and n-network (pull-down network). The logic functions for the two networks are complementary to each other. Normally when the input and output state are stable, only one network is turned on and conducts the output either to power supply node or to ground node and the other network is turned off and blocks the current from flowing. Short-circuit current exists during the transitions as one network is turned on and the other network is still active. For example, the input signal to an inverter is switching from 0 to  $V_{dd}$ . During this transaction, there exists a short time interval where the input voltage is larger than  $V_m$  but less than  $V_{dd} - |V_{tp}|$ . During this time interval, both PMOS-transistor (p-network) and NMOS-transistor (n-network) are turned on and the short-circuit current flows through both kinds of transistors from power supply line to the ground.

The exact analysis of the short-circuit current in a simple inverter [18] is complex, this is analyzed by SPICE simulation. It is observed that the short-circuit current is proportional to the slope of input signals, the output loads and the transistor sizes [19]. The short-circuit current consumes typically less than 10% of the total power in a "well-designed" circuit [19].

### 2.1.2 Leakage Power

Leakage currents are due to two sources: one from the currents that flow through the reverse biased diodes (reverse biased PN-Junction current), the other from the currents that flow through transistors that are non-conducting (subthreshold channel conduction current).

Figure 2.1: Leakage current types: (a) reverse biased diode current, (b) subthreshold leakage current.

The leakage currents are proportional to the leakage area and exponential of the threshold voltage. The leakage currents are due to manufacturing technology and cannot be modified by the designers except in some logic styles. Subthreshold leakage and reverse-biased junction leakage, both increases dramatically with temperature and are independent of the operating voltage for a given fabrication process.

The leakage current is in the order of pico-Ampere, but it increases as the threshold voltage is reduced. In some cases, like large RAMs, the leakage current is one of the main concerns. The leakage current is currently not a severe problem in most digital designs. However, the power consumed by leakage current can be as large as the power consumed by the switching current for  $0.06\mu m$  technology. The usage of multiple threshold voltages can reduce the leakage current in deep-submicron technology. Leakage current is difficult to predict, measure or optimized.

Generally, leakage current serves no useful purposes, but some circuits do exploit it for intended operations, such as power-on reset signal generation. The leakage power problem mainly appears in very low frequency circuits or ones with "sleep modes" where dynamic activities are suppressed.

### 2.1.3 Switching Power

The switching currents are due to the charging and discharging of node capacitances. The node capacitances mainly include gate, overlapping, and interconnection capacitances. The power consumed by switching current [18] can be expressed as

$$P = \alpha C_L f V_{dd}^2 / 2 \tag{2.1}$$

where  $\alpha$  a is the switching activity factor,  $C_L$  is the load capacitance, f is the clock frequency, and  $V_{dd}$  is the supply voltage.

The above equation (2.1) shows that the switching power depends on a few quantities that are readily observable and measurable in CMOS circuits. It is applicable to almost every digital circuit and hence provides guidelines for the low power design.

The power consumed by switching current is the dominant part of the power consumption. Reducing the switching current is the focus of most low power design techniques. For large capacitance circuits, reduction of the frequency is the best way to reduce the switching power. The use of different coding methods, number representation systems, continuing sequences and data representations can directly alter the switching frequency of the design, which alters the switching power. The best method of reducing switching frequency is to eliminate logic switching that is not necessary for computation.

## 2.2 Low Power Techniques

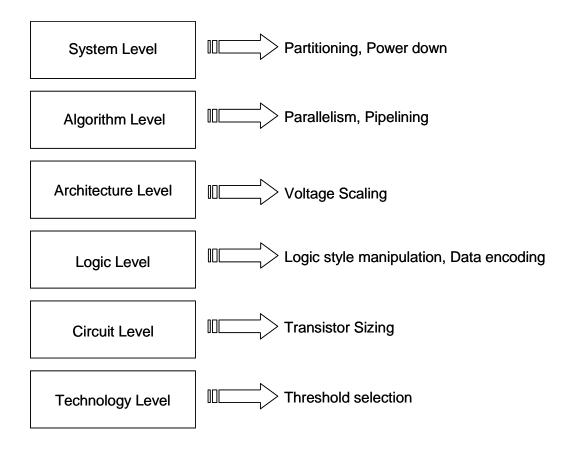

Low power techniques can be discussed at various levels of abstractions: system level, algorithm and architecture level, logic level, circuit level, and technology level [18], [21]. Figure 2.2 shows some examples of techniques at the different levels.

Figure 2.2: Low-power design methodology at different abstraction levels.

In the following sections, an overview for different low power techniques has been described in detail. This is organized on the basis of abstraction level.

### 2.2.1 System Level

A system typically consists of both hardware and software components, which affect the power consumption. The system design includes the hardware/software partitioning, hardware platform selection (application-specific or general-purpose processors), resource sharing (scheduling) strategy, etc. The system design usually has the largest impact on the power consumption and hence the low power techniques applied at this level have the most potential for power reduction.

At the system level, it is hard to find the best solution for low power in the large design space and there is a shortage of accurate power analysis tools at this level. However, if, for example, the instruction-level power models for a given processor are available, software power optimization can be performed [23]. It is observed that faster code and frequently usage of cache are most likely to reduce the power consumption.

The order of instructions also have an impact on the internal switching within processors and hence on the power consumption.

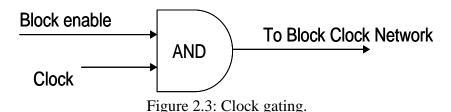

The power-down and clock gating are two of the most used low power techniques at system level. The non-active hardware units are shut down to save the power. The clock drivers, which often consume 30-40% of the total power consumption, can be gated to reduce switching activities as illustrated in figure 2.3.

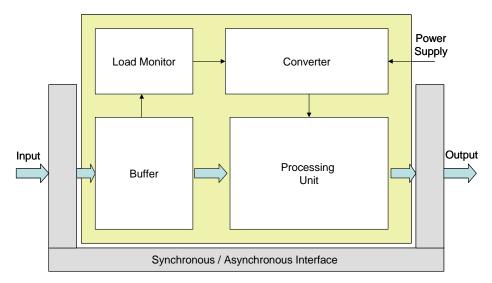

The power-down can be extended to the whole system. This is called sleep mode and widely used in low power processors. The system is designed for the peak performance. However, the computation requirement is time varying. Adapting clocking frequency and/or dynamic voltage scaling to match the performance constraints is another low power technique. The lower requirement for performance at certain time interval can be used to reduce the power supply voltage. This requires either feedback mechanism (load monitoring and voltage control) or predetermined timing to activate the voltage down-scaling.

Figure 2.4: Asynchronous design with dynamic voltage scaling.

Asynchronous design of the circuit can also be used as another low power designing technique. The asynchronous designs have many attractive features, like non-global clocking, automatic power-down, no spurious transitions, and low peak current, etc. It is easy to reduce the power consumption further by combining the asynchronous design technique with other low power techniques, for instance, dynamic voltage scaling technique [20], as shown in the following figure 2.4.

# 2.2.2 Algorithm Level

The algorithm selection has large impact on the power consumption. The task of algorithm design is to select the most energy-efficient algorithm that just satisfies the constraints. The cost of an algorithm includes the computation part and the communication/storage part. The complexity measurement for an algorithm includes the number of operations and the cost of communication and storage. Reduction of the number of operations, cost per operation, and long distance communications are key issues to algorithm selection.

One important technique for low power of the algorithmic level is algorithmic transformations [21]. This technique exploits the complexity, concurrency, regularity, and locality of an algorithm. Reducing the complexity of an algorithm reduces the number of operations and hence the power consumption. The possibility of increasing concurrency in an algorithm allows the use of other techniques, e.g., voltage scaling, to reduce the power consumption. The regularity and locality of an algorithm affects the controls and communications in the hardware.

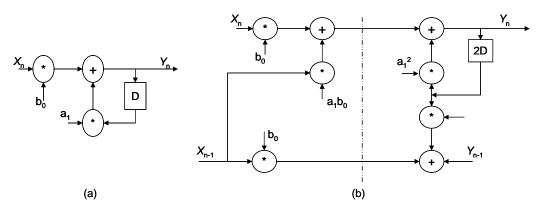

Figure 2.5: (a) Original signal flow graph. (b) Unrolled signal flow graph.

The loop unrolling technique [18], [12 - 13] is a transformation that aims to enhance the speed. This technique can be used for reducing the power consumption. With loop unrolling, the critical path can be reduced and hence voltage scaling can be applied to reduce the power consumption.

In figure 2.5, the unrolling reduces the critical path and gives a voltage reduction of 26% [18 - 23]. This reduces the power consumption with 20% even the capacitance load is increases with 50% [13]. Furthermore, this technique can be combined with other techniques at architectural level, for instance, pipeline and interleaving, to save more power. In some cases, like digital filters, the faster algorithms, combined with voltage-scaling, can be used for energy-efficient applications [18].

## 2.2.3 Architecture Level

According to the selection of the algorithm, the architecture can be determined for the given algorithm. From equation (2.1) we can say that, an efficient way to reduce the dynamic power consumption is the voltage scaling. When supply voltage is reduced, the power consumption is reduced. However, this increases the gate delay. To compensate the delay, low power techniques like parallelism and pipelining [14] architectures were used.

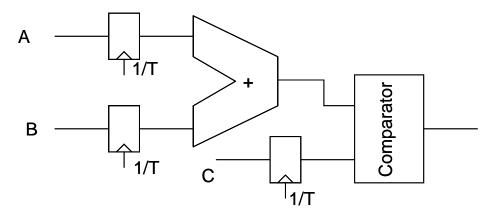

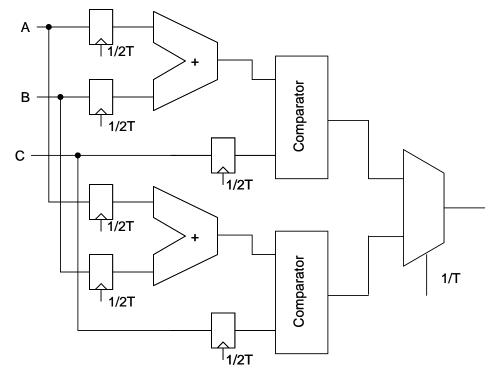

The use of two parallel datapath is equivalent to interleaving of two computational tasks. A datapath to determine the largest number of C and (A + B) is shown in figure 2.6. It requires an adder and a comparator. The original clock frequency is 40 MHz [14].

Figure 2.6: Original data path.

In order to maintain the throughput while reducing the power supply voltage, we use a parallel architecture. The parallel architecture with twice the amount of resources is shown in figure 2.7. The clock frequency can be reduced to half, from 40 MHz to 20 MHz since two tasks are executed concurrently. This allows the supply

voltage to be scaled down from 5 V to 2.9 V [14]. Since the extra routing is required to distribute computations to two parallel units, the capacitance load is increased by a factor of 2.15 [14]. The power is calculated by using equation (2.2).

Figure 2.7: Parallel implementation.

$$P_{par} = C_{par} V_{par}^2 f_{par} = (2.15C_{actual})(0.58V_{actual})^2 (\frac{f_{actual}}{2}) = 0.36P_{actual}$$

(2.2)

Figure 2.8: Pipelining implementation.

$$P_{pipe} = C_{pipe} V_{pipe}^2 f_{pipe} = (1.15C_{actual})(0.58V_{actual})^2 (f_{actual}) = 0.39P_{actual}$$

(2.3)

Pipelining is another method for increasing the throughput. By adding a pipelining buffer / register after the adder in figure 2.8., the throughput can the

increased from  $1/(T_{add} + T_{comp})$  to  $1/\max(T_{add}, T_{comp})$ . If  $T_{add}$  is equal  $T_{comp}$ , this increases the throughput by a factor of 2. As a result the supply voltage also scaled down to 2.9 V (the gate delay doubles) [14]. The effective capacitance increases to a factor of 1.15 because of the insertions of latches [14]. The power consumption for pipelining [14] is calculated using equation (2.3).

Main advantage of pipelining is the low area overhead in comparison with using parallel data paths. Another benefit is that the amount of glitches can be reduced. However, since the delay increases significantly as the voltage approaches the threshold voltage and the capacitance load for routing and/or pipeline registers increases, there exists an optimal power supply voltage. Reduction of supply voltage lower than the optimal voltage increases the power consumption.

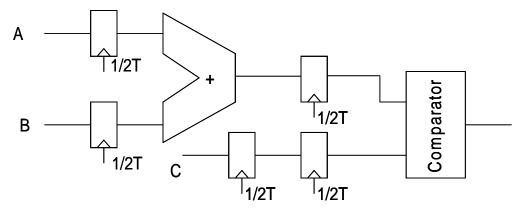

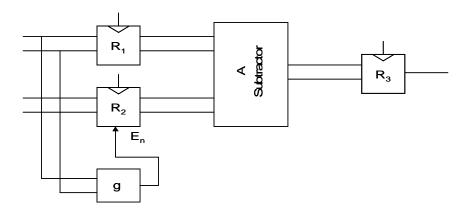

# 2.2.4 Logic Level

The power consumption depends on the switching activity factor, which in turn depends on the statistical characteristics of data. The low power techniques at the logic level, however, focus mainly on the reduction of switching activity factor by using the signal correlation and the node capacitances. In case of the gated clocking, the clock input to non-active functional block does not change by gating, and, hence, reduces the switching of clock network.

Figure 2.9: A precomputation structure for low power.

Precomputation [18] uses the same concept to reduce the switching activity factor: a selective precomputing of the output of a circuit is done before the outputs are required, and this reduces the switching activity by gating those inputs to the circuit. As shown in figure 2.9, the input data is partitioned into two parts, corresponding to

registers  $R_1$  and  $R_2$ . One part,  $R_1$ , is computed in precomputation block g, one clock cycle before the computation of A. The result from g decides gating of  $R_2$ . The power can then be saved by reducing the switching activity factor in A.

Lets consider a comparator as an example of precomputation for low-power. The comparator takes the MSB of the two numbers to register  $R_1$  and the others to  $R_2$ . The comparison of MSB is performed in g. If two MSBs are not equal, the output from g gated the remaining inputs. In this way, only a small portion of inputs to the comparator's main block A (subtracter) is changed. Therefore the switching activity is reduced.

Gate reorganization [18] is another technique used to restructure the circuit. This can be decomposition a complex gate to simple gates, or combines simple gates to a complex gate, duplication of a gate, deleting/addition of wires. The decomposition of a complex gate and duplication of a gate help to separate the critical and non-critical path. Which reduce the size of gates in the non-critical path, as a result reduces the power consumption. In some cases, the decomposition of a complex gate increases the circuit speed and gives more space for power supply voltage scaling. The composition of simple gates can reduce the power consumption. The complex gate can reduce the charge/discharge of high-frequently switching node. The deleting of wires reduces the circuit size as a result, reduces the load capacitance. The addition of wires helps to provide an additional interconnection for better results.

Logic encoding defines the way data bits are represented on the circuits. The encoding is usually optimized for reduction of delay or area. In low power design, the encoding is optimized for reduction of switching activities since various encoding schemes have different switching properties.

In a counter design, counters with binary and Gray code have the same functionality. For N-bit counter with binary code, a full counting cycle requires  $2(2^n - 1)$  transitions [18] A full counting cycle for a Gray coded N-bit counter requires only  $2^n$  transitions. For instance, the full counting cycle for a 2-bit binary coded counter is from 00, 01, 10, 11, and back to 00, which requires 6 transitions. The full counting cycle for 2-bit Gray coded counter is from 00, 01, 11, 10, and back to 00, which requires 4 transitions. The binary coded counter has twice transitions as the

Gray coded counter when the n is large. Using binary coded counter therefore requires more power consumption than using Gray coded counter under the same conditions.

Traditionally, the logic coding style is used for enhancement of speed performance. Careful choice of coding style is important to meet the speed requirement and minimize the power consumption. This can be applied to the finite state machine, where states can be coded with different schemes.