# Numerical Simulation of Low-Frequency Noise in Polysilicon Thin-Film Transistors

Laurent Pichon, Abdelmalek Boukhenoufa, Christophe Cordier, Bogdan Cretu

## ▶ To cite this version:

Laurent Pichon, Abdelmalek Boukhenoufa, Christophe Cordier, Bogdan Cretu. Numerical Simulation of Low-Frequency Noise in Polysilicon Thin-Film Transistors. IEEE Electron Device Letters, Institute of Electrical and Electronics Engineers, 2007, 28 (8), pp.716. <10.1109/LED.2007.900849>. <hal-00171712>

HAL Id: hal-00171712 https://hal.archives-ouvertes.fr/hal-00171712

Submitted on 12 Sep 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Numerical simulation of low frequency noise in polysilicon thin film transistors

L. Pichon\*, A. Boukhenoufa, C. Cordier, B. Cretu

\*Groupe Microélectronique, IETR, UMR CNRS 6164, campus de beaulieu, 35042 Rennes cedex, France

Groupe de Recherches en Informatique, Image, Automatique et Instrumentation de Caen (GREYC), CNRS UMR 6072, ENSICAEN-Université de Caen, 6 bd du Maréchal Juin, 14050 Caen Cedex 5, France.

Abstract-Numerical simulations of low-frequency noise are carried out in two technologies of N-channel polysilicon thin film transistors biased from weak to strong inversion, and operating in the linear mode. Noise is simulated by GR processes. The contribution of grain boundaries on the noise level is higher in the strong inversion region. The microscopic noise parameter deduced from numerical simulations is lower than the macroscopic one defined according to the Hooge empirical relationship and deduced from noise measurements. The higher macroscopic value is attributed to the drain current crowding induced by non conducting spots in the devices due to structural defects. The ratio of these two noise parameters <u>can be</u> considered as <u>an indicator</u> to qualify TFT technology.

Index terms- low frequency noise, Generation-Recombination, polysilicon TFTs, numerical simulation, impedance field method

#### I. INTRODUCTION

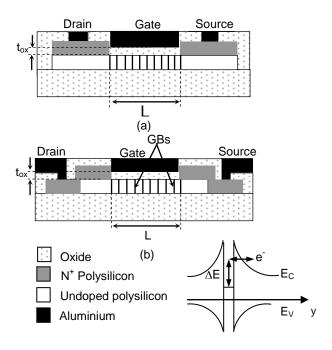

The physical origin of low-frequency (1/f) noise in TFTs due to carrier fluctuation is still controversial. It can be explained by trapping/detrapping into slow oxide traps [1-3] and/or by generation/recombination (GR) processes of carriers at defects such grain boundaries (GBs) [3] and thus the corresponding defect densities can be deduced. 1/f noise level is then strongly dependent on fabrication process. In this work we analyze by numerical simulations the 1/f noise level in N-Channel polysilicon TFTs biased in the linear mode. Noise is simulated by GR mechanisms (and the impact of the (structural) defects is pointed). Studied TFTs are issued from two (low temperature ≤600°C) technologies: Furnace Solid Phase Crystallized (FSPC) and Laser Solid Phase Crystallized (LSPC) TFTs. FSPC TFTs are built with one poly-Si layer: the upper part is heavily doped (source and drain regions) and the bottom part is none intentionally doped (active layer): see figure 1 (a). LSPC TFTs are fabricated with two poly-Si layers: source and drain regions are made on doped layer, whereas an underlying undoped layer constitutes the active one (see figure 1 (b)). Active layer in LSPC TFTs undergoes an additional solid phase thermal annealing by using a scan of an Ar laser beam. Details concerning TFT fabrication are given in ref [4,5].

#### II. SIMULATION

In both simulated TFTs (fig. 1) the doped and undoped polycrystalline films are 150nm thick. The oxide thickness  $t_{ox}$  is 60nm in FSPC TFT and 74nm in LSPC TFT. In FSPC TFT we get W/L=50 $\mu$ m/20 $\mu$ m, whereas in LSPC TFT W/L=80 $\mu$ m/60 $\mu$ m. The polysilicon is described by introducing equally spaced GBs, depicted as thin amorphous silicon layer with a width of 2 nm, perpendicular to the carrier transit direction. The grain size in FSPC TFT and LSPC TFT is 300 nm and 500 nm, respectively. Geometrical dimensions of each part of the structure correspond to those of processed devices (see ref [4,5]).

1/f noise simulation is based on the impedance field method (IFM) of Shockley by using the DESSIS-ISE multidimensional simulator of ISE-TCAD software [6]. A numerically efficient Green function approach to the Langevin equation-based simulation of the IFM is the basis for the implementation in ISE simulator. The complex Green functions G describe the propagation of perturbations inside the device to the contacts. The noise voltage spectral density was calculated from integration over all noise sources [6]:

$$S(\omega, r) = \sum_{\alpha = n, p} \int_{\Omega} G_{\alpha} K_{\alpha, \alpha}^{GR} G_{\alpha}^{*} dr + \sum_{\alpha = n, p} \int_{\Omega} G_{\alpha} K_{\alpha, \alpha}^{fGR} G_{\alpha}^{*} dr$$

$$\tag{1}$$

where  $K^{GR}$ ,  $K^{fGR}$  and  $\Omega$  represent the GR and the flicker GR local noise sources and the device volume respectively. The GR noise source model that is expressed as a tensor:

$$K_{n,n}^{GR} = \frac{J_n \otimes J_n}{n} \frac{4\alpha_{gr} \tau_{gr}}{1 + \omega^2 \tau_{gr}^2}$$

(2)

$J_n$  is the local current density, n the local carrier density,  $\tau_{gr}$  the equivalent GR lifetime,  $\alpha_{gr}$  a constant which represents the quasi Poissonian character of the carrier number (N) fluctuations  $(\langle \Delta N^2 \rangle = \alpha_{gr} \langle N \rangle)$  and  $\omega = 2\pi f$  is the angular frequency. The 1/f noise source is represented as the sum of GR noises produced by sub bands of impurities or defects, with a <u>corresponding</u> distribution of trapping characteristic times between  $\tau_1$  and  $\tau_2$ :  $g(\tau) = (\ln(\tau_2/\tau_1)\tau)^{-1}[3]$ . The flicker GR local noise source is expressed as a tensor:

$$K_{n,n}^{fGR} = \frac{J_n \otimes J_n}{n} \frac{2\alpha_H}{\pi f \log(\frac{\tau_2}{\tau_1})} \left[\arctan(\omega \tau_2) - \arctan(\omega \tau_1)\right]$$

(3)

$\alpha_{\rm H}$  is identified to the microscopic Hooge noise parameter associated with the local source of noise.

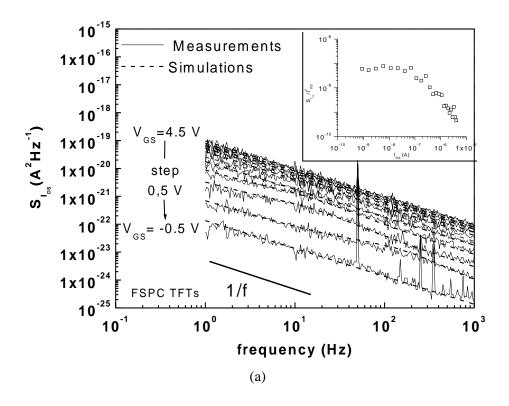

The calculation of the drain current noise spectral density requires knowledge of the local noise source K. We defined the flicker GR local noise sources  $K^{fGR}$  in the whole bulk of the active layer with  $\alpha_H$  assumed identical for all sources. In order to obtain a 1/f behaviour in the studied frequency band (1Hz-10<sup>3</sup>Hz), the relaxation times  $\tau_1$  and are fixed at  $10^{-7}$ s and  $10^4$ s, respectively. For GR mechanism at  $SiO_2/Sipoly$  interface  $\tau = \tau_0 \exp(\gamma y)$  with  $\tau_0 \sim 10^{-12}$ s,  $\gamma \sim 10^{10}$ m<sup>-1</sup>, and y the tunnel path. For GR mechanism at GBs associated to thermally assisted tunnelling process (see inset of fig 1)  $\tau = \tau_0 \exp(\Delta E/kT) \exp(\gamma y)$  [7]. For example if  $y \approx 3$ nm and  $\Delta E \approx 0.2$ eV it gives  $\tau_2 \sim 10^4$  and this justify the high value of  $\tau_2$ . For some spectrums with a Lorentzian (figure 2), we introduced a GR local noise source  $K^{GR}$ .

#### III. RESULTS AND DISCUSSION

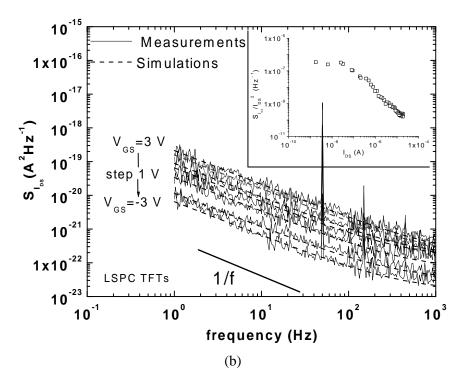

A good fit of experimental with numerical noise spectra was obtained (figure 2), and then the microscopic noise parameter  $\alpha_H$  in (3) was deduced for FSPC and LSPC TFTs. Values of  $\alpha_H$  versus effective voltage (V<sub>GS</sub>-V<sub>0</sub>), with V<sub>0</sub> the flatband voltage, are reported in figure 3. Plots of macroscopic apparent noise parameter  $\alpha_{app}$ , deduced from the experimental measurements [8] according to the Hooge formula  $S_{IDS}/I_{DS}^2$  $\alpha_{app}/(fN)$  with N the free carrier number in the channel, is also reported. For both devices  $\alpha_H$  and  $\alpha_{app}$ increase from weak to moderate inversion and then it decreases from moderate to strong inversion. This singular behaviour, previously reported for  $\alpha_{app}$  [8], suggest that  $\alpha_H$  and  $\alpha_{app}$  are directly related. Higher value of  $\alpha_{app}$  could be explained by the current crowding (CC) due to structural defects inducing non conducting spots [9,10,11]. In such case CC is characterized [11] by standing 1/f noise in a relative noise level for a unit area  $C_{us} = KR_{sh} = (f S_{IDS}/I^2_{DS})WL$  with  $K = \alpha_{app}q\mu$  ( $\mu$  carrier mobility) and  $R_{sh} = (V_{DS}/I_{DS})(W/L)$ the sheet resistance (linear mode-V<sub>DS</sub>=300mV). Plots of C<sub>us</sub> versus R<sub>sh</sub> reported in the inset of the figure 3 show that  $K \ge K_{Au} = 5 \times 10^{-21} \text{cm}^2/\Omega$  obtained for gold resistor indicating CC on a microscopic scale. For homogeneous materials  $\alpha_H/\alpha_{app}\sim 1$  whereas for disordered materials  $\alpha_H/\alpha_{app}<<1$ . In our case, the maximum value of this ratio is ~0.17 and ~0.11 respectively for FSPC and LSPC TFTs. The lower value in LSPC TFT can be explained by the poorer quality of the access resistance because of the active layer/source(drain) region interface acting as an additional non conducting spot. This effect is consistent with the higher measured macroscopic parameter and the higher K-value for LSPC TFTs (figure 3). Thus  $\alpha_H/\alpha_{app}$  could be considered as an indicator of quality.

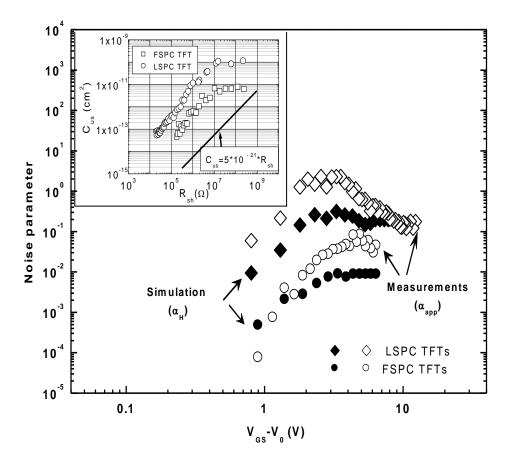

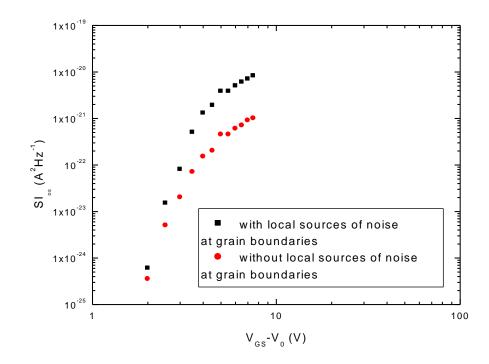

In the figure 4 we report the impact of the local sources of noise at the GBs on the noise level in the TFTs. The results show that the addition of sources of noise at the GBs leads to a significantly higher simulated drain current noise in the strong inversion region, and thus that the contribution of the grain boundaries on 1/f noise generation in TFTs is higher at the On-State.

### IV. CONCLUSION

Numerical simulations of low frequency noise in TFTs is presented. Noise is modelled by carrier fluctuations due to <u>GR mechanisms</u> of carriers from defects within the active layer. The study underlines the impact of the structural defects of polysilicon and/or of those induced by the design of the devices on the 1/f noise level in polysilicon TFTs.

#### **REFERENCES**

- [1] R.Carluccio, A.Corradetti, G.Fortunato, "Noise performances in polycrystalline silicon thin-film-transistors fabricated by excimer laser crystallization" Appl. Phys. Lett.,71(5), pp 578-580, 1997

- [2] L.Pichon, A.Boukhenoufa, C.Cordier, B.Cretu, «Determination of interface state distribution in polysilicon thin film transistors from low-frequency noise measurements: Application to analysis of electrical properties » *J. Appl. Phys.*, vol 100, 0545041-0545046, 2006

- [3] C.A.Dimitriadis, G.Kamarinos, J.Brini, « Model of Low Frequency Noise in Polycrystalline Silicon Thin-Film Transistors" IEEE Elect. Dev. Lett., vol. 22, N°8, pp 381-383, 2001

- [4] L.Pichon, K.Mourgues, F.Raoult, T.Mohammed-Brahim, K.Kis-Sion, D.Briand, O.Bonnaud, "Thin film transistors fabricated by in-situ doped unhydrogenated polysilicon films obtained by solid phase crystallization" *Semicond. Sci. Technol.*, 16, pp 918-924, 2001

- [5] J.F. Michaud, R. Rogel, T. Mohammed-Brahim, M. Sarret, O. Bonnaud, *Thin Solid Films* 487, p 81, 2005

- [6] DESSIS-ISE, ISE-TCAD Release 8.5, User's Manual, Zurich, 2004

- [7] G.Vincent, A.Chantre, D.Bois, « Electric field effect on the thermal emission of traps in semiconductors junctions » J. Appl. Phys. vol 50, N°8, pp 5484-5487, 1979

- [8] A.Boukhenoufa, L.Pichon, C.Cordier, B.Cretu, L.Ding, R.Carin, J. F. Michaud, T. Mohammed-Brahim "Apparent noise parameter bahvior in N-MOS transistors operating from subthreshold to above-threshold regions", CP780, Noise and Fluctuations: 18<sup>th</sup> International Conference on Noise and Fluctuations-ICNF 2005, edited by T. Gonzalez, J. Mateos, and D. Pardo, 2005, pp 319-322

- [9] E. P.Vandamme, L K.J.Vandamme, « Current crowding and its effect on 1/f noise and third harmonic distorsion a case-study for quality assessment of resistors », *Microelectron. Reliab.*, 40, pp 1847-1853, 2000

- [10] A.Mercha, L.K.J.Vandamme, L.Pichon, R.Carin, O.Bonnaud "Current crowding and 1/f noise in polycrystalline silicon thin film transistors" J. Appl. Phys., 90, N°8, pp 4019-4026, 2001

- [11] L.K.J.Vandamme, H.J.Casier, "The 1/f noise versus sheet resistance in poly-Si is similar to poly-SiGe resistors and Au-layers" Proceedings of 34<sup>th</sup> ESSDERC, editors R.P.Mertens and C.L.Claeys, pp 365-368, 2004. ISBN 0-7803-84-78-4

## Figure captions

- Figure 1: Schematic cross-section structure of devices for 2D simulation, (a) FSPC TFT, (b) LSPC TFT. For simplicity, all Grain Boundaries (GBs) are not represented on the figure. <u>Inset: schematic thermally assisted tunnelling process at grain boundaries.</u>

- Figure 2: Experimental and simulated noise current spectra at different gate voltages for (a) FSPC TFT (W/L= $50\mu m/20\mu m$ ) and (b) LSPC TFT (W/L= $80\mu m/60\mu m$ ) biased in the linear mode (V<sub>DS</sub>=300mV). <u>Insets:</u> Plots of the normalized noise current spectral versus the corresponding measured drain current.

- Figure 3: Noise parameters versus effective gate voltage. Flatband voltage  $V_0$  is approximatively identified to the gate voltage corresponding to the minimum of drain current.  $\alpha_{app}$  is deduced from measurements of  $S_{IDS}$ , and  $\alpha_H$  by fitting the calculation according to (1) and (3) of  $S_{IDS}$  with the corresponding measurements. Inset: Calculated  $C_{us}$  versus  $R_{sh}$  for FSPC and LSPC TFTs.

- Figure 4: Simulated noise current spectral versus effective gate voltage in TFT: effect of local source of noise at the grain boundaries on noise level.

Figure 1

Figure 2

Figure 3

Figure 4