### TECHNISCHE UNIVERSITÄT HAMBURG

#### Master's Thesis

# Dynamic Symbolic Execution for Enhanced Intermediate Representation of Data Flow Space Applications

Author:

Hany Abdelmaksoud

Degree Program:

M.Sc. Mechatronics

First Examiner:

Prof. Dr.-Ing. Görschwin Fey

Second Examiner:

Prof. Dr.-Ing. Thorsten A. Kern

Supervisor:

Dr.-Ing. Zain A. H. Hammadeh German Aerospace Center (DLR)

March 23, 2022

## ABSTRACT

Verifying the safety and security requirements of embedded software requires a code analysis. Many software systems are developed based on software development libraries; therefore, code specifications are known at compiling time. Hence, many source-code analyses will be excluded, and low-level intermediate representations (LLIRs) of the analyzed binaries are preferred. Improving the expressiveness of the LLIR and enhancing it with more information from the binaries will improve the tightness of the applied analyses. This work is interested in developing a lifter that lifts binaries into an enhanced LLIR and can resolve indirect jumps. LLVM is used as the LLIR.

Our proposed lifter, which we call DEL (Dynamic symbolic Execution Lifter), combines both static and dynamic symbolic execution and strives to fully recover the analyzed program's control flow. DEL consists of an API to translate ARMv7-M assembly instructions into static single assignment LLVM instructions, an LLIR to Z3 expressions parser, a memory model, a register model, and a specialized condition flags handler. This work used a case study based on a software development library for onboard data-handling applications developed at the German Aerospace Center (DLR), which is called the Tasking Framework. DEL demonstrated high accuracy of around 93% in resolving indirect jumps in our case study.

# **DECLARATION**

I hereby declare on oath that the work in this thesis was composed and originated by myself and has not been submitted for another degree or diploma at any university or other institute of tertiary education. I certify that all information sources and literature used are indicated in the text and a list of references is given in the bibliography.

Hany Abdelmaksoud

Hamburg, March 23, 2022

# Contents

| 1 | Intr         | roduction 1                                            | 3         |  |  |  |  |  |  |

|---|--------------|--------------------------------------------------------|-----------|--|--|--|--|--|--|

|   | 1.1          | Contribution                                           | 6         |  |  |  |  |  |  |

|   | 1.2          | Structure                                              | 6         |  |  |  |  |  |  |

| 2 | Stat         | State of the art                                       |           |  |  |  |  |  |  |

|   | 2.1          | Binary lifting                                         | 8         |  |  |  |  |  |  |

|   |              | 2.1.1 General Phases of Binary Lifting                 | 9         |  |  |  |  |  |  |

|   |              |                                                        | 26        |  |  |  |  |  |  |

|   | 2.2          |                                                        | 27        |  |  |  |  |  |  |

|   |              | v                                                      | 28        |  |  |  |  |  |  |

|   |              | 2.2.2 BinRec                                           | 28        |  |  |  |  |  |  |

|   |              |                                                        | 29        |  |  |  |  |  |  |

|   |              |                                                        | 29        |  |  |  |  |  |  |

|   |              |                                                        | 80        |  |  |  |  |  |  |

|   |              |                                                        |           |  |  |  |  |  |  |

| 3 | Tas          | 6                                                      | 1         |  |  |  |  |  |  |

|   | 3.1          | Task-Channel Model                                     | 32        |  |  |  |  |  |  |

|   | 3.2          | Execution Model                                        | 32        |  |  |  |  |  |  |

|   | 3.3          | Tasking Framework in use                               | 35        |  |  |  |  |  |  |

|   | 3.4          | Tasking Framework as a C++ Library                     | 35        |  |  |  |  |  |  |

|   | 3.5          | Tasking Framework and its relevance to static analysis | 6         |  |  |  |  |  |  |

|   | 3.6          | Tasking Framework in this thesis                       | 86        |  |  |  |  |  |  |

| 4 | DE           | L Lifter                                               | 9         |  |  |  |  |  |  |

|   | 4.1          | Motivation                                             | 9         |  |  |  |  |  |  |

|   | 4.2          |                                                        | 2         |  |  |  |  |  |  |

|   | 4.3          |                                                        | 18        |  |  |  |  |  |  |

|   | 4.4          |                                                        | 60        |  |  |  |  |  |  |

|   |              | 1                                                      | 60        |  |  |  |  |  |  |

|   |              | 1                                                      | 60        |  |  |  |  |  |  |

|   |              |                                                        | $\dot{2}$ |  |  |  |  |  |  |

|   |              |                                                        | 62        |  |  |  |  |  |  |

|   |              | V                                                      | 55        |  |  |  |  |  |  |

| 5 | Evo          | luation 5                                              | 9         |  |  |  |  |  |  |

| 9 | 5.1          |                                                        | 59        |  |  |  |  |  |  |

|   | $5.1 \\ 5.2$ |                                                        | 54        |  |  |  |  |  |  |

|   | 9.2          | 0 0                                                    | :1        |  |  |  |  |  |  |

8 CONTENTS

|              |                                           | 5.2.3<br>5.2.4 | Indirect jumps' results          | 65<br>65<br>75<br>75<br>76<br>76 |

|--------------|-------------------------------------------|----------------|----------------------------------|----------------------------------|

| 6            | 6.1                                       |                | nsion                            | <b>77</b><br>77<br>77            |

| Re           | fere                                      | nces           |                                  | <b>7</b> 8                       |

| ΑĮ           | pen                                       | dices          |                                  | <b>7</b> 9                       |

| A            | The                                       | Taski          | ng Framework's Join fork example | <b>7</b> 9                       |

| В            | B Example DSEIR module                    |                |                                  |                                  |

| $\mathbf{C}$ | C Relevant Tasking Framework header files |                |                                  |                                  |

# List of Figures

| 1.1 | The two approaches to get an IR, compiling source code and lifting binaries         | 14 |

|-----|-------------------------------------------------------------------------------------|----|

| 1.2 | From source code to CFG                                                             | 15 |

| 2.1 | A lifted IR instance of Valgrind [62].                                              | 18 |

| 2.2 | Binary lifting stages                                                               | 19 |

| 2.3 | DEL 's reconstructed CFG for WCET crc benchmark [6]                                 | 24 |

| 2.4 | DEL 's reconstructed CFG for the icrc1 function                                     | 25 |

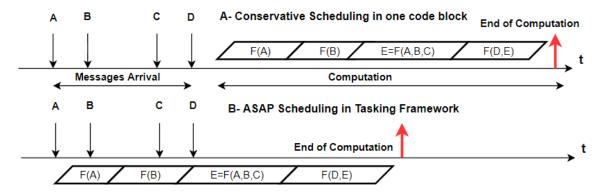

| 3.1 | Scheduling in the Tasking Framework adapted from [10]                               | 31 |

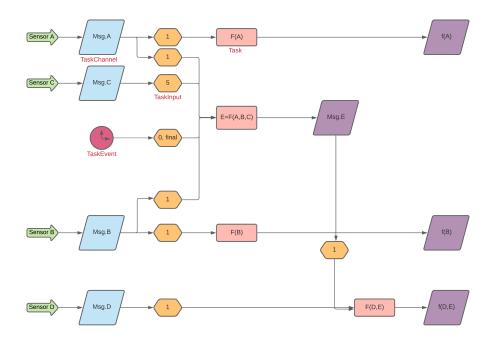

| 3.2 | Task Channel Model adapted from [10]                                                | 32 |

| 3.3 | BIRD - AOCS and the Tasking Framework Components adapted from [10]                  | 33 |

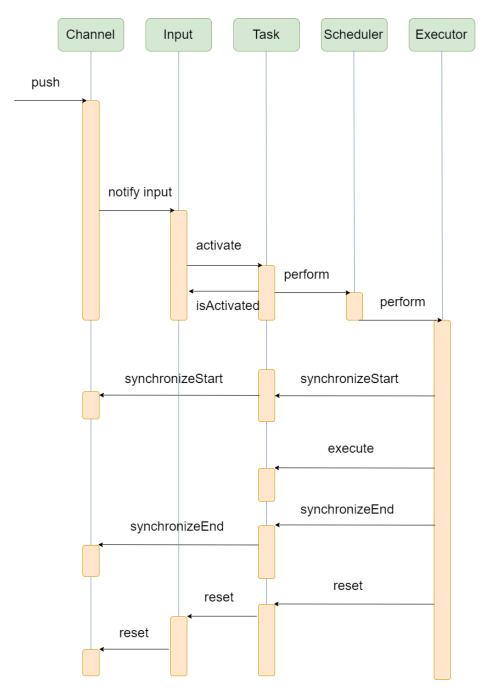

| 3.4 | The Tasking Framework's sequence diagram adapted from [10]                          | 34 |

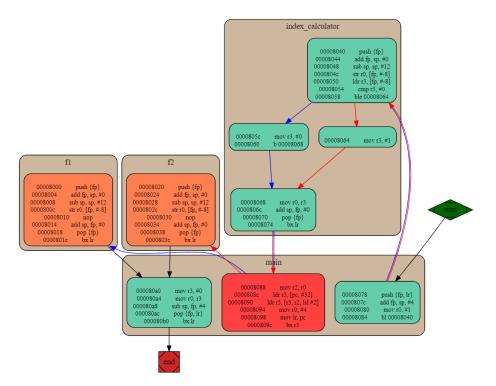

| 4.1 | Two potential paths from the main entry point till the basic block of the indirect  |    |

|     | jump (00008088)                                                                     | 40 |

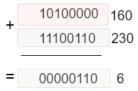

| 4.2 | Bit-vector addition with overflow example                                           | 46 |

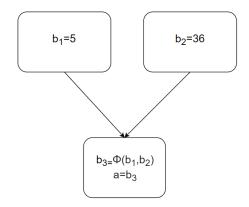

| 4.3 | $\Phi$ Function adapted from [10]                                                   | 47 |

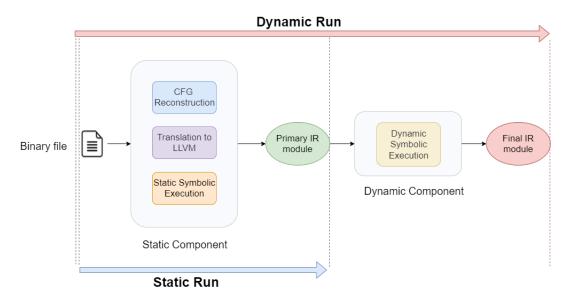

| 4.4 | DEL 's static and dynamic run modes                                                 | 49 |

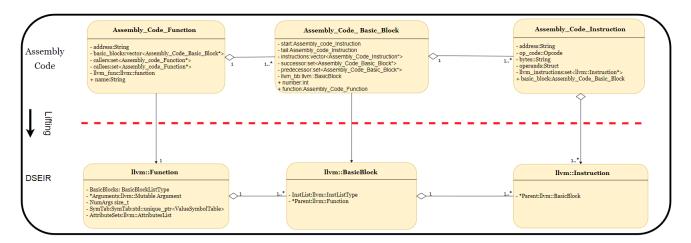

| 4.5 | DEL 's UML class diagram.                                                           | 51 |

| 4.6 | An indirect jump's relevant instructions highlighted in yellow                      | 54 |

| 5.1 | Six potential paths from the start entry point till the basic block of the indirect |    |

|     | jump (000080dc)                                                                     | 62 |

| 5.2 | DEL's full re_constructed control flow graph of the example program                 | 63 |

| 5.3 | Experimental setup                                                                  | 65 |

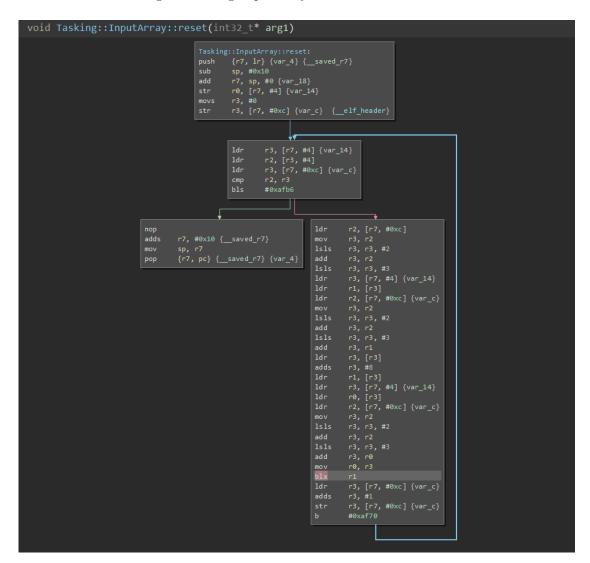

| 5.4 | Tasking::InputArray::reset function CFG                                             | 66 |

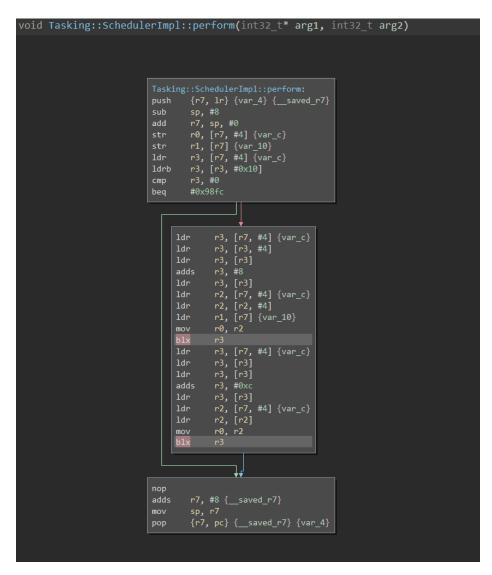

| 5.5 | Tasking::SchedulerImpl::perform function CFG                                        | 68 |

| 5.6 | Tasking::TaskImpl::synchronizeStart function CFG                                    | 69 |

| 5.7 | Tasking::TaskImpl::synchronizeStart function CFG                                    | 71 |

| 5.8 | Tasking::clock::isPending function CFG                                              | 73 |

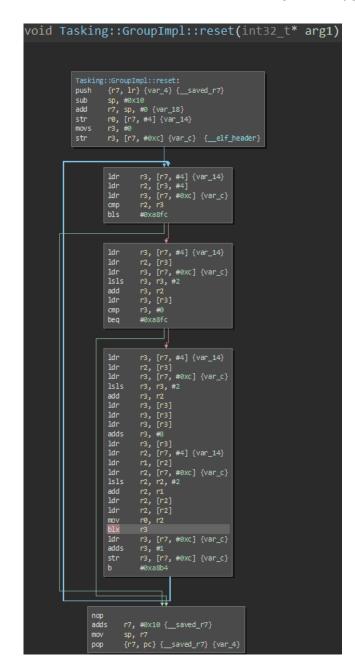

| 5.9 | Tasking::GroupImpl::reset function CFG.                                             | 74 |

# List of Tables

| 4.1 | DSEIR example table                                  | 52 |

|-----|------------------------------------------------------|----|

| 5.1 | Performance results: Angr vs DEL                     | 31 |

| 5.2 | Tasking::InputArray::reset function results          | 37 |

| 5.3 | Tasking::SchedulerImpl::perform function results     | 38 |

| 5.4 | Tasking::TaskImpl::synchronizeStart function results | 70 |

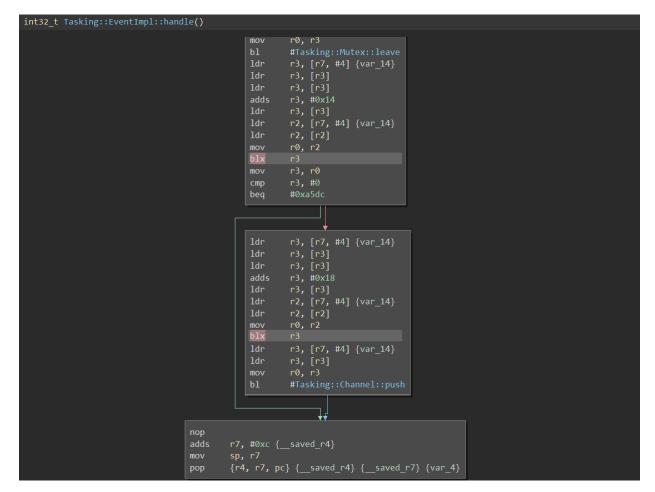

| 5.5 | Tasking::EventImpl::handle function results          | 71 |

| 5.6 | Tasking::clock::isPending function results           | 73 |

| 5.7 | Tasking::GroupImpl::reset function results           | 74 |

| 5.8 | Join fork case study overall results                 | 75 |

| 5.9 | Performance results                                  | 75 |

# Acronyms

AOCS Attitude and Orbit Control System

APSR Application Processor Status Register

ARGV Argument Vector

ASAP As Soon As Possible Scheduling

ATON Autonomous Terrain-based Optical Navigation

**BIRD** Bi-spectral Infrared Detection Representation

CFG Control Flow Graph

CPSR Current Processor Status Register

**DEL** Dynamic symbolic Execution Lifter

**DLR** Deutsches Zentrum für Luft- und Raumfahrt

**DSE** Dynamic Symbolic Execution

**DSEIR** Dynamic Symbolic Executable Intermediate Representation

Eu:CROPIS Euglena Combined Regenerative Organic Food Production In Space

${f ICFTS}$  Indirect Control Flow Targets

IR Intermediate Representation

**ISA** Instruction Set Architecture

ODARIS On-board Data Analysis and Real-time Information System

OSRA Offset Shifted Range Analysis

PIC Position Independant Code

ScOSA Scalable On-Board Computing for Space Avionics

${\bf SET}$  Simple Expression Tracker

SSA Static Single Assignment

SSE Static Symbolic Execution

UCSE Under Constrained Symbolic Execution

WCET Worst Case Execution Time

### Chapter 1

# Introduction

Designing embedded systems for space applications is a complicated process. The modernization of aerospace systems has given rise to more-electric technologies and tightly interconnected architectures, contributing to a considerable increase in design complexity. Various architectural design approaches develop these systems effectively and efficiently. Because of its capacity to address the complexity of systems, the model-based approach is amongst the most ubiquitous design techniques [10]. The model-based approach entails creating models as rudimentary blocks, which create the entire embedded system's software using code that is generated automatically [10]. This approach enhances productivity and guarantees the correctness of the software as the applications are implemented in a structured and error-proof manner [10]. There are numerous software analysis techniques that can be applied on the developed models including data flow analysis [12, 72], worst-case execution time analysis (WCET) [80], input/output analysis [54], and security analysis [33]. Nevertheless, their analysis becomes increasingly challenging because the developed models are intricate and dynamic.

The Tasking Framework is a model-based framework developed by the German Aerospace Center's Institute for Software Technology (DLR). This software library supports the scheduling of embedded software space systems. Tasks are represented in the Taking Framework as graphs of tasks with arbitrary activation patterns. It is implemented in C++ and follows an eventdriven paradigm. The framework's capabilities have been applied to a wide range of non-safety critical aerospace applications since its inception, including [76] and [45]. The Tasking Framework must be certified for use in safety-critical applications, which can be indeed an arduous process. The ECS-Q-ST-40C is the most commonly used certification standard for aerospace-embedded programs and the standard for validating implementation and verification tools [1]. It defines five levels of design assurance, varying between E-Level, which requires the least amount of testing and verification, to A-Level, which necessitates significant testing and verification. The standard demands the Tasking Framework at the very least to demonstrate functional correctness and the absence of dangers in the software to get qualified for the C-Level certification. The presented proofs must not be vulnerable to any logical or reasonable objections. It is required to show that all real-time tasks are completed on time or that missing the deadlines will not jeopardize the system's safety [10].

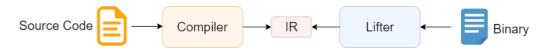

The computation of the WCET helps establish deadline correctness. A precise WCET analysis requires detailed architectural knowledge. Performing a WCET analysis to the source code of the Tasking Framework makes it language-dependent, while analyzing its binaries is hardware-dependent. Consequently, analyzing at the intermediate representation (IR) level proves a more viable option. An IR is the data format used inside a compiler or virtual machine to represent

source code. It is designed to be suitable for post-processing, for instance, optimization and translation. It should accurately represent the source code with no loss of information – and independent of any specific source or target language. Strictly speaking, there are two approaches to acquiring the IR of a program, as shown in Figure 1.1, is either through compiling source code or through lifting binaries.

Nevertheless, the high-level IR acquired from compilers lacks information about the memory model and ignores linking effects. As a result, low-level IRs acquired through binary lifting have become an increasingly attractive alternative for performing software analyses at the intermediate level of a program. Even so, due to underlying factors such as the handling of condition flags and resolving indirect control flow targets, it is pretty challenging to generate a highly accurate and 100% representative IR.

Figure 1.1: The two approaches to get an IR, compiling source code and lifting binaries.

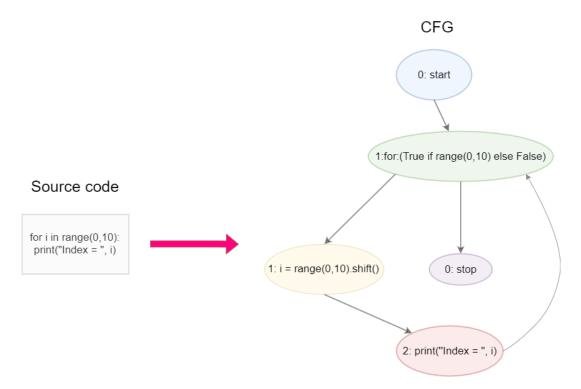

An IR should be able to capture the control flow of the original program. A control flow graph (CFG) illustrates such flow. Figure 1.2 showcases the CFG of a simple Python program. A CFG represents all possible paths a program takes during execution in program analysis. The CFG consists of nodes exhibiting blocks of instructions and directed edges exhibiting control flow jumps [90]. The CFG is the cornerstone of numerous program analysis techniques, such as taint analysis [44, 84] and symbolic execution [53, 73]. The CFG is also prominent in program verification [42, 70], malware detection [28, 47], code similarity analysis [63, 74], and software vulnerability detection [49, 87]. Consequently, implementing the right approach to generate a complete and accurate CFG while lifting to an IR is imperative [90].

Nevertheless, indirect jumps present a challenge when constructing complete CFGs [31]. We can classify a jump instruction as either direct or indirect. A direct jump has a statically determined target which refers to a specific location in the program; however, for an indirect jump, the jump target is execution-dependent and is only known at run-time [90]. In most cases, indirect branches provide dynamic programming behaviors by implementing standard programming constructs such as function pointers and virtual function calls [90]. While indirect jumps are ubiquitous and helpful, a purely static analysis often fails to resolve an indirect jump's target due to its dynamic nature, which poses intrinsic issues when lifting into an IR module that mirrors a complete CFG.

There are two lifting solutions available today: static lifting and dynamic lifting. Static techniques do not require executing the target programs; instead, they only need to examine their code structure. These approaches offer high code coverage at a low time cost. As a result, static lifting tools like McSema [2] are used extensively in a wide range of analyses. Nevertheless, static techniques lack completeness because of their inability to resolve indirect jump relations [90]. A dynamic lifter such as BinRec [14] on the other hand, runs programs on a set of test suites and acquires control flow information from the traces of the execution while lifting. This dynamic approach is capable of resolving several indirect jumps. However, the precision of the CFG constructed by it is determined by how well the test cases cover indirect jumps. Xu et al. [85] proposed forcing a program's execution to investigate both possible paths of each conditional branch in order to increase test case coverage. Although forced execution is a powerful tool for analyses, it still lacks sufficient coverage for large-scale programs.

In this thesis, we propose a novel hybrid static-dynamic symbolic execution lifter (DEL) that

Figure 1.2: From source code to CFG.

combines both dynamic and static techniques while lifting to a low-level virtual machine (LLVM) [3] IR. Our approach is motivated by the fact that each indirect jump in the program can have multiple potential-jump targets. Each indirect jump's target calculation depends on an input-based potential execution path starting from the program's entry point up to the basic block that terminates with the indirect jump in question.

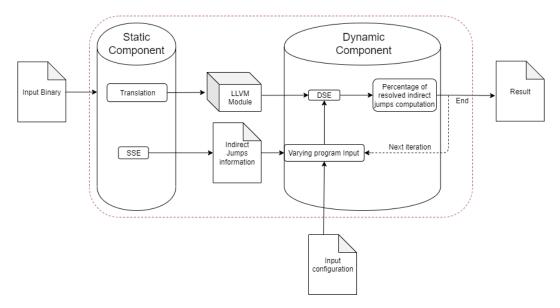

Our key insight is to combine static and dynamic symbolic execution while lifting to resolve all potential-jump targets of each indirect branch instruction. More specifically, The static part of our approach aims to construct a preliminary IR module while generating a mathematical expression for each potential-jump target address of each indirect jump detected in the binary we aim to lift. The dynamic part then performs the dynamic symbolic execution (DSE) [78] of the statically generated IR module to resolve all individual expressions of each potential-jump target of all indirect jumps to a concrete value. DEL uses Microsoft's Z3 [37] solver for its DSE engine. We suggested an iterative approach of varying the program's input during the dynamic analysis continuously. By varying the program input, we aim to explore all possible execution paths leading to an indirect jump instruction's basic block and resolve all possible potential-jump targets for each indirect jump detected. As the final output, we consider the IR constructed through multiple iterations.

In order to lift into a more complete and representative IR for the Tasking Framework, DEL implements its memory and register model. The lifted IR module captures the effects of each instruction on the state of the memory and register model and the effects of each instruction on the state of the condition flags.

#### 1.1 Contribution

Nowadays, binary lifting tools rely heavily on static disassembly techniques and heuristics to disassemble binaries, an approach that fails to identify indirect control-flow targets, accurately distinguish between data constants and code pointers, and correctly interpret instruction and data byte boundaries. In this thesis, we present DEL, a new optimized approach of dynamic binary lifting to a low-level IR. DEL makes it possible to make use of current IR-level compiler analyses on binaries where static lifting falls short. DEL integrates symbolic execution into the lifting process to generate an enhanced IR that models the state of the memory, registers, and condition flags of the program as it executes. We divided our work into the following tasks.

#### • Overview of the state-of-the-art lifting tools and techniques

We present an overview of the available lifting tools and techniques.

• Introducing a new hybrid approach for lifting binaries into an enhanced intermediate representation

We introduce a new hybrid lifting approach that tackles issues related to existing lifting tools.

#### • Comprehensive Evaluation

We evaluate the percentage of indirect control flow targets resolved by our lifting approach for a given test case of the Tasking Framework.

#### 1.2 Structure

Following is an outline of this thesis. Chapter two discusses program analysis at the IR level and presents an overview of the state-of-the-art lifting tools and techniques. Chapter three presents the Tasking Framework and its relevance for IR analysis. Chapter four presents our new dynamic lifting tool DEL and its enhanced generated IR module features. Chapter five discusses the results of our approach. Finally, Chapter six presents our discussion and future steps.

### Chapter 2

# State of the art

Many safety and security analyses can be performed on the IR of a program. An application could have one of two IRs, one that is spawned from binary lifters, the other from compilers. Both IRs possess expressive capabilities that set them apart. IRs obtained from source code exhibit high-level language constructs such as loops and functions. Alternatively, IRs obtained from a binary lifter do not have to take into account these language abstractions in their underlying syntax tree. Using a binary lifter to derive the IR of a program could be especially useful when the analyses require information that cannot be extracted from the source code. This thesis focuses on IRs acquired from binary lifters and does not consider the work of compilers in IR generation.

In an IR code analysis, various analysis techniques are typically used to model data types, flows, and control paths of the program being analyzed. The refined model can then be evaluated to identify well-known security issues. The results can be compiled into comprehensive vulnerability reports with effective practical countering actions to tackle such vulnerabilities.

There are two approaches when analyzing at the IR level: static and dynamic analyses.

#### • Static analysis

A static analysis examines programs to obtain specific code characteristics and behaviors before it is run. It is extensively utilized in many compiler optimizations and program analyses. It gives the chance to collect information about programs without executing them, thus acquiring a minimal or zero runtime cost [88]. A static analysis typically identifies bugs preceding the execution of a program (e.g., between coding and unit testing).

#### • Dynamic analysis

A dynamic analysis entails examining a particular program as it runs. Various tools are available for dynamic analysis, including profilers, checkers, and execution visualizers. A program could have code for analysis incorporated fully inline or external routines that are invoked by the inline analysis code. This code runs in the background, not disrupting the program's normal execution (other than maybe slugging it down), but instead carries out additional work (during the analysis session), such as checking for bugs or assessing performance [61]. A dynamic analysis pinpoints potential bugs that may appear when a program is run (e.g., during unit testing).

Both strategies complement one another. A static analysis is generally reliable, as it considers all execution paths in a program. A dynamic analysis, however, is usually less pessimistic than a static analysis because it employs real values "in the perfect light of runtime" [38]. However, it

lacks sound reasoning, as it only examines a single execution path [41]. Consequently, in reality, a dynamic analysis tends to be far less complex than a static analysis.

As we move forward, we examine the first step of analyzing at the IR level: the generation of an IR module through binary lifting.

#### 2.1 Binary lifting

Binary lifting is transforming a binary executable into a higher-level intermediate language. A crucial part of binary translation, analysis, and instrumentation applications is the translation of low-level machine instructions into higher-level IR [52]. A mapping table between machine instructions and IR is usually manually created in these systems. The mapping table designates a single or a set of IR instructions to each assembly code instruction in the Instruction Set Architecture (ISA). ISA cross-compatibility is typically achieved with this method. A formal definition of binary lifting adapted from [52] is as follows:

#### **Definition 1** (Binary Lifting).

Binary lifting is a function  $\uparrow_{ins}^{tar}$ :  $I_{ISA}^{ins} \to I_{IR}^{tar}$ , where  $I_{ISA}$  is an instruction from a specific ISA,  $I_{IR}$  is an IR instruction, *ins* is the name of an ISA and tar is the target IR we would like to lift to.

For example,  $I_{ISA}^{x86}$  means x86 assembly language, and  $I_{IR}^{VEX}$  is VEX IR.  $\uparrow_{x86}^{vex}$  is a function to which an x86 binary code is given as input and outputs a translated VEX instance. So the expression  $\uparrow_{vex}^{x86}(0x41)$  lifts the binary instruction 0x41 into a VEX IR instance as highlighted in Figure 2.1, 0x41 is the inc ecx when decoded. A tool that conducts this process of lifting binaries is called a binary lifter.

```

1 t2 = GET:I32(ecx)

2 t1 = Add32(t2,0x00000001)

3 t3 = GET:I32(cc_op)

4 t4 = GET:I32(cc_dep1)

5 t5 = GET:I32(cc_dep2)

6 t6 = GET:I32(cc_ndep)

7 t7 = x86g_calculate_eflags_c(t3,t4,t5,t6):Ity_I32

8 PUT(cc_ndep) = t7

9 PUT(cc_op) = 0x00000012

10 PUT(cc_dep1) = t1

11 PUT(cc_dep2) = 0x00000000

12 PUT(ecx) = t1

13 PUT(eip) = 0x00000001; Ijk_Boring

```

Figure 2.1: A lifted IR instance of Valgrind [62].

The term Binary-Based IR was first introduced by [52] to differentiate between two types of IRs: one derived from binary lifters, the other from compilers. The main distinguishing feature between Binary-Based IRs and IRs from compiler theory [11] is their expressive ability [52]. IRs generated from source code exhibit high-level language constructs such as loops and functions. However, Binary-Based IRs do not need to take such language components into account in their abstract syntax tree [52]. Binary analysis tools like Valgrind and bap create their own Binary-Based IRs to convey the semantics of binary code at a low level.

Strictly speaking, Binary-Based IRs have two main properties: explicitness and self-containment [52]. A Binary-Based IR is said to be explicit if it updates only a single variable in the execution context. On the other hand, the self-containment property of a Binary-Based IR basically demonstrates whether or not it fully reflects the relevant binary code semantics. For instance,

In QEMU [24], the semantics of binary instructions are often expressed with external functions. Here, is an example from [52] of a logical AND instruction in x86: pand xmm0, xmm1. Upon lifting the instruction to the Binary IR of QEMU (TCG), the IR instance directly forwards both operands to an external function named pandxmm rather than explicitly defining its operation within the IR's semantics. In this scenario, [52] argued that the IR instance is not self-contained since it has a side-effect.

Typically, in IR analysis, The explicitness helps perform control- and data-flow analyses; however, self-containment makes it possible to conduct analyses without unwanted over-approximation [52].

#### 2.1.1 General Phases of Binary Lifting

This section highlights the common steps that a binary lifting tool goes through to transform binaries to a higher-level intermediate representation. Figure 2.2 illustrates these steps according to the logical order of their application to low-level code.

The first step in lifting binary code is to disassemble it. In the next section, we will discuss the different disassembly methods currently used in practice.

Figure 2.2: Binary lifting stages.

#### • Disassembly

Disassembly is the translation of a program from machine code into assembly language [55]. Next, we highlight the two different disassembly techniques currently employed by existing binary analysis tools.

#### - Disassembly methods

#### \* Static disassembly

A static disassembler reads the binary from a file and parses the headers and section contents to disassemble it. This technique has zero runtime overhead because all of the work takes place offline. When utilized by tools like profilers and binary rewriters, the output of a static disassembler can boost performance [20]. The GNU objdump utility is a good example of a static disassembler.

By far, the most well-known disassembler for static analysis and reverse engineering is IDA pro [4]. To find function start addresses, IDA Pro utilizes a depth-first call-graph traversal. The disassembler can accurately identify only functions that are directly called. For indirect function calls, however, it uses heuristics like scanning for conventional function prologue patterns. Nevertheless, the applied heuristics are not portable to other architectures and are complex to implement [40]. Even with the high static disassembly coverage of IDA Pro, it cannot be used in analyses that have no tolerance for intermittent errors in the disassembly output [20].

#### \* Dynamic disassembly

A dynamic disassembler interacts with the software to be disassembled. Each instruction is deconstructed before it is executed as the software runs. The key benefit of this method is that data and code can be differentiated because the

disassembler only disassembles the instructions that will be executed. As instructions are deconstructed and executed, it becomes possible to use dynamic disassemblers with self-modifying code [20].

Because control must be passed to the disassembler before each instruction can be carried out, the performance of dynamic disassemblers is their worst flaw. In other words, the application runtime is significantly slowed down since control must be handed to the disassembler prior to the execution of each instruction. Moreover, disassemblers that use dynamic disassembly do not provide full code coverage since such a technique only disassembles specific program paths, which are executed given a predefined program input [20].

Despite the runtime overhead and low coverage of dynamic disassembly, [20] argued that the approach's ability to resolve indirect control flow targets makes it very useful for much current instrumentation and binary analysis tools, including Pin [58] and Valgrind [62].

```

804964a: bf 00

804964c: 55

push%ebp

nop

804964c: 55

push%ebp

804964d: 89 e5

mov %esp,%ebp

8049644 89 65

804964f · 53

push%ebx

mov %esp,%ebp

804964f: 53

push%ebx

8049650: 83 ec 04

sub $0x4.%esp

8049650: 83 ec 04

jmp 0x8049658

sub $0x4.%esp

8049653: eb 04

8049653: eb 04

jmp 0x8049658

8049655: e6 02

out 0x2, al

8049655: e6 02 04

<junk>

8049657: 04 be

add al, Oxbe

8049658: be 05 00 00 00

8049659: 05 00 00 00 12

add eax,0x12000

mov 1$0x5, %esi

```

Listing 1: Dynamic Disassembly Output.

Listing 2: Linear Disassembly Output.

#### - Disassembly algorithms

#### \* Linear sweep

Utilizing the linear sweep algorithm is the easiest and quickest way to disassemble binaries [20]. The GNU disassembler, objdump, is based on such algorithm [5]. The disassembly commences from the entry point found in the binary's header in virtually every binary. Each consecutive instruction is disassembled from the subsequent position, which is determined by adding the current instruction's length to its start address.

Linn and Debray's publication [57] is the foundation for the linear sweep method. Algorithm 1 from [57] below is a pseudocode depiction of the linear disassembly approach's theoretical implementation.

The linear sweep algorithm, however, has its shortcomings. Its main flaw is that it cannot differentiate between data and code. Any data contained in the code is disassembled incorrectly [20]. Above is a sample log from [20] that includes the attested disassembled output using a dynamic disassembler shown in Listing 1 and that of objdump shown in Listing 2. [20] demonstrated through the runtime disassembler output that some garbage bytes are stored following the jump instruction. The jump target follows the current instruction, 0x8049658, by 0x4 bytes. They argued that it is possible that the garbage bytes are perhaps data or merely alignment bytes. When using a linear disassembler, following the rendering of the two-byte jump instruction that appears at address 0x8049653, the disassembler proceeds with decoding at address 0x8049655, which is most likely not code. As a result, the actual jump destination is wrongly deconstructed, and

the output is a jump in the middle of the instruction [20].

#### \* Recursive traversal

The recursive traversal algorithm traverses through one starting address to one end address in a sequential manner for every recursive traversal call. If the algorithm has visited an address already, the procedure will return. Otherwise, the algorithm decodes the current address instruction and checks whether it is a jump or a call instruction. In this approach, potential branches and function calls are followed to identify new controlling edges.

Algorithm 2 from [57] highlights the pseudocode characterization of a recursive traversal algorithm. Because it considers the control flow in the binary, the recursive traversal approach has several advantages over the linear sweep [20]. For example, data is not falsely identified as code. As a jump instruction is disassembled, the disassembler decodes the jump target rather than heedlessly disassembling the next instruction. However, code accessed by indirect control flow transfers is not disassembled by a recursive disassembly algorithm [20].

```

Algorithm 2 Recursive Traversal Algorithm

1 Require: startAddress, endAddress

procedure RECURSIVETRAVERSAL(addr)

2

while startAddress \le addr < endAddress do

3

if addr has already been visited then return

4

I \leftarrow decode\ instruction\ at\ address\ (addr)

5

markaddr\ as\ visited

6

if I is branch or function call then

for all possible targets t of I do recursive Traversal(t)

8

10

else

addr = addr + length(I)

11

12

procedure MAIN

13

startAddress \leftarrow address \ of \ the \ first \ executable \ byte

endAddress \leftarrow address \ of \ the \ last \ executable \ byte

14

linear sweep(entry point)

15

```

#### • Control flow graph re-construction

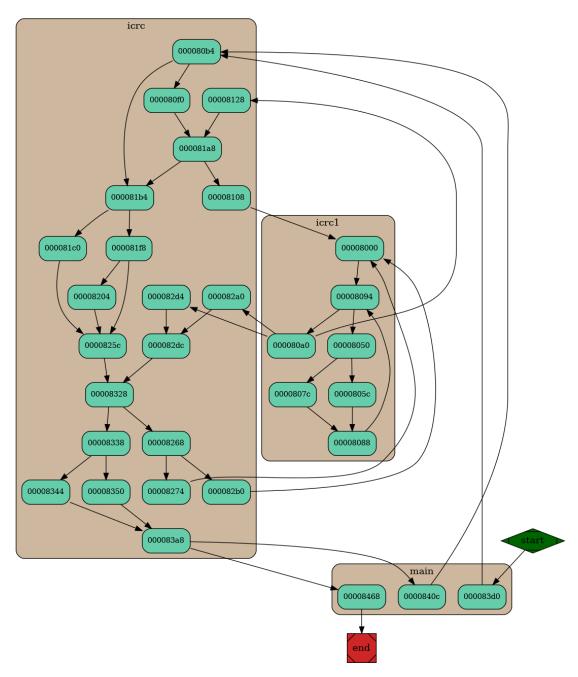

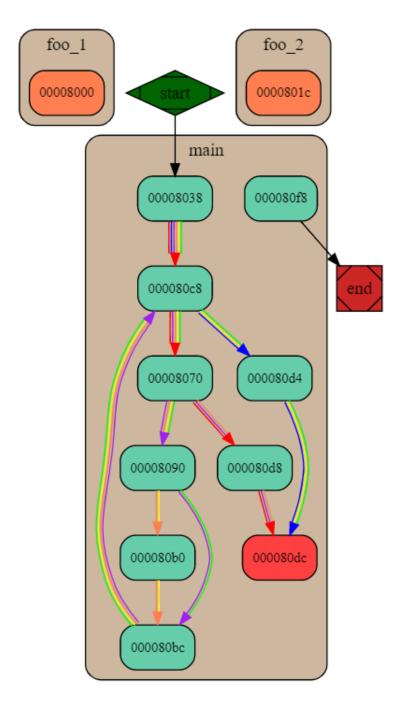

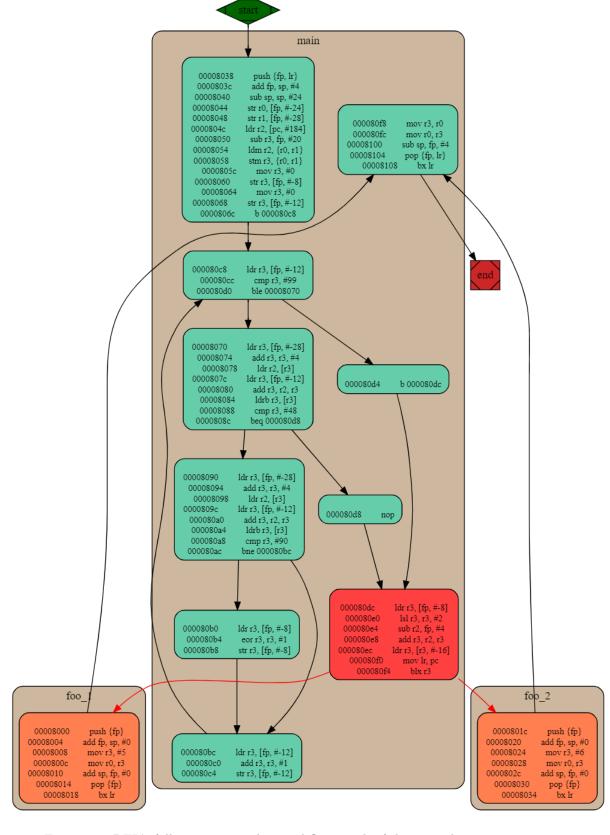

For binary analyses, a Control Flow Graph (CFG) is indispensable. It is a graph that illustrates all paths that could potentially be taken throughout the execution of a program. Figure 2.3 shows a sample CFG built for the Mälardalen WCET crc benchmark binaries [6]. In this example, there are three functions, icrc, icrc1, and main. Each function in the

source code is viewed as a cluster of interlinked basic blocks. Each basic block is represented by a node containing the address of the first instruction in that basic block.

A CFG is required for conducting an accurate IR analysis. For most IR analysis algorithms, the flow of the program being analyzed is a crucial consideration, and hence such algorithms indeed require a CFG. Following the disassembly of binary code, it is necessary to create a CFG or build on the premise of one created before disassembly.

There are numerous algorithms to choose from for building CFGs. A disassembler can readily determine the targets of the edges caused by direct branches and call instructions and append the edges for them to the CFG. Like any static disassembler, IDA Pro, for example, creates a CFG with only the direct branch and call instructions as edges without considering indirect jumps.

The traditional method for creating a CFG is to begin at the start of a function and continue through instructions. At first, the CFG has neither nodes nor edges. The algorithm begins at the point of entry, and whenever a jump command is found, the current basic block ends. Generally, a basic block contains instructions devoid of branching instructions or targets of branching instructions between them. In other words, in a basic block, an instruction is executed prior to the instructions in subsequent addresses in the same basic block, with no instruction being executed in the middle [88].

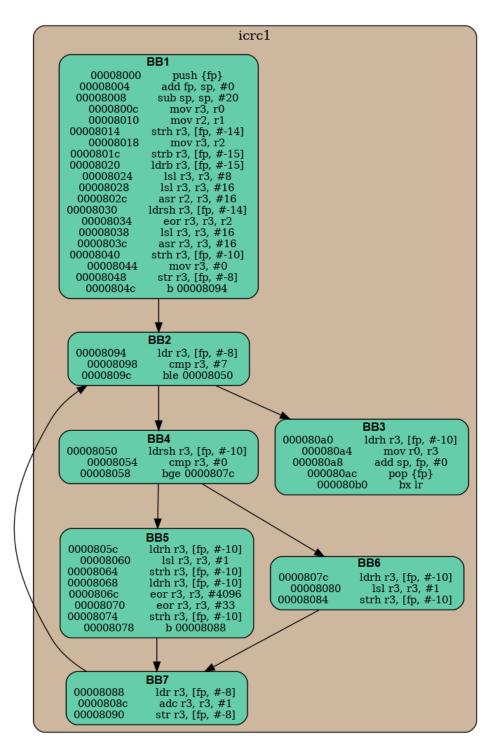

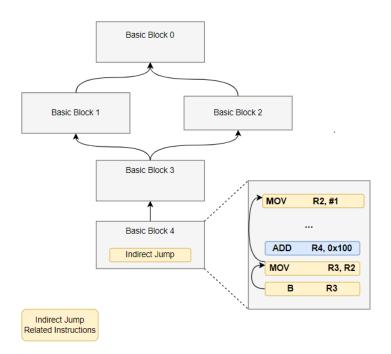

For example, in the code snippet of Listing 3 of the function icrc1 in Mälardalen WCET crc benchmark, Figure 2.4 shows that the icrc1 function is constructed of 7 basic blocks. Each basic block ends with a branching instruction such as the basic block labeled BB1 or ends with an assembly instruction immediately preceding an instruction targetted by a jump instruction. A good example for the latter case would be BB6, where its last instruction of address 0x00008084 directly precedes the load instruction of address 0x00008088, which is the target address of the unconditional branching instruction 0x00008078 of BB5.

```

unsigned short icrc1(unsigned short CRC, unsigned char onech)

2

{

3

unsigned short ans=(crc^onech << 8);</pre>

5

for (i=0:i<8:i++) {

6

if (ans & 0x8000)

ans = (ans <<= 1) ^ 4129;

8

else

9

ans <<= 1;

10

11

12

return ans:

}

13

```

Listing 3: Icrc1 source code from Mälardalen WCET crc benchmark [6].

Even though the standard approach for CFG construction mentioned above is frequently used in analyzing the control flow of both the source and intermediate level representations generated by compilers, it cannot be applied in the opposite direction when binaries are statically lifted into IR. There are indirect calls and jumps where the targets can only be found in registers or memory. As a result, it is not always feasible to determine the destination of indirect calls and jumps statically. The targets of indirect calls and jumps can result from data segments that are globally initialized, such as function tables and

jump tables [88]. They could rely on the input set, which is difficult to establish statically. In light of this, existing static analyses can either be cautious, reasoning that an indirect jump can leap to any basic block, any instruction, or in the middle of an instruction, or perhaps arbitrarily supposing that every indirect jump can only step into a limited number of targets [88].

Balakrishnan et al. devised the Value Set Analysis (VSA) algorithm for statically analyzing the memory contents in binary code [21]. On-the-spot detection of control flow boundaries caused by indirect calls is possible using this method. Here, the aim is primarily to create an IR for binary code analogous to the IR produced by a compiler from the source code. Firstly, the algorithm used in this technique takes as input the assembly code provided by IDA Pro, which includes procedure boundaries and an incomplete CFG. Secondly, a value set analysis is conducted to develop a complete CFG. With its coupled numeric and pointer analysis algorithm, VSA calculates a rounded-off set of values or addresses that could be stored in each register and memory location [22]. Generally speaking, VSA can be helpful when analyzing indirect jump targets or even analyzing the potential targets of "read" and "write" operations in memory. However, due to failed branch conditions tracking, value set analysis can suffer from a lack of accuracy [56].

In light of the approaches mentioned above, it becomes clear that a strictly static approach hinders the accurate reconstruction of a CFG from binary code. Consequently, resorting to the dynamic execution of the program being analyzed has become a more appealing option. The goal is to run programs against a suite of test cases and acquire the control-flow data from the traces of the execution [90]. This method can resolve indirect jumps and capture an accurate control flow. However, the ability of the test cases to cover all indirect jumps determines the completeness of the CFG created using this method [10]. Conventional dynamic analysis tools handle only a limited part of the program execution routes. In light of this, [85] has implemented forced execution to increase the code coverage. In forced execution, the code is run symbolically to examine both pathways at each branch point, and the indirect branches' targets are retrieved in a scale-able manner at run time. Using the same rationale to resolve indirect jumps, Syder [78] implemented the dynamic symbolic execution (DSE), which is a method for determining the program's execution based on a particular input value.

In this study, DEL aims to integrate both static and dynamic symbolic execution into the lifting process itself. Its goal is to provide an enhanced intermediate representation of C++ programs by combining some of the above-mentioned static and dynamic approaches. Firstly, DEL statically disassembles the binary it aims to lift and then constructs a preliminary CFG using the standard approach for CFG reconstruction discussed above. DEL then translates all the assembly instructions generated by its disassembler into an LLVM IR module. Embedded inside this module is the preliminary CFG constructed from step one. DEL then performs a static symbolic execution in an effort of formulating each potential target of the indirect jumps into individual Z3 formulas. DEL then proceeds with dynamically symbolically executing the preliminary IR module to resolve the Z3 formulas generated for each indirect jump detected and finally output an enhanced IR module that can accurately represent the control flow of the program being analyzed.

Figure 2.3: DEL 's reconstructed CFG for WCET crc benchmark [6].

Figure 2.4: DEL 's reconstructed CFG for the icrc1 function.

#### • Translation

After re-constructing the CFG of a program, a lifting tool typically translates each assembly code instruction into its equivalent set of IR instructions.

DEL implements its assembly to IR translator as a C++ API. DEL's translator takes an assembly code instruction as an argument and maps its opcode to the relevant API that translates it into a set of LLVM instructions. For this study, DEL's translator API was implemented for a subset of the ARMv7-M ISA [7] present in the assembly code of the Tasking Framework's case study, the Join fork example shown in Listing A.1. ARM assembly instructions that were not included in the assembly code of our case study have not been considered in the implementation of the translator API. Chapter 4 explains in more detail how the API was implemented.

With translation marking the end of the binary lifting process, next, we explore the current limitations of binary lifting tools.

#### 2.1.2 Today's challenges in binary lifting

Binary lifting has not gained much traction in practice due to its reliance on static disassembly. This approach fails to account for indirect control-flow targets, distinguish between data constants and code pointers, and recognize instruction and data byte boundaries [14].

[14] argued that transformation, analysis, and recompilation of binary code could be complicated without accurate representation at the high level. If the binary code is encoded or ciphered, the problem is exacerbated. [14] highlighted some prominent challenges when performing binary lifting and program transformations using purely static approaches. Here, we provide an overview of these challenges and promote our hybrid approach of lifting by highlighting why static approaches cannot be relied upon in the context of binary lifting.

#### • Code vs data, and reference ambiguity:

Data and references inserted into programs by compilers are usually not labeled. Program analysis must deduce the relevant labels to segregate code from data and constants from references. In the general case, there is no clear-cut answer to such an issue, and modern analyzers use heuristics to estimate the right labeling scheme [82, 83, 89]. If, for example, a data value has the correct alignment and a valid binary code address, it can be deemed a code reference. However, value collisions are common [82], and many platforms do not require alignment.

Generally speaking, analyzing how the processor interprets values from memory can aid a dynamic tool with precisely assigning labels.

#### • Indirect control flow:

Based on the execution context, indirect control flow transfers (ICFTS) can pass control to multiple target locations. Such indirect calls take the form of function pointers in C code, and they are, in fact, more common in C++ code appearing as virtual functions. Additionally, position-independent code (PIC) and switch statements are frequently enacted in indirect branches. All direct branches turn into indirect branches in PIC, which append the offset of the binary/ library's memory mapping to the branch target.

Based on the standard scenario, statically determining all potential targets of ICFTS is impossible [46]. However, when it comes to determining the possible targets of branching instructions that get their target address from jump tables, static techniques have proven

to be proficient [39, 89]. Nevertheless, resolving indirect function calls and returns remains an issue. Although Wang et al. [83] claim that their technique can assist in dealing with ICFTs, their prototype Uroboros indeed does not [14]. Moreover, based on architecture, the rudimentary analytical techniques [39] employed in Rev.Ng [40] state they at best have achieved 90-95 percent jump target recovery.

As opposed to the approaches mentioned above, given enough input configurations (to cover as many execution paths as possible), the DSE of code at the intermediate level can effectively identify control flow targets. The DSE follows the execution path to any jump target, regardless of how the destination address is derived.

#### • poorly-structured code:

Apart from optimization, manually produced assembly code is also used for debugging and disassembly prevention. Although the generated code is deterministic, excessive optimizations added by a compiler may lead to poorly defined instruction constructs [18]. Overlapping instructions remain a popular anti-disassembly strategy [86], but they can also be found in highly optimized libraries [18]. [14] mentioned that some compilers reduce selection control structures (e.g., switch/case) to jump tables and inline data. However, detecting function boundaries can become challenging with overlapping multi-entry functions, basic blocks, and tail calls.

Typically, dynamic techniques avoid handling ill-formed code, as they are only concerned with instructions that the processor executes [14].

#### • Obfuscation:

Binary lifting techniques will inevitably encounter binary files that have been actively modified to impede analysis. Even though various obfuscation strategies have been thoroughly published [34, 35, 79], they nevertheless pose major difficulties in actual use. Virtualizing obfuscators, for example, convert executable code in code segments to bytecode in data segments and insert a virtual machine in the program to elucidate the bytecode [17, 34]. The static code parts of a program covered by such an obfuscator give very little insight into the program's functionality. Moreover, control-flow flattening [35], obscure predicates [36] and aliasing [81] are some additional obfuscation approaches that can indeed pose problems. These modifications can be utilized to synthetically expand the complexity and size of the control-flow graph of a program to the point where performing an accurate IR analysis becomes very challenging. However, employing dynamic approaches midst of the lifting process can reverse all of these obfuscating processes by eliminating dead code and aliases that are not needed [14].

Now that we have discussed the most prevailing challenges faced by today's existing binary lifters, we move forward to review the state-of-the-art binary analysis and lifting tools.

#### 2.2 State of the Art Analysis Tools

There have been many frameworks developed for program analysis. In most cases, these projects go beyond simply analyzing binaries to reverse engineer systems and firmware. There is currently no single tool capable of performing all the tasks required in the analysis process. Rather than choosing one, it is worthwhile to explore all alternatives. Tools such as these are primarily utilized for binary analysis, malware analysis, and reverse engineering. The purpose of this section is to provide a comprehensive overview of the most popular program analysis tools out there, emphasizing their strengths and shortcomings.

#### 2.2.1 McSema

McSema is a static binary lifter that transforms executable binaries to LLVM IR. Analysts can use McSema to detect security vulnerabilities in binary programs, independently verify vendor source code, and write high-code-coverage application tests. Despite its strengths when employed in the static binary analysis, McSema does indeed have its shortcomings. When it comes to CFG reconstruction, McSema relies heavily on IDA Pro, where only directly called functions can be accurately identified. As a result, IDA Pro, in a way, hinders McSema's performance due to its inability to detect function pointers in real-world code correctly. Such a scenario is demonstrated in Listing 4 of the excerpt of decompress.c: libjpeg example from a case study by [13]. Here, the structure object "progress" provides a member field "progress monitor" that stores the address of a callback function at line 8, While at the same time, a second member "pass-limit" holds an integer indicating a loop bound at line 9, which turns out to be in a comparable value range as that of the address of the callback function. Altinay [13] reasons that the fact that IDA utilizes heuristics to determine integers with values in the executable section as code pointers will cause McSema's lifted binaries in this specific case to incorrectly modify the integer, which in turn alters the program's semantics. Likewise, if the code pointers are not identified correctly, callbacks could be poorly managed in this case.

Another challenge would be dealing with obfuscated code. McSema is designed for the translation of compiler-generated binaries and due to its reliance on the thoroughness of IDA pro's recovered CFG, using McSema in the accurate binary analysis of obfuscated code becomes infeasible. After all, IDA pro's recovered CFG will not always accurately capture the program's semantics, especially if code encryption takes place.

```

void callback_func(j_common - ptr cinfo) {

printf("");

2

3

int main(int arge, char** argv) {

4

struct jpeg - decompress - struct info; //jpeg info

5

6

struct jpeg - progress - mgr progress;

// After some initialization code

progress.progress monitor = callback_func;

progress.pass_limit = 0x8048860;

9

10

progress.pass - counter = OL;

info.progress = &progress;

11

jpeg - start_decompress(&info);

12

13

char* data = (char*)malloc(dataSize);

readData(info, data);

14

}

15

```

Listing 4: Excerpt of decompress.c: libjpeg example in C [8].

#### 2.2.2 BinRec

BinRec uses dynamic analysis to lift binary code to LLVM IR, where complicated transformations can be applied, then lowers it back to machine code, resulting in a recovered binary [14].

Binrec's primary purpose is to retrieve code that is difficult to analyze statically. Even though their use of dynamic analysis eliminates this obstacle, it also introduces the issue of covering code that is not used when lifting. While dynamically lifting a program from a single trace, the user is only presented with one of the multiple alternative code pathways. As a result, the recovered binary only works for paths with all of the control flow edges detected during lifting.

#### 2.2.3 BAP

BAP is an open-source platform for performing binary code verification and analysis. One of BAP's flaws is that its lifting mechanism assumes it will be directed to an aligned sequence of instructions. As a result, the user must determine code locations. Although this can be accomplished by using a recursive descent analysis [26], still such analysis technique is once more ineffectual at resolving indirect control flow targets. Consequently, employing BAP in analyses where indirect jumps must be resolved becomes exceedingly challenging. Moreover, BAP uses IR instructions that are not explicit, which makes the prospect of the DSE of its lifted IR challenging and hence restricts the tool's ability to perform control- and data-flow analyses based on the DSE [10].

#### 2.2.4 REV.NG

REV.NG is a binary analysis framework that works with a variety of architectures and is based on QEMU [24] and LLVM. When it comes to CFG recovery, REV.NG largely relies on the Simple Expression Tracker (SET) and Offset Shifted Range Analysis (OSRA) [39].

SET is a technique for extracting jump targets from translated code. It recognizes all store instructions and keeps track of how the value being stored is calculated successively. The analysis continues as long as the operations that make up the expression rely only on one non-constant operand. In actuality, the purpose of SET is to gather the destination addresses of direct and indirect jumps that realize the target address in many instructions. This method can be quite useful for finding the most basic jump targets embedded in the code. It can retrieve the destinations of direct jumps, indirect jumps with a fixed destination manifested in a register, and all call instruction return addresses [39]. However useful it may be, SET still fails to retrieve jump targets resulting from switch statements in which the jump destination address is dependent on a non-constant operand: the result of the switch statement's expression evaluation [39].

OSRA however, is a specific data flow analysis whose purpose is to illustrate how the target address of an indirect jump caused by a switch statement is calculated. It achieves this by formulating each Static Single Assignment (SSA) value of the relevant IR instruction as an expression that eventually highlights all the operations involved in the target address computation. It is primarily implemented to recover jump targets for a specific variety of switch statements. OSRA however, is not without flaws. In general, OSRA is not capable of reading data from memory segments contained in binary code and only supports a limited set of binary operations [39].

In REV.NG, both SET and OSRA collaborate while utilizing an SSA intermediate representation and cycle several times until they yield no further information that could be used in the CFG reconstruction process. Indeed, these analyses could be utilized as a prelude towards obtaining a basic CFG. However, the recovered CFGs' accuracy tends to be a problem [39]. A source of such inaccuracy could be, for example, an aggressively optimized nested switch. Where REV.NG could not determine the size of the jump tables utilized by the inner switch statement in specific functions that used nested switch statements. Another source of inaccuracy is the jump table addresses spilled on the stack. Because the initial address of a jump table may be utilized several times within the function, GCC can spill it on the stack in the function prologue in some cases [40]. Furthermore, due to it not having a dynamic component that involves the actual execution of the program being analyzed, REV.NG has no information about function calls, making tracking stack values across function calls exceedingly challenging [40].

#### 2.2.5 Angr

Angr is a binary analysis framework that combines many current cutting-edge binary analysis algorithms. It provides a reliable foundation for many different analyses, both static and dynamic. When analyzing binaries, this binary analysis tool particularly introduces a dynamic component. It employs a technique known as under-constrained symbolic execution UCSE [66], which rather than executing the full program, executes an arbitrary function within the program that is being analyzed directly.

The fundamental goal of Angrs' usage of UCSE is to prove the correctness of Real Code. Instead of starting with main, UCSE starts with an arbitrary function chosen by the user. When the function exits all possible execution paths within it, the intended check of the function's correctness is complete (a real case example would be checking that the introduction of a patch does not cause a crash). However, directly invoking functions within a program poses a unique complication where a program's crash points detected by UCSE are not reproducible. This problem happens because each function is executed independently while at the same time the analysis cannot reason about how to get to a certain function. Since each function is generated without prior knowledge of its arguments and the global variables with which it is called in actual executions, the analysis is rendered inaccurate [66]. On the other hand, performing the DSE of the whole program involves acquiring input values from outside sources. [66] argued that in most circumstances, valid software should reject erroneous external inputs rather than crashing. Individual functions, however, frequently have preconditions forced on their inputs. A function may, for example, require non-null pointer arguments. Moreover, because UCSE executes functions without prompting the user for their preconditions, the inputs it takes into account may be an over-approximation of the permissible values the function can take [66]. As a result, UCSE symbolic inputs are labeled as under-constrained, indicating that they lack specific constraints. While this approach allows inaccessible code to be thoroughly examined, the lack of preconditions may result in unfounded errors being reported during execution [66].

Strictly speaking, the DSE of the whole program essentially investigates every execution path during a program's execution in a bit-precise manner and considers all possible input values. It explores a much larger number of paths than conventional testing, hence guaranteeing a high program coverage and making it even possible to check whether a particular combination of inputs could result in the program failure.

### Chapter 3

# Tasking Framework

Nowadays, running sophisticated algorithms and complex processing data pose a formidable challenge for space missions, which is why managing resources is of great importance for the success of such missions. Rather than using trajectory control advance algorithms, which necessitated the use of more power [10], missions like Rosetta or the Mars rover landing were built on a list of directives to regulate landing and maneuvering in order to conserve energy. The estimator and observer control modules were developed in a fixed fashion (order and time) during the creation of the TET-1 satellite mission (Technology demonstration) and the Bi-spectral Infrared Detection (BIRD) missions. The module's full calculation duration was the time it took to wait for the sensors' data plus an extra delay to guarantee a full data delivery prior to the start of the calculation. Because of an overestimation of the timing delay, this model causes a timing violation throughout the control cycle. This problem was not found until after the launch, when a timing failure in another bus application caused the computed tasks to be reordered, resulting in erroneous data and the malfunctioning of the orbit control systems [60].

Figure 3.1: Scheduling in the Tasking Framework adapted from [10].

DLR's onboard computer-next-generation project began to establish reliable processors and network nodes with an operating system that would guarantee satellite timing behavior.

This design must also account for multi-core and distributed systems' timing behavior. The Tasking Framework constituted the foundation of this concept. The framework was created primarily to increase the performance of attitude control systems by breaking the computational

data from the sensor into small portions, each of which is referred to as a task, and then scheduling them according to their readiness [10]. The Tasking Framework was created using the inversion of control design paradigm, which is commonly utilized in creating lightweight frameworks. The Autonomous Terrain-based Optical Navigation (ATON) project [76] uses the framework, which is a technology to navigate a lunar landing scenario that uses multiple image processing techniques [60]. The framework's most essential feature is its ability to alter the time behavior of the tasks being processed [10]. Figure 3.1 from [10] shows the impact of using the ASAP scheduling policy on overall response time, as opposed to conventional scheduling, which starts calculation at a predetermined time in the computation cycle.

#### 3.1 Task-Channel Model

The task-channel paradigm presented in [43] was used to create the Tasking Framework. The idea is to create a barrier between functionality and data. [10] described a task as a "stateless executable program" with memory and I/O ports in this model, whereas a channel is a message queue that links the output port of one task to the input port of another. The channel in the Tasking Framework is a data container that the task object may handle. It works as an interface that serves as a link between tasks and connects software outputs and inputs, as demonstrated in Figure 3.2. The use of a task-channel architecture improves the reusability of code [10]. It is conducive in systems that are distributed in which some components of the software must be moved between processing nodes [10]. The Tasking Framework was created with data-flow-oriented applications in mind. The operation of a system is understood by looking at how data flows through it. [10] argued that data-flow-focused methodologies require that the input data of the system be determined and processed to produce the appropriate outputs. The program is constructed as a sequence of successive operations that occur in a specific order using this method. The Tasking Framework employs this design paradigm to introduce an interface that is structural and not reliant on the availability of data but rather on its flow. All APIs, except for the Execution class APIs, demonstrate a high level of generalization, as they are no longer constrained by the presence of input data and the current task [10]. The framework can be compared to operating systems in that it controls the entire process in a deterministic, generic, and abstract manner [45].

Figure 3.2: Task Channel Model adapted from [10].

#### 3.2 Execution Model

[10] stated that when all task inputs are active, a task instance  $\tau$  is launched in the Tasking Framework. For example, Task **A** will be executed in Figure 3.3 when input 1 is active immediately after receiving Msg.A from sensor A. Marking one of the task's inputs as final is another

approach to triggering it right away. If this input is enabled, the task will execute regardless of the state of the other inputs. in Figure 3.3 Task E, for example, will be triggered when the task event (Timer) gives the input 0, which is marked as final, regardless of the state of the other inputs. C will be triggered immediately after that.

The Tasking Framework's schematic diagram is depicted in Figure 3.4. When a message from a sensor is received, the main execution thread uses the channel class's **push()** method to alert the related inputs. In the scenario where all task inputs have been set up, the Tasking Framework will instantly inform a thread to run the waiting instance of this task by invoking **perform()**. The framework's scheduler kicks off the task right away. The job will begin as soon as a free resource, such as a CPU core, becomes available; or else, the task will be queued [45, 60].

Figure 3.3: BIRD - AOCS and the Tasking Framework Components adapted from [10].

Figure 3.4: The Tasking Framework's sequence diagram adapted from [10].

#### 3.3 Tasking Framework in use

Several DLR initiatives have made use of the Tasking Framework. This section briefly highlights 3 projects mentioned in [10] where the Tasking Framework plays a key role. The Tasking Framework was utilized to apply the functional tasks and link them by means of channels in ATON. In this model, channels are data-containers that store data, while events are used to trigger the different system components routinely. 4 threads were employed by the developers to run the software on the prototype flying computer.

The Attitude and Orbit Control System (AOCS) was developed using the Tasking Framework in the Euglena Combined Regenerative Organic Food Production In Space project (Eu:CROPIS) [59].

Another DLR project presents and evaluates a novel onboard computing architecture consisting of re-configurable interlinked commercial off-the-shelf processors coupled in a single distributed system. The project is called Scalable On-Board Computing for Space Avionics (ScOSA) [77]. The Tasking Framework is a component of the middle-ware and the core API for developing the ScOSA-based application. On-board Data Analysis and Real-time Information System (ODARIS) [68], and Rendezvous Navigation [67] are two examples of applications that will be implemented utilizing the Tasking Framework to run on ScOSA.

#### 3.4 Tasking Framework as a C++ Library

The Tasking Framework is created by the German Aerospace Center's Institute for Software Technology (DLR). The framework is a platform for event-driven execution for onboard software systems that run in real-time. It enables tasks to be implemented as graphs with capricious patterns of activation [10]. It is developed in C++ based on the event-driven programming approach and is capable of multi-threading programming [45]. Even though C++ is not often used to construct aerospace applications, it was employed in the development of this framework because of the following factors as discussed by [10]:

- To begin with, the language is modular since it employs object-oriented programming. Class implementation in C can also be achieved using struct, but due to constructors and deconstructors, C++ surpasses it. These constructors ensure that objects are always properly instantiated, while the destructors ensure that they are permanently deleted when they are no longer needed, guarding against bugs or leaks.

- Thanks to C++'s templates, it is possible to program abstractly and generically. It is possible to transform a template into a macro that creates a unique data type that is fully functional. These templates can help adapt algorithms efficiently for various types with reduced resource demand.

- Another reason to use C++ is type safety. In type safety, the compiler makes sure all variables are valid and that there are no mix-ups of data types involved in the relevant operations. In contrast to C++, the C function memory can copy double values into an array of char values, eventually generating meaningless data.

- It is not easy to create distinctive descriptive naming in large projects; hence prefixes have traditionally been appended to the names. As a result, names become long and difficult to read. The simplest way to fix that issue is to use namespaces in C++. Multiple occurrences of the same name in various contexts are permitted by such namespaces, which are determined later during compilation. This C++ feature ensures that the name is used in many informative and distinctive ways.

- As opposed to C, which allocates and frees memory by invoking malloc() and free(), C++ utilizes new and delete, adding constructors and destructors to prevent memory leaks and other errors.

- C++ provides novel features such as inheritance, operator overloading, and virtual functions that are not present in C.

- In C++, references and smart pointers are far more secure than regular C pointers because they prevent pointers from referencing NULL or being uninitialized.

#### 3.5 Tasking Framework and its relevance to static analysis

[10] argued the relevance of the Tasking Framework in static analysis. Their argument is based on a handful of points, which we highlight in the following paragraphs:

Strictly speaking, the application is treated as a directed graph in data-flow programming, where the tasks handle the data and then pipe-lined to the following tasks in the sequence. In this case, instructions' execution does not depend on the completion of previous tasks; instead, once the data becomes available, they can be executed, which is known as event-driven execution.

Abstract classes are provided by the Tasking Framework. The classes can be used to create applications organized as a directed network of tasks and channels. As a result, the API loops that link the channels and tasks are constrained. Put another way; the API is not reliant on any data provided at run-time.

The channels in Tasking Framework serve as data containers. The Tasking Framework's technique for exchanging data between tasks and inputs is preordained and independent of the data type or value.

### 3.6 Tasking Framework in this thesis

Typically, strict verification and validations are required before the Tasking Framework could be employed in hard real-time safety-critical applications.

A static analysis is the only way to assess the system's real-time capabilities and demonstrate its ability to meet deadlines. At all execution stages, a static analysis computes a general overestimate for all sets of architectural states. It guarantees that a specific condition will not be encountered at a specific execution point. This safety attribute permits a safe WCET upper bound to be established. The framework's provision of WCET is the initial step toward developing safety-critical applications. This thesis aims to optimize the lifting of C++ applications' binaries for effective loop bounding and WCET analysis at the IR level. We evaluate our novel approach of combining both static and dynamic symbolic execution while lifting binaries of the Tasking Framework case study, the Join fork example in Listing A.1. The Join fork example is an illustrative example for an onboard data processing application inspired by the ATON project.

Similar to [10], The Tasking Framework makes a suitable candidate test case for our thesis for two main reasons. Firstly, the Tasking Framework is designed to help create data-handling

applications. It proposes a novel satellite onboard data modeling and computes scheduling approach. The framework deviates from conventional scheduling, which requires all compute processes to wait to receive a single message. It does, however, introduce an ASAP schedule, which more effectively utilizes the time available and improves the worst-case response time of the entire onboard system. For this reason, conducting a WCET analysis at the IR level is critical for computing end-to-end real-time assurances on the envisaged satellite onboard system scheduling model.

The second reason for using the Tasking Framework as our case study is that it is a real-world application that investigates whether WCET can be conducted on model-based C++ code. The framework provides most C++ structures employed in embedded safety-critical applications [10]. Abstract classes and virtual methods are covered. As a result, it is a viable candidate for WCET analysis at the IR level.

# Chapter 4

# **DEL Lifter**

This chapter introduces DEL, our new lifting tool that combines static and dynamic symbolic execution while lifting into LLVM IR. We start by presenting the motives behind the techniques we adopted, then discuss some definitions, followed by presenting our concept and implementation.

# 4.1 Motivation

There are three main reasons behind the techniques we adopted while implementing our lifting tool, DEL:

- We chose to integrate symbolic execution into the lifting process as such a method gives a clear insight into the program's workflow. Dynamic and static analyses are coupled together in this procedure. It generalizes a valid and exact program trace to forecast how the program will behave when presented with a particular input [10]. Through the proposed technique, we resolve indirect control flow targets and check the correctness of the lifting process.

- DEL's intermediate representation language DSEIR uses a subset of LLVM instructions due

to its popularity and its support of various forms of analyses as natural loop information,

memory dependence analysis, and many more. Such analyses could be very useful when

applied to data flow space applications.

- To generate an enhanced IR of data flow space applications, DEL implements its memory and register models. It makes sure the effect of condition flags checking and updating functionalities of assembly instructions are captured in the lifted IR module.

Let us consider the example program in Listing 5. Here, different inputs to the program could result in different potential-jump targets for a single indirect jump instruction. Based on the input argument of the index\_calculator function, the program ends up either invoking function f1 or function f2 in line 18 of Listing 5. Listing 6 shows a snippet of the assembly code of the program. Figure 4.1 shows DEL's re-constructed control flow graph (CFG) for the program. The figure illustrates the two possible paths that could be taken from the start entry point of the program to the basic block with the indirect jump in line 31 of Listing 6. The two paths define two potential-jump target addresses for the indirect jump, and those are the addresses of functions f1 and f2 (00008000,00008020). The assembly instruction in line 28 of Listing 6, ldr r3, [r3, r2, lsl 2] defines the calculation of each possible jump target address. The computation

takes the form of Equation 4.1 where each jump target address (J) is computed by adding the jump table's base address (A) with a variable offset (X) multiplied by the memory byte size in bits (k).

$$J = A + kX \tag{4.1}$$

In this scenario, the base address of the jump table is stored in r3, and the offset is stored in r2. The **lsl 2** resembles a multiply operation by the constant 4. This factor represents the size of a memory byte in bits for the used architecture at the time of disassembling the program.

As the program invokes the index calculator function, the input argument is stored in r0, which is then conveyed to r3 through the store and load operations in lines 5 and 6 of Listing 6, respectively. The compare instruction in line 7 of Listing 6, **cmp r3**, #0, checks if the value held in r3 is equal to zero or not. This value reflects the argument passed to the index\_calculator function. Depending on the result of the comparison, the program can branch to basic block L6 setting r3 to 1 in line 12 of Listing 6 or Alternatively, execute the instruction in line 9 of Listing 6 and set r3 to 0. This results in two potentially different offset calculations by the instruction in line 28, and hence a different jump target address for the indirect jump in line 31.

This example program was intentional to highlight how different inputs to a program can result in different potential-jump target addresses for a single indirect branching instruction. For this purpose, our approach firstly performs a static symbolic execution (SSE) to formulate each potential-jump target address of each indirect jump in the program as a Z3 expression. Secondly, we perform a dynamic symbolic execution (DSE) using the Z3 solver from Microsoft Research [37] to resolve the Z3 expressions of the indirect jump target addresses to their concrete values.

Figure 4.1: Two potential paths from the main entry point till the basic block of the indirect jump (00008088).

4.1. MOTIVATION 41

```

// Type your code here, or load an example.

1