# **Purdue University**

# Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

8-2018

# III-V and 2D Devices: from MOSFETs to Steep-Slope Transistors

Mengwei Si *Purdue University*

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

## **Recommended Citation**

Si, Mengwei, "III-V and 2D Devices: from MOSFETs to Steep-Slope Transistors" (2018). *Open Access Dissertations*. 2072.

https://docs.lib.purdue.edu/open\_access\_dissertations/2072

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# III-V AND 2D DEVICES: FROM MOSFETS TO STEEP-SLOPE TRANSISTORS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Mengwei Si

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2018

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Peide Ye, Chair

School of Electrical and Engineering

Dr. Mark S. Lundstrom

School of Electrical and Engineering

Dr. Joerg Appenzeller

School of Electrical and Engineering

Dr. Zhihong Chen

School of Electrical and Engineering

# Approved by:

Dr. Venkataramanan Balakrishnan

Head of the School Graduate Program

To my parents and my wife

#### **ACKNOWLEDGMENTS**

I would first like to thank my advisor, Professor Peide Ye, for his support, encouragement and guidance during my PhD study at Purdue University. In particular, I appreciate that he taught me to understand something that I'll remember for my whole life. That is to spend all the efforts to focus on the most important thing.

I would also like to give my great appreciation to my committee members: Professor Mark Lundstrom, Professor Joerg Appenzeller and Professor Zhihong Chen for their insightful suggestions and discussions during my PhD study.

My thanks also go to all my colleagues in Professor Ye's group. They provide innovative discussions and overcome technical obstacles. In particular, I would like to many thanks to Dr. Jiangjiang Gu, for his training and guidance when I was a first year PhD student. In addition, I would also like to thank Dr. Lin Dong, Dr Han Liu, Dr. Adam T. Neal, Dr. Heng Wu, Dr. Jingyun Zhang, Dr. Xuefei Li, Nathan Conrad, Dr. Hong Zhou, Dr. Yuchen Du, Dr. Linming Yang, Dr. Yexin Deng, Sami Alghamdi, Gang Qiu, Wonil Chung and Jinhyun Noh for their help in the past years.

I would also like to thank to all my collaborators, Prof. Roy G. Gordon, Dr. Xinwei Wang, Dr. Xiabing Lou from Harvard University, Prof. Muhammad A. Alam and Dr. Sanghoon Shin from Purdue University, Dr. Chun-Jung Su from National Nano Device Laboratories of Taiwan and Dr. Chunsheng Jiang from Tsinghua University.

Thanks to Birck Nanotechnology Center and all the staffs, Bill Rowe, Kenny Schwartz, Dave Lubelski, Jeremiah Shepard, Dan Hosler, Lorraine Fox, Geoff Gardner, John Coy and Ira Young for their technical support on cleanroom facilities and Mary Jo, Nancy Black and other clerical staffs for their helps.

And thanks to my parents for their continuous support.

# TABLE OF CONTENTS

|    |      | P                                                                                                            | age  |

|----|------|--------------------------------------------------------------------------------------------------------------|------|

| LI | ST O | F TABLES                                                                                                     | vii  |

| LI | ST O | F FIGURES                                                                                                    | viii |

| SY | MB(  | DLS                                                                                                          | XV   |

| AI | BBRE | EVIATIONS                                                                                                    | viii |

| AI | BSTR | ACT                                                                                                          | xxi  |

| 1  | INT  | RODUCTION                                                                                                    | 1    |

|    | 1.1  | Computer and Binary Logic                                                                                    | 1    |

|    | 1.2  | Charge Based Logic and High Performance Computing                                                            | 2    |

|    | 1.3  | The Moore's Law and Power-constraint Scaling                                                                 | 3    |

|    | 1.4  | MOSFETs with High Moblity Channel Materials                                                                  | 7    |

|    | 1.5  | SS Reduction in MOSFETs and Steep-slope Transistors                                                          | 11   |

|    |      | 1.5.1 Device Scaling and Short Channel Effects                                                               | 11   |

|    |      | 1.5.2 Steep-slope Transistors                                                                                | 12   |

|    | 1.6  | Thesis Outline                                                                                               | 14   |

| 2  |      | MOSFETS FOR LOW POWER AND HIGH PERFORMANCE OS LOGIC APPLICATIONS                                             | 15   |

|    | 2.1  | Introduction                                                                                                 | 15   |

|    | 2.2  | Ultimately Scaled Sub-10 nm V-Gate InGaAs MOSFETs                                                            | 15   |

|    | 2.3  | InGaAs Gate-all-around MOSFETs with Raised Source and Drain and Ultrathin Body Structures                    | 21   |

|    | 2.4  | Effects of Forming Gas Anneal on Ultrathin InGaAs Nanowire Metaloxide-semiconductor Field-effect Transistors | 25   |

| 3  | СНА  | ARACTERIZATION OF ULTRA-SCALED III-V MOSFETS                                                                 | 33   |

|    | 3 1  | Introduction                                                                                                 | 33   |

|    |       |        |                                                                                             | Page  |

|----|-------|--------|---------------------------------------------------------------------------------------------|-------|

|    | 3.2   |        | e Interface Trap Density Extraction of Ultra-scaled MOSFETs: rection to Subthreshold Method | . 34  |

|    | 3.3   |        | Frequency Noise and Random Telegraph Noise on Near-ballistic MOSFETs                        | . 40  |

| 4  | III-V | TUNI   | NELING FIELD-EFFECT TRANSISTORS                                                             | . 59  |

|    | 4.1   | Introd | luction                                                                                     | . 59  |

|    | 4.2   | Chann  | nel Length Scaling of Planar InGaAs Tunnel Field-effect Transist                            | ors59 |

|    | 4.3   | 3D Ga  | ate-all-around InGaAs Tunnel Field-effect Transistors                                       | . 70  |

| 5  |       |        | E CAPACITANCE FIELD-EFFECT TRANSISTORS WITH EMERGING SEMICONDUCTOR MATERIALS                | . 76  |

|    | 5.1   | Introd | luction                                                                                     | . 76  |

|    | 5.2   | Physic | es of Negative Capacitance Field-effect Transistors                                         | . 76  |

|    | 5.3   | ALD 1  | Deposited Hafnium Zirconium Oxide as Ferroelectric Insulators                               | . 78  |

|    | 5.4   | Negati | ive Capacitance Field-effect Transistors with 2D Semiconductors                             | . 83  |

|    |       | 5.4.1  | Steep-slope Hysteresis-free Negative Capacitance $MoS_2$ Transistors                        | . 83  |

|    |       | 5.4.2  | ${ m MoS_2}$ Negative Capacitance Field-effect Transistors with Internal Metal Gate         | . 91  |

|    | 5.5   | III-V  | Negative Capacitance Field-effect Transistors                                               | . 96  |

| 6  | CON   | NCLUS! | ION AND OUTLOOK                                                                             | 101   |

|    | 6.1   | Conclu | usion                                                                                       | 101   |

|    | 6.2   | Outloo | ok                                                                                          | 102   |

| R  | EFER  | ENCE   | S                                                                                           | 105   |

| V] | ГТА   |        |                                                                                             | 118   |

| ΡI | IBLI  | CATIO  | NS                                                                                          | 110   |

# LIST OF TABLES

| Tab. | le                                                                                          | Р | age |

|------|---------------------------------------------------------------------------------------------|---|-----|

| 1.1  | Bandgap of common semiconductors at 300 K                                                   |   | 10  |

| 3.1  | $D_{it}$ extraction results from DIBL-SS relation on simulation data of silicon GAA MOSFETs |   | 39  |

| 3.2  | Description of samples and device dimensions                                                |   | 42  |

# LIST OF FIGURES

| Figu | ıre                                                                                                                                                                                                                                                                                                                                                             | Page  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

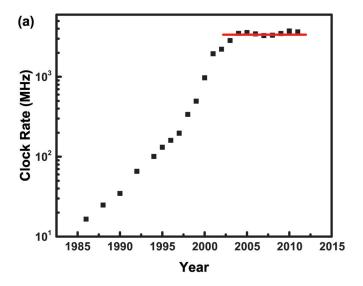

| 1.1  | (a) Clock rate of selected CPU versus year. (b) Power density of selected CPU versus year. Data source from Ref. [4]                                                                                                                                                                                                                                            | . 4   |

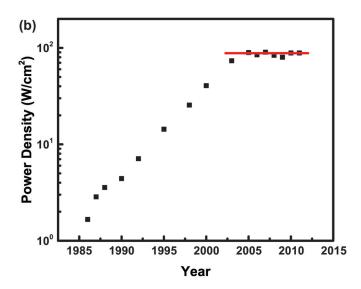

| 1.2  | (a) $V_{DD}$ reduces while $I_{ON}$ is kept the same in MOSFETs. (b) The effect of mobility enhancement at same $I_{OFF}$ . (c) The effect of SS reduction at same $I_{OFF}$                                                                                                                                                                                    | . 6   |

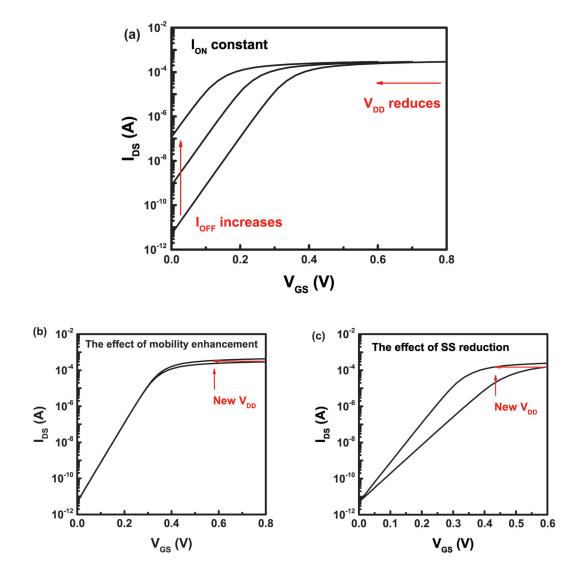

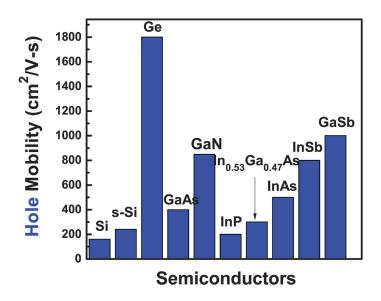

| 1.3  | (a) Electron and (b) hole mobilities comparison among group IV and III-V semiconductor materials                                                                                                                                                                                                                                                                | . 8   |

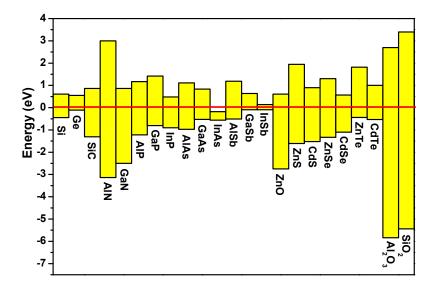

| 1.4  | Charge neutral level alignments over selected semiconductor materials                                                                                                                                                                                                                                                                                           | . 9   |

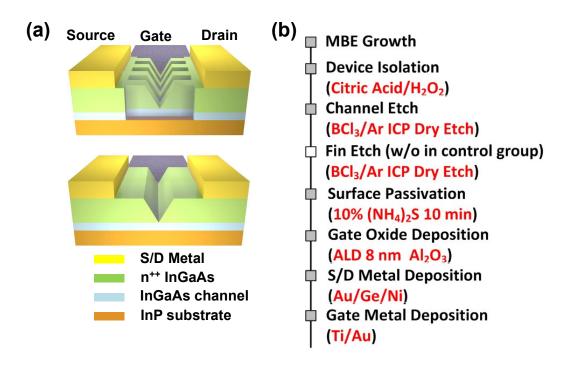

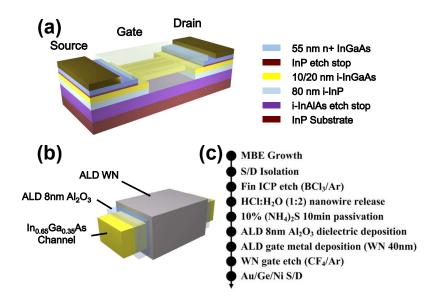

| 2.1  | (a) Schematic diagram of a sub-10 nm V-Gate FinFET and a planar MOS-FET. (b) Fabrication process flow of V-Gate FinFETs and planar MOSFE                                                                                                                                                                                                                        | Ts.17 |

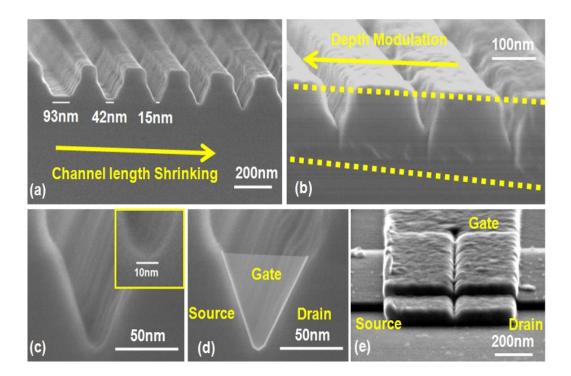

| 2.2  | (a) Channel length shrinking by etch window length modulation. (b) Channel thickness modulation by lithography window length modulation. (c) Illustration of sub-10 nm V-Gate channel. (d) Device structure illustration based on (c). (e) SEM image for a sub-10 nm InGaAs V-Gate MOSFET                                                                       | . 18  |

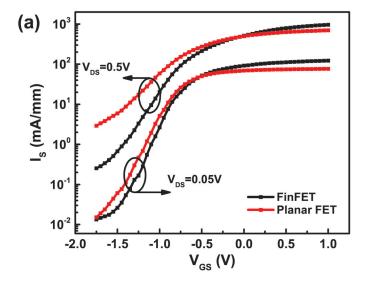

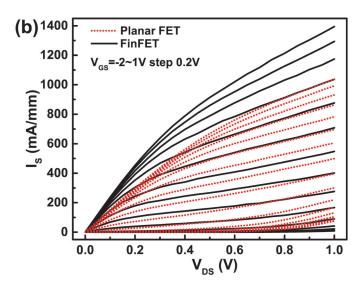

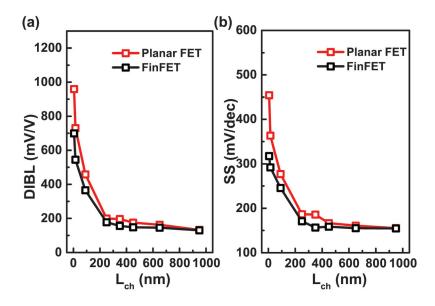

| 2.3  | (a) Transfer and (b) output characteristics of two well-behaved sub-10 nm V-Gate InGaAs FinFET and Planar MOSFET with an estimated channel length of 3 nm. Due to the drain to substrate leakage current and huge area difference between contacts and wires, $I_S$ is presented instead of $I_D$ , showing the fundamental transport properties inside channel | . 19  |

| 2.4  | (a) SS and (b) DIBL scaling metrics for planar V-Gate devices and V-Gate FinFETs. SS is extracted at $V_{DS}$ =0.5 V                                                                                                                                                                                                                                            | . 20  |

| 2.5  | (a) Schematic diagram, (b) cross sectional view and (c) fabrication process flow of $n+$ raised source and drain InGaAs gate-all-around MOSFETs                                                                                                                                                                                                                 | . 22  |

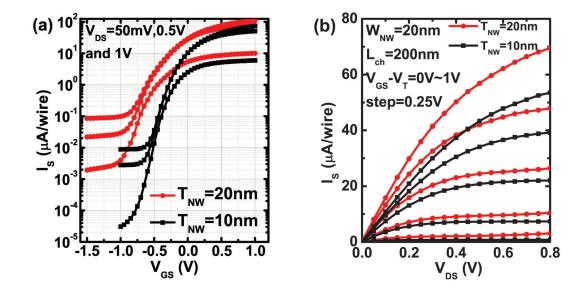

| 2.6  | (a) Transfer and (b) output characteristics of two well-behaved $n+$ raised source and drain InGaAs gate-all-around MOSFETs                                                                                                                                                                                                                                     | . 23  |

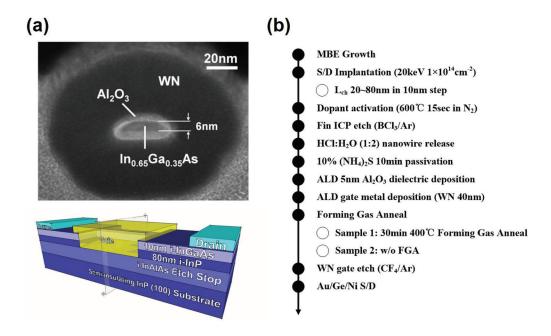

| 2.7  | Off-state leakage current comparison between the devices with $10 \text{ nm}$ and $20 \text{ nm}$ $T_{NW}$ at different drain voltages                                                                                                                                                                                                                          | . 25  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

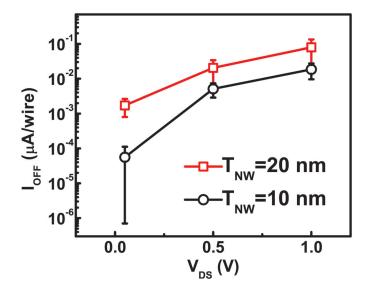

| 2.8  | (a) Cross sectional TEM image and schematic diagram of an InGaAs GAA MOSFET with $T_{NW}=6\mathrm{nm}$ . (b) Fabrication process flow of the InGaAs GAA MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                         | . 27 |

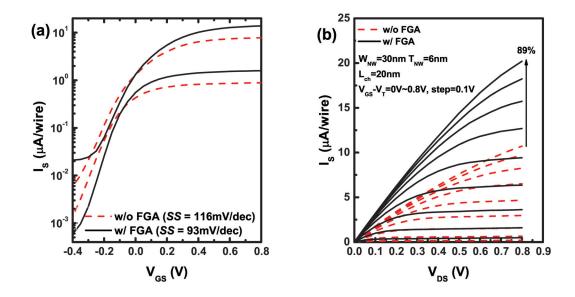

| 2.9  | (a) Output and (b) transfer characteristics of two typical InGaAs GAA MOSFETs with $L_{ch}=20\mathrm{nm},W_{NW}=30\mathrm{nm}$ and $T_{NW}=6\mathrm{nm}$ with and without FGA treatment. Due to the significant reverse junction leakage current, $I_S$ is presented instead of $I_D$                                                                                                                                                                                                                                                                                                   | . 28 |

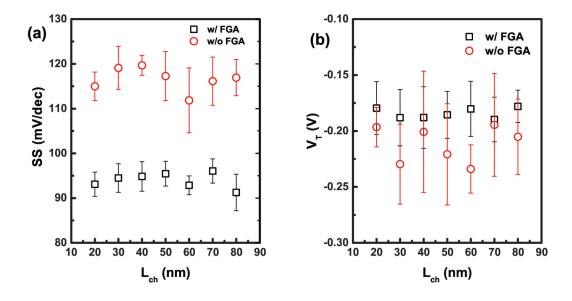

| 2.10 | (a) SS and (b) $V_T$ of these devices with $W_{NW}=30\mathrm{nm}$ and $T_{NW}=6\mathrm{nm}$ versus $L_{ch}$ . With FGA and their control devices are in comparison. Each data point represents 5-10 measured devices. $V_T$ is extracted from linear extrapolation at $V_{DS}=50\mathrm{mV}$ .                                                                                                                                                                                                                                                                                          | . 29 |

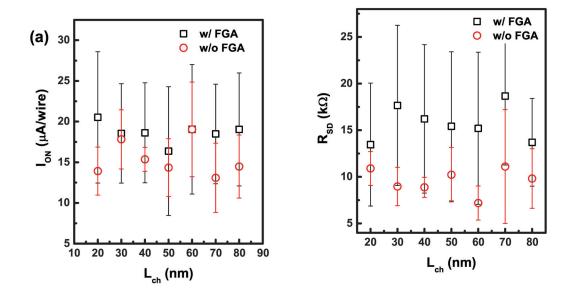

| 2.11 | (a) $I_{ON}$ and (b) $R_{SD}$ versus $L_{ch}$ in comparison between FGA devices and their control ones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 30 |

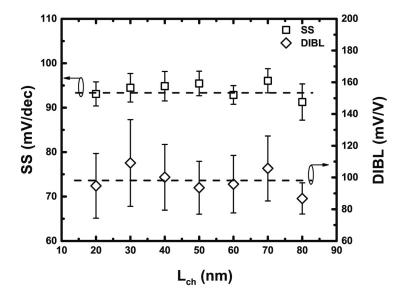

| 2.12 | SS and DIBL versus $L_{ch}$ of FGA treated InGaAs GAA MOSFETs with $W_{NW}=30\mathrm{nm}$ and $T_{NW}=6\mathrm{nm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 31 |

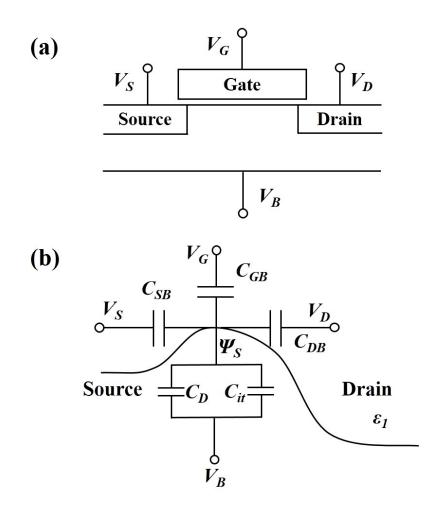

| 3.1  | Illustration of the capacitor model of 2D electrostatics on MOSFETs. $\Psi_S$ is the potential at the top barrier which is controlled by gate, source, drain and body potentials. $C_{SB}$ , $C_{DB}$ and $C_{GB}$ represent source to body capacitance, drain to body capacitance and gate to body capacitance, respectively. $C_D$ is the depletion capacitance, it is sometimes absent in the thin-body SOI and nanowire structures considered. $C_{it}$ is the interface trap capacitance. The model describes the electrostatic control of the potential on the top of the barrier | . 35 |

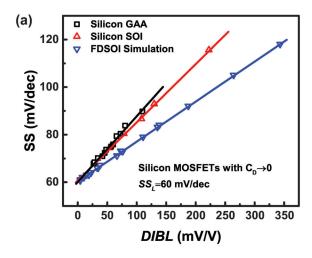

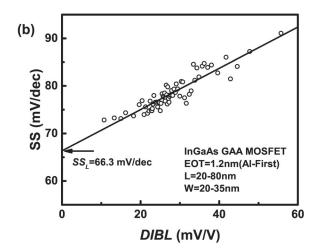

| 3.2  | SS versus DIBL of (a) silicon GAA MOSFETs [74], SOI silicon MOSFETs [75], simulation of FDSOI silicon MOSFETs [76], (b) InGaAs GAA MOSFETs (Sample A in [12]). The SS at long channel limit is extracted by linear fitting of SS with respect to DIBL. For (b), SS is extracted at $V_{DS}$ =0.05 V and DIBL is extracted at a constant current in subthreshold region, each data point represents the average of 10 nearby devices                                                                                                                                                     | . 38 |

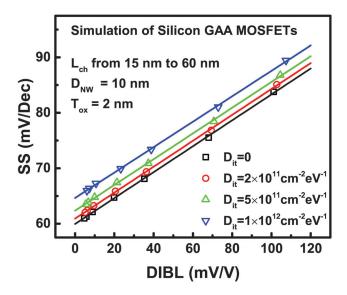

| 3.3  | Simulation of SS versus DIBL of silicon GAA MOSFETs with various $D_{it}$ values. The simulated devices have a cylinder silicon nanowire channel with $L_{ch}$ from 15 nm to 60 nm, 10 nm nanowire diameter and with 2 nm SiO <sub>2</sub> as gate dielectric. $D_{it}$ from 0 to $1 \times 10^{12}$ eV <sup>-1</sup> cm <sup>-2</sup> are used in simulation                                                                                                                                                                                                                           | . 39 |

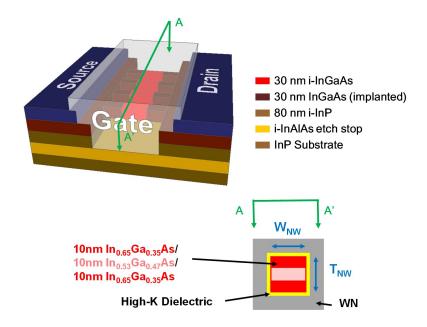

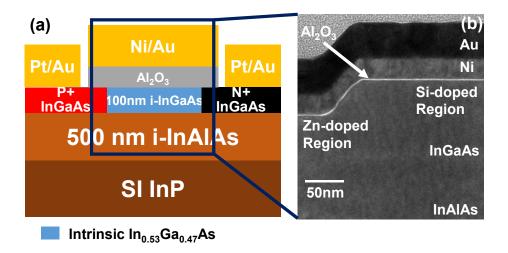

| 3 4  | Schematic and cross-section of the present InGaAs GAA MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41   |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

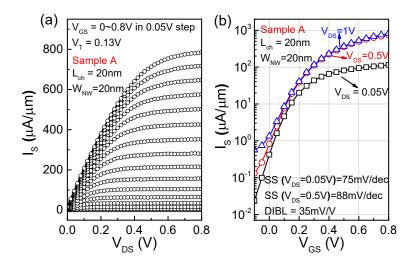

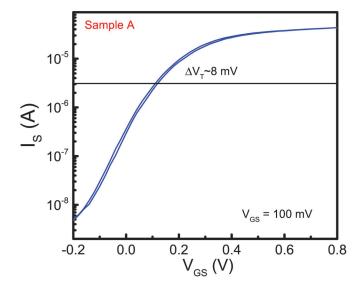

| 3.5  | (a) Output and (b) transfer characteristics of a $L_{ch}$ =20 nm InGaAs GAA MOSFET with Al <sub>2</sub> O <sub>3</sub> /LaAlO <sub>3</sub> gate dielectric (Sample A, EOT=1.2 nm) and $W_{NW}$ =20 nm. $I_S$ is used due to relatively large junction leakage current in $I_D$                                                                                                                                               |      |

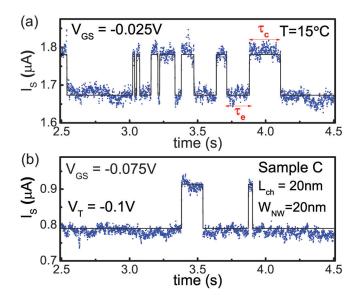

| 3.6  | $I_S$ fluctuation due to RTN in (a) $V_{GS}$ = $-0.025\mathrm{V}$ , (b) $V_{GS}$ = $-0.075\mathrm{V}$ on InGaAs GAA MOSFETs measured at 15 °C. Capture/emission time constants $(\tau_c/\tau_e)$ are defined in (a)                                                                                                                                                                                                          |      |

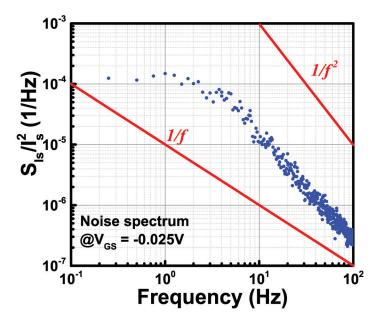

| 3.7  | Normalized $I_S$ noise of RTN signal shown in Fig. 3.6(a), showing $1/f^2$ characteristics                                                                                                                                                                                                                                                                                                                                   | . 45 |

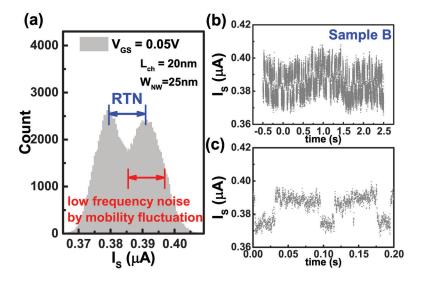

| 3.8  | (a) Histogram of a RTN signal of sample B with $L_{ch}$ =20 nm and $W_{NW}$ =25 nm. (b) and (c) RTN signals in time domain of the same signal as (a). (c) is a time segment inside (b)                                                                                                                                                                                                                                       |      |

| 3.9  | Measurement of hysteresis of a typical device of Sample A with $L_{ch}$ =20 nm and $W_{NW}$ =20 nm. The device shows negligible hysteresis. The estimated trap number by hysteresis is on the order of several traps                                                                                                                                                                                                         |      |

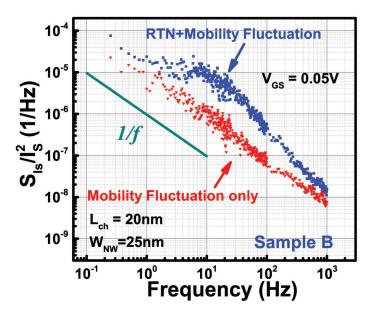

| 3.10 | Normalized $I_S$ noise of Sample B devices with RTN signal and without RTN signal. Noise spectrum of device without RTN is attributed to mobility fluctuation                                                                                                                                                                                                                                                                |      |

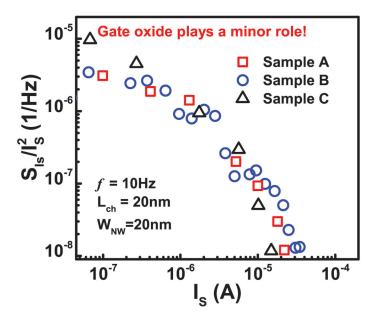

| 3.11 | PSD of $I_S$ normalized by $I_S^2$ vs. $I_S$ at $f=10\mathrm{Hz}$ for Sample A, B and C devices with $L_{ch}=20\mathrm{nm}$ and $W_{NW}=20\mathrm{nm}$ . Devices with different gate oxides exhibit similar noise level, showing weakly dependent on interfaces and types of oxides                                                                                                                                          |      |

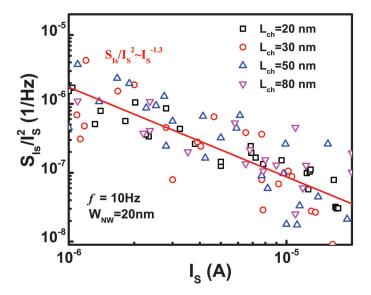

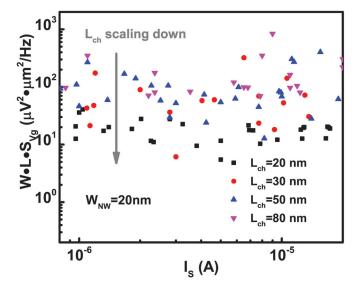

| 3.12 | PSD of $I_S$ normalized by $I_S^2$ at $f=10\mathrm{Hz}$ for various $L_{ch}$ and $W_{NW}=20\mathrm{nm}$ at $V_{DS}=0.05\mathrm{V}$ on Sample B. Normalized $I_S$ noise versus $I_S$ of devices with different $L_{ch}$ weakly depend on interfaces and types of oxides. At least 5 devices are measured for each $L_{ch}$ , showing a statistical trend                                                                      |      |

| 3.13 | Input gate voltage noise normalized by channel width times channel length of the same data set as Fig. 3.12. $W$ is the channel width and $L$ is the channel length in this figure                                                                                                                                                                                                                                           |      |

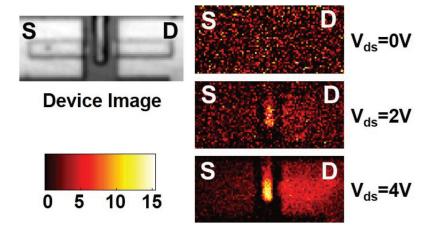

| 3.14 | Thermo-reflectance image on an InGaAs GAA MOSFET with $L_{ch}$ =80 nm, $W_{NW}$ =30 nm at $V_{GS}$ =1 V and at $V_{DS}$ from 1 V to 4 V. Color scale shows the temperature difference ( $\Delta T$ ) in kelvin. The drain side is heated at high $V_{DS}$ by ballistic electrons, indicating that electrons travel substantial distance into the contact before reaching equilibrium which indicates nearballistic transport |      |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pa | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

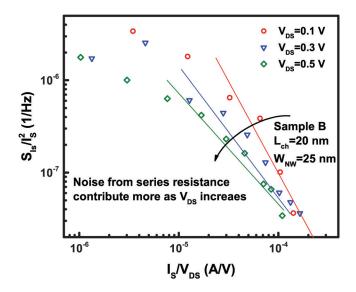

| 3.15 | $S_{I_S}/I_S^2$ vs. $I_S/V_{DS}$ at different $V_{DS}$ . $S_{I_S}/I_S^2$ shows weaker negative correlation with $I_S/V_{DS}$ as $V_{DS}$ increases. This phenomenon suggests noise from series resistance has a higher contribution to the source current noise as $V_{DS}$ increases                                                                                                                                              |    | 54  |

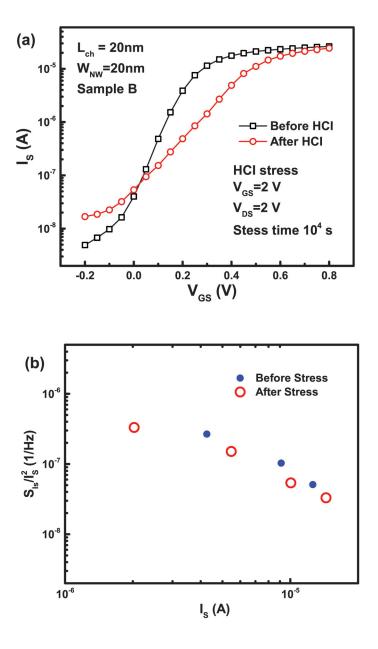

| 3.16 | (a) Transfer characteristics of an $L_{ch}$ =20 nm, $W_{NW}$ =20 nm device of Sample B, fresh device (square) and after $V_{GS}$ =2 V, $V_{DS}$ =2 V stress for $1 \times 10^4$ s (circle). (b) $S_{I_S}/I_S^2$ vs. $I_S$ of the device in (a) before stress and after stress measured at $V_{DS}$ =0.05 V. Although defects are generated at drain side, the PSD of $I_S$ shows similar level on fresh device and stressed device | e. | 55  |

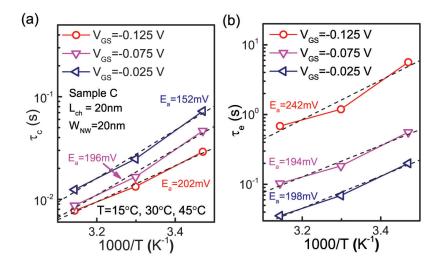

| 3.17 | Temperature dependent (a) capture and (b) emission time constant of RTN in device shown in Fig. 3.6                                                                                                                                                                                                                                                                                                                                |    | 56  |

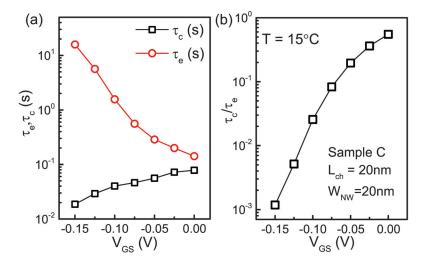

| 3.18 | (a) Mean capture and emission time constant corresponding to different gate voltages. (b) $\tau_c/\tau_e$ dependence on $V_{GS}$ . The positive correlation indicates electron trapping happens between channel and gate oxide                                                                                                                                                                                                     |    | 57  |

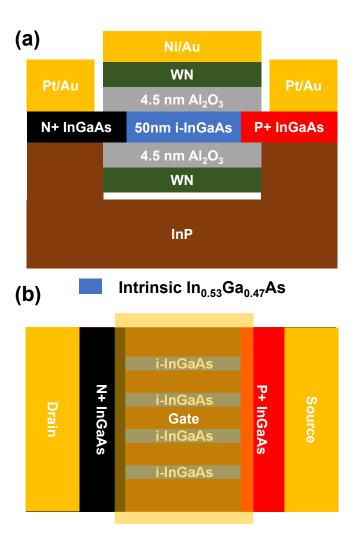

| 4.1  | (a) Schematic diagram and (b) TEM cross-sectional image of an InGaAs planar TFET                                                                                                                                                                                                                                                                                                                                                   |    | 60  |

| 4.2  | Fabrication process flow for the InGaAs TFET                                                                                                                                                                                                                                                                                                                                                                                       |    | 61  |

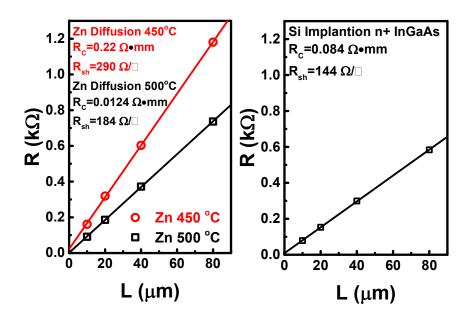

| 4.3  | TLM measurement on doped InGaAs by (a) Zn diffusion and (b) Si implantation                                                                                                                                                                                                                                                                                                                                                        |    | 62  |

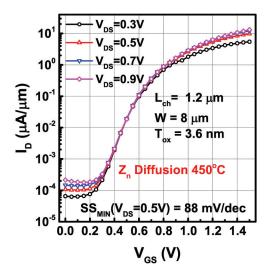

| 4.4  | Transfer characteristics of an InGaAs TFET with $L_{ch}$ =1.2 µm and 3.6 nm Al <sub>2</sub> O <sub>3</sub> (EOT=1.8 nm) as dielectric. P+ region is doped through Zn Diffusion at 450 °C                                                                                                                                                                                                                                           |    | 63  |

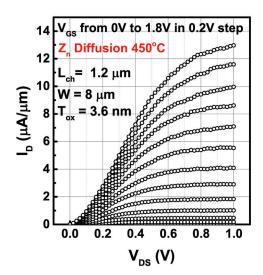

| 4.5  | Output characteristics of the same device shown in Fig. 4.4                                                                                                                                                                                                                                                                                                                                                                        |    | 63  |

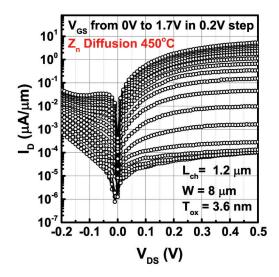

| 4.6  | Output characteristics in log-scale of the same device shown in Fig. 4.4. Negative differential resistance is observed in negative $V_{DS}$ region                                                                                                                                                                                                                                                                                 |    | 64  |

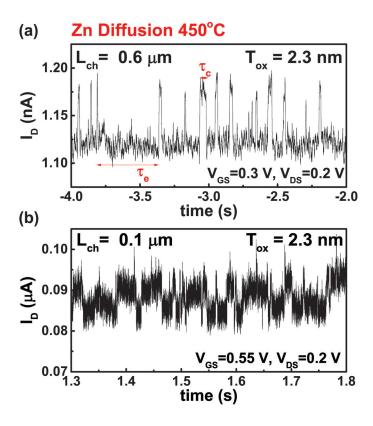

| 4.7  | $I_D$ fluctuation due to RTN in (a) InGaAs TFET with $L_{ch}{=}0.6\mu\text{m}$ (b) InGaAs TFET with $L_{ch}{=}0.1\mu\text{m}$                                                                                                                                                                                                                                                                                                      |    | 65  |

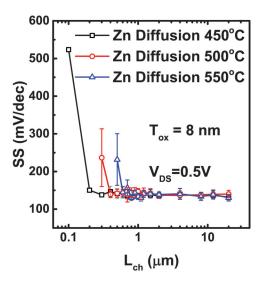

| 4.8  | SS scaling metrics for InGaAs TFET with 8 nm $Al_2O_3$ as gate dielectric and p+ region is doped by Zn diffusion from 450 °C to 550 °C                                                                                                                                                                                                                                                                                             |    | 66  |

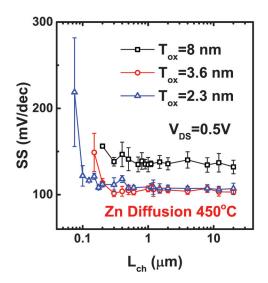

| 4.9  | SS scaling metrics for InGaAs TFETs with 2.3 nm to 8 nm $Al_2O_3$ as gate dielectric and p+ region is doped by Zn diffusion from 450 °C                                                                                                                                                                                                                                                                                            |    | 66  |

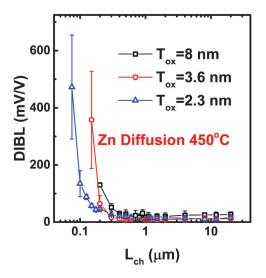

| 4.10 | DIBL scaling metrics for InGaAs TFETs with 2.3 nm to 8 nm $\rm Al_2O_3$ as gate dielectric and p+ region is doped by Zn diffusion from 450 °C                                                                                                                                                                                                                                                                                      |    | 67  |

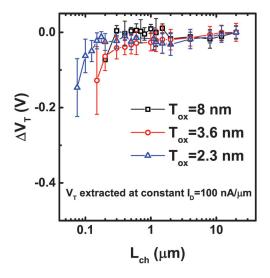

| 4.11 | $V_T$ roll-off for InGaAs TFETs with 2.3 nm to 8 nm Al <sub>2</sub> O <sub>3</sub> as gate dielectric and p+ region is doped by Zn diffusion at 450 °C                                                                                                                                                                                                                                                                             |    | 67  |

| Figu | re                                                                                                                                                                                                                                                                                    | Pa | age |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

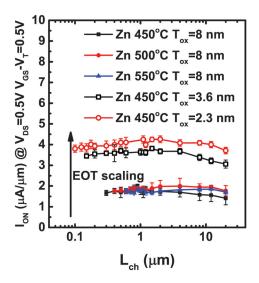

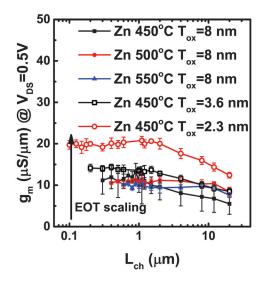

| 4.12 | $I_{ON}$ scaling metrics for InGaAs TFETs with 2.3 nm to 8 nm Al <sub>2</sub> O <sub>3</sub> as gate dielectric and p+ region is doped by Zn diffusion from 450 °C to 550 °C.                                                                                                         | •  | 68  |

| 4.13 | Maximum $g_m$ scaling metrics for InGaAs TFETs with 2.3 nm to 8 nm $Al_2O_3$ as gate dielectric                                                                                                                                                                                       |    | 68  |

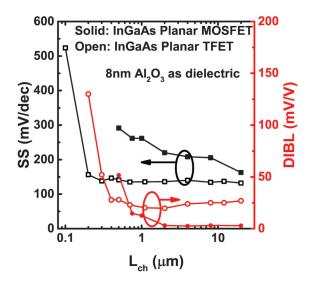

| 4.14 | Comparison of SS scaling metrics between InGaAs TFETs and InGaAs planar MOSFETs with 8 nm Al <sub>2</sub> O <sub>3</sub> as gate dielectric. The InGaAs planar MOSFETs has a lightly doped channel with $N_A$ =1 × 10 <sup>17</sup> cm <sup>-3</sup>                                  |    | 69  |

| 4.15 | (a) Cross-sectional view and (b) top view schematic diagrams of an InGaAs GAA TFET                                                                                                                                                                                                    |    | 71  |

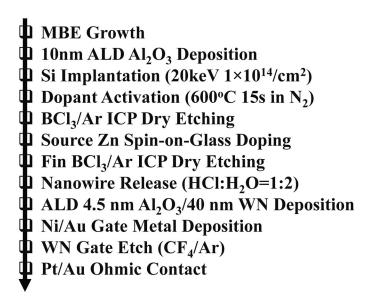

| 4.16 | Fabrication process flow for the InGaAs GAA TFET                                                                                                                                                                                                                                      |    | 72  |

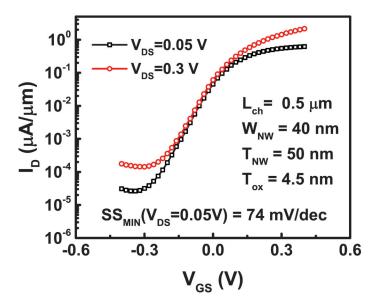

| 4.17 | Transfer characteristics of an InGaAs GAA TFET with $L_{ch}$ =0.5 µm and 4.5 nm Al <sub>2</sub> O <sub>3</sub> (EOT=2 nm) as dielectric                                                                                                                                               |    | 73  |

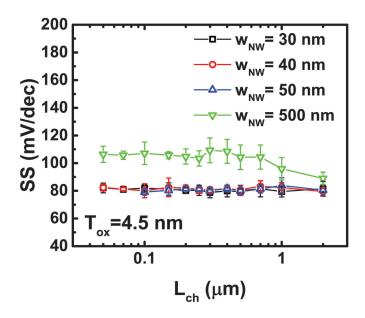

| 4.18 | SS scaling metrics for InGaAs GAA TFETs with 4.5 nm Al <sub>2</sub> O <sub>3</sub> as gate dielectric and with various $W_{NW}$                                                                                                                                                       |    | 74  |

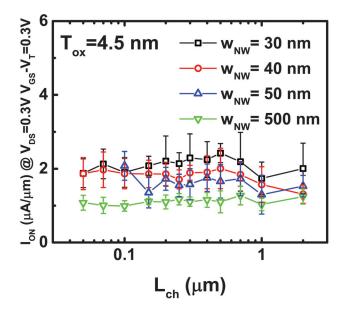

| 4.19 | $I_{ON}$ scaling metrics for InGaAs GAA TFETs with 4.5 nm Al <sub>2</sub> O <sub>3</sub> as gate dielectric and with various $W_{NW}$                                                                                                                                                 |    | 74  |

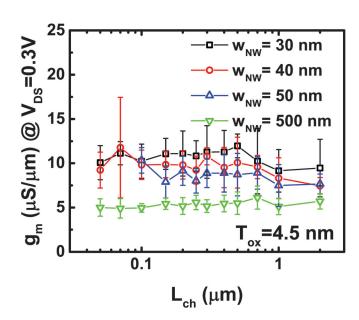

| 4.20 | $\mathbf{g}_m$ scaling metrics for InGaAs GAA TFETs with 4.5 nm $\mathrm{Al_2O_3}$ as gate dielectric and with various $W_{NW}$                                                                                                                                                       |    | 75  |

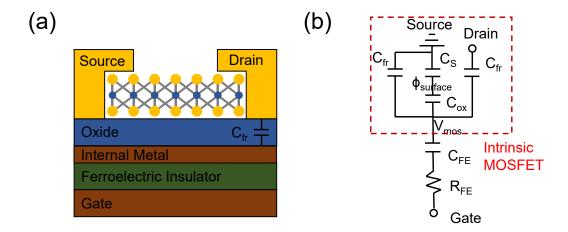

| 5.1  | (a) Schematic diagram of a back-gate 2D NC-FET. (b) Simplified small-signal capacitance representation of the 2D NC-FET. $C_S$ is the capacitance of 2D channel, $C_{ox}$ is the capacitance of the oxide layer, and $C_{FE}$ is the capacitance of the ferroelectric insulator layer |    | 77  |

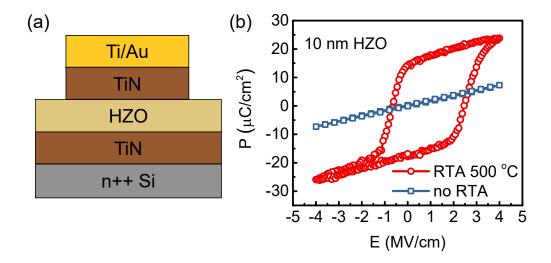

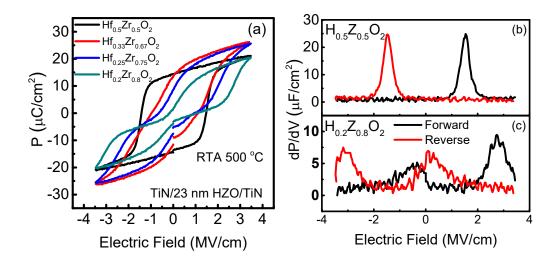

| 5.2  | (a) Schematic diagram of a HZO MIM capacitor. (b) Polarization-electric field measurement of HZO MIM capacitors without RTA and RTA at 500 °C in $N_2$ for 1 min                                                                                                                      | •  | 79  |

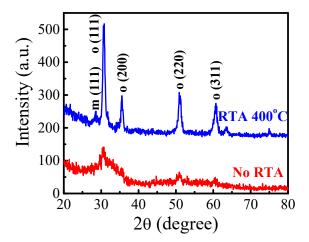

| 5.3  | GI-XRD diffractograms of HZO. The formation of non-centrosymmetric ophase is believed to lead to the ferroelectricity of HZO films after annealing at $400^{\circ}\text{C}.$                                                                                                          |    | 79  |

| 5.4  | (a) Hysteresis loop of P-E for $TiN/23nm$ HZO/ $TiN$ MIM capacitors with different Hf:Zr ratio. $dP/dV$ vs. electric field for both (b) ferroelectric and (c) anti-ferroelectric HZO with different Hf:Zr ratio                                                                       |    | 80  |

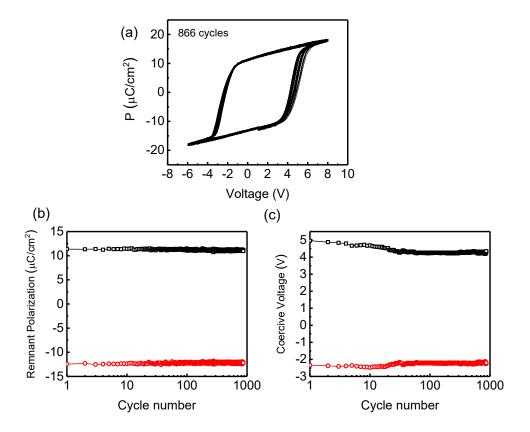

| 5.5  | (a) Polarization-voltage measurement for 866 cycles (4 ms measurement time for each) on the same HZO MIM capacitor. (b) Remnant polarization versus cycle number. (c) Coercive voltage versus cycle number                                                                            | •  | 81  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

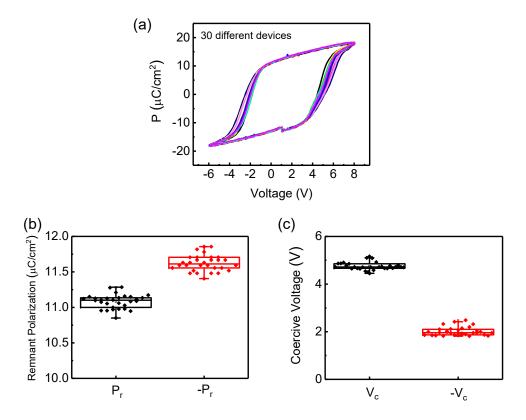

| 5.6  | (a) P-V measurement of 30 different HZO MIM capacitor devices. (b) Box plot of statistical distribution of remnant polarization. (c) Box plot of statistical distribution of coercive voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 82 |

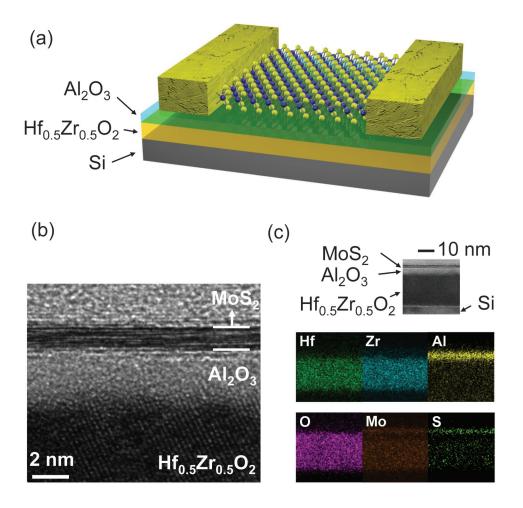

| 5.7  | (a) Schematic view of a $MoS_2$ NC-FET. (b) Cross-sectional view of a representative sample showing bi-layer $MoS_2$ channel, amorphous $Al_2O_3$ and polycrystalline HZO gate dielectric. (c) Corresponding EDS elemental mapping showing the distribution of elements of Hf, Zr, Al, O, Mo and S.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 85 |

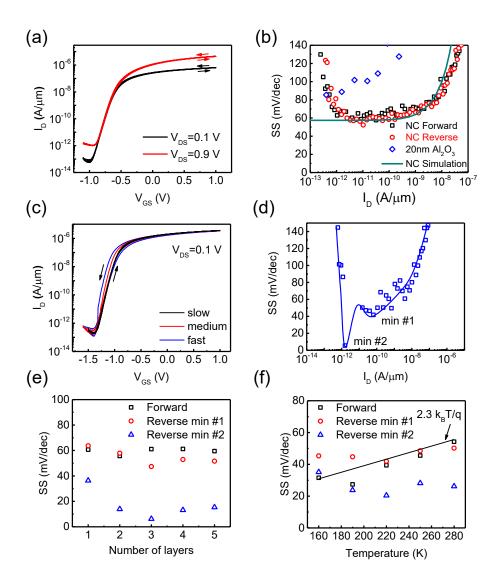

| 5.8  | (a) $I_D - V_{GS}$ characteristics measured at room temperature and at $V_{DS}$ from 0.1 V to 0.9 V. (b) SS versus $I_D$ characteristics of the same device in (a), showing minimum SS below $60\mathrm{mV/dec}$ for both forward and reverse sweep. (c) $I_D - V_{GS}$ characteristics measured at room temperature and at $V_{DS}$ =0.1 V at different gate voltage sweep speed. (d) SS versus $I_D$ characteristics during fast reverse sweep of the same device in (c). The SS versus $I_D$ characteristics show two local minima, defined as min #1 and min #2. (e) Layer dependence of SS from 1 layer to 5 layers. The SS of MoS <sub>2</sub> NC-FETs shows weak thickness dependence. (f) Temperature dependence of SS from 160 K layer to 280 K | . 86 |

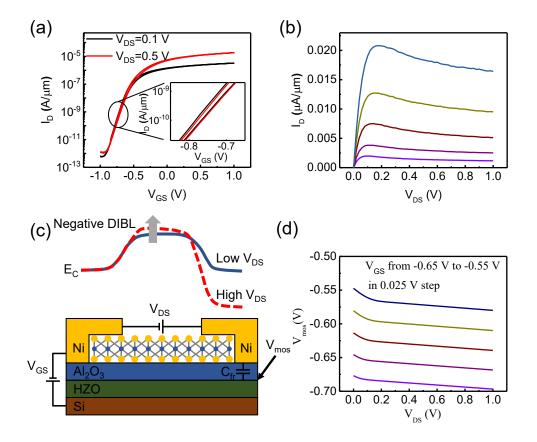

| 5.9  | (a) $I_D - V_{GS}$ characteristics measured at room temperature and at $V_{DS}$ at 0.1 V and 0.5 V. Inset: zoom-in image of $I_D - V_{GS}$ curve between $-0.8$ V to $-0.7$ V. (b) $I_D - V_{DS}$ characteristics measured at room temperature at $V_{GS}$ from $-0.65$ V to $-0.55$ V in $0.025$ V step. Clear NDR can be observed because of the negative DIBL effect induced by negative capacitance. (c) Illustration of band diagram of negative DIBL effect. (d) Simulation of interfacial potential vs. $V_{DS}$                                                                                                                                                                                                                                  | . 88 |

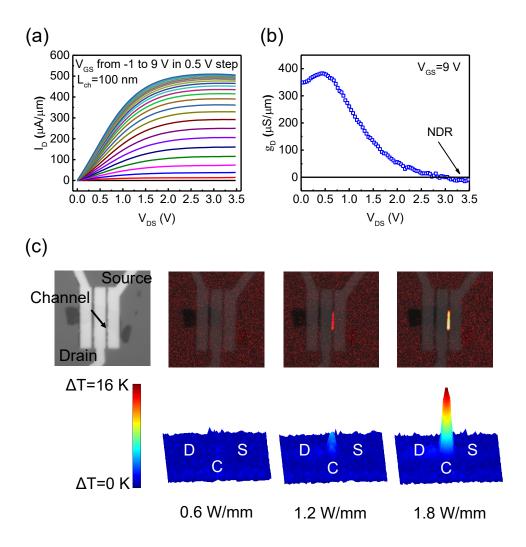

| 5.10 | (a) $I_D - V_{DS}$ characteristics measured at room temperature at $V_{GS}$ from $-1\mathrm{V}$ to $9\mathrm{V}$ in $0.5\mathrm{V}$ step. This device has a channel length of $100\mathrm{nm}$ . (b) $\mathrm{g}_D - V_{DS}$ characteristics from (a) at $V_{GS} = 9\mathrm{V}$ . $\mathrm{g}_D$ less than zero at high $V_{DS}$ highlights the NDR effect due to self-heating. (c) Thermo-reflectance image and (d) temperature map at different power density from $0.6\mathrm{W/mm}$ to $1.8\mathrm{W/mm}$                                                                                                                                                                                                                                            | . 90 |

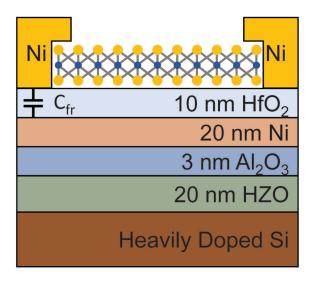

| 5.11 | Schematic of a $MoS_2$ NC-FETs with internal metal gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 92 |

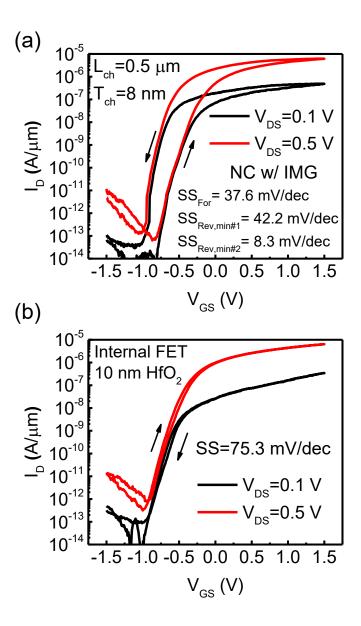

| 5.12 | (a) $I_D - V_{GS}$ characteristics of a MoS <sub>2</sub> NC-FET with IMG measured at room temperature, same structure as Fig. 5.11. (b) $I_D - V_{GS}$ characteristics of the internal MoS <sub>2</sub> FET of the same device as (a) but has 10 nm HfO <sub>2</sub> as gate dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 93 |

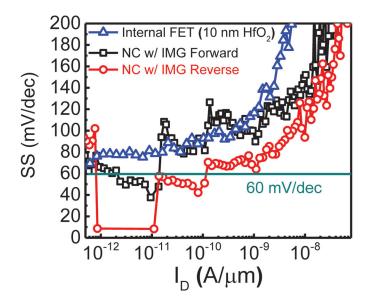

| 5.13 | SS vs. $I_D$ characteristics of MoS <sub>2</sub> NC-FET with IMG and internal MoS <sub>2</sub> FET of the same device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 94 |

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

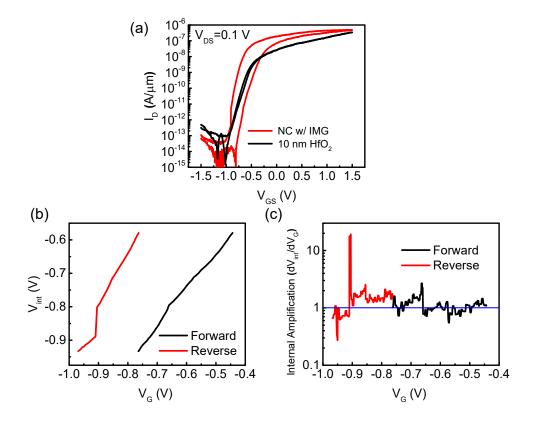

| 5.14   | (a) $I_D - V_{GS}$ characteristics comparison between MoS <sub>2</sub> NC-FET with IMG and the internal MoS <sub>2</sub> FET of the same device. (b) $V_{int}$ vs. $V_G$ for MoS <sub>2</sub> NC-FET with IMG calculated based on internal MoS <sub>2</sub> FET as in (a). (c) Internal amplification calculated based on $\mathrm{d}V_{int}/\mathrm{d}V_G$ in (b)                                                                                                          | . 95 |

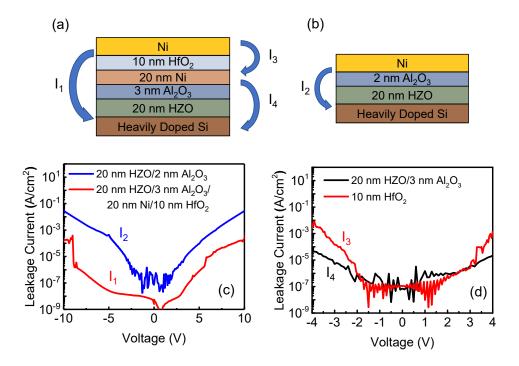

| 5.15   | (a) Cross-sectional view of a capacitor for leakage current measurement with same gate stack as $\text{MoS}_2$ NC-FET with IMG. (b) Cross-sectional view of a capacitor for leakage current measurement with same gate stack as $\text{MoS}_2$ NC-FET without IMG. (c) Leakage current density of the gate stack of $\text{MoS}_2$ NC-FET with/without IMG $(I_1/I_2)$ . (4) Leakage current density of internal gate dielectric $(I_3)$ and of ferroelectric stack $(I_4)$ | . 96 |

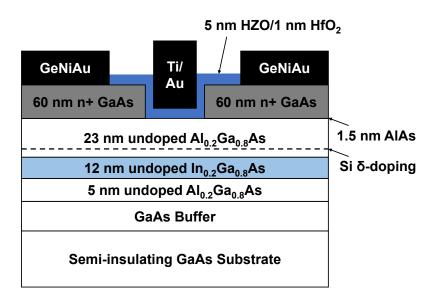

| 5.16   | Cross-sectional view of an InGaAs NC-FET with ferroelectric MOSHEMT structure                                                                                                                                                                                                                                                                                                                                                                                               | . 97 |

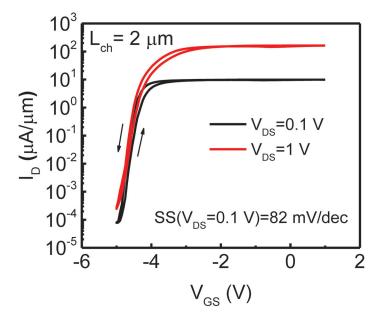

| 5.17   | $I_D-V_{GS}$ characteristics of a representative InGaAs NC-FET with 2 μm channel length                                                                                                                                                                                                                                                                                                                                                                                     | . 99 |

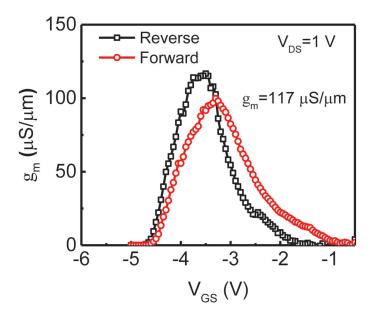

| 5.18   | $g_m-V_{GS}$ characteristics at $V_{DS}{=}1\mathrm{V}$ of the same InGaAs NC-FET as in Fig. 5.17                                                                                                                                                                                                                                                                                                                                                                            | . 99 |

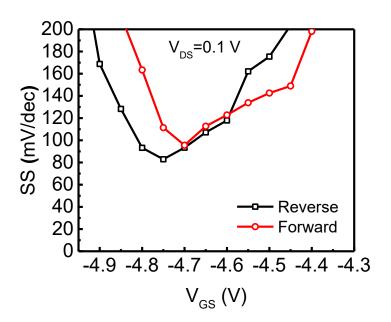

| 5.19   | SS versus $V_{GS}$ characteristics at $V_{DS}$ =0.1 V of the same InGaAs NC-FET as in Fig. 5.17                                                                                                                                                                                                                                                                                                                                                                             | 100  |

## SYMBOLS

m mass

v velocity

f frequency

$k, k_B$  Boltzmann constant

q elementary charge

T temperature

Q charge

A area

$V_{DD}$  supply voltage

$V_{GS}$  gate-to-source voltage

$V_{DS}$  drain-to-source voltage

$V_S$  source voltage

$V_D$  drain voltage

$V_G$  gate voltage

$V_T$  threshold voltage

$V_c$  coercive voltage

t time

$C_L$  load capacitance

$C_{ox}$  oxide capacitance

$C_D$  depletion capacitance

$C_S$  semiconductor capacitance

$C_{GB}$  gate to top barrier capacitance

$C_{SB}$  source to top barrier capacitance

$C_{DB}$  drain to top barrier capacitance

$C_{FE}$  capacitance of ferroelectric insulator

$C_{fr}$  fringe capacitance

$C_{it}$  interface trap capacitance

$D_{it}$  interface trap density

$\epsilon_{ox}$  oxide permitivity

$I_{ON}$  on-current

$I_{OFF}$  off-current

$I_{DS}$  drain-to-source current

$I_D$  drain current

$I_S$  source current

$\mu$  mobility

W channel width

$W_{Fin}$  fin width

$W_{NW}$  nanowire width

$T_{NW}$  nanowire thickness

$T_{ch}$  channel thickness

$T_{ox}$  oxide thickness

$t_{FE}$  ferroelectric insulator thickness

$L_{NW}$  nanowire length

$L, L_{ch}$  channel length

$L_{mask}$  mask length

P power

$P_D$  dynamic power

$P_S$  static power

$P_r$  remnant polarization

$N_T$  number of transistors per unit area

N number of carriers

$E_G$  bandgap

$E_c$  coercive field

$E_F$  fermi level

$E_C$  conduction band energy level

$E_V$  valence band energy level

$g_m$  transconductance

$g_D$  drain conductance

$R_{SD}$  S/D series resistance

$R_S$  source series resistance

$R_D$  drain series resistance

$R_C$  contact resistance

$R_{sh}$  sheet resistance

$\Phi_S$  surface potential

$S_{I_S}$  source current power spectral density

$S_{Vg}$  input gate noise

$au_c$  capture time constant

$au_e$  emission time constant

## **ABBREVIATIONS**

FET field-effect transistor

MOSFET metal-oxide-semiconductor field-effect transistor

MOSHEMT metal-oxide-semiconductor high-electron-mobility transistor

CMOS complementary metal-oxide-semiconductor

CPU central process unit C-V capacitance voltage

I-V current voltage

ALU arithmetic logic unit

IC integrated circuit

GND ground

SOI semiconductor on insulator

2D 2-dimensional 3D 3-dimensional

SCE short channel effect

CNL charge neutral level

TNL trap neutral level

EOT equivalent oxide thickness

GAA gate-all-around

TFET tunneling field-effect transistor

NC-FET negative-capacitance FET

MEMS microelectromechanical system

TMD transition metal dichalcogenide

BTBT band-to-band tunneling

SS subthreshold slope

TMA trimethylaluminum

S/D source and drain

n+ highly n-doped

p+ highly p-doped

MBE molecular beam epitaxy

ALD atomic layer deposition

RTA rapid thermal annealing

DIBL drain induced barrier lowering

WN tungsten nitride

FGA forming gas anneal

TEM transmission electron microscope

STD standard deviation

LFN low frequency noise

RTN random telegraph noise

FDSOI fully depleted SOI

PSD power spectral density

PBTI positive bias temperature instability

HCI hot carrier injection

SOG spin on glass

NDR negative differential resistance

BP black phosphorus

P-E polarization-electric field

P-V polarization-voltage

FE ferroelectric

AFE anti-ferroelectric

LK Landau-Khalatnikov

MIM metal-insulator-metal

HZO hafnium zirconium oxide

XRD X-ray diffraction

JL junctionless

IMG internal metal gate

EDS energy dispersive X-ray spectrometry

#### ABSTRACT

Si, Mengwei PhD, Purdue University, August 2018. III-V and 2D Devices: from MOSFETs to Steep-Slope Transistors. Major Professor: Peide D. Ye.

With silicon CMOS technology approaching the scaling limit, alternating channel materials and novel device structures have been extensively studied and attracted a lot of attention in solid-state device research. In this dissertation, solid-state electron devices for post-Si CMOS applications are explored including both new materials such as III-V and 2D materials and new device structures such as tunneling fieldeffect transistors and negative capacitance field-effect transistors. Multiple critical challenges in applying such new materials and new device structures are addressed and the key achievements in this dissertation are summarized as follows: 1) Development of fabrication process technology for ultra-scaled planar and 3D InGaAs MOSFETs. 2) Interface passivation by forming gas anneal on InGaAs gate-all-around MOSFETs. 3) Characterization methods for ultra-scaled MOSFETs, including a correction to subthreshold method and low frequency noise characterization in short channel devices. 4) Development of short channel InGaAs planar and 3D gate-allaround tunneling field-effect transistors. 5) Negative capacitance field-effect transistors with hysteresis-free and bi-directional sub-thermionic subthreshold slope and the integration with various channel materials such as InGaAs and MoS<sub>2</sub>.

# 1. INTRODUCTION

# 1.1 Computer and Binary Logic

The digital revolution, known as the "Third Industrial Revolution", origins from the invention of modern computers. Modern computers are digital machines using binary logic with "1" and "0" only in the Boolean algebra. Computing machines with continuous values are the analog computers. They used machinery that represented continuous numeric quantities such as angle of shark rotation or electrical potential. However, digital computers have shown their superior over analogy ones in terms of robustness, complexity and speed.

Binary logic is the logic system used in modern digital computers, in which "1" represents by a electrical potential, usually a high supply voltage, and "0" represents by a different electrical potential, usually a ground potential. The formal theory of binary computing dates back to 18<sup>th</sup> century, when G. W. Leibnitz invented the binary number system. The binary logic was proved by G. Boole to be a complete system that allows computational processes to be mathematically modeled [1].

There are three basic logic gates, NOR, AND and OR with logic "1" and logic "0" as inputs and outputs. All other logics can be obtained from these three simple logics. They are the building blocks of the arithmetic logic unit (ALU) of the central process unit (CPU). Mathematically, with the three basic logic gates, any complicated arithmetic process can be achieved. Therefore, to build up a computer system, a major task is to found physical states to represent the logic "0" and logic "1", and find the physical method to do all the three basic operations. The logic "0" and logic "1" can be different in different type of computers. For example, in the old mechanical computer, the position of an object or the angle of rotation can be used for different

logic levels. In more advanced computing concepts, electrons with quantized spin state, spin up and spin down can be used for logic levels, so-called spin transistors [2].

# 1.2 Charge Based Logic and High Performance Computing

In current silicon based complementary metal-oxide-semiconductor (CMOS) technology, the logic "1" and logic "0" are represented by a high voltage and a low voltage. The NOR, AND and OR operations are achieved through the proper connection of a set of metal-oxide-semiconductor field-effect transistors (MOSFETs). Traditionally, supply voltage  $(V_{DD})$  is used as high voltage for logic "1" and ground (GND) is used as low voltage for logic "0". The pMOSFETs are used to drive the output voltage from GND to  $V_{DD}$  through current flow from  $V_{DD}$  to the output capacitor and the nMOSFETs are used to drive the output voltage from  $V_{DD}$  to GND through current flow from the output capacitor to GND. The time to complete this single logic operation can be estimated as

$$t = \frac{C_L V_{DD}}{I_{ON}} \tag{1.1}$$

where t is time consumed in a single logic operation,  $C_L$  is the load capacitance and  $I_{ON}$  is the drive current of the MOSFET. Therefore, the requirements for high performance MOSFETs are divided into three parts if the three items are independent of each other.

- small load capacitance  $C_L$

- small supply  $V_{DD}$

- large on-current  $I_{ON}$

According to the square law of current-voltage characteristics of a MOSFET [3], explicitly

$$I_{DS} = \frac{W\mu C_{ox}}{L} [(V_{GS} - V_T)V_{DS} - V_{DS}^2] \qquad for \qquad V_{DS} < V_{GS} - V_T, \tag{1.2a}$$

and

$$I_{DS} = \frac{W\mu C_{ox}}{L} (V_{GS} - V_T)^2 \quad for \quad V_{DS} \ge V_{GS} - V_T$$

(1.2b)

where

$$C_{ox} = \frac{\epsilon_{ox}}{T_{ox}} \tag{1.2c}$$

and  $I_{DS}$  is drain-to-source current, W is channel width, L is channel length,  $\mu$  is the mobility,  $V_{GS}$  is gate-to-source voltage,  $V_{DS}$  is drain-to-source voltage and  $V_T$  is threshold voltage. Meanwhile,  $I_{ON}$  is defined as  $I_{DS}$  at  $V_{GS}=V_{DS}=V_{DD}$ , which is given by

$$I_{ON} \sim \frac{W\mu C_{ox}}{L} V_{DD}^2. \tag{1.3}$$

Considering both eq. (1.1) and (1.3), we can get the conclusion that reducing  $V_{DD}$  is not a good idea as  $V_{DD}$  and  $I_{ON}$  are correlated. Therefore, the criteria for high speed integrated circuits (ICs) should be modified as following

- small load capacitance  $C_L$

- large on current  $I_{ON}$

As a result, by reducing L,  $I_{ON}$  becomes larger while  $C_L$  becomes smaller as part of  $C_L$  is the gate capacitance which is proportional to L. So the time per logic operation will be reduced so that the speed of the ICs can be improved. Therefore, for transistors and ICs, it is always said, "Smaller is better".

#### 1.3 The Moore's Law and Power-constraint Scaling

Then it comes to the famous "Moore's Law", which originated from 1965 by G. E. Moore, states that the number of transistors per unit area has doubled and will double approximately every 18 months. Moore observed and predicted the revolution of semiconductor industry which last even until the author writes this thesis at 2018. However, although transistor number per unit area keeps increasing and transistor

Fig. 1.1. (a) Clock rate of selected CPU versus year. (b) Power density of selected CPU versus year. Data source from Ref. [4].

size keeps shrinking, the power density of CPU saturates at  $\sim 100\,\mathrm{W/cm^2}$  and clock rate saturates at  $\sim 4\,\mathrm{GHz}$  since 2000 [4,5], as shown in Fig. 1.1. It shows that the scaling down of CMOS technology is now limited by the power density, which lead to

too much heat generation to dissipate. The power density of an IC can be expressed as,

$$P = P_S + P_D \tag{1.4}$$

where P is power,  $P_S$  is static power when the circuits are in off-state and  $P_D$  is the dynamic power which represents the power consumption during a logic operation. The dynamic power is mainly due to the charging or discharging to the load capacitor when the logic level is changed. The static power is mainly caused by off-state leakage current, such as subthreshold current, junction leakage and tunneling leakage current. Here we assume subthreshold current dominate the off-current  $(I_{OFF})$ , which is the general case in ICs. The dynamic power and static power can be expressed approximately as

$$P_D \sim N_T C_L V_{DD}^2 f,\tag{1.5}$$

and

$$P_S \sim N_T I_{OFF} V_{DD} \tag{1.6}$$

where  $N_T$  is transistor density and f is the clock frequency or clock rate. If we reduced the size of the transistor by a factor of  $\alpha$  ( $\alpha$  < 1) so that  $L \to \alpha L$ ,  $W \to \alpha W$ ,  $T_{ox} \to \alpha T_{ox}$ . Thus,  $N_T \to \frac{1}{\alpha^2} N_T$  and  $C_L \to \alpha C_L$  for a simple gate capacitor approximation. The actual  $C_L$  is larger than this approximation due to other parasitic effects. Therefore, if f and  $V_{DD}$  keep unchanged, the dynamic power density of the IC will increase by at least  $1/\alpha$  and the static power of the IC will increase by  $1/\alpha^2$ , which will make the chip too hot to work. The clock frequency should not be reduced because reducing clock frequency means the reduction of CPU performance. Thus, the only way to keep the CMOS scaling trend is to reduce  $V_{DD}$ .

However, to reduce  $V_{DD}$  is not as simple as just reduce the supply voltage. Firstly, simply reduce  $V_{DD}$  without doing anything will result in  $I_{ON}$  reduction so that device performance will degrade, according to eq. (1.2b). Second, if  $I_{ON}$  is kept unchanged

Fig. 1.2. (a)  $V_{DD}$  reduces while  $I_{ON}$  is kept the same in MOSFETs. (b) The effect of mobility enhancement at same  $I_{OFF}$ . (c) The effect of SS reduction at same  $I_{OFF}$ .

by engineering threshold voltage  $(V_T)$ ,  $I_{OFF}$  will increase so that  $P_S$  is increased, as shown in Fig. 1.2(a).

There are two ways to solve this problem. Both of them are hot research topics in electron device research currently. The one is to use high mobility material as channel material so that  $I_{ON}$  will increase so that a lower  $V_{DD}$  can be applied, as shown in Fig. 1.2(b). No  $I_{OFF}$  increase will happen if  $V_T$  and subthreshold slope (SS) are the same. The other way is to reduce SS or use steep-slope transistors. SS reduction in traditional MOSFETs can be achieved using advanced 3-dimensional (3D) structure or thin-body semiconductor on insulator (SOI) structure in terms of short channel effects (SCEs) reduction but it has a thermionic limit of  $\sim 60 \,\mathrm{mV/dec}$  at room temperature. Steep-slope transistor are transistors with SS less than the thermionic limit of MOSFETs. As a result, steep-slope transistors can work at a lower  $V_{DD}$  comparing with MOSFETs without decrease of  $I_{ON}$  or increase of  $I_{OFF}$ , as shown in Fig. 1.2(c). Both MOSFETs with high mobility channel materials and steep-slope transistors will be discussed further in the following sections.

## 1.4 MOSFETs with High Mobility Channel Materials

Silicon has many unique advantages so that it is the channel material in semiconductor industry for logic applications in the past decades.

- Only homogeneous oxide, SiO<sub>2</sub>, is formed during thermal oxidation while never happens on compound semiconductors or even on Ge.

- Low interface trap density  $(D_{it})$  on  $SiO_2/Si$  interface.

- Suitable bandgap  $(E_G)$

- Balanced mobility for both electrons and holes

However, silicon has little advantage in electron and hole mobilities over other high mobility III-V materials and Ge. Fig. 1.3 shows the electron and hole mobilities comparison among group IV and III-V semiconductor materials. The first thing to consider is that which material is the most suitable for transistors other than silicon. Here, the concept of fermi level pinning is introduced before the study of Ge and III-V materials. The fermi level pinning problem is mainly caused by the

Fig. 1.3. (a) Electron and (b) hole mobilities comparison among group IV and III-V semiconductor materials.

Fig. 1.4. Charge neutral level alignments over selected semiconductor materials.

interface traps such that fermi level  $(E_F)$  at the oxide/semiconductor interface are pinned to a certain energy level, as shown in the charge neutral level (CNL) alignments over selected semiconductor materials in Fig. 1.4. For III-V materials, the  $E_F$  at the oxide/semiconductor interface is difficult to move too far from the CNL due to the relatively high and U-shape  $D_{it}$  [6]. As a result, if the CNL aligns to near the conduction band  $(E_C)$ , it is easier to have electrons accumulated in the oxide/semiconductor interface while if the CNL aligns to near the valence band  $(E_V)$ , it is easier to have holes accumulated in the oxide/semiconductor interface. Therefore, by selecting semiconductors with proper CNL, the fermi level pinning problem can be reduced.

Other than interface quality, bandgap of semiconductor is also an important character for solid state devices. For MOSFETs targeting on high speed and low power applications, too small bandgap will result in high thermal emission leakage current, large tunneling leakage current and high impact ionization current. Meanwhile, too

wide bandgap causes difficulties in channel inversion at same  $D_{it}$  level. Table 1.1 summaries the bandgap of common semiconductor materials at room temperature.

$\begin{tabular}{ll} Table 1.1. \\ Bandgap of common semiconductors at <math>300\,\mathrm{K}$  \end{tabular}

| Semiconductor                                     | $E_G$ (eV) |

|---------------------------------------------------|------------|

| Si                                                | 1.12       |

| Ge                                                | 0.661      |

| GaAs                                              | 1.424      |

| InAs                                              | 0.354      |

| $\mathrm{In}_{0.53}\mathrm{Ga}_{0.47}\mathrm{As}$ | 0.74       |

| InP                                               | 1.344      |

| GaSb                                              | 0.726      |

| InSb                                              | 0.17       |

| GaN (Wurtzite)                                    | 3.39       |

| GaN (Zinc Blende)                                 | 3.2        |

| AlN                                               | 6.2        |

| InN                                               | 1.9-2.05   |

| $\operatorname{SiC}$                              | 2.36       |

| GaP                                               | 2.26       |

\*Data source from [7]

Summarizing the above discussion, to apply high mobility channel materials into CMOS ICs, here are the requirements which have to be considered.

- Higher electron or hole mobility comparing with silicon.

- Relative low  $D_{it}$ . CNL aligns near  $E_C$  for nMOSFETs while CNL aligns near  $E_V$  for pMOSFETs.

- Suitable bandgap  $(E_G)$

- Ability to co-integrate onto same wafer for both nMOSFETs and pMOSFETs.

Therefore, considering both Fig. 1.3, Fig. 1.4 and Table 1.1, InGaAs has the most potential for nMOSFETs because its high electron mobility, CNL aligns near  $E_C$  and reasonable bandgap (0.74 eV in In<sub>0.53</sub>Ga<sub>0.47</sub>As). Although it has lower mobility comparing with InAs and InSb, but InAs and InSb have too small  $E_G$ . In the same way, Ge is considered to be a potential channel material for pMOSFETs because its high hole mobility, CNL aligns near  $E_V$  and reasonable bandgap (0.661 eV).

## 1.5 SS Reduction in MOSFETs and Steep-slope Transistors

# 1.5.1 Device Scaling and Short Channel Effects

As discussed in chapter 1.3, scaling is one of the major driven force in semiconductor industry. Currently, silicon CMOS technology has entered 10 nm technology node. SS has a thermionic limit of 60 mV/dec for MOSFETs. However, at short channel devices, it becomes more difficult to approach this limit due to SCEs because SS becomes larger when SCEs become stronger. The key to reduce the SCEs in MOSFETs is to make the distance between channel area and gate electrode as close as possible, in other words, to improve the gate control ability. To achieve this goal, there are several methods that can be applied in MOSFET engineering [8–12]. Firstly, reducing the equivalent oxide thickness (EOT) in gate dielectric to improve the gate control. Second, increasing the channel doping so that the depletion width can be reduced. Thus, channel area is closer to the gate. But to increase channel doping means to reduce carrier mobility. Halo technology is to increase channel doping only near the source and drain which has the same mechanism as increase channel doping uniformly but it has other benefits such as lower doping channel for higher carrier mobility. These two methods are applied for decades before 22 nm technology node was introduced to replace planar bulk silicon CMOS technology. Third, by introducing thin body SOI structure, depletion width is limited by the thickness of the semiconductor so that channel is more close the gate electrode. Note that 2-dimensional (2D) materials play the same role as SOI structure in terms of SCEs control. Forth, applying 3D structure, such as FinFET structure or gate-all-around (GAA) structure to improve the channel control ability. FinFET was introduced in 22 nm node by Intel. The GAA structure has stronger immunity to SCEs than FinFET structure so that it might be applied in future CMOS technology nodes. Here the methods to reduce SCEs in MOSFETs are summarized.

- Reducing EOT.

- Increasing channel doping, uniformly or halo.

- Applying thin body SOI structure or 2D materials.

- Applying 3D structures such as FinFET or GAA.

Although it seems that there are many methods to further scale the devices, people are really approaching the physical limit of MOSFETs. Now in the smallest device, there are only less than 100 silicon atoms between source and drain. Quantum effects might destroy the MOSFET operation once the device is further scaled to ten silicon atoms or less.

## 1.5.2 Steep-slope Transistors

The motivation of steep-slope transistors has already been discussed in chapter 1.3. Many device concepts have been proposed to surpass this limitation such as the Tunneling FET (TFET) [13,14], negative-capacitance FET (NC-FET) [15–17] and microelectromechanical (MEMS) switch [18,19]. The SS of traditional MOSFET can be expressed as

$$SS = ln(10)\frac{kT}{q}(1 + \frac{C_{it} + C_S}{C_{ox}})$$

(1.7)

where k is Boltzmann constant, T is temperature, q is elementary charge,  $C_{it}$  is interface trap capacitance and  $C_S$  is the semiconductor capacitance. In most cases,  $C_S$  can approximately equal to depletion capacitance  $(C_D)$ . For transistor with ideal interface  $(C_{it}=0)$  and  $C_S \ll C_{ox}$ , eq. 1.7 becomes

$$SS = ln(10)\frac{kT}{q}. (1.8)$$

It is also known as the thermionic limit of SS for MOSFET ( $\sim 60\,\mathrm{mV/dec}$  at room temperature) because thermal emission over the channel barrier dominates the subthreshold current, which is a temperature dependent process.

Currently there are two popular ways to overcome this limit, tunneling field-effect transistor and negative capacitance field-effect transistor. Both of the above device concepts can be CMOS compatible and are explored in this thesis.

#### Tunneling field-effect transistors

TFET is basically a gated p-i-n diode. Such structure was proposed back to 1970s [20,21] with surface tunneling as carrier transport mechanism. The first TFET with sub-60 mV/dec at room temperature was demonstrated at 2004 [13] which attracted a lot of attention and extensively studied as a steep-slope transistor since then. In the operation mode, the p-i-n diode is reversely biased so that the main current transport mechanism from source to drain is the Zener band-to-band tunneling (BTBT). With a gate voltage on the intrinsic region to control the band bending, such device can be abruptly switched on and off. Moreover, as BTBT isn't a temperature dependent process and subtreshold current in a normal MOSFET induced by thermal emission is blocked due to the existence of the bandgap (no barrier modulation), the SS of a TFET can break the thermionic limit of the subtreshold slope.

# Negative capacitance field-effect transistors

Salahuddin and Datta [15] proposed the negative capacitance field-effect transistor by inserting a ferroelectric insulator into the gate stack the MOSFET. By replacing oxide capacitance to the capacitance of ferroelectric insulator  $(C_{FE})$  in eq. 1.7 as

$$SS = ln(10)\frac{kT}{q}(1 + \frac{C_{it} + C_S}{C_{FE}})$$

(1.9)

where  $C_{FE}$  can be negative so that the overall SS can be less than the thermionic limit  $\ln(10)kT/q$ . The real negative capacitance in ferroelectric insulators cannot be directly measured by capacitance-voltage (C-V) or polarization-voltage (P-V) measurement because it is unstable. However, the negative capacitance effect can exist when it is in series with a positive capacitor, so that the total capacitance can be larger than the positive capacitor. Therefore, the negative capacitance in the ferroelectric insulator can provide a overall internal amplification to break the thermionic limit of MOSFET at  $60 \,\mathrm{mV/dec}$  at room temperature.

#### 1.6 Thesis Outline

This thesis mainly pursues the potential channel materials and novel device structures and innovations, targeting on high speed and low power device applications at the end of silicon CMOS scaling. Chapter 2 mainly discusses nMOSFETs made of high mobility III-V material, InGaAs. InGaAs MOSFETs are studied in terms of device scaling, 3D structure and interface trap reduction. Chapter 3 studies the advanced electrical characterization in MOSFETs with small channel lengths. Chapter 4 discusses the fabrication and characterization of planar and 3D III-V TFETs. Chapter 5 discusses the fabrication and characterization of NC-FET made of III-V and 2D materials. Chapter 6 summaries the thesis and presents a outlook to the development of post-CMOS electron devices.

# 2. III-V MOSFETS FOR LOW POWER AND HIGH PERFORMANCE CMOS LOGIC APPLICATIONS

#### 2.1 Introduction

In 2002, Ye and Wilk started to deposit  $Al_2O_3$  on GaAs [22], which later was proved to have the ability to effectly remove the native oxide of GaAs due to the reaction between Trimethyl Aluminum (TMA) and the native oxide of GaAs [23–25]. This work opens a hot research on MOSFETs with high mobility III-V materials [11,12,26–45]. Currently, InGaAs has been considered as one of the most promising channel materials for future CMOS logic circuits because of its high electron injection velocity, properly aligned CNL and suitable bandgap [46]. People have spent a lot of efforts on fabricating InGaAs MOSFETs with short channel length and high  $I_{ON}$  and many works have been done on improving the oxide/InGaAs interface.

In this chapter, section 2.2 studies a novel dry etching method to obtain sub-10 nm  $L_{ch}$  beyond the lithography resolution limit and this type of MOSFET with  $L_{ch}$  down to  $\sim 3$  nm are demonstrated on both planar devices and FinFETs. To further improve the immunity to short channel effects, in section 2.3, the InGaAs GAA MOSFETs with raised S/D and ultrathin body structures are studied and performance improvement with thinner body are demonstrated. In section 2.4, the effect of forming gas anneal (FGA) on  $Al_2O_3/InGaAs$  interface are studied and it is found that FGA can significantly improve the quality of  $Al_2O_3/InGaAs$  interface.

### 2.2 Ultimately Scaled Sub-10 nm V-Gate InGaAs MOSFETs

There has been several works focusing on the scaling of InGaAs transistors. In-GaAs MOSFETs with implanted source and drain (S/D) have already been demon-

strated with channel length down to 20 nm [11,12,29]. However, InGaAs MOSFETs with implanted S/D structure suffer from large series resistance due to solid solubility limit and source starvation [47,48]. Meanwhile, InGaAs MOSFETs with n+ (highly n-doped) raised S/D structure have been reported by regrowth method [30–33,37,49] or wet etching related methods [34,35] with high on-current. InGaAs MOSFETs with sub-7 nm was also demonstrated by anisotropic wet etching method [36]. In this work, by fully using the anisotropic dry etching properties of III-V, using anisotropic dry etching process is proposed to fabricate the V-Gate InGaAs MOSFETs, featured with n+ reaised S/D and extremely short channel. Lithography etch window length modulation technique is applied to push the  $L_{ch}$  down to sub-10 nm (minimum  $L_{ch} \sim 3$  nm) beyond the lithography resolution limit. Ultimately scaled InGaAs FinFETs and planar MOSFETs with channel length down to sub-10 nm are demonstrated. InGaAs FinFETs with sub-10 nm  $L_{ch}$  shows better immunity to SCEs than planar MOSFETs which is promising for CMOS logic circuits beyond 10 nm technology node.