# A Figure of Merit for Optimization of Nanocrystal Flash Memory Design

Aykutlu Dâna<sup>1</sup>, Imran Akca<sup>1</sup>, Atilla Aydinli<sup>1,\*</sup>, Rasit Turan<sup>2</sup>, and Terje G. Finstad<sup>3</sup>

<sup>1</sup> Department of Physics, Bilkent University, 06800 Ankara, Turkey

<sup>2</sup> Department of Physics, Middle East Technical University, 06800 Ankara, Turkey

<sup>3</sup> Department of Physics, University of Oslo, P.Box 1048 – Blindern, 0316 Oslo, Norway

Nanocrystals can be used as storage media for carriers in flash memories. The performance of a nanocrystal flash memory depends critically on the choice of nanocrystal size and density as well as on the choice of tunnel dielectric properties. The performance of a nanocrystal memory device can be expressed in terms of write/erase speed, carrier retention time and cycling durability. We present a model that describes the charge/discharge dynamics of nanocrystal flash memories and calculate the effect of nanocrystal, gate, tunnel dielectric and substrate properties on device performance. The model assumes charge storage in quantized energy levels of nanocrystals. Effect of temperature is included implicitly in the model through perturbation of the substrate minority carrier concentration and Fermi level. Because a large number of variables affect these performance measures, in order to compare various designs, a figure of merit that measures the device performance in terms of design parameters is defined as a function of write/erase/discharge times which are calculated using the theoretical model. The effects of nanocrystal size and density, gate work function, substrate doping, control and tunnel dielectric properties and device geometry on the device performance are evaluated through the figure of merit. Experimental data showing agreement of the theoretical model with the measurement results are presented for devices that has PECVD grown germanium nanocrystals as the storage media.

**Keywords:** Nanocrystals, Germanium, PECVD, Germanosilicate, Capacitance Spectroscopy, Memory, Retention.

#### 1. INTRODUCTION

Nanocrystals (NCs) formed by annealing silicon dioxide films having excess Si or Ge has attracted much attention due to optical and electronic properties of such nanostructures.<sup>1-3</sup> In particular, NCs embedded in silicon oxide films have been subject of study for their potential applications in memory devices.<sup>4</sup> Among various methods of synthesis of the NCs are, ion implantation into oxide, co-sputtering of oxide and germanium (Ge), low pressure chemical vapor deposition (LPCVD) and plasma enhanced chemical vapor deposition (PECVD) followed by appropriate annealing of the grown films.<sup>5,6</sup> Since many parameters of NCs such as density, size, and composition can be adjusted by proper choice of deposition parameters, NCs offer flexibility in design of flash memory cells. However, understanding of charge storage mechanisms is important in optimization of device performance.

In this paper, we analyze nanocrystal memory charging and retention dynamics by assuming carrier storage in NC energy levels instead of deep traps. Based on this assumption, we present a theoretical model that includes the effect of NC dimensions and density to calculate the charging and discharging dynamics. Gate work function, substrate doping and tunnel dielectric properties are inherently included. This study is restricted to electron storage in Ge NCs for the sake of simplicity. The analysis can be extended to Si NCs by adjustment of material parameters, and can further be extended for hole storage in Si and Ge NCs with proper adjustment of the band-bending model.

# 2. THEORETICAL MODELLING

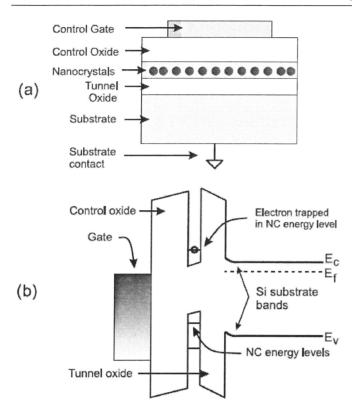

A typical nanocrystal metal-oxide-semiconductor (NC-MOS) memory element consists of a standard MOS capacitor with a layer of NCs embedded in the oxide between the gate and the substrate as shown in Figure 1.

Based on the assumption that only NCs are responsible for charge storage and that a single electron per NC is

<sup>\*</sup>Author to whom correspondence should be addressed.

Fig. 1. Typical nanocrystal MOS capacitor memory test element with an n-type substrate. (a) Cross-section and (b) band diagram of charged element under 0 V bias.

stored for a total of  $n_{\rm NC}$  NCs, the flat-band voltage shift  $\Delta V_{\rm FB}$  is approximately given by<sup>7</sup>

$$\Delta V_{\rm FB} = \frac{q n_{\rm nc}}{\epsilon_{\rm ox}} \left( t_{\rm cox} + \frac{\epsilon_{\rm ox} t_{\rm nc}}{2 \epsilon_{\rm ge}} \right) \tag{1}$$

where q is the electronic charge,  $t_{\rm cox}$  is the control oxide thickness,  $t_{\rm nc}$  is the average diameter of the NCs,  $\in$ 's are the dielectric constants of respective materials.

In order to evaluate dynamical properties of such memory elements, charging and discharging currents must be calculated taking into account tunnelling through the barrier for a given electric field within the tunnelling region. The currents also depend on availability of source and target states. Since there are many device parameters that collectively determine the charge-discharge currents, a simple closed form formula can not be obtained that covers all cases. Therefore, in the following subsections, charge and discharge currents are studied separately, and intuitive formulas are given whenever possible.

## 2.1. Charging of the NC-MOS Element

It is best to capture the essential features of charging dynamics with a minimally complex model. During the write cycle, the device is in accumulation and initially there is no stored charge in the device. In this case, the oxide field  $F_{\rm tox}$  will be determined by the gate voltage during writing,  $V_{\rm write}$ , approximately as  $F_{\rm tox} \simeq V_{\rm write}/t_{\rm ox}$ ,

where  $t_{ox}$  is the total effective oxide thickness. The tunnelling current through a trapezoidal barrier can be calculated in two different limits, the direct tunnelling and Fowler-Nordheim limits. It should be noted that, it is desirable to have low fields in flash memory devices in order to increase device reliability. In the case of direct tunnelling, charging current density can be calculated using a transmission coefficient which can be calculated by the WKB approach for direct tunneling. The charging current density then becomes<sup>8</sup>

$$J_{\rm c} = \frac{AF_{\rm tox}^2}{V_{\rm B}} \times \exp\left[-\left(1 - \left(1 - \frac{F_{\rm tox}t_{\rm tox}}{V_{\rm B}}\right)^{3/2}\right) \frac{BV_{\rm B}^{3/2}}{F_{\rm tox}}\right]$$

(2)

where  $A = q^2 m_{\rm si}/16\pi^2 m_{\rm ox}\hbar$ ,  $B = 2\sqrt{8m_{\rm ox}q}/3\hbar$ ,  $F_{\rm tox}$  is the tunnel oxide field during charging,  $m_{\rm ox}$  is the tunnel effective mass and  $V_{\rm B}$  is the barrier height between the oxide and the substrate. At high fields ( $F_{\rm tox}t_{\rm tox} > V_{\rm B}$ ) the tunnelling is through a triangular barrier (FN regime) and the tunnel transparency term in Eq. (2) must be rewritten, resulting in a charging current density given by

$$J_{\rm c} = \frac{AF_{\rm tox}^2}{V_{\rm B}} \times \exp\left[-\frac{BV_{\rm B}^{3/2}}{F_{\rm tox}}\right] \tag{3}$$

The actual charge deposited will depend on the availability of final states. This can be accounted for by including a capture cross section per nanocrystal. The differential charge deposited per unit area  $d\sigma$  in a time interval  $d\tau$  can be calculated through

$$d\sigma = p_{\rm c} D_{\rm trap} J_{\rm c}(F_{\rm tox}) d\tau \tag{4}$$

where  $p_{\rm c}$  is the average capture cross section, and  $D_{\rm trap}$  is the available density of target states. The capture probability may depend on NC shape and  $D_{\rm trap} \approx N_{\rm NC}$  is the NC areal density.

## 2.2. Discharging of the NC-MOS Element

During retention, the device is in depletion and  $V_{\rm gate}=0$ . If NC bound states are responsible for storage of carriers, discharge occurs by tunnelling from the NC ground state to the substrate, either by direct or trap assisted tunnelling. For the case of direct tunnelling, the current density describing the discharge of the NCs is different than Eq. (2) mainly because available source states are not a bulk continuum but are the NC states. Assuming a delta-function distribution for the NC states  $D_{\rm NC}(E)=N_{\rm NC}\delta(E-E_{\rm NC})$  located at the quantization energy  $E_{\rm NC}$  and a single stored carrier for every NC, the discharge current density can be given as

$$J_{\rm d} = q N_{\rm NC} T_{\rm t}(E_{\rm NC}) v_{\rm NC} \tag{5}$$

where  $v_{\rm NC} \simeq \hbar \pi/2 m_{\rm ge} d^2$  is the semi-classical escape attempt rate for NCs of diameter  $d.^{10}$

The transmission probability  $T_{\rm t}(E,F_{\rm tox})$  for a single electron at energy E can be calculated through the WKB approximation as

$$T_{\rm t}(E) \approx 4 \exp \left[ -\left(1 - \left(1 - \frac{F_{\rm tox}t_{\rm tox}}{V_{\rm B}(E)}\right)^{3/2}\right) \frac{BV_{\rm B}(E)^{3/2}}{F_{\rm tox}} \right]$$

(6)

The tunnel oxide field is determined by the amount of stored carriers as well as by the band-bending. For a given stored charge, the oxide field therefore depends on the tunnel oxide thickness, total oxide thickness, substrate doping, gate work-function and dielectric constants. In order to obtain an intuitive result, we consider the case where stored charge is small and tunnel oxide field is proportional to the stored charge (or flat-band shift),  $F_{\text{tox}} \approx \Delta V_{\text{FB}}/2t_{\text{ox}}$ .

For the calculation of the discharge current through Eqs. (5) and (6), the barrier height must also be calculated. The barrier height is a function of the NC ground state energy given by  $V_{\rm B}(E) = V_{\rm B0} - E_{\rm NC}$ , where  $V_{\rm B0}$  is the bulk barrier height. The energy levels of uncapped germanium NCs have recently been measured directly as a function of size, using scanning tunnelling spectroscopy. An empirical formula for the conduction band minimum of Ge NCs as a function of size is given by

$$E_{\text{CBM}}(d) = E_{\text{CBM}}(\infty) + \frac{11.86}{d^2 + 1.51d + 3.3936} \tag{7}$$

where the energies are in eV, d is the nanocrystal diameter in nm. Equation (7) can be used to estimate  $E_{\rm NC}$ , which can be used in the estimation of the tunnelling barrier observed by the NCs during discharge.

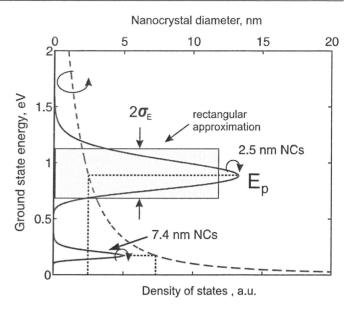

The size distribution of NCs leads to a distribution of energies. Considering a Gaussian size distribution, a density of states (DOS) can be calculated (Fig. 2). The DOS can also be approximated by a Gaussian. In this case, the stored charge is distributed to the available NC states according to Fermi-Dirac distribution with a local quasi-Fermi level. For a Gaussian density of states with peak energy  $E_{\rm p}$  and half width of  $\sigma_{\rm E}$ , the quasi-Fermi level of the nanocrystal ensemble is given in the zero temperature limit by

$$E_{\rm F} = E_{\rm P} + \sqrt{2}\sigma_{\rm E} \times Erf^{-1} \left(\frac{2n_{\rm c}}{N_{\rm NC}} - 1\right) \tag{8}$$

where  $Erf^{-1}$  denotes the inverse of the error-function,  $n_c$  is the total number of stored carriers and  $N_{\rm NC}$  is the total number of nanocrystals. The quasi-Fermi depends strongly on the ratio of total stored charge to number of NCs.

Escape of carriers near or above the quasi-Fermi level dominates the discharge current. Therefore, discharge current depends on the number of stored carriers which is proportional to the flat-band voltage shift through Eq. (1). This feature of the escape current is the reason of super-exponential charge decay in NC memory elements. A more intuitive, closed-form formula for the discharge current is

**Fig. 2.** Schematic description of density of states (solid curves) for the ground states of nanocrystals with two representative average diameters of 2.5 and 7.4 nm. Minimum of energy corresponds to the conduction band edge of bulk germanium. Dotted curve shows electron ground state of NCs as a function of size as described by Eq. (7). Areas under the curves are equal to the NC areal density.

desirable to compare the effect of design parameters on charge retention. However, a simple closed-form expression can not be obtained without further simplifying assumptions. A closed-form formula can be obtained by assuming a rectangular shaped density of states, neglecting band bending effects, assuming a gate work-function that is aligned with the substrate Fermi level and calculating in the zero temperature limit. Then Eq. (8) can be approximated by

$$E_{\rm F} = E_{\rm P} + \sqrt{2}\sigma_{\rm E} \left(\frac{2n_{\rm c}}{N_{\rm NC}} - 1\right) \tag{9}$$

Under these assumptions, Eqs. (5), (6), and (9) can be used to calculate a closed form for the discharge current at zero gate bias. The discharge current is then given as a function of the flat-band voltage shift  $\Delta V_{\rm FB}$  due to stored carriers as

$$J_{\rm d} \simeq \frac{4qN_{\rm NC}\pi\hbar\sqrt{V_{\rm p}}\exp\left[-\frac{3}{2}Bt_{\rm tox}\sqrt{V_{\rm p}}\right]}{3m_{\rm ge}d^2Bt_{\rm tox}\sigma_{\rm E}} \times \left(\exp\left(\frac{3Bt_{\rm tox}\sigma_{\rm E}}{2\sqrt{V_{\rm p}}}\frac{\Delta V_{\rm FB}}{\Delta V_{\rm max}}\right) - 1\right) \tag{10}$$

where  $V_{\rm p}=V_{\rm B}-E_{\rm p}/q$  is the barrier height observed by the average size NC,  $\sigma_{\rm E}$  is the width of the rectangular energy distribution,  $t_{\rm tox}$  is the tunnel oxide thickness,  $m_{\rm ge}$  is the electron mass in the nanocrystal,  $\Delta V_{\rm max} \simeq q N_{\rm NC} t_{\rm ox}/\in_{\rm ox}$  is the maximum flat-band voltage shift when all nanocrystals carry an electron, and  $B=4\sqrt{2m_{\rm ox}q}/3\hbar$ ,  $m_{\rm ox}$  being the electron tunnelling mass. Note that  $V_{\rm p}$  and  $\sigma_{\rm E}$  are normalized by q, to have units of Volts.

The approximate discharge current density given by Eq. (10) includes the effects of NC density, size distribution, flat-band voltage shift as well as tunnel oxide thickness and tunnel barrier height.

## 2.3. Temporal Decay of Stored Charge

The time decay of the NC charge can be calculated through integration of Eq. (10) which is of the form  $J_{\rm d}(\Delta V_{\rm FB}) = J_{\rm d0}(\exp(\beta\Delta V_{\rm FB})-1)$ . The retention time  $\tau_{\rm ret}$  is found as a function of initial and final flat-band voltage shifts as

$$\tau_{\text{ret}} = \frac{C_{\text{ox}}}{J_{\text{d0}}\beta} \ln \left( \frac{e^{\beta V_{\text{i}}} - 1}{e^{\beta V_{\text{f}}} - 1} \right) - C_{\text{ox}} \frac{V_{\text{i}} - V_{\text{f}}}{J_{\text{d0}}}$$

(11)

where  $V_{\rm i}$  is the initial flat-band shift before decay,  $V_{\rm f}$  is the final flat-band shift at time  $\tau_{\rm ret}$ ,  $\beta=3Bt_{\rm tox}\sigma_{\rm E}/2\sqrt{V_{\rm p}}\Delta V_{\rm max}$  is as given in Eq. (10). The factor  $J_{\rm d0}$  can be referred from Eq. (10) and  $C_{\rm ox}$  is the device capacitance per unit area.

# 2.4. Figure of Merit for a Nanocrystal Memory Cell

The figure of merit (FOM) definition chosen in this article is

$$FOM = \log_{10} \left( \frac{\tau_{ret}}{\tau_{charge}} \right) \simeq \log_{10} \left( \frac{J_{c}}{J_{d}} \right)$$

(12)

where  $au_{\mathrm{ret}}$  and  $au_{\mathrm{charge}}$  are the retention and charging times for a given set of device parameters. The FOM depends on many design parameters such as the write voltage  $V_{\rm write}$ , desired retention time  $au_{\rm ret}$ , desired flat-band voltage shift at the end of retention time  $V_{\rm f}$ , tunnel barrier properties such as width, dielectric constant and barrier height, control dielectric properties such as width and dielectric constant, substrate doping, gate work-function, nanocrystal size distribution and material composition. The effects of some of the parameters are interrelated through non-linear equations and only a numerical result for the FOM can be obtained without simplifying assumptions. Using numerical calculation, the FOM can be calculated for a given device geometry (control and tunnel barrier thicknesses) and nanocrystal size distribution. A greater FOM will mean a faster device writing time,  $\tau_{\text{charge}}$ . A FOM of about 18 is desirable which means a nanosecond write time for 10 year data storage.

## 3. EXPERIMENTAL DETAILS

## 3.1. Sample Preparation

The oxide-germanosilicate-oxide trilayer films were grown in a PECVD reactor (model PlasmaLab 8510C) on Si substrates using 180 sccm SiH<sub>4</sub> (2% in N<sub>2</sub>), 225 sccm NO<sub>2</sub> and varying flow rates of GeH<sub>4</sub> (2% in He) as precursor gases, at a sample temperature of 350 °C, a process

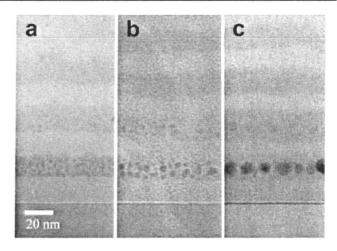

Fig. 3. Formation of Ge NCs as a function of anneal temperature and  $GeH_4$  flow rate as observed by TEM. Multi-layer structures of germanosilicate with flow rates of 120, 110, 100, and 90 sccm are seen away from the substrate (bottom to top) after annealing at (a) 650 °C, (b) 770 °C, and (c) 850 °C for 5 minutes.

pressure of 1000 mTorr under and an applied RF power of 10 W. The samples were then annealed in  $N_2$  atmosphere in an alumina oven at temperatures ranging from 650 °C to 950 °C for 5 minutes. The samples were loaded and unloaded with ramp times of 1 minute.

Transmission electron microscopy (TEM) images of a multilayered test sample show the formation of NCs as a function of annealing temperature as seen in Figure 3. The layers contain increasing amounts of Ge in layers away from the silicon substrate. High density NC formation is observed only in the bottom-most layer which has a composition of Si<sub>0.6</sub>Ge<sub>0.4</sub>O<sub>2</sub> as determined by XPS analysis. The NC diameter increases nonlinearly from 2.5 nm to 7.4 nm as the annealing temperature is increased from 650 °C to 850 °C as tabulated in Table I. For fabrication of the devices, first a thermal tunnel oxide of thickness 4 nm was grown using dry oxidation, followed by PECVD growth of germanosilicate layer of 10 nm thickness and composition of Si<sub>0.6</sub>Ge<sub>0.4</sub>O<sub>2</sub> were grown on *n*-type silicon substrates with resistivity of 1–10  $\Omega$  cm. This germanium rich layer is where NCs form upon annealing. On top, a  $t_{\rm con} = 17$  nm control oxide was deposited. Backside ohmic metallization was done by AuSb evaporation for the *n*-type substrates followed by rapid thermal annealing in forming gas. Gate metallization was done by shadow evaporation of aluminium.

#### 3.2. Flat-Band Voltage Measurement

Capacitance measurements were performed using a capacitance meter (HP 4278A) using 1 MHz AC excitation with 25 mV amplitude. The flat-band voltage shift can be tracked quasi-real-time for small changes in the flat-band shift by using a digital feedback loop that we developed. The feedback loop operates by measuring the capacitance and using successive approximation to find the value of the

| Table I. Avera    | ige nanocrystal size and v  | width of size of | distribution for differen | ent annealing tempe    | ratures as observed           | by TEM.             |

|-------------------|-----------------------------|------------------|---------------------------|------------------------|-------------------------------|---------------------|

| Equation (7) is u | ised to estimate peak groun | d state energy   | and width of density      | of states distribution | for the nanocrystal           | ensemble.           |

| Annealing         | Diameter (nm)               | $2\sigma$ (nm)   | $E_{\rm p}$ (eV)          | $2\sigma_{\rm E}$ (eV) | $N_{\rm nc}  ({\rm cm}^{-2})$ | $\Delta V_{ m max}$ |

| Annealing temperature (°C) | Diameter (nm)<br>average size | $2\sigma$ (nm) size width | $E_{\rm p}$ (eV) peak energy | $2\sigma_{\rm E}$ (eV) energy width | $N_{\rm nc}$ (cm <sup>-2</sup> ) areal density | $\Delta V_{ m max}$ volts |

|----------------------------|-------------------------------|---------------------------|------------------------------|-------------------------------------|------------------------------------------------|---------------------------|

| 650                        | 2.5                           | 0.6                       | 0.88                         | 0.55                                | $8 \times 10^{12}$                             | 16.9                      |

| 770                        | 3.2                           | 1.0                       | 0.64                         | 0.53                                | $3.2 \times 10^{12}$                           | 6.3                       |

| 850                        | 7.4                           | 1.6                       | 0.17                         | 0.17                                | $8 \times 10^{11}$                             | 1.7                       |

gate bias required to observe a given set-point capacitance value and eliminates the need of tracing the whole CV curve and post-processing of the data to access the value of the flat-band voltage shift. During write/erase pulses, the loop can be momentarily turned off, and after the pulse it can be restarted at the same bias voltage. This method allows rapid monitoring of the changes in the flat-band voltage shift (within few tens of msec) after a write or erase pulse. The flat-band voltage difference can be measured rapidly and can be used to extract the discharge or charge currents.

# 3.3. Charging of Nanocrystals

Dynamic CV measurements have been performed on NC-MOS capacitors, by measuring the CV as a function of time near the flat-band voltage between applied pulses of varying pulse voltage and a fixed pulse duration 50 msec.

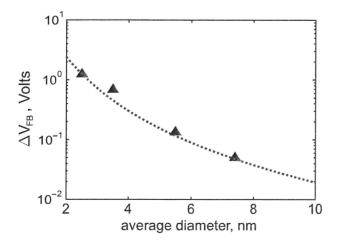

As can be seen in Figure 4, the total accumulated charge measured through flat-band voltage shift follows the nanocrystal density, which is proportional to  $1/d_{\rm nc}^3$ .

The charging currents are extracted from flat-band voltage shift measurements, by applying a 12 V write pulse to previously uncharged three devices with properties shown in Table I. The experimental values of  $J_c$  are 8.68 nA, 4.76 nA, and 0.73 nA per cm<sup>2</sup> for devices with NC densities of  $8 \times 10^{12}$ ,  $3.2 \times 10^{12}$ , and  $8 \times 10^{11}$  cm<sup>-2</sup>

**Fig. 4.** Flat-band voltage shift as a function of nanocrystal diameter (filled triangles) and for the as deposited sample (horizontal dotted line) after a 7 V write pulse of duration 500 msec. The dotted curve is drawn to aid the eye.

respectively. The current density calculated using Eq. (2) is  $21 \text{ nA cm}^{-2}$  using oxide properties found in literature. 9.12 Remarkable proportionality of charge current density to NC density shows that capture cross section  $p_c$  is rather independent of NC size for our NCs and has a value of about  $5 \times 10^{-14} \text{ cm}^2$ .

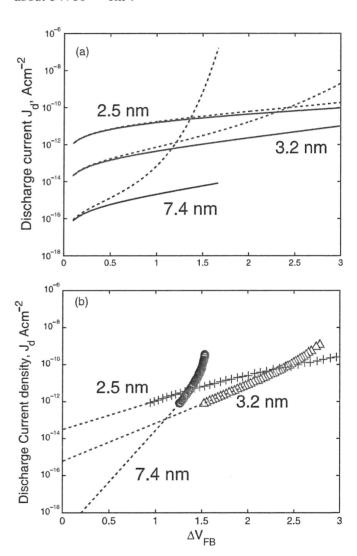

Fig. 5. (a) Discharge currents as a function of flat-band voltage shift calculated for NC-MOS devices under zero gate bias. A tunnel oxide thickness of 4 nm and total oxide thickness of 31 nm is assumed. Bulk barrier height of oxide-silicon interface is taken as 3.3 eV. Nanocrystal parameters are based on experimental values given in Table I. Solid curves are the currents for the rectangular DOS approximation given in Eq. (10) and dashed curves are numerical results assuming Gaussian DOS. (b) Experimental discharge current densities at zero gate bias plotted as a function of flat-band voltage shift for 2.5, 3.2, and 7.4 nm nanocrystals. Dashed lines are linear interpolations drawn to aid the eye.

## 3.4. Discharging of Nanocrystals

The discharge currents have been measured through decay of stored charge for the three devices as shown in Figure 5(b).

The discharge current densities are plotted in Figure 5(a). It is seen that Eq. (10) agrees reasonably well with a more accurate numerical calculation for small ratios of  $\Delta V_{\rm FB}/\Delta V_{\rm max}$  < 0.2. If charging ratio is large, i.e., when  $\Delta V_{\rm FB}/\Delta V_{\rm max}

ightarrow 1$ , the rectangular DOS approximation breaks down. Still, Eq. (10) can be used to estimate effect of design parameters on the retention performance by careful consideration of the value of  $\Delta V_{\rm FB}/\Delta V_{\rm max}$  for the desired memory window. For example, noting the dependence of  $E_p$  given in Eq. (7), it can be seen from Eq. (10) that an increasing NC diameter increases the average barrier height and reduces the discharge current. It can also be seen that, increasing NC density but keeping other parameters constant increases  $\Delta V_{\text{max}}$ , which in turn gives a lower quasi-fermi level for carriers in NCs for the same memory window, and reduces the escape

The smaller NCs can hold more charge due to increased NC density but they also decay faster. Comparison of Figures 5(a, b) shows that the numerical solution predicts the discharge currents rather accurately. For example, it is seen that, as the flat-band voltage nears 1.7 volts ( $\Delta V_{\rm max}$  for the 7.4 nm device), there is a sharp increase in the experimental discharge current. This is in accordance with the numerical solution. Also, size dependence of the discharge currents are similar for theory and experiment. Therefore, we conclude that the model describes the behavior of the NC-MOS device and at smaller charging ratios of  $\Delta V_{\rm FB}/\Delta V_{\rm max}\ll 1$ , Eq. (10) can be used to qualitatively compare devices with different NC properties.

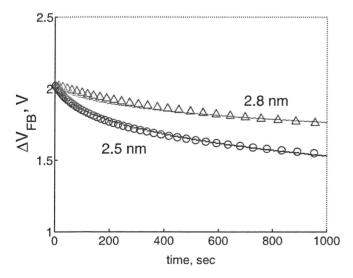

**Fig. 6.** Experimental flat-band shift as a function of time for two capacitors with different average nanocrystal diameters. Smaller NCs with an average diameter of 2.5 nm (triangles) decay faster than those with an average diameter of 2.8 nm (circles). Data is fitted using Eq. (11).

The decay of the charge stored in the NCs has also been recorded for the NC-MOS capacitors with different NC diameters as a function of time. The decay of the flat-band voltage shift is fitted using Eq. (11) as seen in Figure 6. A rapid initial decay followed by a slower decay is in accordance with the predictions of Eqs. (10) and (11). The data can be fitted accurately for short and long time periods by using two adjustable parameters  $J_{d0}$  and  $\beta$ .

## 4. DISCUSSION

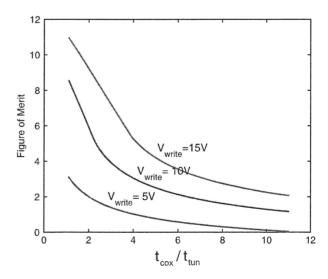

The model agrees well with experiment and can be used to estimate effect of various design parameters on device performance. Based on the theoretical model described in the theoretical section, the FOM has been calculated for various device parameters. The dependence of the FOM on the control dielectric thickness to tunnel dielectric thickness is given in Figure 7.

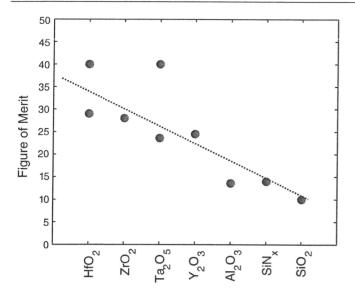

It can be seen that, a decreasing control oxide thickness improves FOM. This can be understood through two mechanism, one being the increase of the charging current at a given write voltage, and the other being reduction of the tunnel dielectric field during retention due to better screening of the NC charge by the gate contact. It is desirable to choose a thin control dielectric with high dielectric constant to enhance these effects and achieve a higher FOM. The FOM has also been calculated for different dielectric materials (material properties from<sup>13</sup>) with same effective oxide thickness, keeping other device parameters the same, as shown in Figure 8.

It is seen that, higher dielectric constant materials enhance device performance. This effect can be understood by the fact that, the actual dielectric thickness is greater for higher dielectric constant, reducing the escape tunnelling

Fig. 7. Figure of Merit (FOM) for a device with 6 nm diameter Ge nanocrystals and 3 nm thick  $\mathrm{SiO}_2$  tunnel dielectric, plotted for  $V_{\mathrm{write}} = 5$ , 10, and 15 Volts as a function of control oxide thickness ( $t_{\mathrm{cox}}$ ) to tunnel oxide thickness ( $t_{\mathrm{tun}}$ ). Memory window is 0.5 Volts. Decreasing control oxide thickness enhances the FOM by enhancement of write current.

**Fig. 8.** Figure of merit for different control and tunnel dielectric materials for nanocrystal diameter of 6 nm, write voltage of 10 V, and effective oxide thickness of 4 nm. Dotted line is drawn to guide the eye.

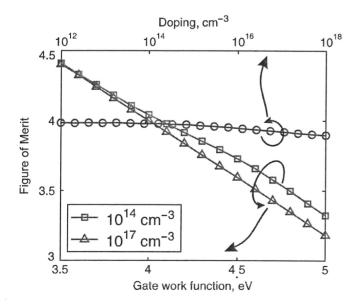

rate. It must be noted that, there is a minimum nanocrystal size for a high-K dielectric, as smaller nanocrystals have a higher quantization energy. Smaller nanocrystals observe smaller barriers and high-K dielectrics generally have smaller conduction band barriers on silicon. The figure of merit is also plotted as a function of substrate doping and gate work-function as seen in Figure 9. It is seen that there is a weak dependence on doping density and work-function of the gate. Numerical calculations were used to calculate the band bending for a given set of parameters.

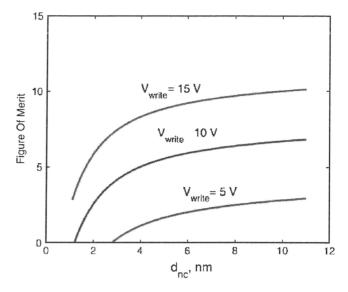

The figure of merit depends strongly on the nanocrystal properties. Smaller nanocrystals can be made with higher areal density but decay faster due to tighter quantum

**Fig. 9.** Figure of merit as a function of gate work-function and substrate doping density for 3 nm diameter nanocrystals, 4 nm tunnel oxide and 20 nm control oxide. Write voltage is 10 V.

Fig. 10. Figure of merit as a function of nanocrystal diameter, suming a nanocrystal density of  $N_{\rm nc} = 10^{12} {\rm cm}^{-2}$ .

confinement. The effect of average nanocrystal diameter is plotted in Figure 10, and it is seen that devices with larger and high density nanocrystals perform better.

## 5. CONCLUSIONS

In this article, we have proposed a charge storage and retention model for NC-MOS memory devices and compared it with experimental results. The model envisions storage of carriers in quantized energy levels of NCs. The escape of carriers is modelled by direct tunnelling out of the NCs to the substrate. The tunnelling rate depends on the field in the tunnel oxide, which is a function of total number of stored carriers as well as the surface potential of the substrate at a given gate bias. The model can be used to predict the effect of various design parameters such as nanocrystal size and composition, total flat-band voltage shift on write speed and retention time. The model predicts the super-exponential time decay commonly observed in NC-MOS elements. For NC-MOS capacitors containing Ge NCs fabricated by the PECVD technique, NC size related quantum confinement is found to play a role in the storage of charges. The model agrees well with the experimental results, and gives useful insight to NC-MOS memory device design. Theory suggests that high-K dielectric devices with large and dense nanocrystals perform better in terms of retention time and write speed.

**Acknowledgments:** This work has been partially supported by the European Commission through the FP6 project called SEMINANO under the contract NMP4-CT-2004-505285 and by TUBITAK under contract No 103T115. Thanks are due to Magnus Willander of Goteburg University for supplying the oxidized silicon wafers.

# References and Notes

- S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, Appl. Phys. Lett. 68, 1377 (1996).

- **2.** X. X. Wang, J. G. Zhang, L. Ding, B. W. Cheng, W. K. Ge, J. Z. Yu, and Q. M. Wang, *Phys. Rev. B* 72, 195313 (2005).

- 3. S. Okamoto and Y. Kanemitsu, Phys. Rev. B 54, 16421 (1996).

- 4. C. Miesner, T. Asperger, K. Brunner, and G. Abstreiter, *Appl. Phys. Lett.* 77, 2704 (2000).

- J. Xu, Z. H. He, K. Chen, X. Huang, and D. Feng, J. Phys. Cond. Mat. 11, 1631 (1999).

- W. K. Choi, V. Ng, S. P. Ng, H. H. Thio, Z. X. Shen, and W. S. Li, J. Appl. Phys. 86, 1398 (1999).

- T. Z. Lu, M. Alexe, R. Scholz, V. Talelaev, and M. Zacharias, <u>Appl.</u> Phys. Lett. 87, 202110 (2005).

- 8. A. Gehring and S. Selberherr, *IEEE Trans. Dev. Mat. Rel.* 4, 3, 306 (2004).

- 9. M. Lenzlinger and E. H. Snow, J. Appl. Phys. 40, 278 (1969).

- A. Nauen, I. Hapke-Wurst, F. Hohls, U. Zeitler, R. J. Haug, and K. Pierz, *Phys. Rev. B* 66, 161303(R) (2002).

- 11. Y. Nakamura, K. Watanabe, Y. Fukuzawa, and M. Ichikawa, *Appl. Phys. Lett.* 87, 133119 (2005).

- M. Depas, B. Vermeire, P. W. Mertens, and R. L. Van Meirhaeghe, Sol. Stat. Elect. 38, 1465 (1995).

- **13.** G. D. Wilk, R. M. Wallace, and J. M. Anthony, *J. Appl. Phys.* 89, 5243 (2001).

Received: 11 August 2006. Revised/Accepted: 11 February 2007.