## Memristive behavior in a junctionless flash memory cell

Ikram Orak, Mustafa Ürel, Gokhan Bakan, and Aykutlu Dana

Citation: Appl. Phys. Lett. **106**, 233506 (2015); View online: https://doi.org/10.1063/1.4922624 View Table of Contents: http://aip.scitation.org/toc/apl/106/23 Published by the American Institute of Physics

## Articles you may be interested in

Memristive operation mode of floating gate transistors: A two-terminal MemFlash-cell Applied Physics Letters **101**, 263504 (2012); 10.1063/1.4773300

Junctionless multigate field-effect transistor Applied Physics Letters **94**, 053511 (2009); 10.1063/1.3079411

Mimic synaptic behavior with a single floating gate transistor: A MemFlash synapse Journal of Applied Physics **114**, 194506 (2013); 10.1063/1.4832334

Temperature-dependent characteristics of junctionless bulk transistor Applied Physics Letters **103**, 133503 (2013); 10.1063/1.4821747

Associative learning with Y-shaped floating gate transistors operated in memristive modes Applied Physics Letters **110**, 053503 (2017); 10.1063/1.4975370

A two-dimensional analytical model for short channel junctionless double-gate MOSFETs AIP Advances **5**, 057122 (2015); 10.1063/1.4921086

**8600 Series VSM** For fast, highly sensitive

measurement performance

LEARN MORE 🕑

## Memristive behavior in a junctionless flash memory cell

Ikram Orak,<sup>1,2</sup> Mustafa Ürel,<sup>3</sup> Gokhan Bakan,<sup>4</sup> and Aykutlu Dana<sup>3,a)</sup> <sup>1</sup>Vocational School of Health Services, Bingöl University, 12000 Bingöl, Turkey <sup>2</sup>Department of Physics, Faculty of Science and Art, Bingöl University, 12000 Bingöl, Turkey <sup>3</sup>UNAM Institute of Materials Science and Nanotechnology, Bilkent University, 06800 Ankara, Turkey <sup>4</sup>Faculty of Engineering, Antalya International University, 07190 Antalya, Turkey

(Received 27 April 2015; accepted 3 June 2015; published online 12 June 2015)

We report charge storage based memristive operation of a junctionless thin film flash memory cell when it is operated as a two terminal device by grounding the gate. Unlike memristors based on nanoionics, the presented device mode, which we refer to as the flashristor mode, potentially allows greater control over the memristive properties, allowing rational design. The mode is demonstrated using a depletion type n-channel ZnO transistor grown by atomic layer deposition (ALD), with HfO<sub>2</sub> as the tunnel dielectric, Al<sub>2</sub>O<sub>3</sub> as the control dielectric, and non-stoichiometric silicon nitride as the charge storage layer. The device exhibits the pinched hysteresis of a memristor and in the unoptimized device,  $R_{off}/R_{on}$  ratios of about 3 are presented with low operating voltages below 5 V. A simplified model predicts  $R_{off}/R_{on}$  ratios can be improved significantly by adjusting the native threshold voltage of the devices. The repeatability of the resistive switching is excellent and devices exhibit 10<sup>6</sup> s retention time, which can, in principle, be improved by engineering the gate stack and storage layer properties. The flashristor mode can find use in analog information processing applications, such as neuromorphic computing, where well-behaving and highly repeatable memristive properties are desirable. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4922624]

Memory and logic operations form the basis of modern information processing systems, where increasingly high density and lower power operation enable higher performance computing and a wide variety of contemporary mobile platforms. Among the non-volatile data storage technologies, floating gate charge storage memory is becoming the dominant technology. Originally, conceived in 1967 by Kahng and Sze,<sup>1</sup> the floating gate memory has evolved over the decades to higher performance and density, and is now a ubiquitous element of computing platforms. Another type of memory and logic element, the memristor was conceptually described, few years later in 1971, by Chua.<sup>2</sup> The memristor is a very general concept which can be implemented with a large variety of physical mechanisms and potentially offers high density, low power, and nonvolatile operation, placing such devices among the candidates of advanced components of future computing systems. Reports of resistive switching in macroscopic and microscopic systems are older than their theoretical description; however, the concept of nanoscale memristive devices for use in memory and logic operations has attracted significant attention in the last decade.<sup>3–12</sup> Previously, we have observed resistive switching based on electrochemistry in graphene and even in organic systems.<sup>13,14</sup> Non-traditional and conventional computing architectures can be potentially implemented using memristive devices.<sup>15–17</sup> One particularly important field is neuromorphic computing, where the nonvolatile operation of solid-state memristors is expected to find application as synaptic elements.<sup>18-21</sup> In order to realize high-density, high-performance neuromorphic computing schemes based on memristive devices, it would be highly desirable to integrate such devices with well-established silicon technology. Although some of the systems that exhibit memristive behavior are potentially not compatible with silicon complementary metal oxide semiconductor (CMOS) technology, some readily are, and resistive switching has been observed even in silicon based materials.<sup>22–26</sup>

According to Waser and Aono, among the various mechanisms that result in resistive switching, memristive operation based on charge storage can be cited as a separate category.<sup>4</sup> Charging based memristor operation has been observed more than 40 years ago by Simmons and Verderber,<sup>27</sup> and the mechanism is loosely explained by the presence of carriers that are injected by Fowler-Nordheim tunneling at high electric fields and subsequently trapped at sites such as defects or metal nanoparticles in the insulator. The modification of the electrostatic barrier of the Metal-insulator-metal (MIM) structure results in changes of its resistance, similar to the changes in channel resistance in a Flash field-effect transistor (FET) upon charging of the floating gate. Resistive switching in metal nanoparticle doped organic conductor films has been recently studied for their memristive properties and applications, and can be considered in this category.<sup>28–30</sup>

In this article, we demonstrate that a thin film junctionless field effect transistor with a floating charge trap layer also exhibits memristive behavior, when operated as a twoterminal device. The significance of this demonstration is that the presented mechanism is well understood, highly repeatable and scalable, CMOS compatible, and allows rational design, while exhibiting nearly ideal memristor characteristics. The demonstration connects the two families of devices at the forefront of contemporary and future computing, namely, the flash memory and the memristor.

<sup>&</sup>lt;sup>a)</sup>E-mail: aykutlu@unam.bilkent.edu.tr

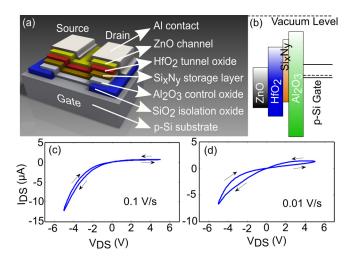

The schematic description of the device is shown in Figure 1(a). A 15 nm thick atomic layer deposited (ALD) ZnO layer is used as the channel between the source and drain contacts made of aluminum. The channel is separated from a 5 nm thick charge storage layer (non-stoichiometric silicon nitride layer) by a 15 nm thick ALD HfO<sub>2</sub> tunnel barrier, followed by a 15 nm thick ALD Al<sub>2</sub>O<sub>3</sub> control oxide on p-type silicon acting as the gate. The band alignments are shown in Figure 1(b). Various gate widths and lengths were used, ranging from 5 to 30  $\mu$ m. The presented stack is typical for thin film flash memories, however, when the device is operated as a two terminal device by connecting the source and gate electrodes together and using drain as the other electrode, it exhibits the frequency dependent pinched hysteresis, typical of a memristor, as shown in Figures 1(c) and 1(d).<sup>3</sup>

In order to understand and relate the memristor operation to device parameters, we resort to a simplified model of the device. In general, a memristor can be described by the constitutive equations as

$$i = g(Q, v)v, \tag{1}$$

$$\frac{dQ}{dt} = h(Q, v), \tag{2}$$

where g(Q, v) is the memductance and the evolution of the state variable Q is now written in terms of the applied voltage, with the dynamic relation defined by a function h(Q, v). In order to determine g(Q, v) and h(Q, v), the current-voltage relation of the junctionless n-channel depletion type device is required. The relation can be given by an extension of the square-law piecewise description of a field effect transistor

$$I_{DS} = \begin{cases} \mu_{eff} C_{ox} \frac{w}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{1}{2} V_{DS}^2 \right] (1 + \lambda V_{DS}), & \text{if } V_{GS} - V_{TH} > V_{DS} > 0 \\ \frac{1}{2} \mu_{eff} C_{ox} \frac{w}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS}), & \text{if } V_{DS} > V_{GS} - V_{TH} > 0 \\ 0, & \text{if } V_{DS} > 0 > V_{GS} - V_{TH} \\ -\mu_{eff} C_{ox} \frac{w}{L} \left[ (V_{GS} + |V_{DS}| - V_{TH}) |V_{DS}| - \frac{1}{2} V_{DS}^2 \right] (1 + \lambda |V_{DS}|), & \text{if } V_{GS} - V_{TH} > 0 > V_{DS} \\ - \frac{1}{2} \mu_{eff} C_{ox} \frac{w}{L} (V_{GS} + |V_{DS}| - V_{TH})^2 (1 + \lambda |V_{DS}|), & \text{if } 0 > V_{GS} - V_{TH} > V_{DS} \\ 0, & \text{if } 0 > V_{DS} > V_{GS} - V_{TH}, \end{cases}$$

$$(3)$$

FIG. 1. (a) Schematic description of the ultrathin-film junctionless ZnO transistor. The ZnO channel area is  $70 \times 60 \,\mu m^2$ . (b) Nominal band alignment of the layers under flatband condition. The bandgaps and affinities of the layers are  $E_g = 1.12 \,\text{eV}$  and  $E_{EA} = 4.05 \,\text{eV}$  for silicon,  $E_g = 8.7 \,\text{eV}$  and  $E_{EA} = 1.35 \,\text{eV}$  for Al<sub>2</sub>O<sub>3</sub>,  $E_g = 5.3 \,\text{eV}$  and  $E_{EA} = 2.05 \,\text{eV}$  for Si<sub>3</sub>N<sub>4</sub>,  $E_g = 5.7 \,\text{eV}$  and  $E_{EA} = 2.65 \,\text{eV}$  for HfO<sub>2</sub>, and  $E_g = 3.3 \,\text{eV}$  and  $E_{EA} = 4.35 \,\text{eV}$  for ZnO. Silicon rich (refractive index n = 1.98) Si<sub>x</sub>N<sub>y</sub> provides trap states for charge storage. (c) When the source-drain voltage V<sub>DS</sub> is swept, a pinched hysteresis is observed in the channel current I<sub>DS</sub>. A rapid scan exhibits smaller hysteresis (d), whereas a slower scan exhibits larger hysteresis. The pinched hysteresis is attributed to channel conductivity modulation upon charging and discharging of the silicon nitride layer.

where  $V_{GS}$  is the gate-source voltage,  $V_{DS}$  is the sourcedrain voltage,  $V_{TH}$  is the threshold voltage,  $\mu_{eff}$  is the effective channel mobility,  $C_{ox}$  is the areal capacitance of the gate stack, w and L are the width and length of the channel, and  $\lambda$ is the Early parameter. The extension of the  $I_{DS}$ - $V_{DS}$  relation to cover the negative V<sub>DS</sub> bias regime is achieved by noticing that, due to symmetry of the junctionless transistor in this regime, the negative drain voltage can be taken as the ground reference and source and gate voltages can be re-referenced with respect to the drain voltage. The model can be used to fit experimental data, as shown in Figure 2(a). In this simplified model, V<sub>TH</sub> is assumed to be constant through the length of the channel. This corresponds to the floating gate being at a single voltage level, which is a first order approximation only, due to the fact that the Si<sub>x</sub>N<sub>y</sub> storage layer allows spatially varying charge density to be stored. In order to derive full memristive dynamics, it is needed to establish the relation between stored charge and threshold voltage, which is given by the following equation:

$$V_{TH} = V_{TH0} - \frac{Q}{C_{con}}.$$

(4)

Here,  $V_{TH0}$  is the native threshold voltage of the device having no stored charge. The charging model can be approximated by a lumped model, where Fowler-Nordheim tunneling between the channel and the storage layer is the only current

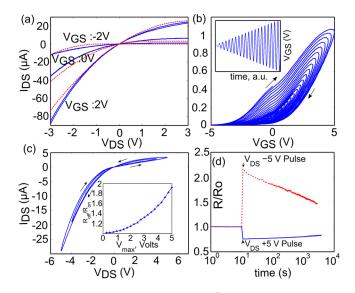

FIG. 2. The ZnO channel area is  $70 \times 60 \,\mu m^2$ . (a) Cyclic I<sub>DS</sub> versus V<sub>DS</sub> curves acquired at a scan speed of 1 V/s for the transistor at gate voltages of V<sub>GS</sub> = -2, 0, and 2 V, superimposed with the predictions of the model given in Eq. (5). (b) When the transistor is operated as a flash memory by applying a time varying voltage to V<sub>GS</sub>, hysteresis is observed in the I<sub>DS</sub> (at V<sub>DS</sub> = 0.1 V). The inset shows the applied voltage waveform. (c) When the same waveform is applied to V<sub>DS</sub>, keeping V<sub>GS</sub> = 0 V, a pinched hysteresis is observed. The resistance ratio R<sub>off</sub>/R<sub>on</sub>, measured at V<sub>DS</sub> = 0.1 V, is shown in the inset as a function of peak voltage amplitude. (d) Retention characteristics of the R<sub>off</sub>/R<sub>on</sub> ratio.

leading to charging. Fowler-Nordheim current depends on the field through the tunnel barrier,  $F_{tun}$ , which is described by the following equation:

$$F_{tun} = \frac{Q}{(C_{con} + C_{tun})t_{tun}} + \frac{C_{con}}{(C_{con} + C_{tun})t_{tun}} \left(V_{GS} - \frac{1}{2}\xi V_{DS}\right).$$

(5)

Here,  $C_{con}$  is the control oxide capacitance,  $C_{tun}$  is the tunnel oxide capacitance,  $t_{tun}$  is the tunnel oxide thickness, and  $\xi \sim 1$  is a geometric correction factor, which accounts for the spatially varying field distribution along the channel length. The stored charge dynamics is then approximately given by<sup>32,33</sup>

$$\frac{dQ}{dt} = -sgn[F_{tun}]\frac{\eta_c q^2 m F_{tun}^2}{16\pi^2 m_{tun} \hbar V_B} \exp\left(-\frac{2V_B^{3/2}\sqrt{8m_{tun}q}}{3\hbar |F_{tun}|}\right), \quad (6)$$

where q is the electronic charge, m and  $m_{tun}$  are the electron masses for the channel and the tunnel barrier, respectively,  $V_B$  is the barrier height, and  $\eta_c$  is the capture efficiency of tunneling electrons by the nitride storage layer. The model can be used to qualitatively explain the charging behavior as exhibited in the hysteresis, as shown in Figure 2(b), when the device is operated as a conventional flash memory: As can be seen from Eqs. (4)–(6), a positive voltage pulse applied at the gate (while the source is grounded) results in a negative charge buildup at the storage layer and a subsequent positive threshold voltage shift. The opposite signs of  $V_{DS}$  and  $V_{GS}$  in Eq. (5), predicts that when a positive pulse is applied at  $V_{DS}$ , while grounding the gate, positive charge will buildup in the storage layer and a negative threshold voltage shift is expected. The negative threshold voltage shift results in increased current at positive voltages (and hence, reduced small signal resistance near zero bias). This is indeed the case, as shown in Figures 2(c) and 2(d). The retention characteristics are shown in Figure 2(d), where the resistance is measured at 100 mV bias following 20 s duration voltage pulses at designated voltages of +/-5 V. The device exhibits extrapolated retention duration of about 10<sup>6</sup> s.

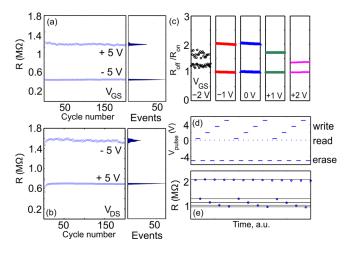

The change in the sign of threshold voltage shift is further emphasized in Figures 3(a) and 3(b), where +5V and -5 V voltage pulses of 10s duration is applied to the gate (flash mode operation) and to the drain (flashristor mode operation) and small signal resistance at  $V_{DS} = 0.1 V$  is measured and plotted. The measurements also show that the written and erased states are highly repeatable, showing better than 5% variation (note the linear scale of the graphs). The flashristor mode can also be used by assigning a common gate to multiple devices. In order to investigate the variation of the Roff/Ron ratio on gate voltage, we measure it by setting a fixed gate voltage (Figure 3(c)). It is observed that the greatest  $R_{off}/R_{on}$  ratio is achieved for  $V_{GS} = 0$ . This is attributed to the reduction of tunnel field during write or erase operation due to the asymmetry generated by a nonzero  $V_{GS}$ . The repeatability of the  $R_{off}/R_{on}$  ratio prompts use of multilevel pulses to write different charges onto the device. A four level pulsing scheme is shown in Figures 3(d)and 3(e), demonstrating feasibility of multilevel operation.

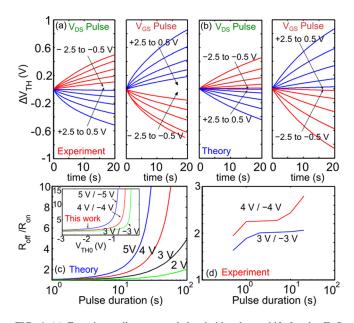

The model presented in the above equations can be used to estimate the dynamic behavior of the device, as shown in Figures 4(a) and 4(b). During positive and negative voltage pulses applied to the drain or to the gate, the source-drain current is recorded. Using a calibration data set, which was acquired rapidly in order to avoid charging of the storage layer, the threshold voltage shifts are extracted, as shown in Figure 4(a). It is observed that, when the pulse is applied to  $V_{GS}$ , a greater threshold voltage shift can be induced as compared to the same voltage applied to  $V_{DS}$  (keeping  $V_{GS} = 0$ ).

FIG. 3. (a) The repeatability and polarity of  $R_{off}$  and  $R_{on}$ , measured at  $V_{DS} = 0.1 V$  when 10 s duration voltage pulses are applied to  $V_{GS}$  (flash mode). (b) Same as (a), with voltage pulses are applied to  $V_{DS}$  and  $V_{GS} = 0 V$  (flashristor mode). (c) The  $R_{off}/R_{on}$ , measured at  $V_{DS} = 0.1 V$ , after writing with gate voltages  $V_{GS} = 2$ , 1, 0, 1, and 2V. Greatest contrast is achieved for  $V_{GS} = 0 V$ . (d) and (e) Multilevel operation is demonstrated by applying the shown waveform to  $V_{DS}$ , keeping  $V_{GS} = 0 V$  (The ZnO channel area is  $70 \times 60 \ \mu m^2$ ).

FIG. 4. (a) Experimentally measured threshold voltage shift for the ZnO channel ( $70 \times 60 \,\mu\text{m}^2$ ) device operated in the flashristor mode ( $V_{DS}$  pulsed with -0.5 to -2.5 V, 0.5 to 2.5 V, and  $V_{GS} = 0$  V) and flash mode ( $V_{DS} = 0.1$  V and  $V_{GS}$  pulsed with -0.5 to -2.5 V and 0.5 to 2.5 V). The threshold voltages are extracted by measuring  $I_{DS}$  as a function of time and fitting to a data set describing transistor operation under various bias conditions. (c) Based on the charging model (Eqs. (4)–(6)), the charging behavior is simulated by using  $\eta_c$ ,  $V_B$ , and  $m_{tun}$  as fitting parameters. The geometric correction parameter in Eq. (5) is found to be  $\xi = 1.4$ . (d) Dependence of the R<sub>off</sub>/R<sub>on</sub> ratio on the native threshold voltage  $V_{TH0}$  for write/erase voltages of +5/-5, +4/-4, and +3/-3 V. The simplified model predicts that, if enough charge can be stored in the floating gate region, the R<sub>off</sub>/R<sub>on</sub> ratio can be made arbitrarily high. (e) According to the model, increasing write/erase durations also improve the R<sub>off</sub>/R<sub>on</sub> ratio. (f) Experimental results show an increase in the R<sub>off</sub>/R<sub>on</sub> ratio as a function of pulse duration.

This is well explained by the theoretical model, as shown in Figure 4(b). Here,  $\eta_c$ ,  $V_B$ , and  $m_{tun}$  are used as fitting parameters. One important point that should be noted is, through fitting, the capture efficiency  $\eta_c$  is found to be a very small value  $(10^{-13})$ . Assuming the model properly describes the operation of the device, this small capture efficiency can be attributed to the small number of trap density in the silicon nitride layer and to the fact that HfO<sub>2</sub> barrier only limits half of the energy range below the silicon nitride conduction band, not prohibiting all of the deposited carriers from rapidly escaping back into the channel. Based on the fitted values, which quantitatively explains the observed threshold voltage shifts, the model is used to investigate the dependence of  $R_{off}/R_{on}$  ratio on device parameters. Assuming an infinite off-on ratio for the transistor, it is observed that the

threshold voltage of the uncharged device, V<sub>TH0</sub>, has a strong effect on the achievable  $R_{off}/R_{on}$  ratio for a given voltage range (Figure 4(c)). Theory predicts that as the charged threshold value becomes positive, the transistor is turned off and the off resistance becomes large. In this case, the  $R_{off}$ Ron ratio can also be made arbitrarily large. In our devices, the uncharged threshold voltage is measured to be around -2 V, and according to Figure 4(a) typical threshold voltage shifts are on the order of 0.5 V (for 2.5 V write voltage) to 1 V (for 5 V write voltage). Therefore, in our measurements, we do not achieve a completely turned off device, hence, the  $R_{off}/R_{on}$  ratio remains low. In order to increase the threshold voltage shift, one can wait for a longer period with the voltage pulse turned on (Figure 4(c)). In our devices this is partly confirmed, a prolonged write/erase pulse duration is indeed observed to improve the  $R_{off}/R_{on}$  ratio (Figure 4(d)).

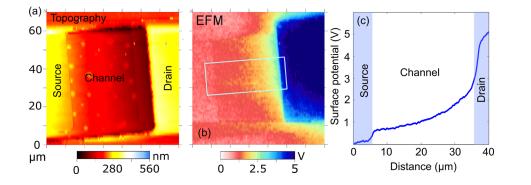

In order to better understand the device operation and obtain a clue to why the carrier capture probability is found to be unexpectedly small in the fitting process (Figure 4(b)), we use electrostatic force microscopy (EFM) (Figures 5(a) and 5(b)). A multi-frequency version of electrostatic force microscopy is used to simultaneously measure topography and surface potential.<sup>34</sup> A metal coated cantilever with a resonance frequency of 71 kHz and nominal spring constant of 2.7 N/m was used in tapping mode, while a sinusoidal voltage (0.5 V amplitude) was applied to the cantilever at a frequency of 11 kHz to avoid harmonics of electrostatic forces from interfering with the topography measurement. The electrostatic forces at 11 kHz were measured using a Stanford Research Systems Lock-in amplifier, SR830. Contact potential difference along the device is measured prior to biased measurements by grounding V<sub>DS</sub> and V<sub>GS</sub>, and used as a baseline. Multiple electrostatic force maps acquired at different bias conditions were used to calibrate the system. It is seen that, for  $V_{DS} = 5 V$  and  $V_{GS} = 0 V$ , there are significant voltage drops at the source-channel and channel-drain contacts as shown in the voltage profile across the channel in Figure 5(c). As a result of the voltage drops, a significantly smaller voltage develops across the channel during operation of the device, reducing the tunnel oxide field. The tunnel rate (Eq. (6)) exponentially depends on the tunnel field, and therefore, the capture probability  $\eta_c$  is estimated to be very small, due to an incorrect assumption about the tunnel field.

The performance of the device is low, considering that the write/erase times are on the order of 1 s, and retention is on the order of  $10^6$  s. Improvements of the device can, in principle, be made by optimizing the storage layer and gate

FIG. 5. (a) Topography and (b) EFM data on the channel region shows that (c) there are significant voltage drops between the source-channel  $(50 \times 45 \ \mu m^2)$  and channel-drain  $(50 \times 45 \ \mu m^2)$  contacts. This non-ideal behavior is due to the large contact resistance in the unannealed contacts, and inhibits development of larger fields between the channel and the floating gate during write/erase cycles.

stack properties. Previously we have predicted that, in a flash memory, a large retention time accompanied with fast write/ erase times are possible by using high- $\kappa$  dielectrics in the gate stack and nanocrystals in the storage layer.<sup>35</sup> The sizes of the devices are also large for high density neuromorphic computing, however, there is no significant variation of threshold voltages and charging characteristics by changing the dimensions within the micrometer range. We therefore estimate that the devices can, in principle, be scaled into the nanoscale regime, unless short channel effects become significant. There are a large number of variations on flash memory devices and programming modes.<sup>36</sup> Among the mechanisms used for writing into storage layers, Hot Electron Injection (HEI) is widely used to speed up write times. In the presented devices, the HEI are insignificant as the size of the device is much greater than the thermalization length of carriers. HEI can become more important as the devices are scaled down to the nanometer range. In conclusion, the flashristor mode may allow high density neuromorphic computing applications using the readily available flash memory technology, extending the use of charge storage memories to future computational architectures.

This work was partially supported by TUBITAK under Grant BIDEB 2218 to Ikram Orak.

- <sup>1</sup>D. Kahng and S. M. Sze, "A floating gate and its application to memory devices," Bell Syst. Tech. J. **46**, 1288–1295 (1967).

- <sup>2</sup>L. O. Chua, "Memristor-the missing circuit element," IEEE Trans. Circuit Theory **18**(5), 507–519 (1971).

- <sup>3</sup>T. Prodromakis, C. Toumazou, and L. Chua, "Two centuries of memristors," Nat. Mater. **11**(6) 478–481 (2012).

- <sup>4</sup>R. Waser and M. Aono, "Nanoionics-based resistive switching memories," Nat. Mater. 6(11), 833–840 (2007).

- <sup>5</sup>R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories-nanoionic mechanisms, prospects, and challenges," Adv. Mater. 21(25–26), 2632–2663 (2009).

- <sup>6</sup>J. F. Gibbons and W. E. Beadle, "Switching properties of thin NiO films," Solid-State Electron. **7**(11), 785–790 (1964).

- <sup>7</sup>F. Argall, "Switching phenomena in titanium oxide thin films," Solid-State Electron. **11**(5), 535–541 (1968).

- <sup>8</sup>K. Terabe, T. Hasegawa, T. Nakayama, and M. Aono, "Quantized conductance atomic switch," Nature 433(7021), 47–50 (2005).

- <sup>9</sup>B. J. Choi, D. S. Jeong, S. K. Kim, C. Rohde, S. Choi, J. H. Oh, and S. Tiedke, "Resistive switching mechanism of TiO<sub>2</sub> thin films grown by atomic-layer deposition," J. Appl. Phys. **98**(3), 033715 (2005).

- <sup>10</sup>D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," Nature 453(7191), 80–83 (2008).

- <sup>11</sup>J. J. Yang, M. D. Pickett, X. Li, D. A. Ohlberg, D. R. Stewart, and R. S. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," Nat. Nanotechnol. 3(7), 429–433 (2008).

- <sup>12</sup>D. H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, and C. S. Hwang, "Atomic structure of conducting nanofilaments in TiO<sub>2</sub> resistive switching memory," Nat. Nanotechnol. 5(2), 148–153 (2010).

- <sup>13</sup>O. O. Ekiz, M. Urel, H. Guner, A. K. Mizrak, and A. Dâna, "Reversible electrical reduction and oxidation of graphene oxide," ACS Nano 5(4), 2475–2482 (2011).

- <sup>14</sup>H. Acar, R. Genc, M. Urel, T. S. Erkal, A. Dana, and M. O. Guler, "Selfassembled peptide nanofiber templated one-dimensional gold

nanostructures exhibiting resistive switching," Langmuir 28(47), 16347–16354 (2012).

- <sup>15</sup>G. S. Snider, "Self-organized computation with unreliable, memristive nanodevices," Nanotechnology **18**(36), 365202 (2007).

- <sup>16</sup>J. J. Yang, J. Borghetti, D. Murphy, D. R. Stewart, and R. S. Williams, "A family of electronically reconfigurable nanodevices," Adv. Mater. 21(37), 3754–3758 (2009).

- <sup>17</sup>Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinali, J. J. Yang, and R. S. Williams, "Memristor–CMOS hybrid integrated circuits for reconfigurable logic," Nano Lett. 9(10), 3640–3645 (2009).

- <sup>18</sup>H. Kim, M. P. Sah, C. Yang, T. Roska, and L. O. Chua, "Neural synaptic weighting with a pulse-based memristor circuit," IEEE Trans. Circuits Syst. I Regul. Pap. **59**(1), 148–158 (2012).

- <sup>19</sup>S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale memristor device as synapse in neuromorphic systems," Nano Lett. **10**(4), 1297–1301 (2010).

- <sup>20</sup>D. Kuzum, R. G. Jeyasingh, B. Lee, and H. S. P. Wong, "Nanoelectronic programmable synapses based on phase change materials for braininspired computing," Nano Lett. **12**(5), 2179–2186 (2012).

- <sup>21</sup>S. Yu, Y. Wu, R. Jeyasingh, D. Kuzum, and H. S. Wong, "An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation," IEEE Trans. Electron Devices 58(8), 2729–2737 (2011).

- <sup>22</sup>S. H. Jo, K. H. Kim, and W. Lu, "High-density crossbar arrays based on a Si memristive system," Nano Lett. 9(2), 870–874 (2009).

- <sup>23</sup>J. Yao, Z. Sun, L. Zhong, D. Natelson, and J. M. Tour, "Resistive switches and memories from silicon oxide," Nano Lett. 10(10), 4105–4110 (2010).

- <sup>24</sup>S. H. Jo, K. H. Kim, and W. Lu, "Programmable resistance switching in nanoscale two-terminal devices," Nano Lett. **9**(1), 496–500 (2009).

- <sup>25</sup>S. Yu, H. Y. Chen, B. Gao, J. Kang, and H. S. P. Wong, "HfOx-based vertical resistive switching random access memory suitable for bit-cost-effective threedimensional cross-point architecture," ACS Nano 7(3), 2320–2325 (2013).

- <sup>26</sup>S. H. Jo and W. Lu, "CMOS compatible nanoscale nonvolatile resistance switching memory," Nano Lett. 8(2), 392–397 (2008).

- <sup>27</sup>J. G. Simmons and R. R. Verderber, "New conduction and reversible memory phenomena in thin insulating films," Proc. R. Soc. London, Ser. A 301(1464), 77–102 (1967).

- <sup>28</sup>J. Ouyang, C. W. Chu, C. R. Szmanda, L. Ma, and Y. Yang, "Programmable polymer thin film and non-volatile memory device," Nat. Mater. 3(12), 918–922 (2004).

- <sup>29</sup>F. Alibart, S. Pleutin, D. Guérin, C. Novembre, S. Lenfant, K. Lmimouni, C. Gamrat, and D. Vuillaume, "An organic nanoparticle transistor behaving as a biological spiking synapse," Adv. Funct. Mater. 20, 330–337 (2010).

- <sup>30</sup>F. Alibart, S. Pleutin, O. Bichler, C. Gamrat, T. Serrano-Gotarredona, B. Linares-Barranco, and D. Vuillaume, "A memristive nanoparticle/organic hybrid synapstor for neuroinspired computing," Adv. Funct. Mater. 22, 609–616 (2012).

- <sup>31</sup>F. B. Oruç, F. Cimen, A. Rizk, M. Ghaffari, A. Nayfeh, and A. Okyay, "Thin-film ZnO charge-trapping memory cell grown in a single ALD step," IEEE Electron Device Lett. 33(12), 1714–1716 (2012).

- <sup>32</sup>I. B. Akca, A. Dâna, A. Aydinli, and R. Turan, "Comparison of electron and hole charge-discharge dynamics in germanium nanocrystal flash memories," Appl. Phys. Lett. **92**(5), 052103 (2008).

- <sup>33</sup>A. Dâna, I. Akça, O. Ergun, A. Aydınlı, R. Turan, and T. G. Finstad, "Charge retention in quantized energy levels of nanocrystals," Physica E 38(1), 94–98 (2007).

- <sup>34</sup>U. Bostanci, M. K. Abak, O. Aktaş, and A. Dâna, "Nanoscale charging hysteresis measurement by multifrequency electrostatic force spectroscopy," Appl. Phys. Lett. **92**(9), 093108 (2008).

- <sup>35</sup>A. Dâna, I. Akca, A. Aydinli, R. Turan, and T. G. Finstad, "A figure of merit for optimization of nanocrystal flash memory design," J. Nanosci. Nanotechnol. 8(2), 510–517 (2008).

- <sup>36</sup>P. Pavan, R. Bez, P. Olivo, and E. Zanoni, "Flash memory cells-an overview," Proc. IEEE 85(8), 1248–1271 (1997).