# PARALLEL MAPPING AND CIRCUIT PARTITIONING HEURISTICS BASED ON MEAN FIELD ANNEALING

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER ENGINEERING AND INFORMATION SCIENCE AND THE INSTITUTE OF ENGINEERING AND SCIENCE OF EILKENT UNIVERSITY IN PARTIAL PULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

By Tevsik Bultan January 1992

QA 402-5 :885 1992

# PARALLEL MAPPING AND CIRCUIT PARTITIONING HEURISTICS BASED ON MEAN FIELD ANNEALING

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER

ENGINEERING AND INFORMATION SCIENCE

AND THE INSTITUTE OF ENGINEERING AND SCIENCE

OF BILKENT UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF SCIENCE

By Tevfik Bultan January 1992

Teufik Bullan tarafından bağışlanmıştır.

```

84

402-5

-B85

1992

B. 11123

```

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Assoc. Prof. Cevelet Aykanat (Principal Advisor)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Assoc. Prof. Kemal Oflazer

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Asst. Prof. İhsan Sabuncuoğlu

P. Sabuncul

Approved by the Institute of Engineering and Science:

Prof. Mehmet Baray, Director of the Institute of Engineering and Science

#### **ABSTRACT**

# PARALLEL MAPPING AND CIRCUIT PARTITIONING HEURISTICS BASED ON MEAN FIELD ANNEALING

#### Tevfik Bultan

M. S. in Computer Engineering and Information Science Supervisor: Assoc. Prof. Cevdet Aykanat January 1992

Mean Field Annealing (MFA) algorithm, recently proposed for solving combinatorial optimization problems, combines the characteristics of neural networks and simulated annealing. In this thesis, MFA is formulated for the mapping problem and the circuit partitioning problem. Efficient implementation schemes, which decrease the complexity of the proposed algorithms by asymptotical factors, are also given. Performances of the proposed MFA algorithms are evaluated in comparison with two well-known heuristics: simulated annealing and Kernighan-Lin. Results of the experiments indicate that MFA can be used as an alternative heuristic for the mapping problem and the circuit partitioning problem. Inherent parallelism of the MFA is exploited by designing efficient parallel algorithms for the proposed MFA heuristics. Parallel MFA algorithms proposed for solving the circuit partitioning problem are implemented on an iPSC/2<sup>1</sup> hypercube multicomputer. Experimental results show that the proposed heuristics can be efficiently parallelized, which is crucial for algorithms that solve such computationally hard problems.

<sup>&</sup>lt;sup>1</sup>iPSC/2 is a registered trademark of Intel Corporation

Keywords: Mean Field Annealing, Neural Networks, Simulated Annealing, Combinatorial Optimization, Mapping Problem, Circuit Partitioning Problem, Parallel Processing, Multicomputers.

### ÖZET

#### ORTAK ALAN TAVLAMASINA DAYANAN PARALEL EŞLEME VE DEVRE PARÇALAMA ALGORİTMALARI

Tevfik Bultan

Bilgisayar Mühendisliği ve Enformatik Bilimleri Bölümü

Yüksek Lisans

Tez Yöneticisi: Assoc. Prof. Cevdet Aykanat

Ocak 1992

Birleşimsel eniyileme problemlerini çözmek için önerilen Ortak Alan Tavlama (OAT) algoritması, sinir ağları ve tavlama benzetimi yöntemlerinin özelliklerini taşır. Bu çalışmada, OAT algoritması eşleme ve devre parçalama problemlerine uyarlanmıştır. Önerilen algoritmaların karmaşıklığını asimtotik olarak azaltan verimli gerçekleme yöntemleri de geliştirilmiştir. Önerilen algoritmaların başarımları tavlama benzetimi ve Kernighan-Lin algoritmaları ile kıyaslıyarak değerlendirilmiştir. Elde edilen sonuçlar OAT'nin eşleme ve devre parçalama problemlerini çözmek için alternatif bir algoritma olarak kullanılabileceğini göstermektedir. Önerilen OAT algoritmaları verimli bir şekilde paralelleştirilmiştir. Devre parçalama problemi için önerilen paralel OAT algoritmaları iPSC/2 hiperküp çok işlemcili bilgisayarında gerçeklenmiştir. Deneysel sonuçlar önerilen algoritmaların verimli bir şekilde paralelleştirilebildiklerini göstermektedir.

Anahtar kelimeler : Ortak Alan Tavlaması, Sinir Ağları, Tavlama Benzetimi, Birleşimsel Eniyileme, Eşleme Problemi, Devre Parçalama Problemi, Paralel İşleme, Çok İşlemcili Bilgisayarlar.

## ACKNOWLEDGEMENT

I am very grateful to my supervisor Assoc. Prof. Cevdet Aykanat as he taught me what research is, and always provided a motivating support during this study.

I would also like to express my gratitude to Assoc. Prof. Kemal Oflazer and Asst. Prof. İhsan Sabuncuoğlu for their remarks and comments on this thesis.

Finally, I wish to thank all my friends, and my family for their morale support.

## Contents

| 1                                         | INTRODUCTION                     |                                                                 | 1  |  |

|-------------------------------------------|----------------------------------|-----------------------------------------------------------------|----|--|

| 2 THEORY                                  |                                  | EORY                                                            | 6  |  |

| 2.1 Hopfield Neural Networks              |                                  | Hopfield Neural Networks                                        | 6  |  |

|                                           |                                  | 2.1.1 Combinatorial Optimization Using Hopfield Neural Networks | 7  |  |

|                                           |                                  | 2.1.2 Problems of Hopfield Neural Networks                      | 8  |  |

|                                           | 2.2                              | Simulated Annealing                                             | 9  |  |

|                                           | 2.3                              | Mean Field Annealing                                            |    |  |

| 3                                         | MF                               | MFA FOR THE MAPPING PROBLEM  3.1 The Mapping Problem            |    |  |

|                                           | 3.1                              |                                                                 |    |  |

|                                           | 3.2 Modeling the Mapping Problem |                                                                 | 17 |  |

| 3.3 Solving the Mapping Problem Using MFA |                                  | Solving the Mapping Problem Using MFA                           | 21 |  |

|                                           |                                  | 3.3.1 Formulation                                               | 23 |  |

|                                           |                                  | 3.3.2 An Efficient Implementation Scheme                        | 28 |  |

|                                           | 3.4                              | Performance of Mean Field Annealing Algorithm                   | 30 |  |

|                                           |                                  | 3.4.1 MFA Implementation                                        | 31 |  |

| CONTENTS | ix |

|----------|----|

|          |    |

|                                                       |     | 3.4.2                                       | Kernighan-Lin Implementation                 | 31 |

|-------------------------------------------------------|-----|---------------------------------------------|----------------------------------------------|----|

|                                                       |     | 3.4.3                                       | Simulated Annealing Implementation           | 32 |

|                                                       |     | 3.4.4                                       | Experimental Results                         | 33 |

|                                                       | 3.5 | Parall                                      | elization of Mean Field Annealing Algorithm  | 37 |

| 4                                                     | MF  | A FOF                                       | R THE CIRCUIT PARTITIONING PROBLEM           | 45 |

|                                                       | 4.1 | The C                                       | Fircuit Partitioning Problem                 | 45 |

|                                                       | 4.2 | Model                                       | ing the Circuit Partitioning Problem         | 46 |

|                                                       | 4.3 | Solvin                                      | g the Circuit Partitioning Problem Using MFA | 49 |

|                                                       |     | 4.3.1                                       | Graph Model                                  | 49 |

|                                                       |     | 4.3.2                                       | Network Model                                | 51 |

| 4.4 Parallelization of Mean Field Annealing Algorithm |     | elization of Mean Field Annealing Algorithm | 56                                           |    |

|                                                       |     | 4.4.1                                       | Graph Model                                  | 57 |

|                                                       |     | 4.4.2                                       | Network Model                                | 59 |

| 5                                                     | CO  | NCLU:                                       | SIONS                                        | 63 |

# List of Figures

| 2.1 | Simulated annealing algorithm.                                                                                                               | 10 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Mean field annealing algorithm.                                                                                                              | 12 |

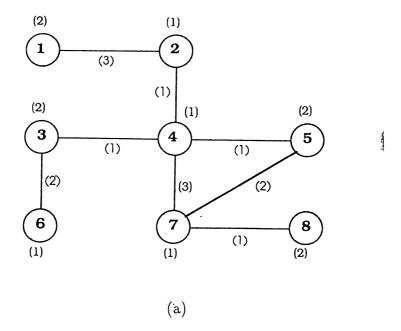

| 3.1 | A mapping problem instance, with (a) TIG, (b) POG (which represents a 2-dimensional hypercube) and (c) PCG.                                  | 22 |

| 3.2 | MFA algorithm for the mapping problem.                                                                                                       | 27 |

| 3.3 | Node program for one iteration of the parallel MFA algorithm for the mapping problem.                                                        | 43 |

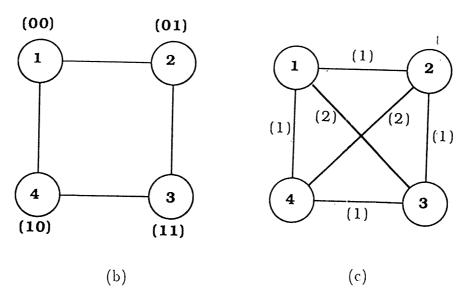

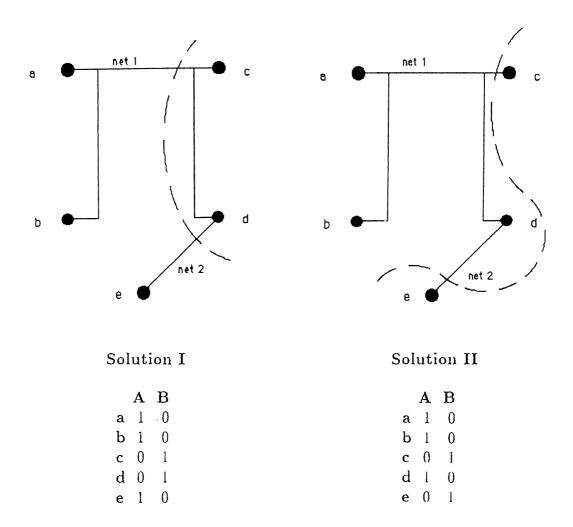

| 4.1 | Modeling of a given circuit partitioning problem instance with (a) graph and (b) network models. Dashed lines indicate an example partition. | 48 |

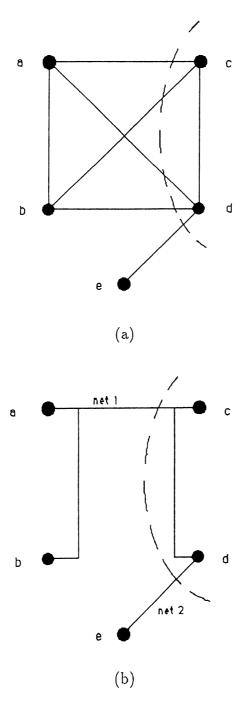

| 4.2 | Two possible solutions for the given circuit partitioning problem instance.                                                                  | 54 |

| 4.3 | Node program for one iteration of the parallel MFA algorithm for the graph partitioning problem                                              | 58 |

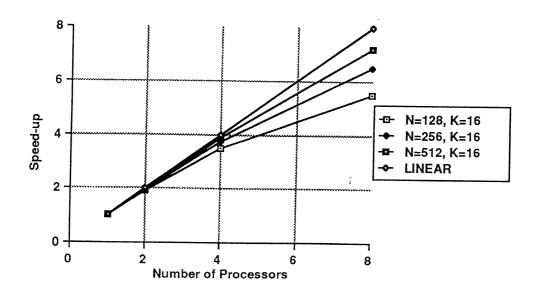

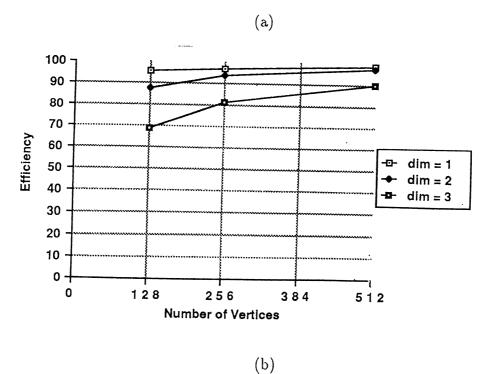

| 4.4 | Speed-up (a) and efficiency (b) curves for the graph partitioning problem.                                                                   | 60 |

| 4.5 | Node program for one iteration of the parallel MFA algorithm for the network partitioning problem.                                           | 61 |

| LIST OF FIGURES | X                                       |

|-----------------|-----------------------------------------|

|                 | • • • • • • • • • • • • • • • • • • • • |

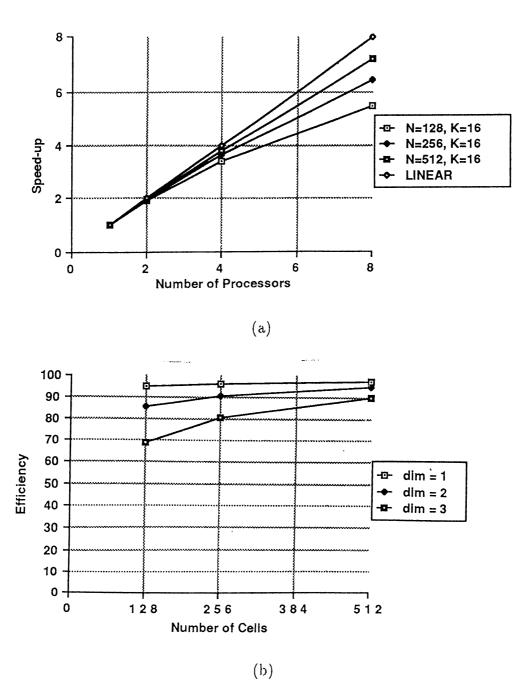

| 4.6 | Speed-up (a) and efficiency (b) curves for the network partition- |    |

|-----|-------------------------------------------------------------------|----|

|     | ing problem.                                                      | 62 |

1

ŧ

**!**

# List of Tables

| 3.1 | Averages of the total communication costs of the solutions found |    |

|-----|------------------------------------------------------------------|----|

|     | by KL-RB, KL-PM, SA and MFA heuristics, for randomly gen-        |    |

|     | erated mapping problem instances.                                | 34 |

| 3.2 | Averages of the computational loads of the minimum and max-      |    |

|     | imum loaded processors for the solutions found by KL-RB, KL-     |    |

|     | PM, SA, MFA heuristics, for randomly generated mapping prob-     |    |

|     | lem instances.                                                   | 35 |

| 3.3 | Average execution times (in seconds) of KL-RB, KL-PM, SA         |    |

|     | and MFA heuristics, for randomly generated mapping problem       |    |

|     | instances.                                                       | 36 |

| 4.1 | Mean cut sizes of the solutions found by MFA, KL, and SA         |    |

|     | heuristics for randomly generated network partitioning problem   |    |

|     | instances.                                                       | 56 |

#### 1. INTRODUCTION

Some cognitive tasks as pattern recognition, associative recall, guiding of a mechanical hand are easily handled by biological neural networks whereas they remain as time consuming tasks for digital computers. This fact motivated scientists and opened a research area called Artificial Neural Networks (ANN). Scope of ANN includes understanding and modeling of biological neural networks, and designing artificial devices that have similar properties. Research on this area started with the early works of McCulloch and Pitts (1943), and has continued with varying levels of popularity until today. From the 1980s onwards, neural network models became the center of extensive study, and have seen an extraordinary growth of interest in their properties. Reasons for this increase in popularity are: better understanding gained on information processing in nature; increasing computer power which enables scientists to make better simulations and analysis of the models; growing interest in parallel computation and analog VLSI.

Research on ANN can be divided into two streams: first one deals with understanding and modeling of the biological neural networks, and second one exploits the information gained on biological neural networks for designing artificial devices or algorithms to perform tasks which are difficult for conventional computers. Until last few years, works on the second area were concentrated on learning and classification capability, and associative memory operation of the neural networks. Recent works by Hopfield and Tank [11, 12, 13, 31] show that solving NP-hard combinatorial optimization problems is another promising area for ANN. Hopfield and Tank proposed that, Hopfield type continuous and deterministic ANN model can be used for solving combinatorial optimization problems [11]. However, simulations of this model reveal the fact that it

is hard to obtain feasible solutions for large problem sizes. Many variants of the Hopfield Neural Network (HNN) have been designed [3, 30, 34] in order to improve the model for obtaining feasible and good solutions.

Combinatorial optimization problems constitute a large class, which is encountered in various disciplines. Optimization problems, in general, are characterized by searching for the *best* values of given variables to achieve a goal. In technical words, the objective is the minimization or maximization of a function, subject to some other constraint functions. A typical example is the general nonlinear programming problem, stated as: find  $\mathbf{x} \in \Re^n$  which

minimizes

$$f(\mathbf{x})$$

subject to  $g_i(\mathbf{x}) \ge 0$   $i = 1, ..., m$

$h_j(\mathbf{x}) = 0$   $j = 1, ..., p$   $(1.1)$

where  $f, g_i, h_j$  are general functions which map  $\Re^n \to \Re$ . The function f is called the cost function, and functions  $g_i$  and  $h_j$  are called constraint functions. Problems, for which the variables of the cost and constraint functions are discrete, are called combinatorial optimization problems. Some problems in this class can not be solved in polynomial time with the known methods. As the problem size increases, computing time needed to solve this kind of problems increases exponentially, resulting with intractable instances. This class of problems, called NP-hard optimization problems, are solved using heuristics. Heuristics are generally problem specific, computationally efficient algorithms. They do not guarantee to find optimal solution, but require much less computing time. The drawback of heuristics is that they usually get stuck in local minima.

In the last decade a powerful method, called Simulated Annealing (SA), has been developed for solving combinatorial optimization problems [18]. This method is the application of a successful statistical method, which is used to estimate the results of annealing process in statistical mechanics, to combinatorial optimization problems. SA is a general method (i.e. it is not problem specific) which guarantees to find the optimum solution if time is not limited. Time needed for simulated annealing is also too much and exact solutions of NP-hard problems still stay intractable. Nice property of simulated annealing

is that, it can be used as a heuristic to obtain near optimal solutions in limited time, and as the time limit is increased, quality of the obtained solutions also increase. SA has the capability of escaping from local minima if sufficient time is given. This method has been successfully applied to various NP-hard optimization problems [18, 20, 23].

The subject of this thesis is a recently proposed algorithm, called Mean Field Annealing (MFA) [22, 33, 34, 35]. MFA was originally proposed for solving the traveling salesperson problem [33, 34]. It combines the collective computation property of HNN with the annealing notion of SA. MFA is a general strategy and can be applied to various problems with suitable formulations. Work on MFA [4, 5, 21, 22, 34, 35] showed that, it can be successfully applied to combinatorial optimization problems. In this thesis, MFA is formulated for two well-known, NP-hard, combinatorial optimization problems: the mapping problem and the circuit partitioning problem.

The mapping problem—arises while developing—parallel programs for distributed-memory, message-passing parallel computers (multicomputers). In order to develop a parallel program for a multicomputer, first the problem is decomposed into a set of interacting sequential sub-problems (or tasks) that can be executed in parallel. Then, each one of these tasks is mapped to a processor of the parallel architecture, in such a way that the total execution time is minimized. This mapping phase is called the mapping problem [2], and is known to be NP-hard. In this thesis, MFA is formulated for solving the mapping problem, and its performance is compared with the performances of other well-known heuristics.

Partitioning of VLSI circuits are needed in various phases of VLSI design. Partitioning means to divide the components of a circuit into two or more evenly weighted partitions, such that the number of signal nets interconnecting them is minimized. This problem, called the circuit partitioning problem, is also an NP-hard combinatorial optimization problem. In this work, MFA is also formulated for solving the circuit partitioning problem, and the performance of the proposed algorithm is compared with the performances of other well-known heuristics.

ł

Heuristics used for solving NP-hard combinatorial optimization problems as the mapping problem and the circuit partitioning problem are time consuming processes and parallelization of them is crucial. There is a large volume of research on the parallelization of such algorithms. One of the motivations in this work is to exploit the inherent parallelism in neural networks in order to obtain efficient parallel algorithms. MFA is a good candidate for efficient parallelization as it uses the collective computation property of HNN.

In order to develop a parallelization scheme, first the parallel computer that will be used must be classified. Classification of parallel architectures can be done according to their memory organization, the number of instruction streams supported, and the interconnection topology. Memory organization in parallel architectures can be divided into two main groups, shared-memory and distributed-memory architectures. In shared-memory architectures, which are named as multiprocessors, a common memory or a common address space is used by all processors. On the other hand, in distributed-memory architectures, processors can not access to a common memory space. Each processor has a local, isolated memory. Synchronization, coordination among processors and data exchange are achieved by message passing among processors. In this type of architectures, each processor may be viewed as an individual computer, hence they are called multicomputers.

Classification according to the interconnection topology determines how to handle communications among processors. Most commonly used topologies are mesh, hypercube and ring.

According to the number of instruction streams supported, parallel architectures can be divided into two groups. SIMD (Single Instruction stream Multiple Data stream) and MIMD (Multiple Instruction stream and Multiple Data stream) architectures. In a SIMD architecture, a central control processor broadcasts the instruction that will be executed to all processors. Each processor executes the same instruction using the data in its local memory. In MIMD architectures, each processor is able to fetch, decode and execute an instruction by itself, which can be different from the instructions executed by other processors.

In this work, MFA is parallelized for distributed-memory MIMD multicomputers, and implemented on a 3-dimensional iPSC/2 hypercube multicomputer. A d-dimensional hypercube consists of  $P = 2^d$  processors with each processor being directly connected to d other (neighbor) processors [28]. The processors of the hypercube are labeled with d-bit binary numbers, and the binary label of each processor differs from that of its neighbor in exactly one bit. The parallelization schemes proposed in this work can also be used for SIMD multicomputers and other interconnection topologies with slight modifications.

In Chapter 2, HNN and SA are reviewed and a general formulation of MFA is given. Chapter 3 presents the proposed formulation of MFA for the mapping problem. Efficient implementation and parallelization of the proposed MFA algorithm is also addressed in this chapter. In Chapter 4, MFA is formulated for solving the circuit partitioning problem. Chapter 4 also presents efficient implementation and parallelization of the proposed algorithm. In Chapter 3 and 4, performances of the proposed MFA algorithms are evaluated in comparison with two well-known heuristics: simulated annealing and Kernighan-Lin. In Chapter 5, conclusions are stated.

#### 2. THEORY

This chapter reviews previous works on Hopfield Neural Networks (HNN) and Simulated Annealing (SA) to give a better understanding of Mean Field Annealing (MFA). In Section 2.1 neural network models proposed by Hopfield are briefly discussed, and application of HNN to combinatorial optimization problems is described. A summary of the later works on HNN is also presented at the end of Section 2.1. Section 2.2 gives the general properties of simulated annealing and describes its application to combinatorial optimization problems. In Section 2.3, MFA algorithm is described, denoting the similarities with previously mentioned two methods.

#### 2.1 Hopfield Neural Networks

One of the main reasons for the growing interest on neural networks in the last decade, is the Artificial Neural Network (ANN) model proposed by Hopfield [9]. Many ideas used in this model have precursors spread over the fifty years of research on neural networks. The importance of the work by Hopfield is that it brings them all together, using a physical analogy and a clear mathematical analysis, and gives a good view of the possible capabilities of the proposed model. Later, Hopfield proposed another model [10] that has the same properties of the original model, and looks very promising for VLSI implementations.

The original model [9] is a discrete, stochastic model, which uses two-state neurons with a stochastic updating algorithm. The continuous and deterministic model, which is proposed later [10], uses neurons with graded response, and

time evolution of the state of the system (change in the states of the neurons) is described by a differential equation. In these two models, an energy function, which always decreases as the system iterates, is defined. In his two consecutive papers [9, 10], Hopfield presented his ANN models as Content Addressable Memory (CAM) in order to explain their properties. In CAM model, minima of the energy function correspond to the stored words. Starting from a given initial state, the system is expected to reach one of these minima, which means to output one of the stored words in the CAM. CAM model of Hopfield can be regarded as an optimizing network: given an input, find one of the stored items which is the *closest* item to the given input. In his later works with Tank [11, 31] it is shown that well-known combinatorial optimization problems as the traveling salesperson problem, can also be solved by HNN.

# 2.1.1 Combinatorial Optimization Using Hopfield Neural Networks

Hopfield and Tank showed that, continuous and deterministic HNN has collective computational properties [11, 12, 13]. In collective computation, decisions taken to solve the problem is not determined by a single unit, but instead responsibility is distributed over a large number of simple, massively connected units. The nature of collective computation suggests that it might be particularly effective for problems that involve global interaction among different parts of the problem. NP-hard optimization problems are such problems. HNN can be used for solving a combinatorial optimization problem by choosing a representation scheme in which the output states of neurons can be decoded as a solution to the target problem. Then, HNN is constructed accordingly by choosing an energy function whose global minimum value corresponds to the best solution of the problem to be solved [11]. Hence, the constructed HNN is expected to compute the best solution to the target problem starting from a randomly chosen initial state by minimizing its energy function. General form of such an energy function (also called Hamiltonian of the system) is

$$H = cost + global constraint$$

(2.1)

Here, cost term represents the cost function of the optimization problem to be solved and global constraint term represents the constraint functions introduced to obtain feasible solutions. Exact solution of the problem corresponds to the global minimum of this energy function.

Motivation behind the works of Hopfield and Tank is to use hardware implementations of HNN to solve large optimization problems. It is a general method to simulate a model on computers before implementing it on hardware in order to observe and solve possible problems. In order to simulate HNN on a computer, first the equations of motion for the neural network are written from the state equations of the neurons. Then, these equations are solved for each neuron iteratively using a numerical method (usually Euler's method is used to compute the resulting differential equations). State of each neuron is computed in discrete time intervals until a stable state is found.

#### 2.1.2 Problems of Hopfield Neural Networks

HNN have been applied to various optimization problems and reasonable results have been obtained for small size problems. However, simulations of this network reveals the fact that, it is hard to obtain feasible solutions for large problem sizes. Wilson and Pawley reports that, most of the simulation results give infeasible tours even for a 10-city traveling salesperson problem [36]. In fact, it is possible to obtain feasible tours by adjusting the parameters of the energy function (i.e., increasing the weights of the terms regarding feasibility), but, quality of the solutions deteriorate with such attempts. As is also indicated in [14], the problem of finding a balance among parameters of the energy function, in order to obtain feasible and good solutions, becomes harder as the problem size increases. Hence, the algorithm does not have a good scaling property, which is a very important performance criterion for heuristic optimization algorithms. Many attempts have been done to improve the performance of Hopfield neural network for obtaining feasible and good solutions. In one of them [3], number of terms in the energy function is decreased to increase the scalability of the algorithm. But also for that model, increase in the size of the problem causes the costs of the solutions to increase significantly.

Works by Szu [30] and Toomarian [32] are also modifications to HNN in which different energy functions are proposed. Recently, MFA is proposed as a successful alternative to HNN [22, 33, 34]. MFA algorithm combines the collective computation property of HNN and annealing notion of SA.

#### 2.2 Simulated Annealing

SA is a powerful method which is used for solving hard optimization problems. In SA, an energy function that corresponds to the cost function of the problem to be solved is defined, similar to energy function defined for HNN. SA is a probabilistic hill-climbing method, which accepts uphill moves with a probability in order to escape from local minima. SA is derived using analogy to a successful statistical model of thermodynamic processes for growing crystals.

Configuration of a solid state material at a global energy minimum is a perfectly homogeneous crystal lattice. It is determined by experience that such configurations can be achieved using the process of annealing [20]. The solid-state material is heated to a high temperature until it reaches an amorphous liquid state. Then it is cooled slowly, according to a specific annealing schedule. If the initial temperature is sufficiently high to ensure a random state, and if the cooling schedule is sufficiently slow to guarantee that the equilibrium is reached at each temperature, final configuration of the material will be close to the perfect crystal with global energy minimum [20]. In thermodynamics, it is stated that, when thermal equilibrium at temperature T is reached, a state with energy E is attained with the Boltzmann probability

$$\frac{1}{Z(T)}e^{-\frac{E}{k_BT}}\tag{2.2}$$

where Z(T) is a normalization factor and  $k_B$  is the Boltzmann constant [20].

There is a fine theoretical model which explains this physical phenomenon. During the annealing process the states of the atoms are perturbed by small random changes. If the change in state lowers the energy of the system, it is always accepted. If not, the change in configuration is accepted with a probability  $e^{-\Delta E/k_BT}$ . The probability of accepting perturbations causing increase

- 1. Get an initial configuration C

- 2. Get initial temperature, and set  $T = T_0$

- 3. While not yet frozen DO

- 3.1 While equilibrium at T is note yet reached DO

- 3.1.1 Generate a random neighbor C' of C

- 3.1.2 Let  $\Delta E = E(C') E(C)$

- 3.1.3 If  $\Delta E \leq 0$  (downhill move), set C = C'

- 3.1.4 if  $\Delta E > 0$  (uphill move), set C = C' with probability  $e^{-\frac{\Delta E}{T}}$

- 3.2 Update T according to the cooling schedule

Figure 2.1. Simulated annealing algorithm.

in energy decreases with the decreasing temperature, and minor modifications occur at lower temperatures. Experiments show that this model gives similar results as physical annealing process [20].

Kirkpatrick applied this model to optimization problems and called the resulting method SA. In transforming the physical model to computational model, energy function is replaced with the cost function of the optimization problem to be solved (note the similarity with HNN), and states of the matter are replaced with the legal configurations of the problem instance. Annealing schedule is controlled with a simulated temperature. Figure 2.1 illustrates the SA algorithm.

Although SA is a powerful method it has some problems. It requires a large amount of computing power because of the need for generating a large number of configurations, and very slow cooling in order to reach equilibrium at each temperature. Performance of the algorithm is closely related to the generation of neighboring configurations. It is an inherently sequential algorithm which

does not give good performance on parallel computers. It is hard to obtain good cooling schedules that results with good solutions in small amount of computer time.

#### 2.3 Mean Field Annealing

MFA merges collective computation and annealing properties of the two methods described above, to obtain a general algorithm for solving combinatorial optimization problems. Mapping problems to MFA is identical to HNN. A neuron matrix is formed such that when neurons take their final values they represent a configuration in the solution space of the problem.

Mathematical analysis of MFA is done by analogy to Ising spin model, which is used to estimate the state of a system of particles or *spins* in thermal equilibrium. Spins in MFA algorithm are analogous to the neurons of HNN. This method was first proposed for solving the traveling-salesperson problem [33], and then it is applied to the graph partitioning problem [4, 5, 21, 35]. Here, general formulation of MFA algorithm [35] is given for the sake of completeness. In the Ising spin model, the energy of a system with S spins has the following form:

$$H(\mathbf{s}) = \frac{1}{2} \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} s_k s_l + \sum_{k=1}^{S} h_k s_k$$

(2.3)

Here,  $\beta_{kl}$  indicates the level of interaction between spins k, l, and  $s_k \in \{0, 1\}$  is the value of spin k. It is assumed that  $\beta_{kl} = \beta_{lk}$  and  $\beta_{kk} = 0$  for  $1 \le k, l, \le S$ . At thermal equilibrium, spin average  $\langle s_k \rangle$  of spin k can be calculated using Boltzmann distribution as follows

$$\langle s_k \rangle = \frac{1}{1 + e^{-\phi_k/T}} \tag{2.4}$$

Here,  $\phi_k$  represents the mean field effecting on spin k, which can be computed using

$$\phi_k = -\frac{\partial \langle H(\mathbf{s}) \rangle}{\partial \langle s_k \rangle} \tag{2.5}$$

where the energy average  $\langle H(s) \rangle$  of the system is

$$\langle H(s) \rangle = \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} \langle s_k s_l \rangle + \sum_{k=1}^{S} h_k \langle s_k \rangle$$

(2.6)

- 1. Get initial temperature, and set  $T = T_0$

- 2. Initialize the spin averages  $\langle \mathbf{s} \rangle = [\langle s_1 \rangle, \dots, \langle s_k \rangle, \dots, \langle s_S \rangle]$

- 3. While temperature T is in the cooling range DO

- 3.1 While system is not stabilized for current temperature DO

- 3.1.1 Select a spin k at random.

- 3.1.2 Compute  $\phi_k$  using

$$\phi_k = -\sum_{l \neq k} \beta_{kl} \langle s_l \rangle - h_k$$

3.1.3 Update  $\langle s_k \rangle$  using

$$\langle s_k \rangle = \{1 + e^{-\phi_k/T}\}^{-1}$$

3.2 Update T according to the cooling schedule

Figure 2.2. Mean field annealing algorithm.

The complexity of computing  $\phi_k$  using Eq. (2.5) and Eq. (2.6) is exponential [35]. However, for large number of spins, the mean field approximation can be used to compute the energy average as

$$\langle H(\mathbf{s}) \rangle = \frac{1}{2} \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} \langle s_k \rangle \langle s_l \rangle + \sum_{k=1}^{S} h_k \langle s_k \rangle$$

(2.7)

Since  $\langle H(\mathbf{s}) \rangle$  is linear in  $\langle s_k \rangle$ , mean field  $\phi_k$  can be computed using the following equation

$$\phi_k = -\frac{\partial \langle H(\mathbf{s}) \rangle}{\partial \langle s_i \rangle} = -\left(\sum_{l \neq k} \beta_{kl} \langle s_l \rangle + h_k\right) \tag{2.8}$$

Thus, the complexity of computing  $\phi_k$  reduces to O(S).

At each temperature, starting with initial spin averages, the mean field effecting on a randomly selected spin is found using Eq. (2.8). Then, spin average is updated using Eq. (2.4). This process is repeated for a random sequence of spins until the system is stabilized for the current temperature. The general form of the Mean Field Annealing algorithm derived from this iterative relaxation scheme is shown in Figure (2.2). MFA algorithm tries to

find equilibrium point of a system of S spins using annealing process similar to SA.

The state equations used in MFA are isomorphic to the state equations of the neurons in the HNN. A synchronous version of MFA, different from the algorithm given in Figure 2.2, can be derived by solving N difference equations for N spin values simultaneously. This technique is identical to the simulations of HNN done using numerical methods. Thus, evolution of a solution in a HNN is equivalent to the relaxation toward an equilibrium state affected by the MFA algorithm at a fixed temperature [35]. Hence MFA can be viewed as an annealed neural network derived from HNN.

HNN and SA methods have a major difference: SA is an algorithm implemented in software, whereas HNN is derived with a possible hardware implementation in mind. MFA is somewhere in between, it is an algorithm implemented in software, having potential for hardware realization [34, 35]. In this work, MFA is treated as a software algorithm as SA. Results obtained are comparable to other software algorithms, conforming this point of view.

### 3. MFA FOR THE MAPPING PROBLEM

In this chapter, Mean Field Annealing (MFA), is formulated for the mapping problem. In Section 3.1, the mapping problem is described and previous approaches used for solving the mapping problem are summarized. Section 3.2 presents a formal definition of the mapping problem by modeling the parallel program design process. Section 3.3 presents the proposed formulation of the MFA algorithm for the mapping problem. An efficient implementation scheme for the proposed algorithm is also described in Section 3.3.2. Section 3.4 presents the performance evaluation of the MFA algorithm for the mapping problem in comparison with two well-known mapping heuristics: simulated annealing and Kernighan-Lin. Finally, efficient parallelization of the MFA algorithm for the mapping problem is proposed in Section 3.5.

#### 3.1 The Mapping Problem

Today, with the aid of VLSI technology, parallel computers not only exist in research laboratories, but are also available on the market as powerful, general purpose computers. Use of parallel computers in various applications, makes the problem of mapping parallel programs to parallel computers more crucial. The mapping problem arises while developing parallel programs for distributed-memory, message-passing parallel computers (multicomputers). In multicomputers, processors neither have shared memory nor have shared address space. Each processor can only access its local memory. Synchronization and coordination among processors are achieved through explicit message passing. Processors of a multicomputer are usually connected by utilizing one of

the well-known direct interconnection network topologies such as ring, mesh, hypercube, etc. These architectures have the nice scalability feature due to the lack of shared resources and the increasing bandwidth with increasing number of processors.

However, designing efficient parallel algorithms for such architectures is not straightforward. An efficient parallel algorithm should exploit the full potential power of the architecture. Processor idle time and the interprocessor communication overhead may lead to poor utilization of the architecture and hence poor overall system performance. Processor idle time arises due to the uneven load balance in the distribution of the computational load among processors of the multicomputer. Parallel algorithm design for multicomputers can be divided into two phases: first phase is the decomposition of the problem into a set of interacting sequential sub-problems (or tasks) which can be executed in parallel. Second phase is mapping each one of these tasks to a processor of the parallel architecture in such a way that the total execution time is minimized. This mapping phase, named as the mapping problem [2], is very crucial in designing efficient parallel programs.

For a class of regular problems with regular interaction patterns, the mapping problem can be efficiently resolved by the judicious choice of the decomposition scheme. In such problems, chosen decomposition scheme yields an interaction topology that can be directly embedded to the interconnection network topology of the multicomputer. Such approaches can be referred as intuitive approaches. However, intuitive mapping approaches yield good results only for a restricted class of problems, under simplifying assumptions. The mapping problem is known to be NP-hard [15, 16]. Hence, heuristics giving sub-optimal solutions are used to solve the problem [1, 2, 6, 15, 16, 26]. Two distinct approaches have been considered in the context of mapping heuristics, one phase approaches and two phase approaches [6]. One phase approaches, referred to as many-to-one mapping, try to map tasks of the parallel program directly onto the processors of the multicomputer. In two phase approaches, clustering phase is followed by a onc-to-one mapping phase. In the clustering phase, tasks of the parallel program is partitioned into as many equal weighted clusters as the number of processors of the multicomputer, while minimizing

the total weight of the inter-cluster interactions [26]. In the one-to-one mapping phase, each cluster is assigned to an individual processor of the multicomputer such that total inter-processor communication is minimized [26].

In two phase approaches, the problem solved in the clustering phase is identical to the multi-way graph partitioning problem. Graph partitioning is the balanced partitioning of the vertices of a graph into a number of bins, such that the total cost of the edges in the edge cut set is minimized. Kernighan-Lin (KL) heuristic [7, 17] is an efficient heuristic, originally proposed for the graph bipartitioning problem, which can also be used for clustering [6, 26]. KL heuristic is a non-greedy, iterative improvement technique that can escape from local minima by testing the gains of a sequence of moves in the search space before performing them. A variant of the KL heuristic can be used for solving one-to-one mapping problem encountered in the second phase [6].

Simulated Annealing (SA) can also be used as a one phase heuristic for solving many-to-one mapping problem [23, 29]. Successful applications of SA to the mapping problem is achieved in various works [23, 29]. It has been observed that the quality of the solutions obtained using SA are superior compared with the results of the other heuristics.

Heuristics proposed to solve the mapping problem are compute intensive algorithms. Solving the mapping problem can be thought as a preprocessing done before the execution of the parallel program on the parallel computer. If the mapping heuristic is executed sequentially, the execution time of this preprocessing can be included in the serial portion of the parallel program, which limits the efficiency that can be attained. In some cases, the sequential overhead caused by this preprocessing is not acceptable, and the need for the parallelization of the preprocessing arises. Efficient parallel mapping heuristics are needed in such cases. KL and SA heuristics are inherently sequential, hence hard to parallelize. Efficient parallelization of these algorithms remain as an important issue in parallel processing research.

In this chapter, Mean Field Annealing (MFA), is formulated for the manyto-one mapping problem. MFA has the inherent parallelism that exists in most of the neural network algorithms, which makes this algorithm a good candidate for parallel mapping heuristics.

#### 3.2 Modeling the Mapping Problem

Parallel program design phases are elaborated in this section in order to present a formal definition of the mapping problem. In the first phase of parallel algorithm design, problem is decomposed into a set of atomic tasks, such that the overall problem is modeled as a set of interacting tasks. Each atomic task is a sequential process to be executed by an individual processor of the parallel architecture. Selection of the decomposition scheme depends on the problem, algorithm to be used for the solution, and the architectural features of the target multicomputer.

In various classes of problems, interaction pattern among the tasks is static. Hence, the decomposition of the algorithm can be represented by a static task graph. Vertices of this graph represent the atomic tasks and the edge set represent the interaction pattern among the tasks. Relative computational costs of atomic tasks can be known or estimated priori to the execution of the parallel program. Hence, weights can be associated with the vertices to denote the computational costs of the corresponding tasks.

There are two different models used for modeling static inter-task communication patterns. These two models are referred as the Task Precedence Graph (TPG) model and Task Interaction Graph (TIG) model [16, 25]. TPG is a directed graph where directed edges represent execution dependencies. In this model, a pair of tasks connected by an edge can not be executed independently. Each edge denotes a pair of tasks: source task and destination task. The destination task can only be executed after the completion of the execution of the source task. Hence, in general, only the subsets of tasks which are unreachable from each other in the TPG can be executed independently.

In TIG, the set of interaction patterns are represented by undirected edges among vertices. In this model, each atomic task can be executed simultaneously and independently. Each edge denotes the need for the bidirectional interaction between corresponding pair of tasks at the completion of the execution of these tasks. Edges may be associated with weights which denote the amount of bidirectional information exchange involved between pairs of tasks. TIG usually represents the repeated execution of the tasks with intervening intertask interactions denoted by the edges.

The TIG model may seem to be unrealistic for general applications since it does not consider the temporal interaction dependencies among the tasks [25]. However, there are various classes of problems which can be successfully modeled with the TIG model. For example, iterative solution of systems of equations, and problems arising in image processing and computer graphics applications can be represented by TIG. In this work, mapping of problems which can be represented by TIG model is addressed.

Second phase of the parallel algorithm design is the assignment of the individual tasks to the processors of the parallel architecture, so that the execution time of the parallel program is minimized. This problem is referred as the mapping problem. In order to solve the mapping problem, parallel architecture must also be modeled in a way that represents its architectural features. Parallel architectures can easily be represented by a Processor Organization Graph (POG), where nodes represent the processors and edges represent the communication links. In fact, POG is a graphical representation of the interconnection topology utilized for the organization of the processors of the parallel architecture. In general, nodes and edges of a POG are not associated with weights, since most of the commercially available multicomputer architectures are homogeneous with identical processors and communication links.

In a multicomputer architecture, each adjacent pair of processors communicate with each other over the communication link connecting them. Such communications are referred as single-hop communications. However, each non-adjacent pair of processors can also communicate with each other via software or hardware routing. Such communications are referred as multi-hop communications. Multi-hop communications are usually routed in a static manner over the shortest path of links between the communicating pairs of processors. Communications between non-adjacent pairs of processors can be associated with relative unit communication costs. Unit communication cost is defined

as the communication cost per unit of information. Unit communication cost between a pair of processors will be a function of the shortest path between these processors and the routing scheme used for multi-hop communications. For example, intermediate processors in the communication path are interrupted in software routing so that each multi-hop communication is realized as a sequence of single-hop messages. Hence, in software routing, the unit communication cost is linearly proportional to the shortest path distance between the pair of communicating processors. Note that, in this communication model, unit communication costs between adjacent pairs of processors are taken to be unity.

Hence, the communication topology of the multicomputer can be modeled by an undirected complete graph, referred here as the Processor Communication Graph (PCG). The nodes of the PCG represent the processors and the weights associated with the edges represent the unit communication costs between pairs of processors. As is mentioned earlier, PCG can easily be constructed using the topological properties of the POG and the routing scheme utilized for inter-processor communication. In the PCG, edges between pairs of nodes representing the adjacent pairs of processors denote physical links whereas edges between pairs of nodes representing non-adjacent pairs of processors denote virtual communication links (i.e. communication paths) established for routing multi-hop communications.

The objective in mapping TIG to PCG is the minimization of the expected execution time of the parallel program on the target architecture represented by the TIG and the PCG respectively. Thus, the mapping problem can be modeled as an optimization problem by associating the following quality measures with a good mapping:

- Interprocessor communication overhead should be minimized. Tasks which have high interaction, i.e., large amount of data exchange, should be in the same processor or nearby processors.

- Computational load should be uniformly distributed among processors.

Computational load assigned to each processor should be equal as much as possible in order to minimize processor idle time.

The parallel execution time is expected to decrease as these criteria are satisfied.

A mapping problem instance can be formally defined as follows. An instance of the mapping problem includes two undirected graphs, Task Interaction Graph (TIG) and Processor Communication Graph (PCG). The TIG  $G_T(V, E)$ , has |V| = N vertices labeled as (1, 2, ..., i, j, ..., N). Vertices of the TIG represent the atomic tasks of the parallel program. Vertex weight  $w_i$  denotes the computational cost associated with task i for  $1 \le i \le N$ . Edge weight  $e_{ij}$  denotes the volume of interaction between tasks i and j connected by edge  $(i, j) \in E$ . The PCG  $G_P(P, D)$ , is a complete graph with |P| = K nodes and  $|D| = {K \choose 2}$  edges. Nodes of the PCG, labeled as (1, 2, ..., p, q, ..., K), represent the processors of the target multicomputer. Edge weights  $d_{pq}$ , for  $1 \le p, q \le N$  and  $p \ne q$ , denote the unit communication cost between processors p and q.

Given an instance of the mapping problem with TIG,  $G_T(V, E)$ , and PCG,  $G_P(P, D)$ , question is to find a many-to-one mapping function  $M: V \to P$ , which assigns each vertex of the graph  $G_T$  to a unique node of graph  $G_P$ , and minimizes the total interprocessor communication cost (CC)

$$CC = \sum_{(i,j)\in E} e_{ij} d_{M(i)M(j)}$$

(3.1)

while having the computational load ( $CL_p$ : computational load of processors p)

$$CL_p = \sum_{i \in V, M(i) = p} w_i, \qquad 1 \le p \le K$$

(3.2)

of each processor balanced. Here, M(i) = p denotes the label (p) of the processor that task i is mapped to. In Eq. (3.1), each edge (i,j) of the TIG contributes to the communication cost (CC), only if vertices i and j are mapped to two different nodes of the PCG, i.e.,  $M(i) \neq M(j)$ . The amount of contribution is equal to the product of the volume of interaction  $e_{ij}$  between these two tasks and the unit communication cost  $d_{pq}$  between processors p and q where p = M(i) and q = M(j). The computational load of a processor is the summation of the weights of the tasks assigned to that processor. Perfect load balance is achieved if  $CL_p = (\sum_{i=1}^N w_i)/K$  for  $1 \leq p \leq K$ . Balancing of the

computational loads of the processors can be explicitly included in the cost function using a term which is minimized when the loads of the processors are equal. Another scheme is to include balancing criteria implicitly in the algorithm. Figure 3.1 illustrates a sample mapping problem instance with N=8 tasks to be mapped onto K=4 processors. Figure 3.1(a) shows the TIG with N=8 tasks. Figure 3.1(b) shows the POG for a 2-dimensional hypercube, and Figure 3.1(c) shows the corresponding PCG. In Figure 3.1, numbers inside the circles denote the vertex labels, and numbers within the parenthesis denote the vertex or edge weights. Binary labeling of the 2-dimensional hypercube is also given in Figure 3.1(b). Note that unit communication cost assignment to edges is performed assuming software routing protocol for multi-hop communications. A solution to the mapping problem instance shown in Figure 3.1 is

Communication cost of this solution can be calculated as

$$CC = \sum_{(i,j)\in E}^{8} e_{ij} d_{M(i)M(j)} = 8$$

(3.3)

Computation loads of the processors are  $CL_p = 3$  for  $1 \le p \le 4$ . Hence, perfect load balance is achieved since,  $(\sum_{i=1}^{8} w_i)/4 = 3$ .

#### 3.3 Solving the Mapping Problem Using MFA

In this section, a formulation of the Mean Field Annealing (MFA) algorithm for the mapping problem is proposed. The TIG and PCG models described in Section 3.2 are used to represent the mapping problem. The formulation is first presented for problems modeled by dense TIGs. The modification in the formulation for mapping problems that can be represented by sparse TIGs is presented later. In this section, an efficient implementation scheme for the proposed formulation is also presented.

Figure 3.1. A mapping problem instance, with (a) TIG, (b) POG (which represents a 2-dimensional hypercube) and (c) PCG.

### 3.3.1 Formulation

A spin matrix, which consists of N task-rows and K processor-columns, is used as the representation scheme. Hence,  $N \times K$  spins are used to encode the solution. The output  $s_{ip}$  of a spin (i,p) denotes the probability of mapping task i to processor p. Here,  $s_{ip}$  is a continuous variable in the range  $0 \le s_{ip} \le 1$ . When MFA algorithm reaches to a solution, spin values converge to 1 or 0 indicating the result. If  $s_{ip}$  is 1, this means that task i is mapped to processor p. For example, a solution to the mapping instance given in Figure 3.1 can be represented by the following  $N \times K$  spin matrix.

Note that, this solution is identical to the solution given at the end of Section 3.2.

Following energy (i.e., cost) function is proposed for the mapping problem

$$H(s) = \frac{1}{2} \sum_{i=1}^{N} \sum_{j \neq i} \sum_{p=1}^{K} \sum_{q \neq p} e_{ij} s_{ip} s_{jq} d_{pq} + \frac{r}{2} \sum_{i=1}^{N} \sum_{j \neq i} \sum_{p=1}^{K} s_{ip} s_{jp} w_i w_j$$

(3.4)

Here,  $e_{ij}$  denotes the edge weight between the pair of tasks i and j, and  $w_i$  denotes the weight of task i in TIG. Weight of the edge between processors p and q in the PCG is represented by  $d_{pq}$ .

Under the mean field approximation, the expression  $\langle H(\mathbf{s}) \rangle$  for the expected value of objective function given in Eq. (3.4) will be similar to the expression given for  $H(\mathbf{s})$  in Eq. (3.4). However, in this case,  $s_{ip}$ ,  $s_{iq}$  and  $s_{jp}$  should be replaced with  $\langle s_{ip} \rangle$ ,  $\langle s_{iq} \rangle$  and  $\langle s_{jp} \rangle$  respectively. For the sake of simplicity,  $s_{ip}$

is used to denote the expected value of spin (i, p) (i.e., spin average  $\langle s_{ip} \rangle$ ) in the following discussions.

In Eq. (3.4), the term  $s_{ip} \times s_{jq}$  denotes the probability that task i and task j are mapped to two different processors p and q, respectively, under the mean field approximation. Hence, the term  $e_{ij} \times s_{ip} \times s_{jq} \times d_{pq}$  represents the weighted interprocessor communication overhead introduced due to the mapping of the tasks i and j to different processors. Note that, in Eq. (3.4), the first quadruple summation term covers all processor pairs in the PCG for each edge pair in the TIG. Hence, the first quadruple summation term denotes the total interprocessor communication cost for a mapping represented by an instance of the spin matrix. Then, minimization of the first quadruple summation term corresponds to the minimization of the interprocessor communication overhead for the given mapping problem instance.

Second triple summation term in Eq. (3.4) computes the summation of the inner products of the weights of the tasks mapped to individual processors for a mapping. Global minimum of the second triple summation term occurs when equal amount of task weights are mapped to each processor. If there is an imbalance in the mapping, second triple summation term increases with the square of the weight of the imbalance, penalizing imbalanced mappings. The parameter r in Eq. (3.4) is introduced to maintain a balance between the two optimization objectives of the mapping problem.

Using the mean field approximation described in Eq. (2.8), the expression for the mean field  $\phi_{ip}$  experienced by spin (i, p) can be found to be

$$\phi_{ip} = -\sum_{j \neq i}^{N} \sum_{q \neq p}^{K} e_{i,j} s_{jq} d_{pq} - r \sum_{j \neq i}^{N} s_{jp} w_i w_j$$

(3.5)

In a feasible mapping, each task should be mapped exclusively to a single processor. However, there exists no penalty term in Eq. (3.4) to handle this feasibility constraint. This feasibility constraint is explicitly handled while updating the spin values. Note that, from Eq. (2.4), individual spin average  $s_{ip}$  is proportional to  $e^{\phi_{ip}/T}$ , i.e.  $s_{ip} \propto e^{\phi_{ip}/T}$ . Then,  $s_{ip}$  is normalized as

$$s_{ip} = \frac{e^{\phi_{ip}/T}}{\sum_{q=1}^{K} e^{\phi_{iq}/T}}$$

(3.6)

This normalization enforces the summation of each row of the spin matrix to be equal to unity. Hence, it is guaranteed that all rows of the spin matrix will have only one spin with output value 1 when the system is stabilized.

Eq. (3.5) can be interpreted in the context of the mapping problem as follows. First double summation represents the rate of increase expected in the total interprocessor communication cost by mapping task i to processor p. Second summation represents the rate of increase in the computational load balance cost associated with processors p by mapping task i to processor p. Hence,  $-\phi_{ip}$  may be interpreted as the expected rate of decrease in the overall quality of the mapping by mapping task i to processor p. Then, in Eq. (3.6),  $s_{ip}$  is updated such that the probability of task i being mapped to processor p increases with increasing mean field  $\phi_{ip}$  experienced by spin (i, p). Hence, the MFA heuristic can be considered as a gradient-descent type algorithm in this context. However, it is also a stochastic algorithm similar to SA due to the random spin update scheme and the annealing process.

In the general MFA algorithm given in Figure 2.2, a randomly chosen spin is updated at a time. However, in the proposed formulation of the MFA for the mapping problem, K spins of a randomly chosen row of the spin matrix are updated at a time. This update operation is performed as follows. Mean fields  $\phi_{ip}$ ,  $(1 \le p \le K)$  experienced by the spins at the *i*-th row of the spin matrix are computed by using Eq. (3.5) for p = 1, 2, ..., K. Then, the spin averages  $s_{ip}$ ,  $1 \le p \le K$  are updated using Eq. (3.6) for p = 1, 2, ..., K. Each row update of the spin matrix is referred as a single iteration of the algorithm.

The system is observed after each spin-row update in order to detect the convergence to an equilibrium state for a given temperature [34]. If energy function H is not decreasing after a certain number of consecutive spin-row updates, this means that the system is stabilized for that temperature [34]. Then, T is decreased according to the cooling schedule, and iteration process is re-initiated. Note that, the computation of the energy difference  $\Delta H$ , necessitates the computation of H (Eq. (3.4)) at each iteration. The complexity of computing H is  $O(N^2 \times K^2)$ , which drastically increases the complexity of one iteration of MFA. Here, we propose an efficient scheme which reduces the

complexity of energy difference computation by an asymptotical factor.

The incremental energy change  $\delta H_{ip}$  because of the incremental change  $\delta s_{ip}$  in the value of an individual spin (i, p) is

$$\delta H = \delta H_{ip} = \phi_{ip} \delta s_{ip} \tag{3.7}$$

due to Eq. (2.5). Since, H(s) is linear in  $s_{ip}$  (see Eq. (3.4)), above equation is valid for any amount of change  $\Delta s_{ip}$  in the value of spin (i, p), that is

$$\Delta H = \Delta H_{ip} = \phi_{ip} \Delta s_{ip} \tag{3.8}$$

At each iteration of the MFA algorithm, K spin values are updated in a synchronous manner. Hence, Eq. (3.8) is valid for all spin updates performed in a particular iteration (i.e. for  $1 \le p \le K$ ). Thus, energy difference due to the spin-row update operation in a particular iteration can be computed as

$$\Delta H = \Delta H_i = \sum_{p=1}^{K} \phi_{ip} \Delta s_{ip}$$

(3.9)

where  $\Delta s_{ip} = s_{ip}^{new} - s_{ip}^{old}$ . The complexity of computing Eq. (3.9) is only O(K) since mean field  $(\phi_{ip})$  values are already computed for the spin updates.

The formulation of the MFA algorithm for the mapping problem instances with sparse TIGs is done as follows. The expression given for  $\phi_{ip}$  (Eq. (3.5)) can be modified for sparse TIGs as

$$\phi_{ip} = -\sum_{j \in Adj(i)} \sum_{q \neq p}^{K} e_{i,j} s_{jq} d_{pq} - r \sum_{j \neq i}^{N} s_{jp} w_i w_j$$

(3.10)

Here, Adj(i) denotes the set of tasks connected to task i in the given TIG. Note that, sparsity of the TIG can only be exploited in mean field computations since spin update operations given in Eq. (3.6) are dense operations which are not effected by the sparsity of the TIG.

The steps of the MFA algorithm for solving the mapping problem is given in Figure 3.2. Complexity of computing first double summation terms in Eq. (3.5) and Eq. (3.10) are  $O(N \times K)$  and  $O(d_{avg} \times K)$  for dense and sparse TIGs respectively. Here,  $d_{avg}$  denotes the average degree of the vertices of the sparse TIG. Second summation operations in Eq. (3.5) and Eq. (3.10) are both O(N) for dense and sparse TIGs. Then, complexity of a single mean field computation

- 1. Get initial temperature, and set  $T = T_0$

- 2. Initialize the spin averages  $\mathbf{s} = [s_{11}, \dots, s_{ip}, \dots, s_{NK}]$

- 3. While temperature T is in the cooling range DO

- 3.1 While H is decreasing DO

- 3.1.1 Select a task i at random.

- 3.1.2 Compute mean fields of the spins at the *i*-th row

$$\phi_{ip} = -\sum_{j\neq i}^{N} \sum_{q\neq p}^{K} e_{i,j} s_{jq} d_{pq} - r \sum_{j\neq i}^{N} s_{jp} w_i w_j$$

- 3.1.3 Compute the summation  $\sum_{p=1}^{K} e^{\phi_{ip}/T}$

- 3.1.4 Compute new spin values at the *i*-th row

$$s_{ip}^{new} = e^{\phi_{ip}/T} / \sum_{p=1}^{K} e^{\phi_{ip}/T}$$

for  $1 \le p \le K$

3.1.5 Compute the change in energy due to these spin updates

$$\Delta H = \sum_{p=1}^{K} \phi_{ip} (s_{ip}^{new} - s_{ip})$$

3.1.6 Update the spin values at the i-th row

$$s_{ip} = s_{ip}^{new}$$

for  $1 \le p \le K$

$3.2 \quad T = \alpha \times T$

Figure 3.2. MFA algorithm for the mapping problem.

is  $O(N \times K)$  and  $O(d_{avg} \times K + N)$  for dense (Eq. (3.5)) and sparse (Eq. (3.10)) TIGs respectively. Hence, complexity of mean field computations for a spin row is  $O(N \times K^2)$  for dense TIGs, and  $O(d_{avg} \times K^2 + N \times K)$  for sparse TIGs (step 3.1.2 in Figure 3.2). Spin update computations (steps 3.1.3, 3.1.4 and 3.1.6) and energy difference computation (step 3.1.5) are both O(K) operations. Hence, the overall complexity of a single MFA iteration is  $O(N \times K^2)$  for dense TIGs, and  $O(d_{avg} \times K^2 + N \times K)$  for sparse TIGs.

## 3.3.2 An Efficient Implementation Scheme

As is mentioned earlier, the MFA algorithm proposed for the mapping problem is an iterative process. The complexity of a single MFA iteration is mainly due to the mean field computations. In this section, we propose an efficient implementation scheme which reduces the complexity of the mean field computations and hence the complexity of the MFA iteration by asymptotical factors.

Assume that, *i*-th spin-row is selected at random for update in a particular iteration. The expression given for  $\phi_{ip}$  (Eq. (3.5)) can be rewritten by changing the order of summations of the first double summation term as

$$\phi_{ip} = -\sum_{q \neq p}^{K} d_{pq} \sum_{j \neq i}^{N} e_{i,j} s_{jq} - r \sum_{j \neq i}^{N} s_{jp} w_{i} w_{j}$$

$$= -\sum_{q \neq p}^{K} d_{pq} \lambda_{iq} - r \psi_{ip}$$

(3.11)

where

$$\lambda_{iq} = \sum_{j \neq i}^{N} e_{i,j} s_{jq} \tag{3.12}$$

$$\psi_{ip} = \sum_{j \neq i}^{N} s_{jp} w_i w_j \tag{3.13}$$

Here,  $\lambda_{iq}$  represents the rate of increase expected in the interprocessor communication by mapping task i to a processor other then q (for the current mapping on processor q), assuming uniform unit communication cost between all pairs of processors in PCG. Similarly,  $\psi_{ip}$  represents the rate of increase expected in the computational load balance cost associated with processor p, by mapping task i to processors p (for the current mapping on processor p).

For an efficient implementation, the overall mean field computation involved in a single iteration can be computed using the following matrix equation

$$\Phi_{i} = -D \times \Lambda_{i} - r\Psi_{i} \tag{3.14}$$

$$= -\Theta_{\mathbf{i}} - r\Psi_{\mathbf{i}} \tag{3.15}$$

Here, **D** is a  $K \times K$  adjacency matrix representing PCG (i.e.  $D_{pq} = d_{pq}$ ), and  $\Phi_{\mathbf{i}}$ ,  $\Lambda_{\mathbf{i}} \Psi_{\mathbf{i}}$  and  $\Theta_{\mathbf{i}}$  are column vectors with K elements, where

$$\Phi_{\mathbf{i}} = [\phi_{i1}, \dots, \phi_{ip}, \dots, \phi_{iK}]^{T} \quad \mathbf{\Lambda}_{\mathbf{i}} = [\lambda_{i1}, \dots, \lambda_{ip}, \dots, \lambda_{iK}]^{T}

\Psi_{\mathbf{i}} = [\psi_{i1}, \dots, \psi_{ip}, \dots, \psi_{iK}]^{T} \quad \mathbf{\Theta}_{\mathbf{i}} = [\theta_{i1}, \dots, \theta_{ip}, \dots, \theta_{iK}]^{T} \quad (3.16)$$

The complexity analysis of the proposed implementation scheme for dense TIGs is as follows. Complexity of computing  $\lambda_{ip}$  and  $\psi_{ip}$  are both O(N). Complexity of constructing  $\Lambda_{\bf i}$  and  $\Psi_{\bf i}$  vectors are both  $O(N \times K)$ , since both vectors contain K such entries. Complexity of computing the matrix-vector product required in Eq. (3.14) is  $O(K^2)$ . Hence, the overall complexity of computing the  $\Phi_{\bf i}$  vector (Eq. (3.14)) reduces to  $O(N \times K + K^2) = O(N \times K)$ , since  $N \gg K$  in general. The complexity of K spin updates and the computation of  $\Delta H$  are both O(K). Thus, the proposed scheme reduces the computational complexity of a single MFA iteration to  $O(N \times K)$  for dense TIGs with  $N \gg K$ .

The complexity analysis of the proposed implementation for sparse TIGs is as follows. Note that, the sparsity of the TIG can only be exploited in the computation of  $\lambda_{iq}$ 's since

$$\lambda_{iq} = \sum_{j \in Adi(i)}^{N} e_{i,j} s_{jq} \tag{3.17}$$

for sparse TIGs. Hence, the complexity of computing an individual  $\lambda_{iq}$  is only  $O(d_{avg})$ . Thus, the complexity of constructing the  $\Lambda_i$  vector reduces to  $O(d_{avg} \times K)$ . The complexity of computing the  $\Theta_i$  vector in Eq. (3.15) reduces to  $O(d_{avg} \times K + K^2)$ . However, the complexity of constructing the  $\Psi_i$  vector required in Eq. (3.15) is  $O(N \times K)$ , dominating the overall complexity of the mean field computations. The complexity of computing the  $\Psi_i$  vector can be reduced as follows. The computation of  $\psi_{ip}$  in Eq. (3.13) can be re-formulated

as

$$\psi_{ip} = \sum_{j \neq i}^{N} s_{jp} w_i w_j = w_i \sum_{j \neq i}^{N} w_j s_{jp} = w_i (\sum_{j=1}^{N} w_j s_{jp} - w_i s_{ip})$$

$$\psi_{ip} = w_i \gamma_p - w_i^2 s_{ip}$$

(3.18)

where

$$\gamma_p = \sum_{j=1}^N w_j s_{jp} \tag{3.19}$$

Here,  $\gamma_p$  represents the computational load of processor p, for the current mapping on processor p. Note that, computationally,  $\gamma_p$  represents weighted sum of spin values of the p-th column of the spin matrix. Hence, initial  $\gamma_p$  value of each column p ( $1 \le p \le K$ ) can be computed by using Eq. (3.19) for the initial spin values. Then,  $\gamma_p$  values can be updated at the end of each iteration (i.e. after spin updates) by using

$$\gamma_p^{new} = \gamma_p^{old} - w_i s_{ip}^{old} + w_i s_{ip}^{new} \tag{3.20}$$

for  $1 \le p \le K$ .

The computation of initial  $\gamma_p$  values can be excluded from the complexity analysis since they are computed only once at the very beginning of the algorithm. In this scheme, the computation of an individual  $\psi_{ip}$  using Eq. (3.18) is an O(1) operation. Hence, the construction of the  $\Psi_{\bf i}$  vector required in Eq. (3.14) becomes an O(K) operation. Thus, the complexity of computing the mean field values reduces to  $O(d_{avg} \times K + K^2)$ . Note that, the update of an individual  $\gamma_p$  value (using Eq. (3.20)) at the end of the iteration is an O(1) operation. Hence, the overall complexity of  $\gamma_p$  updates is O(K) since K weighted column sums should be updated at each iteration. Note that, complexity of spin updates and energy difference computation are also O(K) for sparse TIGs. Hence, the implementation scheme proposed for sparse TIGs reduces the complexity of a single MFA iteration to  $O(d_{avg} \times K + K^2)$ .

## 3.4 Performance of Mean Field Annealing Algorithm

This section presents the performance evaluation of the Mean Field Annealing (MFA) algorithm for the mapping problem, in comparison with two well-known

mapping heuristics: Simulated Annealing (SA) and Kernighan-Lin (KL). Each algorithm is tested using randomly generated mapping problem instances. In the following sections implementations are described in order to give a better understanding of the discussed algorithms.

## 3.4.1 MFA Implementation

MFA algorithm described in the previous section (Figure 3.2) is implemented for testing the performance of the algorithm. Cooling process is started from an initial temperature which is found experimentally. For the mapping problem instances used in the experiments, initial temperature  $T_0$  is found to be varying between  $1 \le T_0 \le 10$ . Coefficient r which determines the balance between two optimization criteria is also found experimentally, varying between  $0.1 \le r \le 1.5$ . At each temperature, iterations continued until  $\Delta H < \epsilon$  for L consecutive iterations. L is set equal to N initially. Parameter  $\epsilon$  is chosen to be between  $10^{-3} \le \epsilon \le 10^{-1}$ . Temperature is decreased using  $\alpha = 0.9$  until T is less than  $T_0/1.5$ . Then, L is set to L/4 and  $\alpha$  is set to 0.5 and cooling is continued until T is less then  $T_0/5.0$ . Resulting spin values after this cooling operation are set to 0 if they are less than 0.5 and set to 1 if they are greater than 0.5. Then the result is decoded as described in Section 3.3 and the resulting mapping is found.

## 3.4.2 Kernighan-Lin Implementation

Kernighan-Lin heuristic is not directly applicable to the mapping problem since it was originally proposed for graph bipartitioning. In order to apply KL heuristic to the mapping problem a two phase approach is used. In the first phase, task interaction graph  $G_T(V, E)$  is partitioned to K clusters, where K is equal to the number of processors. These K clusters are then mapped to processor graph  $G_P(P, D)$  using a one-to-one mapping heuristic in the second phase. One-to-one mapping heuristic used in this work is a variant of KL heuristic.

For the clustering phase, Kernighan-Lin heuristic is implemented efficiently

as described by Fiduccia and Mattheyses [7]. In order to apply KL to K-way graph partitioning two schemes are used. First one, partitioning by recursive bisection (KL-RB), recursively partitions the initial graph to two partitions until K partitions are obtained. Other scheme, partitioning by pairwise mincut (KL-PM), starts with an initial K-way partitioning and then minimizes the cutsizes between each pair of partitions until no improvement can be done. In KL heuristic balancing of the work load of processors is done implicitly by the algorithm. When moving one node from one partition to another, weights of the partitions are tested and moves causing intolerable imbalance are rejected.

In the beginning of second phase, K clusters formed in the first phase are mapped to the K processors of the multicomputer randomly. After this initial mapping, communication cost is minimized by performing a sequence of cluster swaps. An individual cluster swap corresponds to interchanging the mapping of a pair of clusters.

## 3.4.3 Simulated Annealing Implementation

Simulated Annealing algorithm, implemented for solving the mapping problem, uses the one phase approach to map the TIG onto PCG. In simulated annealing, starting from a randomly chosen initial configuration, configuration space is searched for the best solution using a probabilistic hill climbing algorithm. A configuration of the mapping problem is a mapping between TIG and PCG, which assigns each task in TIG to a processor in PCG. In order the search the configuration space, neighborhood of a configuration must be defined. For the implementation in this work, neighborhood of a configuration consists of all configurations which results with moving one vertex (task) of the TIG from the maximum loaded node (processor) of the PCG to another node of PCG. At each iteration of the simulated annealing algorithm, one of the possible moves is chosen randomly as a candidate move. Then the resulting decrease in the total communication cost after performing the candidate move is calculated without changing the configuration. If the candidate move decreases the cutsize, it is realized. If candidate move increases the cutsize, then it is realized with a probability which decreases with the increasing positive difference caused in the

total cutsize by that move. Acceptance probability of the moves that increases the cost is controlled with a temperature parameter T which is decreased using an annealing schedule. Hence, as the annealing proceeds acceptance probability of uphill moves decreases. Cooling schedule used in the implementation of SA algorithm is similar to the schedule given in [22].

## 3.4.4 Experimental Results

In this section, performance of the MFA algorithm is discussed in comparison with SA and KL algorithms. These heuristics are experimented for mapping randomly generated TIGs onto mesh and hypercube connected multicomputers.

Six test TIGs are generated with N=200 and 400 vertices. Vertices of these TIGs are weighted by assigning a randomly chosen integer weight between 1 and 10 to each vertex  $(1 \le w_i \le 10$ , for  $1 \le i \le N)$ . Interaction patterns among the vertices of these TIGs are constructed as follows. A maximum vertex degree,  $d_{max}$ , is selected for each test TIG  $(d_{max} = 8, 16, 32)$  such that, degree  $d_i$  of each vertex i is a randomly chosen value between 1 and  $d_{max}$  (i.e.  $1 \le d_i \le d_{max}$ , for  $1 \le i \le N$ ). Then, each vertex i of TIG is connected to  $d_i$  randomly chosen vertices. Resulting edges are weighted randomly with integer values varying between 1 and 10. These TIGs are mapped to 3-, 4-, 5-dimensional hypercubes and  $4 \times 4$ ,  $4 \times 8$  two dimensional mesh multicomputers. PCGs corresponding to these interconnection topologies are constructed assuming software routing as is described in Section 3.2.